Signal Integrity for High Speed Digital Design 对高速数字信号完整性设计

cadence仿真步骤(精)

CDNLive! Paper – Signal Integrity (SI for Dual Data Rate (DDR Interface Prithi Ramakrishnan iDEN Subscriber Group Plantation, Fl Presented atIntroduction The need for Signal Integrity (SI analysis for printed circuit board (PCB design has become essential to ensure first time success of high-speed, high-density digital designs. This paper will cover the usage of Cadence’s Allegro PCB SI tool for the design of a dual data rate (DDR memory interface in one of Motorola’s products. Specifically, this paper will describe the following key phases of the high-speed design process: Design set-up Pre-route SI analysis Constraint-driven routing Post-route SI analysis DDR interfaces, being source synchronous in nature, feature skew as the fundamental parameter to manage in order to meet setup and hold timing margins. A brief overview of source synchronous signaling and its challenges is also presented to provide context. Project Background This paper is based on the design of a DDR interface in an iDEN Subscriber Group phone that uses the mobile Linux Java platform. The phone is currently in the final stages of system and factory testing, and is due to be released in the market at the end of August 2007 for Nextel international customers. The phone has a dual-core custom processor with an application processor (ARM 11 and a baseband processor (StarCore running at 400MHz and 208MHz respectively. The processor has a NAND and DDR controller, both supporting 16-bit interfaces. The memory device used is a multi-chip package (MCP with stacked NAND (512Mb and DDR (512Mb parts. The NAND device is run at 22MHz and the DDR at 133MHz. The interface had to be supported over several memory vendors, and consequently had to account for the difference in timing margins, input capacitances, and buffer drive strengths between different dies and packages. As customer preference for smaller and thinner phones grows, the design and placement of critical components and modules has become more challenging. In addition to incorporating various sections such as Radio Frequency (RF, Power Management, DC, Audio, Digital ICs, and sub-circuits of these modules, design engineers must simultaneously satisfy the rigid placement requirements for components such as speakers, antennas, displays, and cameras. As such, there arevery few options and little flexibility in terms of placement of the components. This problem was further accentuated by the fact that several layers of the 10 layer board (3-4-3 structure with one ground plane and no power planes were reserved for power, audio, and other high frequency (RF nets, leaving engineers with few layers to choose from for digital circuitry.Figure 1. Memory Interface routes With the DDR interface data switching at266MHz, we had very tight margins — 600ps for data/DQS lines, 280ps for the address lines, and 180ps for control lines. However, with the NAND interface we had larger margins that were on the order of a few tens of nanoseconds. In these situations, choosing a higher drive strength and using terminators of appropriate values (to meet rise times and avoid overshoot/undershoot has become a common practice in DDR designs. However, due to the lack of space on the board, we were not in a position to use terminators. Therefore, we used programmable buffers on our processor, and with the help of Cadence SI tools were able to fine-tune the design. Our group migrated from using Mentor Graphics to Cadence SI during this project. As one might expect, this made the task of designing a high speed DDR interface even more challenging. To help overcome this, we worked extensively with Cadence Services, where Ken Willis supported us on the SI portion of the design. The Source Synchronous Design Challenge Before discussing the specifics of the Motorola DDR interface, a brief overview of source synchronous signaling is provided here for context. Historically, digital interfaces have utilized “common clock” signaling, as shown in the figure below.Clock Driver Tco Interconnect Delay D0 D1 D2 D0 D1 D2 Drive Receive Figure 2. Common clock design With common clock interfaces, the clock signal is provided to the driving and receiving components from an external component. The magnitude of the driver’s Tco (time from clock to output valid and the interconnect delay between the driving and receiving components becomes a limiting factor in the timing of the interface. From a practical standpoint, it becomes increasingly challenging to implement interfacesof this type above several hundred megahertz. In order to accommodate requirements for faster data rates, source synchronous signaling emerged as the new paradigm. This is illustrated in the figure below. Strobe D 0 D 1 D 0 D 1 Drive Receive Figure 3. Source synchronous design.In a source synchronous interface, the “clock” is prov ided locally by the driving component, and is generally called a “strobe” signal. The relationship between the strobe and its associated data bits is known as it leaves the driving component, with setup and hold margins pre-established as the signals are put onto the bus. Tsetup Thold Figure 4. Timing diagram. This essentially takes the driver’s Tco as well as the magnitude of the interconnect delay between the driving and receiving chip out of the timing equation altogether. The timing challenge then becomes to manage the skew between the data and strobe signals such that the setup and hold requirements at the receiving end are still met. Technical Approach The general technical approach used in this project can be broken down into the following key phases of the high-speed design process: Design set-up Pre-route SI analysis Constraint-driven routing Post-route SI analysis First the PCB design database is set up to enable analysis with Allegro PCB SI. Before routing is performed, initial trade-offs are examined at the placement stage, and constraints are captured to facilitate constraint-driven routing. When routing is completed, detailed analysis is performed, interconnect delays extracted, and setup/hold margins are computed. Any adjustments required are fed back to the layout designer, and the postroute analysis is repeated. This basic process is diagrammed below.Detail on the major design phases are provided in the subsequent sections.By virtue of its direct integration with the Allegro PCB layout database, Allegro SI analysis requires that the design be set up to facilitate the automated extraction, circuit building, netlisting, simulation, and analysis that it performs. This essentially means adding the needed intelligence to the physical Allegro database that allows the tool to do its job. This setup involves the following:•Cross section•DC nets•Device definitions•SI modelsBy definition, SI analysis involves the modeling of interconnect parasitics. In order to do this accurately, the tool needs to know the properties and characteristics of the materials used in the PCB stack-up. This information is defined in the Cross Section form, as shown below.It is crucial to get this data correct, as it will be fed to the 2D field solver to model interconnect parasitics during the extraction process. The best source for this detailed information is generally from the PCB fabricator. Layer thickness, dielectric constant, and loss tangent are all critical parameters for the cross section definition.In order for circuit extraction to be done properly, the tool needs to know about DC nets in the design, and what their associated voltage levels are. This accomplishes two main things in the setup; a enables voltage sources to be injected properly in the extracted circuits, and b avoids having the tool needlessly trying to extract extremely large DC nets, and hanging up the analysis process. Take the example of a parallel resistor termination. Allegro SI will encounter the resistor as it walks the signal net to be extracted. The tool will look up the SI model assigned to this resistor, splice in the resistor subcircuit, and continue extracting whatever is on the other side of the resistor. If this is a large DC net (ex. VTT, the desire is for the tool to put a voltage source at the 2nd resistor pin, complete the circuit, and simulate the signal. To do this properly, the tool relies on a VOLTAGE property to exist on the DC net, with a numeric value defined. In the absence of the VOLTAGE property, the tool will simply continue to extract, which in the case of a 2000 pin ground net, would be a large waste of computational time.To identify DC nets, clicking “Logic > Identify DC Nets” will spawn the following form.All DC nets in the design should be identified, to fully optimize SI analysis. These can be identified up front in the schematic, as well as in the physical layout as shown here.The next step in the design set-up process is to verify that the logical “CLASS” and “PINUSE” attributes for the devices in the d esign are defined appropriately. These attributes originate from the schematic symbol libraries and are passed into the Allegro physical layout environment. In an ideal methodology, these libraries would be defined properly and would require no edits. However, this is not always the case, and as these attributes have a bearing on the behavior of the SI analysis, it is worth mention here.The “CLASS” attribute is used to distinguish between different types of components in the PCB design. Legal values of “CLASS” are listed below:•IC – This is used for digital integrated circuits, which contain drivers and/or receivers. These types of components are modeled with an SI model of the type “IbisDevice”. When the automated circuitbuilding algorithms in Allegro PCB SI encounter a model of this type, it looks up the buffer model (driver, receiver, or bidirectional assigned to the pin in question, and inserts it into the circuit along with its associated package parasitics.•IO – A component with CLASS = IO is intended for components that connect off-card to other physical layout designs, such as connectors. These components can be associated with a “DesignLink”, which provides netlisting to other physical designs and enables multi-board SI analysis. So circuit building algorithms expect to jump from a device of CLASS=IO to a similar device on a different physical layout.•DISCRETE – For devices of this class, circuit building algorithms expect to traverse “through” the component, from one pin to another, inserting a s ubcircuit in-between. A good example of this would be a series resistor.If CLASS attributes are not set up properly in the source schematic libraries, they can be edited in the physical layout database for analysis by using the form shown below, launched from the “Logic > Parts List” menu pick. The “PINUSE” attribute also impacts the behavior of the SI analysis, as the tool uses this information to determine if a pin is a driver, receiver, bidirectional, or passive pin. As with the “CLASS” attribute, in an idealmethodology this is defined properly in the schematic libraries, and no editing is required in physical layout. “PINUSE” can be modified in two main ways for SI purposes. The most straightforward way is to ensure that the IOCell models used in the IbisDevice models assigned to components have the appropriate Model Type for the signals they are associated to. When SI models are assigned to components, the tool will check for conflicts between the model and the PINUSE it finds for the component in the design, and will use the SI model to automatically override the PINUSE found in the drawing. So if the correct pin types are found in the SI models, the layout will automatically inherit those settings. For components not explicitly modeled, their PINUSE can be set using the form shown below, launched from the “Logic > Pin Type” menu pick.Signal Integrity (SI models can be assigned using the “Signal Model Assignment” form, shown below.Upon clicking “OK” the selected models will be assigned to the c omponents and saved directly in the layout database. As mentioned previously, “PINUSE” attributes will be synced up, with the SI models superseding attributes in the original layout drawing.Performing pre-route analysis is a key part of the high-speed design process. Once critical componentplacement has been done, Manhattan distances can be used to estimate trace lengths, and can provide a realistic picture of how routed interconnect will potentially perform.Before simulations are run for critical signals, the timing of the interface must be well understood. Toaccomplish this, we will first sketch timing diagrams for each signal group and then extract a representative signal for analysis. Next, we will explore Z0, layer assignments, drive strength, route lengths, spacing, and terminations for these nets.To sketch the timing diagrams, we first analyze the memory interface. The memory interface consists of both DDR and NAND signals and has around seventy nets. To simplify the analysis of the interface, we first divide these nets based on function and then simulate one net from each group. Accordingly, we select one signal from each of the following groups — clock_ddr, strobe_ddr , data_ddr, control_ddr, address_ddr, control_nand, and data_nand — for our pre-route simulations.To understand the timing relations in the interface, we should look at the following operations between the memory device and the processor — read , write , address write, and control operations. Next, we identify the nets involved and the clocking reference signal for each of these operations. We then calculate the worst case slack available from the setup and hold numbers available in the data sheets. In particular, we adopted the worst case numbers across four different memory vendors, to ensure robustness of the manfactured system in the field..1. ReadDuring the read operation, the memory drives the data and DQS lines. The processor has a delay line (a series of buffers which can be tapped at different points, which is used to delay the DQS signal so that it samples the data at quarter of the cycle. The processoralso offers programming options that allow us to apply an offset to the quarter cycle, enabling us to meet our setup and hold times. Hence, the processor self-corrects forstrobe/data skew using this delay line. The granularity of this delay line is 30 ps; that is, each of the buffers of the delay line contributes 30 ps of delay. The data lines 0-7 are clocked with respect to the DQS0 strobe signal, and the data lines 8-15 are clocked with respect to DQS1. Data and strobe lines should be clustered, with the matching constraints determined by the write cycle.2. WriteFigure 7. Write operation at memory interface.During the write operation, both data and DQS are driven by the processor. Data is latched at both the positive and the negative edges of the DQS signals. Here again, data bits 0-7 are clocked by DQS0 and data bits 8-15 are clocked by DQS1. The setup and hold times available as these signals come out of the DDR controller are1.58ns and 1.7ns respectively and the corresponding times required at the memory to ensure correct operation is 0.9ns. Hence, the slack available for routing is the lesser of 1.58ns – 0.9ns or 1.7ns – 0.9ns, which comes out to be 0.68ns. This amounts to an allowable ~85mm mismatch between the data lines. In addition, we need tomake sure that length of the DQS lines is around the average of all the data lines. The data mask signals DQM0 and DQM1 also come into play during the write operation and we should group them along with the respective data lines.3. Address busFigure 8. Address bus operation at memory interface.Both address and clock lines are driven by the processor. The address bits 0-12 are clocked by the differential clock and latched at the positive edge of the clock. The setup and hold times available for these signals from the DDR controller are 1.78ns and 4.22ns respectively and the corresponding times required at the memory to ensure correct operation is 1.5ns for both. Hence the worst case slack for routing is 0.28ns and we have to try to match our signals to meet these numbers. The 0.28ns slack amounts to ~14mm mismatch between the address lines and the clock.4. Control linesFigure 9. Control lines at memory interface.The control signals are clocked by the differential clock and latched at the positive edge of the clock. The setup and hold times coming out of the DDR controller are 1.64ns and 4.04ns respectively. The setup and hold times required at the memory to ensure correct operation is 1.5ns. Hence, the worst case slack for routing is 0.14ns and we have to try and match our signals to meet these numbers. The 0.14 ns slack amounts to ~7mm mismatch between the control lines and the clock.In addition, CLK to DQS skew is around 600 ps. With regards to the NAND lines, setup and hold numbers are in the order of tens of ns and hence routing them as short as possible based on their Manhattan lengths would suffice.To complete pre-route analysis, SigXplorer must be setup for these tasks:a. Extract a topology file for single net analysis. To bring up the net in SigXplorer, it is essential that the models are assigned, as described in Section 2, to each of the drivers, receivers, and components in the signal path.b. Set up parameters for extraction and simulate using SigXplorer.c. Perform measurements using SigWaveThe following screenshots of SigXplorer show this process in detail.Figure 10. SigXplorer screenshots.Since at this point none of the nets in the design are routed we need to set the percent Manhattan section for unrouted interconnect models. We should then select the net, as shown in the next screenshot, for analysis. Analyze Æ SI/EMI Sim Æ Preferences The speed at which the signaltravels in the trace, where Cis 3 x 108 m/s and Ereff is theeffective dielectric constantseen in the interconnectSets the defaultlengthtransmissionlinesAt this point, it is important to check if your driver and receiver pins are set correctly. The net chosen in the above example is a data net, it is bi-directional, hence it can be driven both by the memory device as well as the processor. The view topology icon can be clicked to export this net in SigXplorer.The tool extracts the net along with drivers, receivers and strip lines on various layers of the board. Before you start the simulation, you must set the stimulus frequency, pulse step offset, and cycle count. This can be set in the following GUI.Analyze Æ PreferencesBoth the memory device and the processor have programmable drive strengths. The buffer model can bechanged to pick up the various drive strengths that are available in the dml models of the devices till we observe satisfactory waveforms in SigWave.Analyze Æ SI/EMI Sim ÆprobeinvokesSigXplorerSigXplorer allows you to sweep any of the parameters such as the thickness, length, drive strengths and displays corresponding settle/switch delays, monotonicity, and glitch tolerance for the corresponding simulation. It also allows adding components such asre sistors and capacitors and let’s us sweep their values. We added a resistor in series with our clock in or to get rid of ringing in the rising edge. The tool let us determine what values were suitable for this resistor. As shown in the next figure the waveform corresponding to our simulation can be brought up on SigWave.You can observe the rise/fall times, look for noise margins, overshoot/undershoot of the receiver waveform.The constraints we develop in the pre-route simulation will be used by the routing tool to ensure correct first time results. This leads to our next section; Constraint-driven routing. Once pre-route analysis has been done, and trade-offs have been examined, signal wiring constraints need to be developed to drive the constraint-driven routing process. With the DDR interface being point-to-point between the processor and memory, we translated our timing requirements into length constraints to make the routing as straightforward as possible. We also assigned layer constraints for our DDR signals. Both the length and the layer constraints can be directly applied to the constraint manager before the routing process starts.For our particular design, we determined the following layer assignments from the results of the pre-route simulatio ns, taking into account the layer’s characteristic impedance per our stack-up:Layer 6 Æ ground planeLayer 7 Æ clock, add, ctrlLayer 8 Æ data, strobeLayer 9 Æ NAND interfaceBefore we set up our design for auto-routing, we routed the differential clock lines manually on the layers closest to the ground plane. For the rest of the nets, the layer constraints can be created as shown in thefollowing snapshots of the constraint manager.Electrical Constraint Set Æ WiringRight click on board Æ Create new constraintName the constraint (ex. ECSET1We choose one layer with horizontal orientation and one with vertical for each of our layer sets. You can form groups from the available layer sets and create a new constraint. This constraint, which we define as ECSET1, can be easily read back in the constraint manager and applied to the relevant net group, as shown in the following snapshot.We determined from pre-route analysis the slack available for each of our net groups; however, before we translate these into length constraints it is important to get a report of the Manhattan lengths of each of these signals. To illustrate this, we will focus on the address signals. The Manhattan report of the address lines showed that the shortest lines were 6mm and the longest were 17mm. Accordingly, the minimum length constraint must be longer than 6mm and the maximum length constraint must be longer than 17mm.Additionally, from our timing diagrams, we determined that the maximum spread can be no more than 14mm.Following these restrictions, we set the minimum and maximum length limits for the address line are 11.99 mmto 18.99 mm (shown in the constraint editor window below. Based on the layout designer's recommendations, we were able to constrain a bit tighter (7mm margin and produce better margins.To enter the length constraint, we open the Net Æ Routing ÆTotal etch length section of the constrain manager. We followed this procedure for all the other net groups. The snapshot that follows shows length constraints associated with the address lines. Here, the key is to not to over-constrain your design, but at the same time have enough constraints so the timing and signal integrity parameters are met. Over-constraining the design severely inhibits the auto-router and may leave large portions of the design (as much as 90% un-routed.Once the design is fully routed, detailed simulations can be run for post-route verification. The goal at this phase is to determine final margins over all corners, and find and correct any SI or timing-related issues before the board is released for fabrication. Before starting simulation, it is important to verify that the design is properly routed andthat it meets the specifications/constraints. In particular, it is essential to verify that the design does not include dangling and partially-routed/un-routed nets. We must also verify that all the nets meet the length constraints assigned to them. The Constraint Manager window helps identify nets that are inviolation (shown in red and nets that are in compliance (in green. For convenience and clarity, the Constraint Manager also reports the actual route length and the Manhattan lengths for each net.The next step is to bring up the physical layout and visually inspect the nets to ensure that each net is routed in its appropriate layer, or run DRCs if the signals were explicitly limited to specific layers in Physical Constraint Sets. When test points are associated with a net, we must manually verify that the points are in line with the nets (and are not stubs hanging off the nets. Note that when using the simplerTotal_Etch_Length constraint, the auto-router can meet routing length constraints for the net, even when there are stubs in the design. Thesestubs can produce undesirable effects such as reflections and hence this step is important. If there are too manycritical signals to check manually on larger designs, this check can be automated by using an explicit topology and stub length constraints. After manual inspection, we begin post–route simulation and generate reports to analyze the design. We then export the reports to an Excel spreadsheet to facilitate analysis.We generated both delay and reflection reports. The delay report provides information on timing parameters such as propagation delay, switch and settle rise and fall times. The reflection report presents data on signal integrity parameters such as overshoot, undershoot, noise margin, monotonicity, and glitch. Preparing the design for post-route simulation involves the selection of various options in the SI\EMI Sim preferences list. The following screen display describes this process.In the form above, we set up the frequency of the stimulus and the duty cycle. We also set up V meas as the reference for delay calculations. Choosing the reference as V meas , rather than V IH and V IL , makes analysis much easier and is in accordance with the memory datasheet. We chose V meas as 0.9V which is half of the peak-to-peak voltage swing (1.8V.Now that the design is routed, we need to set the parameters for routed interconnects. Here you can specify the minimum coupling distance for nets for the tool to recognize it as a differential pair. This can be done by invoking Analyze Æ SI ÆPref ÆInterconnect Models.Analyze Æ SI/EMI Sim Æ preferencesThe preceding screenshot shows the option that allows us to select the delay and reflection reports. In this form, we also choose all three simulation modes — fast, typical, and slow — to cover all corner cases. In our experience, running typical mode simulations were not enough to determine final timing margins over process, voltage, and temperature. So, we exported the reports to an Excel spread sheet and analyzed the results. Reflection and delay reports simulate only a primary net and none of its neighbors. As a result, these reports do not take into consideration the parasitics of the power and ground pins.Note:All timings in ns unless labelled otherwise.Component Timingdriving to MemoryTsetup 1.64Tsetup 1.5Thold 4.04Thold 1.5Skew_max = 1.64 - 1.5 = 140ps between clock and controlSkew_max=0.14Clock/Strobe RelationshipsSdram_Ctrl<6:7> is differential clockInterconnect TimingXNet Drvr Rcvr PropDly SettleRise SettleFall AvgSettleSDRAM_CTRL<6>U800 V2_UU2164 C7_U2160.1420291.138511.205381.172SDRAM_CTRL<0>U800U21640.11181.1911.2351.1041.2350.0680.0630.0680.072SDRAM_CTRL<10>U800U21640.12541.1651.207SDRAM_CTRL<11>U800U21640.11141.1411.187SDRAM_CTRL<12>U800U21640.12171.1781.221SDRAM_CTRL<13>U800U21640.10671.1141.153SDRAM_CTRL<14>U800U21640.098231.1041.143SDRAM_CTRL<2>U800U21640.12741.1631.205SDRAM_CTRL<3>U800U21640.091631.1081.153SDRAM_CTRL<8>U800U21640.10811.1371.182SDRAM_CTRL<4>U800U21640.069591.1431.247SDRAM_CTRL<5>U800U21640.08621.1691.285The preceding spreadsheet was created with data from delay reports and was used to analyze the control lines with respect to the clock. The clock signal in our design is called SDRAM_CTRL<6>. The sheet also lists the driver (U800, the processor, receiver(U2164, memory device, propagation delay (0.142029 ns, settle rise (1.13851 ns, and settle fall (1.20538 ns values. The average settle delay (1.172 ns is calculated by averaging the settle rise and settle fall numbers.The control nets SDRAM<0> to SDRAM_CTRL <14> are listed next to the corresponding drivers, receivers, propagation delays, settle rise and settle fall delays. We then look for the minimum and maximum delays of all the settle rise and settle fall delays. These are listed under maximum settle delay (1.235 ns and minimum settle delay (1.104 ns respectively. Using these numbers, we calculate the maximum settle skew (0.063 ns, which is the difference between the maximum settle delay (1.235ns and the average settle。

SIGNALINTEGRITY(信号完整性)外文翻译

SIGNAL INTEGRITYRaymond Y. Chen, Sigrid, Inc., Santa Clara, CaliforniaIntroductionIn the realm of high-speed digital design, signal integrity has become a critical issue, and is posing increasing challenges to the design engineers. Many signal integr ity problems are electromagnetic phenomena in nature and hence related to the EMI/EMC discussions in the previous sections of this book. In this chapter, we will discuss what the typical signal integrity problems are, where they come from, why it is important to understand them and how we can analyze and solve these issues. Several software tools available at present for signal integrity analysis and current trends in this area will also be introduced.The term Signal Integrity (SI) addresses two concerns in the electrical design aspects – the timing and the quality of the signal. Does the signal reach its destination when it is supposed to? And also, when it gets there, is it in good condition? The goal of signal integrity analysis is to ensure reliable high-speed data transmission. In a digital system, a signal is transmitted from one component to another in the form of logic 1 or 0, which is actually at certain reference voltage levels. At the input gate of a receiver, voltage above the reference value Vih is considered as logic high, while voltage below the reference value Vil is considered as logic low. Figure 14-1 shows the ideal voltage waveform in the perfect logic world, whereas Figure 14-2 shows how signal will look like in a real system. More complex data, composed of a string of bit 1 and 0s, are actually continuous voltage waveforms. The receiving component needs to sample the waveform in order to obtain the binary encoded information. The data sampling process is usually triggered by the rising edge or the falling edge of a clock signal as shown in the Figure 14-3. It is clear from the diagram that the data must arrive at the receiving gate on time and settle down to a non-ambiguous logic state when the receiving component starts to latch in. Any delay of the data or distortion of the data waveform will result in a failure of the data transmission. Imagine if the signal waveform in Figure 14-2 exhibits excessive ringing into the logic gray zone while the sampling occurs, then the logic level cannot be reliably detected.SI ProblemsT ypical SI Problems“Timing” is everything in a high-speed system. Signal timing depends on the delay caused by the physical length that the signal must propagate. It also depends on the shape of the waveform w hen the threshold is reached. Signal waveform distortions can be caused by different mechanisms. But there are three mostly concerned noise problems:•Reflection Noise Due to impedance mismatch, stubs, visa and other interconnect discontinuities. •Crosstalk Noise Due to electromagnetic coupling between signal traces and visa.•Power/Ground Noise Due to parasitic of the power/ground delivery system during drivers’ simultaneous switching output (SSO). It is sometimes also called Ground Bounce, Delta-I Noise or Simultaneous Switching Noise (SSN).Besides these three kinds of SI problems, there is other Electromagnetic Compatibility or Electromagnetic Interference (EMC/EMI) problems that may contribute to the signal waveform distortions. When SI problems happen and the system noise margin requirements are not satisfied – the input to a switching receiver makes an inflection below Vih minimum or above Vil maximum; the input to a quiet receiver rises above V il maximum or falls below Vih minimum; power/ground voltage fluctuations disturb the data in the latch, then logic error, data drop, false switching, or even system failure may occur. These types of noise faults are extremely difficult to diagnose and solve after the system is built or prototyped. Understanding and solving these problems before they occur will eliminate having to deal with them further into the project cycle,and will in turn cut down the development cycle and reduce the cost[1]. In the later part of thischapter, we will have further investigations on the physical behavior of these noise phenomena, their causes, their electrical models for analysis and simulation, and the ways to avoid them.1. Where SI Problems HappenSince the signals travel through all kinds of interconnections inside a system, any electrical impact happening at the source end, along the path, or at the receiving end, will have great effects on the signal timing and quality. In a typical digital system environment, signals originating from the off-chip drivers on the die (the chip) go through c4 or wire-bond connections to the chip package. The chip package could be single chip carrier or multi-chip module (MCM). Through the solder bumps of the chip package, signals go to the Printed Circuit Board (PCB) level. At this level, typical packaging structures include daughter card, motherboard or backplane. Then signals continue to go to another system component, such as an ASIC (Application Specific Integrated Circuit) chip, a memory module or a termination block. The chip packages, printed circuit boards, as well as the cables and connecters, form the so-called different levels of electronic packaging systems, as illustrated in Figure 14-4. In each level of the packaging structure, there are typical interconnects, such as metal traces, visa, and power/ground planes, which form electrical paths to conduct the signals. It is the packaging interconnection that ultimately influences the signal integrity of a system.2. SI In Electronic PackagingTechnology trends toward higher speed and higher density devices have pushed the package performance to its limits. The clock rate of present personal computers is approaching gigahertz range. As signal rise-time becomes less than 200ps, the significant frequency content of digital signals extends up to at least 10 GHz. This necessitates the fabrication of interconnects and packages to be capable of supporting very fast varying and broadband signals without degrading signal integrity to unacceptable levels. While the chip design and fabrication technology have undergone a tremendous evolution: gate lengths, having scaled from 50 µm in the 1960s to 0.18 µm today, are projected to reach 0.1 µm in the next few years; on-chip clock frequency is doubling every 18 months; and the intrinsic delay of the gate is decreasing exponentially with time to a few tens of Pico-seconds. However, the package design has lagged considerably. With current technology, the package interconnection delay dominates the system timing budget and becomes the bottleneck of the high-speed system design. It is generally accepted today that package performance is one of the major limiting factors of the overall system performance.Advances in high performance sub-micron microprocessors, the arrival of gigabit networks, and the need for broadband Internet access, necessitate the development of high performance packaging structures for reliable high-speed data transmission inside every electronics system.Signal integrity is one of the most important factors to be considered when designing these packages (chip carriers and PCBs) and integrating these packages together.3、SI Analysis3.1. SI Analysis in the Design FlowSignal integrity is not a new phenomenon and it did not always matter in the early days of the digital era. But with the explosion of the information technology and the arrival of Internet age, people need to be connected all the time through various high-speed digital communication/computing systems. In this enormous market, signal integrity analysis will play a more and more critical role to guarantee the reliable system operation of these electronics products. Without pre-layout SI guidelines, prototypes may never leave the bench; without post-layout SI verifications, products may fail in the field. Figure 14-5 shows the role of SI analysis in the high-speed design process. From this chart, we will notice that SI analysis is applied throughout the design flow and tightly integrated into each design stage. It is also very common to categorize SI analysis into two main stages: reroute analysis and post route analysis.In the reroute stage, SI analysis can be used to select technology for I/Os, clock distributions, chip package types, component types, board stickups, pin assignments, net topologies, and termination strategies. With various design parameters considered, batch SI simulations on different corner cases will progressively formulate a set of optimized guidelines for physical designs of later stage. SI analysis at this stage is also called constraint driven SI design because the guidelines developed will be used as constraints for component placement and routing. The objective of constraint driven SI design at the reroute stage is to ensure that the signal integrity of the physical layout, which follows the placement/routing constraints for noise and timing budget, will not exceed the maximum allowable noise levels. Comprehensive and in-depth reroute SI analysis will cut down the redesign efforts and place/route iterations, and eventually reduce design cycle.With an initial physical layout, post route SI analysis verifies the correctness of the SI design guidelines and constraints. It checks SI violations in the current design, such as reflection noise, ringing, crosstalk and ground bounce. It may also uncover SI problems that are overlooked in the reroute stage, because post route analysis works with physical layout data rather than estimated data or models, therefore it should produce more accurate simulation results.When SI analysis is thoroughly implemented throughout the whole design process, a reliable high performance system can be achieved with fast turn-around.In the past, physical designs generated by layout engineers were merely mechanical drawings when very little or no signal integrity issues were concerned. While the trend of higher-speed electronics system design continues, system engineers, responsible for developing a hardware system, are getting involved in SI and most likely employ design guidelines and routing constraints from signal integrity perspectives. Often, they simply do not know the answers to some of the SI problems because most of their knowledge is from the engineers doing previous generations of products. To face this challenge, nowadays, a design team (see Figure 14-6) needs to have SI engineers who are specialized in working in this emerging technology field. When a new technology is under consideration, such as a new device family or a new fabrication process for chip packages or boards, SI engineers will carry out the electrical characterization of the technology from SI perspectives, and develop layout guideline by running SI modeling and simulation software [2]. These SI tools must be accurate enough to model individual interconnections such as visa, traces, and plane stickups. And they also must be very efficient so what-if analysis with alternative driver/load models and termination schemes can be easily performed. In the end, SI engineers will determine a set of design rules and pass them to the design engineers and layout engineers. Then, the design engineers, who are responsible for the overall system design, need to ensure the design rules are successfully employed. They may run some SI simulations on a few critical nets once the board is initially placed and routed. And they may run post-layout verifications as well. The SI analysis they carry out involves many nets. Therefore, the simulation must be fast, though it may not require the kind of accuracy that SI engineers are looking for. Once the layout engineers get the placement and routing rules specified in SI terms, they need to generate an optimized physical design based on these constraints. And they will provide the report on any SI violations in a routed system using SI tools. If any violations are spotted, layout engineers will work closely with design engineers and SI engineers to solve these possible SI problems.3.2.Principles of SI AnalysisA digital system can be examined at three levels of abstraction: log ic, circuit theory, and electromagnetic (EM) fields. The logic level, which is the highest level of those three, is where SI problems can be easily identified. EM fields, located at the lowest level of abstraction, comprise the foundation that the other levels are built upon [3]. Most of the SI problems are EM problems in nature, such as the cases of reflection, crosstalk and ground bounce. Therefore, understanding the physical behavior of SI problems from EM perspective will be very helpful. For instance, in the following multi-layer packaging structure shown in Figure 14-7, a switching current in via a will generate EM waves propagating away from that via in the radial direction between metal planes. The fields developed between metal planes will cause voltage variations between planes (voltage is the integration of the E-field). When the waves reach other visa, they will induce currents in those visa. And the induced currents in that visa will in turn generate EM waves propagating between the planes. When the waves reach the edges of the package, part of them will radiate into the air and part of them will get reflected back. When the waves bounce back and forth inside the packaging structure and superimpose to each other, resonance will occur. Wave propagation, reflection, coupling and resonance are the typical EM phenomena happening inside a packaging structure during signal transients. Even though EM full wave analysis is much more accurate than the circuit analysis in the modeling of packaging structures, currently, common approaches of interconnect modeling are based on circuit theory, and SI analysis is carried out with circuit simulators. This is because field analysis usually requires much more complicated algorithms and much larger computing resources than circuit analysis, and circuit analysis provides good SI solutions at low frequency as an electrostatic approximation.Typical circuit simulators, such as different flavors of SPICE, employ nodal analysis and solve voltages and currents in lumped circuit elements like resistors, capacitors and inductors. In SI analysis, an interconnect sometimes will be modeled as a lumped circuit element. For instance, a piece of trace on the printed circuit board can be simply modeled as a resistor for its finite conductivity. With this lumped circuit model, the voltages along both ends of the trace are assumed to change instantaneously and the travel time for the signal to propagate between the two ends is neglected. However, if the signal propagation time along the trace has to be considered, a distributed circuit model, such as a cascaded R-L-C network, will be adopted to model the trace. To determine whether the distributed circuit model is necessary, the rule of thumb is – if the signal rise time is comparable to the round-trip propagation time, you need to consider using the distributed circuit model.For example, a 3cm long stripling trace in a FR-4 material based printed circuit board will exhibits 200ps propagation delay. For a 33 MHz system, assuming the signal rise time to be 5ns, the trace delay may be safely ignored; however, with a system of 500 MHz and 300ps rise time, the 200ps propagation delay on the trace becomes important and a distributed circuit model has to be used to model the trace. Through this example, it is easy to see that in the high-speed design, with ever-decreasing signal rise time, distributed circuit model must be used in SI analysis.Here is another example. Considering a pair of solid power and ground planes in a printed circuit board with the dimension of 15cm by 15cm, it is very natural to think the planes acting as a large, perfect, lumped capacitor, from the circuit theory point of view. The capacitor model C= erA/d, an electro-static solution, assumes anywhere on the plane the voltages are the same and all the charges stored are available instantaneously anywhere along the plane. This is true at DC and low frequency. However, when the logics switch with a rise time of 300ps, drawing a large amount of transient currents from the power/ground planes, they perceive the power/ground structure as a two-dimensional distributed network with significant delays. Only some portion of the plane charges located within a small radius of the switching logics will be able to supply the demand. And voltages between the power/ground planes will have variations at different locations. In this case, an ideal lumped capacitor model is obviously not going to account for the propagation effects. Two-dimensional distributed R-L-C circuit networks must be used to model the power/ground pair.In summary, as the current high-speed design trend continues, fast rise time reveals the distributed nature of package interconnects. Distributed circuit models need to be adopted to simulate the propagation delay in SI analysis. However, at higher frequencies, even the distributed circuit modeling techniques are not good enough, full wave electromagnetic field analysis based on solving Maxwell’s equations must come to play. As presen ted in later discussions, a trace will not be modeled as a lumped resistor, or a R-L-C ladder; it will be analyzed based upon transmission line theory; and a power/ground plane pair will be treated as a parallel-plate wave guide using radial transmission line theory.Transmission line theory is one of the most useful concepts in today’s SI analysis. And it is a basic topic in many introductory EM textbooks. For more information on the selective reading materials, please refer to the Resource Center in Chapter 16.In the above discussion, it can be noticed that signal rise time is a very important quantity in SI issues. So a little more expanded discussion on rise time will be given in the next section.信号完整性介绍在高速数字设计领域,信号完整性已经成为一个严重的问题,是造成越来越多的挑战的设计工程师。

ImproveSignalIntegrity

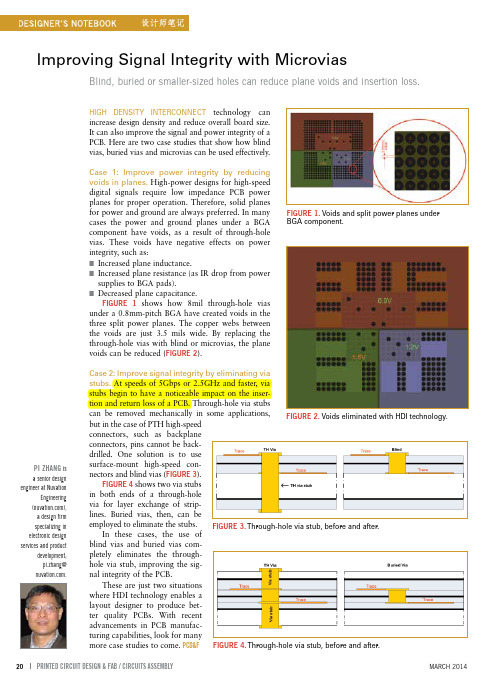

HIGH D ENSITY INTERCONNECT technology canincrease design density and reduce overall board size.It can also improve the signal and power integrity of aPCB. Here are two case studies that show how blindvias, buried vias and microvias can be used effectively.Case 1: Improve power integrity by reducingvoids in planes. High-power designs for high-speeddigital signals require low impedance PCB powerplanes for proper operation. Therefore, solid planesfor power and ground are always preferred. In manycases the power and ground planes under a BGAcomponent have voids, as a result of through-holevias. These voids have negative effects on powerintegrity, such as:■Increased plane inductance.■Increased plane resistance (as IR drop from powersupplies to BGA pads).■Decreased plane capacitance.FIGURE 1 shows how 8mil through-hole viasunder a 0.8mm-pitch BGA have created voids in thethree split power planes. The copper webs betweenthe voids are just 3.5 mils wide. By replacing thethrough-hole vias with blind or microvias, the planevoids can be reduced (FIGURE 2).Case 2: Improve signal integrity by eliminating via stubs. At speeds of 5Gbps or 2.5GHz and faster , via stubs begin to have a noticeable impact on the inser-tion and return loss of a PCB. Through-hole via stubs can be removed mechanically in some applications, but in the case of PTH high-speed connectors, such as backplane connectors, pins cannot be back-drilled. One solution is to use surface-mount high-speed con-nectors and blind vias (FIGURE 3). FIGURE 4 shows two via stubs in both ends of a through-hole via for layer exchange of strip-lines. Buried vias, then, can be employed to eliminate the stubs.In these cases, the use of blind vias and buried vias com-pletely eliminates the through-hole via stub, improving the sig-nal integrity of the PCB.These are just two situationswhere HDI technology enables alayout designer to produce bet-ter quality PCBs. With recentadvancements in PCB manufac-turing capabilities, look for manymore case studies to come. PCD&FPRINTED CIRCUIT DESIGN & FAB / CIRCUITS ASSEMBLY MARCH 201420Improving Signal Integrity with MicroviasBlind, buried or smaller-sized holes can reduce plane voids and insertion loss.PI ZHANG isa senior designengineer at NuvationEngineering(),a design firmspecializing inelectronic designservices and productdevelopment;pi.zhang@.FIGURE 1. Voids and split power planes underBGA component.FIGURE 2. Voids eliminated with HDI technology.FIGURE 4. Through-hole via stub, before and after.FIGURE 3. Through-hole via stub, before and after.。

信号完整性(signal integrity)

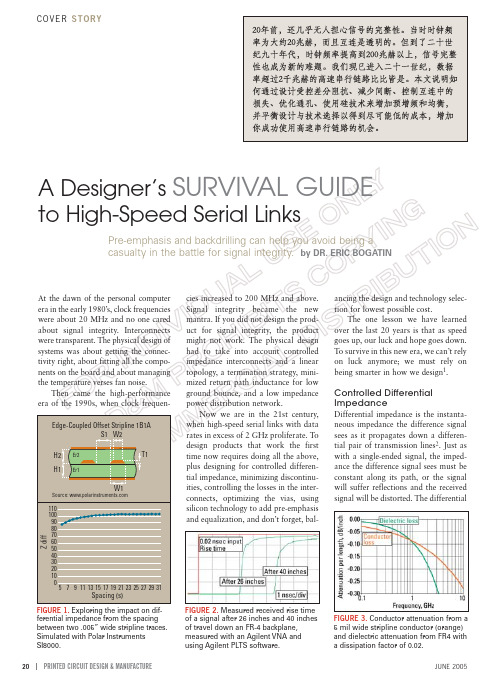

ferential impedance from the spacing between two .005” wide stripline traces. Simulated with Polar InstrumentsSI8000.of a signal after 26 inches and 40 inchesof travel down an FR-4 backplane,measured with an Agilent VNA andusing Agilent PLTS software.FIGURE 3.Conductor attenuation from a5 mil wide stripline conductor (orange)and dielectric attenuation from FR4 witha dissipation factor of 0.02.impedance of all the traces in the board must be at the target value, typically 100 Ω, in order to assure acceptable received signal amplitude and rise time.This is primarily achieved by the selection of line widths, spacing, dielec-tric thickness and knowing the dielectric constant of the laminate materials. The only way of accurately balancing the board stackup and evaluating the toler-ance buildup is with a 2D field solver .FIGURE 1explores how the spacing between two stripline traces affects their differential impedance. An easy-to-use,accurate 2D field solver is an essential tool to survive in this new regime.It is not the losses in the intercon-nects that cause problems in high-speed serial links – it is the frequency depend-ency of the losses. Both conductor loss and dielectric loss absorb more of the higher-frequency components than of the low-frequency components. This means that if you launch an ideal square wave into an interconnect, the rise time will degrade and get longer as it propa-gates, because the higher frequencies that make up the sharp edge are removed. This is illustrated in FIGURE 2.This rise time degradation causes most of the significant problems with high-speed serial interconnects, such as intersymbol interference (ISI), deter-ministic jitter and collapse of the eye diagram. It can be most easily described as the attenuation or loss in the signal as a function of frequency.Conductor loss is frequency-dependent due to skin depth effects.The cross-sectional area for current to travel through a conductor decreases into a thinner and thinner perimeter shell as frequency goes up. This increases the series resistance of boththe signal and return conductors at higher frequency.The only way to reduce the losses from the conductors’ series resistance is by using wider lines. But to use wider lines while still maintaining the target impedance also requires either thicker dielectric layers or lower dielectric constant.Of course, there is a limit to the total thickness of a board. With as many as 40 layers, in .250˝total thickness, the maximum dielectric thickness is on the order of .006˝already. And thicker boards will be more expensive due to material and drilling costs. Further , as we shall see, a thicker board also means longer via stubs, which will cause addi-tional signal integrity problems.Balancing the widest line for lowest rise time degradation, thinnest total board and acceptable cost can only be done with a simulation tool that includes lossy line effects, such as Men-tor Graphics HyperLynx or Agilent Technologies ADS.The second source of frequency-dependent loss comes from the dissipa-tion factor of the laminate. This mate-rial property is a measure of the dipoles in the laminate, which can rotate in the applied field of the signal and suck out energy from the signal.The higher signal frequency compo-nents will rotate the dipoles faster and cause more heat generation. Even though the dissipation factor of most materials is constant with frequency,the attenuation from the dissipation factor will increase with higher fre-quency. A low dissipation factor will minimize the rise time degradation.Insertion loss is a common metric to quantify the frequency-dependentloss of a signal as it propagates down an interconnect. This can be further refined as the attenuation in dB per inch of interconnect. A larger and more negative dissipation factor will mean less high-frequency signal and longer rise time, a bad thing. FIGURE 3shows an example of the insertion loss for both conductor loss and dielectric loss.As a rough rule of thumb, with many popular SERDES chips the typical acceptable attenuation might be as high as -10 dB at the bandwidth of the high-speed serial link, which is about half the bit rate. For a XAUI interface, at 3.125Gbps the bandwidth is about 1.6 GHz.If the interconnect length were 40 inch-es, the acceptable attenuation per length would be about -10 dB/40 inches, or ~ -0.25 dB/inch, at 1.6 GHz.In the example above, the total attenuation from the conductor loss and dielectric loss would be -0.12 dB/inch +-0.15 dB/inch = -0.27 dB/inch. This is above the estimated acceptable limit,which suggests a marginal design.For a robust design, either the line width must be increased, the dissipa-tion factor decreased, the interconnect length decreased, the SERDES noise margin increased, or silicon processing (i.e., pre-emphasis in the drivers)would have to be used.The Power of Pre-emphasisThe problem with attenuation in inter-connects isn’t the attenuation – it’s the frequency dependence that causes rise time degradation. If we know how much the higher frequencies will be attenuated and put an extra amount of these into the signal when it is launched, we might be able to see asharper rise time at the receiver. TheFIGURE unched signal with pre-emphasis from an Altera Stratix GX FPGA. (Figures 4, 5 and 6 courtesy ofAltera Corp.)FIGURE 5. Eye diagram of a XAUI sig-nal received after 57 inches in an FR-4backplane trace.The signal is unusable.FIGURE 6. The same FR-4 interconnect,57 inches in length, as in Figure 3, but with pre-emphasis used in the driver,utilizing the Altera Stratix GX FPGA.technique of adding high-frequency components into the launched signal is called pre-emphasis.An example of the time domain waveform of the launched signal with pre-emphasis is shown in FIGURE 4.There is an extra pulse at the tran-sitions. When this signal travels down the interconnect, the extra high-fre-quency components will be absorbed, flattening the waveform back into a more normal looking waveform. Pre-emphasis is a powerful technique of recovering a signal at the far end of a lossy line.In FIGURE 5is displayed the eye diagram of a XAUI signal, received after 57 inches in an FR-4 intercon-nect. There is so much frequency-dependent attenuation that all the bits are grossly distorted and cannot be read with any certainty. This intercon-nect is completely unusable.However, with pre-emphasis, extra high-frequency components are added to the signal and the frequency-dependent attenuation sucks out these extra components, leaving behind a much more usable signal. This is shown in FIGURE 6.The combination of conventional FR-4 boards and pre-emphasis in the drivers is a powerful combination for designing successful high-speed serial links. The higher the bandwidth, the greater the need for wider lines, lower dissipation factor and silicon processing.Though pre-emphasis can over-come losses in the interconnect, it can-not overcome the sharp resonances from via stubs. Ultimately, these stubs will be a fundamental limit to the bit rate for backplane interconnects.If conductor and dielectric loss were the only processes decreasing the insertion loss with frequency, pre-emphasis could compensate. Unfortu-nately, the stubs created by through vias can act as resonators and absorb a very large amount of the signal energy in narrow frequency bands. An exam-ple of the measured insertion loss of a backplane channel with and without a via stub is shown in FIGURE 7.The resonator is created when a signal uses a through via to transition from two closely spaced layers, such as between layers 1 and 4 or 2 and 5 in aBackdrilled via200-mil through-hole via stub0-20-40-60-80-10005101520Even lower frequency bit rates can suffer from via stub resonances, if their bandwidths are riding on the edge of the resonance curve. The most effective way of eliminating this problem is to move the via stub resonant frequency as high as possible, by using as short a via stub as possible. This can be done by removing NFPs from unused layers, limiting layer transitions to those near the outer layers, and backdrilling any stubs that might be left.Backdrilling is the process of re-drilling the bottom of the via with an oversized drill bit, after the through via has been plated. This removed the plat-ed through hole that is not being used and eliminates the resonating stub. FIG-URE 8shows an example of an as-fab-ricated through-hole via in an 18-layer board, and a similar via that has been backdrilled to remove the long stub.Backdrilling has become the de facto standard in all high-performance backplanes used in systems at 5 Gbps and above. To allow scalability of a backplane that may be first used at 2.5 Gbps or even 3.125 Gbps, so that it could be used later in life at 5 Gbps, backdrilling is often employed. This way, higher bit rate cards can be plugged into this legacy backplane and still operate acceptably.Beginning of an EraIn this new era of high-speed serial links operating at 2 Gbps and above, a new set of signal integrity concerns must be considered for a system to work the first time. In addition to all the other signal integrity problems like terminations and topologies, crosstalk, ground bounce and power distribu-tion, now we must design out differen-tial impedance problems, deal with losses and include via stub effects.To survive this new set of mine-fields requires new skills, new tools and new technologies. The elements of survival include the use of 2D field solvers to accurately design the stackup and routing for differential pairs, the selection of optimal dielectric materials with low dielectric constant to allow wide lines and thin boards, low dissi-pation factor for low insertion loss and the use of silicon processing such as pre-emphasis. Finally, techniques to minimize the length of via stubs suchas backdrilling are essential.Now interconnects are not onlynot transparent but are the dominantfactor determining whether a large,high-performance system will work thefirst time, every time. By paying carefulattention to all of these importantissues, you can be successful in this eraand earn the right to face the chal-lenges of the next generation of high-performance systems. PCD&MERIC BOGATIN is the CTO at IDI, andpresident of Bogatin Enterprises. He canbe reached at eric@.REFERENCES1.This paper is based on Online Lecture 184,A Designer’s Survival Guide to High-SpeedSerial Links, posted on www.bethe. To view this lecture for free,enter coupon code PCDM0507.2.Bogatin, Eric, Signal Integrity - Simplified,Prentice Hall, 2003.。

差分阻抗测量方法

差分阻抗测量方法Differential impedance measurement is a crucial technique in thefield of electrical engineering. It plays a significant role in ensuringthe reliable performance of high-speed digital circuits. By accurately measuring the impedance of differential signal paths, engineers can determine if the signal integrity of a circuit is within acceptable limits. This helps in preventing signal distortions, crosstalk, and other potential issues that could impact the overall functionality of the circuit. The measurements obtained through this technique provide valuable insights into the electrical characteristics of the circuit, allowing engineers to make informed decisions about its design and operation.差分阻抗测量方法在电气工程领域起着至关重要的作用。

它对于确保高速数字电路的可靠性性能至关重要。

通过准确测量差分信号路径的阻抗,工程师可以确定电路的信号完整性是否在可接受的范围内。

这有助于防止信号失真、串扰以及其他可能影响电路整体功能的问题。

高速数字系统设计-科大版

关键的性能瓶颈:CPU主频、内存访问速度以及I/O访问速度之间的发展差距

2012/2/13

中国科技大学 快电子学 安琪

19

Intel® Core™ Duo Processor Microprocessor Architecture

2012/2/13

中国科技大学 快电子学 安琪

20

Intel® Pentium® processor Extreme Edition 955

数据来源:Intel

中国科技大学 快电子学 安琪 15

2012/2/13

Moore’s Law的描述

2012/2/13

中国科技大学 快电子学 安琪

16

Moore’s Law的描述

2012/2/13

中国科技大学 快电子学 安琪

17

“Moore’s Law remains a fundamental enabler of our growth, & it’s alive and well at Intel. But the way we and our customers look at Moore’s Law has changed. Moore’s Law isn’t just about more transistors. It’s also about how creatively you use those transistors.

By Stephen H. Hall, Garrett W. Hall & James A. McCall

中文版: “高速数字系统设计” -互连理论和设计实践手册 伍 微 等译,机械工业出版社,2005.3 Signal Integrity: Simplified

高速电路信号完整性分析

摘要随着现代电子技术的迅速发展,高速电路的应用范围也在日益扩大,系统时钟频率在迅速提高。

由于上升时间的加快和电路集成度的不断增加,印制电路板的线迹互连和板层特性对系统电气性能的影响越来越突出,引发了很多信号完整性问题。

互连关系在低频电路设计中可视为集总参数,线迹互连和板层特性的影响可以不考虑。

但是,高速电路中的互连线已经成为具有分布参数的传输线,印制电路板材料的介电常数也影响着电路系统的性能,从而出现反射、串扰、和同步开关噪声等信号完整性问题,造成了信号失真、时序混乱、数据错误以及系统误触发等严重的后果。

信号完整性理论的逐步完善为解决这些问题提供了理论依据,而仿真软件的发展则给电路设计者提供了一把利刃。

用基本理论作指导,仿真软件为工具,就可以在产品生产之前尽可能早地发现信号完整性问题隐患,最大限度地减少因为信号完整性问题而导致的产品设计失败的概率,使产品一次开发成功成为可能,大大缩短开发周期,降低开发成本。

论文对高速电路设计中的信号完整性问题作了理论研究与实际仿真。

有以下的基本内容:研究了信号完整性的基本理论,包括高速电路理论、电磁场理论和传输线理论。

用建模的方式分析了反射形成的机理,提出了各种改善反射的端接措施。

研究了电容矩阵与电感矩阵,用来描述串扰;用耦合解释了串扰原理。

介绍了本文的仿真软件Hyperlynx和仿真模型。

在熟练掌握Hyperlynx软件的基础上,对这些内容做了仿真分析:多种情况的反射现象、多种参数对反射的影响、电容矩阵与电感矩阵的求解、耦合电磁场的模拟、各种串扰的分析等。

理论分析与仿真实践都表明:端接技术对改善高速电路中的信号反射效果非常明显;提出的减少串扰的布线策略是可行的;由矩阵可以计算耦合线的串扰。

从而提供了较完备的高速电路反射与串扰的分析策略。

关键词:信号完整性;反射;串扰;端接;仿真AbstractWith the development of modern electronic technology, the range of application is expanding increasingly for high speed circuit, and systematic clock frequency is increasing rapidly.With more quick risetime and the increase of integrated degree of circuit, the line's mutual link of printed circuit board and board layer's property have greater influence on the systematic electrical performance, and caused a lot of signal integrity problems.For the design of low frequency circuit, the mutual link relations can be regard as lumped parameters, and the influence of line's mutual link and board layer's property can be neglected.But the interconnects of the high speed circuit becomes a transmission line with distributed parameters, and the permittivity of the printed circuit board also influences the performance of circuit system. Therefore, a lot of signal integrity problems have appeared, such as reflection, crosstalk and simultaneous switching noise, etc., which cause serious consequences such as signal distortion, out-of-order timing, incorrect data and incorrect trigger of the system.The gradual improvements of the theories in signal integrity provided a theoretical basis for solving these problems, and the development of simulation software provided keen edge to circuit designers.With basic theory as guide and simulation software as tool, we can discover the hidden signal integrity problems earlier before the product made, and the probability of the failure caused by signal integrity problems is reduced at the lowest level. Then it is possible that products can be developed very successfully only one time, and the development period is shortened and the cost is reduced.This paper made a theoretical study and actual simulation as to the signal integrity problems in the design of high speed circuit. The basic contents are as follows: The fundamental theories of signal integrity were studied, including high speed circuit theory, electromagnetic field theory and transmission line theory. The mechanism in forming reflections were analyzed by modeling, and various termination measures for improving reflections were given. Capacitance matrix and inductance matrix were studied, which were used to describe crosstalk; The crosstalk principle was explained by coupling. Simulation software Hyperlynx and simulation models for this paper were introduced. On the basis of mastering Hyperlynx, some contents were simulated and analyzed, that is, various reflection phenomena, the influence on reflection by various parameters, solving capacitance matrix and inductance matrix,simulating coupled electromagnetic field, analyzing various crosstalks, etc. Theoretical analysis and actual simulation indicated that the effects of termination technology are very obvious on improving signal reflection of high-speed circuit; The proposed routing tactics for reducing crosstalks are feasible; crosstalk of coupled lines can be worked out from matrix.Accordingly, more integrated analysis tactics of reflection and crosstalk in high speed circuit were offered.Keywords: signal integrity; reflection; crosstalk; termination; simulation插图索引图 2.1 实际元件的等效模型 (10)图 2.2 实际数字信号波形 (10)图 2.3 接收器中的ESD 钳位保护结构 (11)图 2.4 建立时间和保持时间 (11)图 2.5 小段传输线的集总参数模型 (12)图 2.6 互连中常用的各种均匀传输线的横截面举例 (13)图 2.7 信号传输的电磁场模型 (15)图 2.8 传输线零阶模型 (16)图 2.9 传输线的物理结构与一阶模型 (17)图 2.10 50Ω传输线的两种横截面 (18)图 2.11 三种均匀传输线示意图 (18)图 3.1 输入/输出缓冲器整体结构模型图 (22)图 3.2 输入缓冲器模型 (23)图 3.3 输出缓冲器模型 (23)图 4.1 传输线反射模型 (26)图4.2 与1 V入射信号对应的终端电压值随终端阻抗变化的曲线 (28)图 4.3 有短串接线与无短串接线波形比较 (29)图 4.4 突变长度分别为0.5in,1.0in,2.0in,3.0in时传输线上的反射 (30)图 4.5 短桩线模型及其反射信号与传输信号 (32)图 4.6 传输线远端容性负载的电容量不同时,传输线上的反射信号 (33)图 4.7 传输线中途不同容性负载时,传输线上的终端信号和源端信号 (35)图 4.8 与传输线并联的容性突变的并联阻抗等效图 (36)图4.9 上升时间为50 ps的信号分别通过电感值L=0,5nH的突变 (37)图 4.10 多次反射计算图解 (39)图 4.11 各种阻尼情况下的电路模型 (40)图 4.12 各种阻尼情况下的仿真波形 (41)图 4.13 各种端接方法示意图 (42)图4.14 无终端端接模型及133 MHz时钟信号接收端波形 (43)图 4.15 点对点拓扑结构四种常用的端接方法示意图 (44)图4.16 传输线有和没有源端端接时,其远端的快速上升边的电压信号 (45)图 4.17 传输线具有源端串联电阻时的源端电压波形 (46)图 5.1 串扰中的干扰源与被干扰对象 (47)图 5.2 n 节耦合传输线模型其中一节的等效电路模型 (48)图 5.3 5 条耦合传输线的横截面图 (49)图5.4 使用场求解器工具计算的5条耦合传输线的电磁场分布 (50)图5.5 SPICE电容矩阵元素图 (51)图 5.6 电感矩阵元素图 (52)图 5.7 两条耦合线的等效电路模型 (53)图 5.8 静态线近端的端接电阻两端的容性耦合电压的一般特性 (54)图 5.9 静态线远端的端接电阻两端的容性耦合电压的典型特性 (54)图 5.10 信号沿动态线传输时的感应电流图示 (56)图 5.11 耦合电流仿真波形 (57)图 5.12 差模下的电磁场分布 (58)图 5.13 共模下的电磁场分布 (58)图 5.14 减少并行线长度的走线方式 (59)图 5.15 不同耦合长度的近端串扰电压 (60)图 5.16 远端串扰与上升时间的关系仿真 (61)附表索引表5.1 耦合电流数据比较 (58)第1章绪论1.1信号完整性问题的提出摩尔定律最早给出了电子产品的发展方向――更小、更快、更便宜、研发周期更短。

30_signal_and_power_integrity

• Is every thing ok because the ambient “Functional Test” passed?

Purple - 3.3 V 0.5 V/div Note more noise as AD driven “High”

Green - D Gnd 0.5 V/div Note more noise as AD driven “Low” Yellow - AD 12 2 V/div

• Signal Integrity ensures signals are of sufficient quality to reliably transmit their required information, and do not cause problems to themselves or to other components in the system. • Signal Integrity applies to Digital, Analog and Power electronics • Signal Integrity issues are more common now because electronics are more dense and chips have faster rise times – Assuring Signal Integrity now involves more knowledge of such RF techniques as terminations, impedance matching • Major function of engineering, next to conceiving the correct design, is implementing the design correctly • Signal integrity assures the circuit design operates as intended and must be designed in. – Correct design relies on experience, best practices, analysis and simulation to ensure desired signal quality.

Samtec 微型抗摧断系统说明书