SI9801DY中文资料

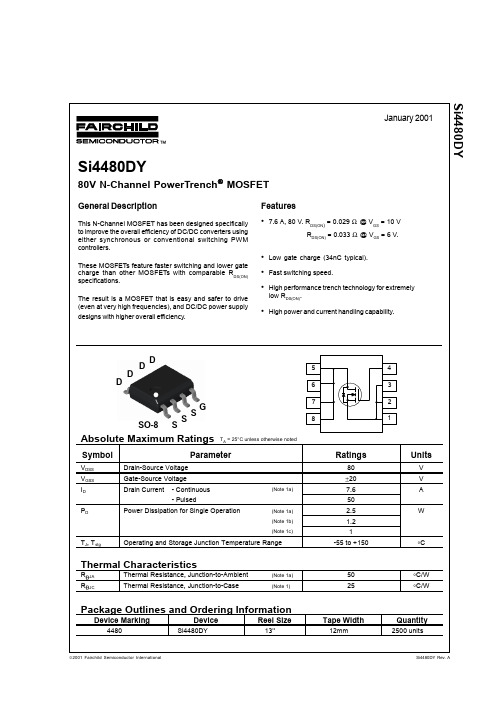

SI4480DY中文资料

VDD = 40 V, ID = 1 A, VGS = 10 V, RGEN = 6 Ω

13 8 34 16

26 20 60 30 46

ns ns ns ns nC nC nC

VDS = 40 V, ID = 7.6 A, VGS = 10 V

34 6.1 6.9

Drain-Source Diode Characteristics and Maximum Ratings

Off Characteristics

BVDSS ∆BVDSS ∆ TJ IDSS IGSSF IGSSR Drain-Source Breakdown Voltage Breakdown Voltage Temperature Coefficient Zero Gate Voltage Drain Current Gate-Body Leakage, Forward Gate-Body Leakage, Reverse

2 RDS(ON), NORMALIZED DRAIN-SOURCE ON-RESISTANCE 1.8 1.6 1.4 1.2 1 0.8 0.6 0.4 -50 -25 0 25 50 75 100

o

ID = 7.6A VGS = 10V

ID = 3.8A 0.05 TA = 125oC 0.04 0.03 0.02 0.01 0

Scale 1 : 1 on letter size paper 2: Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2.0%

Si4480DY Rev A

元器件交易网

FDS3580 Si4 480DY

Typical Characteristics

Si4826DY资料

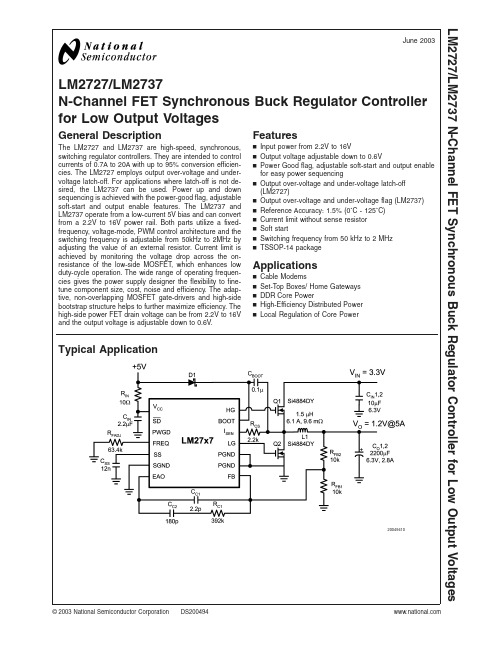

LM2727/LM2737N-Channel FET Synchronous Buck Regulator Controller for Low Output VoltagesGeneral DescriptionThe LM2727and LM2737are high-speed,synchronous,switching regulator controllers.They are intended to control currents of 0.7A to 20A with up to 95%conversion efficien-cies.The LM2727employs output over-voltage and under-voltage latch-off.For applications where latch-off is not de-sired,the LM2737can be used.Power up and down sequencing is achieved with the power-good flag,adjustable soft-start and output enable features.The LM2737and LM2737operate from a low-current 5V bias and can convert from a 2.2V to 16V power rail.Both parts utilize a fixed-frequency,voltage-mode,PWM control architecture and the switching frequency is adjustable from 50kHz to 2MHz by adjusting the value of an external resistor.Current limit is achieved by monitoring the voltage drop across the on-resistance of the low-side MOSFET,which enhances low duty-cycle operation.The wide range of operating frequen-cies gives the power supply designer the flexibility to fine-tune component size,cost,noise and efficiency.The adap-tive,non-overlapping MOSFET gate-drivers and high-side bootstrap structure helps to further maximize efficiency.The high-side power FET drain voltage can be from 2.2V to 16V and the output voltage is adjustable down to 0.6V.Featuresn Input power from 2.2V to 16Vn Output voltage adjustable down to 0.6Vn Power Good flag,adjustable soft-start and output enable for easy power sequencingn Output over-voltage and under-voltage latch-off (LM2727)n Output over-voltage and under-voltage flag (LM2737)n Reference Accuracy:1.5%(0˚C -125˚C)n Current limit without sense resistor n Soft startn Switching frequency from 50kHz to 2MHz n TSSOP-14packageApplicationsn Cable Modemsn Set-Top Boxes/Home Gateways n DDR Core Powern High-Efficiency Distributed Power nLocal Regulation of Core PowerTypical Application20049410June 2003LM2727/LM2737N-Channel FET Synchronous Buck Regulator Controller for Low Output Voltages©2003National Semiconductor Corporation Connection Diagram2004941114-Lead Plastic TSSOPθJA =155˚C/WNS Package Number MTC14Pin DescriptionBOOT (Pin 1)-Supply rail for the N-channel MOSFET gate drive.The voltage should be at least one gate threshold above the regulator input voltage to properly turn on the high-side N-FET.LG (Pin 2)-Gate drive for the low-side N-channel MOSFET.This signal is interlocked with HG to avoid shoot-through problems.PGND (Pins 3,13)-Ground for FET drive circuitry.It should be connected to system ground.SGND (Pin 4)-Ground for signal level circuitry.It should be connected to system ground.V CC (Pin 5)-Supply rail for the controller.PWGD (Pin 6)-Power Good.This is an open drain output.The pin is pulled low when the chip is in UVP ,OVP ,or UVLO mode.During normal operation,this pin is connected to V CC or other voltage source through a pull-up resistor.ISEN (Pin 7)-Current limit threshold setting.This sources a fixed 50µA current.A resistor of appropriate value should be connected between this pin and the drain of the low-side FET.EAO (Pin 8)-Output of the error amplifier.The voltage level on this pin is compared with an internally generated ramp signal to determine the duty cycle.This pin is necessary for compensating the control loop.SS (Pin 9)-Soft start pin.A capacitor connected between this pin and ground sets the speed at which the output voltage ramps rger capacitor value results in slower output voltage ramp but also lower inrush current.FB (Pin 10)-This is the inverting input of the error amplifier,which is used for sensing the output voltage and compen-sating the control loop.FREQ (Pin 11)-The switching frequency is set by connect-ing a resistor between this pin and ground.SD (Pin 12)-IC Logic Shutdown.When this pin is pulled low the chip turns off the high side switch and turns on the low side switch.While this pin is low,the IC will not start up.An internal 20µA pull-up connects this pin to V CC .HG (Pin 14)-Gate drive for the high-side N-channel MOS-FET.This signal is interlocked with LG to avoid shoot-through problems.L M 2727/L M 2737 2Absolute Maximum Ratings(Note1) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.V CC7V BOOTV21V Junction Temperature150˚C Storage Temperature−65˚C to150˚C Soldering InformationLead Temperature(soldering,10sec)260˚CInfrared or Convection(20sec)235˚C ESD Rating2kVOperating RatingsSupply Voltage(V CC) 4.5V to5.5V Junction Temperature Range−40˚C to+125˚C Thermal Resistance(θJA)155˚C/WElectrical CharacteristicsV CC=5V unless otherwise indicated.Typicals and limits appearing in plain type apply for T A=T J=+25˚C.Limits appearing in boldface type apply over full Operating Temperature Range.Datasheet min/max specification limits are guaranteed by design, test,or statistical analysis.Symbol Parameter Conditions Min Typ Max UnitsV FB_ADJ FB Pin Voltage V CC=4.5V,0˚C to+125˚C0.5910.60.609V V CC=5V,0˚C to+125˚C0.5910.60.609V CC=5.5V,0˚C to+125˚C0.5910.60.609V CC=4.5V,−40˚C to+125˚C0.5890.60.609V CC=5V,−40˚C to+125˚C0.5890.60.609V CC=5.5V,−40˚C to+125˚C0.5890.60.609V ON UVLO Thresholds RisingFalling 4.23.6VI Q-V5Operating V CC CurrentSD=5V,FB=0.55VFsw=600kHz1 1.52mASD=5V,FB=0.65VFsw=600kHz0.8 1.7 2.2 Shutdown V CC Current SD=0V0.150.40.7mAt PWGD1PWGD Pin Response Time FB Voltage Going Up6µs t PWGD2PWGD Pin Response Time FB Voltage Going Down6µs I SD SD Pin Internal Pull-up Current20µA I SS-ON SS Pin Source Current SS Voltage=2.5V0˚C to+125˚C -40˚C to+125˚C 8511111515µAI SS-OC SS Pin Sink Current During OverCurrent SS Voltage=2.5V95µAI SEN-TH I SEN Pin Source Current TripPoint0˚C to+125˚C-40˚C to+125˚C352850506565µAERROR AMPLIFIERGBW Error Amplifier Unity GainBandwidth5MHzG Error Amplifier DC Gain60dBSR Error Amplifier Slew Rate6V/µAI FB FB Pin Bias Current FB=0.55VFB=0.65V 01530100155nAI EAO EAO Pin Current Sourcing andSinking V EAO=2.5,FB=0.55VV EAO=2.5,FB=0.65V2.80.8mAV EA Error Amplifier Maximum Swing MinimumMaximum1.23.2VLM2727/LM27373Electrical Characteristics(Continued)V CC =5V unless otherwise indicated.Typicals and limits appearing in plain type apply for T A =T J =+25˚C.Limits appearing in boldface type apply over full Operating Temperature Range.Datasheet min/max specification limits are guaranteed by design,test,or statistical analysis.SymbolParameterConditionsMinTypMaxUnitsGATE DRIVE I Q-BOOTBOOT Pin Quiescent CurrentBOOTV =12V,EN =00˚C to +125˚C -40˚C to +125˚C 9595160215µAR DS1Top FET Driver Pull-Up ON resistanceBOOT-SW =5V @350mA 3ΩR DS2Top FET Driver Pull-Down ON resistanceBOOT-SW =5V @350mA 2ΩR DS3Bottom FET Driver Pull-Up ON resistanceBOOT-SW =5V @350mA 3ΩR DS4Bottom FET Driver Pull-Down ON resistanceBOOT-SW =5V @350mA2ΩOSCILLATORf OSCPWM FrequencyR FADJ =590k Ω50kHzR FADJ =88.7k Ω300R FADJ =42.2k Ω,0˚C to +125˚C 500600700R FADJ =42.2k Ω,-40˚C to +125˚C 490600700R FADJ =17.4k Ω1400R FADJ =11.3k Ω2000DMax Duty Cyclef PWM =300kHz f PWM =600kHz9088%LOGIC INPUTS AND OUTPUTSV SD-IH SD Pin Logic High Trip Point 2.63.5V V SD-IL SD Pin Logic Low Trip Point 0˚C to +125˚C -40˚C to +125˚C 1.31.25 1.61.6VV PWGD-TH-LOPWGD Pin Trip PointsFB Voltage Going Down 0˚C to +125˚C -40˚C to +125˚C 0.4130.4100.4300.4300.4460.446VV PWGD-TH-HIPWGD Pin Trip PointsFB Voltage Going Up 0˚C to +125˚C -40˚C to +125˚C0.6910.6880.7100.7100.7340.734VV PWGD-HYSPWGD Hysteresis (LM2737only)FB Voltage Going Down FB VoltageGoing Up35110mVNote 1:Absolute maximum ratings indicate limits beyond which damage to the device may occur.Operating ratings indicate conditions for which the device operates correctly.Opearting Ratings do not imply guaranteed performance limits.Note 2:The human body model is a 100pF capacitor discharged through a 1.5k resistor into each pin.L M 2727/L M 2737 4Typical Performance CharacteristicsEfficiency (V O =1.5V)F SW =300kHz,T A =25˚CEfficiency (V O =3.3V)F SW =300kHz,T A =25˚C2004941220049413V CC Operating Current vs TemperatureF SW =600kHz,No-Load Bootpin Current vs Temperature for BOOTV =12VF SW =600kHz,Si4826DY FET,No-Load2004941420049415Bootpin Current vs Temperature with 5V BootstrapF SW =600kHz,Si4826DY FET,No-Load PWM Frequency vs Temperaturefor R FADJ =43.2k Ω2004941620049417LM2727/LM27375Typical Performance Characteristics(Continued)R FADJ vs PWM Frequency(in 100to 800kHz range),T A =25˚CR FADJ vs PWM Frequency(in 900to 2000kHz range),T A =25˚C2004941820049419V CC Operating Current Plus Boot Current vs PWM Frequency (Si4826DY FET,T A =25˚C)Switch Waveforms (HG Falling)V IN =5V,V O =1.8V I O =3A,C SS =10nF F SW =600kHz2004942020049423Switch Waveforms (HG Rising)V IN =5V,V O =1.8V I O =3A,F SW =600kHzStart-Up (No-Load)V IN =10V,V O =1.2V C SS =10nF,F SW =300kHz2004942420049421L M 2727/L M 2737 6Typical Performance Characteristics(Continued)Start-Up (Full-Load)V IN =10V,V O =1.2V I O =10A,C SS =10nFF SW =300kHzStart Up (No-Load,10x C SS )V IN =10V,V O =1.2V C SS =100nF,F SW =300kHz2004942220049426Start Up (Full Load,10x C SS )V IN =10V,V O =1.2V I O =10A,C SS =100nFF SW =300kHz ShutdownV IN =10V,V O =1.2V I O =10A,C SS =10nFF SW =300kHz2004942520049427Start Up (Full Load,10x C SS )V IN =10V,V O =1.2V I O =10A,C SS =100nFF SW =300kHzLoad Transient Response (I O =0to 4A)V IN =12V,V O =1.2VF SW =300kHz2004943320049428LM2727/LM27377Typical Performance Characteristics(Continued)Load Transient Response (I O =4to 0A)V IN =12V,V O =1.2VF SW =300kHzLine Transient Response (V IN =5V to 12V)V O =1.2V,I O =5A F SW =300kHz2004942920049430Line Transient Response (V IN =12V to 5V)V O =1.2V,I O =5A F SW =300kHz Line Transient ResponseV O =1.2V,I O =5A F SW =300kHz2004943120049432L M 2727/L M 2737 8Block Diagram20049401Application InformationTHEORY OF OPERATIONThe LM2727is a voltage-mode,high-speed synchronous buck regulator with a PWM control scheme.It is designed for use in set-top boxes,thin clients,DSL/Cable modems,and other applications that require high efficiency buck convert-ers.It has power good (PWRGD),output shutdown (SD),over voltage protection (OVP)and under voltage protection (UVP).The over-voltage and under-voltage signals are OR gated to drive the Power Good signal and a shutdown latch,which turns off the high side gate and turns on the low side gate if pulled low.Current limit is achieved by sensing the voltage V DS across the low side FET.During current limit the high side gate is turned off and the low side gate turned on.The soft start capacitor is discharged by a 95µA source (reducing the maximum duty cycle)until the current is under control.The LM2737does not latch off during UVP or OVP ,and uses the HIGH and LOW comparators for the power-good function only.START UPWhen V CC exceeds 4.2V and the enable pin EN sees a logic high the soft start capacitor begins charging through an internal fixed 10µA source.During this time the output of the error amplifier is allowed to rise with the voltage of the soft start capacitor.This capacitor,Css,determines soft start time,and can be determined approximately by:An application for a microprocessor might need a delay of 3ms,in which case C SS would be 12nF.For a different device,a 100ms delay might be more appropriate,in which case C SS would be 400nF.(39010%)During soft start the PWRGD flag is forced low and is released when the voltage reaches a set value.At this point this chip enters normal operation mode,the Power Good flag is released,and the OVP and UVP functions begin to monitor Vo.NORMAL OPERATIONWhile in normal operation mode,the LM2727/37regulates the output voltage by controlling the duty cycle of the high side and low side FETs.The equation governing output voltage is:The PWM frequency is adjustable between 50kHz and 2MHz and is set by an external resistor,R FADJ ,between the FREQ pin and ground.The resistance needed for a desired frequency is approximately:LM2727/LM27379Application Information(Continued)MOSFET GATE DRIVERSThe LM2727/37has two gate drivers designed for driving N-channel MOSFETs in a synchronous mode.Power for the drivers is supplied through the BOOTV pin.For the high side gate (HG)to fully turn on the top FET,the BOOTV voltage must be at least one V GS(th)greater than Vin.(BOOTV ≥2*Vin)This voltage can be supplied by a separate,higher voltage source,or supplied from a local charge pump struc-ture.In a system such as a desktop computer,both 5V and 12V are usually available.Hence if Vin was 5V,the 12V supply could be used for BOOTV.12V is more than 2*Vin,so the HG would operate correctly.For a BOOTV of 12V,the initial gate charging current is 2A,and the initial gate dis-charging current is typically 6A.In a system without a separate,higher voltage,a charge pump (bootstrap)can be built using a diode and small ca-pacitor,Figure 1.The capacitor serves to maintain enough voltage between the top FET gate and source to control the device even when the top FET is on and its source has risen up to the input voltage level.The LM2727/37gate drives use a BiCMOS design.Unlike some other bipolar control ICs,the gate drivers have rail-to-rail swing,ensuring no spurious turn-on due to capacitive coupling.POWER GOOD SIGNALThe power good signal is the or-gated flag representing over-voltage and under-voltage protection.If the output volt-age is 18%over it’s nominal value,V FB =0.7V,or falls 30%below that value,V FB =0.41V,the power good flag goes low.The converter then turns off the high side gate,and turns on the low side gate.Unlike the output (LM2727only)the power good flag is not latched off.It will return to a logic high whenever the feedback pin voltage is between 70%and 118%of 0.6V.UVLOThe 4.2V turn-on threshold on V CC has a built in hysteresis of 0.6V.Therefore,if V CC drops below 3.6V,the chip enters UVLO mode.UVLO consists of turning off the top FET,turning on the bottom FET,and remaining in that conditionuntil V CC rises above 4.2V.As with shutdown,the soft start capacitor is discharged through a FET,ensuring that the next start-up will be smooth.CURRENT LIMITCurrent limit is realized by sensing the voltage across the low side FET while it is on.The R DSON of the FET is a known value,hence the current through the FET can be determined as:V DS =I *R DSON The current limit is determined by an external resistor,R CS ,connected between the switch node and the ISEN pin.A constant current of 50µA is forced through Rcs,causing a fixed voltage drop.This fixed voltage is compared against V DS and if the latter is higher,the current limit of the chip has been reached.R CS can be found by using the following:R CS =R DSON (LOW)*I LIM /50µAFor example,a conservative 15A current limit in a 10A design with a minimum R DSON of 10m Ωwould require a 3.3k Ωresistor.Because current sensing is done across the low side FET,no minimum high side on-time is necessary.In the current limit mode the LM2727/37will turn the high side off and the keep low side on for as long as necessary.The chip also discharges the soft start capacitor through a fixed 95µA source.In this way,smooth ramping up of the output voltage as with a normal soft start is ensured.The output of the LM2727/37internal error amplifier is limited by the volt-age on the soft start capacitor.Hence,discharging the soft start capacitor reduces the maximum duty cycle D of the controller.During severe current limit,this reduction in duty cycle will reduce the output voltage,if the current limit con-ditions lasts for an extended time.During the first few nanoseconds after the low side gate turns on,the low side FET body diode conducts.This causes an additional 0.7V drop in V DS .The range of V DS is normally much lower.For example,if R DSON were 10m Ωand the current through the FET was 10A,V DS would be 0.1V.The current limit would see 0.7V as a 70A current and enter current limit immediately.Hence current limit is masked dur-ing the time it takes for the high side switch to turn off and the low side switch to turn on.UVP/OVPThe output undervoltage protection and overvoltage protec-tion mechanisms engage at 70%and 118%of the target output voltage,respectively.In either case,the LM2727will turn off the high side switch and turn on the low side switch,and discharge the soft start capacitor through a MOSFET switch.The chip remains in this state until the shutdown pin has been pulled to a logic low and then released.The UVP function is masked only during the first charging of the soft start capacitor,when voltage is first applied to the V CC pin.In contrast,the LM2737is designed to continue operating dur-ing UVP or OVP conditions,and to resume normal operation once the fault condition is cleared.As with the LM2727,the powergood flag goes low during this time,giving a logic-level warning signal.SHUT DOWNIf the shutdown pin SD is pulled low,the LM2727/37dis-charges the soft start capacitor through a MOSFET switch.The high side switch is turned off and the low side switch is turned on.The LM2727/37remains in this state until SD is released.20049402FIGURE 1.BOOTV Supplied by Charge Pump L M 2727/L M 2737 10Application Information(Continued)DESIGN CONSIDERATIONSThe following is a design procedure for all the componentsneeded to create the circuit shown in Figure3in the Ex-ample Circuits section,a5V in to1.2V out converter,capableof delivering10A with an efficiency of85%.The switchingfrequency is300kHz.The same procedures can be followedto create the circuit shown in Figure3,Figure4,and tocreate many other designs with varying input voltages,out-put voltages,and output currents.INPUT CAPACITORThe input capacitors in a Buck switching converter are sub-jected to high stress due to the input current waveform,which is a square wave.Hence input caps are selected fortheir ripple current capability and their ability to withstand theheat generated as that ripple current runs through their ESR.Input rms ripple current is approximately:The power dissipated by each input capacitor is:Here,n is the number of capacitors,and indicates that powerloss in each cap decreases rapidly as the number of inputcaps increase.The worst-case ripple for a Buck converteroccurs during full load,when the duty cycle D=50%.In the5V to 1.2V case,D= 1.2/5=0.24.With a10Amaximum load the ripple current is 4.3A.The Sanyo10MV5600AX aluminum electrolytic capacitor has a ripplecurrent rating of2.35A,up to105˚C.Two such capacitorsmake a conservative design that allows for unequal currentsharing between individual caps.Each capacitor has a maxi-mum ESR of18mΩat100kHz.Power loss in each device isthen0.05W,and total loss is0.1W.Other possibilities forinput and output capacitors include MLCC,tantalum,OSCON,SP,and POSCAPS.INPUT INDUCTORThe input inductor serves two basic purposes.First,in highpower applications,the input inductor helps insulate theinput power supply from switching noise.This is especiallyimportant if other switching converters draw current from thesame supply.Noise at high frequency,such as that devel-oped by the LM2727at1MHz operation,could pass throughthe input stage of a slower converter,contaminating andpossibly interfering with its operation.An input inductor also helps shield the LM2727from highfrequency noise generated by other switching converters.The second purpose of the input inductor is to limit the inputcurrent slew rate.During a change from no-load to full-load,the input inductor sees the highest voltage change across it,equal to the full load current times the input capacitor ESR.This value divided by the maximum allowable input currentslew rate gives the minimum input inductance:In the case of a desktop computer system,the input currentslew rate is the system power supply or"silver box"outputcurrent slew rate,which is typically about0.1A/µs.Total inputcapacitor ESR is9mΩ,hence∆V is10*0.009=90mV,andthe minimum inductance required is0.9µH.The input induc-tor should be rated to handle the DC input current,which isapproximated by:In this case I IN-DC is about2.8A.One possible choice is theTDK SLF12575T-1R2N8R2,a1.2µH device that can handle8.2Arms,and has a DCR of7mΩ.OUTPUT INDUCTORThe output inductor forms the first half of the power stage ina Buck converter.It is responsible for smoothing the squarewave created by the switching action and for controlling theoutput current ripple.(∆I o)The inductance is chosen byselecting between tradeoffs in efficiency and response time.The smaller the output inductor,the more quickly the con-verter can respond to transients in the load current.Asshown in the efficiency calculations,however,a smaller in-ductor requires a higher switching frequency to maintain thesame level of output current ripple.An increase in frequencycan mean increasing loss in the FETs due to the chargingand discharging of the gates.Generally the switching fre-quency is chosen so that conduction loss outweighs switch-ing loss.The equation for output inductor selection is:Plugging in the values for output current ripple,input voltage,output voltage,switching frequency,and assuming a40%peak-to-peak output current ripple yields an inductance of1.5µH.The output inductor must be rated to handle the peakcurrent(also equal to the peak switch current),which is(Io+0.5*∆I o).This is12A for a10A design.The Coilcraft D05022-152HC is1.5µH,is rated to15Arms,and has a DCR of4mΩ.OUTPUT CAPACITORThe output capacitor forms the second half of the powerstage of a Buck switching converter.It is used to control theoutput voltage ripple(∆V o)and to supply load current duringfast load transients.In this example the output current is10A and the expectedtype of capacitor is an aluminum electrolytic,as with theinput capacitors.(Other possibilities include ceramic,tanta-lum,and solid electrolyte capacitors,however the ceramictype often do not have the large capacitance needed tosupply current for load transients,and tantalums tend to bemore expensive than aluminum electrolytic.)Aluminum ca-pacitors tend to have very high capacitance and fairly lowESR,meaning that the ESR zero,which affects systemstability,will be much lower than the switching frequency.The large capacitance means that at switching frequency,the ESR is dominant,hence the type and number of outputcapacitors is selected on the basis of ESR.One simpleformula to find the maximum ESR based on the desiredoutput voltage ripple,∆V o and the designed output currentripple,∆I o,is:LM2727/LM2737Application Information(Continued)In this example,in order to maintain a 2%peak-to-peak output voltage ripple and a 40%peak-to-peak inductor cur-rent ripple,the required maximum ESR is 6m Ω.Three Sanyo 10MV5600AX capacitors in parallel will give an equivalent ESR of 6m Ω.The total bulk capacitance of 16.8mF is enough to supply even severe load ing the same capacitors for both input and output also keeps the bill of materials simple.MOSFETSMOSFETS are a critical part of any switching controller and have a direct impact on the system efficiency.In this case the target efficiency is 85%and this is the variable that will determine which devices are acceptable.Loss from the ca-pacitors,inductors,and the LM2727itself are detailed in the Efficiency section,and come to about 0.54W.To meet the target efficiency,this leaves 1.45W for the FET conduction loss,gate charging loss,and switching loss.Switching loss is particularly difficult to estimate because it depends on many factors.When the load current is more than about 1or 2amps,conduction losses outweigh the switching and gate charging losses.This allows FET selection based on the R DSON of the FET.Adding the FET switching and gate-charging losses to the equation leaves 1.2W for conduction losses.The equation for conduction loss is:P Cnd =D(I 2o *R DSON *k)+(1-D)(I 2o *R DSON *k)The factor k is a constant which is added to account for the increasing R DSON of a FET due to heating.Here,k =1.3.The Si4442DY has a typical R DSON of 4.1m Ω.When plugged into the equation for P CND the result is a loss of 0.533W.If this design were for a 5V to 2.5V circuit,an equal number of FETs on the high and low sides would be the best solution.With the duty cycle D =0.24,it becomes apparent that the low side FET carries the load current 76%of the time.Adding a second FET in parallel to the bottom FET could improve the efficiency by lowering the effective R DSON .The lower the duty cycle,the more effective a second or even third FET can be.For a minimal increase in gate charging loss (0.054W)the decrease in conduction loss is 0.15W.What was an 85%design improves to 86%for the added cost of one SO-8MOSFET.CONTROL LOOP COMPONENTSThe circuit is this design example and the others shown in the Example Circuits section have been compensated to improve their DC gain and bandwidth.The result of this compensation is better line and load transient responses.For the LM2727,the top feedback divider resistor,Rfb2,is also a part of the compensation.For the 10A,5V to 1.2V design,the values are:Cc1=4.7pF 10%,Cc2=1nF 10%,Rc =229k Ω1%.These values give a phase margin of 63˚and a bandwidth of 29.3kHz.SUPPORT CAPACITORS AND RESISTORSThe Cinx capacitors are high frequency bypass devices,designed to filter harmonics of the switching frequency and input noise.Two 1µF ceramic capacitors with a sufficient voltage rating (10V for the Circuit of Figure 3)will work well in almost any case.Rbypass and Cbypass are standard filter components de-signed to ensure smooth DC voltage for the chip supply and for the bootstrap structure,if it is e 10Ωfor the resistor and a 2.2µF ceramic for the cap.Cb is the bootstrap capacitor,and should be 0.1µF.(In the case of a separate,higher supply to the BOOTV pin,this 0.1µF cap can be used to bypass the supply.)Using a Schottky device for the boot-strap diode allows the minimum drop for both high and low side drivers.The On Semiconductor BAT54or MBR0520work well.Rp is a standard pull-up resistor for the open-drain power good signal,and should be 10k Ω.If this feature is not necessary,it can be omitted.R CS is the resistor used to set the current limit.Since the design calls for a peak current magnitude (Io +0.5*∆I o )of 12A,a safe setting would be 15A.(This is well below the saturation current of the output inductor,which is 25A.)Following the equation from the Current Limit section,use a 3.3k Ωresistor.R FADJ is used to set the switching frequency of the chip.Following the equation in the Theory of Operation section,the closest 1%tolerance resistor to obtain f SW =300kHz is 88.7k Ω.C SS depends on the users requirements.Based on the equation for C SS in the Theory of Operation section,for a 3ms delay,a 12nF capacitor will suffice.EFFICIENCY CALCULATIONSA reasonable estimation of the efficiency of a switching controller can be obtained by adding together the loss is each current carrying element and using the equation:The following shows an efficiency calculation to complement the Circuit of Figure 3.Output power for this circuit is 1.2V x 10A =12W.Chip Operating LossP IQ =I Q-V CC *V CC2mA x 5V =0.01WFET Gate Charging LossP GC =n *V CC *Q GS *f OSCThe value n is the total number of FETs used.The Si4442DY has a typical total gate charge,Q GS ,of 36nC and an r ds-on of 4.1m Ω.For a single FET on top and bottom:2*5*36E -9*300,000=0.108W FET Switching LossP SW =0.5*V in *I O *(t r +t f )*f OSC The Si4442DY has a typical rise time t r and fall time t f of 11and 47ns,respectively.0.5*5*10*58E -9*300,000=0.435WL M 2727/L M 2737。

SI4336DY中文资料

FEATURESD Ultra Low On-Resistance Using High Density TrenchFET r Gen II Power MOSFET Technology D Q g Optimized D 100% R g TestedAPPLICATIONSD Synchronous Buck Low-Side −Notebook −Server−WorkstationD Synchronous Rectifier, POLVishay SiliconixN-Channel 30-V (D-S) MOSFETPRODUCT SUMMARYV DS (V)r DS(on) (W )I D (A)Q g (Typ)0.00325 @ V GS = 10 V 25300.0042 @ V GS= 4.5 V2236SO-8S D S D S D GD5678Top View2341Ordering Information:Si4336DYSi4336DY-T1 (with Tape and Reel)N-Channel MOSFETGDABSOLUTE MAXIMUM RATINGS (T A = 25_C UNLESS OTHERWISE NOTED)ParameterSymbol10 secsSteady State UnitDrain-Source Voltage V DS 30Gate-Source VoltageV GS "20VT A = 25_C 2517Continuous Drain Current (T J = 150_C)a T A = 70_CI D 2013Pulsed Drain Current (10 m s Pulse Width)I DM 70AContinuous Source Current (Diode Conduction)a I S 2.91.3Avalanche CurrentL = 0.1 mH I AS 50Maximum Power Dissipation T A = 25_C 3.5 1.6aT A = 70_C P D 2.21W Operating Junction and Storage Temperature RangeT J , T stg−55 to 150_CTHERMAL RESISTANCE RATINGSParameterSymbol TypicalMaximumUnitM iJ ti t A bi t t v 10 sec 2935Maximum Junction-to-Ambient a Steady State R thJA 6780_Maximum Junction-to-Foot (Drain)Steady StateR thJF1316C/WNotesa.Surface Mounted on 1” x 1” FR4 Board.Vishay SiliconixSPECIFICATIONS (T J = 25_C UNLESS OTHERWISE NOTED)ParameterSymbol Test Condition Min Typ Max UnitStaticGate Threshold Voltage V GS(th)V DS = V GS , I D = 250 m A 1.03.0V Gate-Body LeakageI GSS V DS = 0 V, V GS = "20 V "100nAV DS = 30 V, V GS = 0 V 1Zero Gate Voltage Drain Current I DSS V DS = 30 V, V GS = 0 V, T J = 55_C5m A On-State Drain Current aI D(on)V DS w 5 V, V GS = 10 V 30A Drain-Source On-State Resistance V GS = 10 V, I D = 25 A 0.00260.00325a r DS(on)V GS = 4.5 V, I D = 22 A 0.00330.0042W Forward Transconductance a g fs V DS = 15 V, I D = 25 A 110S Diode Forward Voltage aV SDI S = 2.9 A, V GS = 0 V0.721.1VDynamic bInput Capacitance C iss 5600Output CapacitanceC oss V = 15 V, V GS = 0 V, f = 1 MHz860pF Reverse Transfer Capacitance C rss DS 415pTotal Gate Charge Q g 3650Gate-Source Charge Q gs V = 15 V, V GS = 4.5 V, I D = 20 A 18nC Gate-Drain Charge Q gd DS 10Gate Resistance R g 0.81.32.0WTurn-On Delay Time t d(on)2435Rise Timet r V 1625Turn-Off Delay Time t d(off)DD = 15 V, R L = 15 WI D ^ 1 A, V GEN = 10 V, R = 6 W90140ns Fall Timet f g 3250Source-Drain Reverse Recovery Timet rrI F = 2.9 A, di/dt = 100 A/m s 4570Notesa.Pulse test; pulse width v 300 m s, duty cycle v 2%.b.Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.0.00.51.01.52.02.53.03.54.00.00.40.81.21.62.0V DS − Drain-to-Source Voltage (V)V GS − Gate-to-Source Voltage (V)Vishay SiliconixTYPICAL CHARACTERISTICS (25_C UNLESS NOTED)0100020003000400050006000700006121824300.0000.0010.0020.0030.0040.0051020304050012345651015202530354045−50−250255075100125150Gate ChargeOn-Resistance vs. Drain Current− G a t e -t o -S o u r c e V o l t a g e (V )Q g − Total Gate Charge (nC)V DS − Drain-to-Source Voltage (V)C − C a p a c i t a n c e (p F )V G S − O n -R e s i s t a n c e (r D S (o n )W )I D − Drain Current (A)CapacitanceOn-Resistance vs. Junction TemperatureT J − Junction Temperature (_C)1.01.20.0000.0030.0060.0090.0120.0152468100.110500.000.20.40.60.8Source-Drain Diode Forward Voltage− O n -R e s i s t a n c e (r D S (o n )W )V SD − Source-to-Drain Voltage (V)V GS − Gate-to-Source Voltage (V)− S o u r c e C u r r e n t (A )I S 1r D S (o n ) − O n -R e s i i s t a n c e (N o r m a l i z e d )Vishay SiliconixTYPICAL CHARACTERISTICS (25_C UNLESS NOTED)210.10.01Normalized Thermal Transient Impedance, Junction-to-FootN o r m a l i z e d E f f e c t i v e T r a n s i e n t T h e r m a l I m p e d a n c eVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?72417.。

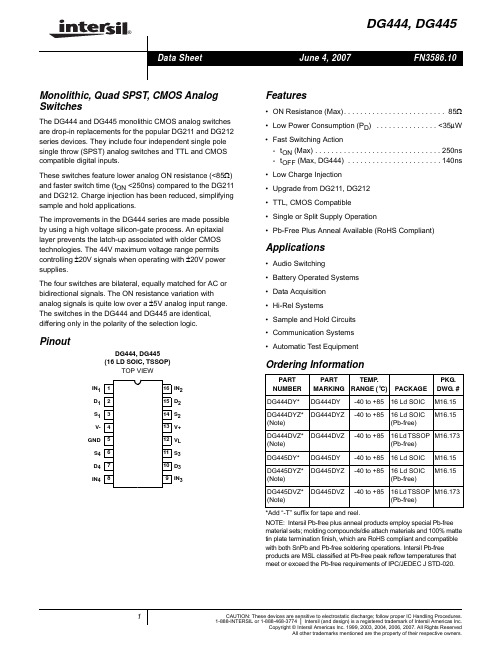

DG444DYZ中文资料

Copyright © Intersil Americas Inc. 1999, 2003, 2004, 2006, 2007. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

元器件交易网

®

Data Sheet

DG444, DG445

June 4, 2007

FN3586.10

Monolithic, Quad SPST, CMOS Analog Switches

The DG444 and DG445 monolithic CMOS analog switches are drop-in replacements for the popular DG211 and DG212 series devices. They include four independent single pole single throw (SPST) analog switches and TTL and CMOS compatible digital inputs.

9801TB说明书液晶总线无显示探测器

SST-9801B-Z气体报警控制系统使用说明书制造商:深圳市索富通实业有限公司安装、使用产品前,请阅读使用说明书使用说明书目录1、概述 (1)2、系统特点与系统主要参 ......................................................................................................................... 数 (1)2.1 系统特点 (1)2.2 系统主要参数 (1)3、系统组成及适用气体 (2)3.1 系统组成 (2)3.2 适用气体 (2)4、探测器的工作原理、结构与安装 (2)4.1 探测器的工作原理 (2)4.2 探测器的结构 (3)4.3 探测器的安装 (3)5、控制器的工作原理、结构与安装 (3)5.1 控制器的工作原理 (3)5.2 控制器的结构 (3)5.3 控制器的安装 (3)5.4 面板说明 (4)6、系统使用与功能菜单操作 (6)6.1 系统使用 (6)6.2 功能菜单操作 (11)7、维护与故障检修 (13)7.1 日常维护 (13)7.2 故障检修 (13)7.3 检测元件寿命及使用注意事项 (13)8、系统接线示意图 (14)附录1 探测器编码示意图 (15)《保修条款》 (16)参考附录目录使用说明书1、概述SST-9801B-Z报警控制系统由两部分组成:气体探测器与气体报警控制器;气体探测器(一次表)安装在可能有气体泄漏的危险场所,其核心元件为气敏传感器;气体报警控制器(二次表)安装在安全场所的值班室内。

当空气中有检测气体泄漏时,气体探测器检测信号通过电缆立即传送到报警控制单元。

控制器显示出气体浓度,当超过设定的报警浓度值时,报警控制器即发出声、光报警信号并输出联动控制信号,控制风机等设备排除险情,从而起到保障工厂安全生产,避免事故发生。

广泛用于各类炼油厂、油库、化工厂、液化气站等易发生泄漏的特殊场所。

SI4425DY中文资料

January 2001Si4425DYSingle P-Channel, Logic Level, PowerTrench General Description Features Absolute Maximum Ratings T A = 25o C unless otherwise noted SOT-23SuperSOT TM This P-Channel Logic Level MOSFET is produced using Fairchild Semiconductor's advanced PowerTrench process that has been especially tailored to minimize the on-state resistance and yet maintain low gate charge for superior switching performance.These devices are well suited for notebook computer applications: load switching and power management,battery charging circuits, and DC/DC conversion.SSSSO-8DDD Gpin 14425TRADEMARKSACEx™CoolFET™CROSSVOLT™E 2CMOS TM FACT™FACT Quiet Series™FAST ®FASTr™GTO™HiSeC™The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORTDEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROV AL OF FAIRCHILD SEMICONDUCTOR CORPORA TION.As used herein:ISOPLANAR™MICROWIRE™POP™PowerTrench™QS™Quiet Series™SuperSOT™-3SuperSOT™-6SuperSOT™-8TinyLogic™1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant intothe body, or (b) support or sustain life, or (c) whosefailure to perform when properly used in accordancewith instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a lifesupport device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Product Status DefinitionAdvance InformationPreliminary No Identification Needed Obsolete This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.This datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.Formative or In DesignFirst ProductionFull ProductionNot In ProductionDISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY , FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.UHC™VCX™。

SI4401DDY-T1-GE3;中文规格书,Datasheet资料

0.024 V GS = 4.5 V 0.018 V GS = 10 V 0.012

C - Capacitance (pF)

3600 Ciss 2700

1800

0.006

900

Coss Crss

0 0 10 20 30 40 50

0 0 8 16 24 32 40

ID - Drain Current (A)

0.5

1.0

1.5

2.0

VDS - Drain-to-Source Voltage (V)

VGS - Gate-to-Source Voltage (V)

Output Characteristics

0.030 4500

Transfer Characteristics

RDS(on) - On-Resistance (Ω)

50 V GS = 10 V thru 5 V 40

ID - Drain Current (A)

10

V GS = 4 V

ID - Drain Current (A)

8

30

6

20

4 T C = 25 °C 2

10 V GS = 3 V 0 0.0

T C = 125 °C 0 T C = - 55 °C 0 1 2 3 4

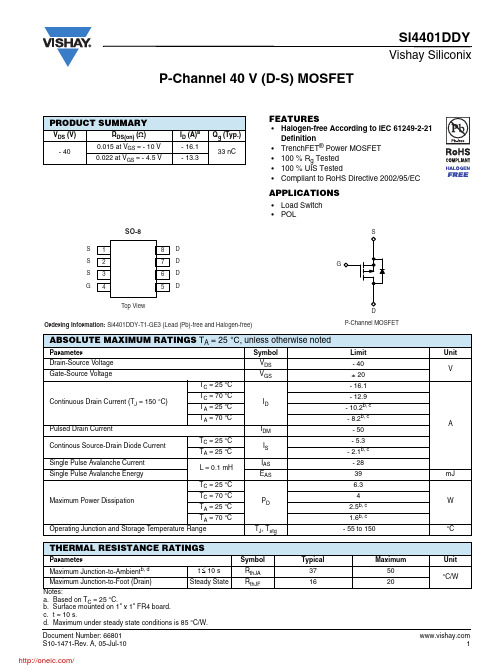

• Halogen-free According to IEC 61249-2-21 Definition • TrenchFET® Power MOSFET • 100 % Rg Tested • 100 % UIS Tested • Compliant to RoHS Directive 2002/95/EC

Si4401DDY

Vishay Siliconix

SI4410DYTRPBF;SI4410DYPBF;中文规格书,Datasheet资料

ParameterMax.UnitsV DSDrain- Source Voltage30V I D @ T A = 25°C Continuous Drain Current, V GS @ 10V ±10I D @ T A = 70°C Continuous Drain Current, V GS @ 10V ±8.0AI DMPulsed Drain Current ±50P D @T A = 25°C Power Dissipation 2.5P D @T A = 70°C Power Dissipation 1.6Linear Derating Factor0.02W/°C dv/dt Peak Diode Recovery dv/dt 5.0V/ns E AS Single Pulse Avalanche Energy 400mJ V GSGate-to-Source Voltage± 20V T J, T STGJunction and Storage Temperature Range-55 to + 150°Cl N-Channel MOSFET l Low On-Resistance l Low Gate Charge l Surface Mount lLogic Level Drive lLead-Free09/22/04Si4410DYPbFHEXFET ® Power MOSFETParameterMax.UnitsR θJAMaximum Junction-to-Ambient50°C/WThermal ResistanceThis N-channel HEXFET ® Power MOSFET is produced using International Rectifier's advanced HEXFET power MOSFET technology. The low on-resistance and low gate charge inherent to this technology make this device ideal for low voltage or battery driven power conversion applications The SO-8 package with copper leadframe offers enhanced thermal characteristics that allow power dissipation of greater that 800mW in typical board mount applications.DescriptionAbsolute Maximum RatingsW 1PD - 95168SO-8V DSS = 30V R DS(on) = 0.0135ΩSi4410DYPbFRepetitive rating; pulse width limited bymax. junction temperature.Notes:Pulse width ≤ 300µs; duty cycle ≤ 2%. When mounted on FR4 Board, t ≤10 secStarting T J = 25°C, L = 8.0mHR G = 25Ω, I AS = 10A. (See Figure 15)I SD ≤2.3A, di/dt ≤ 130A/µs, V DD ≤ V (BR)DSS ,T J ≤ 150°CSi4410DYPbF 3Vs. TemperatureFig 2. Typical Output CharacteristicsFig 3. Typical Transfer Characteristics101001000481216GSV , Gate-to-Source Voltage (V)D I , D r a i n -t o -S o u r c e C u r r e n t (A )Si4410DYPbFGate-to-Source VoltageDrain-to-Source Voltage Forward VoltageSi4410DYPbF 5Fig 11. Typical Effective Transient Thermal Impedance, Junction-to-AmbientCase TemperatureFig 10. Typical Power Vs. Time204060801000.010.1110100P o w e r ( W )Time (sec)Si4410DYPbFFig 12. Typical On-Resistance Vs. DrainCurrent Fig 13. Typical On-Resistance Vs. GateVoltage0.000.040.080.120.160.201020304050I , Drain Current (A)D R , D r a i n -t o -S o u r c e O n R e s i s t a n c e DS (o n )(Ω)0.000.010.020.03345678910R , D r a i n -t o -S o u r c e O n R e s i s t a n c e D S (o n )(Ω)GSV , Gate-to-Source Voltage (V)Fig 14.1.52.02.53.0-60-40-20020406080100120140160JT , Junction Temperature (°C)G S (t h )V , V a r i a n c e ( V )Vs. Drain CurrentSi4410DYPbFSO-8 Package OutlineSi4410DYPbFData and specifications subject to change without notice.This product has been designed and qualified for the Consumer market.Qualifications Standards can be found on IR’s Web site.IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105TAC Fax: (310) 252-7903Visit us at for sales contact information .09/04330.00(12.992) MAX.14.40 ( .566 )12.40 ( .488 )NOTES :1. CONTROLLING DIMENSION : MILLIMETER.2. OUTLINE CONFORMS TO EIA-481 & EIA-541.FEED DIRECTIONTERMINAL NUMBER 112.3 ( .484 )11.7 ( .461 )8.1 ( .318 )7.9 ( .312 )NOTES:1. CONTROLLING DIMENSION : MILLIMETER.2. ALL DIMENSIONS ARE SHOWN IN MILLIMETERS(INCHES).3. OUTLINE CONFORMS TO EIA-481 & EIA-541.SO-8 Tape and ReelDimensions are shown in millimeters (inches)分销商库存信息:IRSI4410DYTRPBF SI4410DYPBF。

SI3048资料

Si3035 3.3V FCC/JATE D I R E C T A CC E S S A RR A NG E M E N T!Other Patents PendingRev. 1.2 12/00Copyright © 2000 by Silicon Laboratories Si3035-DS12Si30352Rev. 1.2Si3035 T A B L E O F C O N T E N T SSection Page Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Typical Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Bill of Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Analog Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Isolation Barrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Off-Hook . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Ring Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Improved JATE Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Digital Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Clock Generation Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Analog Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 On-Hook Line Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Loop Current Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Multiple Device Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Filter Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Revision Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 In-Circuit Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Exception Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Appendix—UL1950 3rd Edition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Pin Descriptions: Si3021 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 Pin Descriptions: Si3012 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 SOIC Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 TSSOP Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Rev. 1.23Si3035Electrical SpecificationsTable 1. Recommended Operating ConditionsParameter1Symbol Test Condition Min2Typ Max2Unit Ambient Temperature T A K-Grade02570°C Si3021 Supply Voltage, Analog V A 4.75 5.0 5.25V Si3021 Supply Voltage, Digital3V D 3.0 3.3/5.0 5.25V Notes:1. The Si3035 specifications are guaranteed when the typical application circuit (including componenttolerances) and any Si3021 and any Si3012 are used. See Figure16 on page 15 for typical application circuit.2. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.Typical values apply at nominal supply voltages and an operating temperature of 25°C unless otherwise stated.3. The digital supply, V D, can operate from either 3.3V or 5.0V. The Si3021 supports interface to 3.3V logic whenoperating from 3.3V. The 3.3V operation applies to both the serial port and the digital signalsRGDT, OFHK, RESET, M0, and M1.Table 2. Loop Characteristics(V A = Charge Pump, V D = +3.3 V ± 0.3V, T A = 0 to 70°C for K-Grade, Refer to Figure1)Parameter Symbol Test Condition Min Typ Max Unit DC Termination Voltage V TR I L = 20 mA——7.7V DC Termination Voltage V TR I L = 105 mA12——V DC Ring Current (with caller ID)I RDC——1mA DC Ring Current (w/o caller ID)I RDC——20µA AC Termination Impedance Z ACT—600—ΩOperating Loop Current I LP20—120mA Loop Current Sense Bits LCS LCS = Fh180155—mA Ring Voltage Detect V RD131826V RMS Ring Frequency F R15—68Hz On-Hook Leakage Current I LK V BAT = –48V——1µA Ringer Equivalence Num. (with caller ID)REN— 1.0 1.67—Ringer Equivalence Num. (w/o caller ID)REN—0.2——4Rev. 1.2Si3035Table 3. DC Characteristics, V D = +5V(V A = +5 V ±5%, V D = +5V ±5%, T A = 0 to 70°C for K-Grade)Parameter Symbol Test Condition Min Typ Max Unit High Level Input Voltage V IH 3.5——V Low Level Input Voltage V IL——0.8V High Level Output Voltage V OH I O = –2 mA 3.5——V Low Level Output Voltage V OL I O = 2 mA——0.4V Input Leakage Current I L–10—10µA Power Supply Current, Analog I A V A pin —0.31mA Power Supply Current, Digital1I D V D pin—1418mA Total Supply Current, Sleep Mode1I A + I D PDN = 1, PDL = 0— 1.3 2.5mA Total Supply Current, Deep Sleep1,2I A + I D PDN = 1, PDL = 1—0.040.5mA Notes:1.All inputs at 0.4 or V D – 0.4 (CMOS levels). All inputs held static except clock and all outputs unloaded(Static I OUT = 0mA).2. RGDT is not functional in this state.Table 4. DC Characteristics, V D = +3.3V(V A = Charge Pump, V D = +3.3V ± 0.3V, T A = 0 to 70°C for K-Grade)Parameter Symbol Test Condition Min Typ Max Unit High Level Input Voltage V IH 2.0——V Low Level Input Voltage V IL——0.8V High Level Output Voltage V OH I O = –2 mA 2.4—— V Low Level Output Voltage V OL I O = 2 mA——0.35V Input Leakage Current I L–10—10µA Power Supply Current, Analog1,2I A V A pin—0.31mA Power Supply Current, Digital3I D V D pin—912mA Total Supply Current, Sleep Mode3I A + I D PDN = 1, PDL = 0— 1.2 2.5mA Total Supply Current, Deep Sleep3,4I A + I D PDN = 1, PDL = 1—0.040.5Power Supply Voltage, Analog1,5V A Charge Pump On 4.3 4.6 5.00V Notes:1.Only a decoupling capacitor should be connected to V A when the charge pump is on.2. There is no I A current consumption when the internal charge pump is enabled and only a decoupling cap is connectedto the V A pin.3. All inputs at 0.4 or V D – 0.4 (CMOS levels). All inputs held static except clock and all outputs unloaded(Static I OUT = 0mA).4. RGDT is not functional in this state.5. The charge pump is recommended to be used only when V D < 4.5V. When the charge pump is not used, V A should beapplied to the device before V D is applied on power up if driven from separate supplies.Rev. 1.25Si3035Table 5. AC Characteristics(V A = Charge Pump, V D = +3.3V ± 0.3V, T A = 0 to 70°C for K-Grade)Parameter Symbol Test Condition Min Typ Max Unit Sample Rate1Fs Fs = F PLL2/51207.2—11.025kHz PLL1 Output Clock Frequency F PLL1FPLL1 = F MCLK"M1/N136—58MHz Transmit Frequency Response Low –3 dB corner—16—Hz Receive Frequency Response Low –3 dB corner—16—Hz Transmit Full Scale Level2 (0 dB gain)V TX—0.98—V PEAK Receive Full Scale Level 2,3 (0 dB gain)V RX—0.98—V PEAK Dynamic Range4DR VIN = 1 kHz, –3 dBFS8086—dB Dynamic Range5DR VIN = 1 kHz, –3 dBFS—84—dB Total Harmonic Distortion6THD VIN = 1 kHz, –3 dBFS—–84—dB Dynamic Range (call progress AOUT)DR AO VIN = 1 kHz60——dB THD (call progress AOUT)THD AO VIN = 1 kHz— 1.0—% AOUT Full Scale Level—0.75 V D—V PP AOUT Output Impedance—10—kΩMute Level (call progress AOUT)–90——dB Dynamic Range (caller ID mode)DR CID VIN = 1 kHz, –13dBFS—60—dB Caller ID Full Scale Level (0 dB gain)2V CID—0.8—V PEAK Notes:1.See Figure23 on page 22.2. Parameter measured at TIP and RING of Figure16 on page 15.3. Receive Full Scale Level will produce – 0.9 dBFS at SDO.4. DR = 3 dB + 20 log (RMS signal/RMS noise). Applies to both the transmit and receive paths. Measurement bandwidthis 300 to 3400 Hz. Sample Rate = 9.6 kHz, Loop Current = 40 mA.5. DR = 3 dB + 20 log (RMS signal/RMS noise). Applies to both the transmit and receive paths. Measurement bandwidthis 15 to 3400 Hz. Sample Rate = 9.6 kHz, Loop Current = 40 mA.6. THD = 20 log (RMS distortion/RMS signal). Applies to both the transmit and receive paths.Sample Rate = 9.6kHz, Loop Current = 40 mA.6Rev. 1.2Si3035Rev. 1.27Figure 2. General Inputs Timing DiagramTable 6. Absolute Maximum RatingsParameter Symbol Value Unit DC Supply VoltageV D , V A –0.5 to 6.0V Input Current, Si3021 Digital Input Pins I IN ±10mA Digital Input VoltageV IND –0.3 to (V D + 0.3)V Operating Temperature Range T A –40 to 100°C Storage Temperature RangeT STG–65 to 150°CNote:Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operationshould be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Table 7. Switching Characteristics—General Inputs(V A = Charge Pump, V D = 3.0 to 5.25V, T A = 0 to 70°C for K-Grade, C L = 20 pF)Parameter 1Symbol Min Typ Max Unit Cycle Time, MCLK t mc 16.67—1000ns MCLK Duty Cycle t dty 405060%Rise Time, MCLK t r ——5ns Fall Time, MCLK t f ——5ns MCLK Before RESET ↑t mr 10——cycles RESET Pulse Width 2t rl 250——ns M0, M1 Before RESET ↑3t mxr150——nsNotes:1.All timing (except Rise and Fall time) is referenced to the 50% level of the waveform. Input test levels areV IH = V D – 0.4V, V IL = 0.4V. Rise and Fall times are referenced to the 20% and 80% levels of the waveform.2. The minimum RESET pulse width is the greater of 250 ns or 10 MCLK cycle times.3. M0 and M1 are typically connected to V D or GND and should not be changed during normal operation.Si3035Table 8. Switching Characteristics—Serial Interface (DCE = 0)(V A = Charge Pump, V D = 3.0 to 5.25V, T A = 0 to 70°C for K-Grade, C L = 20 pF)Parameter Symbol Min Typ Max Unit Cycle time, SCLK t c3541/256 Fs—ns SCLK duty cycle t dty—50—% Delay time, SCLK ↑ to FSYNC ↓t d1——10ns Delay time, SCLK ↑ to SDO valid t d2——20ns Delay time, SCLK ↑ to FSYNC ↑t d3——10ns Setup time, SDI before SCLK ↓t su25——ns Hold time, SDI after SCLK ↓t h20——ns Setup time, FC ↑ before SCLK ↑t sfc40——ns Hold time, FC ↑ after SCLK ↑t hfc40——ns Note:All timing is referenced to the 50% level of the waveform. Input test levels are V IH = V D – 0.4V, V IL = 0.4VFigure 3. Serial Interface Timing Diagram8Rev. 1.2Si3035Rev. 1.29Table 9. Switching Characteristics—Serial Interface (DCE = 1, FSD = 0)(V A = Charge Pump, V D = 3.0 to 5.25V, T A = 0 to 70°C for K-Grade, C L = 20 pF)Parameter 1,2Symbol Min Typ Max Unit Cycle Time, SCLK t c 3541/256 Fs —ns SCLK Duty Cyclet dty —50—%Delay Time, SCLK ↑ to FSYNC ↑t d1——10ns Delay Time, SCLK ↑ to FSYNC ↓t d2——10ns Delay Time, SCLK ↑ to SDO valid t d30.25t c – 20—0.25t c + 20ns Delay Time, SCLK ↑ to SDO Hi-Z t d4——20ns Delay Time, SCLK ↑ to RGDT ↓t d5——20ns Delay Time, SCLK ↑ to RGDT ↑t d6——20ns Setup Time, SDO Before SCLK ↓t su 25——ns Hold Time, SDO After SCLK ↓t h 20——ns Setup Time, SDI Before SCLK t su225——ns Hold Time, SDI After SCLKt h220——nsNotes:1.All timing is referenced to the 50% level of the waveform. Input test levels are V IH = V D – 0.4V, V IL = 0.4V.2. Refer to the section "Multiple Device Support" on page 25 for functional details.Si303510Rev. 1.2Figure 5. Serial Interface Timing Diagram (DCE = 1, FSD = 1)Table 10. Switching Characteristics—Serial Interface (DCE = 1, FSD = 1)(V A = Charge Pump, V D = 3.0 to 5.25V, T A = 0 to 70°C for K-Grade, C L = 20 pF)Parameter 1,2Symbol Min Typ Max Unit Cycle Time, SCLK t c 3541/256 Fs —ns SCLK Duty Cyclet dty —50—%Delay Time, SCLK ↑ to FSYNC ↑t d1——10ns Delay Time, SCLK ↑ to FSYNC ↓t d2——10ns Delay Time, SCLK ↑ to SDO valid t d30.25t c – 20—0.25t c + 20ns Delay Time, SCLK ↑ to SDO Hi-Z t d4——20ns Delay Time, SCLK ↑ to RGDT ↓t d5——20ns Setup Time, SDO Before SCLK ↓t su 25——ns Hold Time, SDO After SCLK ↓t h 20——ns Setup Time, SDI Before SCLK t su225——ns Hold Time, SDI After SCLKt h220——nsNotes:1.All timing is referenced to the 50% level of the waveform. Input test levels are V IH = V D – 0.4V, V IL = 0.4V.2.Refer to the section "Multiple Device Support" on page 25 for functional details.Si3035 Table 11. Digital FIR Filter Characteristics—Transmit and Receive(V A = Charge Pump, V D = +5V ±5%, Sample Rate = 8kHz, T A = 0 to 70°C for K-Grade)Parameter Symbol Min Typ Max Unit Passband (0.1 dB)F(0.1 dB)0— 3.3kHz Passband (3 dB)F(3 dB)0— 3.6kHz Passband Ripple Peak-to-Peak–0.1—0.1dB Stopband— 4.4—kHz Stopband Attenuation–74——dB Group Delay t gd—12/Fs—sec Note:Typical FIR filter characteristics for Fs = 8000 Hz are shown in Figures 6, 7, 8, and 9.Table 12. Digital IIR Filter Characteristics—Transmit and Receive(V A = Charge Pump, V D = +5V ±5%, Sample Rate = 8 kHz, T A = 0 to 70°C for K-Grade)Parameter Symbol Min Typ Max Unit Passband (3 dB)F(3dB)0— 3.6kHz Passband Ripple Peak-to-Peak–0.2—0.2dB Stopband— 4.4—kHz Stopband Attenuation–40——dB Group Delay t gd— 1.6/Fs—sec Note:Typical IIR filter characteristics for Fs = 8000 Hz are shown in Figures 10, 11, 12, and 13. Figures 14 and 15 show group delay versus input frequency.Rev. 1.211Si303512Rev. 1.2Figure 6. FIR Receive Filter Response Figure 7. FIR Receive Filter Passband Ripple Figure 8. FIR Transmit Filter ResponseFigure 9. FIR Transmit Filter Passband RippleFor Figures 6–9, all filter plots apply to a sample rate of Fs = 8kHz. The filters scale with the sample rate as follows:F (0.1 dB) = 0.4125 Fs F (– 3 dB) = 0.45 Fswhere Fs is the sample frequency.Si3035Rev. 1.213Figure 10. IIR Receive Filter Response Figure 11. IIR Receive Filter Passband RippleFigure 12. IIR Transmit Filter ResponseFigure 13. IIR Transmit Filter Passband RippleFor Figures 10–13, all filter plots apply to a sample rate of Fs = 8kHz. The filters scale with the sample rate as follows:F (–3 dB) = 0.45 Fswhere Fs is the sample frequency.Si303514Rev. 1.2Figure 14. IIR Receive Group Delay Figure 15. IIR Transmit Group DelaySi3035Bill of MaterialsTable 13. Component Values—Typical ApplicationComponent1Value Supplier(s) C1,C4150 pF, 3kV, X7R, ±20%Novacap, Venkel, Johanson, Murata,Panasonic, SMEC C2Not InstalledC30.22 µF, 16V, X7R, ±20%C5 1 µF, 16V, Tant/Elec, ±20%C6,C10,C160.1 µF, 16V, X7R, ±20%C7,C8,C915 nF, 250 V, X7R, ±20%Novacap, Johanson, Murata, Panasonic, SMEC C1139 nF, 16V, X7R, ±20%C122 2.7 nF, 16V, X7R, ±20%C2320.1 µF, 16V, Tant/Elec/X7R, ±20%C24, C25, C31,C3231000 pF, 3kV, X7R, ±10%Novacap, Venkel, Johanson, Murata, Panasonic, SMEC C304Not InstalledD1,D25Dual Diode, 300 V, 225 mA Central SemiconductorD3,D4BAV99 Dual Diode, 70 V, 350 mW Diodes, Inc., OnSemiconductor, FairchildFB1,FB2Ferrite Bead MurataQ1,Q3A42, NPN, 300 V OnSemiconductor, FairchildQ2A92, NPN, 300 V OnSemiconductor, FairchildRV1Sidactor, 275 V, 100 A Teccor, ST Microelectronics, Microsemi, TIRV2MOV, 240 V PanasonicR151 Ω, 1/2 W ±5%R215 Ω, 1/4 W ±5%R36Not InstalledR42,R18,R212301 Ω, 1/10 W, ±1%R5,R636 kΩ, 1/10 W ±5%R9,R10 2 kΩ, 1/10 W ±5%R22,R2320 kΩ, 1/10 W ±5%R27,R2810 Ω, 1/10 W ±5%U1Si3021Silicon LabsU2Si3012Silicon LabsZ1Zener diode, 18V Vishay, Rohm, OnSemiconductorZ4,Z5Zener diode, 5.6V, 1/2 W Diodes, Inc., OnSemiconductor, Fairchild Notes:1.The following reference designators were intentionally omitted: C13–C15, C17–C22, C26–C29, R7, R8, R11–R17,R19, and R20.2. If JATE support is not required, C12, and C23 may be removed.3. Alternate population option is C24, C25 (2200pF, 3 kV, X7R, ±10% and C31, C32 not installed).4. Install only if needed for improved radiated emissions performance (10 pF, 16V, NPO, ±10%).5. Several diode bridge configurations are acceptable (suppliers include General Semi, Diodes Inc.)6. If the charge pump is not enabled (with the CPE bit in Register6), V A must be 4.75 to 5.25 V. R3 can be installed witha 10Ω, 1/10 W, ±5% if V D is also 4.75 to 5.25 V.16Rev. 1.2Si3035Rev. 1.217Analog OutputFigure 17 illustrates an optional application circuit to support the analog output capability of the Si3035 for call progress monitoring purposes. The ARM bits in Register 6 allow the receive path to be attenuated by 0dB, –6dB,or –12dB. The ATM bits, which are also in Register 6, allow the transmit path to be attenuated by –20dB, –26dB,or –32dB. Both the transmit and receive paths can also be independently muted.Figure 17. Optional Connection to AOUT for a Call Progress Speaker‘Table 14. Component Values—Optional Connection to AOUTSymbol ValueC12200 pF, 16 V, ±20%C2, C3, C50.1 µF, 16 V, ±20%C4100 µF, 16 V, Elec. ±20%C6820 pF, 16 V, ±20%R1 3 k Ω, 1/10 W, ±5%R210 Ω, 1/10 W, ±5%R347 k Ω, 1/10 W, ±5%U1LM386Si303518Rev. 1.2Functional DescriptionThe Si3035 is an integrated chipset that provides a low-cost, isolated, silicon-based interface to the telephone line. The Si3035 saves cost and board area by eliminating the need for a modem AFE or serial codec. It also eliminates the need for an isolation transformer, relays, opto-isolators, and a 2- to 4-wire hybrid. The Si3035 solution requires only a few low-cost, discrete components to achieve full compliance with FCC Part 68 and JATE out-of-band noise requirements. See Figure 16 on page 15 for a typical application circuit. See the pin-compatible Si3034 or Si3044 data sheets for designs requiring global support.The Si3035 North America/Japan DAA offers a number of new features not supported by the Si3032 device.These include operation from a single 3.3V power supply, JATE (Japan) filter option, finer resolution for both transmit and receive levels on AOUT (call progress output), daisy-chaining for up to eight devices, and an optional IIR filter. Table 15 summarizes the new Si3035features.InitializationWhen the Si3035 is initially powered up, the RESET pin should be asserted. When the RESET pin is deasserted, the registers will have default values. This reset condition guarantees the line-side chip (Si3012) is powered down with no possibility of loading the line (i.e.,off-hook). The following is an example initializationprocedure:1.Program the PLLs with registers 7 to 9 (N1[7:0], M1[7:0],N2[3:0] and M2[3:0]) to the appropriate divider ratios for the supplied MCLK frequency and desired sample rate, as defined in "Clock Generation Subsystem" on page 20.2.Wait until the PLLs are locked. This time is between100µS and 1ms.3.Write an 0x80 into Register 6. This enables the chargepump for the V A pin, powers up the line-side chip (Si3012), and enables the AOUT for call progress monitoring.After this procedure is complete, the Si3035 is ready for ring detection and off-hook.Isolation BarrierThe Si3035 achieves an isolation barrier through a low-cost, high-voltage capacitor in conjunction with Silicon Laboratories’ proprietary ISOcap signal processing techniques. These techniques eliminate any signal degradation due to capacitor mismatches,common mode interference, or noise coupling. As shown in Figure 16 on page 15, the C1, C2, and C4capacitors isolate the Si3021 (DSP-side) from the Si3012 (line-side). All transmit, receive, control, and caller ID data are communicated through this barrier.The ISOcap inter-chip communication is disabled by default. To enable it, the PDL bit in Register 6 must be cleared. No communication between the Si3021 and Si3012 can occur until this bit is cleared. The clock generator must be programmed to an acceptable sample rate prior to clearing the PDL bit.Off-HookThe communication system generates an off-hook command by applying logic 0 to the OFHK pin or writing a logic 1 to bit 0 of control Register 5. The OFHK pin must be enabled by setting bit 1 (OHE) of Register 5.With OFHK at logic 0, the system is in an off-hook state.This state is used to seize the line for incoming/outgoing calls and can also be used for pulse dialing. With OFHK at logic 1, negligible DC current flows through the hookswitch. When a logic 0 is applied to the OFHK pin,the hookswitch transistor pair, Q1 and Q2, turn on. The net effect of the off-hook signal is the application of a termination impedance across TIP and RING and the flow of DC loop current. The termination impedance has both an AC and a DC component.The AC termination impedance is a 604-Ω resistor,which is connected to the TX pin. The DC termination is a 51-Ω resistor, which is connected to the DCT pin.When executing an off-hook sequence, the Si3035requires 1548/Fs seconds to complete the off-hook and provide phone line data on the serial link. This includes the 12/Fs filter group delay. If necessary, for the shortestTable 15. New Si3035 FeaturesCategory Si3032Si3035Daisy-Chaining —Up to 8 DevicesOptional IIR Filter —Yes Receive Gain 0, 6dB 0, 3, 6, 9, 12dB Transmit Attenuation0, –3dB 0, –3, –6 –9,–12dB V A 5V 3.3V* or 5V V D3.3V or 5V3.3V or 5VJATE Support —Yes AOUT Levels (dB)0, mute0, –6, –12, mute*Note: The V A supply is internally generated by an on-chipcharge pump.Si3035Rev. 1.219delay, a higher Fs may be established prior to executing the off-hook, such as an Fs of 10.286 kHz. The delay allows line transients to settle prior to normal use.Ring DetectThe ring signal enters the Si3035 through low value capacitors connected to TIP and RING. RGDT is a clipped, half-wave rectified version of the ringing waveform. See Figure 18 for a timing diagram of the RGDT pin.The integrated ring detect of the Si3035 allows the device to present the ring signal to the DSP , through the serial port, with no additional signaling required. The signal sent to the DSP is a clipped version of the original ring signal. In addition, the Si3035 passes through the caller ID data unaltered.The system can also detect an occurring ring by the status of the RDT bit of Register 5. This bit is a read-only bit that is set when the line-side device detects a ring signal at RNG1 and RNG2. The RDT bit clears when the system either goes off-hook or 4.5 to 9seconds after the last ring is detected.If caller ID is supported in the system, the designer can enable the Si3035 to pass this information to the SDO output. Following the completion of the first ring, the system should set the ONHM bit (Register 5, bit 3). This bit must be cleared at the conclusion of the receipt of the caller ID data and prior to the next ring burst.The Si3021 can support a wake-up-on-ring function using the RGDT signal. Refer to "Power Management"on page 24 for more details .Improved JATE SupportThe HYBD pin connects to a node on the internal hybrid cancellation circuit providing a pin for a balancing capacitor, C12. C23 adds the necessary transmit out-of-band filtering required to meet JATE out-of-band noise specifications. The addition of C23 alters the transmit path frequency response which must be balanced with capacitor C12 to obtain maximum hybrid cancellation.Products using the Si3035 which have been submitted for JATE approval should document a waiver for the JATE DC Termination specification. This specification is met in the Si3034 global DAA device.Digital InterfaceThe Si3035 has two serial interface modes that support most standard modem DSPs. The M0 and M1 mode pins select the interface mode. The key difference between these two serial modes is the operation of the FSYNC signal. Table 16 summarizes the serial mode definitions.Figure 18. Ring Detect TimingTable 16. Serial ModesMode M1 M0Description0 0 0FSYNC frames data1 0 1FSYNC pulse starts data frame2 1 0Slave mode 31 1ReservedSi303520Rev. 1.2The digital interface consists of a single, synchronous serial link which communicates both telephony and control data.In Serial mode 0 or 1, the Si3021 operates as a master,where the master clock (MCLK) is an input, the serial data clock (SCLK) is an output, and the frame sync signal (FSYNC) is an output. The MCLK frequency and the value of the sample rate control registers 7, 8, 9,and 10 determine the sample rate (Fs). The serial port clock, SCLK, runs at 256 bits per frame, where the frame rate is equivalent to the sample rate. Refer to "Clock Generation Subsystem" on page 20 for more details on programming sample rates.The Si3035 transfers 16-bit or 15-bit telephony data in the primary timeslot and 16-bit control data in the secondary timeslot. Figure 19 and Figure 20 show the relative timing of the serial frames. Primary frames occur at the frame rate and are always present. To minimize overhead in the external DSP , secondary frames are present only when requested.Two methods exist for transferring control information in the secondary frame. The default power-up mode uses the LSB of the 16-bit transmit (TX) data word as a flag to request a secondary transfer. In this mode, only 15-bit TX data is transferred, resulting in a loss of SNR but allowing software control of the secondary frames.As an alternative method, the FC pin can serve as a hardware flag for requesting a secondary frame. The external DSP can turn on the 16-bit TX mode by setting the SB bit of Register 1. In the 16-bit TX mode, the hardware FC pin must be used to request secondary transfers.Figure 21 and Figure 22 illustrate the secondary frame read cycle and write cycle, respectively. During a read cycle, the R/W bit is high and the 5-bit address field contains the address of the register to be read. The contents of the 8-bit control register are placed on the SDO signal. During a write cycle, the R/W bit is low and the 5-bit address field contains the address of the register to be written. The 8-bit data to be written immediately follows the address on SDI. Only one register can be read or written during each secondary frame. See "Control Registers" on page 34 for the register addresses and functions.In serial mode 2, the Si3021 operates as a slave device,where the MCLK is an input, the SCLK is a no connect (except for the master device for which it is an output),and the FSYNC is an input. In addition, the RGDT/FSD pin operates as a delayed frame sync (FSD) and the FC/RGDT pin operates as ring detect (RGDT). In this mode, FC operation is not supported. For further details on operating the Si3021 as a slave device, refer to "Multiple Device Support" on page 25.Clock Generation SubsystemThe Si3035 contains an on-chip clock generator. Using a single MCLK input frequency, the Si3035 can generate all the desired standard modem sample rates,as well as the common 11.025 kHz rate for audio playback.The clock generator consists of two PLLs (PLL1 and PLL2) that achieve the desired sample frequencies.Figure 23 on page 22 illustrates the clock generator.。

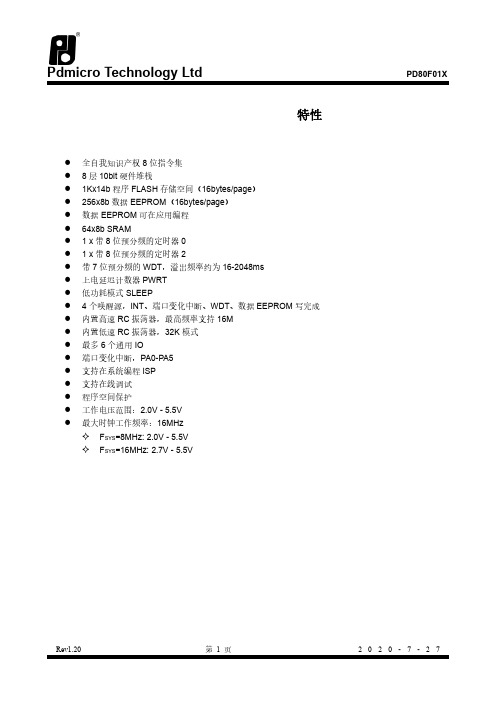

PD80F01x系列_中文资料_数据手册

Rev1.20

第1页

2020-7-27

Pdmicro Technology Ltd

PD80F01X

目录

特性..................................................................................................................................................................................1

2.1. 地址映射................................................................................................................................................................. 9 2.1.1. SFR,BANK0................................................................................................................................................. 9 2.1.2. SFR,BANK1............................................................................................................................................... 10 2.1.3. TMR0,地址 0x01........

DG412DY中文资料

• Widest Dynamic Range • Low Signal Errors and Distortion • Break-Before-Make Switching Action • Simple Interfacing

APPLICATIONS

• Precision Automatic Test Equipment • Precision Data Acquisition • Communication Systems • Battery Powered Systems • Computer Peripherals

Logic "0" ≤ 0.8 V Logic "1" ≥ 2.4 V

DG411 ON OFF

DG413

DG413

Dual-In-Line and SOIC

LCC

IN1 1

D1 IN1 NC IN2 D2

Key

16 IN2

3 2 1 20 19

D1 2 S1 3 V- 4 GND 5 S4 6 D4 7 IN4 8

Switch Off Leakage Current

Symbol VANALOG

rDS(on) IS(off) ID(off)

Channel On Leakage Current

Digital Control Input Current, VIN Low Input Current, VIN High Dynamic Characteristics

To achieve high-voltage ratings and superior switching performance, the DG411 series was built on Vishay Siliconix’s high voltage silicon gate process. An epitaxial layer prevents latchup.

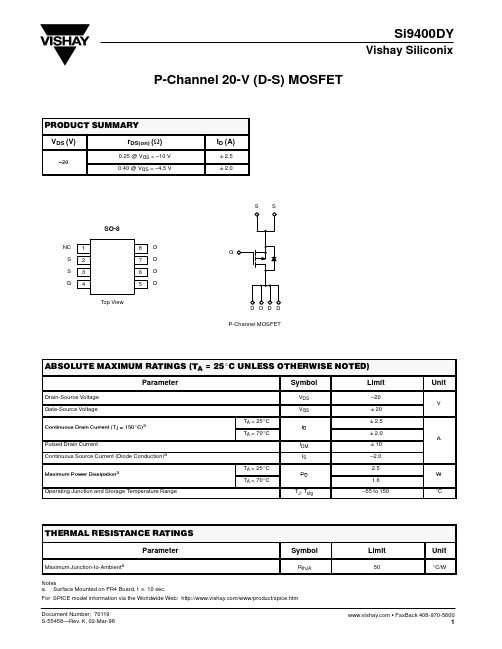

SI9400DY中文资料

80

60 0.0 40 –0.5 20

–1 –50

–25

0

25

50

75

100

125

150

0 0.001 0.01 0.1 1 10

TJ – Temperature (_C)

Normalized Thermal Transient Impedance, Junction-to-Ambient

2 1 Duty Cycle = 0.5 Normalized Effective Transient Thermal Impedance

0 0 2 4 6 8 10

VSD – Source-to-Drain Voltage (V)

VGS – Gate-to-Source Voltage (V)

1.0

Threshold Voltage

100

Single Pulse Power

0.5 V GS(th) Variance (V)

ID = 250 µA

元器件交易网

Si9400DY

Vishay Siliconix

P-Channel 20-V (D-S) MOSFET

PRODUCT SUMMARY

VDS (V)

–20

rDS(on) (W)

0.25 @ VGS = –10 V 0.40 @ VGS = –4.5 V

ID (A)

Symbol

RthJA

Limit

50

Unit

_C/W

1

元器件交易网

Si9400DY

Vishay Siliconix

SPECIFICATIONS (TJ = 25_C UNLESS OTHERWISE NOTED)

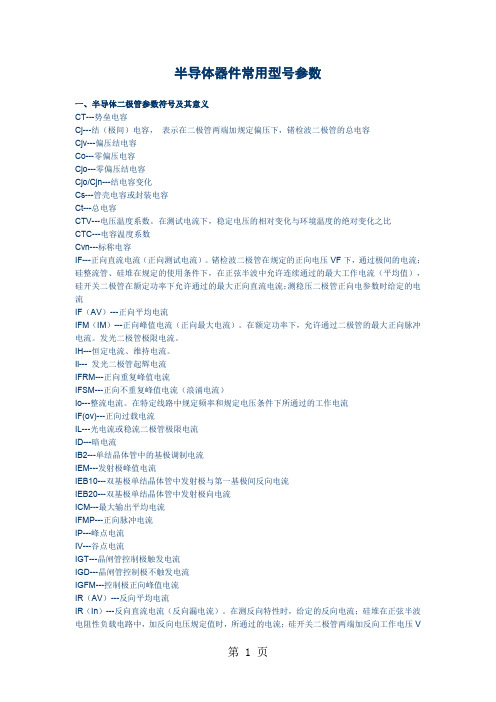

半导体器件芯片常用型号参数12页word文档

半导体器件常用型号参数一、半导体二极管参数符号及其意义CT---势垒电容Cj---结(极间)电容,表示在二极管两端加规定偏压下,锗检波二极管的总电容Cjv---偏压结电容Co---零偏压电容Cjo---零偏压结电容Cjo/Cjn---结电容变化Cs---管壳电容或封装电容Ct---总电容CTV---电压温度系数。

在测试电流下,稳定电压的相对变化与环境温度的绝对变化之比CTC---电容温度系数Cvn---标称电容IF---正向直流电流(正向测试电流)。

锗检波二极管在规定的正向电压VF下,通过极间的电流;硅整流管、硅堆在规定的使用条件下,在正弦半波中允许连续通过的最大工作电流(平均值),硅开关二极管在额定功率下允许通过的最大正向直流电流;测稳压二极管正向电参数时给定的电流IF(AV)---正向平均电流IFM(IM)---正向峰值电流(正向最大电流)。

在额定功率下,允许通过二极管的最大正向脉冲电流。

发光二极管极限电流。

IH---恒定电流、维持电流。

Ii--- 发光二极管起辉电流IFRM---正向重复峰值电流IFSM---正向不重复峰值电流(浪涌电流)Io---整流电流。

在特定线路中规定频率和规定电压条件下所通过的工作电流IF(ov)---正向过载电流IL---光电流或稳流二极管极限电流ID---暗电流IB2---单结晶体管中的基极调制电流IEM---发射极峰值电流IEB10---双基极单结晶体管中发射极与第一基极间反向电流IEB20---双基极单结晶体管中发射极向电流ICM---最大输出平均电流IFMP---正向脉冲电流IP---峰点电流IV---谷点电流IGT---晶闸管控制极触发电流IGD---晶闸管控制极不触发电流IGFM---控制极正向峰值电流IR(AV)---反向平均电流IR(In)---反向直流电流(反向漏电流)。

在测反向特性时,给定的反向电流;硅堆在正弦半波电阻性负载电路中,加反向电压规定值时,所通过的电流;硅开关二极管两端加反向工作电压VR时所通过的电流;稳压二极管在反向电压下,产生的漏电流;整流管在正弦半波最高反向工作电压下的漏电流。

HD44780U中文资料

3

元器件交易网

HD66727

LCD-II Family Comparison

Item Power supply voltage LCD-II (HD44780U) 2.7V to 5.5V HD66702R 5V ± 10% (standard) 2.7 V to 5.5V (low voltage) 3.0V to 8.3V 20 characters × 2 lines HD66710 2.7V to 5.5V HD66712U 2.7V to 5.5V

CGRAM DDRAM SEGRAM Segment signals Common signals Liquid crystal drive waveform Clock source Rf oscillation frequency Liquid crystal voltage booster circuit Liquid crystal drive operational amplifier Bleeder-resistor for liquid crystal drive Liquid crystal contrast adjuster Key scan circuit Extension driver control signal Reset function Horizontal smooth scroll Vertical smooth scroll Number of displayed lines Low power control Bus interface Package

Duty Ratio 1/10

Oscillation Frequency 40 kHz 80 kHz 120 kHz 160 kHz

si2301中文资料

场效应管:场效应晶体管(Field Effect Transistor缩写(FET))简称场效应管。

主要有两种类型:结型场效应管(junction FET—JFET)和金属- 氧化物半导体场效应管(metal-oxide semiconductor FET,简称MOS-FET)。

由多数载流子参与导电,也称为单极型晶体管。

它属于电压控制型半导体器件。

具有输入电阻高(107~1015Ω)、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点,现已成为双极型晶体管和功率晶体管的强大竞争者。

场效应管(FET)是利用控制输入回路的电场效应来控制输出回路电流的一种半导体器件,并以此命名。

由于它仅靠半导体中的多数载流子导电,又称单极型晶体管。

FET 英文为Field Effect Transistor,简写成FET。

SI2301是一种P沟道场效应管。

简介:SI2301是MOS管的一种,属于场效应管。

主要参数:晶体管类型:P沟道MOSFET最大功耗PD :1.25W栅极门限电压VGS :2.5V(典型值)漏源电压VDS :-20V(极限值)漏极电流ID:TA=25°时:-2.3A,TA=70°时:-1.5A通态电阻RDS(on):0.145ohm(典型值)栅极漏电流IGSS:±100nA结温:55℃to+150℃封装:SOT-23(TO-236)替代型号:WT-2301 WTC2301 SMG2301 CES2301 KI2301BDS封装类型:SOT-23P沟MOS晶体管:金属氧化物半导体场效应(MOS)晶体管可分为N沟道与P沟道两大类,P沟道硅MOS场效应晶体管在N型硅衬底上有两个P+区,分别叫做源极和漏极,两极之间不通导,栅极上加有足够的正电压(源极接地)时,栅极下的N型硅表面呈现P型反型层,成为连接源极和漏极的沟道。

改变栅压可以改变沟道中的电子密度,从而改变沟道的电阻。

SI4804

Si4804DY Max Min Typ Max Unit

Symbol

Min

Typ

Dynamic

Total Gate Charge Gate-Source Charge Gate-Drain Charge Gate Resistance Qg Qgs Qgd Rg 0.5 7 2.9 2.5 1.5 2.6 11 13 2 2.7 NS W 20 nC

Specificபைடு நூலகம்tion Comparison

Vishay Siliconix

Si4804BDY vs. Si4804DY

Description: Dual N-Channel, 30-V (D-S) MOSFET Package: SOIC-8 Pin Out: Identical Part Number Replacements: Si4804BDY Replaces Si4804DY Si4804BDY—E3 (Lead Free version) Replaces Si4804DY Si4804BDY-T1 Replaces Si4804DY-T1 Si4804BDY-T1—E3 (Lead Free version) Replaces Si4804DY-T1 Summary of Performance: The Si4804BDY is the replacement for the original Si4804DY; both parts perform identically including limits to the parametric tables below.

Si9110DY-T1中文资料