微电子专业英语词汇

微电子专业英语

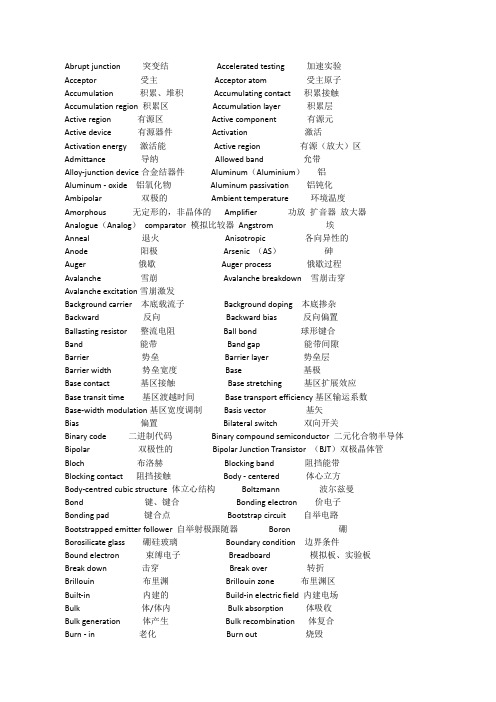

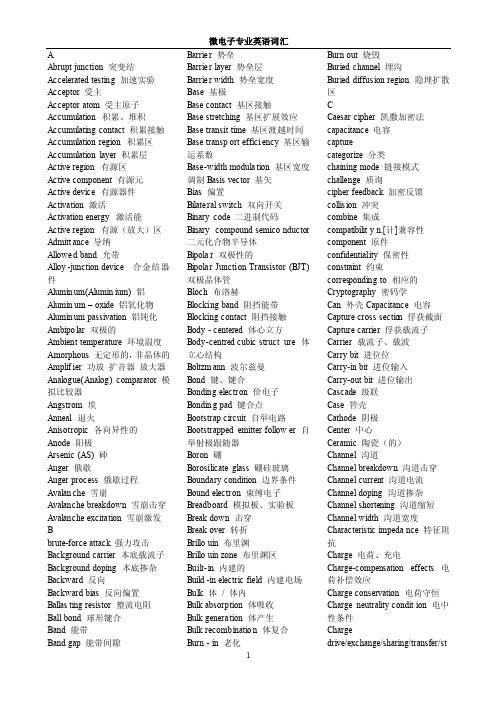

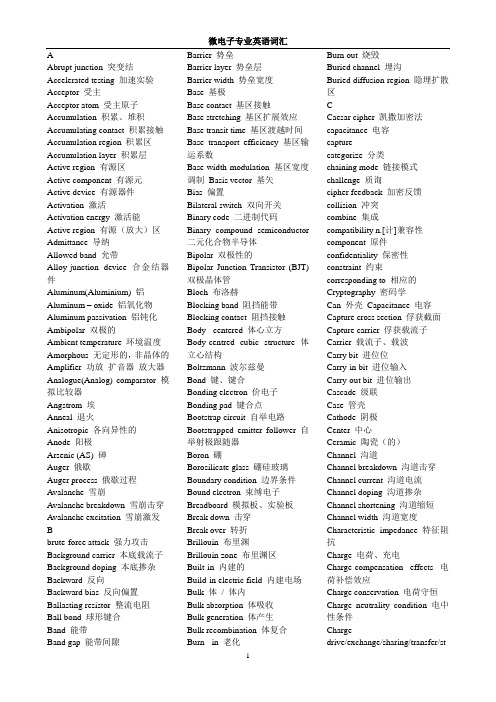

微电子学专业词汇Abe absorb in 集中精力做某事access control list 访问控制表active attack 主动攻击activeX control ActiveX控件advanced encryption standard AES,高级加密标准algorithm 算法alteration of message 改变消息application level attack 应用层攻击argument 变量asymmetric key cryptography 非对称密钥加密attribute certificate属性证书authentication 鉴别authority 机构availability 可用性Abrupt junction 突变结Accelerated testing 加速实验Acceptor 受主Acceptor atom 受主原子Accumulation 积累、堆积Accumulating contact 积累接触Accumulation region 积累区Accumulation layer 积累层Active region 有源区Active component 有源元Active device 有源器件Activation 激活Activation energy 激活能Active region 有源(放大)区Admittance 导纳Allowed band 允带Alloy-junction device 合金结器件Aluminum(Aluminium) 铝Aluminum – oxide 铝氧化物Aluminum passivation 铝钝化Ambipolar 双极的Ambient temperature 环境温度Amorphous 无定形的,非晶体的 Amplifier 功放扩音器放大器Analogue(Analog) comparator 模拟比较器Angstrom 埃Anneal 退火Anisotropic 各向异性的Anode 阳极Arsenic (AS) 砷Auger 俄歇Auger process 俄歇过程Avalanche 雪崩Avalanche breakdown 雪崩击穿Avalanche excitation 雪崩激发Bbrute-force attack 强力攻击Background carrier 本底载流子Background doping 本底掺杂Backward 反向Backward bias 反向偏置Ballasting resistor 整流电阻Ball bond 球形键合Band 能带Band gap 能带间隙Barrier 势垒Barrier layer 势垒层Barrier width 势垒宽度Base 基极Base contact 基区接触Base stretching 基区扩展效应Base transit time 基区渡越时间Base transport efficiency 基区输运系数Base-width modulation 基区宽度调制 Basis vector 基矢Bias 偏置Bilateral switch 双向开关Binary code 二进制代码Binary compound semiconductor 二元化合物半导体Bipolar 双极性的Bipolar Junction Transistor (BJT) 双极晶体管Bloch 布洛赫Blocking band 阻挡能带Blocking contact 阻挡接触Body - centered 体心立方Body-centred cubic structure 体立心结构Boltzmann 波尔兹曼Bond 键、键合Bonding electron 价电子Bonding pad 键合点Bootstrap circuit 自举电路Bootstrapped emitter follower 自举射极跟随器Boron 硼Borosilicate glass 硼硅玻璃Boundary condition 边界条件Bound electron 束缚电子Breadboard 模拟板、实验板Break down 击穿Break over 转折Brillouin 布里渊Brillouin zone 布里渊区Built-in 内建的Build-in electric field 内建电场Bulk 体 / 体内Bulk absorption 体吸收Bulk generation 体产生Bulk recombination 体复合Burn - in 老化Burn out 烧毁Buried channel 埋沟Buried diffusion region 隐埋扩散区CCaesar cipher 凯撒加密法capacitance 电容capturecategorize 分类chaining mode 链接模式challenge 质询cipher feedback 加密反馈collision 冲突combine 集成compatibility n.[计]兼容性component 原件confidentiality 保密性constraint 约束corresponding to 相应的Cryptography 密码学Can 外壳 Capacitance 电容Capture cross section 俘获截面Capture carrier 俘获载流子Carrier 载流子、载波Carry bit 进位位Carry-in bit 进位输入Carry-out bit 进位输出Cascade 级联Case 管壳Cathode 阴极Center 中心Ceramic 陶瓷(的)Channel 沟道Channel breakdown 沟道击穿Channel current 沟道电流Channel doping 沟道掺杂Channel shortening 沟道缩短Channel width 沟道宽度Characteristic impedance 特征阻抗Charge 电荷、充电Charge-compensation effects 电荷补偿效应Charge conservation 电荷守恒Charge neutrality condition 电中性条件Charge drive/exchange/sharing/transfer/storage 电荷驱动 / 交换 / 共享/ 转移 / 存储Chemmical etching 化学腐蚀法Chemically-Polish 化学抛光Chemmically-Mechanically Polish (CMP) 化学机械抛光Chip 芯片Chip yield 芯片成品率Clamped 箝位Clamping diode 箝位二极管Cleavage plane 解理面Clock rate 时钟频率Clock generator 时钟发生器Clock flip-flop 时钟触发器Close-packed structure 密堆积结构Close-loop gain 闭环增益Collector 集电极Collision 碰撞Compensated OP-AMP 补偿运放Common-base/collector/emitter connection 共基极 / 集电极 / 发射极连接Common-gate/drain/source connection 共栅 / 漏 / 源连接Common-mode gain 共模增益Common-mode input 共模输入Common-mode rejection ratio (CMRR) 共模抑制比Compatibility 兼容性Compensation 补偿Compensated impurities 补偿杂质Compensated semiconductor 补偿半导体Complementary Darlington circuit 互补达林顿电路Complementary Metal-Oxide-Semiconductor Field-Effect-Transistor(CMOS) 互补金属氧化物半导体场效应晶体管Complementary error function 余误差函数Compound Semiconductor 化合物半导体 Conductance 电导Conduction band (edge) 导带 ( 底 ) Conduction level/state 导带态Conductor 导体Conductivity 电导率Configuration 组态Conlomb 库仑Conpled Configuration Devices 结构组态 Constants 物理常数Constant energy surface 等能面Constant-source diffusion 恒定源扩散Contact 接触 Contamination 治污Continuity equation 连续性方程Contact hole 接触孔Contact potential 接触电势Continuity condition 连续性条件Contra doping 反掺杂Controlled 受控的Converter 转换器Conveyer 传输器Copper interconnection system 铜互连系统Couping 耦合Covalent 共阶的Crossover 跨交Critical 临界的Crossunder 穿交Crucible 坩埚Crystal defect/face/orientation/lattice 晶体缺陷 / 晶面 / 晶向 / 晶格Current density 电流密度Curvature 曲率Cut off 截止Current drift/dirve/sharing 电流漂移 / 驱动 / 共享Current Sense 电流取样Curvature 弯曲Custom integrated circuit 定制集成电路 Cylindrical 柱面的Czochralshicrystal 直立单晶Czochralski technique 切克劳斯基技术( Cz 法直拉晶体 J )Ddedicate 专用的,单一的denial of service(DOS)拒绝服务攻击diffusion 扩散digital signature algorithm 数字签名算法dynamic 动态的Dangling bonds 悬挂键Dark current 暗电流Dead time 空载时间Debye length 德拜长度De.broglie 德布洛意Decderate 减速Decibel (dB) 分贝Decode 译码Deep acceptor level 深受主能级Deep donor level 深施主能级Deep impurity level 深度杂质能级Deep trap 深陷阱Defeat 缺陷Degenerate semiconductor 简并半导体 Degeneracy 简并度Degradation 退化Degree Celsius(centigrade) /Kelvin 摄氏 / 开氏温度Delay 延迟Density 密度Density of states 态密度Depletion 耗尽Depletion approximation 耗尽近似Depletion contact 耗尽接触Depletion depth 耗尽深度Depletion effect 耗尽效应Depletion layer 耗尽层Depletion MOS 耗尽 MOSDepletion region 耗尽区Deposited film 淀积薄膜Deposition process 淀积工艺Design rules 设计规则Die 芯片(复数 dice )Diode 二极管Dielectric 介电的Dielectric isolation 介质隔离Difference-mode input 差模输入Differential amplifier 差分放大器Differential capacitance 微分电容Diffused junction 扩散结Diffusion 扩散Diffusion coefficient 扩散系数Diffusion constant 扩散常数Diffusivity 扩散率Diffusion capacitance/barrier/current/furnace 扩散电容 / 势垒 / 电流/ 炉Digital circuit 数字电路Dipole domain 偶极畴Dipole layer 偶极层Direct-coupling 直接耦合Direct-gap semiconductor 直接带隙半导体Direct transition 直接跃迁Discharge 放电Discrete component 分立元件Dissipation 耗散Distribution 分布Distributed capacitance 分布电容istributed model 分布模型Displacement 位移Dislocation 位错Domain 畴Donor 施主Donor exhaustion 施主耗尽Dopant 掺杂剂Doped semiconductor 掺杂半导体oping concentration 掺杂浓度Double-diffusive MOS(DMOS) 双扩散 MOS. Drift 漂移Drift field 漂移电场Drift mobility 迁移率Dry etching 干法腐蚀Dry/wet oxidation 干 / 湿法氧化Dose 剂量Duty cycle 工作周期Dual-in-line package ( DIP )双列直插式封装Dynamics 动态Dynamic characteristics 动态属性Dynamic impedance 动态阻抗Eexpertise 专长extractorEarly effect 厄利效应Early failure 早期失效Effective mass 有效质量Einstein relation(ship) 爱因斯坦关系Electric Erase Programmable Read Only Memory(E2PROM) 一次性电可擦除只读存储器Electrode 电极Electrominggratim 电迁移Electron affinity 电子亲和势Electronic -grade 电子能Electron-beam photo-resist exposure 光致抗蚀剂的电子束曝光Electron gas 电子气Electron-grade water 电子级纯水Electron trapping center 电子俘获中心 Electron Volt (eV) 电子伏Electrostatic 静电的Element 元素 / 元件 / 配件Elemental semiconductor 元素半导体 Ellipse 椭圆Ellipsoid 椭球Emitter 发射极Emitter-coupled logic 发射极耦合逻辑 Emitter-coupled pair 发射极耦合对Emitter follower 射随器Empty band 空带Emitter crowding effect 发射极集边(拥挤)效应Endurance test =life test 寿命测试Energy state 能态Energy momentum diagram 能量 - 动量(E-K) 图 Enhancement mode 增强型模式Enhancement MOS 增强性MOS Entefic ( 低 ) 共溶的Environmental test 环境测试Epitaxial 外延的Epitaxial layer 外延层Epitaxial slice 外延片Expitaxy 外延Equivalent curcuit 等效电路Equilibrium majority /minority carriers 平衡多数 / 少数载流子Erasable Programmable ROM (EPROM) 可搽取(编程)存储器Error function complement 余误差函数Etch 刻蚀Etchant 刻蚀剂Etching mask 抗蚀剂掩模Excess carrier 过剩载流子Excitation energy 激发能Excited state 激发态Exciton 激子Extrapolation 外推法Extrinsic 非本征的Extrinsic semiconductor 杂质半导体Ffabrication 伪造fleshed outFace - centered 面心立方Fall time 下降时间Fan-in 扇入Fan-out 扇出Fast recovery 快恢复Fast surface states 快界面态Feedback 反馈Fermi level 费米能级Fermi-Dirac Distribution 费米 - 狄拉克布Femi potential 费米势Fick equation 菲克方程(扩散)Field effect transistor 场效应晶体管Field oxide 场氧化层Filled band 满带Film 薄膜Flash memory 闪烁存储器Flat band 平带Flat pack 扁平封装Flicker noise 闪烁(变)噪声Flip-flop toggle 触发器翻转Floating gate 浮栅Fluoride etch 氟化氢刻蚀Forbidden band 禁带Forward bias 正向偏置Forward blocking /conducting 正向阻断 / 导通Frequency deviation noise 频率漂移噪声Frequency response 频率响应Function 函数GgridGain 增益Gallium-Arsenide(GaAs) 砷化钾Gamy ray r 射线Gate 门、栅、控制极Gate oxide 栅氧化层Gauss ( ian )高斯Gaussian distribution profile 高斯掺杂分布Generation-recombination 产生 - 复合Geometries 几何尺寸Germanium(Ge) 锗Graded 缓变的Graded (gradual) channel 缓变沟道Graded junction 缓变结Grain 晶粒Gradient 梯度Grown junction 生长结Guard ring 保护环Gummel-Poom model 葛谋 - 潘模型Gunn - effect 狄氏效应Hhandle 处理hierarchical 层次Hardened device 辐射加固器件Heat of formation 形成热Heat sink 散热器、热沉Heavy/light hole band 重/轻空穴带Heavy saturation 重掺杂Hell - effect 霍尔效应Heterojunction 异质结Heterojunction structure 异质结结构Heterojunction Bipolar Transistor ( HBT )异质结双极型晶体High field property 高场特性High-performance MOS.( H-MOS) 高性能 MOS.Hormalized 归一化Horizontal epitaxial reactor 卧式外延反应器Hot carrior 热载流子Hybrid integration 混合集成Iimplementinductance 电感initialization vector IV初始化向量integrity完整性interception 截获interruption中断Image - force 镜象力Impact ionization 碰撞电离Impedance 阻抗Imperfect structure 不完整结构Implantation dose 注入剂量Implanted ion 注入离子Impurity 杂质Impurity scattering 杂志散射Incremental resistance 电阻增量(微分电阻)In-contact mask 接触式掩模Indium tin oxide (ITO) 铟锡氧化物 Induced channel 感应沟道Infrared 红外的Injection 注入Input offset voltage 输入失调电压Insulator 绝缘体Insulated Gate FET(IGFET) 绝缘栅FET Integrated injection logic 集成注入逻辑Integration 集成、积分Interconnection 互连Interconnection time delay 互连延时Interdigitated structure 交互式结构Interface 界面Interference 干涉International system of unions 国际单位制Internally scattering 谷间散射Interpolation 内插法Intrinsic 本征的Intrinsic semiconductor 本征半导体 Inverse operation 反向工作Inversion 反型Inverter 倒相器Ion 离子Ion beam 离子束Ion etching 离子刻蚀Ion implantation 离子注入Ionization 电离Ionization energy 电离能Irradiation 辐照Isolation land 隔离岛Isotropic 各向同性Jjava applet Java小程序Junction FET(JFET) 结型场效应管Junction isolation 结隔离Junction spacing 结间距Junction side-wall 结侧壁Kkey wrapping 密钥包装LLatch up 闭锁Lateral 横向的Lattice 晶格Layout 版图Lattice binding/cell/constant/defect/distortion 晶格结合力 / 晶胞 / 晶格 / 晶格常熟 / 晶格缺陷 / 晶格畸变Leakage current (泄)漏电流Level shifting 电平移动Life time 寿命linearity 线性度Linked bond 共价键Liquid Nitrogen 液氮Liquid - phase epitaxial growth technique 液相外延生长技术Lithography 光刻Light Emitting Diode(LED) 发光二极管Load line or Variable 负载线Locating and Wiring 布局布线Longitudinal 纵向的Logic swing 逻辑摆幅Lorentz 洛沦兹Lumped model 集总模型Mmasquerade伪装message digest 消息摘要modification 修改multidrop 多站, 多支路Majority carrier 多数载流子Mask 掩膜板,光刻板Mask level 掩模序号Mask set 掩模组Mass - action law 质量守恒定律Master-slave D flip-flop 主从 D 触发器Matching 匹配Maxwell 麦克斯韦Mean free path 平均自由程Meandered emitter junction 梳状发射极结Mean time before failure (MTBF) 平均工作时间Megeto - resistance 磁阻Mesa 台面MESFET-Metal Semiconductor 金属半导体 FETMetallization 金属化Microelectronic technique 微电子技术Microelectronics 微电子学Millen indices 密勒指数Minority carrier 少数载流子Misfit 失配Mismatching 失配Mobile ions 可动离子Mobility 迁移率Module 模块Modulate 调制Molecular crystal 分子晶体Monolithic IC 单片 ICMOSFET 金属氧化物半导体场效应晶体管Mos. Transistor(MOST )MOS. 晶体管 Multiplication 倍增Modulator 调制Multi-chip IC 多芯片 ICMulti-chip module(MCM) 多芯片模块 Multiplication coefficient 倍增因子Nnetwork level attack网络层攻击non-repudiation 不可抵赖Naked chip 未封装的芯片(裸片)Negative feedback 负反馈Negative resistance 负阻Nesting 套刻Negative-temperature-coefficient 负温度系数Noise margin 噪声容限Nonequilibrium 非平衡Nonrolatile 非挥发(易失)性Normally off/on 常闭/ 开Numerical analysis 数值分析Ooptimize 使最优化Occupied band 满带Officienay 功率Offset 偏移、失调On standby 待命状态Ohmic contact 欧姆接触Open circuit 开路Operating point 工作点Operating bias 工作偏置Operational amplifier (OPAMP) 运算放大器Optical photon =photon 光子Optical quenching 光猝灭Optical transition 光跃迁Optical-coupled isolator 光耦合隔离器Organic semiconductor 有机半导体Orientation 晶向、定向Outline 外形Out-of-contact mask 非接触式掩模Output characteristic 输出特性Output voltage swing 输出电压摆幅Overcompensation 过补偿Over-current protection 过流保护Over shoot 过冲Over-voltage protection 过压保护Overlap 交迭Overload 过载Oscillator 振荡器Oxide 氧化物Oxidation 氧化Oxide passivation 氧化层钝化Pparallelparasitic 寄生的partition [简明英汉词典]n.分割, 划分, 瓜分, 分开, 隔离物vt.区分, 隔开, 分割presentation n.介绍, 陈述, 赠送, 表达primitiveprivateprobablyproceedingprofoundpropertypseudocollision伪冲突Package 封装Pad 压焊点Parameter 参数Parasitic effect 寄生效应Parasitic oscillation 寄生振荡Passination 钝化Passive component 无源元件Passive device 无源器件Passive surface 钝化界面Parasitic transistor 寄生晶体管Peak-point voltage 峰点电压Peak voltage 峰值电压Permanent-storage circuit 永久存储电路Period 周期Periodic table 周期表Permeable - base 可渗透基区Phase-lock loop 锁相环Phase drift 相移Phonon spectra 声子谱Photo conduction 光电导Photo diode 光电二极管Photoelectric cell 光电池Photoelectric effect 光电效应Photoenic devices 光子器件Photolithographic process 光刻工艺(photo) resist (光敏)抗腐蚀剂Pin 管脚Pinch off 夹断Pinning of Fermi level 费米能级的钉扎(效应)Planar process 平面工艺Planar transistor 平面晶体管Plasma 等离子体Plezoelectric effect 压电效应Poisson equation 泊松方程Point contact 点接触Polarity 极性Polycrystal 多晶Polymer semiconductor 聚合物半导体Poly-silicon 多晶硅Potential ( 电 ) 势 Potential barrier 势垒Potential well 势阱Power dissipation 功耗Power transistor 功率晶体管Preamplifier 前置放大器Primary flat 主平面Principal axes 主轴Print-circuit board(PCB) 印制电路板Probability 几率Probe 探针Process 工艺Propagation delay 传输延时Pseudopotential method 膺势发Punch through 穿通Pulse triggering/modulating 脉冲触发 / 调制Pulse Widen Modulator(PWM) 脉冲宽度调制Punchthrough 穿通Push-pull stage 推挽级QQuality factor 品质因子Quantization 量子化Quantum 量子Quantum efficiency 量子效应Quantum mechanics 量子力学Quasi – Fermi - level 准费米能级Quartz 石英Rrelease of message contents发布消息内容register 寄存器registration 注册, 报到, 登记resistance 电阻routingrunning key cipher 运动密钥加密法Radiation conductivity 辐射电导率Radiation damage 辐射损伤Radiation flux density 辐射通量密度Radiation hardening 辐射加固Radiation protection 辐射保护Radiative - recombination 辐照复合Radioactive 放射性Reach through 穿通Reactive sputtering source 反应溅射源Read diode 里德二极管Recombination 复合Recovery diode 恢复二极管Reciprocal lattice 倒核子Recovery time 恢复时间Rectifier 整流器(管)Rectifying contact 整流接触Reference 基准点基准参考点Refractive index 折射率Register 寄存器Registration 对准Regulate 控制调整Relaxation lifetime 驰豫时间Reliability 可*性Resonance 谐振Resistance 电阻Resistor 电阻器Resistivity 电阻率Regulator 稳压管(器)Relaxation 驰豫Resonant frequency 共射频率Response time 响应时间Reverse 反向的Reverse bias 反向偏置Sscratchscratchpad 缓存secret 密钥substrate 衬底synchronizesynthesizesymmetric key cryptography 对称密钥加密sophisticate 复杂的suspend 悬挂,延缓Sampling circuit 取样电路Sapphire 蓝宝石( Al2O3 )Satellite valley 卫星谷Saturated current range 电流饱和区Saturation region 饱和区Saturation 饱和的Scaled down 按比例缩小Scattering 散射Schockley diode 肖克莱二极管Schottky 肖特基Schottky barrier 肖特基势垒Schottky contact 肖特基接触Schrodingen 薛定厄Scribing grid 划片格Secondary flat 次平面Seed crystal 籽晶Segregation 分凝Selectivity 选择性Self aligned 自对准的Self diffusion 自扩散Semiconductor 半导体Semiconductor-controlled rectifier 可控硅Sendsitivity 灵敏度Serial 串行 / 串联Series inductance 串联电感Settle time 建立时间Sheet resistance 薄层电阻Shield 屏蔽Short circuit 短路Shot noise 散粒噪声Shunt 分流Sidewall capacitance 边墙电容Signal 信号Silica glass 石英玻璃Silicon 硅Silicon carbide 碳化硅Silicon dioxide (SiO2) 二氧化硅Silicon Nitride(Si3N4) 氮化硅Silicon On Insulator 绝缘硅Siliver whiskers 银须Simple cubic 简立方Single crystal 单晶Sink 沉Skin effect 趋肤效应Snap time 急变时间Sneak path 潜行通路Sulethreshold 亚阈的Solar battery/cell 太阳能电池Solid circuit 固体电路Solid Solubility 固溶度Sonband 子带Source 源极Source follower 源随器Space charge 空间电荷Specific heat(PT) 热Speed-power product 速度功耗乘积Spherical 球面的Spin 自旋Split 分裂Spontaneous emission 自发发射Spreading resistance 扩展电阻Sputter 溅射Stacking fault 层错Static characteristic 静态特性Stimulated emission 受激发射Stimulated recombination 受激复合Storage time 存储时间Stress 应力Straggle 偏差Sublimation 升华Substrate 衬底Substitutional 替位式的Superlattice 超晶格Supply 电源Surface 表面Surge capacity 浪涌能力Subscript 下标Switching time 开关时间Switch 开关Ttoken 令牌trace 追溯traffic analysis 分析通信量Trojan horse 特洛伊木马Tailing 扩展Terminal 终端Tensor 张量Tensorial 张量的Thermal activation 热激发Thermal conductivity 热导率Thermal equilibrium 热平衡Thermal Oxidation 热氧化Thermal resistance 热阻Thermal sink 热沉Thermal velocity 热运动Thermoelectricpovoer 温差电动势率Thick-film technique 厚膜技术Thin-film hybrid IC 薄膜混合集成电路Thin-Film Transistor(TFT) 薄膜晶体 Threshlod 阈值Thyistor 晶闸管Transconductance 跨导Transfer characteristic 转移特性Transfer electron 转移电子Transfer function 传输函数Transient 瞬态的Transistor aging(stress) 晶体管老化Transit time 渡越时间Transition 跃迁Transition-metal silica 过度金属硅化物Transition probability 跃迁几率Transition region 过渡区Transport 输运Transverse 横向的Trap 陷阱Trapping 俘获Trapped charge 陷阱电荷Triangle generator 三角波发生器Triboelectricity 摩擦电Trigger 触发Trim 调配调整Triple diffusion 三重扩散Truth table 真值表Tolerahce 容差Tunnel(ing) 隧道(穿)Tunnel current 隧道电流Turn over 转折Turn - off time 关断时间UUltraviolet 紫外的Unijunction 单结的Unipolar 单极的Unit cell 原(元)胞Unity-gain frequency 单位增益频率Unilateral-switch 单向开关Vvarietyvectorverify 检验victoryverticalvia 通孔virus 病毒Vacancy 空位Vacuum 真空Valence(value) band 价带Value band edge 价带顶Valence bond 价键Vapour phase 汽相Varactor 变容管Varistor 变阻器Vibration 振动Voltage 电压WWorm 蠕虫Wafer 晶片Wave equation 波动方程Wave guide 波导Wave number 波数Wave-particle duality 波粒二相性Wear-out 烧毁Wire routing 布线Work function 功函数Worst-case device 最坏情况器件YYield 成品率ZZener breakdown 齐纳击穿Zone melting 区熔法。

微电子专业词汇

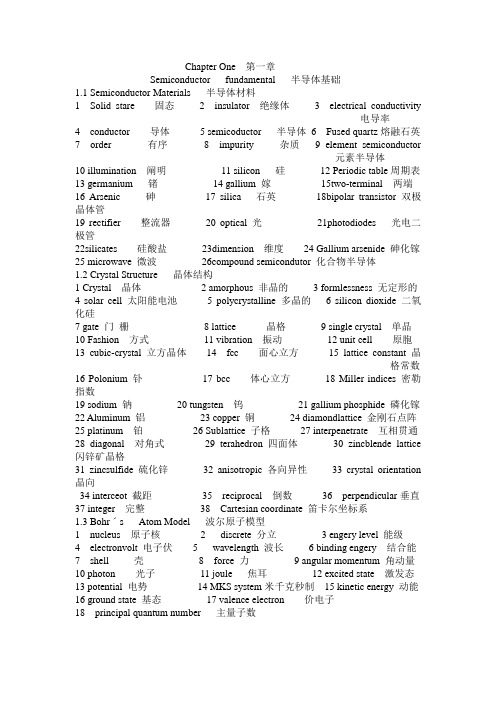

AA Silicon Wafer/Chip Fabrication System 硅晶圆/芯片生产设施FABabrupt junction 突变结absolute zero 绝对零Abs.ZAC current source 交流电源Aacceptor 受主acceptor atom 受主原子access control register 存取控制寄存器ACR access function register 存取操作寄存器AFS access time 存取时间ATaccessory 附件Accaccumulate 累加Accumaccumulation 积累、堆积accumulating register 累加寄存器AR accumulation factor 累加系数AFaccumulator 累加器Aaccumulator and buffer 累加器和缓冲器AB active 有源的,实际的Actactive filter 有源滤波器ACTERactive region 有源区active device 有源器件activation 激活adaptive computer system 自适应计算机系统ACS adaptive control optimization 自适应控制优化ACOAdaptor 转接器,适配器adder 加法器ADDaddress 地址address adder 地址加法器AAdaddress bus 地址总线ABadmittance 导纳allowed band 允带alloy-junction device 合金结器件alternating current 交流电ACaluminum 铝Alaluminum passivation 铝钝化ambient temperature 环境温度amplifier 放大器AMPamplifier detector 放大检波器ADamplifier output 放大器输出AOAmplitude 振幅amplitude frequency modulation 振幅-频率调制AFMamplitude frequency response 振幅频率响应AFR amplitude modualtion/frequency modulation 调幅-调频AM/FMamplitude modulation 调幅,振幅调制AM amplitude modulaton phase modulation 调幅-调相AM/PManalogue/analoganalog feedback 模拟反馈AFanalog function generator 模拟函数发生器AFG analog input module 模拟输入模块AIManalog phase locked loop 模拟锁相环路APLL analog to digital 模拟/数字转换,模数转换A/D analog-digital-analog converter 模-数-模转换器ADACangstrom 埃anneal 退火anisotropic 各向异性anode 阳极antenna 天线Antapplication data structure 应用数据结构ADS application process 应用进程APapplication program interface 应用程序接口API application specific integrated circuit 专用集成电路ASICapplication specific standard products 专用标准产品ASSPapproximate 近似的Apprarithmetic logic unit 数学逻辑单元,运算部件ALUarithmetic register 运算寄存器Ath.Rarray 数组, 阵列array control unit 阵列控制器ACUassembler 汇编器,汇编程序assembly 装配,部件Assy.assembly language 汇编语言ALassembly language program 汇编语言程序APL attenuate 衰减attenuation 衰减attenuation constant 衰减常数attenuator 衰减器audio frequency 音频AFaudio frequency amplifier 音频放大器AFA auger 俄歇avalanche breakdown 雪崩击穿avalanche excitation 雪崩激发auto-answer 自动应答automatic biasing 自偏置automatic gain control 自动增益控制AGCBback bias 反馈偏压back coupling 反馈back current 反向电流back diffusion 反向扩散back feed 反馈BFback injection 反向注入backward forward counter 双向计数器ball bond 球焊band 能带band filter 带通滤波器BFbandgap 带隙band gap energy 带隙band pass 通带band pass filter带通滤波器BPFband width 带宽,频带宽度BWBandwidth 频带宽度BWbandwidth range 带宽范围bang-bangBarkhausen oscillation 巴克豪森振荡barrier capacitance 势垒电容barrier layer 势垒层base circuit 基极电路base contact 基极接触base contact area 基极接触区base control signal 基极控制信号base current drive 基极电流驱动base diffusion capacitance 基区扩散电容base diffusion isolation 基区扩散隔离base distribution 基区分布base electrode 基极base transit time 基区渡越时间Base transport efficiency 基区输运系数base-width modulation 基区宽度调制base emitter saturation voltage 基极-发射极饱和电压base emitter voltage drop 基极-发射极电压降base region 基区base resistance 基区电阻base resistance noise 基区电阻噪声bell 贝尔bias current 偏置电流bias current compensation 偏置电流补偿bibliography 书目,文献目录bidirectional antenna 双向天线bidirectional bus 双向总线bidirectional bus driver 双向总线驱动器bidirectional characteristic 双向特性bidirectional current 双向电流bilateral switch 双向开关binary add 二进制加,二进制加法指令BA binary cell 二进制单元binary code 二进制码binary coded decimal 二-十进制BCD binary coded octal 二-八进制BCObinary decoder 二进制译码器BDbinary-coded address 二进制编码地址binary-coded character 二进制编码符号binary-coded date 二进制编码数据BCD bio chip 生物芯片bio sensor 生物传感器bipolar junction transistor BJTbipolar device 双极型器件bipolar fabrication 双极型器件制造bipolar transistor 双极型晶体管biswitch 双向开关bit 位bbit 比特,二进制的一位bit density 二进制位密度bit error rate 误码率BERbit interleave 位交错bit per second 位/秒BP/Sbit rate 位速率block structure 程序块结构,分程序结构bond 键合bonding 焊接,键合bonding pad 键合区Bonding electron 价电子Boolean algebra 布尔代数,逻辑代数Boolean calculus 布尔演算Boolean character 布尔字符Boolean equation 布尔方程式Boolean factor 布尔因式Boolean format 布尔格式Boolean function 布尔函数Boolean logic 布尔逻辑Boolean operation 布尔运算bootstrapping 自举boron 硼boron diffusion 硼扩散Borosilicate glass 硼硅玻璃bottom-up design 自底向上设计boundary condition 边界条件Bound electron 束缚电子branch controller 支线控制器branch current 支路电流branch voltage 支路电压braze bonding 铜焊breadboard 模拟板break request 中断请求BRbreak request signal 中断请求信号BRS breakdown 击穿breakdown threshold 击穿阈限breakdown voltage 击穿电压Bd.Vbreak-in operation 插入操作bridge 电桥bridge circuit 桥路Brillouin zone 布里渊区broad band 宽带broad band amplifier 宽频放大器buffer 缓冲器Bbuffer amplifier 缓冲放大器BAbuffer B register 缓冲器B寄存器BBReg. buffer channel 缓冲通道buffer element 缓冲单元buffer gate 缓冲门built-in electric field 内建电场built-in field 自建电场built-in test 内部测试BITbuilt-in voltage 内建电压bulk 体bulk absorption 体吸收bulk carrier lifetime 体载流子寿命bulk effect 体效应bulk effect device 体效应器件bulk resistivity 体电阻率bulk resistor 体电阻器buried collector region 隐埋集电区buried diffused region 隐埋扩散区buried layer 隐埋层burn-in 老化burn-out 烧毁burst 猝发,爆发bus circuit 总线电路bus control unit 总线控制器BCUbus driver 总线驱动器bus interface 总线接口bus interface circuit 总线接口电路BICbus interface controller 总线接口控制器BIC bus transceiver 总线收发器bus transfer 总线传送BTrby-product 副产品byte 字节Bbyte address 字节地址byte addressable storage 字节寻址存储器Ccalibrate 校准calling device 呼叫设备CDcan 外壳capacitance 电容,容量CAP capacitance of p-n junction PN结电容capacitance relay 电容式继电器capacitance tolerance 电容公差capacitive coupling 电容耦合capacitive feedback 电容反馈capacitive load 电容负载capacitive reactance 容抗capacitor 电容器,电容CAPcapacity 电容量Capcapture 俘获capture cross section 俘获截面capture carrier 俘获载流子carbon 碳carbon brush 碳刷carrier 载波,媒体,载流子Carrcarrier band 载波频带CBcarrier current 载波电流carrier current communication 载波通信carrier current control 载流控制carrier frequency 载波频率,载频FC,CARR-FREQ carry bit 进位位carry-in bit 进位输入carry-out bit 进位输出carry byte 进位字节CBcartridge 盒式磁带机cascade 级联cascade connection 级联cascade control 级联控制cascaded amplifier 共射共栅放大器cascode stage 共源共栅级cascodes 共源共栅cascode current mirrors 共源共栅电流镜cascode differential pair 共源共栅差分对cascode operational amplifiers 共源共栅运算放大器cathode 阴极cathode emission 阴极放射cathode ray oscillograph 阴极记录仪cell area 单元面积cellular array 单元阵列centigrade temperature scale 摄氏温度刻度central processing unit 中央处理器CPUceramic 陶瓷的ceramic capacitor 陶瓷电容器ceramic dual in-line package 陶瓷双列直插式封装ceramic hybrid IC 陶瓷混合集成电路CHIC ceramic packaging 陶瓷封装channel 通道,信道C 沟道channel breakdown 沟道击穿channel current 沟道电流channel capacity 信道容量chapter 章,段character 字符character check 字符校验character code 字符代码character emitter 字符发生器character encoding 字符编码characteristic bit 特征位characteristic curve 特性曲线characteristic frequency 特性频率characteristic function 特征函数charge 电荷charge conservation 电荷守恒charge neutrality condition电中性条件charge amplifier 电荷放大器charge carrier 载流子charge carrier density 载流子浓度charge transfer 电荷转移charging 充电charging current 充电电流check bit 校验位check character 校验字符check code 校验代码chemical etching 化学腐蚀法chemical polish 化学抛光chemical polishing 化学抛光chemical transport 化学输送chemical vapor deposition 化学汽相淀积CVD chip 芯片chip yield 芯片成品率circuit protection 电路保护circuit reliability 电路可靠性Circuitry 电路,线路,电路图citation 引用citation index 引用索引citizens band 民用波段CBclamp 钳位clamper 钳位电路clamping diode 钳位二极管close-loop gain 闭环增益clock comparator 时钟比较器clock counter 时钟计数器clock frequency 时钟频率clock generator 时钟发生器clock recovery device 时钟恢复器件CRD clock signal 时钟信号clock skew 时钟时滞clockwise 顺时针方向Clkw.Cw.closed loop feedback 闭合环路反馈closed loop gain 闭环增益coaxial 同轴coaxial antenna 同轴天线coaxial cable 同轴电缆coder 编码员,编码器coder/decoder 编码器/译码器CODEXcoefficient 系数coil 线圈collector 集电极Ccollector base bias circuit 集电极-基极偏置电路collector base breakdown voltage 集电极-基极击穿电压collector base current 集电极-基极电流collector base cut-off current 集电极-基极截止电流collector base junction 集电极-基极结collector base voltage 集电极-基极电压collector bias 集电极偏置collector breakdown voltage 集电极击穿电压collector capacitance 集电极电容collector circuit 集电极电路collector contact 集电极接触collector contact area 集电极接触面积collector contact region 集电极接触区collector current 集电极电流collector current density 集电极电流密度collector diffusion resistor 集电区扩散电阻collector electrode 集电极电极collector junction 集电结collector junction current 集电结电流common automatic gain control 普通自动增益控制CAGCcommon base 共基极CBcommon base amplifier 共基极放大器common base circuit 共基极电路common base connection 共基极连接common base current gain 共基极电流增益ccommon base stage 共基极级common battery 共电制COMMON block 公用块common collector 共集电极CCcommon collector amplifier 共集电极放大器common collector stage 共集电极级common data base 公用数据库CDBcommon drain stage 共漏级common drain-common base 共漏-共基极Cd-Cb common emitter 共发射极CEcommon emitter amplifier 共发射极放大器common emitter connection 共发射极连接common emitter current gain 共发射极电流增益common gate connection 共栅极连接common gate stage 共栅极级common mode 共模common mode gain 共模增益common mode input 共模输入common mode input capacitance 共模输入电容common mode input impedance 共模输入阻抗common mode input voltage 共模输入电压common mode rejection 共模抑制common mode rejection ratio 共模抑制比CMRR common mode signal 共模信号common mode voltage gain 共模电压增益common mode voltage range 共模电压范围common source transistor 共源晶体管common substrate 公共衬底communicate 通信,传送Cmct. communication buffer 通信缓冲compaction 压缩comparator 比较器compatibility 兼容性compatible 兼容的,相容的compensated amplifier 补偿放大器compensated operational amplifier 补偿运算放大器compensated OP-AMP补偿运算放大器compensation 补偿,校正Compiler 编译器,编译程序complement 补码complementary logic 互补逻辑complementary logic switch 互补逻辑开关complementary metal oxide semiconductor 互补金属氧化物半导体CMOScomplementary push-pull 互补推挽complex logic 复合逻辑component 元件;部分,组成部分,成分compound semiconductor 化合物半导体concentration 浓度Concn.concentrator 集中器,集线器conductance 电导,导率,电导系数conduction 传导conduction band(edge) 导带(底)conductivity 电导率constant current 恒流,恒流源constant current power supply 恒流电源constant voltage 恒压,恒压源constraint 约束Cryptography 密码学continuous variable 连续变量control block 控制器,控制块control board 控制板CBcontrol bus 控制总线co-processor 协处理器corona 电晕corona discharge 电晕放电corona effect 电晕效应correction 校正correction program 校正程序critical 临界的cross check 交叉校验cross fire 串扰cross talk 串话,串音,串扰,干扰CT cross banding 交叉结合crystal 晶体VTALcrystal diode 晶体二极管cubic 立方Cu.cubic centimeter 立方厘米cm3cubic crystal 立方晶体curie 居里curie temperature 居里温度current 电流Ccurrent amplification 电流放大current amplification factor 电流放大系数current amplifier 电流放大器current density 电流密度CDcurrent feed 电流馈电current gain 电流增益CGcurrent gain 电流增益current limiter 限流器current limiting 限流current logic 电流逻辑current mirror 电流镜current sense 电流取样custom integrated circuit 定制集成电路Ddangling bonds 悬挂键dark current 暗电流data access 数据存取data access protocol 数据存取协仪DAPdata access register 数据存取寄存器DARdata acquisition 数据采集DAdata acquisition and control system 数据采集和控制系统data acquisition equipment 数据采集设备DAE data acquisition system 数据采集系统DASdata acquisition unit 数据采集单元DAUdata adapter unit 数据转接器data array 数据组,数据阵列data base 数据库data base administrator 数据库管理员data block 数据块data break 数据间歇data buffer 数据缓冲器data buffer local storage 数据缓冲局部存储器DBLSdata buffer register 数据缓冲寄存器data buffer unit 数据缓冲器DBUdata bus 数据总线DBdata cell 数据单元DCdata chain 数据链data chaining 数据链接data channel 数据通道DCdata collection and analysis 数据收集和分析data collection station 数据收集站data communication 数据通信data communication buffer 数据通信缓冲器data communication channel 数据通信信道DCC data communication equipment 数据通信设备data control block 数据控制块DCBdata control system 数据控制系统DCSdata converter 数据转换器data counter 数据计数器DCdata definition 数据定义DDdata definition language 数据定义语言DDLdata definition name 数据定义名字data delay 数据延迟data demand 数据请求DDdata description 数据描述data display unit 数字显示器data element 数据元data format 数据格式data frame 数据帧data generator 数据发生器data handling 数据处理data initialization statement 数据初值语句data input 数据输入data input /out interface 数字输入/输出接口DIOI data input bus 数据输入总线DIBdata input/output 数据输入/输出DIOdata input/output register 数据输入/输入寄存器data interface 数据接口data interface format 数据接口格式DIFdata processing 数据处理data processing algorithm 数据处理算法DPA data processing cycle 数据处理流程data telemetry 数据远收装置data terminal 数据终端data transfer rate 数据传送率data transfer register 数据传送寄存器data transfer unit 数据传送器DTUdata transmission 数据传输DTdatum 数据dc breakdown 直流击穿dc coupled 直流耦合dc coupling 直流耦合dc fan-out 直流扇出dc generator 直流发电机dc leakage current 直流漏电流dc load 直流负载dc noise margin 直流噪声容限dc operating point 直流工作点dc overcurrent relay 直流过流继电器debug 调试debugging 调试decibel 分贝DBdecision element 判定元件decoder 解码器,译码器DE,DCDRdecoder driver 译码驱动器decoding 译码,解码decoupling 退耦,去耦decoupling circuit 退耦电路,去耦电路deep acceptor level 深受主能级deep donor level 深施主能级deep submicron 深亚微米defect 缺陷degenerate semiconductor 简并半导体degradation 退化delay circuit 延迟电路delay flip-flop 延迟触发器,D触发器delay line 延迟线delete 删除depletion 耗尽depletion layer 耗尽层depletion region 耗尽区depletion-layer capacitance 耗尽层电容deposited film 淀积薄层deposit 淀积,沉积Dep.diagnosis 诊断diagnostic decision logic table 诊断判定逻辑表DDLTDiagnostic Function Test 诊断式功能测试DFT diagnostic program 诊断程序DPdie 管芯die bonding 管芯键合/粘贴die bond 芯片粘贴wire bond 打焊线dielectric 电介质,绝缘体,非传导性的dielectric absorption 介质吸收dielectric breakdown 介质击穿dielectric breakdown voltage 介质击穿电压dielectric constant 介电常数dielectric isolation 介质隔离difference 差分differential amplifier 差分放大器differential gain 差分增益differential gain control 差分增益控制differential input voltage 差分输入电压differential input voltage range 差分输入电压范围differential nonlinearity 微分非线性DNL differential operational amplifier 差分运算放大器differential output voltage 差分输出电压differentiator 微分器diffused junction 扩散结diffused mesa transistor 扩散台面型晶体管diffused planar transistor 扩散平面型晶体管diffused resistor 扩散电阻diffused transistor 扩散型晶体管diffusion 扩散diffusion barrier 扩散势垒diffusion capacitance 扩散电容diffusion coefficient 扩散系数diffusion process 扩散工艺digit 数字,数位,位digit compression 数字压缩digit delay 数字延迟digit emitter 数字发送器digit logic 数字逻辑digit per second 位/秒DPsdigital 数字的Ddigital adder 数字加法器digital analog function table 数字模拟函数DAFT digital computer 数字计算机digital control 数(字)控(制)digital logic circuit 数字逻辑电路DLCDigital Signal Processong 数字信号处理DSP digital to analog 数模转换D/Adigital to analog converter 数模转换器DAC digital voltmeter 数字电压表DVmdigital/analog converter 数字/模拟转换器diode 二极管Ddirect access 直接访问,直接存取direct coupled 直接耦合的DCdirect coupled logic 直接耦合逻辑DCLdirect current 直流电DCdisc, disk 磁盘discharge 放电discharge breakdown 放电击穿discrete 分立的,离散的,不连续的discrete component 分立元件discrete device 分立器件discrete element 分立元件discrete Fourier transform 离散型傅里叶变换DFT dislocation 位错displacement 位移distortion 失真,曲解,变形,畸变DISTN distortion delay 失真延迟distributed 分布的distributed capacitance 分布电容distributed computer 分布式计算机disturbance 干扰DI water, de-ionized water去离子水donor 施主donor atom 施主原子donor atom density 施主原子浓度donor center 施主中心donor charge 施主电荷dope 掺杂doped dielectric 掺杂电介质doped epitaxial layer 掺杂外延层doped polycrystalline silicon diffusion 掺杂多晶硅扩散doped semiconductor 掺杂半导体doping 掺杂dot matrix 点矩阵drain breakdown voltage 漏击穿电压drain capacitance 漏电容drain region 漏区drift current 漂移电流drift mobility 迁移率dry etching 干法刻蚀dry/wet oxidation 干/湿法氧化dose 剂量dual in-line package 双列直插式封装DIPDual In-Line 双列直插式DILdual-diffused MOS 双扩散金属--氧化物--半导体DMOSdynamic 动态的Dyndynamic characteristics 动态特性dynamic circuit 动态电路dynamic random access memory 动态随机存取存储器DRAMdynamic range 动态范围Eerror detection code 错误检测码EDCerase 擦除ECL microprocessor 发射极耦合逻辑微处理机effective address 有效地址EAeffective gate voltage 有效栅电压effective mass 有效质量electric field 电场electric field intensity 电场强度electric field strength 电场强度electric field vector 电场矢量Electrical/Electronics Engineer 电气/电子工程师EEelectrically erasable programmable read onlymemory 电可擦除可编程只读存储器E2PROM,EEPROMelectrically programmable logic 电可编程逻辑EPL erasable programmable read only memory 电可编程只读存储器EPROMelectricity 电Electrionic Design Automation 电子设计自动化EDAelectromagnetic 电磁的Emelectromagnetic interference 电磁干扰EMI electromagnetic radiation 电磁辐射Electro migration 电迁移electron scanning 电子扫描electron volt 电子伏特eVelectronic computer 电子计算机Electronic Mail 电子邮递E-MailElectronics Industries Association 美国电子工业协会EIAelectro-optical effect 电光效应electrostatic 静电的, 静电学的electrostatic coupling 静电耦合Electrostatic Discharge 静电释放ESD electrostatic shield 静电屏蔽Embedded Array Block 嵌入式阵列区块EAB emitter 发射极Eemitter follower 射极跟随器EFemitter-coupled logic 电流开关逻辑,发射极耦合逻辑ECLencoder 编码器encoder /decoder 编码器/解码器En/Dec encoding 编码enhancement MOS 增强型金属氧化物半导体epi-planar integrated circuit 外延平面集成电路EPICepitaxial 处延的epitaxial deposition 外延淀积epitaxial device 外延器件epitaxial film 外延膜epitaxial growth 外延生长epitaxial growth process 外延生长加工epitaxial growth technology 外延生长技术epitaxial slice 外延片equivalent circuit 等效电路equivalent circuit diagram 等效电路图equivalent differential input resistance 等效差动输入电阻equivalent impedance 等效阻抗equivalent input noise current 等效输入噪声电流equivalent input noise voltage 等效输入噪声电压equivalent input offset current 等效输入补偿电流equivalent noise input 等效噪声输入equivalent noise sideband input 等效噪声边带输入ENSIequivalent resistance 等效电阻equivalent series resistance 等效串联电阻erasability 可擦性erasable memory 可擦存储器EMerror 误差Eerror check and correction 误差检测与校正ECC error correction code 错误校正码ECCerror ratio 误差率etch 蚀刻excess 过剩,剩余Exexcess electron 过剩电子excess electron density 过剩电子浓度excess hole density 过剩空穴浓度excess minority carrier 过剩少数载流子excess minority carrier density 过剩少数载流子浓度excess minority carrier lifetime 过剩少数载流子寿命excess minority electron density 过剩少数电子浓度excess minority hole density 过剩少数空穴浓度excitation 激发excitation energy 激发能excited atom 激发原子exclusive 排除,排斥,唯一的,专有的Exclu exclusive NOR gate 同门exclusive OR gate 异或门XORexponential 指数的Expexponential curve 指数曲线exponential damping 指数阻尼exponential decay 指数衰减exposure 曝光exposure equipment 曝光设备Ffan-in 扇入,扇入端FIfan-out 输出,输出端FOfarad 法拉FFaraday effect 法拉第效应fast Fourier transform 快速傅里叶变换FFT fault 故障fault-tolerant 容错系统fault-tolerant computer 容错计算机fault-tolerant concept 容错概念fault-tolerant software 容错软件fault-tolerant technique 容错技术feedback 反馈Ffeedforward 前馈fermi energy 费米能(量)fermi level 费米能级fermi function 费米函数fermi potential 费米电势fiber optic 光纤维,光纤fiber optic communications 光纤通信fiber optic probe 光纤探头field effect 场效应field -effect capacitor 场效应电容器field -effect device 场效应器件field -effect region 场效应区Field Effect Transistor 场效应管FETfield oxide 场氧化层FIFO memory 先进先出存储FIFO queue 先进先出队列FIFO shift register 先进先出移位寄存器FIFO stack register 先进先出堆栈寄存器FIFO storage 先进先出存储器filter 过滤器finite 有限的finite element method 有限元法fired state 开态Flat band 平带Flat pack 扁平封装Flicker noise 闪烁噪声flip chip 倒装片flip chip bonder 倒装焊接机flip chip bonding 倒装焊接flip-flop 触发器F-Fflip-flop circuit 双稳态电路floating address 浮动地址Floating gate 浮栅flow chart 流程图flow diagram 流程图fluorescence 荧光fluorescent 荧光的fluorescent lamp 荧光灯fluorescent screen 荧光屏Fluoride etch 氟化氢刻蚀forbidden band 禁带Forward bias 正向偏置Forward blocking/conducting 正向阻断/导通format statement 格式语句four probe method 四探针法four-point probe measurement 四探针测量four-quadrant multiplier 四象限乘法器frame 帧frequency divider 分频器FDfrequency doubler 倍频器FDfunction 操作,功能,函数Fn,FUNfunction electronic block 电子功能块FEB functional code 操作码FCGgain 增益Ggain control 增益控制GCgain-bandwidth 增益频宽GBGallium Arsenide 砷化镓GaAsgate 门G 栅gate circuit 门电路GCgate oxidegate leaking current 栅漏电流GLCgateway 网关Gauss(ian) 高斯Gaussian distribution profile 高斯分布general assembly program 通用汇编程序GAP general communications interface 通用通信设备GCIgeneral logic unit 通用逻辑单元GLUgeneral processor 通用处理机GPgenerator 发生器,振荡器Ggeneration-recombination 产生-复合giga 吉(109)Ggigabit 吉位(109)位gigahertz 吉赫千兆赫GHzgraded junction 缓变结gradient 梯度Hhalf add 半加HAhalf subtractor 半减法器HShardware description language 硬件描述语言HDL harmonic 谐波harmonic analysis 谐波分析harmonic component 谐波分量harmonic distortion 谐波失真harmonic interference 谐波干扰heat aging 热老化heat sink 散热器heavily-doped 重掺杂衬底Hell effect 霍尔效应Heterojunction 异质结Heterojunction bipolar transistor 异质结双极晶体管Heterojunction structure异质结结构hormalized 归一化Hertz 赫兹Hzheteroepitaxy 异质外延high pass 高通滤波器HPhigh pass filter 高通滤波器HPFhigh Q 高品质因数high quality 高质量因数HQhole mobility 空穴迁移率host 主机hot carrier 热载流子hybrid 混合的hybrid analog-digital simulation 模拟--数字混合仿真hybrid circuit 混合电路hysteresis 迟滞IIC manufacturing process yield 集成电路制造成品率IC photomasking 集成电路光掩膜id est 即,就是i.e. that is (to say )image converter 图像转换器image data 图像数据image data base 图像数据库immediate access 立即存取immediate access storage 立即访问存储器IAS immediate access store 立即存取存储immediate address 立即地址immediate address instruction 立即地址指令immediate addressing 立即寻址immediate data 立即数据immediate instruction 立即指令implantation equipment 掺杂设备implanted atom 注入原子implanted boron atoms 注入硼原子impurity 杂质impurity absorption 杂质吸收impurity atom 杂质原子impurity density 杂质密度impurity diffusion 杂质扩散increment 增量,递增,加1 Inc.Incremental resistance 电阻增量(微分电阻)indirect address 间接地址indirect addressing 间接寻址IAindirect addressing 间接寻址,间接定址inductance 电感Inductance and Capacitance 电感和电容LC inductive 感应的inductive circuit 电感性电路inductive coupling 电感耦合inductive feedback 电感反馈inductor 电感器Infrared 红外线infrared bonding 红外焊infrared detector 红外探测器infrared emitting diode 发射红外线二极管infrared light 红外线Infrared Light Emitting Diode 红外线发光二极管IRLEDinjection 注入injection efficiency 注入效率Input offset voltage 输入失调电压Institute of Electrical and Electronics Engineers 电气及电子工程师学会IEEEInstitute of Electrical and Mail Standard 电气工程师学会IEEinstruction 指令instruction address 指令地址I Addinstruction address 指令地址instruction address A-register 指令地址A寄存器IAAinstruction address B-register 指令地址B寄存器IABinstruction address register 指令地址寄存器IAR instruction address register 指令地址寄存器insulated 绝缘的Insulated gate FET 绝缘栅FET IGFET insulated-gate bipolar transistor---IGBT绝缘栅双极晶体管integrated amplifier 集成放大器integrated circuit 集成电路ICintegrated injection circuit 集成注入电路integrated injection logic 集成注入逻辑I2L interface 接口,界面interface circuit 接口电路interference 干扰international standard book number 国际标准书号ISBNInternational Standard Serial Number 国际标准序号ISSNinternational standards organization 国际标准化组织ISOInternational system of unions 国际单位制Interrupt 中断INTintellectual property 知识产权IPintrinsic 本征的intrinsic semiconductorinverse operation 反向工作inverse voltage 反向电压inversion layer 反型层inverter 反相器,非门inversion 反型inverting amplifier 倒相放大器ion 离子ion beam 离子束ion etching 离子刻蚀ion implantation 离子注入ion trap 离子陷阱irradiance 辐照度irradiation 辐照isolated 隔离的isolated amplifier 隔离放大器isolation capacitance 隔离电容isolation diffusion 隔离扩散isolation land 隔离岛JJunction FET 结型场效应晶体管JFETsJunction isolation 结隔离junction field effect transistor 结型场效应晶体管JEFTjitterLlarge scale integrated circuit 大规模集成电路LSIC Laser Diode 激光二极管LDlaser scribing 激光划片latch up 闭锁latching circuit 自锁电路latching current 闩锁电流lateral 横向的lattice 点阵、晶格lattice binding 晶格结合力layout 规划,布局LC oscillator 电感电容振荡器least significant bit 最低有效位LSBleakage current (泄)漏电流light amplifier 光放大器lithography 光刻light emitting diode 发光二极管LEDLimiting amplifierLimiterlinear circuit 线性电路linear control 线性控制linear distortion 线性失真linear integrated circuit 线性集成电路LIClinked bond 共价键liquid Nitrogen 液态氮liquid crystal display 液晶显示LCDliquid phase epitaxy 液相外延LPEliquid-phase epitaxial growth technique 液相外延生长技术locating and wiring 布局布线placement and routing 布局布线layoutLogical Unit 逻辑单元LULogic swing 逻辑摆幅loop difference signal 环路差值信号loop feedback signal 环路反馈信号loss angle 损耗角loss factor 损耗因数loss index 损耗指数loss of signal 信号损耗LOSlow band 低频带low noise amplifier 低噪声放大器LNAlow pass filter 低通滤波器LPFLow-Pressure Chemical Vapor Deposition 低压化学气相沉淀LPCVDLow-V oltage Technology 低电压技术LVTMmachine address 机器地址machine address instruction 机器地址指令machine code 机器代码machine code instruction 机器码指令machine language 机器语言macro 宏功能,宏magnetic 磁性的magnetic amplifier 磁放大器magnetic hysteresis 磁滞majority carrier 多数载流子mask 屏蔽,掩膜,掩膜板Mskmaster slave D flip-flop 主从D型触发器master slave flip-flop 主从触发器master slave mode 主从模式master slice 母片Mass-action law 质量守恒定律matrix table 矩阵表maximum peak reverse voltage 最大反向峰值电压maximum peak voltage 最大峰值电压maximum rating 最大额定值mean square 均方MSmean time 平均时间MTmean time to failure 平均无故障时间MTTF medium scale integration 中规模集成电路MSI medium-scale integrated circuit 中规模集成电路MSICmegabit 兆位memory bus 存储器总线MBMetal Oxide Semiconductor Field Effect Transistor 金属氧化半导体场效应管MOS FETmetallic packaging 金属封装metallic rectifier 金属整流器micro 微μmicrocircuit 微电路microcomputer 微型计算机microelectronics 微电子学micron 微米μmmicroprocessing unit 微处理机microprocessor 微处理机,微处理器μP microwave 微波Millen indices 密勒指数millivolt 毫伏millivoltmeter 毫伏表millivolts per meter 毫伏/米milliwatt 毫瓦mWminimum 最小值MINminority carrier 少数载流子minority electron density 少数载流子电子密度mismatching 失配mixer 混频器MIX,MXRMobile ions 可动离子mobility 迁移率modem 调制--解调器modulation 调制MODmodule 组件,模块molecule 分子Molmonolithic IC 单片ICmonobrid circuit 单片混合电路most significant bit 最高有效位MSB multiplication 倍增multi-chip IC 多芯片ICmultiplication coefficient 倍增因子multichip circuit 多片电路multichip integrated circuit 多芯片集成电路Multichip Package 多芯片封装MCPMulti-Chip Unit 多芯片单元MCUmultifinger transistors 叉指晶体管multiplexer 复用器,多路调制器MUX multiplier 乘数,乘法器Mlprmultiply 乘NNaked chip 裸片nanosecond 纳秒nsnarrow band 窄(频)带NBnarrow band channel 窄带信道narrow band filter 窄带滤波器National Academy of Science 国家科学院NAS National Semiconductor 国家半导体,国半companyN-channel metal oxide semiconductor N沟道金属氧化物半导体NMOSnegative feedback负反馈negative-temperature-coefficient 负温度系数nesting 套刻noise 噪声,干扰noise analysis 噪声分析noise margin 噪声容限noise suppression 噪声抑制nonlinear 非线性nonlinear distortion 非线性失真non-return-to-zero 不归零NRZnormally off/on 常闭/开n-type semiconductor N型半导体null 零,无,空行Nyquist 尼奎斯特图Ooccupied band 满带octal 八进制的odd-even check 奇偶校验offset 偏移,失调,补偿offset current 补偿电流offset error 偏离误差offset voltage 补偿电压ohm 欧Ωohmic contact 欧姆接触open loop gain 开环增益Operational Amplifier 运算放大器OPAMP optical 光的,光学的optical photon=photon 光子optical communications 光通信optical coupler 光耦合器optical coupled isolator光耦合隔离器optical fibre 光导纤维optical image processor 光学图像处理学OIP optimization 优化optimum code 最佳代码optoelectronic transistor 光电晶体管optoelectronics 光电子学oscillate 振荡oscillation 振荡oscillator 振荡器OSCoscillogram 波形图oscillograph 示波器overcompensation 过补偿over shoot 过冲overcurrent protection 过电流保护overdamping 过阻尼overdriving 过驱动overflow 溢出,上溢overvoltage 过压Ovoxygen 氧OPpackage 插件,组件Pkgpackaging 封装padparallel 并行的,并联的Parparallel adder 并行加法器parallel addition 并行加法parallel/serial 并行/串行P/Sparameter 参数,参量parasitic capacitance 寄生电容pass-band 通带passivate 使钝化,钝化作用passivation 钝化passive 无源passive device 无源器件,无源元件peak current 峰值电流peripheral 外围的,周围的,外围设备。

微电子专业英语

Abrupt junction 突变结Accelerated testing 加速实验Acceptor 受主Acceptor atom 受主原子Accumulation 积累、堆积Accumulating contact 积累接触Accumulation region 积累区Accumulation layer 积累层Active region 有源区Active component 有源元Active device 有源器件Activation 激活Activation energy 激活能Active region 有源(放大)区Admittance 导纳Allowed band 允带Alloy-junction device合金结器件Aluminum(Aluminium)铝Aluminum - oxide 铝氧化物Aluminum passivation 铝钝化Ambipolar 双极的Ambient temperature 环境温度Amorphous 无定形的,非晶体的Amplifier 功放扩音器放大器Analogue(Analog)comparator 模拟比较器Angstrom 埃Anneal 退火Anisotropic 各向异性的Anode 阳极Arsenic (AS)砷Auger 俄歇Auger process 俄歇过程Avalanche 雪崩Avalanche breakdown 雪崩击穿Avalanche excitation雪崩激发Background carrier 本底载流子Background doping 本底掺杂Backward 反向Backward bias 反向偏置Ballasting resistor 整流电阻Ball bond 球形键合Band 能带Band gap 能带间隙Barrier 势垒Barrier layer 势垒层Barrier width 势垒宽度Base 基极Base contact 基区接触Base stretching 基区扩展效应Base transit time 基区渡越时间Base transport efficiency基区输运系数Base-width modulation基区宽度调制Basis vector 基矢Bias 偏置Bilateral switch 双向开关Binary code 二进制代码Binary compound semiconductor 二元化合物半导体Bipolar 双极性的Bipolar Junction Transistor (BJT)双极晶体管Bloch 布洛赫Blocking band 阻挡能带Blocking contact 阻挡接触Body - centered 体心立方Body-centred cubic structure 体立心结构Boltzmann 波尔兹曼Bond 键、键合Bonding electron 价电子Bonding pad 键合点Bootstrap circuit 自举电路Bootstrapped emitter follower 自举射极跟随器Boron 硼Borosilicate glass 硼硅玻璃Boundary condition 边界条件Bound electron 束缚电子Breadboard 模拟板、实验板Break down 击穿Break over 转折Brillouin 布里渊Brillouin zone 布里渊区Built-in 内建的Build-in electric field 内建电场Bulk 体/体内Bulk absorption 体吸收Bulk generation 体产生Bulk recombination 体复合Burn - in 老化Burn out 烧毁Buried channel 埋沟Buried diffusion region 隐埋扩散区Can 外壳Capacitance 电容Capture cross section 俘获截面Capture carrier 俘获载流子Carrier 载流子、载波Carry bit 进位位Carry-in bit 进位输入Carry-out bit 进位输出Cascade 级联Case 管壳Cathode 阴极Center 中心Ceramic 陶瓷(的)Channel 沟道Channel breakdown 沟道击穿Channel current 沟道电流Channel doping 沟道掺杂Channel shortening 沟道缩短Channel width 沟道宽度Characteristic impedance 特征阻抗Charge 电荷、充电Charge-compensation effects 电荷补偿效应Charge conservation 电荷守恒Charge neutrality condition 电中性条件Charge drive/exchange/sharing/transfer/storage 电荷驱动/交换/共享/转移/存储Chemmical etching 化学腐蚀法Chemically-Polish 化学抛光Chemmically-Mechanically Polish (CMP)化学机械抛光Chip 芯片Chip yield 芯片成品率Clamped 箝位Clamping diode 箝位二极管Cleavage plane 解理面Clock rate 时钟频率Clock generator 时钟发生器Clock flip-flop 时钟触发器Close-packed structure 密堆积结构Close-loop gain 闭环增益Collector 集电极Collision 碰撞Compensated OP-AMP 补偿运放Common-base/collector/emitter connection 共基极/集电极/发射极连接Common-gate/drain/source connection 共栅/漏/源连接Common-mode gain 共模增益Common-mode input 共模输入Common-mode rejection ratio (CMRR)共模抑制比Compatibility 兼容性Compensation 补偿Compensated impurities 补偿杂质Compensated semiconductor 补偿半导体Complementary Darlington circuit 互补达林顿电路Complementary Metal-Oxide-Semiconductor Field-Effect-Transistor(CMOS)互补金属氧化物半导体场效应晶体管Complementary error function 余误差函数Computer-aided design (CAD)/test(CAT)/manufacture(CAM)计算机辅助设计/ 测试/制造Compound Semiconductor 化合物半导体Conductance 电导Conduction band (edge)导带(底)Conduction level/state 导带态Conductor 导体Conductivity 电导率Configuration 组态Conlomb 库仑Conpled Configuration Devices 结构组态Constants 物理常数Constant energy surface 等能面Constant-source diffusion恒定源扩散Contact 接触Contamination 治污Continuity equation 连续性方程Contact hole 接触孔Contact potential 接触电势Continuity condition 连续性条件Contra doping 反掺杂Controlled 受控的Converter 转换器Conveyer 传输器Copper interconnection system 铜互连系统Couping 耦合Covalent 共阶的Crossover 跨交Critical 临界的Crossunder 穿交Crucible坩埚Crystal defect/face/orientation/lattice 晶体缺陷/晶面/晶向/晶格Current density 电流密度Curvature 曲率Cut off 截止Current drift/dirve/sharing 电流漂移/驱动/共享Current Sense 电流取样Curvature 弯曲Custom integrated circuit 定制集成电路Cylindrical 柱面的Czochralshicrystal 直立单晶Czochralski technique 切克劳斯基技术(Cz法直拉晶体J)Dangling bonds 悬挂键Dark current 暗电流Dead time 空载时间Debye length 德拜长度De.broglie 德布洛意Decderate 减速Decibel (dB)分贝Decode 译码Deep acceptor level 深受主能级Deep donor level 深施主能级Deep impurity level 深度杂质能级Deep trap 深陷阱Defeat 缺陷Degenerate semiconductor 简并半导体Degeneracy 简并度Degradation 退化Degree Celsius(centigrade)/Kelvin 摄氏/开氏温度Delay 延迟Density 密度Density of states 态密度Depletion 耗尽Depletion approximation 耗尽近似Depletion contact 耗尽接触Depletion depth 耗尽深度Depletion effect 耗尽效应Depletion layer 耗尽层Depletion MOS 耗尽MOSDepletion region 耗尽区Deposited film 淀积薄膜Deposition process 淀积工艺Design rules 设计规则Die 芯片(复数dice)Diode 二极管Dielectric 介电的Dielectric isolation 介质隔离Difference-mode input 差模输入Differential amplifier 差分放大器Differential capacitance 微分电容Diffused junction 扩散结Diffusion 扩散Diffusion coefficient 扩散系数Diffusion constant 扩散常数Diffusivity 扩散率Diffusion capacitance/barrier/current/furnace 扩散电容/势垒/电流/炉Digital circuit 数字电路Dipole domain 偶极畴Dipole layer 偶极层Direct-coupling 直接耦合Direct-gap semiconductor 直接带隙半导体Direct transition 直接跃迁Discharge 放电Discrete component 分立元件Dissipation 耗散Distribution 分布Distributed capacitance 分布电容Distributed model 分布模型Displacement 位移Dislocation 位错Domain 畴Donor 施主Donor exhaustion 施主耗尽Dopant 掺杂剂Doped semiconductor 掺杂半导体Doping concentration 掺杂浓度Double-diffusive MOS(DMOS)双扩散MOS.Drift 漂移Drift field 漂移电场Drift mobility 迁移率Dry etching 干法腐蚀Dry/wet oxidation 干/湿法氧化Dose 剂量Duty cycle 工作周期Dual-in-line package (DIP)双列直插式封装Dynamics 动态Dynamic characteristics 动态属性Dynamic impedance 动态阻抗Early effect 厄利效应Early failure 早期失效Effective mass 有效质量Einstein relation(ship)爱因斯坦关系Electric Erase Programmable Read Only Memory(E2PROM)一次性电可擦除只读存储器Electrode 电极Electrominggratim 电迁移Electron affinity 电子亲和势Electronic -grade 电子能Electron-beam photo-resist exposure 光致抗蚀剂的电子束曝光Electron gas 电子气Electron-grade water 电子级纯水Electron trapping center 电子俘获中心Electron Volt (eV)电子伏Electrostatic 静电的Element 元素/元件/配件Elemental semiconductor 元素半导体Ellipse 椭圆Ellipsoid 椭球Emitter 发射极Emitter-coupled logic 发射极耦合逻辑Emitter-coupled pair 发射极耦合对Emitter follower 射随器Empty band 空带Emitter crowding effect 发射极集边(拥挤)效应Endurance test =life test 寿命测试Energy state 能态Energy momentum diagram 能量-动量(E-K)图Enhancement mode 增强型模式Enhancement MOS 增强性MOS Entefic (低)共溶的Environmental test 环境测试Epitaxial 外延的Epitaxial layer 外延层Epitaxial slice 外延片Expitaxy 外延Equivalent curcuit 等效电路Equilibrium majority /minority carriers 平衡多数/少数载流子Erasable Programmable ROM (EPROM)可搽取(编程)存储器Error function complement (erfc)余误差函数Etch 刻蚀Etchant 刻蚀剂Etching mask 抗蚀剂掩模Excess carrier 过剩载流子Excitation energy 激发能Excited state 激发态Exciton 激子Extrapolation 外推法Extrinsic 非本征的Extrinsic semiconductor 杂质半导体Face - centered 面心立方Fall time 下降时间Fan-in 扇入Fan-out 扇出Fast recovery 快恢复Fast surface states 快界面态Feedback 反馈Fermi level 费米能级Fermi-Dirac Distribution 费米-狄拉克分布Femi potential 费米势Fick equation 菲克方程(扩散)Field effect transistor 场效应晶体管Field oxide 场氧化层Filled band 满带Film 薄膜Flash memory 闪烁存储器Flat band 平带Flat pack 扁平封装Flicker noise 闪烁(变)噪声Flip-flop toggle 触发器翻转Floating gate 浮栅Fluoride etch 氟化氢刻蚀Forbidden band 禁带Forward bias 正向偏置Forward blocking /conducting正向阻断/导通Frequency deviation noise频率漂移噪声Frequency response 频率响应Function 函数Gain 增益Gallium-Arsenide(GaAs)砷化钾Gamy ray r 射线Gate 门、栅、控制极Gate oxide 栅氧化层Gauss(ian)高斯Gaussian distribution profile 高斯掺杂分布Generation-recombination 产生-复合Geometries 几何尺寸Germanium(Ge)锗Graded 缓变的Graded (gradual)channel 缓变沟道Graded junction 缓变结Grain 晶粒Gradient 梯度Grown junction 生长结Guard ring 保护环Gummel-Poom model 葛谋-潘模型Gunn - effect 狄氏效应Hardened device 辐射加固器件Heat of formation 形成热Heat sink 散热器、热沉Heavy/light hole band 重/轻空穴带Heavy saturation 重掺杂Hell - effect 霍尔效应Heterojunction 异质结Heterojunction structure 异质结结构Heterojunction Bipolar Transistor(HBT)异质结双极型晶体High field property 高场特性High-performance MOS.(H-MOS)高性能MOS. Hormalized 归一化Horizontal epitaxial reactor 卧式外延反应器Hot carrior 热载流子Hybrid integration 混合集成Image - force 镜象力Impact ionization 碰撞电离Impedance 阻抗Imperfect structure 不完整结构Implantation dose 注入剂量Implanted ion 注入离子Impurity 杂质Impurity scattering 杂质散射Incremental resistance 电阻增量(微分电阻)In-contact mask 接触式掩模Indium tin oxide (ITO)铟锡氧化物Induced channel 感应沟道Infrared 红外的Injection 注入Input offset voltage 输入失调电压Insulator 绝缘体Insulated Gate FET(IGFET)绝缘栅FET Integrated injection logic集成注入逻辑Integration 集成、积分Interconnection 互连Interconnection time delay 互连延时Interdigitated structure 交互式结构Interface 界面Interference 干涉International system of unions国际单位制Internally scattering 谷间散射Interpolation 内插法Intrinsic 本征的Intrinsic semiconductor 本征半导体Inverse operation 反向工作Inversion 反型Inverter 倒相器Ion 离子Ion beam 离子束Ion etching 离子刻蚀Ion implantation 离子注入Ionization 电离Ionization energy 电离能Irradiation 辐照Isolation land 隔离岛Isotropic 各向同性Junction FET(JFET)结型场效应管Junction isolation 结隔离Junction spacing 结间距Junction side-wall 结侧壁Latch up 闭锁Lateral 横向的Lattice 晶格Layout 版图Lattice binding/cell/constant/defect/distortion 晶格结合力/晶胞/晶格/晶格常熟/晶格缺陷/晶格畸变Leakage current (泄)漏电流Level shifting 电平移动Life time 寿命linearity 线性度Linked bond 共价键Liquid Nitrogen 液氮Liquid-phase epitaxial growth technique 液相外延生长技术Lithography 光刻Light Emitting Diode(LED)发光二极管Load line or Variable 负载线Locating and Wiring 布局布线Longitudinal 纵向的Logic swing 逻辑摆幅Lorentz 洛沦兹Lumped model 集总模型Majority carrier 多数载流子Mask 掩膜板,光刻板Mask level 掩模序号Mask set 掩模组Mass - action law质量守恒定律Master-slave D flip-flop主从D触发器Matching 匹配Maxwell 麦克斯韦Mean free path 平均自由程Meandered emitter junction梳状发射极结Mean time before failure (MTBF)平均工作时间Megeto - resistance 磁阻Mesa 台面MESFET-Metal Semiconductor金属半导体FETMetallization 金属化Microelectronic technique 微电子技术Microelectronics 微电子学Millen indices 密勒指数Minority carrier 少数载流子Misfit 失配Mismatching 失配Mobile ions 可动离子Mobility 迁移率Module 模块Modulate 调制Molecular crystal分子晶体Monolithic IC 单片IC MOSFET金属氧化物半导体场效应晶体管Mos. Transistor(MOST )MOS. 晶体管Multiplication 倍增Modulator 调制Multi-chip IC 多芯片ICMulti-chip module(MCM)多芯片模块Multiplication coefficient倍增因子Naked chip 未封装的芯片(裸片)Negative feedback 负反馈Negative resistance 负阻Nesting 套刻Negative-temperature-coefficient 负温度系数Noise margin 噪声容限Nonequilibrium 非平衡Nonrolatile 非挥发(易失)性Normally off/on 常闭/开Numerical analysis 数值分析Occupied band 满带Officienay 功率Offset 偏移、失调On standby 待命状态Ohmic contact 欧姆接触Open circuit 开路Operating point 工作点Operating bias 工作偏置Operational amplifier (OPAMP)运算放大器Optical photon =photon 光子Optical quenching光猝灭Optical transition 光跃迁Optical-coupled isolator光耦合隔离器Organic semiconductor有机半导体Orientation 晶向、定向Outline 外形Out-of-contact mask非接触式掩模Output characteristic 输出特性Output voltage swing 输出电压摆幅Overcompensation 过补偿Over-current protection 过流保护Over shoot 过冲Over-voltage protection 过压保护Overlap 交迭Overload 过载Oscillator 振荡器Oxide 氧化物Oxidation 氧化Oxide passivation 氧化层钝化Package 封装Pad 压焊点Parameter 参数Parasitic effect 寄生效应Parasitic oscillation 寄生振荡Passination 钝化Passive component 无源元件Passive device 无源器件Passive surface 钝化界面Parasitic transistor 寄生晶体管Peak-point voltage 峰点电压Peak voltage 峰值电压Permanent-storage circuit 永久存储电路Period 周期Periodic table 周期表Permeable - base 可渗透基区Phase-lock loop 锁相环Phase drift 相移Phonon spectra 声子谱Photo conduction 光电导Photo diode 光电二极管Photoelectric cell 光电池Photoelectric effect 光电效应Photoenic devices 光子器件Photolithographic process 光刻工艺(photo)resist (光敏)抗腐蚀剂Pin 管脚Pinch off 夹断Pinning of Fermi level 费米能级的钉扎(效应)Planar process 平面工艺Planar transistor 平面晶体管Plasma 等离子体Plezoelectric effect 压电效应Poisson equation 泊松方程Point contact 点接触Polarity 极性Polycrystal 多晶Polymer semiconductor聚合物半导体Poly-silicon 多晶硅Potential (电)势Potential barrier 势垒Potential well 势阱Power dissipation 功耗Power transistor 功率晶体管Preamplifier 前置放大器Primary flat 主平面Principal axes 主轴Print-circuit board(PCB)印制电路板Probability 几率Probe 探针Process 工艺Propagation delay 传输延时Pseudopotential method 膺势发Punch through 穿通Pulse triggering/modulating 脉冲触发/调制Pulse Widen Modulator(PWM)脉冲宽度调制punchthrough 穿通Push-pull stage 推挽级Quality factor 品质因子Quantization 量子化Quantum 量子Quantum efficiency量子效应Quantum mechanics 量子力学Quasi - Fermi-level准费米能级Quartz 石英Radiation conductivity 辐射电导率Radiation damage 辐射损伤Radiation flux density 辐射通量密度Radiation hardening 辐射加固Radiation protection 辐射保护Radiative - recombination辐照复合Radioactive 放射性Reach through 穿通Reactive sputtering source 反应溅射源Read diode 里德二极管Recombination 复合Recovery diode 恢复二极管Reciprocal lattice 倒核子Recovery time 恢复时间Rectifier 整流器(管)Rectifying contact 整流接触Reference 基准点基准参考点Refractive index 折射率Register 寄存器Registration 对准Regulate 控制调整Relaxation lifetime 驰豫时间Reliability 可*性Resonance 谐振Resistance 电阻Resistor 电阻器Resistivity 电阻率Regulator 稳压管(器)Relaxation 驰豫Resonant frequency共射频率Response time 响应时间Reverse 反向的Reverse bias 反向偏置Sampling circuit 取样电路Sapphire 蓝宝石(Al2O3)Satellite valley 卫星谷Saturated current range电流饱和区Saturation region 饱和区Saturation 饱和的Scaled down 按比例缩小Scattering 散射Schockley diode 肖克莱二极管Schottky 肖特基Schottky barrier 肖特基势垒Schottky contact 肖特基接触Schrodingen 薛定厄Scribing grid 划片格Secondary flat 次平面Seed crystal 籽晶Segregation 分凝Selectivity 选择性Self aligned 自对准的Self diffusion 自扩散Semiconductor 半导体Semiconductor-controlled rectifier 可控硅Sendsitivity 灵敏度Serial 串行/串联Series inductance 串联电感Settle time 建立时间Sheet resistance 薄层电阻Shield 屏蔽Short circuit 短路Shot noise 散粒噪声Shunt 分流Sidewall capacitance 边墙电容Signal 信号Silica glass 石英玻璃Silicon 硅Silicon carbide 碳化硅Silicon dioxide (SiO2)二氧化硅Silicon Nitride(Si3N4)氮化硅Silicon On Insulator 绝缘硅Siliver whiskers 银须Simple cubic 简立方Single crystal 单晶Sink 沉Skin effect 趋肤效应Snap time 急变时间Sneak path 潜行通路Sulethreshold 亚阈的Solar battery/cell 太阳能电池Solid circuit 固体电路Solid Solubility 固溶度Sonband 子带Source 源极Source follower 源随器Space charge 空间电荷Specific heat(PT)热Speed-power product 速度功耗乘积Spherical 球面的Spin 自旋Split 分裂Spontaneous emission 自发发射Spreading resistance扩展电阻Sputter 溅射Stacking fault 层错Static characteristic 静态特性Stimulated emission 受激发射Stimulated recombination 受激复合Storage time 存储时间Stress 应力Straggle 偏差Sublimation 升华Substrate 衬底Substitutional 替位式的Superlattice 超晶格Supply 电源Surface 表面Surge capacity 浪涌能力Subscript 下标Switching time 开关时间Switch 开关Tailing 扩展Terminal 终端Tensor 张量Tensorial 张量的Thermal activation 热激发Thermal conductivity 热导率Thermal equilibrium 热平衡Thermal Oxidation 热氧化Thermal resistance 热阻Thermal sink 热沉Thermal velocity 热运动Thermoelectricpovoer 温差电动势率Thick-film technique 厚膜技术Thin-film hybrid IC薄膜混合集成电路Thin-Film Transistor(TFT)薄膜晶体Threshlod 阈值Thyistor 晶闸管Transconductance 跨导Transfer characteristic 转移特性Transfer electron 转移电子Transfer function 传输函数Transient 瞬态的Transistor aging(stress)晶体管老化Transit time 渡越时间Transition 跃迁Transition-metal silica 过度金属硅化物Transition probability 跃迁几率Transition region 过渡区Transport 输运Transverse 横向的Trap 陷阱Trapping 俘获Trapped charge 陷阱电荷Triangle generator 三角波发生器Triboelectricity 摩擦电Trigger 触发Trim 调配调整Triple diffusion 三重扩散Truth table 真值表Tolerahce 容差Tunnel(ing)隧道(穿)Tunnel current 隧道电流Turn over 转折Turn - off time 关断时间Ultraviolet 紫外的Unijunction 单结的Unipolar 单极的Unit cell 原(元)胞Unity-gain frequency 单位增益频率Unilateral-switch单向开关Vacancy 空位Vacuum 真空Valence(value)band 价带Value band edge 价带顶Valence bond 价键Vapour phase 汽相Varactor 变容管Varistor 变阻器Vibration 振动Voltage 电压Wafer 晶片Wave equation 波动方程Wave guide 波导Wave number 波数Wave-particle duality 波粒二相性Wear-out 烧毁Wire routing 布线Work function 功函数Worst-case device 最坏情况器件Yield 成品率Zener breakdown 齐纳击穿。

微电子技术专业英语

Aabruptly 立刻abundance 分布量accelerated 加速accommodat接纳,供应adjacent 接近的affinity 倾向alloying 合金align 排列amorphous type不定形amplifier 放大器analog 模拟的anisotropic 各向异性的anncal 退火annihilate 消灭approximate 近似;相符性arbitary 任意的arsenic 砷at rest 静止avalanche 雪崩Bbarrier 势垒base 基极bias 偏压bipolar junction transistor双极性晶体管(BJT)biasing 偏置boron 硼boundary 边界bulk 体积buried layer 埋层Ccapacitance 电容channel 沟道coefficient 系数collision 碰撞collector 集电极compensate 补偿composite 复合的concentration 浓度conductor 导体conduction band 导带conductivity 磁场configuration 结构constant 常数constitute 构成constituent 要素consumption 功耗constant 恒定core 核心corresponding 对应的correspond 相一致covalent band 价带critical 临界crystal 晶体crystal lattice 晶格crystal orientation 晶向cube 立方cubic 立方的current 电流cutoff 节制DDangling bond 悬挂键dashed line 虚线decay 衰减deficiency 缺乏degenerate 简并density 浓度deplete 耗尽depletion region 耗尽层device 器件dielectic constant 介电常数dielectic 绝缘体,电介质diffusion 扩散dimension 量纲diode 二极管discontinuity 中断discrete 离散的displacement 位移distribution 分布donor 施主doping level 掺杂浓度dopant 掺杂剂drain 漏drift 漂移duplicate 复制Eeffective potential energy有效势能electrode 电极electrostatic 静电学的election 电子自旋element semiconductor 元素半导体elevate 提升emitter 发射极epitaxy 外延equidistant 等距的equilibrium 平衡excess 过盛excitation 激发external 外部的extracted 抽取extrapotation 外推extrinic 非本征FFabrication制作finite 限定的figure of merit 品质因子flat band voltage平带电压flexibility 适应性flux 流动fraction 比例forbidden region 禁带forward bia 正向偏压Ggallium 镓gaseous 气态的gate 栅;门germanium 锗generate 生成graded 缓变gradient 梯度Hhomejunction同质节Iillumination 光照impact ionization 碰撞电离implantation 注入impurity 杂质incident ion 射入离子incorporate 合并infinite 无限的influx 流入inherently 本身insulator 绝缘体interaligitated structure 叉指型结构interatomic 原子间的intercept 截距interest 意义interface 界面,接口integration 积分intrinsic 本征inverted 反向inversion layer反型层ionized 电离isolated 孤立的isotropic 各向同性JJoule 焦耳KKinetic 运动的LLateral 侧面的leakage 漏load 负载lowercase 小写的MMacroscopic 宏观的mass 质量magnitude 数值上MBE 分子束外延merit 优点mfinity 无穷大microsopic微观的migration 迁移modulation 调制momentum 要素multiplication 倍增Nnet doping 净掺杂neutral 中性normalized 归一化nucleus 核OOhmis 欧姆的optical 光学orbit 轨道,转orientation 倾向性oscillator 振荡器oscilloscope 示波器overlap 重叠Pparallel resistant 并联电阻parasitic 寄生的parameters 参数peak 峰值permittivity 介电常数perpendicular竖直的penetrate 进入,渗透photoconductivity光电导性photon 光子polysilicon 多晶硅practical 替代predominate 控制probability 几率proportional 比例的profile 分布pn junction PN结pulse 脉冲Qquantum mechanics 量子力学qualitative 定性Rrange 射程ratio 比值rearranging 排列reclaimable 可回收reciprocal 互惠的recombination center 复合中心resistivity 抵抗力response 响应reverse bia 正向偏压Ssaturation 饱和区scatter 散射self-aligned 自对准的semilog 半对数short-circuiting 短路simulation 仿真slope 斜率solid-state 固体材料solubility 溶度source 源space-charge 空间电荷spatial 空间的stationary 固定的step junction 突变节substrate 衬底,基片subthreshold 亚阈值supersede 替代supply 电源switch 开关Tterminal voltage 端电压tern 项tetrahedron 四分体thermal 热量的traverse 横越transit 运输transiston region 过渡区transistor 晶体管transconduction跨导transconductance互导transiet 瞬时的trunnel 遂穿Uuniform 均匀Vvacancy 空缺vaccum 真空valence band 价带valid 有效的vertical 直立的velocity 速率vibration 振动voltage 电压varies exponentially 指数变化Wwell 阱wafer 晶片work function功函数。

半导体、微电子专业英语单词

半导体、微电子专业英语单词半导体、微电子专业英语单词汇总有关半导体、微电子的专业英语单词都有哪些呢?以下是店铺整理的半导体、微电子专业英语单词汇总,欢迎参考!半导体、微电子专业英语单词11. acceptance testing (WAT: wafer acceptance testing)2. acceptor: 受主,如B,掺入Si中需要接受电子3. ACCESS:一个EDA(Engineering Data Analysis)系统4. Acid:酸5. Active device:有源器件,如MOS FET(非线性,可以对信号放大)6. Align mark(key):对位标记7. Alloy:合金8. Aluminum:铝9. Ammonia:氨水10. Ammonium fluoride:NH4F11. Ammonium hydroxide:NH4OH12. Amorphous silicon:α-Si,非晶硅(不是多晶硅)13. Analog:模拟的14. Angstrom:A(1E-10m)埃15. Anisotropic:各向异性(如POLY ETCH)16. AQL(Acceptance Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)17. ARC(Antireflective coating):抗反射层(用于METAL等层的光刻)18. Antimony(Sb)锑19. Argon(Ar)氩20. Arsenic(As)砷21. Arsenic trioxide(As2O3)三氧化二砷22. Arsine(AsH3)23. Asher:去胶机24. Aspect ration:形貌比(ETCH中的深度、宽度比)25. Autodoping:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)26. Back end:后段(CONTACT以后、PCM测试前)27. Baseline:标准流程28. Benchmark:基准29. Bipolar:双极30. Boat:扩散用(石英)舟31. CD: (Critical Dimension)临界(关键)尺寸。

微电子专业英语词汇-推荐下载

Chip 芯片

Chip yield 芯片成品率

Clamped 箝位

Clamping diode 箝位二极管

Cleavage plane 解理面

Clock rate 时钟频率

Clock generator 时钟发生器

Clock flip-flop 时钟触发器

Close-packed structure 密堆积结

偿半导体

Complementary Darlington circuit

互补达林顿电路

Complementary Metal-Oxide-

Semiconductor

Field-Effect-

Transistor(CMOS)

互补金属氧化物半导体场效应

晶体管

Complementary error function 余

误差函数

Compound Semiconductor 化合

物半导体 Conductance 电导

对全部高中资料试卷电气设备,在安装过程中以及安装结束后进行高中资料试卷调整试验;通电检查所有设备高中资料电试力卷保相护互装作置用调与试相技互术通关,1系电过,力管根保线据护敷生高设产中技工资术0艺料不高试仅中卷可资配以料置解试技决卷术吊要是顶求指层,机配对组置电在不气进规设行范备继高进电中行保资空护料载高试与中卷带资问负料题荷试22下卷,高总而中体且资配可料置保试时障卷,各调需类控要管试在路验最习;大题对限到设度位备内。进来在行确管调保路整机敷使组设其高过在中程正资1常料中工试,况卷要下安加与全强过,看2度并22工且22作尽22下可22都能2可地护1以缩关正小于常故管工障路作高高;中中对资资于料料继试试电卷卷保破连护坏接进范管行围口整,处核或理对者高定对中值某资,些料审异试核常卷与高弯校中扁对资度图料固纸试定,卷盒编工位写况置复进.杂行保设自护备动层与处防装理腐置,跨高尤接中其地资要线料避弯试免曲卷错半调误径试高标方中高案资等,料,编5试要写、卷求重电保技要气护术设设装交备备4置底高调、动。中试电作管资高气,线料中课并3敷试资件且、设卷料中拒管技试试调绝路术验卷试动敷中方技作设包案术,技含以来术线及避槽系免、统不管启必架动要等方高多案中项;资方对料式整试,套卷为启突解动然决过停高程机中中。语高因文中此电资,气料电课试力件卷高中电中管气资壁设料薄备试、进卷接行保口调护不试装严工置等作调问并试题且技,进术合行,理过要利关求用运电管行力线高保敷中护设资装技料置术试做。卷到线技准缆术确敷指灵设导活原。。则对对:于于在调差分试动线过保盒程护处中装,高置当中高不资中同料资电试料压卷试回技卷路术调交问试叉题技时,术,作是应为指采调发用试电金人机属员一隔,变板需压进要器行在组隔事在开前发处掌生理握内;图部同纸故一资障线料时槽、,内设需,备要强制进电造行回厂外路家部须出电同具源时高高切中中断资资习料料题试试电卷卷源试切,验除线报从缆告而敷与采设相用完关高毕技中,术资要资料进料试行,卷检并主查且要和了保检解护测现装处场置理设。备高中资料试卷布置情况与有关高中资料试卷电气系统接线等情况,然后根据规范与规程规定,制定设备调试高中资料试卷方案。

微电子专业英语词汇

微电子专业英语词汇 IMB standardization office【IMB 5AB- IMBK 08- IMB 2C】Abrupt junction 突变结['brpt] 突然的;Accelerated testing 加速实验[k'selreitid]Acceptor 受主 Acceptor atom 受主原子['tm] n. 原子Accumulation [,kju:mju'lein]积累,堆积Accumulating contact(n. 接触,联系)积累接触Accumulation region['ri:dn]地区积累区 Accumulation layer['lei] 层积累层Active region 有源区['ktiv]积极的,有源的 Active component [km'punnt]元件有源元Active device 有源器件 Activation 激活Activation energy 激活能 Active region 有源(放大)区Admittance [d'mitns]导纳 Allowed band [b?nd]带允带Alloy-junction device ['l]合金结器件 Aluminum(Aluminium) ['lju:minm]铝Aluminum – oxide ['ksaid]铝氧化物 Aluminum passivation [psi'vein]钝化铝钝化Ambipolar [,mbi'pul]双极的 Ambient temperature ['mbint]环境温度Amorphous ['m:fs]无定形的,非晶体的 Amplifier ['mplifai]功放扩音器放大器Analogue(Analog) ['nlɡ] comparator ['kmpreit]模拟比较器 Angstrom ['strm]埃Anneal ['ni:l]退火 Anisotropic [n,aisu'trpik]各向异性的Anode ['nud]阳极 Arsenic ['ɑ:s?nik (AS) 砷Auger [':ɡ]俄歇 Auger process 俄歇过程Avalanche ['vlɑ:nt]雪崩 Avalanche breakdown(击穿) 雪崩击穿Avalanche excitation [,eksi'tei?n](激发)雪崩激发Background(背景,本底,基底) carrier 本底载流子 Background doping 本底掺杂Backward ['bkwd]反向 Backward bias ['bai?s](偏置,)偏爱反向偏置Ballasting ['blst] resistor 整流电阻 Ball bond [b?nd](结合)球形键合Band 能带 Band gap [ɡ?p](间隙)能带间隙Barrier 势垒 Barrier layer 势垒层Barrier ['bri] width 势垒宽度 Base 基极Base contact 基区接触 Base stretching 基区扩展效应Base transit(运输)time基区渡越时间 Base transport efficiency [i'fi?nsi](效率)基区输运系数Base-width modulation [,mdju'lein(调制)基区宽度调制 Basis vector ['vekt]矢量基矢Bias 偏置 Bilateral [,bai'ltrl] switch 双向开关Binary ['bain?ri]code(代码)二进制代码Binary compound semiconductor二元化合物半导体Bipolar [bai'pul]双极性的 Bipolar Junction Transistor (晶体管)(BJT)双极晶体管Bloch [bl?k]布洛赫 Blocking ['blki](截止,阻塞) band 阻挡能带Blocking contact 阻挡接触 Body(身体,主题) - centered(居中的)体心立方Body-centred cubic ['kju:bik]立方体structure ['strkt]结构体立心结构 Boltzmann 波尔兹曼Bond 键、键合 Bonding electron 价电子Bonding pad 键合点 Bootstrap circuit ['s:kit]电路自举电路Bootstrapped emitter [i'mit]发射器 follower(追随者)自举射极跟随器 Boron ['b:rn]硼Borosilicate [,b:ru'silikit]硼硅酸盐 glass 硼硅玻璃 Boundary condition 边界条件Bound electron 束缚电子 Breadboard 模拟板、实验板Break down 击穿 Break over 转折Brillouin 布里渊 Brillouin zone 布里渊区Built-in 内建的 Build-in electric field 内建电场Bulk [b?lk]体/体内 Bulk absorption 体吸收Bulk generation 体产生 Bulk recombination [,ri:kmbi'nein]体复合Burn - in 老化 Burn out 烧毁Buried ['berid]埋葬的 channel埋沟 Buried diffusion扩散 region 隐埋扩散区Can 外壳 Capacitance[k'p?st()ns]电容Capture俘获 cross section 俘获截面 Capture carrier 俘获载流子Carrier 载流子、载波 Carry bit 进位位Carry-in bit 进位输入 Carry-out bit 进位输出Cascade [k?s'keid]级联,串联级联 Case 管壳Cathode['kθud]阴极 Center 中心Ceramic [si'r?mik]陶瓷(的) Channel['tnl] (频道)沟道Channel breakdown 沟道击穿 Channel current 沟道电流Channel doping 沟道掺杂 Channel shortening 沟道缩短Channel width 沟道宽度 Characteristic impedance[im'pi:d?ns]特征阻抗Charge (控告)电荷,充电 Charge-compensation[,kmpen'sein](补偿) effects 电荷补偿效应Charge conservation(保存,保持) 电荷守恒Charge neutrality[nju'trlt](中性) condition电中性条件Charge drive/exchange/sharing/transfer/storage 电荷驱动/交换/共享/转移/存储Chemmical etching[nju'trlt]化学腐蚀法 Chemically-Polish['pl](磨光)化学抛光Chemmically-Mechanically [m'knkl](机械地)Polish (CMP) 化学机械抛光 Chip 芯片Chip yield(产量)芯片成品率 Clamped 箝位Clamping diode 箝位二极管 Cleavage['klivd] plane(平面)解理面Clock rate(比率)时钟频率 Clock generator 时钟发生器Clock flip-flop(触发器)时钟触发器 Close-packed structure(构造)密堆积结构Close-loop(环) gain(获利,增加)闭环增益 Collector 集电极Collision[k'l()n](冲突)碰撞 Compensated(补偿) OP-AMP 补偿运放Common-base/collector/emitter connection 共基极/集电极/发射极连接Common-gate/drain/source connection 共栅/漏/源连接Common-mode gain 共模增益 Common-mode input 共模输入Common-mode rejection(抑制,拒绝)ratio (CMRR) 共模抑制比Compatibility[km,pt'blt]兼容性 Compensation 补偿Compensated impurities(杂质)补偿杂质 Compensated semiconductor 补偿半导体Complementary(补足的) Darlington circuit(电路,回路)互补达林顿电路Complementary Metal-Oxide-Semiconductor Field-Effect-Transistor(晶体管)(CMOS) 互补金属氧化物半导体场效应晶体管Complementary error function(功能,函数)余误差函数Computer-aided【辅助的】design (CAD)/test(CAT)/manufacture(CAM)Compound['kmpand] Semiconductor 化合物半导体 Conductance[kn'dkt()ns]电导Conduction(传导band (edge) 导带(底) Conduction level/state 导带态Conductor 导体 Conductivity 电导率Configuration(配置)组态 Conlomb['kulm]库仑Conpled Configuration Devices 结构组态 Constants(常量,常数)物理常数Constant energy surface 等能面 Constant-source diffusion(扩散,传播)恒定源扩散Contact(联系,接触)接触 Contamination[kn,tm'nen]玷污Continuity[,knt'njut](连续性)equation(方程式,等式)连续性方程Contact hole孔接触孔Contact potential(潜能,潜在的)接触电势 Continuity condition 连续性条件Contra['kntr]相反 doping 反掺杂 Controlled 受控的Converter[kn'vt](converter转变,转换)转换器 Conveyer[kn've]传输器Copper(铜) interconnection[,ntk'nkn](互联) system 铜互连系统 Couping 耦合Covalent[k'vel()nt](共价的)共阶的 Crossover 跨交Critical (批评的)临界的 Crossunder 穿交Crucible['krusb()l]坩埚Crystal defect缺陷/face/orientation/lattice 晶体缺陷/晶面/晶向/晶格Current density(密度)电流密度 Curvature'kvt曲率Cut off 截止Current drift(漂移)/dirve/sharing电流漂移/驱动/共享Current Sense(感觉,检测)电流取样 Curvature 弯曲Custom(风俗,习惯,定制的integrated circuit 定制集成电路 Cylindrical 柱面的Czochralshicrystal 直立单晶crystal(晶体,单晶)Czochralski technique 切克劳斯基技术(Cz 法直拉晶体 J)Dangling ['d?g()l;bonds 悬挂键 Dark current 暗电流Dead time 空载时间 Debye length 德拜长度德布洛意 Decderate 减速Decibel ['des?bel] (dB) 分贝 Decode 译码Deep acceptor level 深受主能级 Deep donor['dn(捐赠者level 深施主能级Deep impurity(杂质,不存,不洁)level 深度杂质能级 Deep trap 深陷阱Defeat 缺陷Degenerate semiconductor 简并半导体 Degeneracy 简并度Degradation[,degr'de()n]退化 Degree Celsius(centigrade) /Kelvin 摄氏/开氏温度Delay 延迟 Density 密度Density of states 态密度 Depletion 耗尽Depletion approximation 耗尽近似 Depletion contact 耗尽接触Depletion depth 耗尽深度 Depletion effect 耗尽效应Depletion layer 耗尽层 Depletion MOS 耗尽 MOSDepletion region 耗尽区 Deposited film(电影,薄膜) 淀积薄膜Deposition process 淀积工艺 Design rules 设计规则Die 芯片(复数 dice) Diode 二极管Dielectric 介电的 Dielectric isolation(隔离。

微电子专业英语

Diffusion扩散,传播diffusion furnaces扩散炉facility设施设备quartz石英Tube管子,管,真空管diameter直径transformer变压器pipe管子;笛子Valve阀门;阀flowmeter流量计resemble像;很像wafers晶圆profile规范;概要Vent通风口;出口;排放exhaust排气;排放装置etiquette礼仪;礼节chain smoker老烟枪optics光学MIT麻省理工学院align排列;对准mesa transistor台面型晶体管geometry几何学,图形emitter发射者;发射体base基区emulsion感光剂;乳状液masking plate掩模板expose使··曝光mercury lamp汞灯aluminum铝ohmic欧姆的ohmic contanct欧姆接触moderately相当地dope掺杂antimony锑boron硼yield成品率prevail流行;成功;优先tentative试验的;暂时的advertising campaign广告宣传silicon硅portfolio业务量despite尽管diffusion capacitance扩散电容quartz crystal石英晶体tube diode真空二极管Program Overview and File程序概要和文件exhaust valve排气阀exhaust algorithm穷举算法chain break链中断optics design光学设计mesa diffusion台面扩散Geometry Theorem Prover几何学定理证明emitter follower射极跟随器Base Band基带Mercury tank水银槽ohmic resistance 欧姆电阻doped oxide diffusion掺杂氧扩散Yield criteria合格率标准tentative table of equipment 试行设备表silicon MESFET process硅金属半导体场效应晶体管工艺epitaxial(晶体)取向附生的;外延的micrologic显微科学的WESCON(Western Electronic Show and Convention)西部电子展览和会议shift register移位寄存器inverter反相器order of magnitude数量级isolation绝缘;隔离isolation diffusion隔离扩散result in造成warpage热变形;扭曲IC(integrated circuits)集成电路obsolete废弃的,过时的RTL(resistor transistor logic)电阻晶体管逻辑(电路)DTL(diode transistor logic)二极管晶体管逻辑(电路)unilaterally单方地IRE(Institute of Radio Engineers)无线电工程师学会NAND gate与非门discrete分立的discrete component分立元件the crowd大众Revenue收入hide躲藏;隐瞒reliability可靠性vibration振动;颤动vibration test振动测试explosive爆炸的trigger触发;发射capacity容量estimate估计climb on the bandwagon赶时髦cycle time周期overall从头到尾;总的inertial guidance惯性制导flight control飞行控制ground地Texas Instruments德克萨斯(德州)仪器RCA美国无线电公司General Electric通用电气公司Autonetics自动控制学qualification资格;限制;执照shift register latch移位寄存器锁存电路isolation barrier隔离势垒isolation region隔离区isolation masking隔离掩蔽isolation leakage隔离漏流discrete IC分立集成电路revenue bond收益债券revenue tax财政关税hidden field隐式字段reliability statistics可靠性统计vibration noise振动干扰inertial mass惯性质量ground base共基极接地qualification test合格性试验ground circuit接地电路qualification time鉴定时间qualification phase限定相位mulish执拗的unyielding不易弯曲的obstinate顽固的persistent坚持不懈的Utah犹他州Salt Lake City盐湖城solid state固态responsibility责任priority优先权field effect场效应FET场效应晶体管originate from源于doctorate博士学位flip-flop触发器amplifier放大器gate栅oxide氧化物aluminum铝deposit放置,淀积vaccum真空oxidation氧化threshold voltage阈值电压drain漏fabrication制造instability不稳定性pinch-off夹断pinch-off voltage夹断电压alloy合金standby备用的power density功率密度triode三级真空管circuitry电路packing density存储密度patent专利complementary互补的persistent registration持久性定位solid unit固态器件gate region栅区gate oxide thickeness栅氧化层厚度vacuum tube真空管oxidation film氧化膜oxidation mask氧化掩膜threshold control阈值控制alloying reaction熔合反应Standby Power Supply备用电源general perpose通用的operational amplifier运算放大器industry standards工业标准plug-in插入式的overload protection过载保护freedom from没有identical to和··完全不同operational control unit运算控制单元plug and play即插即用latch mode锁存模式overload circuit breaker过载断路器identical operation恒等运算Schottky-clamped肖特基箝位memory-decoding存储译码data routing数据选择propagation delay time传播延迟时间access time存取时间negligible可忽略不计的demultiplexing多路输出选择Schottky Clamped Transistor肖特基箝位晶体管Schottky Barrier肖特基势垒Access Register存取寄存器Power功耗channel通道serial串行ADC模数转换器data-acquisition数据采集Multiplexer多路复用器bandwidth带宽track/hold采样/保持interface接口Ultra极端的single +5V supply +5V单电源analog input模拟输入single-ended单端Differential差分的unipolar/bipolar单极的/双极的TM(trade mark)商标strobe选通Family系列digital signal processor数字信号处理器successive逐次的approximation 逼近的reference基准drift漂移ppm(parts per million)百万分之几buffer缓冲Amplifier放大器gain增益trim微调LSB(least significant bit)最低有效位pin引脚Quantization error量化误差power-down断电power up加电shut down关闭sampling rate抽样率DIP(dual in-line package)双列直插式封装SO package(small outline package)小外形SOP SSOP(shrink-small-outline package)缩小型SOP anti-aliasing filter抗混叠滤波器data sheet数据表capacitor电容float悬空Falling edge下降沿impedance阻抗clock period时钟周期rising edge上升沿Duty cycle占空比circuitry电路flexible可变的microprocessor微处理器block diagram 框图pseudo伪的differential input差分输入comparator比较器equivalent相等的With respect to关于span跨越cycle周期restore恢复binary-weighted capacitor二进制加权电容General Input总输入General Register通用寄存器Analog to Digital Converter模数转换Multiplexer circuit多路转换电路Ultra Large Scale IC超大规模集成电路differential amplifier差动放大器unipolar transistor单极晶体管bipolar COMS双极型互补金属氧化物半导体Digital Clock Pulse数字时钟脉冲Reference Voltage参考电压Gain margin增益裕度quantization noise量化噪声SOJ J型引脚小外形封装TSOP薄小外形封装VSOP甚小外形封装TSSOP薄的缩小型SOP SOT小外形晶体管SOIC小外形集成电路impedance mismatch阻抗失配flexible printed circuit柔性印制电路Ion implantation离子注入molecule分子electric field电场target靶子;目标A wide variety of各种各样的dose剂量substrate基板;衬底crystal structure晶体结构Incidence发生phosphorus磷dope掺杂homogeneity同质性reproducibility可重复性profile剖面concentration浓度relatively比较而言nitride氮化物penetration刺穿;渗透penetration depth穿透深度gradient梯度sequence序列optimization最佳化dopant掺杂property性质restricted to限于domain领域shallow浅的theoretical理论上trajectory轨道distribute分配collision碰撞randomly随机的impact冲击力arsenic砷的crystalline silicon单晶硅dominant支配channel effect沟道效应tail尾巴tendency趋势saturate浸透,饱和conventional通常的tilt倾斜simulation仿真thermal vibration热振动interaction相互作用ion absorption离子吸收ion beam etching离子束蚀刻ion laser离子激光dose of medicine药剂量substrate interconnection衬底互连incidence zone入射区optimization cost优化成本dopant diffusion掺杂剂扩散domain name域名shallow binding浅结合distributed capacitance分布电容collision channel冲突通道randomly distributed data随机分布数据impact strength冲击强度impact response击打响应channeling diode沟道二极管conventional model传统模型thermal conduction热传导Simulation Analysis and Modeling模拟分布与模型化thermal agitation noise热噪声Thermal oxidation热氧化elevate提升angstroms埃inclination低下来ambient环境Room temperature室温oxidation furnace氧化炉diffusion furnace扩散炉cabinet机壳Fuse熔断quartz石英tube管undergo经受;承担heating coil加热线圈Glassware玻璃制品paddles短桨oxidizing agent氧化剂dry oxidation干法氧化Wet oxidation湿法氧化silicon硅silicon dioxide二氧化硅relative density相对密度Parabolic抛物线hamper妨碍empirically经验地halogen卤素flux变化Ambient condition环境条件ambient noise环境噪音ambient temperature环境温度Quartz crystal石英晶体quartz oscillator石英振荡器undergo change历经变化Quartz Crystal Frequencey Oscillator石英晶体频率振荡器undergo examination受到审讯Undergo experience经历undergo surgery接受手术undergo punishment遭受处罚Heating and ventilation供暖和通风heating effect热效应heating time加热时间Silicon chip硅片silicon dioxide layer二氧化硅层relative accuracy相对精度Relative divergence相对偏差relative magnitude相对值parabolic antenna抛物线天线Flux coating焊剂涂敷flux counter磁通计数器flux leakage漏磁Assemble装配packaging封装manufacture制造transform改变semiconductor半导体functional product功能产品end user终端用户electrical connection电连接Transmission传送thermal dissipation热损reliability可靠性innovation革新Architecture 建筑system integration系统集成expansion膨胀wireless无线的Bio-chips生物芯片optoelectronics光电子学scale等级gap间隙diversification多样化MEMS:Micro Electro Mechanical System微电子机械系统slack松弛mechanism混合SIP(system-in-package)系统芯片functional density功能密度printable可印刷的Embedded devices嵌入式器件emerging新兴的regulatory管理的assemble cell装配单元packaging technique组装技术transforming principle转化要素semiconductor junction半导体结transmission band传输频带expansion connector扩展接口System Application Architecture系统应用程序体系wireless terminal无线终端chip addressing芯片寻址gap junction间隙结合gap length间隙长度slack business松弛业务slack variable松弛变量mechanism design机械设计printable character可打印字符emerging technology新兴技术pin assignment引脚分配pin configuration引脚配置category construction类别构造identical equation恒等方程identical entry恒等项fan out扇出perspective view透视图perspective projection透视投影portable terminal 便携式终端stacked graph叠式图stacked interrupt栈式中断minimal automaton最小自动化precision coding精确编码precision instrument精密仪器alignment pattern对准模式alignment requirement校准请求absorption spectrum吸收谱absorption coefficient吸收系数refractive index折射率scattering layer散射层coupling capacitance耦合电容filter condition筛选条件filter factor过滤因子dielectric layer介电层impedance bridge阻抗电桥impedance mismatch阻抗失配integrated passive devices(IPD)集成无源器件exclusive专有地filter过滤器resistive电阻性的inductive电感性的capacitive电容性的capacitor电容器polymer聚合物dielectric电介质impedance阻抗RF-signal射频信号cellular网眼的thin film薄膜mountable可安装的bondable能捆绑的alumina氧化铝filter conditions筛选条件filter plate滤光板dielectric breakdown电介质击穿dielectric constant介电常数dielectric isolation电介质隔离法。

微电子专业英语词汇