ARM7体系结构详细介绍(ppt 112页)

ARM7体系结构详细介绍课件下载(PPT112张)

3.1 ARM简介

各ARM体系结构版本——V5

在V4版本的基础上,对现在指令的定义进行 了必要的修正,对V4版本的体系结构进行了扩展 并并增加了指令,具体如下:

▪改进了ARM/Thumb状态之间的切换效率; ▪E---增强型DSP指令集,包括全部算法操作和16 位乘法操作; ▪J----支持新的JAVA,提供字节代码执行的硬件 和优化软件加速功能。

优化的缓存结构提高了处理器访问低速存储器 的性能;

可在0.18µm, 0.15µm, 0.13µm工艺的硅芯片上实 现

3.1 ARM简介

ARM11

ARM11 MPCore:可综合的多 处理器核,1至4个处理器可配 置;

ARM1136J(F)-S:可配置的数 据和指令Cache,可提供1.9位 的MPEG4编码加速功能; ARM1156T2(F)-S:带集成浮

SecurCor e

SC100:第一个32位安全处理 器;、SC110:在SC100上增 加密钥协处理器;

SC200:带Jazelle技术的高级 安全处理器;

SC210:在SC200上增加密钥 协处理器

SecurCore是专门为智能卡、安全IC提供 的32位安全处理器, 为电子商务、银行、 网络、移动多媒体、公共交通提供安全解 决方案;

3.1 ARM简介

ARM体系结构

ARM体系结构的特点:

▪每条数据处理指令都对算术逻辑单元和移位器控 制,实现了ALU和移位器的最大利用; ▪地址自动增加和减少寻址模式,优化程序循环; ▪多寄存器装载和存储指令实现最大数据吞吐量; ▪所有指令的条件执行实现最快速的代码执行。

3.1 ARM简介

各ARM体系结构版本

公司的特点是只 设计芯片,而不生产。它将技术 授权给世界上许多著名的半导体、 软件和OEM厂商,并提供服务。

ARM7体系结构概述

指令长度:统一长度的指令域,简化指令译码。

周立功单片机

2.1 ARM简介

• ARM体系结构

ARM体系结构的特点,使其非常适用于嵌 入式系统:

低功耗:对于电池供电的设备,功耗无疑是重点; 高代码密度:小的代码量可以减小存储成本; 小面积:芯片内可以集成更多的外设,使系统硬件 更紧凑简洁; 方便的硬件调试技术:降低开发难度和成本。

2.7 内部寄存器

• R14寄存器与异常发生

异常发生时,程序要跳转至异常服务程序,对 返回地址的处理与子程序调用类似,都是由硬件完 成的。区别在于有些异常有一个小常量的偏移。

周立功单片机

程序计数器R15(PC)

寄存器R15为程序计数器(PC),它指 向正在取指的地址。可以认为它是一个通用 寄存器,但是对于它的使用有许多与指令相 关的限制或特殊情况。如果R15使用的方式 超出了这些限制,那么结果将是不可预测的。

周立功单片机

2.2 ARM7TDMI

• 三级流水线

正在执行的指令

正在译码的指令 正在预取的指令

LDR STR SUB . . . ADD R1,R1,#1 R0,AddInstr R0,NextInstr R1,R1,#1

内 核 流 水 线

(1) (2) (3) (4)

源 程 序

周立功单片机

第2章 目录

周立功单片机

第2章 目录

1.简介 2.ARM7TDMI 3.ARM7TDMI的模块和 内部框图 4.体系结构直接支持的 数据类型 5.处理器状态 6.处理器模式 7.内部寄存器 8. 程序状态寄存器 9.异常 10.中断延迟 11.复位 12.存储器及存储器映射 I/O

周立功单片机

第2章-1 ARM7处理器结构

2.1.3 ARM7TDMI功能信号图

ARM7TDMI

07:21

ARM7TDMI处理器的功能信号

26

时钟和定时

MCLK 全局主时钟,所有存储访问和处理器操作

的主时钟。速度可控制分别访问不同速度的外设和 存储器。

nWAIT 为低电平时处理器将其访问时间延长几个

时钟周期,用于访问低速外设,不用时接高电平。

内核 流水线 典型频率(MHz) 总线架构 ARM7 3 80 冯诺伊曼 ARM9 5 150 哈佛 ARM10 6 260 哈佛 ARM11 8 335 哈佛

07:21

17

2.1.2 ARM7TDMI

3 存储器访问

ARM7TDMI处理器使用了冯· 诺依曼(Von Neumann)结构,指令和数据共用一条32位总线。 只有装载、存储和交换指令可以对存储器中的数据 进行访问。 ARM处理器支持下列数据类型: 字节 8位 半字 16位(必须分配为占用两个字节) 字 32位(必须分配为占用4各字节)

ARM公司简介

ARM是Advanced RISC Machines的缩写,它是一家微处 理器行业的知名企业,该企业设 计了大量高性能、廉价、耗能低 的RISC (精简指令集)处理器。

公司的特点是只 设计芯片,而不生产。它将技术 授权给世界上许多著名的半导体、 软件和OEM厂商,并提供服务。

07:21 6

2.1 ARM微处理器结构

2.1.1 简介 2.1.2 ARM7TDMI特点 2.1.3 ARM7TDMI的模 块和内部框图

07:21

10

2.1.2 ARM7TDMI

ARM7TDMI

ARM7TDMI基于ARM体系结构V4版本,是目 前较低端的ARM核。但仍具有广泛的应用,其最 显著的应用为数字移动电话。

ARM7体系结构

支持EmbededICE观察硬件;

支持64位乘法; 支持片上调试; 支持高密度16位的Thumb指令集;

22

2.2 ARM7TDMI

三级流水线

ARM处理器使用流水线来增加处理器指令流的速 度,这样可使几个操作同时进行,并使处理和存储器系 统连续操作,能提供0.9MIPS/MHz的指令执行速度。 ARM7TDMI的流水线分3级,分别为: 取指 译码 执行

译码

执行

处理指令并将结果写回寄存器 识别将要被执行的指令 从存储器装载一条指令

25

2.2 ARM7TDMI

三级流水线结构的指令执行顺序

周期1 周期2 周期3 周期4 周期5 周期6

PC

…… 指令1 指令2 指令3 指令4 …… 程序存储器

26 1

取指 译码 执行

处理器执行一条 指令的三个阶段

取指 译码 执行 取指 译码 执行 取指 译码 执行 在第1个周期,PC指向指令1,此时指令1 进入三级流水线的取指阶段。

嵌入式计算机系统

朱松盛 生物医学工程

第2章 ARM7体系结构

第2章 ARM7体系结构

1.ARM简介 2.ARM7TDMI 3.ARM的模块、内核 和功能框图 4.ARM处理器状态 5.ARM处理器模式

6.ARM内部寄存器 7.当前程序状态寄存器 8.ARM体系的异常、中 断及其向量表 9.ARM体系的存储系统

17

2.1 ARM简介

CortexTM-A8处理器简介

该处理器是ARM公司所开发的基于ARMv7架构的 首款应用级处理器,其特色是运用了可增加代码密度 和加强性能的技术、可支持多媒体以及信号处理能力 的NEONTM技术、以及能够支持Java和其他文字代码语 言的提前和即时编译的Jazelle@RTC技术。 众多先进的技术使其适用于家电以及电子行业等各 种高端的应用领域。

ram课件第3章++arm7体系结构

• 3.3 ARM7TDMI的模块和内核框图

DBGRNG(0) DBGRNG(1) DBGEXT(0) DBGEXT(1) LOCK WRITE SIZE[1:0] PROT[1:0] TRANS[1:0] ADDR[31:0] CPU

EmbeddedICE-RT ºêµ¥Ôª

´ ¨è É Ã Á 2

3.1 ARM简介

• 各ARM体系结构版本

ARM体系结构从最初开发到现在有了巨大的 改进,并仍在完善和发展。为了清楚的表达每个 ARM应用实例所使用的指令集,ARM公司定义了5 种主要的ARM指令集体系结构版本,以版本号 V1~V5表示。

3.1 ARM简介

• 各ARM体系结构版本——V1

该版本的ARM体系结构,只有26位的寻址空 间,没有商业化,其特点为: 基本的数据处理指令(不包括乘法); 字节、字和半字加载/存储指令; 具有分支指令,包括在子程序调用中使用的分 支和链接指令; 在操作系统调用中使用的软件中断指令。

乘法器 桶形移位器 写数据寄存器 32位ALU 指令管线读数据寄存器 Thumb指令译码器

WDATA[31:0]

RDATA[31:0]

ARM7TDMI模块

• 3.3 ARM7TDMI的模块和内核框图

DBGTCKEN CLK

DBGTMS DBGTDI

DBGnTRST

ʱÖÓ

CLKEN nIRQ

ͬ²½µÄ EmbededICE-RT ɨÃèµ÷ÊÔ·ÃÎʶ˿Ú

第3章 目录

1.简介 2.ARM7TDMI 3.ARM7TDMI的模块和 内部框图 4.体系结构直接支持的 数据类型 5.处理器状态 6.处理器模式 7.内部寄存器 8. 程序状态寄存器 9.异常 10.中断延迟 11.复位 12.存储器及存储器映射 I/O 13.寻址方式简介 14.ARM7指令简介 15.协处理器接口 16.调试接口简介 17.ETM接口简介

嵌入式控制系统-第2章-2-ARM7处理器模式及与存储器组织PPT课件

-

21

简介

2.3.2 内部寄存器

在ARM7TDMI处理器内部有37个32位用户可 见的寄存器。其中有31个通用寄存器,6个状态寄 存器。

在不同的工作模式和处理器状态下,程序员可 以访问的寄存器也不尽相同。

-

17

2.3.1 存储器及存储器映射I/O

存储器格式

地址空间的规则:

▪位于地址A的字包含的字字节位于地址A,A+1,A+2和

A+3;

半字

半字

▪位于地址A的半字包含的字节位于地址A和A+1;

▪位于地址A+2的字节半字字包节 含字的节字节字节位于地址A+2和

A+3;

地址A A+1 A+2 A+3

▪位于地址A的字包含的半字位于地址A和A+2;

CHAPTER

2 ARM7体系结构

-

1

上次课内容 ARM微处理器结构

1.ARM简介 2.ARM7TDMI特点 3.ARM7TDMI的模块和

内部框图

-

2

第2章 ARM7体系结构

2.2 ARM处理器状态和模式 2.3 ARM存储器组织

-

3

第2章 ARM7体系结构

2.2 ARM处理器状态和模式 2.3 存储器组织

中中止止 ((aabbtt)) 用 存于 储的支器寄持保虚护存拟器内存,和以/或避免在A异RM常7TD退M出I没件协的处状理器态的不软可靠未定。义指令异常响应时进入此

件仿真

模式

-

10

2.2.2 处理器模式

ARM7体系结构详细介绍

ARM7体系结构详细介绍简介ARM(Advanced RISC Machines)是一种32位的RISC(Reduced Instruction Set Computer)处理器架构,广泛应用于嵌入式系统、智能手机和平板电脑等领域。

ARM7是ARM体系结构中的一代经典产品,采用了精简指令集,具有低功耗、高效能和高性价比等特点。

架构特性处理器核心ARM7处理器核心是一个半导体芯片,包含了用于指令解码、执行、访存等任务的硬件单元。

ARM7采用了5级流水线架构,可以实现超过20万条指令每秒的处理性能。

此外,ARM7支持可选的乘法器、除法器和调试接口,以满足不同的应用需求。

寄存器ARM7提供了一组寄存器来存放指令和数据。

寄存器分为通用寄存器和特殊目的寄存器两种。

通用寄存器包括16个32位的寄存器,用于存储临时数据和计算结果。

特殊目的寄存器包括程序计数器(PC)、堆栈指针(SP)等,用于指导程序执行和管理堆栈。

存储器ARM7的存储器包括内部存储器和外部存储器两部分。

内部存储器分为指令存储器和数据存储器,用于存放程序指令和数据。

外部存储器通常是闪存、RAM等,用于扩展存储容量。

ARM7支持32位的地址总线,可以寻址最多4GB的内存空间。

性能与功耗ARM7采用了先进的CMOS工艺,使得它具有低功耗和高性能的特性。

ARM7的功耗通常在几个毫瓦到几十个毫瓦之间,可以满足嵌入式系统对功耗的严格要求。

同时,ARM7的高性能使得它可以处理复杂的计算任务,例如图像处理、音视频处理等。

调试与开发ARM7支持ARM公司定义的JTAG调试接口,可以通过调试器进行程序的单步调试、断点设置等操作。

此外,ARM7还提供了丰富的开发工具和软件支持,开发者可以使用C语言、汇编语言等进行编程,方便快捷地开发ARM7的应用程序。

应用领域由于ARM7具有低功耗、高效能和高性价比等特点,因此广泛应用于各种嵌入式系统和移动设备。

下面是一些主要的应用领域:嵌入式系统ARM7在嵌入式系统中得到了广泛的应用,例如工业控制、智能家居、汽车电子等领域。

ARM7体系结构专业讲堂PPT课件

3.2 ARM7TDMI

▪ 三级流水线

ARM7TDMI处理器使用流水线来增加处理器指 令流的速度。这样可使几个操作同时进行,并使处 理和存储器系统连续操作,能提供0.9MIPS/MHz的 指令执行速度。

ARM7TDMI的流水线分3级,分别为: 取指 译码 执行

5.处理器状态

14.ARM7指令简介

6.处理器模式

15.协处理器接口

7.内部寄存器

16.调试接口简介

8. 程序状态寄存器

17.ETM接口简介

3.4 体系结构直接支持的数据类型

▪ 体系结构直接支持的数据类型

ARM处理器支持下列数据类型:

字节 8位

1

半字 16位(必须分配为占用两个字节) 1 2

地址寄存器

地址增加器

寄存器组 31*32位寄存器 (6个状态寄存器)

扫描调试 控制

指令译码 和

控制逻辑

乘法器

桶形移位器 32位ALU

写数据寄存器

指令管线读数据寄存器 Thumb指令译码器

WDATA[31:0]

RDATA[31:0]

ARM7TDMI内核框图

CLK CLEN CFGBIGEND nIRQ nFIQ nRESET ABORT LOCK WRITE

LDR R0,=Lable

BX

R0

地址最低位为 0,表示切换 到ARM状态

第3章 目录

1.简介

9.异常

2.ARM7TDMI

10.中断延迟

3.ARM7TDMI的模块和 11.复位

内部框图

12.存储器及存储器映射

4.体系结构直接支持的 I/O

《微机原理与嵌入式系统基础》课件第2章

第 2 章 ARM7 体系结构

ARM7采用ARM v4T结构,分为三级流水线,具有如下 特点:

(1) RISC处理器结构。 (2) 具有嵌入式ICE-RT逻辑,调试开发方便。 (3) 极低的功耗,适合对功耗要求较高的应用,如便携式 产品。 (4) 能够提供0.9 MIPS/MHz的三级流水线结构。 (5) 支持32位的ARM指令集和16位的Thumb指令集。 (6) 直接支持8 bit、16 bit和32 bit数据操作。 (7) 对操作系统的支持广泛,包括WinCE、Linux、Palm OS等。

第 2 章 ARM7 体系结构

在计算机体系结构中,另外一个重要的内容是存储器体系 结构。现在常用的有两种:冯·诺依曼存储器体系结构和哈佛 存储器体系结构。传统的计算机采用冯·诺依曼结构存储体系, 也称为普林斯顿结构,是一种将程序指令存储器和数据存储器 合并在一起编址的存储器结构,其主要特征是:程序和数据共 用一个存储空间,只是安排在不同的地址空间位置;取指和取 数操作使用同一套总线,只是在不同的时间访问不同的目标存 储单元。目前使用冯·诺依曼结构的MPU(微处理器)和MCU(微 控制器)有很多,如Intel 8086、ARM公司的ARM7、MIPS公司 的MIPS处理器等。

第 2 章 ARM7 体系结构

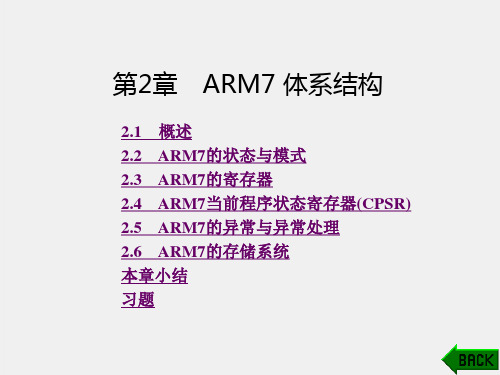

第2章 ARM7 体系结构

2.1 概述 2.2 ARM7的状态与模式 2.3 ARM7的寄存器 2.4 ARM7当前程序状态寄存器(CPSR) 2.5 ARM7的异常与异常处理 2.6 ARM7的存储系统 本章小结 习题

第 2 章 ARM7 体系结构

2.1 概 述

所谓处理器的“体系结构”(或称为“系统结构”),是 处理器的逻辑抽象,是指程序员在使用某处理器编制程序时, 所“看到”从而可以在程序中使用的处理器资源构成、使用方 式、工作原理及其相互间的关系。其中最为重要的就是处理器 所提供的指令系统和寄存器组模型。

chapter2ARM7体系结构

系统

(sys)

用于支持操作系统的特 与用户模式类似,但具有可以

权任务等 这五种模式直称接为切换异到常其它模模式式等。特权

快快中中断断 ((ffiiqq)) 支 道持处它高理们速数除据了传输可及以通通过FIQ程异常序响切应时换进进入此入模外式 ,

中中断断 ((iirrqq)) 用于也通可用中以断由处理特定的异IRQ常异常进响入应时。进当入此特模定式

冯·诺依曼存储器体系结构和哈佛存储器体 系结构

2020/4/11

西安邮电学院 计算机系

page 6

1. RISC处理器

RISC是精简指令集计算机的缩写,其目标是设计出 在高时钟频率下单周期执行,简单而有效的指令集。 RISC处理器具有以下特点: ① 采用LOAD/STORE结构。因为访问存储器指令所需 要的时间比较长,在指令系统中要尽量减少这类指 令,所以RISC指令中只保留不可再少的 LOAD/STORE两种存储器访问指令; ② 硬布线控制逻辑。使得大多数指令在单周期内执行 完成,以减少微程序技术中的指令解释开销; ③ 减少指令和寻址方式的种类。寻址方式简单,指令 系统小; ④ 指令长度固定。

(abt) 用 存于 储可资支 器以源持保虚护使。拟用内存这和个/或模式在A访RM问7TD一M些I没有受大控用处的

(und)

支持硬件协处理器的软 件仿真

未定义指令异常响应时进入此 模式

2020/4/11

西安邮电学院 计算机系

page 19

ARM7处理器约定了进入到5种异常模式的 对应事件:

① 管理模式(svc):复位或执行SWI软中断指 令时,进入该模式。

Power/Power PC 9% MIPS 6%

2020/4/11

arm7简介PPT优秀课件

Target.c文件模块

6

config.h包含一些类型定义和系统时钟定义。 target.h包含一些特殊定义和开/关IRQ中断、 FIQ中断的声明。

分散加载机制: mem_a.scf适用于片内FLASH发布,对应于生成 目标RelInFLASH,LPC2131的mem_c.scf和 mem_a.scf相同。 mem_c.scf适用于片内FLASH 调试。 mem_b.scf适用于片内RAM调试,对应于生成目 标DebugInRAM

DCD 0

• IRQ_Addr

DCD 0

• FIQ_Addr

DCD FIQ_Handler9来自系统复位后地址空间映射

10

存储器重新映射

11

12

13

mem_a加载效果

14

mem_b加载效果

15

谢谢大家!

不当之处请批评指正

16

•

LDR PC, ResetAddr

•

LDR PC, UndefinedAddr

•

LDR PC, SWI_Addr

•

LDR PC, PrefetchAddr

•

LDR PC, DataAbortAddr

•

DCD 0xb9205f80

•

LDR PC, [PC, #-0xff0]

•

LDR PC, FIQ_Addr

• ResetAddr

DCD ResetInit

• UndefinedAddr DCD Undefined

• SWI_Addr

DCD SoftwareInterrupt

• PrefetchAddr DCD PrefetchAbort

• DataAbortAddr DCD DataAbort

ARM7内部结构PPT

4 5

CPOL MSTR

6

LSBF

控制传输字节的移动方向 LSBF=1:数据传输LSB(bit0)在先 LSBF=0:数据传输MSB(bit7)在先

SPI中断使能位 SPIE=1:每次SPIE或MODF由0变为1,都会产生硬件中断 SPIE=0:SPI中断关闭

7

SPIE

SPI数据寄存器——SPDR

双向数据寄存器用于SPI数据的发送和接收。 处于主模式时,写该寄存器将启动SPI数据传输。从数据传输开始到SPIF状态位置位 并且还没有读取状态寄存器这段时间不能对该寄存器执行写操作 发送数据通过将数据写入该寄存器来实现,SPI接收的数据可以从该寄存器读出。 处于主模式时,没有缓冲区,所以在发送数据期间,不能再对寄存器进行写操作

10

11 7:2

VPB总线时钟是处理器时钟的1/2

无效 无效

四、SPI接口

在同一总线上可以有多个主机和从机,在同一时刻只允许有一个主机操作总线。在数据 传输过程中,总线上只能有个主机和一个从机。在一次数据传输中,主机总是向从机发 送一个字节数据(主机通过MOSI),而从机也总是向主机发送一个字节数据(主机通过 MISO接收数据),SPI总线时钟是由主机产生的。

SPI引脚描述

引脚名称 SCK

描述 串行时钟:用于同步SPI接口间数据传输的时钟信号。该信号总是由主机 驱动并且从机接收。时钟可编辑为高有效或低有效。它只是在数据传输 时才激活,其它任何时候都处在非激活或三态。 主入从出 主出从入 从机选择信号,低电平有效,用于指示被选择参与数据传输的从机。每 个从机都有各自特定的从机选择输入信号。 在数据传输之前,SSEL必须为低电平并且整个传输过程中保持低电平。 如果在数据的传输过程中SSEL变为高电平,传输被终止,从机返回空闲 状态并将任何接收到的数据丢失。这种异常没有其他指示。 该信号不直接由主机驱动,可通过软件使用一个普通IO口驱动。

2019精品第章7体系结构课件数学

1.1 ARM简介

• ARM处理器核简介——ARM10

该系列包括ARM1020E和ARM1020E处理器核, 其核心在于使用向量浮点(VFP)单元VFP10提供 高性能的浮点解决方案,从而极大提高了处理器的 整型和浮点运算性能。

可以用于视频游戏机和高性能打印机等场合。

基本的数据处理指令(不包括乘法); 字节、字和半字加载/存储指令; 具有分支指令,包括在子程序调用中使用的分 支和链接指令; 在操作系统调用中使用的软件中断指令。

1.1 ARM简介

• 各ARM体系结构版本——V2

同样为26位寻址空间,现在已经废弃不再使用, 它相对V1版本有以下改进:

具有乘法和乘加指令; 支持协处理器; 快速中断模式中的两个以上的分组寄存器; 具有原子性加载/存储指令SWP和SWPB。

改进了ARM/Thumb状态之间的切换效率; 允许非T变量和T变量一样,使用相同的代码 生成技术; 增加计数前导零指令和软件断点指令; 对乘法指令如何设置标志作了严格的定义。

3.1 ARM简介

• ARM处理器核简介

ARM公司开发了很多系列的ARM处理器核, 目前最新的系列已经是ARM11了,而ARM6核以及 更早的系列已经很罕见了。目前应用比较广泛的系 列是:

LOCK

DBGINSTRVALID DBGRQ DBGBREAK DBGACK DBGnEXEC DBGEXT[1] DBGEXT[0] DBGEN DBGRNG[1] DBGRNG[0] DBGCOMMRX DBGCOMMTX

数据类型

13.寻址方式简介

5.处理器状态

14.ARM7指令简介

6.处理器模式

ARM7体系结构20130304PPT课件

第13页/共50页

简介

·Xscale简介

Intel Xscale微控制器则提供全性能、高性价比、 低功耗的解决方案,支持16位Thumb指令并集成数字 信号处理(DSP)指令。

主要应用于手提式通讯和消费电子类设备。

第14页/共50页

ARM7体系结构

• 简介

状态:32位,处理器执行字方式的ARM指令,处理器默 认为此状态;

状态: 16位,处理器执行半字方式的Thumb指令。

注意: 两个状态之间的切换并不影响处理器模式或寄 存器内容。

第26页/共50页

处理器状态

·状态切换的一个例子

使用BX指令将ARM内核的操作状态在ARM状态和 Thumb状态之间进行切换。 从ATRhuMm状b状态态切切换换到到ThAuRmMb状态下的程序代码如下:

第27页/共50页

ARM7体系结构

• 简介

• 的模块、内核和功能框图 • 处理器状态 • 处理器模式

• 内部寄存器 • 7.当前程序状态寄存器 • 体系的异常体系的存储系

统

第28页/共50页

2.5 ARM处理器模式

·简介

ARM体系结构支持7种处理器模式,分别为:用户 模式、快中断模式、中断模式、管理模式、中止模式、 未定义模式和系统模式。这样的好处是可以更好的支持 操作系统并提高工作效率。ARM7TDMI完全支持这七种 模式。

译2码.在阶第段二,个取周出期指,令P3C。指向指令2,此 时4指.在令第1进4个入周三期级,流指水令线1的执译行码完阶成段,,指同令2和 时指取令出3指流令水2线。推进一级,同时开始指令4的

取指处理。

第20页/共50页

·思考题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.2 ARM7TDMI

三级流水线

ARM7TDMI处理器使用流水线来增加处理器指 令流的速度。这样可使几个操作同时进行,并使处 理和存储器系统连续操作,能提供0.9MIPS/MHz的 指令执行速度。

ARM7TDMI的流水线分3级,分别为: 取指译码执行

ARM处理器支持下列数据类型:

字节 8位

1

半字 16位(必须分配为占用两个字节) 1 2

字 32位(必须分配为占用4各字节) 1 2 3 4

3.4 体系结构直接支持的数据类型

体系结构直接支持的数据类型

注意: V4版本之后的ARM结构都支持这3种结构(包括 V4版本),而以前的版本只支持字节和字; 当数据类型定义为无符号型时,N位数据值使用正 常的二进制格式表示范围为0~2N-1的非负整数; 当数据类型定义为有符号型时,N位数据值使用2 的补码格式表示范围为-2N-1~+2N-1-1的整数;

半字加载/存储指令; 字节和半字的加载和符号扩展指令; 具有可以转换到Thumb状态的指令(BX); 增加了用户模式寄存器的新的特权处理器模式。

3.1 ARM简介

各ARM体系结构版本——V5

在V4版本的基础上,对现在指令的定义进行 了必要的修正,对V4版本的体系结构进行了扩展 并并增加了指令,具体如下:

1.简介

9.异常

2.ARM7TDMI

10.复位

3.ARM7TDMI的模块和 11.存储器及存储器映射

内部框图

I/O

4.体系结构直接支持的 数据类型

5.处理器状态

6.处理器模式

7.内部寄存器

8. 程序状态寄存器

3.1 ARM简介

ARM公司简介

ARM是Advanced RISC Machines的缩写,它是一家微处 理器行业的知名企业,该企业设 计了大量高性能、廉价、耗能低 的RISC (精简指令集)处理器。

3.3 ARM7TDMI的模块和内核框图

ADDR[31:0] 地址寄存器

扫描调试 控制

PC总线 地址增量器

ALU

总 线

寄存器组 31*32位寄存器 (6个状态寄存器)

A

乘法器

总

线

桶形移位器

32位ALU

增量器总线

B 总0]

指令译码 和

逻辑控制

指令流水线读数据寄存器 Thumb指令译码器 RDATA[31:0]

基本的数据处理指令(不包括乘法); 字节、字和半字加载/存储指令; 具有分支指令,包括在子程序调用中使用的分 支和链接指令; 在操作系统调用中使用的软件中断指令。

3.1 ARM简介

各ARM体系结构版本——V2

同样为26位寻址空间,现在已经废弃不再使用, 它相对V1版本有以下改进:

具有乘法和乘加指令; 支持协处理器; 快速中断模式中的两个以上的分组寄存器; 具有原子性加载/存储指令SWP和SWPB。

第3章 目录

1.简介

9.异常

2.ARM7TDMI

10.复位

3.ARM7TDMI的模块和 11.存储器及存储器映射

内部框图

I/O

4.体系结构直接支持的 数据类型

5.处理器状态

6.处理器模式

7.内部寄存器

8. 程序状态寄存器

3.5 处理器状态

处理器状态

ARM7TDMI处理器内核使用V4T版本的ARM结 构,该结构包含32位ARM指令集和16位Thumb指令 集。因此ARM7TDMI处理器有两种操作状态:

发送

译码

执行

访存

写入

ARM10 (Fetch) (Issue) (Decode) (Execute) (Memory) (Write)

预取

预取

发送

译码

转换

执行

访存

写入

ARM11 (Fetch) (Fetch) (Issue) (Decode) (Snny) (Execute) (Memory) (Write)

3.1 ARM简介

各ARM体系结构版本——V3

寻址范围扩展到32位(目前已废弃),具有独立 的程序:

具有乘法和乘加指令; 支持协处理器; 快速中断模式中具有的两个以上的分组寄存器; 具有原子性加载/存储指令SWP和SWPB。

3.1 ARM简介

各ARM体系结构版本——V4

不在为了与以前的版本兼容而支持26位体系结构, 并明确了哪些指令会引起未定义指令异常发生,它相 对V3版本作了以下的改进:

ARM7 SecurCore

Cortex

ARM9

ARM9E

ARM10

ARM11

Xscale

3.1 ARM简介

ARM7

预取

译码

执行

(Fetch) (Decode) (Execute)

ARM9

预取

译码

执行

访存

写入

(Fetch) (Decode) (Execute) (Memory) (Write)

预取

ARM体系结构从最初开发到现在有了很大的 改进,并仍在完善和发展。为了清楚的表达每个 ARM应用实例所使用的指令集,ARM公司定义了6 种主要的ARM指令集体系结构版本,以版本号 V1~V6表示。

3.1 ARM简介

各ARM体系结构版本——V1

该版本的ARM体系结构,只有26位的寻址空 间,没有商业化,其特点为:

公司的特点是只 设计芯片,而不生产。它将技术 授权给世界上许多著名的半导体、 软件和OEM厂商,并提供服务。

3.1 ARM简介

ARM公司简介

将技术授权给 其它芯片厂商

...

形成各具特色 的ARM芯片

3.1 ARM简介

微处理器是整个系统的核心,通常由3大部分 组成:控制单元、算术逻辑单元和寄存器。

章) ,程序如下所示。

跳转地址标号

;从Arm状态切换到Thumb状态 LDR R0,=Lable+1

地址最低位为 1,表示切换

BX

R0

到Thumb状态

;从Thumb状态切换到ARM状态

LDR R0,=Lable

BX

R0

地址最低位为 0,表示切换 到ARM状态

第3章 目录

1.简介

9.异常

2.ARM7TDMI

6.处理器模式

7.内部寄存器

8. 程序状态寄存器

简介

3.2 ARM7TDMI

ARM7TDMI基于ARM体系结构V4版本,是目 前低端的ARM核。具有广泛的应用,其最显著的 应用为数字移动电话。

注意:“ARM核”并不是芯片,ARM核与其它部 件如RAM、ROM、片内外设组合在一起才能构成 现实的芯片。

3.1 ARM简介

ARM体系结构

ARM体系结构的特点:

每条数据处理指令都对算术逻辑单元和移位器控 制,实现了ALU和移位器的最大利用; 地址自动增加和减少寻址模式,优化程序循环; 多寄存器装载和存储指令实现最大数据吞吐量; 所有指令的条件执行实现最快速的代码执行。

3.1 ARM简介

各ARM体系结构版本

3.2 ARM7TDMI

简介

ARM7TDMI支持32位寻址范围,并弥补了 ARM6不能在低于5V电源电压下工作的不足。 ARM7TDMI的后缀意义为:

ARM7 T D M I - S

ARM7TDMI 的可综合(synthesizable)版 本(软核),对应用工程师来说其编程模 型与ARM7TDMI 一致; 支持Embeded-ICE观察硬件;

3.1 ARM简介

ARM体系结构

ARM处理器为RISC芯片,其简单的结构使 ARM内核非常小,这使得器件的功耗也非常低。 它具有经典RISC的特点:

大的、统一的寄存器文件; 装载/保存结构,数据处理 操作只针对寄存器的 内容,而不直接对存储器进行操作; 简单的寻址模式; 统一和固定长度的指令域,简化了指令的译码, 便于指令流水线设计。

微处理器

输入

算术逻辑单元

控制单元 输出

寄存器

存储器

3.1 ARM简介

ARM处理器的应用

当前主要应用于消费类电子领域; 到目前为止,基于ARM技术的微处理器应用约占据

了32位嵌入式微处理器75%以上的市场份额 全球80%的GSM/3G手机、99%的CDMA手机以及

绝大多数PDA产品均采用ARM体系的嵌入式处理器, “掌上计算”相关的所有领域皆为其所主宰。 ARM技术正在逐步渗入到我们生活的各个方面。

9.异常

2.ARM7TDMI

10.复位

3.ARM7TDMI的模块和 11.存储器及存储器映射

内部框图

I/O

4.体系结构直接支持的 数据类型

5.处理器状态

6.处理器模式

7.内部寄存器

8. 程序状态寄存器

3.4 体系结构直接支持的数据类型

体系结构直接支持的数据类型

CLK CLEN CFGBIGEND nIRQ nFIQ nRESET ABORT LOCK WRITE

SIZE[1:0] PROT[1:0] TRANS[1:0]

DBG输出 DBG输入 CP控制 CP握手

ARM7TDMI模块

3.3 ARM7TDMI功能信号图

ARM7TDMI

第3章 目录

1.简介

3.2 ARM7TDMI

存储器访问

ARM7TDMI处理器使用了冯·诺依曼(Von Neumann)结构,指令和数据共用一条32位总线。 只有装载、存储和交换指令可以对存储器中的数据 进行访问。

数据可以是字节( 8位)、半字( 16位)或者 字(32位)。