计算机汇编语言入门

汇编语言教程

汇编语言教程第一章:引言汇编语言是一种底层的编程语言,通常用于编写对计算机硬件直接操作的程序。

本教程将向你介绍汇编语言的基本概念和语法,帮助你快速入门汇编编程。

1.1 汇编语言的概念汇编语言是一种符号性的语言,它使用助记符和指令集来操纵计算机硬件。

每个汇编语言指令都会被翻译成对应的机器码指令,从而让计算机执行相应的操作。

1.2 为什么学习汇编语言学习汇编语言可以帮助你更深入地理解计算机的运行原理,提高编程技能,以及优化性能。

第二章:汇编语言的基本结构在本章中,我们将介绍汇编语言程序的基本结构,包括指令、寄存器、内存等。

2.1 指令汇编语言指令包括数据传送指令、算术指令、逻辑指令等,用于执行各种操作。

2.2 寄存器寄存器是用于存储数据和执行操作的临时存储器。

常见的寄存器包括通用寄存器、特殊寄存器等。

2.3 内存内存用来存储程序和数据,汇编程序通过内存地址来读写数据。

第三章:汇编语言编程实例在本章中,我们将通过一些实际的编程示例来演示如何使用汇编语言编写程序。

3.1 Hello World程序下面是一个简单的Hello World程序的汇编代码示例:section .datamsg db 'Hello, World!', 0x0Asection .textglobal _start_start:mov eax, 4mov ebx, 1mov ecx, msgmov edx, 13int 0x80mov eax, 1xor ebx, ebxint 0x803.2 计算两数之和下面是一个计算两个数之和的汇编代码示例:section .datanum1 dw 10num2 dw 20section .textglobal _start_start:mov ax, [num1]add ax, [num2]ret结语通过本教程,相信你已经对汇编语言有了初步的了解,并且能够编写一些简单的汇编程序。

汇编语言入门教程

汇编语言入门教程汇编语言是一种低级编程语言,直接与计算机硬件进行交互,对于学习计算机原理和底层开发非常重要。

本文将为您介绍汇编语言的基本概念和使用方法,以及如何开始编写汇编程序。

一、汇编语言简介汇编语言是一种以指令集为基础的机器语言,它使用助记符号来代替二进制代码,使程序的编写更加直观。

汇编语言与特定的计算机体系结构紧密相关,不同的处理器有不同的汇编语言。

二、准备工作在开始学习汇编语言之前,您需要一台支持汇编语言开发的计算机和相应的开发工具。

常用的汇编语言开发工具有MASM、NASM和FASM等。

您可以根据自己的需求选择合适的工具。

三、汇编指令和寄存器1. 汇编指令汇编语言的指令包括数据传输指令、算术逻辑指令、控制转移指令等。

每个指令执行特定的操作,例如MOV指令可以将数据从一个位置传输到另一个位置。

2. 寄存器寄存器是计算机内部一小块非常快速的内存空间,用于存储临时数据和地址。

常见的寄存器有通用寄存器、状态寄存器和段寄存器等。

在编写汇编程序时,您需要了解不同寄存器的作用和使用方法。

四、汇编程序的基本结构一个典型的汇编程序由如下几个部分组成:1. 数据段:用于存储程序所需的数据2. 代码段:包含汇编指令,定义程序执行的步骤和过程3. 堆栈段:用于存储程序的运行时数据和函数调用时的参数五、汇编程序实例以下是一个简单的汇编程序示例,实现将两个数相加并将结果存储到指定的位置:```assemblysection .datanumber1 db 10number2 db 5result db ?section .textglobal _start_start:mov al, [number1] ; 将number1的值加载到AL寄存器add al, [number2] ; 将number2的值加到AL寄存器mov [result], al ; 将结果存储到result变量中mov eax, 1 ; 系统调用号:标准输出mov ebx, 1 ; 文件描述符:标准输出流mov ecx, result ; 输出的数据mov edx, 1 ; 数据的长度int 0x80 ; 调用系统中断mov eax, 0x1 ; 系统调用号:退出程序xor ebx, ebx ; 错误代码为0int 0x80 ; 调用系统中断```六、汇编语言学习资源如果您想深入学习汇编语言,以下是一些优秀的学习资源:1. 《汇编语言程序设计》(王爽):经典的汇编语言入门教材,适合初学者。

汇编语言入门教程

汇编语言入门教程汇编语言是一种低级机器语言的抽象表示形式,它将计算机底层的指令表示为可读的文本形式。

掌握汇编语言对于理解计算机硬件和编写高效的程序非常重要。

本教程将带您从零开始学习汇编语言的基础知识和编程技巧。

第一部分:介绍和准备工作1.1什么是汇编语言?1.2为什么要学习汇编语言?1.3汇编语言的基本特点和用途1.4开发环境的准备第二部分:汇编语言基础2.1数据表示和计算机内存2.2寄存器和指令2.3内存寻址方式2.4常用汇编指令2.5标志寄存器和条件分支指令第三部分:汇编语言编程技巧3.1数据的传递和处理3.2循环和分支结构3.3子程序的调用和返回3.4输入和输出操作3.5中断处理和异常控制第四部分:实例和应用4.1计算机硬件的控制4.2内存和外设的读写操作4.3实践项目和应用案例第五部分:调试和优化5.1调试汇编程序5.2性能优化和代码压缩技巧5.3代码的移植和扩展在学习汇编语言时,您需要了解计算机的基本结构和组成部分,包括中央处理器(CPU)、寄存器、内存等。

您还需要安装一款支持汇编语言的集成开发环境(IDE),并了解如何进行编译、调试和执行程序。

在学习汇编语言的基础知识时,您将学习如何表示和处理不同类型的数据,例如整数、浮点数和字符串。

您还将学习如何使用寄存器进行数据传输和计算,以及如何使用不同的寻址方式访问内存中的数据。

在学习汇编语言的编程技巧时,您将学习如何使用循环和分支结构进行条件判断和控制流程。

您还将学习如何编写子程序进行模块化的程序设计,并学习如何进行输入和输出操作以及异常处理。

通过实例和应用的学习,您将了解如何使用汇编语言实现一些常见的功能和操作。

例如,您将学习如何控制计算机硬件,如显示器、键盘和鼠标等。

您还将学习如何进行内存和外设的读写操作,以及如何处理中断和异常。

最后,您将学习如何调试和优化汇编程序,以确保程序的正确性和性能。

您将学习如何使用调试工具进行单步调试和变量跟踪,并学习如何进行代码的优化和压缩。

汇编语言基础知识

汇编语言基础知识汇编语言是直接在硬件之上工作的编程语言,首先要了解硬件系统的结构,才能有效地应用汇编语言对其编程,因此,本章对硬件系统结构的问题进行部分探讨,首先介绍了计算机的基本结构、Intel 公司微处理器的发展、计算机的语言以及汇编语言的特点,在此基础上重点介绍寄存器、内存组织等汇编语言所涉及到的基本知识。

1.1 微型计算机概述微型计算机由中央处理器(Central Processing Unit ,CPU )、存储器、输入输出接口电路和总线构成。

CPU 如同微型计算机的心脏,它的性能决定了整个微型计算机的各项关键指标。

存储器包括随机存储器(Random Access Memory ,RAM )和只读存储器(Read Only Memory ,ROM )。

输入输出接口电路用来连接外部设备和微型计算机。

总线为CPU 和其他部件之间提供数据、地址和控制信息的传输通道。

如图1.1所示为微型计算机的基本结构。

外部设备存储器输入输出接口电路中央处理器CPU地址总线数据总线控制总线图1.1 微型计算机基本结构特别要提到的是微型计算机的总线结构,它使系统中各功能部件之间的相互关系变为各个部件面向总线的单一关系。

一个部件只要符合总线结构标准,就可以连接到采用这种总线结构的系统中,使系统功能得到扩展。

数据总线用来在CPU 与内存或其他部件之间进行数据传送。

它是双向的,数据总线的位宽决定了CPU 和外界的数据传送速度,8位数据总线一次可传送一个8位二进制数据(即一个字节),16位数据总线一次可传送两个字节。

在微型计算机中,数据的含义是广义的,数据总线上传送的不一定是真正的数据,而可能是指令代码、状态量或控制量。

地址总线专门用来传送地址信息,它是单向的,地址总线的位数决定了CPU 可以直接寻址的内存范围。

如CPU 的地址总线的宽度为N ,则CPU 最多可以寻找2N 个内存单元。

控制总线用来传输控制信号,其中包括CPU送往存储器和输入输出接口电路的控制信号,如读信号、写信号和中断响应信号等;也包括其他部件送到CPU的信号,如时钟信号、中断请求信号和准备就绪信号等。

第1章汇编语言知识学习基本知识

第1章汇编语⾔知识学习基本知识第1章汇编语⾔基础知识本章介绍学习汇编语⾔程序设计所必须具备的基本知识,主要包括汇编语⾔的基本概念及计算机中数据的表⽰⽅法。

通过本章的学习,读者应能了解汇编语⾔概念及其使⽤的进位计数制、不同进位计数制之间的转换、计算机编码以及基本数据类型。

本章内容要点:汇编语⾔的概念汇编语⾔的特点不同进位计数制之间的转换计算机编码1.1汇编语⾔概述1.1.1 汇编语⾔基本概念⾃然语⾔是具有特定语⾳和语法等规范的、⽤于⼈类表达思想并实现相互交流的⼯具。

⼈与⼈之间只有使⽤同⼀种语⾔才能进⾏直接交流,否则就必须通过翻译。

要使计算机为⼈类服务,⼈们就必须借助某种⼯具,告诉计算机“做什么”甚⾄“怎么做”,这种⼯具就是程序设计语⾔。

程序设计语⾔通常分为三类:机器语⾔、汇编语⾔和⾼级语⾔。

⽽前两种语⾔与机器密切相关,统称为低级语⾔。

1.机器语⾔机器语⾔是计算机第⼀代语⾔,它全部由0、1代码组成,是能够直接被机器所接受的语⾔,是最底层的计算机语⾔。

机器语⾔不容易记忆,程序编写难度⼤,调试修改繁琐,且不易移植,现在程序员很少⽤。

但机器语⾔执⾏速度最快,它是⼀种⾯向机器的程序设计语⾔。

2.汇编语⾔为了克服机器语⾔难以记忆、表达和阅读的缺点,⼈们采⽤具有⼀定含义的符号作为助忆符,⽤指令助忆符、符号地址等组成的符号指令称为汇编格式指令(或汇编指令)。

例如,⽤ADD表⽰加法指令,SUB表⽰减法指令,MOV表⽰传送指令等。

汇编语⾔是汇编指令集、伪指令集和使⽤它们规则的统称。

伪指令的概念将在第4章介绍。

汇编语⾔⽐机器语⾔直观,容易记忆和理解,⽤汇编语⾔编写的程序也⽐机器语⾔程序易读、易检查、易修改。

对于不同的计算机,针对同⼀问题所编写的汇编语⾔源程序是互不通⽤的。

⽤汇编语⾔编写的程序执⾏效率⽐较⾼,但通⽤性与可移植性仍然⽐较差。

计算机不能直接识别⽤汇编语⾔编写的程序,必须由⼀种专门翻译程序将汇编语⾔程序翻译成机器语⾔程序,计算机才能执⾏。

汇编语言的学习步骤

汇编语言的学习步骤汇编语言作为低级语言的一种,是计算机硬件与高级编程语言之间的桥梁。

学习汇编语言可以帮助我们更深入地理解计算机底层的工作原理,提升编程的效率与质量。

下面是学习汇编语言的步骤,希望对你有所帮助。

Step 1:了解计算机体系结构在学习汇编语言之前,了解计算机的体系结构是非常重要的。

学习者需要了解计算机的组成部分,包括处理器、内存、输入输出设备以及其他外围设备。

掌握各组件之间的工作原理和相互关系,可以帮助我们理解汇编语言的运行机制。

Step 2:选取适合的汇编语言在市场上有多种不同的汇编语言可供选择,如x86、ARM等。

选择合适的汇编语言要根据自己的需求和实际情况进行判断。

一般而言,x86是最常见和广泛使用的汇编语言之一。

Step 3:学习汇编语言基础知识汇编语言是一种与硬件直接交互的语言,因此学习者需要掌握一些基础的概念和知识。

首先,了解各种指令的含义和功能,如数据传输指令、算术和逻辑指令等。

其次,要学会使用寄存器进行数据的读写和计算。

最后,掌握常用的编程技巧和调试方法,如单步执行、断点调试等。

Step 4:阅读汇编语言文档和教程阅读和理解汇编语言文档和教程是学习的关键。

可以选择一些经典的教材或者网络资源,比如《汇编语言》一书,或者在线的教学视频、博客文章等。

通过系统地学习和实践,逐渐掌握汇编语言的基本原理和技能。

Step 5:练习编写简单的程序尽早动手实践是掌握汇编语言的关键。

选择一些简单的编程项目,如计算器、加密算法等,通过编写相应的汇编语言程序来提升自己的编程能力。

可以加入一些汇编语言编程的社区或者论坛,与其他学习者一起交流和分享经验。

Step 6:深入学习高级的汇编语言特性一旦掌握了汇编语言的基础知识,可以进一步学习一些高级的特性和技巧,如宏汇编、模块化编程等。

学习者可以深入研究相关的文献和资料,提升自己的编程水平。

Step 7:应用汇编语言进行优化汇编语言被广泛应用于性能敏感的领域,如游戏开发、图形处理等。

计算机汇编语言入门

虽然 MASM 编译器不阻止用负数值初始化 BYTE,但不是

定义数组字节

使用多个初始化值 list1 BYTE 10,20,30,40 list2 BYTE 10,20,30,40 BYTE 50,60,70,80 BYTE 81,82,83,84 list3 BYTE ?,32,41h,00100010b list4 BYTE 0Ah,20h,‘A’,22h

定义字符串

如果需要用若干行来写一条字符串,除最后一行以外,每一 行都用逗号来结束 menu BYTE ”Checking Account”,0dh,0ah,0dh,0ah, ”1. Create a new account”,0dh,0ah, ”2. Open an existing account”,0dh,0ah, ”3. Credit the account”,0dh,0ah, ”4. Debit the account”,0dh,0ah, ”5. Exit”,0ah,0ah, ”Choice> ”,0

定义 WORD 和 SWORD 数据

在内存中定义 16-bit 整数

或双字符 单值或多值

word1 WORD 65535 ; largest unsigned value word2 SWORD –32768 ; smallest signed value word3 WORD ? ; uninitialized, unsigned word4 WORD ”AB” ; double characters myList WORD 1,2,3,4,5 ; array of words array WORD 5 DUP(?) ; uninitialized array

使用 DUP 操作码

使用 DUP 为数组或字符串预留空间。语法: counter DUP(argument ) 其中,counter 和 argument 必须是常数或常数表达式 var1 BYTE 20 DUP(0) ; 20 bytes, all equal to zero var2 BYTE 20 DUP(?) ; 20 bytes, uninitialized var3 BYTE 4 DUP(”STACK”) ; 20 bytes: ”STACKSTACKSTACKSTACK” var4 BYTE 10,3 DUP(0),20 ; 5 bytes

Assembly汇编语言基础入门

Assembly汇编语言基础入门汇编语言是一种低级机器语言的表示形式,它使用助记符和符号来代替机器码,方便程序员编写和理解。

在计算机科学领域,汇编语言是一门重要的编程语言,对于理解计算机的工作原理和进行底层的编程调优具有重要作用。

本文将介绍汇编语言的基础知识,包括语法和常用指令的使用。

一、汇编语言概述汇编语言是计算机硬件指令集的一种表示形式,它通过助记符和符号来代表不同的机器指令。

汇编语言与具体的计算机体系结构紧密相关,不同的计算机体系结构使用不同的汇编语言。

汇编语言的优点是直接操作硬件,可以实现高度优化的代码,但是缺点是可移植性差,需要了解底层的硬件细节。

汇编语言通常用于编写驱动程序、操作系统和高性能的应用程序。

二、汇编语言的基本语法1. 汇编语言使用英文助记符作为指令的代号,例如MOV表示数据传送指令,ADD表示加法指令。

2. 汇编语言使用伪指令来定义常量、变量和符号地址,例如DAT 定义数据,ORG定义起始地址。

3. 汇编语言使用标号来表示程序的入口和跳转地址,标号可以是任意合法的字符串。

4. 汇编语言使用寄存器来操作数据,不同的寄存器有不同的用途,例如AX用于存放常用的数据,BX用于存放地址。

5. 汇编语言使用操作数来指定操作的数据,操作数可以是寄存器、内存或立即数。

三、汇编语言的常用指令1. 数据传送指令:MOV指令用于将数据从一个位置拷贝到另一个位置。

2. 算术指令:ADD、SUB、MUL、DIV等指令用于进行基本的算术运算。

3. 逻辑指令:AND、OR、NOT、XOR等指令用于进行逻辑运算。

4. 分支指令:JMP、JE、JNE、JZ、JNZ等指令用于程序的跳转和条件判断。

5. 栈指令:PUSH、POP、CALL、RET等指令用于操作程序的栈空间。

6. 输入输出指令:IN、OUT、INT等指令用于与外部设备进行数据交换。

四、编写汇编程序的步骤编写汇编程序可以分为以下几个步骤:1. 确定程序的功能和需求。

汇编语言基础知识

进制 二进制 十六进制 十进制

16 位正数 最小值 最大值 进制 00000000000000000 0111111111111111 二进制 0000h 7FFFh 十六进制 0 +32767 十进制 32 位正数 最小值 00000000 0 ②

最大值 7FFFFFFFh 2147483647

进制 十六进制 十进制

1.3 怎样学好汇编语言 "The only way to learn a new programming language is by writing programs in it." --- Brian W. Kernighan & Dennis M. Ritchie "The best way to become a better programmer is to write programs." --- James Sinnamon 1.4 第一个汇编语言程序 data segment hi db "Hello,world!", 0Dh, 0Ah, "$" data ends code segment assume cs:code, ds:data main: mov ax, data mov ds, ax mov ah, 9 mov dx, offset hi int 21h mov ah, 4Ch int 21h code ends end main

1011 1000 0000 0001 0000 0000 0000 0101 0000 0001 0000 0000 汇编语言是对机器语言的符号化 Intel CPU 电脑中,所以长度超过 1 个字节的值 都按照低字节在前,高字节在后的顺序存放到内存中。 例如有一个 16 位数=1011 0110 1111 0000 高8位 低8位 现在要把它放到内存地址 1000 开始的单元中: 地址 值 1000 1111 0000 1001 1011 0110 Little-Endian 表示法 1.1.3 汇编语言 港台:组合语言

汇编语言基础知识.

4.汇编语言程序设计的意义

学习汇编语言的意义: 1)与硬件密切相关,是学习硬件类课程的先行课 和基础课。 2)有利于理解计算机的工作原理。 3)可直接而有效地控制硬件。 4)执行效率高,占用空间小。 5)特殊应用只能使用汇编语言,如加密解密等。 应该指出的是:在计算机速度大大提高和存储器容 量大大增加的今天,高级语言的使用更为广泛和普遍 (特别是编写大型程序)。

×16-1+11 ×16-2 引入十六进制数的目的是为了描述二进制数。

数的书写方法:

1)二进制数尾部加B(b)。 2)十六进制数尾部加H(h);如记数符号a,b,c, d,e,f打头,头部应加0,如0A8F5H;记数符号 a,b,c,d,e,f 不区别大小写,与ABCDEF等效。 3)十进制数尾部加D(d),但通常可以省略。

二进制的数符集中有两个符号:0和1;

八进制的数符集中有8个符号:0,1,2,3,4,5,6,7;

十 进 制 的 数 符 集 中 有 10 个 符 号 : 0,1,2,3,4,5,6, 7,8,9;

十 六 进 制 的 数 符 集 中 有 16 个 符 号 : 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F。

★集成开发环境:开发工具包括文本编辑、翻译程序、 调试程序、连接程序等,在DOS时代,其各自是独立 的;现在将其集成为一个软件,即为“集成开发环 境”。

返回1.1

1.1.3计算机的程序设计语言

低级语言 程序设计语言

1.机器语言 2.汇编语言

3.高级语言 C/C++、JAVA、 DELPHI……

1.机器语言

负数原码:符号位为1,数值位照抄。 例:X=+25=+00011001B [X]原=00011001B

汇编语言教程

汇编语言教程1. 概述汇编语言(Assembly Language)是一种低级程序设计语言,它直接利用计算机硬件体系结构进行编程。

本教程将为您介绍汇编语言的基本概念、语法规则和应用场景,帮助您快速入门汇编语言编程。

2. 汇编语言的基本概念2.1 计算机硬件体系结构计算机硬件由中央处理器(CPU)、存储器、输入设备和输出设备等组成。

了解计算机硬件体系结构对理解汇编语言编程至关重要。

2.2 汇编语言与高级语言汇编语言相对于高级语言更加接近计算机底层,使用汇编语言编写的程序执行效率高,但编写难度也较大。

高级语言则提供了更加友好和简洁的语法,适用于快速开发大型项目。

2.3 汇编器和汇编语言的翻译汇编器是将汇编语言代码翻译成机器语言代码的工具。

汇编语言源代码通过汇编器进行编译,生成可执行文件。

3. 汇编语言的语法规则3.1 寄存器和内存汇编语言使用寄存器和内存来存储和操作数据。

寄存器是CPU内部的存储单元,内存则是计算机中用于存储数据的设备。

掌握寄存器和内存的使用方法是使用汇编语言的基础。

3.2 汇编指令汇编语言通过汇编指令来完成各种操作,如加载数据到寄存器、进行算术运算、条件判断和跳转等。

熟悉常用的汇编指令是掌握汇编语言编程的关键。

3.3 标志位和条件码汇编语言中的标志位和条件码用于控制程序的流程和执行结果。

了解标志位和条件码的含义和使用方法对编写结构化的汇编程序非常重要。

4. 汇编语言编程实例4.1 汇编语言的简单示例通过一个简单的示例代码,介绍如何使用汇编语言编写一个加法运算的程序,并展示程序的编译和执行过程。

4.2 汇编语言的进阶示例结合实际应用场景,演示如何使用汇编语言编写更复杂的程序,如字符串操作、文件读写和图形界面等。

5. 汇编语言的应用场景5.1 嵌入式系统开发汇编语言在嵌入式系统开发中得到广泛应用,能够充分利用硬件资源,提高系统性能和响应速度。

5.2 驱动程序开发汇编语言常用于编写设备驱动程序,直接操作硬件设备接口,提供更高效的驱动性能。

WindowsX8664位汇编语言入门

WindowsX8664位汇编语言入门Windows x86-64位汇编语言入门汇编语言是计算机硬件和操作系统之间的桥梁,它能够直接控制计算机的底层硬件。

对于计算机科学的学习者来说,了解汇编语言是非常重要的一步。

本文将介绍如何入门并学习Windows x86-64位汇编语言。

一、了解汇编语言的基本概念在开始学习汇编语言之前,我们需要先了解一些基本概念。

汇编语言是一种低级语言,它使用助记符来代替机器指令,这样更方便我们理解和编写程序。

汇编语言的基本单位是指令,每条指令对应着一条机器指令。

在x86-64架构中,指令长度可以是1到15个字节。

二、安装并配置开发环境要开始编写和执行汇编语言程序,我们首先需要安装一个好的开发环境。

在Windows操作系统上,常用的开发环境有MASM、NASM、TASM等。

这些开发工具可以帮助我们将汇编代码转换为可执行文件。

三、学习汇编语言的语法和指令集汇编语言与其他高级编程语言相比,语法更加简单和直接。

学习汇编语言的关键就是理解和掌握其语法和指令集。

在学习过程中,我们可以参考官方文档或者一些经典的教程,如《汇编语言程序设计》。

四、编写你的第一个汇编程序现在,我们可以尝试编写自己的第一个汇编程序。

我们可以从一个简单的程序开始,比如输出一个简单的“Hello, World!”。

下面是示例代码:section .datamsg db 'Hello, World!', 0section .textglobal _start_start:; 输出字符串mov eax, 4mov ebx, 1mov ecx, msgmov edx, 13int 0x80; 退出程序mov eax, 1xor ebx, ebxint 0x80这个程序使用Linux系统调用来输出字符串,并退出程序。

我们可以使用汇编器将其编译成可执行文件,然后在命令行中运行。

五、深入学习汇编语言的高级特性一旦掌握了汇编语言的基础知识,我们就可以进一步学习一些高级特性,如函数调用、内存管理、寄存器的使用等。

如何轻松学好汇编语言

如何轻松学好汇编语言汇编语言作为底层的编程语言,是计算机体系结构的基石之一。

掌握汇编语言不仅可以加深对计算机的理解,还能提升程序的性能和调试的能力。

然而,对于初学者来说,汇编语言可能显得复杂而晦涩。

本文将分享一些学习汇编语言的方法和技巧,帮助读者轻松掌握这门重要的编程语言。

一、了解计算机体系结构在学习汇编语言之前,我们需要先对计算机的体系结构有所了解。

理解计算机的工作原理和组成部分,对于学习汇编语言非常重要。

可以通过查阅相关的教材、网络资源或者参加计算机组成原理的课程来获取这方面的知识。

二、选择合适的汇编语言汇编语言有多种类型,如x86、ARM等,针对不同的计算机体系结构,对应的汇编语言也有所不同。

初学者可以选择较为常用的x86汇编语言进行学习。

x86汇编语言广泛应用于个人计算机和服务器等平台,学习资源丰富,使用较为方便。

三、阅读优质教材或教程在学习汇编语言时,阅读优质的教材或教程是非常重要的。

这些教材通常会从基础概念开始介绍,逐步引导读者了解汇编语言的语法和编程技巧。

推荐一些经典的汇编语言教材,如《汇编语言》、《汇编语言程序设计》等。

此外,还可以参考一些在线教程或者视频教程,以更加形象生动地学习汇编语言。

四、进行实践和编程练习学习汇编语言最有效的途径是进行实践和编程练习。

通过亲自编写汇编程序,加深对语言特性和语法规则的理解。

可以选择一些简单的示例程序进行模仿和练习,慢慢提升编程技能。

同时,还可以参考一些开源的汇编语言项目,学习和借鉴其他人的代码和经验。

五、参加相关的讲座或培训如果条件允许,参加一些汇编语言相关的讲座或培训是提升学习效果的好方法。

这些讲座和培训通常由专业人士主讲,能够深入浅出地解释难点和关键知识点。

同时,还可以与其他学习者交流和分享经验,加深理解和扩展思路。

六、使用辅助工具和调试器在学习汇编语言过程中,可以借助一些辅助工具和调试器,提高学习效率和编程质量。

例如,可以使用汇编语言的集成开发环境(IDE)来编写和调试程序,或者使用模拟器来模拟执行程序。

汇编语言入门教程

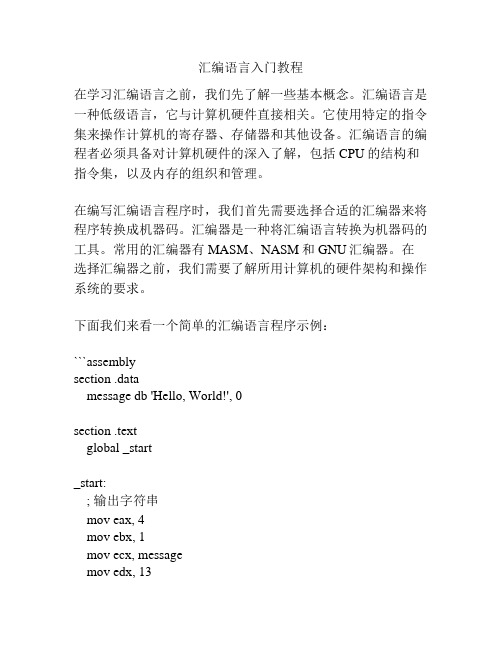

汇编语言入门教程在学习汇编语言之前,我们先了解一些基本概念。

汇编语言是一种低级语言,它与计算机硬件直接相关。

它使用特定的指令集来操作计算机的寄存器、存储器和其他设备。

汇编语言的编程者必须具备对计算机硬件的深入了解,包括CPU的结构和指令集,以及内存的组织和管理。

在编写汇编语言程序时,我们首先需要选择合适的汇编器来将程序转换成机器码。

汇编器是一种将汇编语言转换为机器码的工具。

常用的汇编器有MASM、NASM和GNU汇编器。

在选择汇编器之前,我们需要了解所用计算机的硬件架构和操作系统的要求。

下面我们来看一个简单的汇编语言程序示例:```assemblysection .datamessage db 'Hello, World!', 0section .textglobal _start_start:; 输出字符串mov eax, 4mov ebx, 1mov ecx, messagemov edx, 13int 0x80; 退出程序mov eax, 1xor ebx, ebxint 0x80```在上面的示例中,我们定义了一个字符串变量message,并在程序中输出了该字符串。

首先,我们将字符串的地址保存在ecx寄存器中,然后使用系统调用将字符串输出到标准输出。

接下来,我们使用了另一个系统调用来退出程序。

我们将1保存在eax寄存器中,表示退出程序的系统调用编号。

通过将ebx寄存器的值设置为0,我们告诉操作系统程序退出时不返回任何错误代码。

这只是一个简单的汇编语言程序示例,但它涵盖了汇编语言程序的基本结构和语法。

在接下来的教程中,我们将逐步学习如何编写更复杂的汇编语言程序,并介绍汇编语言的各种特性和技巧。

汇编程序设计语言知识点

汇编程序设计语言知识点汇编程序设计语言是一种低级别的程序设计语言,用于编写计算机的底层代码。

它与高级语言相比,更加接近机器的指令集架构,可以直接操作计算机的硬件和寄存器。

在本文中,将介绍汇编程序设计语言的一些重要知识点。

一、汇编语言基础知识1. 汇编语言的发展历程:从机器语言到汇编语言;2. 汇编语言的组成部分:指令、操作数和寄存器;3. 汇编语言的语法规则:标号、指令、操作数和注释的格式;4. 汇编程序的编写流程:编辑、汇编、链接和运行。

二、汇编语言的数据类型1. 二进制数和十六进制数的表示方法;2. 常用的数据类型:字节、字和双字;3. 数据的存储方式:大端字节序和小端字节序;4. 数据的表示范围和溢出问题。

三、汇编语言的指令集1. 数据传输指令:MOV、XCHG、PUSH和POP等;2. 算术运算指令:ADD、SUB、INC和DEC等;3. 逻辑运算指令:AND、OR、XOR和NOT等;4. 条件转移指令:JMP、JZ、JE和JG等;5. 循环控制指令:LOOP、LOOPZ和LOOPNZ等;6. 系统调用指令:INT、CALL和RET等。

四、汇编语言的控制结构1. 顺序结构:代码按顺序执行;2. 条件结构:根据条件选择执行路径;3. 循环结构:根据条件循环执行代码块;4. 无限循环:使用JMP指令实现无限循环。

五、汇编语言的调试和优化1. 调试工具:调试器、寄存器监视、内存监视和断点设置;2. 常见的调试问题和解决方法;3. 优化技巧:减少指令数量、减少内存访问和提前计算等。

六、汇编语言的应用领域1. 操作系统开发:汇编语言作为操作系统内核的编程语言;2. 嵌入式系统开发:汇编语言用于编写驱动程序和底层代码;3. 游戏开发和图形编程:汇编语言用于优化性能和实现特殊效果;4. 加密和反汇编:汇编语言用于加密算法和反编译程序。

结语本文介绍了汇编程序设计语言的基础知识、数据类型、指令集、控制结构、调试和优化等重要知识点,以及其在不同领域的应用。

大学计算机专业-汇编语言

RET指令用于从子程序返回,并从堆栈中弹出返回地 址。

04 汇编语言程序结构

程序的基本结构

汇编语言程序由指令和数据组成,指令告诉计算机做什么,数据则是被处理的对 象。

程序的基本结构包括程序头、程序体和程序尾。程序头包含程序的标识符、版本 号等信息;程序体是程序的主体,包含程序的逻辑实现;程序尾包含程序的结束 标识符。

02

汇编语言的特点是具有高度的可移植性和可读性,同时能够直

接控制计算机硬件。

汇编语言通常用于编写系统软件、驱动程序、嵌入式系统等需

03

要高效控制硬件的程序。

汇编语言的历史和发展

1

汇编语言的历史可以追溯到计算机发展的初期, 当时人们使用助记符来编写机器指令。

2

随着计算机技术的不断发展,汇编语言也在不断 演变和完善,出现了许多不同的汇编器、汇编语 法和指令集。

01

03

汇编语言通常比高级语言执行速度更快,因为其指令 直接对应硬件操作。但高级语言由于其抽象性,使得

编程更加方便和高效。

04

汇编语言的可移植性较差,因为不同的计算机架构有 不同的汇编语言。而高级语言通常更容易在不同的平 台上移植和运行。

THANKS FOR WATCHING

感谢您的观看

汇编语言和高级语言都遵循一定的语法规则,通过编程语 言的指令来控制计算机执行任务。

汇编语言和高级语言都需要经过编译或解释才能被计算机 执行。

与高级语言的主要区别

汇编语言的指令是直接对应计算机硬件操作的,而高 级语言则是一层抽象,通过编译器或解释器转换成机

器指令。

输标02入题

汇编语言的语法相对简单,但需要程序员对计算机硬 件有较深的理解。高级语言的语法相对复杂,但提供 了更丰富的抽象和表达能力。

汇编语言-基础知识

汇编语⾔-基础知识汇编语⾔-基础知识汇编语⾔的产⽣计算机作为⼀个只能读懂和执⾏⼆进制的东西,在其刚被发明出时,都是⽤机器语⾔(01⼆进制形式表⽰)来写⼊程序,随着程序越来越复杂,需要更长的组合,不光⼀个微⼩的0->1将会导致错误,以及过于难记忆与分辨。

随后找到了⼀种解决⽅法,将这些最基础⼆进制的指令,⽤⼀串字符表⽰,再由电脑的汇编器(Assembler)将这串字符转化成⼆进制机器语⾔,程序员只需要负责写汇编指令的源代码即可。

汇编语⾔由三部分组成:1. 汇编指令(有与其专门对应的机器码)2. 伪指令(由汇编器执⾏,没有与其专门对应的机器码)3. 其他符号(如+,-,*,/由汇编器执⾏,没有与其专门对应的机器码)程序放在哪⾥CPU是电脑能够运算的核⼼部件,但是想要指挥CPU,需要有指令和数据,储存运⾏中程序的指令和数据的就是常说的内存。

对于磁盘中的数据, CPU⽆法直接直⾏,需要加载到内存中才可以被CPU所使⽤。

指令和数据⼀样,都是⼀串⼆进制码, CPU在⼯作的时候,会根据需要把它们解释成指令或者数据,例如1000101111000011这⼀串⼆进制码,它既可以表⽰数据8BC3_H,⼜可以表⽰指令mov ax, bx (8086CPU中)。

对于内存,⽬前的⽅式均为以8个bit即1byte为最⼩的存储单元(1byte可以保存8位⼆进制数), CPU想从内存中读取或者存储数据,⾸先需要找到要存在内存的地址,传达控制信息是读⼊还是写⼊,以及读或写的数据。

在⼀台计算机中, CPU通过总线,与内存等外部设备进⾏连接,总线可分为三种,分别是地址总线,数据总线以及控制总线,字如其意,地址总线负责找到要读取或者储存的那个位置,数据总线负责数据的传输,控制总线负责传输要执⾏的⾏为是读⼊还是写⼊。

对于8086CPU,他的地址总线有20根,数据总线有16根,也就是说他的寻址空间为2^20Byte,也就是最多可以寻址1MB内存,最多每次只能传输16bit(2Byte)的数据。

汇编语言手册

汇编语言手册汇编语言是一种底层计算机语言,用于编写各种软件和驱动程序。

它与高级编程语言相比,更加接近计算机底层的硬件操作。

本手册旨在为使用汇编语言编程的开发人员提供详细的参考和指南。

1. 汇编语言的基础知识汇编语言是一种基于机器语言的符号表示方法,通过将操作码和操作数转换为人可读的指令,实现与计算机底层硬件的交互。

首先,我们需要了解汇编语言的基本概念和语法规则,包括寄存器、内存、指令和操作数的使用方法等。

2. 汇编语言的数据类型和指令在汇编语言中,有多种数据类型和指令可以使用。

常见的数据类型包括字节、字、双字和四字等。

指令则用于执行各种操作,如算术运算、逻辑运算和数据传输等。

在本节中,我们将详细介绍常用的数据类型和指令的使用方法和注意事项。

3. 汇编语言的程序结构汇编语言编程通常采用的是过程式的编程方法,即通过定义和调用过程来组织代码。

程序结构的良好设计对于代码的可读性和维护性至关重要。

本节将介绍如何定义和调用过程、使用标签和跳转指令来实现程序的跳转和分支。

4. 汇编语言的输入输出输入输出是任何程序的必要部分。

在汇编语言中,我们通过各种输入输出指令来实现与外部设备的交互。

例如,可以使用键盘输入数据、从内存中读取数据、将数据输出到屏幕或保存到文件等。

本节将介绍如何使用输入输出指令完成常见的输入输出任务。

5. 汇编语言的调试和优化调试和优化是程序开发过程中不可或缺的环节。

在本节中,我们将介绍如何使用调试工具和技术,如断点调试、寄存器跟踪和内存监视等,来定位和修复程序中的错误。

另外,我们还将探讨如何通过代码重构和性能优化等方式提高程序的效率和质量。

6. 汇编语言的应用领域汇编语言虽然底层和复杂,但在某些特定的应用领域中仍然有其存在的价值。

比如,嵌入式系统开发、驱动程序编写和逆向工程等都需要掌握一定的汇编语言知识。

本节将简要介绍几个常见的应用领域,并提供相关的实例和参考资料。

总结:本手册提供了关于汇编语言的详细参考和指南。

汇编基础入门知识

汇编基础⼊门知识From:学习汇编前你应该知道的知识1、汇编需要什么⼯具和程序,到哪⾥下载?⽬前阶段,汇编程序仅需要两个程序就够了。

masm.exe,link.exe。

前者是编译程序,后者是链接程序。

另外,为了验证和调试程序,还需要⼀个程序debug.exe,该程序由windows本⾝就提供。

将⼆者下载后,放到某⼀个⽬录中(任意⽬录都可以),考虑到很多命令需要通过键盘敲⼊,所以建议你不要把⽂件放⼊到长⽂件名⽬录、中⽂⽬录或很深的⽬录中。

⽐如你可以建⼀个“D:\Masm”⽬录,并建议此后的程序都放这个⽬录,此后称这个⽬录为汇编⽬录。

2、学习汇编需要有哪些编程⽅⾯的知识?没有任何编程⽅⾯的知识,学习此语⾔等于缘⽊求鱼,所以请放弃学习的想法。

⼀般来说⾄少要知道如下⼏点:*)程序的运⾏逻辑结构有顺序(按语句依次执⾏)、分⽀结构(IF...THEN...ELSE...),循环结构(FOR...NEXT)三种结构。

*)知道什么是⼦程序,什么是调⽤。

*)汇编程序员的视⾓。

不同编程视⾓编程要求是不⼀样的。

⽐如删除⽂件:>>⽤户的视⾓是找到“删除”按钮或菜单,然后单击⼀下即可。

>>⾼级程序员的视⾓是知道删除的⽂件,并发出删除命令。

这些通过API实现。

>>汇编程员的视⾓是得到要删除的⽂件名,找到该⽂件所在位置,通过调⽤删除“中断命令”进⾏删除。

>>操作系统开发⼈员的视⾓则是接到删除命令后,先找到系统根⽬录区,由根⽬录区的链接依次找到⼦⽬录区,直到找到要删除的⽂件,然后按照操作系统删除⽂件的规则对该⽂件名进⾏修改。

⽐如DOS,只把第⼀个字符改成"?"。

按程序语句等价的⾓度看,⼀⾏VB的打印语句,⽤汇编实现⼤约需要⼀百⼆⼗多⾏。

知道汇编语⾔的视⾓后就要知道,前⾯的道路是坎坷的,没有耐⼼是不⾏的。

想通过⼏分钟⼏⾏程序就完成很复杂的操作不是件容易的事。

3、学汇编有什么⽤?汇编产⽣于DOS时代或更早,⽽现在是Windows时代,所以可能遗憾地说:尽管还有批⽜⼈在⽤汇编开发核⼼级程序,但我们⼏乎没什么⽤,除了必要时间能拿来分析⼀两个程序的部分代码之外,别的也就没⼲什么⽤了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实模式内存寻址

实模式举例

举例:mov AX, [BX] 假设: 段寄存器中的内容:1000H 偏移量寄存器中的内容:F000H

实模式内存

实模式寻址特点

20-bit 实模式地址可以在 1M-byte 的空间内(地址范围是 00000-FFFFFH) ,每 16-byte 开始一个新的段 由于实模式中的起始地址,都是以 16-byte 的倍数开始,被 称为段落(paragraph) 结果:

1. 在保护模式下,段寄存器中的内容是个选择器,从选择描述 符表中选出一个描述符 (descriptor),而不是段起始地址 2. 描述符中包含了内存中存储段的位置、长度、和访问权限等 信息

保护模式寻址原理

操作系统中的寻址模式

DOS 操作系统使用实寻址方式 保护模式是 Windows 系统的寻址方式 处理器开机时首先进入实寻址方式 从实模式向保护模式转换的过程:建立总体描述符表 (Global Descriptor Table GDT) 或本地描述符表 (Local Descriptor Table LDT),并在 CPU 的机器字 (machine status word MSW) 中启动保护模式

CISC 与 RISC

CISC - complex instruction set(复杂指令集)

指令集规模大 高级操作 需要微指令解析 例如:Intel 80x86 家族

RISC - reduced instruction set(精简指令集)

简单,原子级指令 指令集规模小 硬件可以直接执行 例如:

向下兼容

实模式使得为 8086/8088 写的程序能够在 80286 及以后的芯 片上运行,而不需要改动。

Intel 芯片的缺省模式

Intel 的芯片加电后,或进行过复位后,都是先进行实模式操 作

内存的第一个 1M 字节,被称作实内存,或传统存储系统。

段和偏移量

内存的实模式地址是由段地址和偏移量地址合成的 段地址的内容,存在一个段基址寄存器中,用来定义一个长 度为 64K-byte 的内存段的起始地址 偏移量地址是用来选在 64K-byte 大小的段内的具体位置的 ⇒ 段的大小 = 64K bytes

内存中的段

段重叠

程序与数据搬迁

使用段起始地址和偏移量的机制,使得搬迁成为可能 搬迁程序:

将程序放入内存中任何位置 无需改变即可执行

Hale Waihona Puke 数据搬迁:将数据存入内存中任何位置 无需改变程序直接使用

程序搬迁实例

寻址方式

操作数是某个操作需要的数据(例如:ADD) 寻址方式帮助我们找到内存中的任何一个数据(操作数)的 位置(即实模式中的物理地址或保护模式中的逻辑地址)进 行操作 CPU 越强大,就可以支持越多的寻址方式 Intel 的 8086 系列芯片(实模式)常用寻址方式包括:

描述符选择器

描述符选择器,使用段寄存器,从两个描述符表中,选择 8192 个描述符中的一个

描述符选择器

在保护模式下,段寄存器的内容为:

1. 13-bit 的区域是描述符选择器 2. 1-bit 作为表选择 (TI) 3. 还有 2-bit 作为优先级选择 (requested privilege level RPL)

分页寻址模式工作步骤

举例

在 16M bytes 的内存中以 C8000H-EFFFFH 为地址的位置, 必须被转向以 110000-137FFFH 为地址的页面,其他页面指 向正常内存的地址

MOD-REG-R/M 区

MOD 区定义 R/M 的操作,并表明是否有置换发生 MOD=00 MOD=01 MOD=10 MOD=11 内存无置换 内存发生 8-bit 置换 内存发生 16/32-bit 置换 寄存器

REG 信息

代码 000 001 010 011 100 101 110 111

两个描述符表各自都可以存放 8192 个描述符

描述符的内容

每个描述符的长度为 8-byte 描述符中的起始地址 (base address) 信息,给出了程序段的 起始位置

描述符的内容

段的长度 (segment limit) 存放着段中最大偏移量的值 举例

如果,某存储段的起始位置为 F00000H,结束位置是 F000FFH,则起始地址是 F00000H,而段的长度是 FFH

1. 立即数寻址 (Immediate Mode) 2. 寄存器寻址 (Register Mode) 3. 寄存器间接寻址 (Register-Indirect Mode) 4. 直接寻址 (Direct Addressing Mode) 5. 间接寻址 (Indirect Addressing Mode) 6. 相对寻址 (Relative Addressing Mode) 7. 变址寻址 (Indexed Addressing Mode)

寄存器寻址

立即数寻址

直接寻址

寄存器间接寻址

基址加变址寻址

寄存器相对寻址

相对基址加变址寻址

堆栈寻址

堆栈

可以临时存放数据 存放进程的返回地址

Intel 8086 系列的堆栈内存由标出顶端位置的堆栈指针 (SP) 和堆栈段寄存器 (SS) 确定 数据进出堆栈的方式,采用后入先出 (LIFO last-in first-out) 机制

W=0 (Byte) AL CL DL BL AH CH DH BH

W=1 (Word) AX CX DX BX SP BP SI DI

W=1 (Word) EAX ECX EDX EBX ESP EBP ESI EDI

R/M 信息

机器码与汇编语言转换

机器码与汇编语言转换

保护模式寻址

保护模式寻址方式(在 80286 及以后的芯片中使用) ,可以 访问 1M 传统内存之外的内存中的数据和程序,同时也仍能 访问 1M byte 传统内存空间 段寄存器的内容在不同模式,对微处理器的意义并不相同

线性地址的形成

线性地址的形成

如果内存中 GDT 和 LDT 的内容如下图中所示,CS 中内容 为 83H,当 指令地址寄存器 IP 中内容为 100H 时,线性地 址是多少?

分页寻址模式

在 80386 及以后系统中的内存分页机制,可以将任何一个物 理地址用任意的逻辑地址表示出来 逻辑地址是由一个程序产生出来的 使用内存的分页机制,逻辑地址被转换成物理地址的过程, 并不需要用户看见

在 80286 系统中,保护模式可以访问的内存段

大小为 1-64K bytes 所有段都位于可以访问的 16M bytes 内存系统内

在 80386 及以后的系统中,保护模式可以访问的内存段

大小为 1-1M bytes ,或 4K-4G bytes 所有段都位于可以访问的 4G bytes 内存系统内

基本运行环境

可寻址内存 通用用途寄存器 指数与基址寄存器 特殊用途寄存器 状态标志寄存器 浮点数,MMX,XMM 寄存器

可寻址内存

实模式

1 MB 空间 20-bit 地址

保护模式

4 GB 空间 32-bit 地址

实模式 Real mode

通过实模式操作,可以使 Intel 8086 使用 20-bit 地址,找到 内存中,最前面的 1MB 空间。 (Pentium 处理器中也使用这 个技术) 实模式操作

段落的大小 = 16 bytes 任何段落的起始地址,都是 16 的倍数

实模式的寻址范围

从 80286 开始(配备外部电路) ,到 80386 到以后的 Pentium Pro 芯片,都有个额外的 64K bytes 减 16 bytes 的 可寻址范围,条件是:

段起始地址是 FFFFH 系统中安装了 HIMEM.SYS 驱动程序

由 TI-bit 选择描述符来自总体描述符表 (GDT, TI=0) 还是本 地描述符表 (LDT, TI=1)

描述符选择器

描述符

描述符描述内存段的位置、长度、以及对该存储段的访问权 限 描述符存在于两种描述符表中:

1. 总体描述符表 (GDT) 存放任何程序都可以使用的程序段的定 义 2. 本地描述符表 (LDT) 存放某一特定程序使用的程序段的定义

ARM (Advanced RISC Machine) DEC Alpha (被 Compaq 收购,又被收入 HP)

Intel 架构指令格式

操作码

操作码

D-bit 指明数据流的方向,如果 D=0,REG → R /M ,如果 D=1,R /M → REG W-bit 指定操作数是一个字节 W=0(8-bit 模式)或双字节 W=1(16-bit 模式)

段 CS SS DS ES FS GS 偏移量 EIP ESP, EBP EAX, EBX, ECX, EDX, ESI, EDI, 8-bit 或 32-bit 数 EDI 作为字符串指令 无 无 用途 指令地址 堆栈地址 数据地址 目标字符串地址 一般地址 一般地址

特殊用途寄存器

编码段寄存器(code segment register CS)用来定义编码段 的起始地址,指令指针(instruction pointer IP)用来指出下 条指令在指令段中的位置 堆栈数据放在堆栈段中,在内存中的起始地址由堆栈指针 (SP)或基指针(BP)中的内容确定 段可以被看成内存中可以上下移动的窗口,访问数据和代码 每个程序可由多个段组成,但只能一次访问四个段 (8086-80286)或六个段(80386 及以后芯片)

这个可寻址的额外区域(0FFFF0H-10FFEFH)被称作高内 存

偏移量地址

理论上讲,偏移量地址的最大值和段起始地址的最大值,都 是 FFFFH 因此,可寻址到的实模式地址最大值为:

使用 HIMEM.SYS 驱动程序,系统就可以访问这块地址

缺省段寄存器与偏移量寄存器