SlaveFIFO使用手册

FIFO标签打印用户手册

利华科技信息技术文档用户手册FIFO标签打印用户手册V1.0苏州))有限公司利华科技((苏州利华科技2008-3-111.引言FIFO标签打印程序(简称FIFO标签打印)的基本功能是:根据MRP系统数据(Turnkey料件依据采购检验申请单,Consign料件依据受托加工入库单),打印以单种物料为基本单元的唯一ID标识入库标签。

1.1编写目的手册编写的目的是方便FIFO标签打印用户正确使用程序,了解异常的反馈流程与常见处理方法。

2.运行环境2.1硬件设备计算机一台(建议配置CPU赛扬1.7,内存256MB,主板含并口)标签打印机一台(建议使用zebra条码打印机)2.2网络环境连接公司办公网络2.3支持软件操作系统:安装.NetFramework2.0及以上Windows操作系统3.使用过程3.1安装与初始化设置3.1.1标签打印机安装(以zebra105sl为例)详见附件"Zebra105SL条码打印机使用手册"3.1.2FIFO标签打印软件安装3.1.2.1安装系统必要组件 Framework 2.0及以上b.MDAC 2.8及以上3.1.2.2安装标签打印程序a.综合帐套选择默认安装(选择适用任何人)安装完毕,运行程序如图b.独立帐套安装参照综合帐套程序安装完毕,运行程序如图3.1.2.3打印机设置A.重命名标签打印机为BarCodePrinterA1.开始\设置\打印机和传真,点击打开"打印机和传真"A2.选择条码打印机,右键点击菜单重命名打印机名为:BarCodePrinter(注:区分大小写)B.新建FIFO标签纸张类型并设为首选项,B1.选择打印机,点击右键选择打印首选项,如下图选择Customize,如下图W*H=80mm*60mm左边距设置为2mm页面设置名称为FIFO 点击"New",新建FIFO标签类型(若存在则修改),参数设置如上图。

【博文连载】CY7C68013同步FIFO配置

【博文连载】CY7C68013同步FIFO配置在VIP Mini开发板资料包08_USB_Keil_Project目录下,Bingo 提供了CY7C68013的同步FIFO配置工程,以及其他的一些功能。

软件版本为Keil UVision 4.73.00,C51V95200。

首先介绍一下68013的Slave FIFO,对于CY7C68013的通信接口而言,最主要的有GPIF 与Slave FIFO。

Slave FIFO模式是FX2最常用的模式。

芯片工作于Slave FIFO模式下,该芯片就像一个USB FIFO。

一端接USB口,另外一端就是一个简单的FIFO接口。

USB的数据直接从上位机传递到该FIFO中,用户可以直接用现成的驱动程序和固件程序进行开发,省去了很多熟悉USB协议和驱动开发的工作。

Slave FIFO通过内部的FIFO 乒乓操作,实现数据的实时传输,框图如下所示:在Slave FIFO模式,68013与处理器只需要如下一个信号的链接,通过简单的片选,写入/读取实现,别可以实现数据的双向通信。

全功能接口如下所示:USB_Camera_Demo工程如下所示,我们主要关心的为USB_Camera_Demo.c、intr.c,其他内容Bingo已经完整的整理封装好。

关于同步FIFO的配置,详见USB_Camera_Demo.c,这里给出最重要的几个寄存器的介绍,请同步参照《FX2+TechRefManual》《USB68013_slave_fifo说明文档》寄存器配置手册。

手册Page342如下图所示:其中EF为EMPTY标志,FF为FULL标志:备注:FLAGA = PF;FLAGB = FF;FLAGC = EF;FLAGD = EP2PF,默认由FIFOADDR选择。

基于同步Slave FIFO技术的高速USB数传系统设计

基于同步Slave FIFO技术的高速USB数传系统设计马琦;吉春花;兰兴;王海滨【期刊名称】《单片机与嵌入式系统应用》【年(卷),期】2013(13)7【摘要】给出一种基于“USB2.0 Slave接口芯片+FPGA”架构的高速USB数传系统设计方案.系统以CY7C68013A为USB协议桥、FPGA为逻辑控制单元,优化设计有限状态机实现同步Slave FIFO接口协议,构建了USB数据高速传输通.道,保证了数据传输、处理过程中的可靠性、实时性和高效性;优化了芯片固件加载方式,实现了系统在线自动升级加载功能.经实测,系统的数据传输处理能力平均可达320 Mb/s,接近USB2.0协议规定的极限速率,固件可在1.2s内完成自动加载,使系统具备了快速升级能力.%This article introduces a kind of high speed USB transport system based on the structure of "USB2.0 Slave interface chip + FPGA".The system uses CY7C68013A as USB protocol bridge and FPGA as its control center,and designs optimized finite-state machine to realize synchronous slave FIFO protocol.The USB data high speed transport channel is constructed and the system acquires good performance in real-time processing,transmission reliability and efficiency.At the same time an optimized software loading method is designed to ensure that the system software can be update on line without any manual operation.The test results show that the system can run stably at the average data transfer rate of up to 40 MB/s and the system software can be update automatically in 1.2 seconds.【总页数】4页(P51-54)【作者】马琦;吉春花;兰兴;王海滨【作者单位】吉尔达集团公司,南通226300;吉尔达集团公司,南通226300;空军工程大学;海军飞行学院【正文语种】中文【中图分类】TP319【相关文献】1.基于DMT技术的测井数传系统设计与仿真 [J], 姚远;余厚全;魏为2.基于光纤光栅传感技术的高速铁路轨道状态远程监测数传系统 [J], 蒋金洲;吕国辉;梁晨;徐玉坡;杜香刚;商绍华3.基于USB2.0的高速同步数据采集系统设计 [J], 周云锋;孙书鹰;王宏4.模拟器中基于Slave FIFO模式USB数传系统设计 [J], 王海滨;刘宝华;解传军;孔挺5.基于FPGA的遥感高速图像数传系统设计 [J], 徐磊;崔雪楠因版权原因,仅展示原文概要,查看原文内容请购买。

Slave-FIFO-使用手册

红色飓风III开发板USB2FPGA实验指导Red Logic目录第一章FX2特性介绍 (3)1.1介绍………………………………………………………………………。

3 1.2结构………………………………………………………………………。

.3 1.3特征……………………………………………………………………….。

4第二章Slave FIFO传输 (5)2.1概述.................................................................................。

.5 2.2硬件连接.. (5)2.3 Slave FIFO的几种传输方式 (6)2.3.1 同步Slave FIFO写……………………………………………。

62.3.2 同步Slave FIFO读……………………………………………。

92.3.3异步Slave FIFO写……………………………………………。

112.3.4异步Slave FIFO读 (12)第三章寄存器设置..........................................................................。

15 3.1 IFCONFIG..................................................................。

(15)3.2 PINFLAGSAB/CD.........................................................。

...。

16 3.3 FIFORESET.. (17)3.4 FIFOPINPOLAR.........................................................。

......。

18 3.5 EPxCFG..................................................................。

fifo参数说明

fifo参数说明

FIFO(First In First Out)是一种先进先出的数据缓存器,用于数据的缓存或高速异步数据的交互。

以下是FIFO的一些主要参数:

1. 宽度:FIFO的宽度表示每次读写操作的数据位数。

2. 深度:FIFO的深度表示FIFO可以存储的数据量,计算方式为深度=2的宽度位数次方。

3. 空标志:当FIFO为空时,会产生空标志,此时无法进行读操作。

4. 满标志:当FIFO已满时,会产生满标志,此时无法进行写操作。

5. 读写时钟:对于同步FIFO,读写操作使用同一时钟;对于异步FIFO,读写操作使用不同的时钟。

6. 读写地址:FIFO具有自动加一的读写地址,用于数据的读写操作。

7. 计数器:用于产生空满标志,当计数器的值为0时产生空标志,当计数器的值为FIFO深度时产生满标志。

8. 数据宽度:FIFO存储的数据宽度,用于定义数据在FIFO中的位宽。

了解这些参数对于设计和应用FIFO非常重要,它们会影响FIFO的性能和适用性。

同时,根据具体的应用需求,还可以定制其他参数,如数据预取、奇偶校验等。

模拟器中基于Slave FIFO模式USB数传系统设计

模拟器中基于Slave FIFO模式USB数传系统设计王海滨;刘宝华;解传军;孔挺【摘要】在模拟器的设计中,为了使数据能够快速有效地在模拟器的各个模块之间进行高速传递,提出了一种同步Slave FIFO模式高速USB数据传输设计方法,并完成了系统的软硬件设计。

系统以FPGA作为核心逻辑控制单元,优化设计有限状态机实现同步Slave FIFO接口协议,设计了芯片固件程序,实现系统在线自动升级加载功能。

实际测试表明,本系统数据传输能力平均可达40 MB/s,本系统设计可扩展性好,易于修改和移植,能降低模拟器成本。

%In the design of the simulator, in order to have the data conveyed quickly and efficiently among every model of the simulator, this article introduces a kind of high speed USB transport method, and finishes the hardware and software's design. The system uses FPGA as its control center, and designs optimized finite-state machine to realize synchronous slave FIFO protocol, at the same time chip firmware program is designed to ensure that the system software can be update on line without any manual operation. The test results show that the system can run at the average data transfer rate of up to 40MB/s, and this design which has strong expansibility can be changed and easy-to-port. Besides, it can cut down the cost of the simulator.【期刊名称】《电子设计工程》【年(卷),期】2015(000)001【总页数】3页(P134-136)【关键词】模拟器;FPGA;USB2.0;Slave FIFO【作者】王海滨;刘宝华;解传军;孔挺【作者单位】海军航空兵学院辽宁葫芦岛 125001;海军航空兵学院辽宁葫芦岛125001;海军航空兵学院辽宁葫芦岛 125001;海军航空兵学院辽宁葫芦岛125001【正文语种】中文【中图分类】TP319在现代科研、实验、教学、训练中,模拟器起着重要作用,它是一种由计算机实时控制、多系统协调工作、能模拟作战环境的模拟设备[1]。

基恩士fifow指令使用

基恩士fifow指令使用

首先,需要了解FIFO缓存的基本概念。

FIFO缓存是一种先进先出的数据存储方式,其中最先进入缓存的数据最先被读取。

在基恩士PLC中,FIFO缓存通常用于存储一系列的数据,如传感器数据、温度数据等。

FIFOW指令可以用于向FIFO缓存中写入数据或从FIFO缓存中读取数据。

下面是FIFOW指令的语法:

FIFOW “FIFO名称”,数据

其中,“FIFO名称”为FIFO缓存的名称,“数据”为要写入或读取的数据。

如果要向FIFO缓存中写入数据,可以使用以下代码:

FIFOW “FIFO1”,10

这将把数值10写入名为“FIFO1”的FIFO缓存中。

如果要从FIFO 缓存中读取数据,可以使用以下代码:

FIFOW “FIFO1”,D0

这将把从名为“FIFO1”的FIFO缓存中读取的数据存储到D0寄存器中。

需要注意的是,读取操作将从FIFO缓存中删除已读取的数据。

除了FIFOW指令,基恩士PLC还提供了其他操作FIFO缓存的指令,如FIFOCLR(清空FIFO缓存)、FIFOCNT(获取FIFO缓存中的数据数量)等。

总之,FIFOW指令是一种有效的控制和管理基恩士PLC中FIFO 缓存的方法。

通过了解和使用FIFOW指令,可以更好地管理PLC中的

数据,提高系统的稳定性和可靠性。

Cy7c68013 的win7 驱动和SlaveFifo例程

之前用的是xp环境,用的红色飓风开发板,现在自己做的板子,改成了win7系统,可是原来的eZ-USB控制面板不能用了,搜了一下cypress的官方驱动,Cypress Suite USB 3.4.7,可以支持XP和win7系统。

连上后,按照driver文件夹下面的CyUSB.pdf文件,修改Cypress Suite USB 3.4.7\Driver\bin\wlh\x64下面的cyusb.inf文件,用记事本打开,将里面VID_XXXX&PID_XXXX改成VID_04B4&PID_8613(在设备管理器中可以查看属性,看到这两个16进制数),注意别忘了把这几行前面的注释号“;”去掉,否则认为这一行被注释了哦。

下面的文件是我的CY7C68013的inf文件。

这样系统就可以识别到USB设备了。

但是原来的例程SlaveFIFO不能用了,下载.hex文件之后,识别到SlaveFIFO设备,不能装驱动。

由于对这个USB芯片的固件不熟,研究固件编写短期内搞不定。

于是在Cypress 官方网站上找到了例程AN63787,是关于8bit模式下的slavefifo例程,但是我的FPGA配置的是16位模式,明显看到例程中少了一半字节的数据。

下面只能自己改例程了。

首先下载**版的keil uVision2,/f/12062296.html?from=like更改C:\Cypress\Cypress Suite USB 3.4.7\Firmware\Bulkloop下面的keil工程,用原来红色飓风自带的固件源代码配置进行更改,将 bulkloop.c中TD_Init函数用红色飓风如下TD_Init函数替换,void TD_Init( void ){ // Called once at startup//时钟设置//CPUCS = 0x02; //12MHZ CLKOUT ENALBE//CPUCS = 0x0a; //24MHZ CLKOUT ENALBECPUCS = 0x12; //48MHZ CLKOUT ENALBEIFCONFIG =0x43;//使用外部时钟,IFCLK输入不反向SYNCDELAY;EP2CFG=0xA0; //需要设定为四缓冲,每个缓冲区大小为512字节SYNCDELAY;EP4CFG=0x00;SYNCDELAY;EP6CFG=0xE0;SYNCDELAY;EP8CFG=0x00;SYNCDELAY;FIFORESET = 0x80; // activate NAK-ALL to avoid race conditionsSYNCDELAY; // see TRM section 15.14FIFORESET = 0x02; // reset, FIFO 2SYNCDELAY; //FIFORESET = 0x06; // reset, FIFO 6SYNCDELAY; //FIFORESET = 0x00; // deactivate NAK-ALLSYNCDELAY;PINFLAGSAB = 0xE6; // FLAGA - fixed EP6PF, FLAGB - fixed EP6FFSYNCDELAY;PINFLAGSCD = 0xf8; // FLAGC - fixed EP2EF, FLAGD - reservedSYNCDELAY;PORTACFG |= 0x00; //0x40; // SLCS, set alt. func. of PA7 pinSYNCDELAY;FIFOPINPOLAR = 0x00; // all signals active low,SYNCDELAY;OEA|=0x0F;//小于64字节有效//EP6FIFOPFH=0x00; //DEIS PKSTAT PK2 PK1 PK0 0 PFC9 PFC8//EP6FIFOPFL=0x40; //PFC7 PFC6 PFC5 PFC4 PFC3 PFC2 PFC1 PFC0// handle the case where we were already in AUTO mode...EP2FIFOCFG = 0x01; // AUTOOUT=0, WORDWIDE=1SYNCDELAY;EP2FIFOCFG = 0x11; // AUTOOUT=1, WORDWIDE=1SYNCDELAY;EP6FIFOCFG = 0x09; // AUTOIN=1, ZEROLENIN=0, WORDWIDE=1SYNCDELAY;//IO设置PORTCCFG=0x00;PORTECFG=0x00;OEC=0x00;OEE=0xff;//串口初始化// PA3=0;PA0=1;enum_high_speed=FALSE;}编译生成.hex文件,用EZ-USB控制面板下载到USB芯片中,然后提示找到设备Bulkloop Device,自动安装驱动,点击get piples,Pipe: 0 Type: BLK Endpoint: 2 OUT MaxPktSize: 0x200Pipe: 1 Type: BLK Endpoint: 4 OUT MaxPktSize: 0x200Pipe: 2 Type: BLK Endpoint: 6 IN MaxPktSize: 0x200Pipe: 3 Type: BLK Endpoint: 8 IN MaxPktSize: 0x200选择: BLK Endpoint: 6 IN ,点击传输,这是我用24bitAD芯片采集数据的结果,每采集两次,放入3个数据进FIFO,数据正确但是现在传输速度测试的VC6.0程序还不能用,估计还是因为win7的某些不兼容吧,以后再试。

FX2论文:FX2固件SlaveFIFOGPIF数据传输

FX2论文:FX2 固件 Slave FIFO GPIF 数据传输【中文摘要】通用串行总线(USB)是现今最流行的计算机外围接口标准,它具有即插即用,低价位,低能耗,扩展方便等很多的优点。

Cypress公司的EZ-USB FX2是世界上第一款集成了USB 2.0接口的微控制器。

通过集成USB 2.0收发器、SIE(串行接口引擎,Serial Interface Engine)、增强的8051微控制器以及可编程的外部接口于个单片中,Cypress公司为决策者提供了一个真正高效的解决方案以获取产品最快上市的利益。

同时,大规模的可编程逻辑器件FPGA是当今应用最广泛的可编程专用集成电路之一。

本论文首先详细介绍了EZ-USB FX2芯片的结构和特点,进而对基于EZ-USBFX2和FPGA的数据传输系统的设计和实现进行了详细的叙述,在设计和实现之中包括了固件程序的设计,驱动程序,可编程逻辑器件FPGA,并分别使用FX2和FPGA两者连接的两种接口方式(Slave FIFO方式和GPIF方式),最终实现了高速的数据传输。

通过整个数据传输系统的研究,为使用USB 总线和FPGA进行数据采集等更加广泛的应用提供了很好的指导和借鉴。

【英文摘要】Universal Serial Bus(USB) is one of the most popular development in PC peripheral interconnect technology since the introduction of serial and parallel in theearly’B has the advantage of high-speed, hot plug in and play, low price, engrossing less system resource and easy toexpand. EZ-USB FX2 of the company of Cypress is the first interface chip of microcontroller with USB2.0. By integrating the of USB 2.0, SIE (Serial Interface Engine), the microcontroller of enhanced 8051 and a programmable external...【关键词】FX2 固件 Slave FIFO GPIF 数据传输【采买全文】1.3.9.9.38.8.4.8 1.3.8.1.13.7.2.1同时提供论文写作定制和论文发表服务.保过包发.【说明】本文仅为中国学术文献总库合作提供,无涉版权。

fifo使用

【转】同步FIFO和异步FIFO的Verilog实现2011-10-10 10:59:26| 分类:FPGA学习 | 标签:fifo verilog fpga|举报|字号订阅FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

FIFO一般用于不同时钟域之间的数据传输,比如FIFO的一端是AD数据采集,另一端是计算机的PCI总线,假设其AD采集的速率为16位 100K SPS,那么每秒的数据量为100K×16bit=1.6Mbps,而PCI总线的速度为33MHz,总线宽度32bit,其最大传输速率为 1056Mbps,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。

另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而 DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

FIFO的分类根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。

同步FIFO是指读时钟和写时钟为同一个时钟。

在时钟沿来临时同时发生读写操作。

异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

FIFO设计的难点 FIFO设计的难点在于怎样判断FIFO的空/满状态。

为了保证数据正确的写入或读出,而不发生益处或读空的状态出现,必须保证FIFO在满的情况下,不能进行写操作。

在空的状态下不能进行读操作。

怎样判断FIFO的满/空就成了FIFO设计的核心问题。

..................................................................... ....................................................................同步FIFO的Verilog代码之一在modlesim中验证过。

FIFO使用讲解

置为高电平,才能完成芯片的重置。当然重置是指重置所有的内

部指针(读写指针等),输出寄存器和内存(initializes all internal pointers,output registers and memory),要注意输出被 重置了(因为指针被重置了),而不是芯片内存存储的数据被 重置了,也就是这个信号并不会对芯片内部的数据清零。

FIFO一些参数

WIDTH:FIFO芯片一次读写的数据位数 DEEPTH:FIFO芯片可以存储多少个WIDTH位的数。注意Xilinx的IP核FIFO中下标是

从0开始的,也就是0代表存储的第一个数,deepth-1表示最后一个数 读写时钟:这两个时钟可以是相同的,也可以是独立的,依赖于选择什么样的FIFO类型。

第6页,共8页。

其实图中的每个信号的小间隔也可以说明这个问题。

由于读操作与写操作是相同的。这里就不熬述。 有上述两个读写操作,可以给我们这样的启示: 在写程序的时候,一定要合理的利用时钟。比如说每个上升沿进行操作需要一 定的时间,可能会有延时,可以利用多个相同的时钟分别完成操作。另外要合 理的利用时钟的上升沿和下降沿,不能总是利用上升或下降沿,要综合利用。

每有一次读写时钟,在上升沿都会有一次相应的读写操作。

第1页,共8页。

Wr_en:写使能信号,写之前应该设置为1. Rd_en:读使能信号,读之前应该设置为1.

注意,以上两个信号的设置有一定的技巧,后面详解

Rst: 清零信号

FIFO分类:

同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同 时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独

Slave FIFO开发文档

联系QQ:120076915SoEZ-USB2.0(CY7C68013A)开发板SlaveFIFO开发文档Version(1.0)网址:联系QQ:120076915SoEZ-USB2.0(CY7C68013A)开发板SlaveFIFO开发文档目录一、Slave FIFO传输 (3)1.1概述 (3)1.2硬件连接(标准) (3)1.3 Slave FIFO的几种传输方式 (4)1.3.1同步 Slave FIFO写 (4)1.3.2同步 Slave FIFO读: (7)1.3.3异步 Slave FIFO写: (9)1.3.4异步 Slave FIFO读: (10)二、寄存器设置 (12)2.1 IFCONFIG:接口配置寄存器 (12)2.2 PINFLAGS AB/CD:FLAGx引脚配置寄存器 (13)2.3 FIFORESET:端点缓冲区复位寄存器 (14)2.4 FIFOPINPOLAR:控制引脚极性设置寄存器 (14)2.5 EPxCFG:端点 2,4,6,8配置 (15)2. 6 EPxFIFOCFG:端点 FIFO配置寄存器 (16)2.7 EPxAUTOINLENH/L:端点2,4,6,8AUTOIN长度设置(仅 IN端点有效) (17)2.8 EPxFIFOPFH/L:FIFO可编程 PF状态长度设置 (17)2.9 INPKTEND:结束 IN传输 (18)2.10 OUTPKTEND:强行结束 OUT传输寄存器 (18)2.11 EPxFIFOIE和 EPxFIFOIRQ:端点 FIFO中断(INT4) (19)2.12PORTACFG:端口 A配置 (19)2.13 EPxFIFOBCH EPxFIFOBCL:端点 FIFO计数 (20)2.14 EP24\68 FIFOFLAG(SFR AB:SFR AC)和 EPxFIFOFLGS:端点 FIFO状态标志寄存器 (20)2.15其它通用寄存器 (20)2SoEZ-USB2.0(CY7C68013A)开发板SlaveFIFO开发文档一、Slave FIFO传输1.1概述当有一个与FX2LP芯片相连的外部逻辑只需要利用FX2LP作为一个 USB 2.0接口而实现与主机的高速通讯,而它本身又能够提供满足Slave FIFO要求的传输时序,可以做为Slave FIFO 主控制器时,即可考虑用此传输方式。

基恩士fifow指令使用

基恩士fifow指令使用

基恩士fifow指令是一种针对网络游戏加速的工具,使用方法如下:

1. 在电脑打开基恩士fifow软件,并登录账号。

2. 打开你想要加速的游戏,并在基恩士fifow软件中选择该游戏。

3. 点击“启动加速”按钮。

4. 等待软件联网,如果需要更新则更新后重新启动加速。

5. 在游戏中体验加速效果。

使用基恩士fifow指令时需要注意一些事项:

1. 确保你的网络状况良好,否则加速效果会受到影响。

2. 不要在游戏中使用任何外挂、作弊软件,否则可能会被封号。

3. 不要在游戏中进行非法交易,否则可能会涉及到法律问题。

4. 如有任何疑问或意见,可以在官方网站留言或寻求客服帮助。

基恩士fifow指令使用

基恩士fifow指令使用基恩士FIFO指令使用在计算机科学中,FIFO(First In, First Out)是一种常用的队列数据结构,即先进先出。

基恩士(Keinster)是一个虚构的计算机软件公司,他们开发了一种基于FIFO原则的指令集,可以在软件开发过程中提高效率和优化性能。

本文将介绍如何使用基恩士FIFO指令集。

一、了解基恩士FIFO指令集基恩士FIFO指令集是一组用于管理队列数据结构的指令。

它包括入队、出队、获取队首元素和判断队列是否为空等操作。

这些指令可以用于实现多线程、并发编程和事件驱动编程等场景,提高程序的响应性和性能。

二、入队操作入队操作是将一个元素添加到队列的末尾。

在基恩士FIFO指令集中,可以使用push指令来实现入队操作。

指令格式如下:push <element>其中,<element>表示要入队的元素。

三、出队操作出队操作是将队列中的第一个元素移除并返回。

在基恩士FIFO指令集中,可以使用pop指令来实现出队操作。

指令格式如下:pop该指令会将队列中的第一个元素弹出,并将其返回。

四、获取队首元素获取队首元素操作是获取队列中的第一个元素,但不将其移除。

在基恩士FIFO指令集中,可以使用top指令来实现获取队首元素操作。

指令格式如下:top该指令会返回队列中的第一个元素,但不会将其移除。

五、判断队列是否为空判断队列是否为空操作是判断队列中是否还有元素。

在基恩士FIFO 指令集中,可以使用empty指令来实现判断队列是否为空操作。

指令格式如下:empty该指令会返回一个布尔值,表示队列是否为空。

如果队列为空,则返回true;否则返回false。

六、使用示例下面是一个使用基恩士FIFO指令集的示例,实现了一个简单的任务调度器:```python# 初始化一个空队列queue = []# 将任务添加到队列push queue, "Task 1"push queue, "Task 2"push queue, "Task 3"# 判断队列是否为空if empty queue:print("队列为空")else:print("队列不为空")# 获取队首元素task = top queueprint("队首元素为:", task) # 执行任务while not empty queue:task = pop queueprint("执行任务:", task) # 判断队列是否为空if empty queue:print("队列为空")else:print("队列不为空")```以上示例中,我们首先初始化一个空队列,然后将任务依次添加到队列中。

CY7C68013A_Slave_fifo固件心得

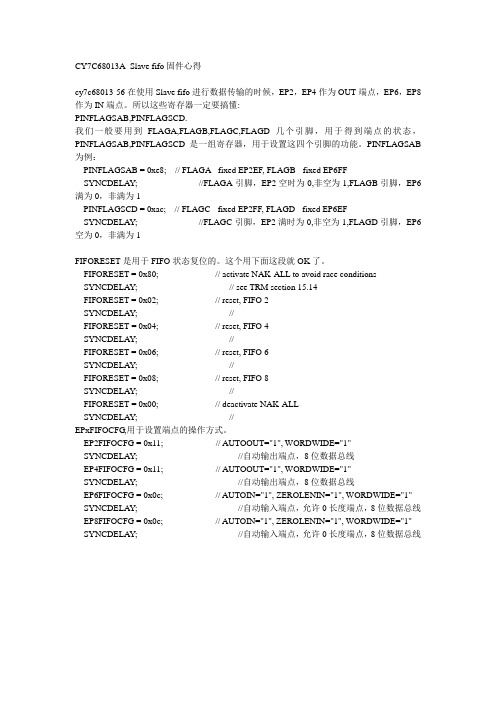

CY7C68013A_Slave fifo固件心得cy7c68013-56在使用Slave fifo进行数据传输的时候,EP2,EP4作为OUT端点,EP6,EP8作为IN端点。

所以这些寄存器一定要搞懂:PINFLAGSAB,PINFLAGSCD.我们一般要用到FLAGA,FLAGB,FLAGC,FLAGD几个引脚,用于得到端点的状态,PINFLAGSAB,PINFLAGSCD是一组寄存器,用于设置这四个引脚的功能。

PINFLAGSAB 为例:PINFLAGSAB = 0xe8; // FLAGA - fixed EP2EF, FLAGB - fixed EP6FF SYNCDELAY; //FLAGA引脚,EP2空时为0,非空为1,FLAGB引脚,EP6满为0,非满为1PINFLAGSCD = 0xac; // FLAGC - fixed EP2FF, FLAGD - fixed EP6EF SYNCDELAY; //FLAGC引脚,EP2满时为0,非空为1,FLAGD引脚,EP6空为0,非满为1FIFORESET是用于FIFO状态复位的。

这个用下面这段就OK了。

FIFORESET = 0x80; // activate NAK-ALL to avoid race conditions SYNCDELAY; // see TRM section 15.14FIFORESET = 0x02; // reset, FIFO 2SYNCDELAY; //FIFORESET = 0x04; // reset, FIFO 4SYNCDELAY; //FIFORESET = 0x06; // reset, FIFO 6SYNCDELAY; //FIFORESET = 0x08; // reset, FIFO 8SYNCDELAY; //FIFORESET = 0x00; // deactivate NAK-ALLSYNCDELAY; //EPxFIFOCFG,用于设置端点的操作方式。

slaveFIFO模式下USB和FPGA的数据通信

slaveFIFO模式下USB和FPGA的数据通信作者:周莹邹连英来源:《中国新通信》2014年第10期【摘要】本文介绍了基于USB2.0的EZ-USB FX2系列接口芯片之一CY7C68013,为解决PC与FPGA的高速数据传输,利用芯片的SlaveFIFO主从模式将CIS传感器采集的纸币数据准确无损地传给PC机,利用verilog HDL语言在FPGA中产生相应的控制信号,最终实现对数据的快速传输,在上位机得到CIS采集的清晰的纸币画面。

【关键词】 FPGA CY7C68013 SlaveFIFO模式 USB 纸币图像数据一、引言USB全称为通用串行总线,是一种作为外围设备与计算机之间通信的标准接口,具有可热插拔、即插即用、快速、双向、以及价格低廉等特性,获得了越来越多用户的接受。

本文使用支持USB2.0协议的CY7C68013接口芯片,作为FPGA与PC之间的传输接口。

二、系统总设计本文利用FPGA芯片作为系统的逻辑控制核心,控制CIS传感器采集纸币数据,并通过A/D将数字信号最终存入SDRAM。

USB接口与上位机通信,只需将SDRAM中的数据通过USB传输到上位机显示。

整体设计如图1所示:2.1 USB枚举过程当集线器端口悬空时,被电阻下拉,当设备插入到集线器时,接了上拉电阻那条数据线的电压对集线器来说,是一个高电平信号,集线器检测到此状态后,报告给USB主控制器,此时便检测到设备。

USB的枚举过程是主机获取USB设备信息的过程。

(1)USB主机检测到有设备插入后对其复位,使用缺省地址发送获取设备描述符的标准请求,主机获取到一个数据包的设备描述符并确认无误后,开始进入设置地址阶段。

(2)USB主机向缺省地址发送设置地址的请求,设备受到该请求后,直接进入到等待主机输入令牌包,主机确认收到后发送ACK,设备收到ACK之后开始启用新地址。

以后主机就通过这个唯一的地址访问该设备。

(3)主机使用新地址再次获取配置描述符。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

红色飓风III开发板USB2FPGA实验指导RedLogic目录第一章FX2特性介绍 (3)1.1介绍 (3)1.2结构 (3)1.3特征 (4)第二章SlaveFIFO传输 (5)2.1概述 (5)2.2硬件连接 (5)2.3SlaveFIFO的几种传输方式 (6)2.3.1同步SlaveFIFO 写 (6)2.3.2同步SlaveFIFO 读 (9)2.3.3异步SlaveFIFO 写 (11)2.3.4异步SlaveFIFO 读 (12)第三章寄存器设置 (15)3.1IFCONFIG (15)3.2PINFLAGSAB/CD (16)3.3FIFORESET (17)3.4FIFOPINPOLAR (18)3.5EPxCFG…………………………………………………… (18)3.6EPxFIFOCFG (19)3.7EPxAUTOINLENH/L (20)3.8EPxFIFOPFH/L (21)3.9INPKTEND (22)3.10OUTPKTEND (22)3.11EPxFIFOIE和EPxFIFOIRQ (22)3.12PORTACFG (23)3.13EPxFIFOBCHEPxFIFOBCL (23)3.14EP24\68FIFOFLAG (24)3.15其它通用寄存器 (25)第四章同步slavefifo测试操作指南 (26)4.1安装软件包 (26)4.2同步写FIFO测试 (26)4.3同步读FIFO测试 (30)第五章红色飓风II开发板USB2FPGA软件设计 (33)5.168013固件程序设计 (33)5.2FPGA源代码设计 (35)第六章USB2FPGA硬件原理图 (37)第七章改板后注意的问题 (37)附录1版本历史 (3)9一.FX2特性介绍1.1介绍CypressSemiconductor公司的EZ-USBFX2是世界上第一款集成USB2.0的微处理器,它集成了USB2.0收发器、SIE(串行接口引擎)、增强的8051微控制器和可编程的外围接口。

FX2这种独创性结构可使数据传输率达到56Mbytes/s,即USB2.0允许的最大带宽。

在FX2中,智能SIE可以硬件处理许多USB1.1和USB2.0协议,从而减少了开发时间和确保了USB的兼容性。

GPIF(GeneralProgrammableInterface)和主/从端点FIFO(8位或16位数据总线)为ATA、UTOPIA、EPP、PCMCIA和DSP等提供了简单和无缝连接接口。

1.2结构CY7C68013结构图如图1所示。

它有三种封装形式:56SSOP,100TQFP和128TQFP。

1.3特征:★内嵌480MBit/s的收发器,锁相环PLL,串行接口引擎SIE ——集成了整个USB2.0协议的物理层。

★为适应USB2.0的480MBit/s的速率,FIFO端点可配置成2,3,4个缓冲区。

★内嵌可工作在48MHz的增强型8051,它具有以下特征:-具有256Byte的寄存器空间,两个串口,三个定时器,两个数据指针。

-四个机器周期(工作在48MHz下时为83.3ns)即组成一个指令周期。

-特殊功能寄存器(包括I/O口控制寄存器)可高速访问。

-应用USB向量中断,具有极短的ISR响应时间。

-只用作USB事务管理,控制,不参与数据传输,较好地解决了USB高速模式的带宽问题。

★“软配置”——USB固件可由USB总线下载,片上不需集成ROM。

★拥有四个FIFO接口,可工作在内部或外部时钟下。

端点和FIFO接口的应用使外部逻辑和USB总线可高速连接。

★内嵌通用可编程接口GPIF,它是一个状态机,可充当主控制器,提供外部逻辑和USB总线的“无胶粘贴”。

★一种单片USB2.0外设解决方案,不需要外部的协议物理层,FX2把所有的功能集成在一个芯片上。

二、SlaveFIFO传输2.1概述当有一个与FX2芯片相连的外部逻辑只需要利用FX2做为一个USB2.0接口而实现与主机的高速通讯,而它本身又能够提供满足SlaveFIFO要求的传输时序,可以做为SlaveFIFO主控制器时,即可考虑用此传输方式。

SlaveFIFO传输的示意图如下:在这种方式下,FX2内嵌的8051固件的功能只是配置SlaveFIFO 相关的寄存器以及控制FX2何时工作在SlaveFIFO 模式下。

一旦8051固件将相关的寄存器配置完毕,且使自身工作在SlaveFIFO 模式下后,外部逻辑(如FPGA )即可按照SlaveFIFO 的传输时序,高速与主机进行通讯,而在通讯过程中不需要8051固件的参与。

2.2硬件连接(标准)在SlaveFIFO 方式下,外部逻辑与FX2的连接信号图如下: IFCLK :FX2输出的时钟,可做为通讯的同步时钟;FLAGA ,FLAGB ,FLAGC ,FLAGD :FX2输出的FIFO 状态信息,如满,空等;SLCS :FIFO 的片选信号,外部逻辑控制,当SLCS 输出高时,不可进行数据传输;SLOE :FIFO 输出使能,外部逻辑控制,当SLOE 无效时,数据线不输出有效数据;SLRD:FIFO读信号,外部逻辑控制,同步读时,FIFO指针在SLRD有效时的每个IFCLK的上升沿递增,异步读时,FIFO读指针在SLRD的每个有效—无效的跳变沿时递增;SLWR:FIFO写信号,外部逻辑控制,同步写时,在SLWR有效时的每个IFCLK的上升沿时数据被写入,FIFO指针递增,异步写时,在SLWR的每个有效—无效的跳变沿时数据被写入,FIFO 写指针递增;PKTEND:包结束信号,外部逻辑控制,在正常情况下,外部逻辑向FX2的FIFO中写数,当写入FIFO端点的字节数等于FX2固件设定的包大小时,数据将自动被打成一包进行传输,但有时外部逻辑可能需要传输一个字节数小于FX2固件设定的包大小的包,这时,它只需在写入一定数目的字节后,声明此信号,此时FX2硬件不管外部逻辑写入了多少字节,都自动将之打成一包进行传输;FD[15:0]:数据线;FIFOADR[1:0]:选择四个FIFO端点的地址线,外部逻辑控制。

2.3SlaveFIFO的几种传输方式2.3.1同步SlaveFIFO写同步SlaveFIFO写的标准连接图如下:同步SlaveFIFO写的标准时序如下:IDLE:当写事件发生时,进状态1;状态1:使FIFOADR[1:0]指向INFIFO,进状态2;状态2:如FIFO满,在本状态等待,否则进状态3;状态3:驱动数据到数据线上,使SLWR有效,持续一个IFCLK 周期,进状态4;状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如下:几种情况的时序图示意如下(FULL,EMPTY,SLWR,PKTEND 均假定低有效):图示FIFO中本来没有数据,外部逻辑写入第一个数据时的情况。

图示假定FX2设定包大小为512字节,外部逻辑向FIFO端点中写入的数据达512字节时的情况。

此时FX2硬件自动将已写入的512字节打成一包准备进行传输,这个动作就和在普通传输中,FX2固件向FIFO端点中写入512字节后,把512这个数写入EPxBC中一样,只不过这个过程是由硬件自动完成的。

在这里可以看出“FX2固件不参与数据传输过程”的含义了。

外部逻辑只须按上面的时序图所示的时序向FIFO端点中一个一个字节(或字)地写数,写到一定数量,FX2硬件自动将数据打包传输,这一切均不需固件的参与,由此实现高速数据传输。

图示的是FIFO端点被写满时的情况。

2.3.2同步SlaveFIFO读:同步SlaveFIFO读的标准连接图如下:同步SlaveFIFO读的标准时序如下:IDLE:当读事件发生时,进状态1;状态1:使FIFOADR[1:0]指向OUTFIFO,进状态2;状态2:使SLOE有效,如FIFO空,在本状态等待,否则进状态3;状态3:从数据线上读数,使SLRD有效,持续一个IFCLK周期,以递增FIFO读指针,进状态4;状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如下:几种情况的时序图示意如下(FULL,EMPTY,SLRD,SLOE均假定低有效):图示正常情况时的时序。

图示FIFO被读空时的情况。

2.3.3异步SlaveFIFO写:异步SlaveFIFO写的标准连接图如下:异步SlaveFIFO写的标准时序如下:IDLE:当写事件发生时,进状态1;状态1:使FIFOADR[1:0]指向INFIFO,进状态2;状态2:如FIFO满,在本状态等待,否则进状态3;状态3:驱动数据到数据线上,使SLWR有效,再无效,以使FIFO写指针递增,进状态4;状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如下:几种情况的时序图示意如下(FULL,EMPTY,SLWR,PKTEND 均假定低有效):图示FIFO中本来没有数据,外部逻辑写入第一个数据时的情况。

2.3.4异步SlaveFIFO读:异步SlaveFIFO读的标准连接图如下:异步SlaveFIFO读的标准时序如下:IDLE:当读事件发生时,进状态1;状态1:使FIFOADR[1:0]指向OUTFIFO,进状态2;状态2:如FIFO空,在本状态等待,否则进状态3;状态3:使SLOE有效,使SLRD有效,从数据线上读数,再使SLRD无效,,以递增FIFO读指针,再使SLOE无效,进状态4;状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如下:几种情况的时序图示意如下(FULL,EMPTY,SLRD,SLOE均假定低有效):图示正常情况时的时序。

三、寄存器设置slavefifo模式下常用寄存器3.1IFCONFIG(E601):接口配置寄存器IFCLKSRC:FIFO时钟内部/外部时钟源选择,0外部时钟源,1内部时钟源。

3048MHZ:如选择内部时钟,30MHz/48MHz频率选择,0IFCLK时钟30M,1IFCLK时钟48M。

IFCLKOE:IFCLK时钟输出使能,0关闭,1打开。

IFCLKPOL:IFCLK输出反转使能,0不反转,1反转。

ASYNC:SlaveFIFO同步/异步工作方式选择,0同步,1异步。

GSTATE:选择是否将GSTATE[2:0]在PORTE[2:0]输出,0关闭,1使能。

IFCFG1:0:FX2I/O端口模式选择,也既是上面所说的FX2与外部逻辑传输方式的选择。

00:I/O方式;01:reserved;10:SlaveFIFO方式;11:GPIF方式。

3.2PINFLAGSAB/CD(E602:E603):FLAGx引脚配置寄存器FLAGA,FLAGB,FLAGC,FLAGD反映FIFO状态选择。