Extensions allowing the Integer Pair Representation

Blast使用方法攻略

Blast使⽤⽅法攻略结果12列Query id,Subject id,% identity,alignment length,mismatches,gap openings,q. start,q. end,s. start,s. end,e-value,bit scoreBlast,全称Basic Local Alignment Search Tool,即"基于局部⽐对算法的搜索⼯具",由Altschul等⼈于1990年发布。

Blast能够实现⽐较两段核酸或者蛋⽩序列之间的同源性的功能,它能够快速的找到两段序列之间的同源序列并对⽐对区域进⾏打分以确定同源性的⾼低。

Blast的运⾏⽅式是先⽤⽬标序列建数据库(这种数据库称为database,⾥⾯的每⼀条序列称为subject),然后⽤待查的序列(称为 query)在database中搜索,每⼀条query与database中的每⼀条subject都要进⾏双序列⽐对,从⽽得出全部⽐对结果。

Blast是⼀个集成的程序包,通过调⽤不同的⽐对模块,blast实现了五种可能的序列⽐对⽅式:blastp:蛋⽩序列与蛋⽩库做⽐对,直接⽐对蛋⽩序列的同源性。

blastx:核酸序列对蛋⽩库的⽐对,先将核酸序列翻译成蛋⽩序列(根据相位可以翻译为6种可能的蛋⽩序列),然后再与蛋⽩库做⽐对。

blastn:核酸序列对核酸库的⽐对,直接⽐较核酸序列的同源性。

tblastn:蛋⽩序列对核酸库的⽐对,将库中的核酸翻译成蛋⽩序列,然后进⾏⽐对。

tblastx:核酸序列对核酸库在蛋⽩级别的⽐对,将库和待查序列都翻译成蛋⽩序列,然后对蛋⽩序列进⾏⽐对。

Blast提供了核酸和蛋⽩序列之间所有可能的⽐对⽅式,同时具有较快的⽐对速度和较⾼的⽐对精度,因此在常规双序列⽐对分析中应⽤最为⼴泛。

可以毫不夸张的说,blast是做⽐较基因组学乃⾄整个⽣物信息学研究所必须掌握的⼀种⽐对⼯具。

AD820

Single-Supply, Rail-to-Rail,Low Power FET-Input Op AmpAD820 Rev. EInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, N orwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©1996–2007 Analog Devices, Inc. All rights reserved.FEATURESTrue single-supply operationOutput swings rail-to-railInput voltage range extends below ground Single-supply capability from 5 V to 36 V Dual-supply capability from ±2.5 V to ±18 V Excellent load driveCapacitive load drive up to 350 pF Minimum output current of 15 mA Excellent ac performance for low power800 μA maximum quiescent currentUnity gain bandwidth: 1.8 MHzSlew rate of 3.0 V/μsExcellent dc performance800 μV maximum input offset voltage1 μV/°C typical offset voltage drift25 pA maximum input bias currentLow noise13 nV/√Hz @ 10 kHz APPLICATIONSBattery-powered precision instrumentation Photodiode preampsActive filters12- to 14-bit data acquisition systems Medical instrumentationLow power references and regulators PIN CONFIGURATIONS NC = NO CONNECTNULL–IN+IN–V SNC+V SV OUTNULL873-1 Figure 1. 8-Lead PDIPNC = NO CONNECTNC–IN+IN–V SNC+V SV OUTNC873-2Figure 2. 8-Lead SOICGENERAL DESCRIPTIONThe AD820 is a precision, low power FET input op amp that can operate from a single supply of 5.0 V to 36 V, or dual supplies of ±2.5 V to ±18 V. It has true single-supply capability, with an input voltage range extending below the negative rail, allowing the AD820 to accommodate input signals below ground in the single-supply mode. Output voltage swing extends to within10 mV of each rail, providing the maximum output dynamic range. Offset voltage of 800 μV maximum, offset voltage drift of1 μV/°C, typical input bias currents below 25 pA, and low input voltage noise provide dc precision with source impedances upto 1 GΩ. 1.8 MHz unity gain bandwidth, −93 dB THD at10 kHz, and 3 V/μs slew rate are provided for a low supply current of 800 μA. The AD820 drives up to 350 pF of direct capacitive load and provides a minimum output current of15 mA. This allows the amplifier to handle a wide range of load conditions. This combination of ac and dc performance, plus the outstanding load drive capability, results in an exceptionally versatile amplifier for the single-supply user. The AD820 is available in two performance grades. The A and B grades are rated over the industrial temperature range of−40°C to +85°C. The AD820 is offered in two 8-lead package options: plastic DIP (PDIP) and surface mount (SOIC).873-4 Figure 3. Gain of 2 Amplifier; V S =5 V, 0 V, V IN = 2.5 V Sine Centered at 1.25 VAD820Rev. E | Page 2 of 24TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 Pin Configurations...........................................................................1 General Description.........................................................................1 Revision History...............................................................................2 Specifications.....................................................................................3 Absolute Maximum Ratings............................................................9 ESD Caution..................................................................................9 Typical Performance Characteristics...........................................10 Application Notes...........................................................................16 Input Characteristics..................................................................16 Output Characteristics...............................................................17 Offset Voltage Adjustment............................................................18 Applications.....................................................................................19 Single Supply Half-Wave and Full-Wave Rectifiers...............19 4.5 V Low Dropout, Low Power Reference.............................19 Low Power 3-Pole Sallen Key Low-Pass Filter.......................20 Outline Dimensions.......................................................................21 Ordering Guide.. (22)REVISION HISTORY2/07—Rev. D to Rev. EUpdated Format..................................................................Universal Updated Outline Dimensions.......................................................21 Changes to the Ordering Guide. (22)5/02—Rev. C to Rev. DChange to SOIC Package (R-8) Drawing....................................15 Edits to Features................................................................................1 Edits to Product Description..........................................................1 Delete Specifications for AD820A-3 V..........................................5 Edits to Ordering Guide..................................................................6 Edits to Typical Performance Characteristics. (8)AD820Rev. E | Page 3 of 24SPECIFICATIONSV S = 0 V , 5 V @ T A = 25°C, V CM = 0 V , V OUT = 0.2 V , unless otherwise noted. Table 1.AD820A AD820B Parameter Conditions Min Typ Max Min Typ Max Unit DC PERFORMANCE Initial Offset 0.1 0.8 0.1 0.4 mV Maximum Offset over Temperature 0.5 1.2 0.5 0.9 mV Offset Drift 2 2 μV/°C Input Bias Current V CM = 0 V to 4 V 2 25 2 10 pA at T MAX 0.5 5 0.5 2.5 nA Input Offset Current 2 20 2 10 pA at T MAX 0.5 0.5 nA Open-Loop Gain V OUT = 0.2 V to 4 V T MIN to T MAX R L = 100 kΩ 400 1000 500 1000 V/mV 400 400 V/mV T MIN to T MAX R L = 10 kΩ 80 150 80 150 V/mV 80 80 V/mV T MIN to T MAX R L = 1 kΩ 15 30 15 30 V/mV 10 10 V/mV NOISE/HARMONIC PERFORMANCE Input Voltage Noise 0.1 Hz to 10 Hz 2 2 μV p-p f = 10 Hz 25 25 nV/√Hz f = 100 Hz 21 21 nV/√Hz f = 1 kHz 16 16 nV/√Hz f = 10 kHz 13 13 nV/√Hz Input Current Noise 0.1 Hz to 10 Hz 18 18 fA p-p f = 1 kHz 0.8 0.8 fA/√Hz Harmonic Distortion R L = 10 kΩ to 2.5 V f = 10 kHz V OUT = 0.25 V to 4.75 V −93 −93 dB DYNAMIC PERFORMANCE Unity Gain Frequency 1.8 1.8 MHz Full Power Response V OUT p-p = 4.5 V 210 210 kHz Slew Rate 3 3 V/μs Settling Time to 0.1% V OUT = 0.2 V to 4.5 V 1.4 1.4 μs to 0.01% 1.8 1.8 μs INPUT CHARACTERISTICSCommon-Mode Voltage Range 1−0.2 +4 –0.2 +4 V T MIN to T MAX −0.2 +4 –0.2 +4 V CMRR V CM = 0 V to 2 V 66 80 72 80 dB T MIN to T MAX 66 66 dB Input ImpedanceDifferential 1013||0.5 1013||0.5 Ω||pF Common Mode 1013||2.8 1013||2.8 Ω||pFAD820Rev. E | Page 4 of 24AD820A AD820B Parameter Conditions Min Typ Max Min Typ Max Unit OUTPUT CHARACTERISTICSOutput Saturation Voltage 2V OL − V EE I SINK = 20 μA 5 7 5 7 mV T MIN to T MAX 10 10 mV V CC − V OH I SOURCE = 20 μA 10 14 10 14 mV T MIN to T MAX 20 20 mV V OL − V EE I SINK = 2 mA 40 55 40 55 mV T MIN to T MAX 80 80 mV V CC − V OH I SOURCE = 2 mA 80 110 80 110 mV T MIN to T MAX 160 160 mV V OL − V EE I SINK = 15 mA 300 500 300 500 mV T MIN to T MAX 1000 1000 mV V CC − V OH I SOURCE = 15 mA 800 1500 800 1500 mV T MIN to T MAX 1900 1900 mV Operating Output Current 15 15 mA T MIN to T MAX 12 12 mA Short-Circuit Current 25 25 mA Capacitive Load Drive 350 350 pF POWER SUPPLY Quiescent Current T MIN to T MAX 620 800 620 800 μA Power Supply Rejection V S + = 5 V to 15 V 70 80 66 80 dB T MIN to T MAX 70 66 dB1This is a functional specification. Amplifier bandwidth decreases when the input common-mode voltage is driven in the range (+ V S – 1 V) to +V S . Common-mode error voltage is typically less than 5 mV with the common-mode voltage set at 1 V below the positive supply. 2V OL − V EE is defined as the difference between the lowest possible output voltage (V OL ) and the minus voltage supply rail (V EE ). V CC − V OH is defined as the difference between the highest possible output voltage (V OH ) and the positive supply voltage (V CC ).AD820Rev. E | Page 5 of 24V S = ±5 V @ T A = 25°C, V CM = 0 V , V OUT = 0 V , unless otherwise noted. Table 2.AD820A AD820B Parameter Conditions Min Typ Max Min Typ Max Unit DC PERFORMANCE Initial Offset 0.1 0.8 0.3 0.4 mV Maximum Offset over Temperature 0.5 1.5 0.5 1 mV Offset Drift 2 2 μV/°C Input Bias Current V CM = –5 V to 4 V 2 25 2 10 pA at T MAX 0.5 5 0.5 2.5 nA Input Offset Current 2 20 2 10 pA at T MAX 0.5 0.5 nA Open-Loop Gain V OUT = 4 V to –4 V R L = 100 kΩ 400 1000 400 1000 V/mV T MIN to T MAX 400 400 V/mV R L = 10 kΩ 80 150 80 150 V/mV T MIN to T MAX 80 80 V/mV R L = 1 kΩ 20 30 20 30 V/mV T MIN to T MAX 10 10 V/mV NOISE/HARMONIC PERFORMANCE Input Voltage Noise 0.1 Hz to 10 Hz 2 2 μV p-p f = 10 Hz 25 25 nV/√Hz f = 100 Hz 21 21 nV/√Hz f = 1 kHz 16 16 nV/√Hz f = 10 kHz 13 13 nV/√Hz Input Current Noise 0.1 Hz to 10 Hz 18 18 fA p-p f = 1 kHz 0.8 0.8 fA/√Hz Harmonic Distortion R L = 10 kΩ f = 10 kHz V OUT = ±4.5 V −93 −93 dB DYNAMIC PERFORMANCE Unity Gain Frequency 1.9 1.8 MHz Full Power Response V OUT p-p = 9 V 105 105 kHz Slew Rate 3 3 V/μs Settling Time to 0.1% V OUT = 0 V to ±4.5 V 1.4 1.4 μs to 0.01% 1.8 1.8 μs INPUT CHARACTERISTICSCommon-Mode Voltage Range 1−5.2 +4 −5.2 +4 V T MIN to T MAX −5.2 +4 −5.2 +4 V CMRR V CM = −5 V to +2 V 66 80 72 80 dB T MIN to T MAX 66 66 dB Input ImpedanceDifferential 1013||0.5 1013||0.5 Ω||pF Common Mode 1013||2.8 1013||2.8 Ω||pFAD820Rev. E | Page 6 of 24AD820A AD820B Parameter Conditions Min Typ Max Min Typ Max Unit OUTPUT CHARACTERISTICSOutput Saturation Voltage 2V OL − V EE I SINK = 20 μA 5 7 5 7 mV T MIN to T MAX 10 10 mV V CC − V OH I SOURCE = 20 μA 10 14 10 14 mV T MIN to T MAX 20 20 mV V OL − V EE I SINK = 2 mA 40 55 40 55 mV T MIN to T MAX 80 80 mV V CC − V OH I SOURCE = 2 mA 80 110 80 110 mV T MIN to T MAX 160 160 mV V OL − V EE I SINK = 15 mA 300 500 300 500 mV T MIN to T MAX 1000 1000 mV V CC − V OH I SOURCE = 15 mA 800 1500 800 1500 mV T MIN to T MAX 1900 1900 mV Operating Output Current 15 15 mA T MIN to T MAX 12 12 mA Short-Circuit Current 30 30 mA Capacitive Load Drive 350 350 pF POWER SUPPLY Quiescent Current T MIN to T MAX 650 800 620 800 μA Power Supply Rejection V S + = 5 V to 15 V 70 80 70 80 dB T MIN to T MAX 70 70 dB1This is a functional specification. Amplifier bandwidth decreases when the input common-mode voltage is driven in the range (+ V S – 1 V) to +V S . Common-mode error voltage is typically less than 5 mV with the common-mode voltage set at 1 V below the positive supply. 2V OL − V EE is defined as the difference between the lowest possible output voltage (V OL ) and the minus voltage supply rail (V EE ). V CC − V OH is defined as the difference between the highest possible output voltage (V OH ) and the positive supply voltage (V CC ).AD820Rev. E | Page 7 of 24V S = ±15 V @ T A = 25°C, V CM = 0 V , V OUT = 0 V , unless otherwise noted. Table 3.AD820A AD820B Parameter Conditions Min Typ Max Min Typ Max Unit DC PERFORMANCE Initial Offset 0.4 2 0.3 1.0 mV Maximum Offset over Temperature 0.5 3 0.5 2 mV Offset Drift 2 2 μV/°C Input Bias Current V CM = 0 V 2 25 2 10 pA V CM = −10 V 40 40 pA at T MAX V CM = 0 V 0.5 5 0.5 2.5 nA Input Offset Current 2 20 2 10 pA at T MAX 0.5 0.5 nA Open-Loop Gain V OUT = +10 V to –10 V R L = 100 kΩ 500 2000 500 2000 V/mV T MIN to T MAX 500 500 V/mV R L = 10 kΩ 100 500 100 500 V/mV T MIN to T MAX 100 100 V/mV R L = 1 kΩ 30 45 30 45 V/mV T MIN to T MAX 20 20 V/mV NOISE/HARMONIC PERFORMANCE Input Voltage Noise 0.1 Hz to 10 Hz 2 2 μV p-p f = 10 Hz 25 25 nV/√Hz f = 100 Hz 21 21 nV/√Hz f = 1 kHz 16 16 nV/√Hz f = 10 kHz 13 13 nV/√Hz Input Current Noise 0.1 Hz to 10 Hz 18 18 fA p-p f = 1 kHz 0.8 0.8 fA/√Hz Harmonic Distortion R L = 10 kΩ f = 10 kHz V OUT = ±10 V −85 −85 dB DYNAMIC PERFORMANCE Unity Gain Frequency 1.9 1.9 MHz Full Power Response V OUT p-p = 20 V 45 45 kHz Slew Rate 3 3 V/μs Settling Time to 0.1% V OUT = 0 V to ±10 V 4.1 4.1 μs to 0.01% 4.5 4.5 μs INPUT CHARACTERISTICS Common-Mode Voltage Range 1 −15.2 +14 −15.2 +14 V T MIN to T MAX −15.2 +14 −15.2 +14 V CMRR V CM = –15 V to +12 V 70 80 74 90 dB T MIN to T MAX 70 74 dB Input Impedance Differential 1013||0.5 1013||0.5 Ω||pF Common Mode 1013||2.8 1013||2.8 Ω||pFAD820Rev. E | Page 8 of 24AD820A AD820B Parameter Conditions Min Typ Max Min Typ Max Unit OUTPUT CHARACTERISTICS Output Saturation Voltage 2 V OL − V EE I SINK = 20 μA 5 7 5 7 mV T MIN to T MAX 10 10 mV V CC − V OH I SOURCE = 20 μA 10 14 10 14 mV T MIN to T MAX 20 20 mV V OL − V EE I SINK = 2 mA 40 55 40 55 mV T MIN to T MAX 80 80 mV V CC − V OH I SOURCE = 2 mA 80 110 80 110 mV T MIN to T MAX 160 160 mV V OL − V EE I SINK = 15 mA 300 500 300 500 mV T MIN to T MAX 1000 1000 mV V CC − V OH I SOURCE = 15 mA 800 1500 800 1500 mV T MIN to T MAX 1900 1900 mV Operating Output Current 20 20 mA T MIN to T MAX 15 15 mA Short-Circuit Current 45 45 mA Capacitive Load Drive 350 350 POWER SUPP L Y Quiescent Current T MIN to T MAX 700 900 700 900 μA Power Supply Rejection V S + = 5 V to 15 V 70 80 70 80 dB T MIN to T MAX 70 70 dB1This is a functional specification. Amplifier bandwidth decreases when the input common-mode voltage is driven in the range (+ V S – 1 V) to +V S . Common-mode error voltage is typically less than 5 mV with the common-mode voltage set at 1 V below the positive supply. 2V OL − V EE is defined as the difference between the lowest possible output voltage (V OL ) and the minus voltage supply rail (V EE ). V CC − V OH is defined as the difference between the highest possible output voltage (V OH ) and the positive supply voltage (V CC ).AD820Rev. E | Page 9 of 24ABSOLUTE MAXIMUM RATINGSTable 4.Parameter Rating Supply Voltage ±18 VInternal Power Dissipation 1Plastic DIP (N) 1.6 W SOIC (R) 1.0 W Input Voltage (+V S + 0.2 V) to −(20 V + V S ) Output Short-Circuit Duration Indefinite Differential Input Voltage ±30 V Storage Temperature Range N −65°C to +125°C R −65°C to +150°C Operating Temperature Range AD820A/B −40°C to +85°C Lead Temperature 260°C (Soldering 60 sec)18-lead plastic DIP package: θJA = 90°C/W 8-lead SOIC package: θJA = 160°C/WStresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ESD CAUTIONAD820Rev. E | Page 10 of 24TYPICAL PERFORMANCE CHARACTERISTICS500–0.50.5OFFSET VOLTAGE (mV)N U M B E R O F U N I T S00873-00540302010–0.4–0.3–0.2–0.100.10.20.30.4Figure 4. Typical Distribution of Offset Voltage (248 Units)480–1010OFFSET VOLTAGE DRIFT (µV/ºC)% I N B I N00873-006403224168–8–6–4–202468Figure 5. Typical Distribution of Offset Voltage Drift (120 Units) 500010INPUT BIAS CURRENT (pA)N U M B E R O F U N I T S00873-00745403530252015105123456789Figure 6. Typical Distribution of Input Bias Current (213 Units)5–5–55COMMON-MODE VOLTAGE (V)I N P U T B I A S C U R R E N T (p A )00873-008–4–3–2–101234Figure 7. Input Bias Current vs. Common-Mode Voltage;V S = +5 V, 0 V and V S = ±5 V1k0.1–1616COMMON-MODE VOLTAGE (V)I N P U T B I A S C U R R E N T (p A )00873-009110100–12–8–404812Figure 8. Input Bias Current vs. Common-Mode Voltage; V S = ±15 V100k0.120140TEMPERATURE (ºC)I N P U T B I A S C UR R E N T (p A )1101001k10k00873-010406080100120Figure 9. Input Bias Current vs. Temperature; V S = 5 V, V CM = 0 V10M10k 100100k LOAD RESISTANCE (Ω)O P E N -L O O P G A I N (V /V )00873-0111k10k 100k1MFigure 10. Open-Loop Gain vs. Load Resistance10M10k –60140TEMPERATURE (ºC)O P E N -L O O P G A I N (V /V )00873-012100k1M–40–2020406080100120Figure 11. Open-Loop Gain vs. Temperature 300–300OUTPUT VOLTAGE (V)I N P U T V O L T A G E (µV )00873-013200100–100–200Figure 12. Input Error Voltage vs. Output Voltage for Resistive Loads40–403OUTPUT VOLTAGE FROM RAILS (mV)I N P U T V O LT A G E (µV )0000873-014200–2060120180240Figure 13. Input Error Voltage vs. Output Voltage within 300 mV of EitherSupply Rail for Various Resistive Loads; V S = ±5 V1k111FREQUENCY (Hz)I N P U T V O L T A G E N O I S E (n V /√H z )0k00873-015101001k 10100Figure 14. Input Voltage Noise vs. Frequency–40–110100100kFREQUENCY (Hz)T H D (d B )00873-0161k 10k–50–60–70–80–90–100Figure 15. Total Harmonic Distortion vs. Frequency00873-017100–201010M FREQUENCY (Hz)O P E N -L O O P G A I N (d B )1001k10k100k1M806040200P H A S E M A R G I N (D E G R E E S )100–2080604020Figure 16. Open-Loop Gain and Phase Margin vs. Frequency 1k 0.0110010MFREQUENCY (Hz)O U T P U T I M P E D A N C E (Ω)00873-0181k 10k 100k 1M0.1110100Figure 17. Output Impedance vs. Frequency16–1605SETTLING TIME (µs)O U T P U T S W I N G F R O M 0 T O ±V00873-01912840–4–8–121234Figure 18. Output Swing and Error vs. Settling Time 10001010MFREQUENCY (Hz)C O M M O N -M ODE R E J E C T I O N (d B )00873-0201001k10k 100k 1M 908070605040302010Figure 19. Common-Mode Rejection vs. Frequency50–13COMMON-MODE VOLTAGE FROM SUPPLY RAILS (V)C O M M O N -M ODE E R R O R V O L T A G E (m V )00873-0214321012Figure 20. Absolute Common-Mode Error vs. Common-Mode Voltagefrom Supply Rails (V S − V CM )1k10.001100LOAD CURRENT (mA)O U T P U T S A T U R A T I O N V O L T A G E (m V )00873-0220.010.111010100Figure 21. Output Saturation Voltage vs. Load Current1k1–60140TEMPERATURE (ºC)O U T P U T S A T U R A T I O N V O L T A G E (m V )00873-023–40–2002040608010012010100Figure 22. Output Saturation Voltage vs. Temperature 800–60140TEMPERATURE (ºC)S H O R T C I R C U I T C U R R E N T L I M I T (m A )00873-024–40–2002040608010012070605040302010 Figure 23. Short Circuit Current Limit vs. Temperature 800003TOTAL SUPPLY VOLTAGE (V)Q U I E S C E N T C U R R E N T (µA )600873-02570060050040030020010048121620242832Figure 24. Quiescent Current vs. Supply Voltage over Different Temperatures12001010MFREQUENCY (Hz)P O W E R S U P P L Y R E J E C T I O N (d B )00873-0261001k10k100k1M110100908070605040302010Figure 25. Power Supply Rejection vs. Frequency30010k10MFREQUENCY (Hz)O U T P U T V O L T A G E (V )00873-027100k1M 252015105Figure 26. Large Signal Frequency Response00873-028+V OUT VFigure 27. Unity-Gain Follower, Used for Figure 28 Through Figure 3200873-029Figure 28. 20 V, 25 kHz Sine Input; Unity-Gain Follower; R L = 600 Ω, V S = ±15 V 00873-03Figure 29. V S = 5 V, 0 V; Unity-Gain Follower Response to 0 V to 4 V Step 00873-031Figure 30. Large Signal Response Unity-Gain Follower; V S = ±15 V, R L = 10 kΩ00873-032Figure 31. Small Signal Response Unity-Gain Follower; V S = ±15 V, R L = 10 kΩ00873-033Figure 32. V S = 5 V, 0 V; Unity-Gain Follower Response to 0 V to 5 V Step00873-035V OUT00873-034OUT V INFigure 33. Unity-Gain Follower, Used for Figure 34Figure 35. Gain of Two Inverter, Used for Figure 36 and Figure 3700873-03700873-036Figure 34. V S = 5 V, 0 V; Unity-Gain Follower Response to 40 mV StepCentered 40 mV Above Ground Figure 36. V S = 5 V, 0 V; Gain of Two Inverter Response to 2.5 V Step,Centered −1.25 V Below Ground00873-038Figure 37. V S = 5 V, 0 V; Gain of Two Inverter Response to 20 mV Step,Centered 20 mV Below GroundAPPLICATION NOTESINPUT CHARACTERISTICSIn the AD820, n-channel JFETs are used to provide a low offset, low noise, high impedance input stage. Minimum input common-mode voltage extends from 0.2 V below –V S to 1 V less than+V S. Driving the input voltage closer to the positive rail causes a loss of amplifier bandwidth (as can be seen by comparing the large signal responses shown in Figure 29 and Figure 32) and increased common-mode voltage error, as illustrated inFigure 20.The AD820 does not exhibit phase reversal for input voltages up to and including +V S. Figure 38a shows the response of anAD820 voltage follower to a 0 V to 5 V (+V S) square wave input. The input and output are superimposed. The output polarity tracks the input polarity up to +V S with no phase reversal. The reduced bandwidth above a 4 V input causes the rounding of the output wave form. For input voltages greater than +V S, a resistor in series with the AD820’s positive input prevents phase reversal, at the expense of greater input voltage noise. This is illustrated in Figure 38b.Since the input stage uses n-channel JFETs, input current during normal operation is negative; the current flows out from the input terminals. If the input voltage is driven more positive than +V S − 0.4 V, the input current reverses direction as internal device junctions become forward biased. This is illustrated in Figure 7.A current-limiting resistor should be used in series with the input of the AD820 if there is a possibility of the input voltage exceeding the positive supply by more than 300 mV, or if an input voltage is applied to the AD820 when ±V S = 0. The amplifier will be damaged if left in that condition for more than 10 seconds. A 1 kΩ resistor allows the amplifier to withstand up to 10 V of continuous overvoltage, and increases the input voltage noise by a negligible amount.Input voltages less than −V S are a completely different story.The amplifier can safely withstand input voltages 20 V below the negative supply voltage as long as the total voltage from the positive supply to the input terminal is less than 36 V. In addition, the input stage typically maintains picoamp level input currents across that input voltage range.The AD820 is designed for 13 nV/√Hz wideband input voltage noise and maintains low noise performance to low frequencies (refer to Figure 14). This noise performance, along with theAD820’s low input current and current noise means that the AD820 contributes negligible noise for applications with source resistances greater than 10 kΩ and signal bandwidths greater than 1 kHz. This is illustrated in Figure 39.873-39+VS5VOUTV(b)(a)Figure 38. (a) Response with R P = 0 Ω; V IN from 0 V to +V S(b) V IN = 0 V to +V S + 200 mV,V OUT = 0 V to +V S, R P = 49.9 kΩ100k0.110k10GSOURCE IMPEDANCE (Ω)INPUTVOLTAGENOISE(µVrms)873-40 10k1k100101100k1M10M100M1GFigure 39. Total Noise vs. Source ImpedanceOUTPUT CHARACTERISTICSThe AD820’s unique bipolar rail-to-rail output stage swings within 5 mV of the negative supply and 10 mV of the positive supply with no external resistive load. The AD820’s approxi-mate output saturation resistance is 40 Ω sourcing and 20 Ω sinking. This can be used to estimate output saturation voltage when driving heavier current loads. For instance, when sourcing 5 mA, the saturation voltage to the positive supply rail is 200 mV; when sinking 5 mA, the saturation voltage to the negative rail is 100 mV .The amplifier’s open-loop gain characteristic changes as a function of resistive load, as shown in Figure 10 through Figure 13. For load resistances over 20 kΩ, the AD820 input error voltage is virtually unchanged until the output voltage is driven to 180 mV of either supply.If the AD820 output is driven hard against the output saturation voltage, it recovers within 2 μs of the input returning to the amplifier’s linear operating region.Direct capacitive load interacts with the amplifier’s effective output impedance to form an additional pole in the amplifier’s feedback loop, which can cause excessive peaking on the pulse response or loss of stability. Worst case occurs when the amplifier is used as a unity-gain follower. Figure 40 shows AD820 pulse response as a unity-gain follower driving 350 pF. This amount of overshoot indicates approximately 20 degrees of phase margin—the system is stable, but is nearing the edge. Configurations with less loop gain, and as a result less loop bandwidth, are much less sensitive to capacitance load effects. Figure 41 is a plot of noise gain vs. the capacitive load that results in a 20 degree phase margin for the AD820. Noise gain is the inverse of the feedback attenuation factor provided by the feedback network in use.00873-041Figure 40. Small Signal Response of AD820 as Unity-Gain Follower Driving350 pF Capacitive Load00873-0425130030kCAPACITIVE LOAD FOR 20º PHASE MARGIN (pF)N O I S E G A I N (1+ )P I P F4321k 3k 10kFigure 41. Noise Gain vs. Capacitive Load ToleranceFigure 42 shows a possible configuration for extendingcapacitance load drive capability for a unity-gain follower. With these component values, the circuit drives 5000 pF with a 10% overshoot.00873-043+V OUT VFigure 42. Extending Unity-Gain Follower Capacitive Load CapabilityBeyond 350 pFOFFSET VOLTAGE ADJUSTMENTThe offset voltage of the AD820 is low, so external offset voltage nulling is not usually required. Figure 43 shows the recom-mended technique for AD820 packaged in plastic DIP . Adjusting offset voltage in this manner changes the offset voltage temperature drift by 4 μV/°C for every millivolt of induced offset. The null pins are not functional for AD820s in the 8-lead SOIC package.+V Figure 43. Offset NullAPPLICATIONSSINGLE SUPPLY HALF-WAVE AND FULL-WAVE RECTIFIERSAn AD820 configured as a unity-gain follower and operated with a single supply can be used as a simple half-wave rectifier. The AD820 inputs maintain picoamp level input currents even when driven well below the negative supply. The rectifier puts that behavior to good use, maintaining an input impedance of over 1011 Ω for input voltages from 1 V from the positive supply to 20 V below the negative supply.The full- and half-wave rectifier shown in Figure 44 operates as follows: when V IN is above ground, R1 is bootstrapped through the unity-gain follower, A1, and the loop of amplifier A2. This forces the inputs of A2 to be equal; thus, no current flowsthrough R1 or R2, and the circuit output tracks the input. When V IN is below ground, the output of A1 is forced to ground. The noninverting input of amplifier A2 sees the ground level output of A1; therefore, A2 operates as a unity-gain inverter. The output at Node C is then a full-wave rectified version of the input. Node B is a buffered half-wave rectified version of the input. Input voltages up to ±18 V can be rectified, depending on the voltage supply used.00873-045R1R2V AC HALF-WAVEBA BCFigure 44. Single-Supply Half- and Full-Wave Rectifier4.5 V LOW DROPOUT, LOW POWER REFERENCEThe rail-to-rail performance of the AD820 can be used to provide low dropout performance for low power reference circuits powered with a single low voltage supply. Figure 45 shows a 4.5 V reference using the AD820 and the AD680, a low power 2.5 V band gap reference. R2 and R3 set up the required gain of 1.8 to develop the 4.5 V output. R1 and C2 form a low-pass RC filter to reduce the noise contribution of the AD680.00873-0462.5VOUTPUT4.5VOUTPUTFigure 45. Single Supply 4.5 V Low Dropout ReferenceWith a 1 mA load, this reference maintains the 4.5 V output with a supply voltage down to 4.7 V . The amplitude of the recovery transient for a 1 mA to 10 mA step change in load current is under 20 mV , and settles out in a few microseconds. Output voltage noise is less than 10 μV rms in a 25 kHz noise bandwidth.。

拉马努金恒等式的证明

∞ k=−∞

(q/a, q/b, q/c, q/d, q/e)k (aq, bq, cq, dq, eq)k

(abcdeq−1)k

=

(q, ab, bc, ac)∞ (aq, bq, cq, abc/q)∞

∞ k=0

(q/a, (q, q2

q/b, q/c, /abc, dq,

de)k eq)k

qk

jouhet@math.univ-lyon1.fr, http://math.univ-lyon1.fr/~jouhet

3Universit´e de Lyon, Universit´e Lyon 1, UMR 5208 du CNRS, Institut Camille Jordan, F-69622, Villeurbanne Cedex, France

∞ k=−∞

(q/a)k (a)k

ak

qk2

−k

=

(q)∞ (a)∞

,

while the right-hand side of (1.7) is equal to 0 (since ab/q = 1). Similarly, if bc = 1, the left-hand side of (1.8) becomes

=

(q, ab/q, bc/q, ac/q)∞ (a, b, c, abc/q2)∞

∞ k=0

(q/a, q/b, q/c)k (q, q3/abc)k

qk

,

∞ k=−∞

(q/a, q/b, q/c)k (aq, bq, cq)k

(abc)k

q

k2

=

(q, ab, bc, ac)∞ (aq, bq, cq, abc/q)∞

rfc2661.Layer Two Tunneling Protocol L2TP

Network Working Group W. Townsley Request for Comments: 2661 A. Valencia Category: Standards Track cisco Systems A. Rubens Ascend Communications G. Pall G. Zorn Microsoft Corporation B. Palter Redback Networks August 1999 Layer Two Tunneling Protocol "L2TP"Status of this MemoThis document specifies an Internet standards track protocol for the Internet community, and requests discussion and suggestions forimprovements. Please refer to the current edition of the "InternetOfficial Protocol Standards" (STD 1) for the standardization stateand status of this protocol. Distribution of this memo is unlimited.Copyright NoticeCopyright (C) The Internet Society (1999). All Rights Reserved.AbstractThis document describes the Layer Two Tunneling Protocol (L2TP). STD 51, RFC 1661 specifies multi-protocol access via PPP [RFC1661]. L2TP facilitates the tunneling of PPP packets across an interveningnetwork in a way that is as transparent as possible to both end-users and applications.Table of Contents1.0 Introduction (3)1.1 Specification of Requirements (4)1.2 Terminology (4)2.0 Topology (8)3.0 Protocol Overview (9)3.1 L2TP Header Format (9)3.2 Control Message Types (11)4.0 Control Message Attribute Value Pairs (12)4.1 AVP Format (13)4.2 Mandatory AVPs (14)4.3 Hiding of AVP Attribute Values (14)Townsley, et al. Standards Track [Page 1]4.4.1 AVPs Applicable To All Control Messages (17)4.4.2 Result and Error Codes (18)4.4.3 Control Connection Management AVPs (20)4.4.4 Call Management AVPs (27)4.4.5 Proxy LCP and Authentication AVPs (34)4.4.6 Call Status AVPs (39)5.0 Protocol Operation (41)5.1 Control Connection Establishment (41)5.1.1 Tunnel Authentication (42)5.2 Session Establishment (42)5.2.1 Incoming Call Establishment (42)5.2.2 Outgoing Call Establishment (43)5.3 Forwarding PPP Frames (43)5.4 Using Sequence Numbers on the Data Channel (44)5.5 Keepalive (Hello) (44)5.6 Session Teardown (45)5.7 Control Connection Teardown (45)5.8 Reliable Delivery of Control Messages (46)6.0 Control Connection Protocol Specification (48)6.1 Start-Control-Connection-Request (SCCRQ) (48)6.2 Start-Control-Connection-Reply (SCCRP) (48)6.3 Start-Control-Connection-Connected (SCCCN) (49)6.4 Stop-Control-Connection-Notification (StopCCN) (49)6.5 Hello (HELLO) (49)6.6 Incoming-Call-Request (ICRQ) (50)6.7 Incoming-Call-Reply (ICRP) (51)6.8 Incoming-Call-Connected (ICCN) (51)6.9 Outgoing-Call-Request (OCRQ) (52)6.10 Outgoing-Call-Reply (OCRP) (53)6.11 Outgoing-Call-Connected (OCCN) (53)6.12 Call-Disconnect-Notify (CDN) (53)6.13 WAN-Error-Notify (WEN) (54)6.14 Set-Link-Info (SLI) (54)7.0 Control Connection State Machines (54)7.1 Control Connection Protocol Operation (55)7.2 Control Connection States (56)7.2.1 Control Connection Establishment (56)7.3 Timing considerations (58)7.4 Incoming calls (58)7.4.1 LAC Incoming Call States (60)7.4.2 LNS Incoming Call States (62)7.5 Outgoing calls (63)7.5.1 LAC Outgoing Call States (64)7.5.2 LNS Outgoing Call States (66)7.6 Tunnel Disconnection (67)8.0 L2TP Over Specific Media (67)8.1 L2TP over UDP/IP (68)Townsley, et al. Standards Track [Page 2]9.0 Security Considerations (69)9.1 Tunnel Endpoint Security (70)9.2 Packet Level Security (70)9.3 End to End Security (70)9.4 L2TP and IPsec (71)9.5 Proxy PPP Authentication (71)10.0 IANA Considerations (71)10.1 AVP Attributes (71)10.2 Message Type AVP Values (72)10.3 Result Code AVP Values (72)10.3.1 Result Code Field Values (72)10.3.2 Error Code Field Values (72)10.4 Framing Capabilities & Bearer Capabilities (72)10.5 Proxy Authen Type AVP Values (72)10.6 AVP Header Bits (73)11.0 References (73)12.0 Acknowledgments (74)13.0 Authors’ Addresses (75)Appendix A: Control Channel Slow Start and CongestionAvoidance (76)Appendix B: Control Message Examples (77)Appendix C: Intellectual Property Notice (79)Full Copyright Statement (80)1.0 IntroductionPPP [RFC1661] defines an encapsulation mechanism for transportingmultiprotocol packets across layer 2 (L2) point-to-point links.Typically, a user obtains a L2 connection to a Network Access Server (NAS) using one of a number of techniques (e.g., dialup POTS, ISDN,ADSL, etc.) and then runs PPP over that connection. In such aconfiguration, the L2 termination point and PPP session endpointreside on the same physical device (i.e., the NAS).L2TP extends the PPP model by allowing the L2 and PPP endpoints toreside on different devices interconnected by a packet-switchednetwork. With L2TP, a user has an L2 connection to an accessconcentrator (e.g., modem bank, ADSL DSLAM, etc.), and theconcentrator then tunnels individual PPP frames to the NAS. Thisallows the actual processing of PPP packets to be divorced from thetermination of the L2 circuit.One obvious benefit of such a separation is that instead of requiring the L2 connection terminate at the NAS (which may require along-distance toll charge), the connection may terminate at a (local) circuit concentrator, which then extends the logical PPP session over Townsley, et al. Standards Track [Page 3]a shared infrastructure such as frame relay circuit or the Internet.From the user’s perspective, there is no functional difference between having the L2 circuit terminate in a NAS directly or using L2TP.L2TP may also solve the multilink hunt-group splitting problem.Multilink PPP [RFC1990] requires that all channels composing amultilink bundle be grouped at a single Network Access Server (NAS).Due to its ability to project a PPP session to a location other thanthe point at which it was physically received, L2TP can be used tomake all channels terminate at a single NAS. This allows multilinkoperation even when the calls are spread across distinct physicalNASs.This document defines the necessary control protocol for on-demandcreation of tunnels between two nodes and the accompanyingencapsulation for multiplexing multiple, tunneled PPP sessions.1.1 Specification of RequirementsThe key words "MUST", "MUST NOT", "REQUIRED", "SHALL", "SHALL NOT","SHOULD", "SHOULD NOT", "RECOMMENDED", "MAY", and "OPTIONAL" in thisdocument are to be interpreted as described in [RFC2119].1.2 TerminologyAnalog ChannelA circuit-switched communication path which is intended to carry3.1 kHz audio in each direction.Attribute Value Pair (AVP)The variable length concatenation of a unique Attribute(represented by an integer) and a Value containing the actualvalue identified by the attribute. Multiple AVPs make up ControlMessages which are used in the establishment, maintenance, andteardown of tunnels.CallA connection (or attempted connection) between a Remote System and LAC. For example, a telephone call through the PSTN. A Call(Incoming or Outgoing) which is successfully established between a Remote System and LAC results in a corresponding L2TP Sessionwithin a previously established Tunnel between the LAC and LNS.(See also: Session, Incoming Call, Outgoing Call).Townsley, et al. Standards Track [Page 4]Called NumberAn indication to the receiver of a call as to what telephonenumber the caller used to reach it.Calling NumberAn indication to the receiver of a call as to the telephone number of the caller.CHAPChallenge Handshake Authentication Protocol [RFC1994], a PPPcryptographic challenge/response authentication protocol in which the cleartext password is not passed over the line.Control ConnectionA control connection operates in-band over a tunnel to control the establishment, release, and maintenance of sessions and of thetunnel itself.Control MessagesControl messages are exchanged between LAC and LNS pairs,operating in-band within the tunnel protocol. Control messagesgovern aspects of the tunnel and sessions within the tunnel.Digital ChannelA circuit-switched communication path which is intended to carrydigital information in each direction.DSLAMDigital Subscriber Line (DSL) Access Module. A network device used in the deployment of DSL service. This is typically a concentrator of individual DSL lines located in a central office (CO) or local exchange.Incoming CallA Call received at an LAC to be tunneled to an LNS (see Call,Outgoing Call).Townsley, et al. Standards Track [Page 5]L2TP Access Concentrator (LAC)A node that acts as one side of an L2TP tunnel endpoint and is apeer to the L2TP Network Server (LNS). The LAC sits between anLNS and a remote system and forwards packets to and from each.Packets sent from the LAC to the LNS requires tunneling with theL2TP protocol as defined in this document. The connection fromthe LAC to the remote system is either local (see: Client LAC) or a PPP link.L2TP Network Server (LNS)A node that acts as one side of an L2TP tunnel endpoint and is apeer to the L2TP Access Concentrator (LAC). The LNS is thelogical termination point of a PPP session that is being tunneled from the remote system by the LAC.Management Domain (MD)A network or networks under the control of a singleadministration, policy or system. For example, an LNS’s Management Domain might be the corporate network it serves. An LAC’sManagement Domain might be the Internet Service Provider that owns and manages it.Network Access Server (NAS)A device providing local network access to users across a remoteaccess network such as the PSTN. An NAS may also serve as an LAC, LNS or both.Outgoing CallA Call placed by an LAC on behalf of an LNS (see Call, IncomingCall).PeerWhen used in context with L2TP, peer refers to either the LAC orLNS. An LAC’s Peer is an LNS and vice versa. When used in context with PPP, a peer is either side of the PPP connection.POTSPlain Old Telephone Service.Townsley, et al. Standards Track [Page 6]Remote SystemAn end-system or router attached to a remote access network (i.e.a PSTN), which is either the initiator or recipient of a call.Also referred to as a dial-up or virtual dial-up client.SessionL2TP is connection-oriented. The LNS and LAC maintain state foreach Call that is initiated or answered by an LAC. An L2TP Session is created between the LAC and LNS when an end-to-end PPPconnection is established between a Remote System and the LNS.Datagrams related to the PPP connection are sent over the Tunnelbetween the LAC and LNS. There is a one to one relationshipbetween established L2TP Sessions and their associated Calls. (See also: Call).TunnelA Tunnel exists between a LAC-LNS pair. The Tunnel consists of aControl Connection and zero or more L2TP Sessions. The Tunnelcarries encapsulated PPP datagrams and Control Messages betweenthe LAC and the LNS.Zero-Length Body (ZLB) MessageA control packet with only an L2TP header. ZLB messages are usedfor explicitly acknowledging packets on the reliable controlchannel.Townsley, et al. Standards Track [Page 7]2.0 TopologyThe following diagram depicts a typical L2TP scenario. The goal is to tunnel PPP frames between the Remote System or LAC Client and an LNS located at a Home LAN.[Home LAN][LAC Client]----------+ |____|_____ +--[Host]| | |[LAC]---------| Internet |-----[LNS]-----+| |__________| |_____|_____ :| || PSTN |[Remote]--| Cloud |[System] | | [Home LAN]|___________| || ______________ +---[Host]| | | |[LAC]-------| Frame Relay |---[LNS]-----+| or ATM Cloud | ||______________| :The Remote System initiates a PPP connection across the PSTN Cloud to an LAC. The LAC then tunnels the PPP connection across the Internet, Frame Relay, or ATM Cloud to an LNS whereby access to a Home LAN isobtained. The Remote System is provided addresses from the HOME LANvia PPP NCP negotiation. Authentication, Authorization and Accounting may be provided by the Home LAN’s Management Domain as if the userwere connected to a Network Access Server directly.A LAC Client (a Host which runs L2TP natively) may also participatein tunneling to the Home LAN without use of a separate LAC. In thiscase, the Host containing the LAC Client software already has aconnection to the public Internet. A "virtual" PPP connection is then created and the local L2TP LAC Client software creates a tunnel tothe LNS. As in the above case, Addressing, Authentication,Authorization and Accounting will be provided by the Home LAN’sManagement Domain.Townsley, et al. Standards Track [Page 8]3.0 Protocol OverviewL2TP utilizes two types of messages, control messages and datamessages. Control messages are used in the establishment, maintenance and clearing of tunnels and calls. Data messages are used toencapsulate PPP frames being carried over the tunnel. Controlmessages utilize a reliable Control Channel within L2TP to guarantee delivery (see section 5.1 for details). Data messages are notretransmitted when packet loss occurs.+-------------------+| PPP Frames |+-------------------+ +-----------------------+| L2TP Data Messages| | L2TP Control Messages |+-------------------+ +-----------------------+| L2TP Data Channel | | L2TP Control Channel || (unreliable) | | (reliable) |+------------------------------------------------+| Packet Transport (UDP, FR, ATM, etc.) |+------------------------------------------------+Figure 3.0 L2TP Protocol StructureFigure 3.0 depicts the relationship of PPP frames and ControlMessages over the L2TP Control and Data Channels. PPP Frames arepassed over an unreliable Data Channel encapsulated first by an L2TP header and then a Packet Transport such as UDP, Frame Relay, ATM,etc. Control messages are sent over a reliable L2TP Control Channelwhich transmits packets in-band over the same Packet Transport.Sequence numbers are required to be present in all control messagesand are used to provide reliable delivery on the Control Channel.Data Messages may use sequence numbers to reorder packets and detect lost packets.All values are placed into their respective fields and sent innetwork order (high order octets first).3.1 L2TP Header FormatL2TP packets for the control channel and data channel share a common header format. In each case where a field is optional, its space does not exist in the message if the field is marked not present. Notethat while optional on data messages, the Length, Ns, and Nr fieldsmarked as optional below, are required to be present on all controlmessages.Townsley, et al. Standards Track [Page 9]This header is formatted:0 1 2 30 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+|T|L|x|x|S|x|O|P|x|x|x|x| Ver | Length (opt) |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Tunnel ID | Session ID |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Ns (opt) | Nr (opt) |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Offset Size (opt) | Offset pad... (opt)+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+Figure 3.1 L2TP Message HeaderThe Type (T) bit indicates the type of message. It is set to 0 for a data message and 1 for a control message.If the Length (L) bit is 1, the Length field is present. This bitMUST be set to 1 for control messages.The x bits are reserved for future extensions. All reserved bits MUST be set to 0 on outgoing messages and ignored on incoming messages.If the Sequence (S) bit is set to 1 the Ns and Nr fields are present. The S bit MUST be set to 1 for control messages.If the Offset (O) bit is 1, the Offset Size field is present. The Obit MUST be set to 0 (zero) for control messages.If the Priority (P) bit is 1, this data message should receivepreferential treatment in its local queuing and transmission. LCPecho requests used as a keepalive for the link, for instance, should generally be sent with this bit set to 1. Without it, a temporaryinterval of local congestion could result in interference withkeepalive messages and unnecessary loss of the link. This feature is only for use with data messages. The P bit MUST be set to 0 for allcontrol messages.Ver MUST be 2, indicating the version of the L2TP data message header described in this document. The value 1 is reserved to permitdetection of L2F [RFC2341] packets should they arrive intermixed with L2TP packets. Packets received with an unknown Ver field MUST bediscarded.The Length field indicates the total length of the message in octets. Townsley, et al. Standards Track [Page 10]Tunnel ID indicates the identifier for the control connection. L2TPtunnels are named by identifiers that have local significance only.That is, the same tunnel will be given different Tunnel IDs by eachend of the tunnel. Tunnel ID in each message is that of the intended recipient, not the sender. Tunnel IDs are selected and exchanged asAssigned Tunnel ID AVPs during the creation of a tunnel.Session ID indicates the identifier for a session within a tunnel.L2TP sessions are named by identifiers that have local significanceonly. That is, the same session will be given different Session IDsby each end of the session. Session ID in each message is that of the intended recipient, not the sender. Session IDs are selected andexchanged as Assigned Session ID AVPs during the creation of asession.Ns indicates the sequence number for this data or control message,beginning at zero and incrementing by one (modulo 2**16) for eachmessage sent. See Section 5.8 and 5.4 for more information on usingthis field.Nr indicates the sequence number expected in the next control message to be received. Thus, Nr is set to the Ns of the last in-ordermessage received plus one (modulo 2**16). In data messages, Nr isreserved and, if present (as indicated by the S-bit), MUST be ignored upon receipt. See section 5.8 for more information on using thisfield in control messages.The Offset Size field, if present, specifies the number of octetspast the L2TP header at which the payload data is expected to start. Actual data within the offset padding is undefined. If the offsetfield is present, the L2TP header ends after the last octet of theoffset padding.3.2 Control Message TypesThe Message Type AVP (see section 4.4.1) defines the specific type of control message being sent. Recall from section 3.1 that this is only for control messages, that is, messages with the T-bit set to 1. Townsley, et al. Standards Track [Page 11]This document defines the following control message types (seeSection 6.1 through 6.14 for details on the construction and use ofeach message):Control Connection Management0 (reserved)1 (SCCRQ) Start-Control-Connection-Request2 (SCCRP) Start-Control-Connection-Reply3 (SCCCN) Start-Control-Connection-Connected4 (StopCCN) Stop-Control-Connection-Notification5 (reserved)6 (HELLO) HelloCall Management7 (OCRQ) Outgoing-Call-Request8 (OCRP) Outgoing-Call-Reply9 (OCCN) Outgoing-Call-Connected10 (ICRQ) Incoming-Call-Request11 (ICRP) Incoming-Call-Reply12 (ICCN) Incoming-Call-Connected13 (reserved)14 (CDN) Call-Disconnect-NotifyError Reporting15 (WEN) WAN-Error-NotifyPPP Session Control16 (SLI) Set-Link-Info4.0 Control Message Attribute Value PairsTo maximize extensibility while still permitting interoperability, a uniform method for encoding message types and bodies is usedthroughout L2TP. This encoding will be termed AVP (Attribute-ValuePair) in the remainder of this document.Townsley, et al. Standards Track [Page 12]4.1 AVP FormatEach AVP is encoded as:0 1 2 30 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+|M|H| rsvd | Length | Vendor ID |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Attribute Type | Attribute Value...+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+[until Length is reached]... |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+The first six bits are a bit mask, describing the general attributes of the AVP.Two bits are defined in this document, the remaining are reserved for future extensions. Reserved bits MUST be set to 0. An AVP receivedwith a reserved bit set to 1 MUST be treated as an unrecognized AVP. Mandatory (M) bit: Controls the behavior required of animplementation which receives an AVP which it does not recognize. If the M bit is set on an unrecognized AVP within a message associatedwith a particular session, the session associated with this messageMUST be terminated. If the M bit is set on an unrecognized AVP within a message associated with the overall tunnel, the entire tunnel (and all sessions within) MUST be terminated. If the M bit is not set, an unrecognized AVP MUST be ignored. The control message must thencontinue to be processed as if the AVP had not been present.Hidden (H) bit: Identifies the hiding of data in the Attribute Value field of an AVP. This capability can be used to avoid the passing of sensitive data, such as user passwords, as cleartext in an AVP.Section 4.3 describes the procedure for performing AVP hiding.Length: Encodes the number of octets (including the Overall Lengthand bitmask fields) contained in this AVP. The Length may becalculated as 6 + the length of the Attribute Value field in octets. The field itself is 10 bits, permitting a maximum of 1023 octets ofdata in a single AVP. The minimum Length of an AVP is 6. If thelength is 6, then the Attribute Value field is absent.Vendor ID: The IANA assigned "SMI Network Management PrivateEnterprise Codes" [RFC1700] value. The value 0, corresponding toIETF adopted attribute values, is used for all AVPs defined withinthis document. Any vendor wishing to implement their own L2TPextensions can use their own Vendor ID along with private Attribute Townsley, et al. Standards Track [Page 13]values, guaranteeing that they will not collide with any othervendor’s extensions, nor with future IETF extensions. Note that there are 16 bits allocated for the Vendor ID, thus limiting this featureto the first 65,535 enterprises.Attribute Type: A 2 octet value with a unique interpretation acrossall AVPs defined under a given Vendor ID.Attribute Value: This is the actual value as indicated by the Vendor ID and Attribute Type. It follows immediately after the AttributeType field, and runs for the remaining octets indicated in the Length (i.e., Length minus 6 octets of header). This field is absent if the Length is 6.4.2 Mandatory AVPsReceipt of an unknown AVP that has the M-bit set is catastrophic tothe session or tunnel it is associated with. Thus, the M bit shouldonly be defined for AVPs which are absolutely crucial to properoperation of the session or tunnel. Further, in the case where theLAC or LNS receives an unknown AVP with the M-bit set and shuts down the session or tunnel accordingly, it is the full responsibility ofthe peer sending the Mandatory AVP to accept fault for causing annon-interoperable situation. Before defining an AVP with the M-bitset, particularly a vendor-specific AVP, be sure that this is theintended consequence.When an adequate alternative exists to use of the M-bit, it should be utilized. For example, rather than simply sending an AVP with the M- bit set to determine if a specific extension exists, availability may be identified by sending an AVP in a request message and expecting a corresponding AVP in a reply message.Use of the M-bit with new AVPs (those not defined in this document)MUST provide the ability to configure the associated feature off,such that the AVP is either not sent, or sent with the M-bit not set.4.3 Hiding of AVP Attribute ValuesThe H bit in the header of each AVP provides a mechanism to indicate to the receiving peer whether the contents of the AVP are hidden orpresent in cleartext. This feature can be used to hide sensitivecontrol message data such as user passwords or user IDs.The H bit MUST only be set if a shared secret exists between the LAC and LNS. The shared secret is the same secret that is used for tunnel authentication (see Section 5.1.1). If the H bit is set in any Townsley, et al. Standards Track [Page 14]AVP(s) in a given control message, a Random Vector AVP must also bepresent in the message and MUST precede the first AVP having an H bit of 1.Hiding an AVP value is done in several steps. The first step is totake the length and value fields of the original (cleartext) AVP and encode them into a Hidden AVP Subformat as follows:0 1 2 30 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Length of Original Value | Original Attribute Value ...+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+... | Padding ...+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+Length of Original Attribute Value: This is length of the OriginalAttribute Value to be obscured in octets. This is necessary todetermine the original length of the Attribute Value which is lostwhen the additional Padding is added.Original Attribute Value: Attribute Value that is to be obscured.Padding: Random additional octets used to obscure length of theAttribute Value that is being hidden.To mask the size of the data being hidden, the resulting subformatMAY be padded as shown above. Padding does NOT alter the value placed in the Length of Original Attribute Value field, but does alter thelength of the resultant AVP that is being created. For example, If an Attribute Value to be hidden is 4 octets in length, the unhidden AVP length would be 10 octets (6 + Attribute Value length). After hiding, the length of the AVP will become 6 + Attribute Value length + sizeof the Length of Original Attribute Value field + Padding. Thus, ifPadding is 12 octets, the AVP length will be 6 + 4 + 2 + 12 = 24octets.Next, An MD5 hash is performed on the concatenation of:+ the 2 octet Attribute number of the AVP+ the shared secret+ an arbitrary length random vectorThe value of the random vector used in this hash is passed in thevalue field of a Random Vector AVP. This Random Vector AVP must beplaced in the message by the sender before any hidden AVPs. The same random vector may be used for more than one hidden AVP in the same Townsley, et al. Standards Track [Page 15]message. If a different random vector is used for the hiding ofsubsequent AVPs then a new Random Vector AVP must be placed in thecommand message before the first AVP to which it applies.The MD5 hash value is then XORed with the first 16 octet (or less)segment of the Hidden AVP Subformat and placed in the Attribute Value field of the Hidden AVP. If the Hidden AVP Subformat is less than 16 octets, the Subformat is transformed as if the Attribute Value field had been padded to 16 octets before the XOR, but only the actualoctets present in the Subformat are modified, and the length of theAVP is not altered.If the Subformat is longer than 16 octets, a second one-way MD5 hash is calculated over a stream of octets consisting of the shared secret followed by the result of the first XOR. That hash is XORed with the second 16 octet (or less) segment of the Subformat and placed in the corresponding octets of the Value field of the Hidden AVP.If necessary, this operation is repeated, with the shared secret used along with each XOR result to generate the next hash to XOR the next segment of the value with.The hiding method was adapted from RFC 2138 [RFC2138] which was taken from the "Mixing in the Plaintext" section in the book "NetworkSecurity" by Kaufman, Perlman and Speciner [KPS]. A detailedexplanation of the method follows:Call the shared secret S, the Random Vector RV, and the AttributeValue AV. Break the value field into 16-octet chunks p1, p2, etc.with the last one padded at the end with random data to a 16-octetboundary. Call the ciphertext blocks c(1), c(2), etc. We will also define intermediate values b1, b2, etc.b1 = MD5(AV + S + RV) c(1) = p1 xor b1b2 = MD5(S + c(1)) c(2) = p2 xor b2. .. .. .bi = MD5(S + c(i-1)) c(i) = pi xor biThe String will contain c(1)+c(2)+...+c(i) where + denotesconcatenation.On receipt, the random vector is taken from the last Random VectorAVP encountered in the message prior to the AVP to be unhidden. The above process is then reversed to yield the original value.Townsley, et al. Standards Track [Page 16]。

rfc3281中文

3

2.术语

为了方便起见,在这个说明中我们使用了术语“客户端”和“服务器端” 。这不表示属 性证书只能用于 C/S 环境。例如,属性证书可以用于 S/MIME v3,在这种环境中使用这些 术语时,邮件客户代理既代表“客户端” ,同时也代表“服务器端” 。 术语 AA AC AC user AC verifier AC issuer AC holder Client Proxying PKC 含义 属性管理机构,颁发属性证书的实体,在本文档中和 AC issuer 同义 属性证书 解析或处理属性证书的实体 检查属性证书有效性的实体并且决定最后如何使用属性证书 签发属性证书的实体,在本文档中和 AA 同义 属性证书持有者字段中(可能是间接的)对应的实体 发出请求动作的实体,请求动作需要接受权限检查 在本文档中,Proxying 通常是指应用服务器端充当应用客户端,代表一个用 户的情况,并不是指授权机构的授权 公钥证书——使用 ASN.1 标准,在 X.509 中定义的证书格式和 RFC2459 中 定义的框架。使用这个(不规范的)缩略词是为了避免与术语“X.509 证书”混 淆 要求进行权限检查的实体

2

这意味着构造这样的应用只要求一次处理一个属性证书。 需要处理超过一个属性证书的 话, 一个接一个地处理。 然而要注意, 属性证书的有效性可能依赖于 PKCs 证书链的有效性, PKCs 证书链有效性的定义请参考[PKIXPROF]。

1.2 属性证书的分发(“推”和“拉”)

如上面讨论, 属性证书提供了一种机制, 这种机制安全地提供了授权信息来实现例如访 问控制决策等功能。然而,属性证书还有很多种可能的通信路径。 在一些环境下,比较适合的方法是从客户端“推”一个属性证书到服务器端。这样客户 端和服务器端不需要建立新的连接, 服务器端没有附加的搜索负担, 这样就改进了性能而且 属性证书验证者只提取“需要知道”的内容。 “推”模式适合于客户端的权限被分配在客户 端的“home”域以内的情况。 另一种情况, 它更适合于服务器端对客户端的简单鉴别, 服务器端从属性证书颁发者请 求或“拉”客户端的属性证书。使用“拉”模式主要的好处是它可以在不改变客户端或者客 户端/服务器端协议的情况下实现。 “拉”模式适合于客户端的权限被分配在服务器的域中, 而不是在客户端的域的情况。 可以交互信息的实体有三个:客户端,服务器端,还有属性证书颁发者。此外,为支 持属性证书检索还应该有一个目录服务器或者其他证书仓库。 图 1 描述了在各个实体间的交互信息(包括属性证书)的抽象视图。本文档没有对这 些交互规定特定的协议。

Introduction_to_x64_Assembly

DF

10 Direction

Direction string instructions operate (increment or decrement)

ID

21 Identification Changeability denotes presence of CPUID instruction

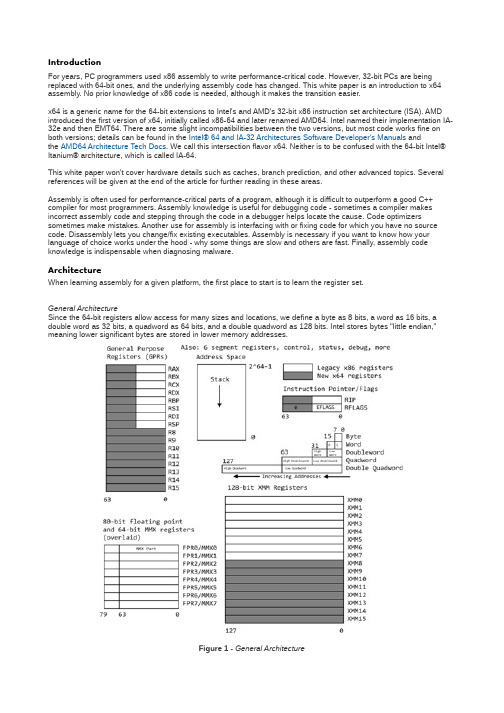

The floating point unit (FPU) contains eight registers FPR0-FPR7, status and control registers, and a few other specialized registers. FPR0-7 can each store one value of the types shown in Table 2. Floating point operations conform to IEEE 754. Note that most C/C++ compilers support the 32 and 64 bit types as float and double, but not the 80-bit one available from assembly. These registers share space with the eight 64-bit MMX registers.

Assembly is often used for performance-critical parts of a program, although it is difficult to outperform a good C++ compiler for most programmers. Assembly knowledge is useful for debugging code – sometimes a compiler makes incorrect assembly code and stepping through the code in a debugger helps locate the cause. Code optimizers sometimes make mistakes. Another use for assembly is interfacing with or fixing code for which you have no source code. Disassembly lets you change/fix existing executables. Assembly is necessary if you want to know how your language of choice works under the hood – why some things are slow and others are fast. Finally, assembly code knowledge is indispensable when diagnosing malware.

Rcpp快速参考指南说明书

return sum/n; // Obtain and return the Mean }

// Place dependent functions above call or // declare the function definition with: double muRcpp(NumericVector x);

double y0 = yy["foo"]; double y1 = yy["bar"];

// Matrix of 4 rows & 5 columns (filled with 0) NumericMatrix xx(4, 5);

// Fill with value int xsize = xx.nrow() * xx.ncol(); for (int i = 0; i < xsize; i++) {

for(int i = 0; i < n; i++){ sum += pow(x[i] - mean, 2.0); // Square

// [[Rcpp::export]]

2 | https:///package=Rcpp

Eddelbuettel and François

double varRcpp(NumericVector x, bool bias = true){ // Calculate the mean using C++ function double mean = muRcpp(x); double sum = 0; int n = x.size();

fortran for 用法

fortran for 用法Fortran is a programming language that was developed in the 1950s and is primarily used for scientific and engineering computations. In this article, we will explore the usage of Fortran, step by step, examining its features, syntax, and application areas.1. Introduction to Fortran:Fortran, short for Formula Translation, was developed by IBM as the first high-level programming language designed specifically for scientific and engineering calculations. It became popular due to its efficiency in handling numerical computations and remains extensively used in these fields.2. Features of Fortran:Fortran is known for its strong support for floating-point calculations, making it ideal for numerical simulations, mathematical modeling, and data analysis. It provides a range of built-in mathematical functions and libraries for complex mathematical operations. Fortran also supports arrays andmulti-dimensional data structures, allowing efficient data manipulation and processing.3. Syntax and Structure:Fortran programs are written in fixed-format style, where columns 1-6 are used for line labels, 7 is for a continuation character, and columns 8-72 are for statements and comments. The general structure of a Fortran program consists of declarations, executable statements, and subroutines or functions.4. Declaring Variables and Constants:In Fortran, variables and constants are declared using the "type" statement. The commonly used types include integer, real, and character. For example, to declare an integer variable called "count", we use the statement "integer :: count".5. Input and Output Operations:Fortran provides various standard input and output functions to interact with the user. The "read" statement is used to accept input from the user, while the "write" statement displays output on the screen or writes it to a file. For example, "read(*,*) x" reads a value into variable x from the default input source, and "write(*,*) x" displays the value of x on the screen.6. Control Structures:Fortran supports the standard control structures such as if-else, do-while, and do-loop. These control structures enable the program to make decisions and iterate over a set of statements based on specified conditions. Loops are particularly useful in performing repetitive tasks and computing over large datasets.7. Modular Programming:Modular programming, which promotes code reusability and organization, is supported in Fortran through the use of subroutines and functions. Subroutines are blocks of code that perform specific tasks and can be called from other parts of the program. Functions, on the other hand, return a value and can be used in expressions.8. Libraries and Extensions:Fortran provides a wide range of libraries and extensions to facilitate scientific and engineering computations. The most commonly used library is the Mathematical Library (MKL), which offers optimized routines for linear algebra, fast Fourier transforms, and numerical integration. Additionally, Fortran can be extended with modules written in other languages like C or C++.9. Parallel Computing:Fortran has excellent support for parallel computing, which allows programs to utilize multiple processors or cores for simultaneous execution. Libraries like OpenMP and MPI (Message Passing Interface) can be used to implement parallel algorithms in Fortran, increasing the speed and efficiency of computation-intensive tasks.10. Applications:Fortran is widely used in various scientific and engineering domains, including weather forecasting, computational physics, computational chemistry, and aerospace engineering. Its efficiency in handling large datasets and complex calculations makes it indispensable for numerical simulations and research purposes.In conclusion, Fortran is a powerful programming language that excels in numerical computations and is widely used in scientific and engineering fields. Its features, syntax, and extensive libraries make it an ideal choice for complex mathematical modeling, data analysis, and simulation tasks. With its continued development and support, Fortran remains a critical tool for scientists and engineers worldwide.。

系统出错提示(中英对照及对策)

系统出错提示(中英对照及对策)最近一些朋友一见到系统出错提示英文时,是一筹莫展,现介绍一些中英对照及对策,供朋友们在学习中参考。

[英文提示] Abort,Retry, Ignore,fail?[中文] 退出,重试,忽略,取消?[原因] 不能识别给出的命令、或发生了使命令不能执行的磁盘或设备错误,可能是磁盘损坏或软驱门没关。

[对策] 按A键彻底终止,并回到DOS提示符。

按R键重复执行该命令。

按I键继续处理,忽略错误,非常冒险,建议不要采用按F键不执行有问题的命令,继续下述处理。

有时会用到。

[英文提示] Access Denied[中文] 拒绝存取[原因] 试图打开一个标记为只读、存贮在写保护的磁盘上或锁定在网络上的文件。

如果在子目录上使用“Type”命令,或在文件上使用“CD(chdir)”命令,也会产生这个信息。

[对策] 应该用“Attrib”命令删除文件的只读状态或从磁盘中去掉写保护,然后再试试。

[英文提示] Bad Command or file name[中文] 错误的命令或文件名[原因] 不能识别输入的命令[对策] 应该检查以确保输入命令的正确性确认在指定目录或用Path命令指定的搜索路径上能找到命令文件。

[英文提示] Boot error[中文] 引导错误[原因] 在引导时检测不到应该的外设。

[对策] 应该检查计算机的设置参数,如用户自己不能解决这个问题,请找专门维修人员。

[英文提示] Cannot find system files[中文] 不能找到系统文件[原因] 试图从没有包含系统文件的驱动器上装入操作系统。

[对策] 应该用sys命令将系统文件复制到根目录中。

除非真的是不能恢复系统文件了,才可用Format/s命令重新格式化磁盘。

[英文提示] Cannot load command,system halted[中文] 不能加载command,系统中止[原因] 应用程序覆盖了内存中的所有或部分。

Contents

8

Zentrum fur ¨ Technomathematik Strong Symbols

Fachbereich 3 Mathematik und Informatik Henning Thielemann

Example: Computer algebra system Mathematica: In> Out> Replace all occurences of x by 2 ReplaceAll[Log [x],x->2] Log [2] Derive Log [x] with respect to x D[Log [x],x]

• Chemical formulas contain not enough information for synthesising substances or simulating reactions. • Musical scores allow for much interpretation. • Theorems in mathematical articles cannot be proven with a machine, calculations can’t be executed. • Computer programs can be executed by a machine, they can be processed by other programs, certain properties can even be proven! But programming language differ very much in robustness, simplicity, orthogonality, consistency, expressiveness.

x64文档

x641. Introduction to x64 Architecturex64, also known as x86-64 or AMD64, is a 64-bit extension of the x86 instruction set architecture. It was developed by AMD and later adopted by Intel. The x64 architecture offers several advantages over its 32-bit predecessor, including increased memory addressing capabilities, improved floating-point performance, and support for more general-purpose registers.2. Memory Addressing in x64In x64 architecture, the memory addressing space is expanded from 32 bits to 48 bits, allowing for a theoretical maximum of 256 TB of addressable memory. This increase in memory space is particularly beneficial for applications that require large amounts of memory, such as scientific simulations, database management systems, and virtualization.3. Registers in x64One of the key differences between x64 and x86 is the increased number of general-purpose registers. While x86 architecture has only 8 general-purpose registers, x64 architecture provides 16 general-purpose registers, including 8 integer registers (RAX, RBX, RCX, RDX, RSI, RDI, RBP, RSP) and 8 additional registers (R8, R9, R10, R11, R12, R13, R14, R15).4. Instruction Set ExtensionsThe x64 architecture introduced several new instruction set extensions, including SSE (Streaming SIMD Extensions), SSE2, SSE3, SSSE3, SSE4, AVX (Advanced Vector Extensions), AVX2, and AVX-512. These extensions provide support for parallel processing, floating-point operations, and other performance-enhancing features. Software developers can take advantage of these extensions to optimize their applications for the x64 architecture.5. Software CompatibilityOne important consideration when migrating from x86 to x64 is software compatibility. Most 32-bit applications can still run on a 64-bit operating system using a compatibility layer called WoW64 (Windows-on-Windows 64). However, some applications may require updates or modifications to work properly in a 64-bit environment. It is recommended to test and validate applications before deploying them on a x64 system.6. Performance BenefitsThe x64 architecture offers several performance benefits over its 32-bit predecessor. The increased memory addressing space allows applications to access more memory, resulting in improved performance for memory-intensive tasks. The additional general-purpose registers provide more storage for data manipulation, reducing the need for memory access. Furthermore, the instruction set extensions enable more efficient parallel processing and floating-point operations, resulting in faster execution of many applications.7. ConclusionThe x64 architecture provides significant enhancements over the previous x86 architecture. With its increased memory addressing capabilities, improved floating-point performance, and expanded set of general-purpose registers, x64 can handle more demanding applications and deliver better overall performance. Software developers should consider optimizing their applications for the x64 architecture to take full advantage of its benefits.。

Chapter02 Functions

volatile while

Not allowed, because an identifier is a token

7 Copyright © 2012 by The McGraw-Hill Companies, Inc. Permission required for reproduction or display.

format_string plain characters – displayed directly unchanged on the screen, e.g. “This is C” conversion specification(s) – used to convert, format and display argument(s) from the argument_list escape sequences – control the cursor, for example, the newline ‘\n’

equal

10 Copyright © 2012 by The McGraw-Hill Companies, Inc. Permission required for reproduction or display.

printf

To display the value of a variable or constant on the screen printf(format_string,argument_list);

Need to make up your own variable names, e.g. lengths: a, b, c angles: a, b, g

For programming in C, the situation is similar choose the variable names, consist of entire words rather than single characters easier to understand your programs if given very descriptive names to each variable

on random graphs