Timed CSP在硬件高层设计中的应用

计算机硬件设计中的片上系统设计

计算机硬件设计中的片上系统设计计算机硬件设计中的片上系统设计是现代计算机发展的重要组成部分。

随着科技的不断进步和需求的不断增长,计算机硬件设计技术也在不断创新和发展。

片上系统设计是一种将多个功能模块集成在一个芯片上的技术,它能够提高计算机系统的性能、降低功耗、减小体积,并且提供更高的可靠性。

本文将从片上系统设计的定义、应用范围、设计原则和未来发展等方面进行探讨。

一、片上系统设计的定义片上系统设计,简称SoC(System on Chip),是指将计算机硬件中的多个功能模块(如CPU、内存、外设等)集成在一个芯片上的技术。

它采用高度集成的设计方式,将原本需要多个电路板组合而成的系统集成到一个芯片中。

这样做的好处是可以提高系统性能,减小系统体积,降低功耗,并提供更高的可靠性。

二、片上系统设计的应用范围片上系统设计广泛应用于各个领域,特别是嵌入式系统和移动设备。

嵌入式系统是指嵌入到其他设备中的计算机系统,如智能家居、工业控制设备等。

移动设备包括智能手机、平板电脑等便携式电子产品。

片上系统设计可以将这些系统所需的所有功能模块都集成到一个芯片中,使系统更加高效、稳定和节能。

三、片上系统设计的设计原则在进行片上系统设计时,需要遵循以下设计原则:1.模块化设计:将系统划分为多个模块,每个模块负责不同的功能,并且模块之间可以独立设计、测试和调试。

这样可以提高设计效率和可维护性。

2.硬件与软件协同设计:片上系统设计中,硬件模块与软件模块之间需要密切配合。

硬件模块的设计需要考虑软件的要求,而软件的编写也要充分考虑硬件的特性。

这样可以提高系统的性能和稳定性。

3.功耗优化:片上系统设计需要考虑到系统的功耗问题。

通过优化电路设计、采用低功耗材料和技术,以及合理的功耗管理策略,可以降低系统的功耗,延长电池寿命。

4.可靠性设计:片上系统设计需要考虑到系统的可靠性和稳定性。

通过采用冗余设计、错误检测与纠正技术、温度与电压管理等手段,可以提高系统的可靠性和容错性。

嵌入式系统中的片上系统设计与实现技术

嵌入式系统中的片上系统设计与实现技术嵌入式系统是指将计算机技术与各种应用领域相结合,嵌入到具体的产品或设备中,并且能够完成特定任务的一种计算机系统。

在嵌入式系统中,片上系统(SoC)被广泛应用。

片上系统是指将计算机核心、存储系统、通信接口、外设、调度器等功能集成到一个芯片上,形成一个完整的计算机系统。

片上系统设计与实现技术是嵌入式系统开发中的核心内容,具有重要意义。

下面将详细介绍一些嵌入式系统中的片上系统设计与实现技术。

1. 硬件设计技术:片上系统的硬件设计是整个系统的基础,包括处理器核心的选择与设计、存储系统的设计、通信接口的设计、外设的设计等。

在选择处理器核心时,需要考虑功耗、性能、可编程性等因素;在设计存储系统时,需要根据应用需求选择合适的存储器类型,如RAM、Flash等,并合理设计存储器的组织结构;在设计通信接口时,需要根据数据传输的要求选择合适的接口类型,如UART、SPI、I2C等;在外设的设计中,需要根据具体应用需求选择适当的传感器、执行器等外设。

2. 软件设计技术:片上系统的软件设计是指针对具体应用需求,为系统开发相应的软件。

软件设计包括编写驱动程序、编写嵌入式操作系统、编写应用软件等。

在编写驱动程序时,需要充分了解硬件的特性和功能,充分利用硬件资源,提高系统性能;在编写嵌入式操作系统时,需要选择合适的操作系统,如Linux、RTOS等,并为系统开发相应的设备驱动程序和应用服务;在编写应用软件时,需要根据具体应用需求,设计相应的算法和实现。

3. 片上系统的布局与布线技术:片上系统中,各个功能模块需要相互连接,完成数据传输与处理。

布局与布线技术是指将各个模块在芯片上合理排布,并设计合理的连线。

在布局时,需要考虑各个功能模块之间的连接关系,尽量减少信号传输的路径长度,降低传输时延和功耗;在布线时,需要根据信号传输的特性,选择合适的线宽和线距,保证信号传输的质量。

4. 功耗优化技术:在嵌入式系统中,功耗是一个重要的性能指标。

计算机硬件设计中的时序与时钟控制技术

计算机硬件设计中的时序与时钟控制技术计算机硬件设计中的时序与时钟控制技术在现代计算机体系结构中起着至关重要的作用。

时序是指计算机中各个组件按照一定的顺序和时间执行操作的过程,而时钟控制技术则是保证各个组件能够在正确的时序下进行协同工作的关键手段。

本文将介绍计算机硬件设计中的时序与时钟控制技术的基本原理和应用。

一、时序的概念和作用时序是计算机硬件设计中一个非常重要的概念,它涉及到计算机中各个组件的工作顺序和时机。

在计算机的执行过程中,不同的指令和数据需要在不同的时间进行处理和传输,如果没有合理的时序控制,就会导致数据错乱、功能错误等问题。

因此,时序在计算机硬件设计中扮演着关键的角色。

二、时序的设计方法和原则在计算机硬件设计中,时序的设计是一个相当复杂的过程,需要考虑多方面的因素。

下面介绍几种常见的时序设计方法和原则。

1.同步时序设计同步时序设计是指在时钟信号的控制下,各个硬件组件按照统一的时间步进进行操作。

这种设计方法具有简单、可控性高的特点,是目前普遍采用的设计方式。

在同步时序设计中,时钟信号的频率和稳定性对于系统的正常工作至关重要。

2.异步时序设计异步时序设计是指在没有统一的时钟信号下,各个硬件组件通过信号传递实现相互之间的协同工作。

这种设计方法在特定的场合下具有一定的优势,特别适用于对功耗、响应时间等有特殊要求的系统。

不过,异步时序设计的复杂度和可调试性相对较低,需要谨慎使用。

3.时序设计原则在进行时序设计时,需要遵循一些基本的原则,以确保系统的可靠性和性能。

首先是正确的数据路径设计,即保证数据的正确流动和传输。

其次是适当的优化设计,尽量减少硬件组件之间的冲突和延迟。

此外,还需要合理地划分时钟域和时钟分频,以适应不同频率和时序的要求。

三、时钟控制技术的应用时钟控制技术在计算机硬件设计中的应用非常广泛,下面介绍几个常见的应用场景。

1.时钟配置和分频通过对时钟信号的配置和分频,可以实现对系统时序和性能的调整。

CSP三大主流结构及现有LED的替代性

CSP三大主流结构及现有LED的替代性发布日期:2015-05-29 稿源:互联网编辑:Jane核心提示:CSP的全称是ChipScalePackage,中文意思是芯片级封装器件,指的是封装尺寸小于芯片尺寸1.2倍的封装器件。

CSP的全称是ChipScalePackage,中文意思是芯片级封装器件,指的是封装尺寸小于芯片尺寸1.2倍的封装器件,三星出货量最大的LM-131A的芯片尺寸是0.78*0.78mm,封装尺寸是1.42*1.42,严格来说目前主流芯片厂商的封装尺寸都不满足此要求,所以称为CSP有点不严谨。

无封装芯片的叫法是从台湾引入,因为芯片没有经过传统的固晶和焊线这些封装流程,因此俗称无封装芯片。

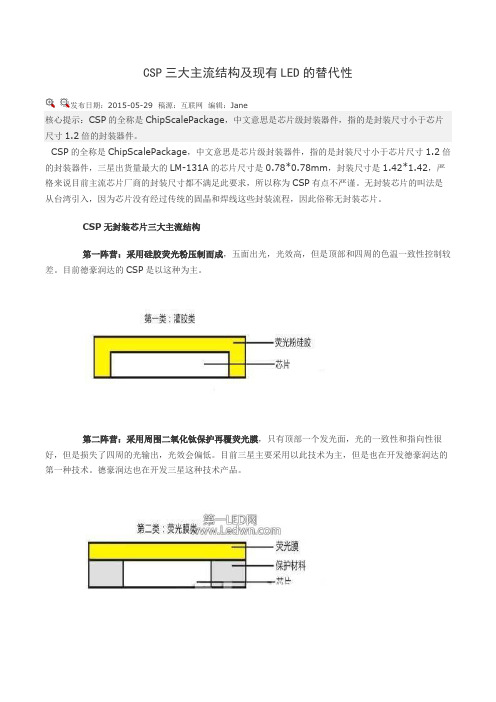

CSP无封装芯片三大主流结构第一阵营:采用硅胶荧光粉压制而成,五面出光,光效高,但是顶部和四周的色温一致性控制较差。

目前德豪润达的CSP是以这种为主。

第二阵营:采用周围二氧化钛保护再覆荧光膜,只有顶部一个发光面,光的一致性和指向性很好,但是损失了四周的光输出,光效会偏低。

目前三星主要采用以此技术为主,但是也在开发德豪润达的第一种技术。

德豪润达也在开发三星这种技术产品。

第三阵营:采用荧光膜全覆盖,再加透明硅胶固定成型,也是五面出光,光效高,光品质稍差,此款主要是飞利浦采用。

在此值得一提的是,另外市面上还有一款自称为CSP的,是带有基板的,虽然也可以做到小体积,但是不是最终形态。

取代传统LED三大应用领域CSP最早使用是在背光和闪光灯,目前苹果和三星的手机闪光灯都是使用CSP无封装芯片,三星和LG的超薄电视部分使用的CSP无封装芯片。

在照明行业,CSP因为体积小,灵活度高,应用范围将越来越广泛。

目前主要表现在三个领域:第一、可以直接替代中功率和大功率。

第二种是多颗矩阵排列,替代COB,因为灯珠间距问题,暂时不能满足光斑要求特别高的小角度射灯。

但是据燧明研发负责人傅海勇表示,此款CSP技术还是有机会代替COB的,成像的原因好解决。

高性能计算机的设计及其应用领域

高性能计算机的设计及其应用领域随着科技的发展,计算机技术越来越成为人们日常生活中必不可少的一部分。

在各种领域中,高性能计算机作为重要的计算设备,已经成为了科学研究、经济运营、军事防卫等各个领域中不可或缺的工具。

本文将探讨高性能计算机的设计及其应用领域。

一、高性能计算机的设计高性能计算机是一种基于大规模并行处理器、分布式操作系统和高速网络等技术的计算设备。

它能够完成更加复杂和庞大的计算任务,具有高速、高效、高可靠的特点。

高性能计算机的设计应该考虑以下几个方面:1.硬件设计在硬件方面,高性能计算机需要采用大量的处理器和内存来提供强大的计算能力。

并行处理器作为高性能计算机的核心,能够使不同的处理器同时进行计算,提高计算速度。

此外,高速网络也是高性能计算机的必要组成部分,它可以在不同的处理器之间进行数据传输。

2.软件设计高性能计算机的软件设计应该充分利用并行处理器的特性,使得不同的处理器可以同时进行计算。

此外,还需要选择适当的并行操作系统和开发环境,开发高效的并行算法。

3.能耗设计高性能计算机的能耗一般非常高,因此在设计时需要尽可能地降低其能耗,同时提高其能源利用率。

这可以通过采用低功耗组件、改进计算节点的能源利用率等方式来实现。

二、高性能计算机的应用领域高性能计算机的应用领域非常广泛,包括科学研究、工程计算、金融交易、天气预报、医学诊断等诸多领域。

1.科学研究高性能计算机在科学研究中的应用已经成为了必不可少的一部分。

高性能计算机能够为各种科学研究提供强大的计算支持,例如大型天文学和计算化学等领域。

2.工程计算工程计算领域中,高性能计算机通常用于计算机模拟、可视化和工程优化等方面。

例如,在航空工程领域中,高性能计算机可以处理空气动力学、结构实验和材料科学等方面的极其复杂的计算需求。

3.金融交易在金融交易领域中,高性能计算机经常用于高速交易和风险控制策略的优化。

高性能计算机可以提供大数据量计算能力,以便进行更加准确的交易决策。

超级计算机设计方案

超级计算机设计方案正文:随着科技的不断发展,计算机的性能与功能需求日益增加。

传统的计算机已经无法满足大规模数据处理和复杂计算任务的要求,因此超级计算机的设计与研发成为了当下科技领域的热点之一。

本文将介绍一种创新的超级计算机设计方案,以满足高性能计算的需求。

一、背景与需求分析超级计算机是一种具备超强计算能力和海量存储能力的计算机系统,被广泛应用于天气预报、大规模数据分析、模拟计算等领域。

然而,传统的超级计算机在面对日益庞大和复杂的计算任务时,性能和效率逐渐滞后。

因此,我们需要设计一种全新的超级计算机,以满足未来高性能计算的需求。

二、设计方案1. 架构设计针对超级计算机的需求,本设计方案采用“异构计算”的架构。

该架构通过将多个不同类型的处理器和加速器结合起来,发挥各自的优势,实现高效的计算能力。

(1)中央处理器(CPU):采用最新的多核处理器,以提供强大的通用计算能力和灵活性。

(2)图形处理器(GPU):利用GPU的并行计算优势,加速计算任务的执行速度,并实现高性能的图像渲染。

(3)领域专用加速器(FPGA):根据具体应用需求,设计和集成定制化的加速器,提供针对特定计算任务的极高效能。

2. 存储系统设计超级计算机对于存储系统的需求也非常高,因此本设计方案提出了以下存储系统设计方案:(1)高速缓存:采用多级缓存设计,以提供更快的数据访问速度和更高的缓存命中率。

(2)分布式存储:通过将存储设备分布在多个节点上,实现数据的并行读写和高速传输,从而提高整体存储系统的性能。

(3)闪存存储:利用固态硬盘(SSD)的高速读写能力,替代传统的机械硬盘,提供更快的数据传输速度。

3. 系统互连技术为了实现高速的数据传输和通信,本设计方案采用了先进的系统互连技术,包括:(1)光纤通信:采用光纤通信技术实现节点间的高速数据传输,以支持分布式存储和分布式计算。

(2)融合互连:通过融合互连技术,实现多种不同类型设备的互联,实现高效的数据共享和通信。

计算机硬件设计中的时序约束与验证

计算机硬件设计中的时序约束与验证计算机硬件设计是一个复杂而精密的工程,其中涉及到许多关键因素,如时序约束和验证。

时序约束是指在硬件设计中对信号传播和设备响应的时序要求,而时序验证则是用于确保这些时序约束得到满足的过程。

本文将介绍计算机硬件设计中的时序约束与验证的重要性以及相关技术与方法。

一、时序约束的重要性时序约束是确保硬件设计功能正确性和稳定性的关键要素之一。

在计算机系统中,各个复杂的硬件模块通过信号进行通信和交互。

如果这些信号的传输时间超出规定的时序范围,就会导致数据错误、系统不稳定甚至系统崩溃。

因此,时序约束的定义和遵守对于保证系统的正常运行至关重要。

二、时序约束的定义和表示时序约束的定义和表示是确保硬件设计正确实现的基础。

通常情况下,时序约束是通过时序约束语言(如SDC)来定义和表示的。

时序约束语言是一种描述时序约束的形式化语言,它可以准确地定义信号即时性、时钟周期等时序约束的要求。

通过使用时序约束语言,设计人员可以明确地指定每个信号的时序要求,确保硬件设计满足所需的时序特性。

三、时序约束的验证方法时序约束的验证是确保硬件设计有效的关键步骤。

在时序约束的验证过程中,主要有两种方法:模拟验证和形式验证。

模拟验证是通过模拟仿真来验证硬件设计是否满足时序约束。

设计人员将时序约束应用于设计中,并进行仿真测试以确保信号传输时间、时钟周期等时序特性符合约束要求。

模拟验证通常是验证时序约束的常用手段,可以辅助设计人员找到并解决潜在的时序问题。

形式验证是通过数学推理和验证技术来验证硬件设计是否满足时序约束。

它使用形式方法对设计进行抽象建模,并通过数学推理来证明设计满足约束要求。

形式验证可以在设计的早期阶段发现潜在的时序问题,有效地提高设计的质量和可靠性。

四、时序约束的优化与调整在硬件设计过程中,时序约束的优化与调整对于提高系统性能和稳定性至关重要。

优化与调整时序约束的常见方法有如下几种:1. 时钟频率调整:通过调整时钟频率可以对系统时序约束进行优化。

高性能计算机的设计和优化

高性能计算机的设计和优化随着科技的不断进步和发展,人们对于计算机的性能和效率的要求也越来越高。

尤其是在大数据、人工智能和高端科学研究等领域,高性能计算机已经成为了必不可少的工具。

如何设计和优化高性能计算机的性能,成为当前计算机领域的重大课题。

本文将会从硬件、软件等方面,探讨高性能计算机的设计和优化,为读者提供参考和启发。

一、硬件设计高性能计算机的硬件设计中,最基本的目标是提升计算机的运算速度和处理能力。

为了实现这个目标,计算机必须要考虑如下方面:1.储存器和存储技术在硬件设计中,储存器是一个很重要的环节,因为CPU在处理信息时需要从储存器中取得数据,如果储存器不能及时为CPU提供数据,CPU就需要等待,从而影响计算机的效率。

因此,设计者需要考虑如何提高储存器的访问速度和容量,以便加快CPU的处理速度。

此外,存储技术也是一个值得研究的方向。

近年来,固态硬盘等新兴的存储技术已经成为了热门话题。

固态硬盘的读写速度比传统硬盘大幅提高,而且容量也比传统硬盘大得多,这都能够为高性能计算机的性能提升提供有力支持。

2.网络带宽和带宽管理高性能计算机的数据传输十分频繁,网络带宽成了决定计算机性能的一大瓶颈。

因此,设计者需要采用更高速的网络技术,如100G网卡、光纤等。

此外,带宽管理也很重要,因为不同任务需要的带宽大小不同。

若某个任务需要非常大的带宽,却被其他任务占用了,则会影响计算机的性能。

3.多核结构和集成电路多核结构是目前高性能计算机的主流选择。

多核CPU在提高计算机的运算速度上具有明显的优势。

对于单个任务,多核CPU能够并行处理,而且也可以并行处理多个任务。

而集成电路的优势在于,能够将多个模块集成到一个芯片上,从而降低了计算机的功耗和体积,并提高了计算机的可靠性。

二、软件优化在高性能计算机的软件设计和优化中,主要目标是提高软件算法的并行度和优化程序的运行效率,以期提高计算机的整体性能。

1.并行计算对于高性能计算机而言,尝试将计算任务并行化是一个很重要的方向。

超级计算机的软硬件研究与应用

超级计算机的软硬件研究与应用随着人工智能、云计算、大数据等领域的快速发展,各种高性能计算设备的需求逐渐增强。

超级计算机作为高性能计算设备中的佼佼者,发挥着越来越重要的作用。

本文将针对超级计算机的软硬件研究与应用进行讨论。

一、超级计算机的硬件研究超级计算机的硬件主要由处理器、存储器、网络和系统架构等几个方面组成。

在这些方面的升级和优化,都能为超级计算机的性能提升作出贡献。

1. 处理器处理器是计算机的核心部分,直接决定着计算机的性能。

在超级计算机领域,目前常用的处理器有Intel、AMD、IBM等。

而且由于需要在超级计算机上进行并行计算,所以处理器的核心数也很重要。

因此,研究优化处理器的核心和性能是当前硬件研究的热点之一。

2. 存储器存储器也是决定计算机性能的重要因素。

在超级计算机中,存储器通常被分成主存储器和辅助存储器两种。

主存储器是指CPU可以直接访问的存储器,而辅助存储器则需要通过I/O接口来访问。

因此,提升主存储器的速度和容量也是超级计算机硬件研究的重点之一。

3. 网络网络是超级计算机硬件研究中的另一个重要因素。

在超级计算机中,涉及到大量的数据传输,在这个过程中,网络的传输速度和传输质量直接关系到计算机性能的提升。

因此,研究网络互连技术,提升数据传输的速度和稳定性,也是当前硬件研究的重点之一。

4. 系统架构超级计算机的系统架构是决定其性能的关键因素之一。

随着硬件技术的发展,当前广泛应用的多处理器体系结构(SMP)已经不能满足超级计算机对于高并行性能的需求。

因此,研究新型的系统架构,如海量并行处理器体系结构等,成为了当前超级计算机硬件研究的趋势之一。

二、超级计算机的软件研究超级计算机的软件研究主要包括操作系统、应用软件和编程模型等方面。

这些方面的研究均能够提升超级计算机的性能和可用性。

1. 操作系统操作系统是计算机软件的基本组成部分,它直接关系到计算机的运行效率和稳定性。

在超级计算机领域,研究针对超级计算机的专门操作系统,以及操作系统的定制化是非常必要的。

python代码timeout机制框架

python代码timeout机制框架Python是一种高级编程语言,它在许多领域都得到了广泛的应用。

然而,编写Python代码时,有时会遇到一些耗时的操作,例如网络请求、繁重的计算或等待外部程序的返回结果。

这些耗时操作可能会导致程序长时间无响应,给用户带来不良体验。

为了解决这个问题,我们可以使用timeout机制来设置一个时间限制,超过该限制的操作将被中断,以保证程序的稳定性和性能。

在Python中,我们可以使用多种方法来实现代码的timeout机制。

下面,我将介绍一种常见的timeout机制框架,以帮助读者更好地理解和应用这个概念。

一、使用signal来设置timeoutsignal是Python中的一个内置模块,它提供了处理信号的功能。

我们可以使用signal模块来捕获SIGALRM信号,并在信号到达时中断程序的执行。

下面是一个使用signal设置timeout的示例代码:```pythonimport signalimport timeclass TimeoutException(Exception):passdef handler(signum, frame):raise TimeoutException()def your_function():# 在这里编写你的耗时操作time.sleep(5)signal.signal(signal.SIGALRM, handler)signal.alarm(3) # 设置3秒的超时时间try:your_function()except TimeoutException:print("Timeout!")else:signal.alarm(0) # 取消超时设置print("Completed!")```在上述代码中,我们首先定义了一个TimeoutException异常,用于在超时时抛出。

然后,我们定义了一个handler函数,用于捕获SIGALRM信号,并抛出TimeoutException异常。

计算机硬件设计中的时序约束与验证方法

计算机硬件设计中的时序约束与验证方法在计算机硬件设计中,时序约束和验证是非常重要的环节。

时序约束用于确保电子系统的正常工作,验证方法则是验证系统是否符合这些约束。

本文将深入探讨计算机硬件设计中的时序约束和验证方法。

一、时序约束的概念和重要性时序约束是指在电子系统中确定各个时钟信号、数据信号以及状态转换的时间关系,以确保电子系统的正确运行。

时序约束描述了设计中关键信号的时序特性,如时钟周期、最大延迟等。

时序约束的正确性对于系统的稳定性、可靠性和性能都具有重要影响。

二、时序约束的设置方法时序约束的设置需要考虑到电路中各个部件之间的数据传输时序。

一般来说,时序约束可以通过一些工具或语言来进行设置,如时序约束语言(SDDL)、时序约束编写语言(SDCL)等。

这些工具和语言都具有自己的语法和规则,可以精确地描述时序约束。

三、常见的时序约束类型1. 时钟信号相关的时序约束:时钟频率、时钟占空比等。

这些约束确保时钟信号的稳定性和可靠性。

2. 数据通路相关的时序约束:数据的传输速率、数据的有效时间等。

这些约束确保数据在各个部件之间正确地传递。

3. 状态转换相关的时序约束:状态的切换时间、状态的保持时间等。

这些约束确保状态之间的转换正确且可靠。

四、时序约束的验证方法1. 仿真验证:通过使用仿真工具,对电路进行仿真测试,验证电路是否满足时序约束。

仿真验证可以提前发现问题,并进行调试和优化。

2. 静态时序分析:使用静态时序分析工具,对电路的时序约束进行静态分析。

这种方法可以在设计阶段发现潜在的时序问题,并指导调整设计。

3. 时序约束检查:通过时序约束检查工具,对设计中的时序约束进行检查和验证。

这种方法可以自动检查设计是否符合时序约束,提高设计的准确性和效率。

五、时序约束的优化和调整在设计过程中,可能会出现时序约束不满足的情况。

此时,需要进行优化和调整,以确保时序约束的满足。

常见的方法包括增加时钟频率、优化电路结构、进行时钟域划分等。

计算机时序的名词解释

计算机时序的名词解释计算机时序是一个与计算机硬件和软件紧密相关的概念,它主要描述了计算机内部各个组件之间操作的顺序和时间间隔。

在计算机体系结构中,时序是确保计算机各个部件正确协同工作的重要因素之一。

本文将对计算机时序的一些关键名词进行解释,以便读者更好地理解这个领域。

时钟周期(Clock Cycle)是计算机时序的重要指标之一。

它是计算机中最基本的计时单位,也被称为时钟振荡器的一个完整周期。

时钟周期通常以纳秒(ns)为单位,用来描述计算机的工作频率。

现代计算机的时钟周期可以达到几纳秒甚至更低。

时钟周期的频率越高,计算机执行指令和处理数据的速度也就越快。

时钟信号(Clock Signal)是计算机体系结构中的一个核心元素。

时钟信号通过时钟发生器产生,它在计算机内部各个组件之间传递,驱动着计算机的工作。

时钟信号从发生器发出后,在整个计算机系统中以恒定的频率传递,确保各个组件按照同步的方式进行操作。

在一个时钟周期内,各个指令的执行和数据的传输必须与时钟信号的上升沿和下降沿对齐。

时序逻辑(Sequential Logic)是计算机中一种重要的逻辑设计方式。

相对于组合逻辑,时序逻辑引入了时钟信号的概念,通过时钟信号的作用来实现状态的存储和转换。

时序逻辑中的触发器和寄存器等元件能够将当前的输入和上一个状态共同决定输出的数值。

这种状态存储和转换的方式使得计算机能够处理更复杂的问题。

时序调度(Timing Scheduling)是计算机操作系统中的一个关键概念。

它涉及到任务的启动、执行和结束的时序控制。

在多任务系统中,时序调度通常通过调度算法来实现。

这些算法能够合理地分配和调度计算机资源,使得各个任务能够按照一定的时序顺序执行,从而提高系统的效率和响应速度。

时序性能(Timing Performance)是评估计算机系统性能的重要指标之一。

时序性能描述了计算机处理和执行指令的速度和效率,通常以时钟周期的数目来衡量。

延时程序设计

延时程序设计延时程序设计概述延时程序设计是指在计算机程序中设置延时等待的技术。

在某些需要延时一段时间后再进行下一步操作的应用场景中,延时程序设计能够提供一个简单、灵活的解决方案。

延时的作用延时的作用在于控制程序执行的时间间隔,以实现程序在特定时间后执行下一步操作的目的。

在许多应用程序中,延时是必不可少的技术,尤其是涉及到与外部设备或其他系统交互的情况下。

延时可以用于实现以下几个功能:- 控制程序的执行速度:通过延时可以限制程序的执行速度,使其与其他设备或系统的速度相匹配,避免数据丢失或冲突。

- 时间调度:通过延时可以实现程序在指定时间点进行某些操作,例如定时任务、周期性任务等。

- 模拟等待:在某些情况下,需要程序等待一段时间再进行下一步操作,以模拟人的行为或特定环境下的时间延迟。

延时的实现方法延时程序设计可以通过多种方式实现,以下是几种常见的方法:1. 休眠方法休眠方法是最简单粗暴的延时实现方式,通过让程序线程休眠一段时间来实现延时效果。

在大多数编程语言中,都提供了相应的休眠函数或方法,例如C/C++中的`sleep()`函数,Java中的`Thread.sleep()`方法,Python中的`time.sleep()`函数等。

这种方式的优点是简单易用,但缺点是占用系统资源较多,不适用于需要高精度延时的应用场景。

2. 循环方法循环方法是一种基于计数的延时实现方式,通过循环执行空操作来消耗一定的时间。

这种方式的原理是根据计算机的执行速度来确定循环的次数,以实现预期的延时效果。

循环方法的优点是对系统资源占用较少,适用于需要高精度延时的应用场景,但缺点是需要根据硬件和操作系统的性能差异进行调整。

3. 定时器方法定时器方法是一种基于硬件定时器的延时实现方式,通过设置定时器的计数器和时钟频率来实现精确的延时效果。

大多数现代计算机都配备了硬件定时器,可以通过操作系统提供的接口来设置定时器的相关参数。

定时器方法的优点是精确度高,可实现微秒级别的延时,但缺点是需要操作系统和硬件的支持,不适用于所有平台。

汇顶数字芯片 数字后端 笔试题 (2)

汇顶数字芯片数字后端笔试题标题:汇顶数字芯片数字后端笔试题引言概述:汇顶数字芯片是一家专注于集成电路设计与制造的公司,数字后端是其产品设计流程中至关重要的一环。

本文将从五个大点出发,详细阐述数字后端的相关知识和技术。

正文内容:一、物理设计1.1 布局设计:包括芯片的功能模块划分、电路的布局和连线规划。

1.2 布线设计:根据布局设计完成的电路图,进行信号线的布线和优化,以满足性能和功耗要求。

二、时序设计2.1 时钟树设计:设计时钟分配网络,确保信号的同步和稳定。

2.2 时序约束:定义电路中各个时序要求,如时钟频率、时钟延迟等。

2.3 时序分析:通过时序约束,对电路进行时序分析,确保电路的正确性和稳定性。

三、功耗优化3.1 逻辑优化:通过逻辑综合和优化技术,减少电路中的逻辑门数量,降低功耗。

3.2 电源规划:合理规划芯片中的电源供应网络,减小功耗。

3.3 时钟优化:通过时钟门控和时钟门控优化技术,减少功耗。

四、物理验证4.1 电路仿真:使用仿真工具对电路进行验证,确保电路的功能和性能。

4.2 物理验证:对芯片的物理设计进行验证,包括电路布局和布线的正确性和稳定性。

4.3 时序验证:通过时序约束和时序分析,对电路的时序进行验证。

五、版图设计5.1 布局规划:将电路的功能模块进行适当布局,满足性能和功耗要求。

5.2 布线规划:根据布局规划完成的电路图,进行信号线的布线和优化。

5.3 版图优化:通过布局规划和布线规划,对电路进行优化,满足性能和功耗要求。

总结:数字后端是汇顶数字芯片设计流程中不可或缺的环节。

物理设计、时序设计、功耗优化、物理验证和版图设计是数字后端的五个重要方面。

物理设计涉及布局设计和布线设计,时序设计包括时钟树设计、时序约束和时序分析。

功耗优化主要涉及逻辑优化、电源规划和时钟优化。

物理验证包括电路仿真、物理验证和时序验证。

版图设计包括布局规划、布线规划和版图优化。

通过这些方面的工作,数字后端能够确保芯片的功能和性能达到预期,并满足设计要求。

斯托米硬件测试技术案

使用原子哥的fsmc寄存器驱动LCD程序,我的RS接在了A0(PF0)其他都和程序里的接法一样,下面红色部分是我修改的部分,现在出现了比较奇怪的现象,就是我把A0弄成推免复位输出就读不到ID,设成其他状态就可以得Data>>8 //data右移八位相当于除以256对吗?我们来看看:假如data= 1111 0110 1001 1011 0110 1011 1101 1010执行左移八位后变成了data1= 0000 0000 1111 0110 1001 1011 0110 1011data= 1111 0110 1001 1011 0110 1011 1101 1010 = 4137380826data1= 0000 0000 1111 0110 1001 1011 0110 1011 = 16161643看来他吗的是完全正确的哦硬件测试的目的就是站在用户的角度,对产品的功能、性能、可靠性、兼容性、稳定性等进行严格的检查,体验用户感受的同时提高产品的质量及市场竞争力。

硬件测试是产品从研发走向生产的必经阶段,也是决定产品质量、降低产品的全寿命周期费用的重要环节,如何将测试工作开展的更全面、更仔细、更专业完善也是众多企业不断追求的目标。

在产品设计阶段,可以对产品设计原型进行虚拟测试,验证设计方案,排除可能的设计缺陷;在生产阶段,可以对产品进行全面的测试,排除产品的潜在故障,从而降低使用过程中的故障率,提高产品的质量和可靠性。

另一方面,可测试性技术可以缩短新产品的研制、试验和评价的周期,降低产品的研制费用,不仅如此,还可以提高产品的可用性、可维护性等指标,减少用于这些方面的费用,从而降低了产品的全寿命周期费用。

到ID9320,还请大侠帮帮我分析下,typedef struct{u16 LCD_REG;u16 LCD_RAM;} LCD_TypeDef;//使用NOR/SRAM的 BANK 4,地址位HADDR[27,26]=11 A10作为数据命令区分线//注意设置时STM32内部会右移一位对其! 111110=0X3E#define LCD_BASE ((u32)(0x6C000000 | 0x0C000002))#define LCD ((LCD_TypeDef *) LCD_BASE)---------------------------------------------------------------------------------------------------1、硬件测试概述硬件测试目的、测试需求的来源;测试的基本原则;硬件测试种类、硬件测试流程技术;2、硬件测试准备技术FMEA(故障模式影响分析)、测试计划;硬件可测试性设计、内涵;产品可测试性设计的必要性;PCB 可测试性的条件、一般要求、策略、影响PCB测试策略的参数;在线测试对印制电路板设计的要求、板的尺寸和节点数;DFT规则的使用、遵守或理解;测试点的可访问性、设置准则、尺寸要求;测试焊盘的尺寸、定位孔要求、器件特殊引脚的处理;功能测试方面的可测性设计要求;PCB可测试性的关键技术及发展;Ad-hoc测试、扫描技术;内建自测技术(BIST)、几种可测试性技术比较、测试的安全措施;void LCD_Init(void){RCC->AHBENR|=1<<8; //使能FSMC时钟RCC->APB2ENR|=1<<3; //使能PORTB时钟RCC->APB2ENR|=1<<5; //使能PORTD时钟RCC->APB2ENR|=1<<6; //使能PORTE时钟RCC->APB2ENR|=1<<7; //使能PORTE时钟RCC->APB2ENR|=1<<8; //使能PORTG时钟RCC->APB2ENR|=1<<0; //使能AFIO时钟GPIOG->CRL&=0XFFFF0FFF;//PG3 推挽输出背光GPIOG->CRL|=0X00003000;//PORTD复用推挽输出GPIOD->CRH&=0X00FFF000;GPIOD->CRH|=0XBB000BBB;GPIOD->CRL&=0XFF00FF00;GPIOD->CRL|=0X00BB00BB;//PORTE复用推挽输出GPIOE->CRH&=0X00000000;GPIOE->CRH|=0XBBBBBBBB;GPIOE->CRL&=0X0FFFFFFF;GPIOE->CRL|=0XB0000000;//PORTF复用推挽输出3、PCA工艺测试技术PCB测试、再流焊实时温度曲线测试技术;PCB的测试方法;手工视觉、X-Ray测试;自动光学检查(AOI)、飞针测试机、ICT测试机、电路板故障检测仪;GPIOF->CRL&=0XFFFFFFF0;GPIOF->CRL|=0X0000000B; //如果去掉就可以得到ID:9320//PORTG12复用推挽输出 A0GPIOG->CRH&=0XFFF0FFFF;GPIOG->CRH|=0X000B0000;GPIOG->ODR |= 1 << 3; //PE0输出高4、PCA电气测试技术低频电路测试技术、各种元器件特性曲线;测试高速电路测试技术、SI分析、信号完整性的仿真、示波器的使用、数字示波器探头选用;传输线特性阻抗、集总式电路特性测试技术;信号质量测试:信号质量测试方法、硬件信号质量测试案例;驱动器电源噪声串扰导致数据线毛刺、过冲和毛刺使FLASH芯片工作异常、损坏率高;信号时序测试:信号时序测试条件、测试覆盖范围、测试参数、测试过程;时序测试案例;信号时序紧张,造成误码严重容差、容错定量测试(操作容限测试)、附加噪声、调节宽总线上的定时;通过同轴电缆延时调节时钟、通过脉冲发生器调节时钟;用于时钟相位调节的简单电路、用锁相环调节时钟;通过改变电压调节时钟;供电、温度、数据吞吐量、硬件测试自动化技术;射频电路测试技术;u16 a;int main(void){Stm32_Clock_Init(9);//系统时钟设置delay_init(72);uart_init(72,9600);LCD_Init();LCD_ShowString(0,0,"START INITing...");while(1)//初始化ov7670{a = LCD_ReadReg(0x0000);printf(" LCD ID:%x\n", a ); //打印LCD IDLCD_ShowString(0,0,"TEST OK");delay_ms(511);LCD_ShowString(0,0," ");};}5、硬件安全测试技术防电击、电气间隙和爬电距离测试;介电强度、供电电源的断开试验;产品防机械危险检验;产品耐机械冲击、撞击试验;设备温度限制和防止火的蔓延、耐热试验、元器件、开关电源安规测试;小功率电动机检测、锂离子电池安全性;注销掉GPIOF->CRL&=0XFFFFFFF0;GPIOF->CRL|=0X0000000B;得到的数据USmart处理从PC丢到STM32串口数据的方法:1. 在串口的中断处理函数USART1_IRQHandler将串口数据填在全局数组USART_RX_BUF中;2. 另外有一个Tim2在不停检查标志位SART_RX_STA&0x8000,如果表示串口接收完成,处理全局数组USART_RX_BUF;由于Timer的数量有限,是否可以不使用Timer,直接在串口中断处理函数USART1_IRQHandler中,调用一个函数Parse_Rx_Buf来处理USART_RX_BUF?本人实验下来的结果是:大多数情况下没有问题。

st语言timer案例

st语言timer案例Timer是一种用于计时的设备,它可以在特定的时间间隔内执行特定的任务。

在ST语言中,Timer被广泛应用于工业自动化领域,用于控制各种设备的运行时间和周期。

下面是关于ST语言中Timer 的一些实际案例。

1. 控制机器人的运行时间在工业生产线上,机器人通常需要按照特定的时间间隔运行。

通过使用Timer,可以设置机器人的运行时间,并在时间到达后停止机器人的运行。

这样可以保证机器人的工作效率,并且避免机器人长时间无效运行。

2. 控制灯光的闪烁间隔在舞台灯光控制系统中,常常需要设置灯光的闪烁间隔。

通过使用Timer,可以设置灯光的闪烁时间和停止时间,并在时间到达后控制灯光的开关,实现灯光的闪烁效果。

3. 控制电梯的开关门时间在大楼电梯系统中,电梯的开关门时间需要精确控制。

通过使用Timer,可以设置电梯的开门时间和关门时间,并在时间到达后控制电梯门的开关,确保电梯运行的安全和顺畅。

4. 控制输送带的运行时间在物流系统中,输送带通常需要按照特定的时间间隔运行。

通过使用Timer,可以设置输送带的运行时间和停止时间,并在时间到达后控制输送带的开关,实现物品的顺利运输。

5. 控制空调的运行时间在办公室和家庭中,空调的运行时间需要合理控制,以节省能源并提供舒适的环境。

通过使用Timer,可以设置空调的开启时间和关闭时间,并在时间到达后控制空调的开关,实现节能和舒适度的平衡。

6. 控制喷淋系统的喷水时间在农业灌溉系统中,喷淋系统需要按照特定的时间间隔进行喷水。

通过使用Timer,可以设置喷淋系统的喷水时间和停止时间,并在时间到达后控制喷淋系统的开关,实现农作物的合理灌溉。

7. 控制家用电器的定时开关在家庭中,一些家用电器需要按照特定的时间进行定时开关。

通过使用Timer,可以设置家用电器的开启时间和关闭时间,并在时间到达后控制家用电器的开关,实现家庭生活的便利和舒适。

8. 控制交通信号灯的切换时间在城市交通系统中,交通信号灯需要按照特定的时间间隔进行切换。

延迟时序电路

延迟时序电路延迟时序电路是一种电子电路,用于延迟输入信号的传输和处理时间。

它在许多电子设备和系统中广泛应用,如计算机、通信设备、测量仪器等。

延迟时序电路可以通过调整电路中的延迟元件和逻辑门的延迟时间来实现不同的延迟效果。

1. 延迟时序电路的原理延迟时序电路的原理基于信号传输的延迟和逻辑门的延迟。

在一个典型的延迟时序电路中,输入信号首先经过一个延迟元件,如延迟线或延迟器。

延迟元件会使信号的到达时间延迟一段时间,这取决于延迟元件的特性和设计。

延迟元件后面通常会连接一些逻辑门,如与门、或门、非门等。

逻辑门的延迟时间也会对信号的传输时间产生影响。

通过调整延迟元件和逻辑门的延迟时间,可以实现不同的延迟效果。

延迟时序电路还可以包括一些辅助元件,如触发器、计数器等。

这些元件可以用于控制延迟时序电路的工作状态和延迟时间。

2. 延迟时序电路的应用延迟时序电路在许多领域都有广泛的应用。

2.1 计算机系统在计算机系统中,延迟时序电路被广泛用于处理器和存储器之间的数据传输。

由于处理器和存储器之间的距离较远,信号传输需要一定的时间。

延迟时序电路可以通过调整延迟时间来确保数据在正确的时间到达目的地,从而保证计算机系统的正常运行。

2.2 通信设备在通信设备中,延迟时序电路可以用于调整信号的传输时间,从而实现数据的同步和解调。

延迟时序电路可以通过调整延迟时间来匹配不同设备之间的传输速率,从而确保数据的准确传输。

2.3 测量仪器在测量仪器中,延迟时序电路可以用于延迟输入信号的时间,以便测量仪器能够准确地采集和处理数据。

延迟时序电路可以通过调整延迟时间来匹配测量仪器的采样速率,从而确保测量结果的准确性。

3. 延迟时序电路的设计设计一个延迟时序电路需要考虑以下几个方面:3.1 延迟元件的选择延迟元件的选择取决于所需的延迟时间和电路的工作频率。

常用的延迟元件包括延迟线、延迟器、电容和电感等。

延迟线和延迟器可以提供较大的延迟时间,而电容和电感则可以提供较小的延迟时间。

硬件延时电路

硬件延时电路硬件延时电路是一种用于控制和调整电信号传输延迟的电路。

它常常应用于需要精确同步和时间控制的电子设备中,如通信系统、计算机网络、测量仪器等。

本文将详细介绍硬件延时电路的工作原理、应用场景以及优缺点等方面。

一、工作原理硬件延时电路通过控制电信号的传输速度和路径,实现对信号传输延迟的调整。

它通常由时钟信号发生器、延时单元、选择器和缓冲器等组成。

在工作时,时钟信号发生器产生一个稳定的时钟信号,作为整个电路的同步信号源。

延时单元接受输入信号,并根据设定的延时时间,延迟输出信号。

选择器根据控制信号选择输入信号或延迟后的输出信号,并将其传输给下一级电路。

缓冲器则用于增强信号的驱动能力,确保信号的传输质量。

二、应用场景硬件延时电路在许多领域都有广泛的应用。

以下是一些常见的应用场景:1. 通信系统:在通信系统中,硬件延时电路用于调整信号的到达时间,以确保数据的同步和可靠传输。

例如,在移动通信系统中,基站之间需要进行时隙同步,硬件延时电路可实现对时隙的精确控制。

2. 计算机网络:在计算机网络中,硬件延时电路用于实现数据包的延迟控制和时序同步。

例如,在以太网中,延时电路可用于控制数据包的发送时间,以避免数据冲突和碰撞。

3. 测量仪器:在科学实验和工程测量中,硬件延时电路用于控制测试信号的到达时间,以确保实验数据的准确性和可重复性。

例如,在声学测量中,延时电路可用于调整声音信号的传播时间,以实现定位和距离测量。

三、优缺点硬件延时电路具有以下优点:1. 精确性高:硬件延时电路使用稳定的时钟信号和精确的延时单元,能够实现高精度的延迟控制。

2. 响应速度快:硬件延时电路通过硬件电路的方式实现延时控制,响应速度较快,适用于对实时性要求较高的场景。

3. 稳定可靠:硬件延时电路的工作稳定可靠,不受外界环境和干扰的影响。

然而,硬件延时电路也存在一些缺点:1. 灵活性较差:硬件延时电路的延时时间通常是固定的,不易根据需要进行调整。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

语 法 So t p s| kp i t t a P — P口Q . Q P

尸 Q

的行为语义 。在进行高层设计系统描述后 ,不易实现对 被描 述系统的无死锁等属性的形式验证检查,这使系统高层设计

使这种开 发方式受到欢迎 。 但是 ,V ro ei g和 VH l DL都不是形 式化语言 , 没有形 式化

操作语义可参见文献[ 。 1 】

裹 1 C P语毫与彝作曲对应关曩 T S l }

操作 停 止 跳 过 等待 时 问 t 带 时间 的事 件前 缀 外 部选择 内部选择

[ y odlTm S ; D ; i — vlyt s iinS C Ke rs ie C P H L Hg l e ss mdc po ; E w d he e e rt

随着硬件设计规模和复杂性的 日益增长 , 利用 H L进行 D 高层次设计,通过逐层转换综合形成最终硬件设计已成为主

通常用大写字母 P 、Q或自定义字符串表示。、是一种特殊 / / 的事件 , 表示进程正常终止 。 可定义为 、 -> T P 称为成 § /- S O , /- -

功结束 进程。进程之 间定义 多种运 算操作。时间用字符 t或 数字表 示。T S C P操作语 义简单总结于表 l 中。详细的 T S CP

[ btat hs ae oi s aie a s ml eds n f a w rwt t e S (C P.h s m f co l etins A s clT ippr rv e f s lw yos t vlei r a i m d PT S ) e yt ntnmp m n t r p d ae b t y e e g o h d e hi C T s e u i i e ao i

( s tt o Mi o lc o isS h o o Ifr t nS in e n e hoo yP kn I tue f c eet nc, co l fnoma o c c dT c n lg, e igUnvri , in 0 8 1 ni r r i e a iesyBe ig10 7 ) t j

维普资讯

第 3 卷 第 7 2 期

己 .

・

计

算

机

工

程

2 0 年 4月 06

Ap i 2 0 rl 0 6

脑

7

Co p trEn i e rn m u e gn e ig

博士论文 ・

文章 号 0 _ 4 ( 00 01 _ 文 标识 l ■ l 0 - 2 2 67 04 o l o 3 8 0 )— _ 3 献 码 A

高层次描述 的外 壳,从而弥) T D h H L在高层 形式说明和结构与实时功能表达 方面的不足 ;同时该方法将时序与功能一体化描述 ,进一步 丰富 了硬件 系统规格 的内容 ,为复杂 的硬件系统设计提供 了一种可执行 的规格 说明方法 。 关■诃 :Tm d S ;H L ie P D ;高层次系统描述 ;S C C E

b sd o a e n HDL a g a e ,a d tes eli mp e ne t l u g s n h l si lme tdwi TCS Ge e al, n h h E n rly HDL l g a e v o fr a e a tc 。 n e r o o da a u g sha en o m lsm n s a dt y aen tg o t n i h

中 分 I P0 田 类号 33 T

Tme S i dC P在硬 件 高层 设计 中的应 用

崔小欣,于教山,崔小乐 , 盛世| l c

( 北京大学信息科学技术 学院微 电子所 ,北京 107) 08

曩 薹: 介绍了一种将 T S C P语言用于硬件高层次系统设计的方法。 该方法以 H L语言作为系统功能实现的核心, T S D 以 C P语言作为系统

要的硬件系统设计方法。目 前适用广泛的 H L语言主要有 D V ro D V D el H L、 H L等。 ig 这些 H L语言具有较强的行为级、 D 算法级、R L级、逻辑门级和开关级 的描 述能力 ,已为 广大 T 硬件设计工程师大量采用。特别是在设计转换工具和综合工 具的支持下,可形成有力的基于 H L的硬件系统设计方法, D

s se lv l r htc r ec it n a dra- m ef c o a p cfc to . nteme o ,hss oto n l iae , etm n n u c o e y tm e e c i t ed s rp o e lt a eu i n i un t n s e iia n I t d ti h rc mi gi i n td t i ga dfn t na i l i h h 自e m h i i r d srb d i l ne u l, dtepo os to san e yt raee e u a l p cfc t nso eh d res se e i e smut o sy a rp e me di ov lwa c e t x c tb ese iiai ft a wa y tm. c a n h d h o o h r

Ap l a i n o i h- v l sg f a d p i to f Ig l e c I e De i n o r wa ewih Ti e P H r t m d CS

CUI a xn YU n h n CUI a l, HENG hi n o i, Xi Du s a , oe S Xi S mi