基于PLX9030的PCI接口设计

通用运动控制卡CompactPCI接口的设计2

通用运动控制卡XXpactPCI接口的设计(2)XX XXXXXX XX XX本系统是一个闭环多轴运动控制硬件系统,具有快速精确的计算能力以及较强的数据通讯能力,是良好的复杂数控系统平台。

XXXX3XXpactPCI接口的设计XX XXXXpactPCI接口的设计要点在于在硬件插拔过程中,不能对XXp actPCI总线产生较大的冲击,不能影响XXpactPCI总线上数据传输的正确.所以应具有良好的热电源切换控制电路和相应的总线电路以及便于软件处理热插拔过程的控制信号。

XXXX电源控制和PCI9030的接口原理框图2所示。

3.1 PCI9030芯片热插拔控制信号的作用XXXX在XXpactPCI规范中规定:(1)板卡插入后,硬件初始化过程中应点亮蓝灯;(2)板卡即将拔出,软件能获知板卡即将拔出,并做好善后工作后,点亮蓝灯。

PCI9030芯片有BD_SEIL#输入信号引脚、ENUM#输出信号引脚、CPCISW输入信号引脚和LEDON# 输出信号引脚,均用作XXpactPn接口热插拔控制信号。

其功能分别如下:XXXXPCI9030的BD_SEL#输入信号引脚同运动控制卡XXpactPCI接口的引脚BD_SEL#相连,当BD_SEL#信号变高时,使PCI9030输出引脚成高阻态,保护芯片。

PCI9030的ENUM# 信号是送到背板的带上拉的集电极开路信号;它XX背板主机CPU板卡是刚刚插入,还是即将拔出。

并XXCPU系统配置改变,使CPU同时执行相关必要的软件操作(在板卡安装时,安装设备驱动程序;在移出板卡前,卸载设备9B动程序)。

板卡的插入/拔出状态是由CPCISW信号送到PCI9030完成的,这时,PCI9030通过ENUM#信号XX背板主饥硬件配置改变情况,同时主机CPU执行相关必要的软件操作.当操作结束时,主机CPU通过PCI9030将CPCISW信号写入HS-CSR寄存器的相应位中,使LEDON#信号变化,点亮或熄灭蓝灯,XX板卡可安全取出或已安全插入。

pci9030

PCI 9030SMARTarget ™ I/O AcceleratorAs PCI evolves in today's complex systems, PLX continues to provide market leading, high performance 32-bit PCI solutions. In this tradition, PLX is offering the PCI 9030 SMARTarget I/O Accelerator.There are many ways to do a PCI target design. Many PCI chip and core designs only attempt to implement the minimum PCI v2.1 bus interface signaling and call it complete. This leaves the burden of connectivity, performance and system compatibility on the designer. Only the PCI 9030 has SMARTarget tech-nology, a set of advanced features which go far beyond the minimum to pro-vide the best possible performance and flexibility to simplify the design. A basic target design is one thing, but a SMARTarget design is much more.The PCI 9030 brings PLX's industry leading experience in the world of PCI designs to you in a way that is simple and convenient to use. The PCI 9030 is the perfect solution for applications such as: Migrating Legacy Designs to PCIWhether you are migrating an ISA or other older design to PCI, or upgrading your current PCI target design, the PCI 9030 with SMARTarget technology pro-vides the fastest and easiest route to PCI. The PCI 9030 has the industry's most flexible local bus which allows for multiple interface options to a wide variety of memory and I/O devices. Combine that with fully tested, compatible PCI v2.2compliance, and your design risk is virtually zero. CompactPCI Hot Swap DesignsBuilding upon PLX's experience in CompactPCI, the PCI 9030 is the industry's first CompactPCI Hot Swap Ready Target device. This allows all of your CompactPCI I/O board designs to be compatible with both traditional CompactPCI and the new Hot Swap system designs.Smaller Form Factor DesignsThe PCI 9030 offers a 180-pin BGA packaging option. Where space is a consid-eration, this ultra-thin, dime-sized package is an ideal solution. This allows for flexibility in real estate sensitive designs such as PMC or PC-MIP Mezzanine cards, and PCMCIA PC-Cards.SMARTarget Technology Performance Featuress PCI v2.2 compliant 32-bit33MHz Target Interface Chip enabling PCI Burst Transfers up to 132Mbytes/second.s Up to 60MHz Local Bus oper-ation enabling burst transfers up to 240Mbytes/seconds PCI Target Read Ahead Mode s PCI Target ProgrammableBursts PCI Target Delayed Write s Posted Memory WritesFlexibility Featuress Programmable 32-bit Local Bus operates up to 60MHz s Supports 5 PCI to Local Address spacess Nine Programmable GPIOs s Four programmable Chip selectss CompactPCI Hot Swap Ready s Big/Little Endian Conversion s Interrupt Generators PCI v1.1 Power Management. s 3.3V, 5V Tolerant PCI Signaling s 3.3V CMOS device in 180-pin BGA or 176-pin PQFP s JTAGA c t ua l S i zes Posted Memory Writes. A PCI memorywrite can be posted to the PCI 9030 for later transfer to the Local bus. This allows for maximum PCI performance and avoids potential deadlock situations.SMARTarget Flexibility Featuress Programmable Local Bus operates up to 60MHz and supports both non-multiplexed and multiplexed 32-bit address/data protocol, and Dynamic Local Bus width control allowing slave accesses of 8-,16- or 32-bit devices.s Supports 5 PCI to Local Addressspaces. These spaces (Space 0,1,2,3 and Expansion ROM Spaces) allow a PCI Bus Master to access the local memory spaces with individually programmable wait states, bus width, and burst capabilities.s The PCI 9030 has 9 programmableGeneral Purpose I/Os which may be used for a variety of purposes.s Four programmable Chipselects eliminate decode logic.s CompactPCI Hot Swap Ready s Supports Automatic on-the-fly BigEndian and Little Endian conversion for all operations and data types.s Interrupt Generator can assert PCI inter-rupts from external and internal sources.s Fully supports the Vital Product Data(VPD) PCI v2.2 extension including New Capabilities Structure. Provides an alter-nate access method for user or system defined parameters or configuration data.s PCI Target Programmable Burst. The PCI 9030 may be programmed for several burst lengths, including unlimited burst.This allows for maximum transfer rates on both the PCI and local bus.s PCI Target Delayed Write. The PCI 9030supports PCI Target Delayed Write mode where the PCI Target Write data is post-poned in the PCI Target Write FIFO to allow uninterrupted burst transactionson the Local bus.This allows for a higher throughput for conditions in which the PCI clock frequency is slower than the Local clock frequency or when Local bus bursting is desirable.PCI 9030 SMARTarget I/O AcceleratorOnly the PCI 9030 has SMARTarget tech-nology, a set of advanced features which go far beyond the minimum to provide the best possible performance and flexi-bility to simplify the design. A basic target design is one thing, but a SMARTarget design is much more.SMARTarget Performance Features:s PCI v2.2 Compliant 32-bit, 33MHz Target Interface Chip enabling PCI Burst Transfers up to 132Mbytes/second.s Up to 60MHz Local Bus operationenabling burst transfers up to 240Mbytes/seconds PCI Target Read Ahead Mode. ThePCI 9030 will prefetch a programmable amount of data from the local bus. The prefetched data can then be burst transferred on the PCI bus from the PCI 9030 internal PCI Target Read FIFO. The prefetch size can be programmed tomatch the PCI master burst length or can be used as PCI Target Read Ahead mode data. This feature allows for increased bandwidth and reduced read latency.32-b it 60M H z Lo ca l Bu s32-b i t , 33M H z C o mp a c t P C I B u sI/OP C I 9030S M A R Ta rg e t ™D e v ic eE N U M #LE DI/OI/OM em o ry32-b it 60M H z Lo c a l B u s32-b it , 33M H z Sy ste m P C I B u sM e m o ryP C I 9030S M A R T a rg e t ™D e v ic eI/OI/OI/OI/OFigure 1.Typical PCI Target Adapter CardFigure 2.Typical CompactPCIHot Swap Adapter CardGPIO's and Programmable Chip selects save additional valuable board space. The PCI 9030 enables a whole new generation of mini form factor PCI cards. This is shown in figure 3 and 4:Additional Featuress 5V Tolerant Operation- The PCI 9030requires 3.3 Vcc. It provides 3.3V signal-ing with 5V I/O tolerance on the PCI and Local Buses.s Serial EEPROM Interface-Contains aninterface for an optional serial EEPROM that can be used to load configuration information.s Clocks-The Local Bus runs from a localbus clock and asserts the necessaryinternal clocks. This clock runs asynchro-nously to the PCI clock. The PCI 9030provides a PCI Buffered clock which can be used as a local bus clock if desired.s PCI Power Management supports bothD0, D3hot and D3cold power states. s 3.3V, 5V Tolerant PCI Signaling enables universal PCI adapters s 3.3V CMOS device in space saving 180pin BGA or 176-PQFP PCI 9030 Applications PCI Target Adapter Card The PCI 9030 can be used in a wide vari-ety of applications in networking, telecom,imaging, industrial and storage. The PCI9030 simplifies migration of legacy designsto PCI by providing a convenient off-the-shelf solution that can enable you tohave your prototypes operational in aslittle as one week. At the same time, thePCI 9030's built in SMARTarget perfor-mance features guarantee you will meet or beat your performance goals. In addi-tion, SMARTarget flexibility features such as 3.3V and 5V tolerant I/O buffers and local bus operation up to 60MHz, enable you to connect a wide variety of memory and I/O devices. With SMARTarget in action, PCI Target Adapter designs have never been simpler. Figure 1 shows a typical PCI Target adapter card.CompactPCI Hot Swap Adapter CardHot Swap capability is a requirement fortoday's CompactPCI systems.The PCI 9030 provides an excellent solution because it isthe industry's first Hot SwapReady Target chip. SMARTarget Technology will ensure a high performance Hot Swap imple-mentation. The PCI 9030 is aPICMG v2.1 Hot Swap Ready target device including the following features:s PCI specification v2.1 or betters Tolerant of Vcc from early power s Tolerant of asynchronous resets Tolerant of precharge voltages Has limited I/O pin leakage at precharge voltage s Incorporates the Hot Swap Control/Status Register (HS_CSR)s Incorporates an Extended Capability Pointer (ECP) mechanism s Incorporates added resources for soft-ware control of ENUM#, the ejectorswitch, and the status LED which indicates to the user insertion /removal s Precharge BIOS internal to the PCI 9030s Early power support internal to the PCI 9030Figure 2 shows a typical Compact PCIHot Swap adapter card. Small Form Factor PCI DesignsIn the real estate conscious world of PMC, PC-MIP, and PCMCIA PC-Cards,the PCI 9030's attractive packaging options are the perfect solution.SMARTarget Flexibility features such as 32-bit 60MHz Local Bus32-b i t , 33M H z P C I B u sI/O Memory PCI 9030SMARTarget ™Device(BGA)Figure 3.PMC Card PCI 9030SMARTarget Device (BGA)32-bit 60MHz Local Bus MemoryI/OFigure 4.PCMCIA PC-CARDPLX Technology, Inc.390 Potrero Ave.Sunnyvale, CA 94085USA Tel: 1-800-759-3735Fax: 1-408-774-2169Email: info@ Web Site: ©2001 by PLX Technology, Inc. All rights reserved. PLX and Data Pipe Architecture are trademarks of PLX Technology, Inc. All oth er product names that appear in this material are for identi cation purposes only and are acknowledged to be trademarks or registered trademarks of their respective companies. Information supplied by PLX is believed to be accurate and r eliable, but PLX Technology, Inc. assumes no responsibility for any errors that may appear in this material. PLXTechnology, Inc. reserves the right, without notice, to make changes in product design or speci cation.Development Tool SupportAs any good designer knows, development tools are just as important as the chips themselves. That is why PLX provides a complete PCI development environment to speed your time to market. The PCI 9030 is supported with a complete Reference Design Kit (RDK) with software debug support, and a hardware development kit (HDK) CD-ROM. These tools provide the easiest PCI target prototyping platform available. With the PLX PCI development environment you can have your hardware and software prototypes running in as little as one week.9030-SIL-PB-P1-037/2000 5KCompactPCI®Product Ordering InformationSee PLX web site for latest version and product support information.Part Number DescriptionPCI 9030-AA60PI PCI SMARTarget I/O Accelerator (PQFP)PCI SMARTarget I/O Accelerator (PQFP) (Lead-Free)PCI SMARTarget I/O Accelerator ( BGA) (Lead-Free)PCI 9030-AA60PI F PCI 9030-AA60BI FPCI 9030-AA60BI PCI SMARTarget I/O Accelerator (BGA)PCI 9030RDK-LITE PCI 9030 Reference Design kitCompactPCI 9030RDK-LITE CompactPCI 9030 Reference Design Kit HDK Collection CD-ROM Hardware Development Kit Collection CD-ROM Host-SDKWindows Host Side Software Development Kit32-bit, 33MHz PCI Bus32-bit, 60MHz Local BusEndian Control LogicLocal Bus Control Logic Dynamic Data Bus Width Control LogicMultiplexed/Non Multiplexed Control LogicLocal Bus Interface Control LogicPCI Bus Control Logic Hot Swap Control LogicPCI Bus Interface Control LogicRead FIFO Write FIF0FIFO Control LogicLocal Con guration RegisterPCICon guration Register Serial EEPROM ControllerPLX PCI 9030 Block Diagram。

带热插拔的CompactPCI的单板接口硬件设计技术

带热插拔的CompactPCI的单板接口硬件设计技术1、CPCI总线随着工业技术的发展,工业现场对计算机的要求像商业台式PC一样,同样需要高速度和高性能,尤其是在可视化图形操作界面、复杂的控制算法以及苛刻的时限要求等场合。

此外,对工业计算机还要有普通办公设备所不及的特殊要求,主要是:坚固:往往要工作在热、冷、脏、差的环境,还要能承受一定的冲击或振动,因此,对通风、散热、坚固性的要求较高。

可靠:平均无故障时间(MTBF)要高。

涉及电气、机械部件,连接器及外围设备的可靠性。

平均维修时间(MTTR)短:为缩短平均维修时间,大多数工业计算机都使用无源底板总线设计,甚至希望能带电插拔出现故障的插件。

模块化:除了要有普通PC的通用配置外,往往还有多种不同用途的I/O,如ADC、PLC、视频接口等。

且不同的应用对象要求各异,这就势必要用模块化解决。

标准化:成功的计算机设计大都不是一家能做好的,只有基于标准平台和工业标准才能从多个售主获得好产品。

前面板I/O:为了使用方便,工业计算机往往需要从前面连接I/O,前面板也兼有某些状态指示、插卡拔取和锁紧功能。

CPCI总线正是为了满足这一需要应运而生的,总的来说CPCI 总线规范是:PCI总线的电气和软件标准+ 欧式卡工业组装标准2、热插拔技术在一般的电子系统中,若出现电路板硬件故障,通常都要关闭系统电源再检修或更换故障设备,这样往往需要较长的停机时间。

在一些对可靠性要求非常高的高可靠系统中(MTTR 要求很短),不允许停机检修和停机更换故障板或只允许很短的停机时间。

要求在系统带电工作过程中更换电路板卡。

在众多的无源背板总线系统中,Compact PCI总线具有完整的支持热插拔的规范,提供了诸如:分级的引脚指针,enum#,蓝色LED,CPCISW,总线的预充电等规范进行支持。

根据同一规范各大生产商推出了自己开发的各种CPCI总线接口芯片和热插拔控制芯片。

这些芯片推出,大大简化了CPCI单板硬件的电气设计技术。

一种CPCI架构下的输入输出板设计

一种CPCI架构下的输入输出板设计发布时间:2021-10-14T05:59:24.710Z 来源:《科学与技术》2021年17期作者:张璐[导读] 本文设计了一种基于CPCI总线技术的DIO板,它主要作用是采集外部继电器接点状态以及驱动外部继电器线圈,并完成AO输出控制。

主要介绍了DIO板的硬件设计方案,并对整板功耗做了分析。

张璐南京恩瑞特实业有限公司江苏省南京市 210000摘要: 本文设计了一种基于CPCI总线技术的DIO板,它主要作用是采集外部继电器接点状态以及驱动外部继电器线圈,并完成AO输出控制。

主要介绍了DIO板的硬件设计方案,并对整板功耗做了分析。

关键词: DIO CPCI 硬件功耗1DIO板功能概述基于CPCI总线的DIO板一般用于车载ATO系统,主要作用是采集外部继电器状态以及驱动外部继电器。

2DIO板硬件设计方案2.1板卡组成DIO板由以下功能模块组成:主处理单元FPGA;CPCI总线接口;输入输出隔离;AO互切模块;DIO板的组成框图及其对外连接关系如下图所示。

DIO板采用FPGA作为DIO的控制单元。

FPGA对外提供16路DI,16路DO,并控制1路AO口的输出。

FPGA通过PCI接口芯片挂接在CPCI总线上,实现CPU与外部DIO口的数据交互。

此外本模块还提供状态指示。

2.2功能实现2.2.1电源共有三种直流电源:24VDC、5VDC、3.3VDC。

5VDC、3.3VDC电源取于CPCI背板,24VDC电源通过背板空余插针外接,不与计算机的电源共用,24VDC电源为驱动输出供电。

电源间要进行电气隔离。

2.2.2驱动输出驱动模块的原理框图如下图所示。

FPGA接收CPU的DO数据并驱动相应的继电器输出电平信号。

为了提高系统的可靠性、安全性,附加了光耦反馈检测回路,用于检测输出结果是否正确。

驱动:采用内部是MOSFET的功率型固态继电器,作为本板3.3V和24V的隔离驱动,输入信号由FPGA控制,驱动终端典型值为24V/50mA。

带热插拔的CompactPCI CAN总线接口板设计

带热插拔的CompactPCI CAN总线接口板设计包乃兰天津工业大学信息与通信工程学院,天津(300160)E-mail:baonailan@摘 要:本文在介绍基于PCI9030的CAN总线接口板的基础上分析了PCI9030的技术特点以及整板设计思想,并介绍了CompactPCI总线热插拔技术特点以及在应用LTC1643L芯片的体会与设计要点。

关键词:CompactPCI总线,PCI9030,热插拔,LTC1643L,CAN总线现场总线CAN(Controller Area Network控制器局域网络)以其高性能、高可靠性及独特的设计,越来越受到人们的重视和青睐。

而在嵌入式计算机方面,CompactPCI总线是当今计算机最快的数据通信总线,通信率达132Mb/s。

同时CompactPCI具有热插拔应用技术。

该技术以其系统可带电插拔部件的独特技术风格,在计算机软件的支持下,正得以广泛的应用。

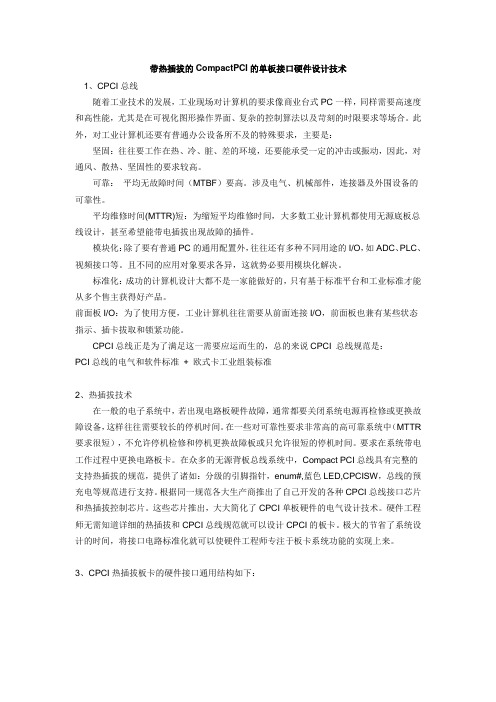

1 整体方案为了扩展CAN总线的功能,与嵌入式计算机相连,设计了具有CAN接口和计算机接口的CAN适配卡,用来收集CAN总线上各个节点的信息,转发给嵌入式计算机,并可将嵌入式计算机的命令和数据转发给各个节点以及完成对CAN总线上的用户系统的部分监控和管理工作。

本设计就是在此基础上开发的一款CompactPCI的CAN总线接口板。

本板主要由CompactPCI总线接口、CAN转CompactPCI的桥接芯片、热插拔、CAN总线四部分组成。

图1为设计的结构框图。

图1 硬件结构框图2 CompactPCI接口总线CompactPCI接口总线定义了更加坚固耐用的PCI版本。

在电气、逻辑和软件方面,它与PCI标准完全兼容。

相对PCI来讲,CompactPCI具有很多优点:(1)具有更好的机械特性。

它增强了PCI系统在电信或其它条件恶劣的工业环境中的可维护性和可靠性。

(2)采用Eurocard封装,系统中气流均匀。

(3)CompactPCI连接器的电源和信号引线支持热插拔规范,这对于容错系统是非常重要的,也是标准PCI所不能实现的功能。

PLX_PCI9030中文版

地总线信号在LCLK的上升沿被驱动和采样。准备和保持时间,考虑到LCLK,必须 被保留。

2.2.5

地址/数据 2.2.5.1复用模式(MODE=1)(Multiplexed Mode) (1)LA[27:2]包含了地址的传输,地址在传输的时候有效,然后在突发周期 (Burst cycle)时加入数据。 (2)LAD[31:0]是32位地址数据复用总线,在地址周期中,LAD[27:0]包含了地址的

(在此,本人觉得 Read Burst,Write Burst译为 读写猝发比较好) 在本地总线上有4种传输方式:读,写,突发读,突发写。总线上的传输的开始取决 于ADS#,结束取决于BLAST#。一次总线的存取包括了一个地址周期,其中有一个 或者多个数据传输。在每一个时钟周期的存取中,本地总线处于四种状态中的一种。 一个时钟周期包括一个本地总线时钟周期。 2.2.3 基本总线状态 四种基本总线状态为:空闲,地址传输,数据传输/等待,复位。一旦本地总线占用 了总线就需要开始一个总线的存取。此时进入了地址传输的状态,ADS#或ALE是有 效的,一个有效的地址存在于地址或数据总线上。数据是在传输数据/等待状态时被 传输的。READY#或者内部等待状态控制器是用来插入等待状态。BLAST#在传输数 据状态中表征最后一次的传输时有效。当所有的数据都传输完之后,总线进入复位 状态,允许总线设备进行复位。然后,总线进入空闲状态,等待下一次存取。 2.2.4 本地总线信号在时序图中的使用(Timing Diagrams) (1) ADS#或ALE表示存取的开始。 (2)READY# 或 WAITo#和BTERM#是用来插入等待状态,并用来结束数据传输

32位,33MHZCPCI总线

内存

I/O

32位,60MHZ本地总线 I/O

PLX_PCI9030中文版

0011(3h)Βιβλιοθήκη 读内存0110(6h)

写内存

0111(7h)

配置读

1010(Ah)

配置写

1011(Bh)

任意读内存

1100(Ch)

按顺序读内存

1110(Eh)

写内存,使无效

1111(Fh)

2.1.2 PCI总线的等待状态

PCI总线通过主模式的IRDY#和从模式的TRDY#来控制PCI总线的等待状态。

2.2 本地总线

2.2.1 介绍 本地总线为PCI总线和非PCI设备提供了一个数据通道,其中包括存储设备和外设。

本地总线是一个32位复用或者非复用的总线,并且有可以被编程为8位、16位、32位的 总线存储区域。本地总线可以直接连接DSP设备。PCI9030是本地总线的主导,PCI9030 可以在本地总线、内部寄存器和FIFOs间传输数据。突发长度不被限制,总线宽度取决 于本地地址空间寄存器的设置。有4个地址空间和一个默认空间(扩展ROM可以被用作 另一个地址空间),每个地址空间包含了一个配置寄存器,当地址空间被使用的时候它 决定了所有本地总线的特性。 2.2.2 传输

时的突发周期。 (3) LW/R表示数据传输的方向。 (4) BLAST#或BTERM#表示存取的结束。 (5) 主要的数据信号:LA地址总线,LAD地址数据总线,LBE[3:0]本地地址使能 (6) 本地总线信号:时钟,地址/数据,控制/状态,仲裁 2.2.5 时钟 LCLK是本地总线时钟,工作频率可达60MHZ,并且异步于PCI总线时钟。大部分本

传输,LAD[1:0]和LBE[1:0]有相同的状态。在数据周期中,LAD[31:0],LAD[15:0] 和LAD[7:0]包含了32位,16位,8位的数据转换。如果总线是8位或者16位宽的, 当通过32位的总线时数据时被复制成32位。 2.2.5.2非复用模式(MODE=0) LA[27:2]:地址线包含了地址的转换,地址在转换期间保持有效,在突发周期增加 数据。 LD[31:0]:32位非分时复用的数据总线,在数据时期,LD[31:0],LD[15:0]或LD[7:0], 分别转换32位,16位或8位数据。如果总线宽度是8位或16位宽度,当数据通过 32位宽的总线时,数据被复制成32位。 控制/状态:控制/状态信号控制着本地总线上的地址的写入取出和数据的流动。 ADS#,ALE:在地址周期时,本地总线处于主模式,并且ADS#被置位了,此时表 示本地总线存取的开始。ALE控制了LA/LAD总线进入外部地址。当在本地地 址空间的对应总线区域描述寄存器中,BTERM#输入被使能了,那么BTERM# 可以用来代替LRDYi#来完成一个存取,而LRDYi#是被忽略了。 LBE[3:0]#:在一个地址周期中,当LBE[3:0]#被使能时,在32位总线上存取时字节通 道就被使用了。它一直保持有效直到数据传输结束。 LLOCKo#:当PCI9030占用总线时,LLOCKo#有效暗示了一个对PCI目标设备的存 取需要通过复用模式来完成。在地址周期的第一个转换时刻,LLOCKo#是有 效的,在这一周期的最后一个转换时刻,LLOCKo#是无效的。如果LLOCKo# 被使能,那么本地总线将不允许被其他设备所占用。 LW/R#:在一个地址周期中,LW/R#被设置为有效来表示数据传输的方向。当PCI9030 是本地总线的主控设备时,PCI9030写数据到本地总线需要将LW/R#设置为高, 读数据设置为低。 RD#:RD#是一个通用目的的读输出口。通过总线区域描述寄存器来控制时序。在 整个数据传输期间RD#一直被声明。通常情况下,RD#是在NARD等待状态时 被声明的,除非读延迟时钟在总线区域描述寄存器中编程设置了 (LASxBRD[27:26]或者EROMBRD[27:26],其中x表示本地地址空间编号)。 RD#是被声明的在整个突发和NARD等待状态中。 READY#:READY#输入引脚在总线区域描述寄存器中有一个使能位(LASxBRD[1] 或者EROMBRD[1]).如果READY#被使能了,这就暗示了写数据被允许了或 总线从模式提供读数据。如果总线从模式需要插入等待状态,READY#就不能 被声明直到允许接受或者提供数据。如果READY#没有被使能,那么本地总线 传输长度由内部等待状态寄存器决定。

PCI9030与PCI9052资料对比及热插拔功能

PCI9030与PCI9052资料对比及热插拔功能1、首先在功能方面:PCI9030比PCI9052多了三个功能:支持热插拔、电源管理和支持重要数据VPD配置;但比PCI9052少了一项功能:支持ISA接口。

2、在引脚方面:由于PCI9030与PCI9052在功能上有差别,因此具体表现在以下管脚上:3、由于CPCI卡与主板的连接不再是通过PCI金手指连接,而是通过插针槽连接,在连接器上除了基本的PCI信号外,为了支持多出的功能,相应增加了一些引脚:灰色背景功能引脚暂时用不到!4、由于在功能上PCI9030与PCI9052有了差别,表现在配置空间上也相应有所变化,具体统计如下:9030PCI配置寄存器9030本地配置寄存器EEPROM中需要存储内容EEPROM中主要内容说明本地地址空间0范围寄存器本地地址空间1~3及本地扩展ROM范围寄存器的说明与本地地址空间0范围寄存器的说明类似本地地址空间0的本地基地址(重映射)寄存器本地地址空间1~3及扩展ROM的本地基地址(重映射)寄存器的说明与本地地址空间0的本地基地址(重映射)寄存器类似本地地址空间0总线区域描述符寄存器本地地址空间1~3及扩展ROM总线区域描述符寄存器的说明与本地地址空间0总线区域描述符寄存器的说明类似片选0基地址寄存器片选1~3基地址寄存器的说明与片选0基地址寄存器的说明类似中断控制/状态寄存器PCI目标应答、串行EEPROM、初始化控制寄存器5、热插拔技术概要插拔有三个过程:物理连接过程,包括热插入(在系统运行中插入单板)和热拔出(在系统运行中拔出单板);硬件连接过程,即系统在硬件层上的连接与断开;软件连接过程,即系统在软件层上的连接与断开。

这些过程可以用一组状态进一步描述,这些状态虽属于系统的不同连接层但彼此关联,如图1所示。

例如,当物理连接层不存在时,硬件连接层就不能产生电气连接;当单板从运行中的系统拔出时,软件连接和硬件连接自动断开。

关于PCI9030

PCI Configuration Register Address 3753/13FE

Status/Command 04H Class Code/Revision ID 08H Subsystem ID/Subsystem Vendor ID 2C

PCI 9030

REGISTERS

PCI Configuration Register Address Reserved/New_Cap Pointer 34H PCI Interrupt Pin/Line 3CH

Power Management Capabilities/Next_Cap Pointer/Capability ID 40H

PCI 9030

REGISTERS

Local Configuration Register Address Local Address Space 0 Range 00H 申请空间 Local Address Space 0 Enable 14H 设置LOCAL基地址 设置LOCAL基地址

PCI 9030

Interface Pins

Local Bus Mode Independent Interface Pins LCLK、 LCLK、 LRESETo# LREQ、 LGNT、LINTi1、 LREQ、 LGNT、LINTi1、LINTi2 CS[3:0]# MODE 1 = Multiplexed mode 0 = Non-Multiplexed mode Non-

PCI 9030

REGISTERS

PCI 9030

REGISTERS

Local Configuration Register Address Local Address Space 0 Bus Region Descriptor Chip Select 0 Base Address EEPROM/Interrupt 28H 3CH 4CH

基于PCI总线的数据采集卡的设计

基于PCI总线的数据采集卡的设计何瑾;张烨君;于彤彦;刘剑辉【摘要】PCI总线对于不同机型具有很强的兼容性,介绍了一种基于PCI总线的4通道数据采集卡的设计方法.PCI总线规范的实现直接决定了模块设计的成功与否,所以重点介绍了PCI总线控制器PCI9030芯片的主要特点和内部结构,并给出了其内部结构框图和桥接电路,最后对数据采集系统的技术指标、系统结构和各部分功能作了简单介绍.【期刊名称】《现代电子技术》【年(卷),期】2006(029)017【总页数】2页(P109-110)【关键词】数据采集;PCI9030;PCI总线;FIFO【作者】何瑾;张烨君;于彤彦;刘剑辉【作者单位】哈尔滨工业大学,黑龙江,哈尔滨,150001;哈尔滨工业大学,黑龙江,哈尔滨,150001;哈尔滨工业大学,黑龙江,哈尔滨,150001;大庆天然气公司,黑龙江,大庆,163416【正文语种】中文【中图分类】TN919.51 引言数据采集系统作为现代信号处理与信息处理的基础,随着新A/D器件的不断推出而得到了较大的发展。

但通用型高速数据采集系统昂贵的产品价格让人望而却步。

因而,寻找一种通过简单的电路设计来获得性能优良的高速数据采集系统一直是工程设计者追求的目标。

要实现高速数据采集,不仅需要高性能的A/D、D/A设备,而且需要高速的数据传输。

现代计算机的CPU运算速度越来越快,把采集到的高速数据传输到计算机内存中,在计算机上进行运算和处理更加灵活而通用,可以更加有效地进行信号的实时监控和处理。

PCI(即外部组件互连)总线被广泛应用于个人计算机中,已成为个人计算机事实上的标准总线。

PCI总线是一种高性能的32 b/64 b地址数据复用总线,总线时钟频率为0~33 MHz,可以支持猝发传输,最高传输速率可达132 MB/s,同时可支持多组外围设备;另外,PCI总线是一种独立于处理器的同步总线,不依赖于任何CPU,因而具有较好的兼容性。

基于DSP的PCI接口设计与实现

基于DSP的PCI接口设计与实现张亮;田泽;楼晓强;王治【摘要】PCI总线是目前应用最广泛的并行总线之一,DSP芯片在数字信号处理领域也有着广泛的应用,但目前大部分DSP芯片不支持PCI总线接口,无法与其他PCI 总线设备通信。

因此文中以DSP芯片外部存储器总线为接口设计实现了一种基于FPGA的PCI总线接口控制逻辑,通过在FPGA内集成EMIF总线接口、PCI总线接口、控制转换逻辑和一块用于数据管理的DPRAM,使DSP芯片可直接通过PCI总线访问外部设备并响应其他PCI设备发来的操作,实现通过PCI总线进行数据交互,扩展了DSP芯片的应用范围。

%PCI had been considered as one of the most widely used parallel buses. DSP chips also had extensive application in digital sig-nal processing field. However,presently most DSP chips didn't support the PCI interface not to communicate with other PCI. introduced the implementation of PCI interface control logics via the external memories bus of the DSP chip. The design integrated EMIF interface, PCI interface,control translated logic and a block of DPRAM for data management into a single FPGA chip,which enabled the DSP chip directly access the external devices through the PCI interface,responsed the operation from other PCI devices and implemented the data exchange through PCI interface,so it expanded the application area of the DSP chips.【期刊名称】《计算机技术与发展》【年(卷),期】2013(000)008【总页数】5页(P114-117,148)【关键词】DSP;EMIF;PCI【作者】张亮;田泽;楼晓强;王治【作者单位】中国航空计算技术研究所,陕西西安 710119;中国航空计算技术研究所,陕西西安 710119;中国航空计算技术研究所,陕西西安 710119;中国航空计算技术研究所,陕西西安 710119【正文语种】中文【中图分类】TP310 引言PCI总线是现在广泛使用的一种具有多路地址和数据线的高性能总线,其自1991年提出之日起至今,已在计算机和工业等领域得到了广泛的应用,可以说是目前使用最广泛的标准总线之一[1]。

基于PLX9030的PCI接口设计

基于PLX9030的PCI接口设计陈诚联想信息产品(深圳)有限公司E-mail:asiagame_cc@摘要:本文介绍了PCI总线规范并从设计角度总结了微机系统中PCI总线的特点, PLX 公司的PCI专用接口芯片PLX9030的特点、功能及使用方法以及设计WINDOWS的WDM 驱动(即WIN32的驱动模型)的方法。

本文论述了在此基础上利用PLX9030接口芯片开发PCI接口卡,使用51单片机进行PWM 解码以及在Windows2000操作系统下,使用DriverStudio软件编写符合WDM模式的PCI 卡驱动程序的硬件和软件实现方法。

关键词:PCI总线,PLX9030,PWM解码,DriverStudio,WDM驱动程序1. 引言在当今信息社会的时代,计算机技术已经渗透进了各行各业。

随着此技术的广泛应用和不断发展,无论工业应用还是办公自动化的应用,对计算机性能的要求都越来越高。

这就促使计算机总线技术也要日趋完善了,不断推出新标准。

而PCI局部总线因为其众多的功能、强大的兼容性,在当今的计算机市场仍然是不可或缺的。

PCI总线(Peripheral Component Interconnect)是Intel公司推出的总线标准,现已成为多媒体计算机总线的实际规范,PCI总线是与微处理器无关的32/64位地址数据复用总线。

PCI总线支持即插即用,从硬件的角度来看,其技术手段是为每一PCI设备提供一个配置空间,操作系统在自检(POST—Power-On-Self Test)的过程中检测所有PCI设备,读取设备的配置信息,并给每一设备分配系统资源,如中断、I/O空间、存储器空间等。

随着计算机系统及应用技术的迅速发展,PCI总线已经成为目前最流行的、也是最有发展前途的计算机系统局部总线,相应的,计算机应用领域的各种功能扩展卡也必将逐步发展为PCI标准的扩展插卡。

本文对PCI总线的规范,特别是针对PCI规范的一些设计开发作了介绍,并在此基础上给出了一种基于PCI局部总线的接口扩展卡的设计,对PCI总线产品开发的过程和使用的工具进行了详细的论述。

DSP运动控制器与PCI总线的接口设计

DSP运动控制器与PCI总线的接口设计谢黎明;陈宏涛【摘要】由于DSP具有高速实时处理能力和丰富的外设功能,目前,以DSP为核心处理器的运动控制器已经成为开放式运动控制器的发展主流,并得到广泛的应用.本文介绍了以DSP为核心处理器的开放式运动控制系统结构,并重点设计使用接口芯片PCI9030完成DSP TMS320LF2407和PCI总线的接口电路,实现了以DSP为核心处理器的运动控制器与上位机进行实时高速数据传输.【期刊名称】《新技术新工艺》【年(卷),期】2010(000)005【总页数】2页(P36-37)【关键词】DSP;运动控制器;接口电路;PCI总线【作者】谢黎明;陈宏涛【作者单位】兰州理工大学,数字制造技术与应用省部共建教育部重点实验室,甘肃,兰州,730050;兰州理工大学,机电工程学院,甘肃,兰州,730050【正文语种】中文【中图分类】TG74.91 系统总体设计方案开放式数控系统具有强大的适应性和灵活配置能力,控制软件具有及时扩展和联接功能,可以适应新技术的发展,扩展各种新功能,同时能适应计算机技术和信息技术的快速发展和更新换代。

本文采用 TMS320LF2407作为运动控制器的核心处理器。

TMS320LF2407是TI公司生产的16位定点DSP,主要针对电动机控制以及实时数据处理。

其主要特点是:采用静态CMOS技术,供电电压为3.3 V,40 MIPS的运行速度。

片内32 K的FLASH程序存储器,544字的双口RAM,2 K的单口RAM。

2个事件管理器模块EVA和EVB,每个模块包括2个16位通用定时器、8个16位PWM 通道、3个捕获单元及 16通道A/D转换器。

此外,TMS320LF2407具有灵活的指令系统、灵活的操作性能、改进的并行结构、高速的运算能力以及很高的性能价格比。

在运动控制器中,DSP主要完成各轴位置速度的PID控制、插补迭代运算以及开关量的输入输出等对实时性要求较高的任务。

基于接口芯片PCI9030的PCI总线接口卡的设计

基于接口芯片PCI9030的PCI总线接口卡的设计

施少敏;马彦恒

【期刊名称】《微计算机信息》

【年(卷),期】2006(000)11Z

【摘要】介绍了如何利用接口芯片PCI9030制作PCI总线接口卡,实现由ISA接口向PCI接口的转换。

文中从实例出发,详细阐述了接口卡的硬件设计、EEPROM的配置、驱动程序的编写等方面的内容。

【总页数】3页(P295-297)

【作者】施少敏;马彦恒

【作者单位】军械工程学院光学与电子工程系,河北石家庄050003

【正文语种】中文

【中图分类】TP336

【相关文献】

1.基于PCI总线的1553B总线接口卡设计 [J], 瞿朝兵;陈涛;徐智勇;何培龙

2.基于PCI局部总线的1553B总线接口卡设计 [J], 赵明阳;朱岩;张建东;史国庆

3.基于CH365芯片的PCI总线接口卡的设计与实现 [J], 李阔

4.基于接口芯片PCI9030的PCI总线接口卡的设计 [J], 施少敏;马彦恒

5.基于PCI总线的APINC429总线接口卡设计 [J], 王魁;苏士美;厉励

因版权原因,仅展示原文概要,查看原文内容请购买。

华为9030参数

500一、视讯技术发展概况视讯技术实现了语音、图像、数据等信息综合在一起的远距离传输,使人们在进行异地交流时利用视讯技术既可以听到对方的声音,又可以看到对方的活动图像和胶片内容,大大增强了异地交流的亲切感和临场感。

在“效率至上”的信息社会中,通过视讯系统,进行协同工作时既可听到对方的声音,又可看到对方的图像,大大增强了沟通的效果,在节约宝贵的时间、精力和金钱的同时,又提高管理和决策效率,充分发挥出视频会议真实、高效、实时的优点,为人们提供了一种简便而有效的协同工作手段。

为了实现信息化,保证信息的快速、高效的传输,很多运营商与企业建设了基于宽带多媒体业务的视频会议系统。

利用业界先进的视频通讯技术,实现了视频、语音和数据的视频稳定传输,提高了宽带网络的利用率和办公效率,并减少了差旅费用、日常会晤费用的支出,并为实时的沟通创造了条件。

随着IT技术的发展以及视频会议需求的日益提高,特别是H.264视频编解码技术的发展为视频图像带来革命性的变革,高清视频已经成为众望所归,技术发展的方向,成为新一代视频会议系统的一个标志性指标。

根据美国咨询机构WR(Wainhouse Research)报告显示,今后5-10年,视频会议主要有如下发展方向•更清晰--视频720p/1080p 50p/60p高清成为新一代视频会议系统的不二选择;音频:AAC-LD宽带音频协议正逐步取代低品质音频通讯协议如G.711、G.728、G.722等•高临场感--多声道、会议室场景技术(远程呈现技术)、3DAV•低带宽、高效率--H.264视频解码协议已经成为高视频编解码的绝对首选•多协议长期并存-- H.320和H.323网络协议长期共存,并有向SIP协议平滑过渡720p/1080p 50p/60p高清会议电视系统在大型行政会议、大型培训、远程教育等领域具有广泛的应用;通过AAC-LD等宽频语音技术,以及双声道、三声道技术,提供高保真、立体声的音频效果,结合双720p、双1080p的辅流技术,视频会议可真正实现三位一体(图像、声音、数据内容)的高质量效果。

PCI9030及其PCI总线接口电路设计

PCI9030及其PCI总线接口电路设计0 引言PXI 总线系统的卓越性能和较低的价格,使得越来越多从事自动测试的工程技术人员开始关注PXI 的发展。

而PXI 总线是PCI 总线在仪器领域的扩展,可以将PXI 总线分为PCI 总线和PXI 扩展的总线两部分。

将进行PCI 总线接口电路的设计,从而为设计PXI 模块仪器,组建PXI 总线自动测试系统做好准备。

目前,PCI 总线接口电路的实现主要有两种方案:一是采用一片大容量FPGA/CPLD 实现PCI 总线接口逻辑;另一种是采用ASIC 芯片完成PCI 总线的接口电路。

由于PCI 总线速度高,协议复杂,采用第一种方案虽然应用很灵活,但是调试困难,开发周期长,而且采用一片工业级可用于PCI 接口的FPGA/CPLD 完成PCI 总线接口功能,远比使用PCI 接口芯片的成本高。

采用第二种方案,功能强,价格低,稳定性好,开发周期较短。

通过对上述两种接口方案的比较,从综合开发难度、芯片功能、开发速度和开发经费等方面考虑,在此采用后一种方案完成PCI 总线的接口设计。

1 PCI9030 芯片及其主要特点PCI9030 是全球最大的PCI 接口设备制造商PLXTechnology 于1999 年3 月推出的全新的32 b/33 MHz PCI 目标设备接口芯片。

它采用PLX 先进的SMARTarget 技术,不仅为各种应用提供了最大的灵活性,而且大大简化了系统设计,具有最高的性价比,能够满足各种应用的要求。

PLX 计划用它替代应用广泛的PCI9050 和PCI9052。

PCI9030 主要有以下特点;(1)采用PLX 先进的SMARTarget 技术,完全兼容PCI 2.2 协议规范,PCI 突发传输速率高达132 MB,/s,是第一个符合CompactPCI PICMG2.1 标准的工业级目标设备接口芯片。

(2)支持高达60 MHz 的局部总线操作,突发传输模式下速率可达240 MB/s,支持PCI 目标预取模式、PCI 目标可编程突发传输、PCI 目标延迟写模式和PMW(Posted Memory Writes)模式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于PLX9030的PCI接口设计陈诚联想信息产品(深圳)有限公司E-mail:asiagame_cc@摘要:本文介绍了PCI总线规范并从设计角度总结了微机系统中PCI总线的特点, PLX 公司的PCI专用接口芯片PLX9030的特点、功能及使用方法以及设计WINDOWS的WDM 驱动(即WIN32的驱动模型)的方法。

本文论述了在此基础上利用PLX9030接口芯片开发PCI接口卡,使用51单片机进行PWM 解码以及在Windows2000操作系统下,使用DriverStudio软件编写符合WDM模式的PCI 卡驱动程序的硬件和软件实现方法。

关键词:PCI总线,PLX9030,PWM解码,DriverStudio,WDM驱动程序1. 引言在当今信息社会的时代,计算机技术已经渗透进了各行各业。

随着此技术的广泛应用和不断发展,无论工业应用还是办公自动化的应用,对计算机性能的要求都越来越高。

这就促使计算机总线技术也要日趋完善了,不断推出新标准。

而PCI局部总线因为其众多的功能、强大的兼容性,在当今的计算机市场仍然是不可或缺的。

PCI总线(Peripheral Component Interconnect)是Intel公司推出的总线标准,现已成为多媒体计算机总线的实际规范,PCI总线是与微处理器无关的32/64位地址数据复用总线。

PCI总线支持即插即用,从硬件的角度来看,其技术手段是为每一PCI设备提供一个配置空间,操作系统在自检(POST—Power-On-Self Test)的过程中检测所有PCI设备,读取设备的配置信息,并给每一设备分配系统资源,如中断、I/O空间、存储器空间等。

随着计算机系统及应用技术的迅速发展,PCI总线已经成为目前最流行的、也是最有发展前途的计算机系统局部总线,相应的,计算机应用领域的各种功能扩展卡也必将逐步发展为PCI标准的扩展插卡。

本文对PCI总线的规范,特别是针对PCI规范的一些设计开发作了介绍,并在此基础上给出了一种基于PCI局部总线的接口扩展卡的设计,对PCI总线产品开发的过程和使用的工具进行了详细的论述。

2. PCI总线和接口芯片特点2.1 PCI总线概述计算机总线是计算机各部件之间进行信息传输的公共通道。

微型计算机系统中广泛采用总线结构,其优点是系统成本低、组态灵活、维修方便。

采用总线标准设计、生产的硬件模块兼容性强,并通过系统总线可以方便地组合在一起,以构成满足不同需要的微机系统。

计算机总线技术包括通道控制功能、使用方法、仲裁方法和传输方式等。

总线的结构不同,性能差别很大。

总线的传输率是其性能的主要技术指标。

另外,总线的可操作性、兼容性和性价比,也是很重要的技术特征。

PCI总线是先进的高性能局部总线,可同时支持多组外围设备。

其优化的设计可充分利用今日最先进的微处理器及个人电脑科技。

它可确保电脑部件、附加卡及系统之间的运作可靠。

PCI总线规范正式的2.2版本于1999年2月发布。

具有高性能、支持线性突发传输、极小的存取延迟、采用总线主控和同步操作、不受处理器限制、适合于各种机型、兼容性强、预留了发展空间、低成本、高效益和即插即用等优点。

它兼容5V和3.3V两种电压信号环境,PCI以其突出的性能备受计算机和通信界的青睐,现已取代以往的ISA,EISA等总线,成为微机系统总线标准,主要性能指标如下:总线时钟:33.3MHz/66.6MHz总线宽度:数据总线的数量,PCI兼容32位/64位两种总线宽度最大传输速度:33.3MHz 工作频率、32bit宽度时为133MB/s; 66.6 MHz工作频率、64位宽度时为:512MB/s适应5V和3.3V电源环境总线上数据与时钟为同步工作方式逻辑时序:边缘敏感即边沿触发类负载能力:可连接的扩充电路板的数量为3个具有突发传输、并发工作和自动配置的功能使用PCI总线结构的设备,可以达到理论上峰值为132Mbytes/s的数据率,虽然这个数字会因为总线繁忙和设备自身的原因和实际值有些出入,但是达到60Mbytes/s的实际传送数据率还是有可能的。

还因为它和存储器之间的交互基本上通过DMA方式,CPU占用率很低,功耗很小。

所以,即使是一些低速设备也淘汰了ISA总线,开始采用PCI总线结构。

[2] 2.2 PCI局部总线信号在一个PCI应用系统中,如果某设备取得了总线控制权,就称其为“主设备”;而被主设备选中以进行通信的设备称为“从设备”或“目标设备”。

对于相应的接口信号线,通常分为必备的和可选的两大类。

为了处理数据,寻址,接口控制,仲裁以及系统功能,PCI接口要求作为目标设备的必备信号线有47条。

图2-1为按功能分类的引脚,必要的在左边,可选的引脚在右边。

信号的方向说明是针对总线主设备/目标设备组合设备而言的。

图2-1 PCI局部总线信号图中“#”号表示低电平有效,否则为高电平有效。

其中比较重要的几类信号有:系统信号定义CLK :输入,系统时钟信号。

其频率最好可达33MHz;RST#:输入,PCI复位信号。

用来使PCI专用的特性寄存器和定序器相关的信号恢复规定的初始状态。

2.地址和数据信号AD[31:0]:双向三态输入/输出,它们是地址、数据多路复用的引脚;C/BE[3:0]#:双向三态输入/输出,它们是总线命令和字节使能多路复用信号线。

在地址期中,这四条线上传输的是总线命令;在数据期内,它们传输的是字节使能信号。

PAR:双向三态输入/输出,AD[31:0]和C/BE[3:0]的奇偶校验位。

3.接口控制信号FRAME#:持续的并且低电平有效的三态信号,PCI帧周期信号。

由当前主设备驱动,表示一次访问的开始和持续时间;TRDY#:持续的并且低电平有效的三态信号,PCI目标准备好信号;该信号有效表示从设备已经作好完成当前数据传输的准备工作,也就是说,可以进行相应的数据传输;IRDY#:持续的并且低电平有效的三态信号,PCI主控准备好信号;该信号的有效表明发起本次传输的设备能够完成一个数据期;STOP#:持续的并且低电平有效的三态信号,停止数据传送信号,有效时,表示目标要求当前总线主控设备停止当前传送;LOCK#:持续的并且低电平有效的三态信号,锁定信号。

当该信号有效时,表示驱动它的设备所进行的操作可能需要多个传输才能完成。

也就是说,对此设备的操作是排它性的;DEVSEL#:输入/输出,PCI设备选择信号,有效时,表示驱动它的设备已成为当前访问的从设备,换言之,它的有效说明总线上某处的某一设备已被选中;IDSEL:输入,PCI初始化设备选择信号,在参数配置读写传输期间,用作片选信号。

4.仲裁信号REQ#:双向三态输入/输出,PCI占用请求信号。

该信号一旦有效即表明驱动它的设备要求使用总线;GNT#:双向三态输入/输出,PCI总线占用允许信号。

一个点到点的信号线,用来向申请占用总线的设备表示,其请求已获得批准。

5.错误报告信号PERR#:持续的并且低电平有效的三态信号。

但该信号不报告特殊周期中的数据奇偶错;SERR#:漏级开路信号。

系统错误报告信号。

该信号的作用是报告地址奇偶错、特殊命令序列中的数据奇偶错,以及其它可能引起灾难性后果的系统错误。

6.中断信号INTA:输出,PCI中断信号。

在PCI总线中是可选项,不一定必须具有。

并且中断信号属电平敏感性,低电平有效,使用漏级开路方式驱动。

[4]2.3 开发方案的选择目前,PCI总线接口电路的设计一般有两种方案:一种是选用可编程逻辑器件(FPGA/CPLD)。

使用可编程器件,用户可以灵活地开发出适合自己需要的具有特定功能的PCI接口芯片。

然而,PCI总线与过去的ISA总线相比有其独特的要求和特点,其规范定义中牵扯到的概念和引线定义较为复杂,规则相对繁多,机械及电气特性要求严格,应用者短时间内一般难以掌握,对于一般的工程项目来说,成本较高。

现在有许多生产可编程逻辑器件的厂商都提供经过严格测试的PCI接口功能模块IP核,用户只需进行适当组合即可。

另一种是选用PCI专用芯片组(又称桥接电路),通过专用芯片来实现完整的PCI主控模块和目标模块的功能,将复杂的PCI总线接口转换为相对简单的用户接口,用户只需设计转换后的总线接口即可。

PCI总线接口电路又分为主控设备和目标设备。

主控设备可以控制总线,驱动地址、数据和控制信号;目标设备不能启动总线操作,只能依赖于主控设备从其中读取数据或向其传送数据。

主控设备芯片价格较高,目标设备芯片价格则比较便宜,而且目标设备芯片比较简单,易于操作。

目前两大PCI专用接口芯片生产商是AMCC公司和PLX公司。

AMCC公司的PCI接口芯片有S5920、S5933、S5935D等。

S5920是目标设备芯片;S5933既可以设置为主控设备芯片,又可以设置为目标设备芯片;S5935是S5933的改进版,同样既可以设置为主控设备芯片,又可以设置为目标设备芯片。

PLX公司在PCI接口芯片的设置生产中首屈一指,其目标设备芯片主要有PLX9030、PLX9052和PLX9050;主控设备芯片主要有PLX9054、PLX9080和PLX9060。

PLX9060是最早的32位主控设备芯片,PLX9080是PLX9060的后继产品,而PLX9054则是一种性价比很高的芯片,其性能比PLX9080、PLX9052更优越。

本设计根据应用项目的要求,确定使用PCI从控,由此选定了PLX9030作为协议芯片。

2.4 PCI接口芯片简介本设计中采用的PCI接口芯片是PLX9030,该芯片符合PCI v2.2规范,是一种性价比很高的芯片,具体性能特性如下:符合 PCI v2.2 规范的 32 位 33MHz 目标接口芯片,使 PCI 突发传输速度高达 132 兆字节/秒。

高达 60MHz 的局域总线操作使突发传输速度高达 240 兆字节/秒PCI 目标预读取模式PCI 目标可编程突发模式PCI 目标写延迟上传存储器写入可编程 32 位局域总线操作,高达 60MHz支持 5 个 PCI 到本地地址空间和I/O口映射九个可编程 GPIO四个可编程芯片选择支持 CompactPCI 热交换Big/Little Endian 编码转换中断生成器PCI 1.1 版电源管理3.3V,5V 容错 PCI 信号传输180 针 mBGA 或 176 针 PQFP 封装的 3.3V CMOS 设备JTAG [1]其结构如图2-2图2-2 PLX9030芯片结构图如图所示,PLX9030提供三种物理总线接口:PCI总线,Local总线接口及串行EEPROM 接口。

本设计只需要利用9030的Local总线与PCI总线之间数据传输的从模式(Direct Slave)即可满足要求,同时9030还具有5个PCI到Local地址空间,9个可编程GPIOs,4个可编程芯片选择信号,以及中断发生器能力。