基于FPGA的图像采集及VGA显示

基于FPGA的VGA接口显示的设计与实现

编号基于FPGA的VGA接口显示的设计与实现Design and implementation of VGAinterface based on FPGA display学生姓名王雪专业控制科学与工程学号S120400520指导教师杨晓慧学院电子信息工程学院二〇一三年六月摘要利用现场可编程逻辑器件FPGA产生VGA时序信号和彩条图像信号,并将其作为信号源,应用于彩色等离子显示器的电路开发,方便彩色等离子显示器驱动控制电路的调试。

FPGA芯片具有可靠性高、编程灵活、体积小等优点,实验经过软硬件调试,最终在显示器上显示彩条正确图像。

利用此原理,可以设计更多的彩色图像,且可将采集的图像进行实时显示,将此作为信号源,应用于显示器电路的开发或某些嵌入式系统中,进行视频设备的调试与性能分析或系统中信号处理模块的调试与性能分析等。

关键词:FPGA VGA接口时序控制彩条信号AbstractVGA-timing signals and color strip image were obtained by using FPGA.The signals were used as sources when developing the circuits of color plasma display panel, and it took great convenience to the debugging of the driving and controlling circuit of color plasma display panel.The FPGA chip has the advantages of high reliability, small volume, flexible programming,just because of this,the test could achieve the desired results,display scree displays color bar signals.According to this principle, we can design color image more, and make the image real-time display, such as the signal source, used in display circuit development or some embedded systems, video equipment debugging and performance analysis of the system signal processing module debugging and performance analysis.Keywords:FPGA, VGA interface,timing control, color bar signals目录摘要 (1)Abstract (2)第一章引言 (4)第二章VGA显示接口的方案设计和原理 (5)2.1 VGA接口 (5)2.2 VGA显示原理 (5)2.3 VGA信号时序 (6)2.4 VGA显示方案实现 (7)第三章系统模块设计 (8)3.1系统模块原理图 (8)3.2 分频模块 (8)3.3 VGA彩条信号产生模块 (8)3.4 实验结果 (12)第四章结论 (13)致谢 (14)参考文献 (15)第一章引言视频图形阵列(VGA)作为一种标准的显示接口已经得到广泛的应用。

基于FPGA实现VGA的彩色图片显示

基于FPGA实现VGA的彩色图片显示

0 引言

视频图形阵列显示接口是微机系统使用的一种通用显示接口,广泛应用于智能控制系统中,作为系统的显示终端。

对于由嵌入式微处理器构成的

图像处理系统来说,采用VGA显示输出具有兼容性强、显示内容丰富的优势。

同时,VGA显示接口具有结构简单、性能可靠、兼容性强、时序容易控

制的特点。

因此,结合FPGA的VGA图像控制器在嵌入式的图像处理系统中有广泛的应用前景。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转

变为R、G、B三原色信号和行场同步信号,信号通过电缆传输到显示设备中。

1 VGA显示

常见的VGA接口的彩色显示器,一般由cRT(阴极射线管)构成,

色彩由R、G、B(红:Red,绿:Green,蓝:Blue三基色组成。

显示采用逐。

FPGA实现VGA显示图片

阿力这几天看了些关于VGA显示的文档,以及显示的方法,今天做一下总结,分享给大家,让大家少走弯路(顺便也赚一个财富,呵呵)。

声明一下以下内容全是本人尝试过总结出来的,绝对不是直接的复制粘贴。

我的板子是ep2c8的,现在我尽可能详细的说明如何用FPGA实现VGA显示的。

首先,关于VGA的原理,我就不在这里赘述了,大家只要简单的了解就行。

关于VGA的时序问题,主要是实现VSYNC、HSYNC以及相应的data:首先选择分辨率,以640*480@60为例,通过查表可知行频、场频、时钟、数据前后消隐以及有效的像素长度。

接着,就可以根据以上信息写入程序了:`timescale1ns/1psmodule vga(clk_25m,rst,hsync,vsync,addr);input clk_25m,rst;output hsync,vsync,addr;reg[17:0]addr;reg hsync,vsync;reg[9:0]x_cnt;reg[9:0]y_cnt;always@(posedge clk_25m or negedge rst)//行计数器beginif(!rst)x_cnt<=10'd0;else if(x_cnt==10'd799)x_cnt<=10'd0;else x_cnt<=x_cnt+1'd1;endalways@(posedge clk_25m or negedge rst)//场计数器beginif(!rst)y_cnt<=10'd0;else if(y_cnt==10'd524)y_cnt<=10'd0;else if(x_cnt==799)y_cnt<=y_cnt+1'd1;endalways@(posedge clk_25m or negedge rst)//行场同步信号beginif(!rst)hsync<=1'b1;else if(x_cnt==10'd0)hsync<=1'b0;//产生hsync信号else if(x_cnt==10'd96)hsync<=1'b1;endalways@(posedge clk_25m or negedge rst)beginif(!rst)vsync<=1'b1;else if(y_cnt==10'd0)vsync<=1'b0;//产生hsync信号else if(x_cnt==10'd2)vsync<=1'b1;end/*--产生有效位--*/reg valid_y;reg valid;always@(posedge clk_25m or negedge rst)beginif(!rst)valid_y<=1'b0;else if(y_cnt==10'd32)//由于分频后时钟不是完全一致,故有效位不完全按照表格,有偏差valid_y<=1'b1;else if(y_cnt==10'd512)valid_y<=1'b0;endalways@(posedge clk_25m or negedge rst)beginif(!rst)valid<=1'b0;else if((x_cnt==10'd141)&&valid_y)valid<=1'b1;else if((x_cnt==10'd781)&&valid_y)valid<=1'b0;endalways@(posedge clk_25m)//重复显示图片beginif(!valid)addr<=18'd0;elseaddr<=(y_dis%60*80)+(x_dis%80);//显示图片,尺寸80×60endendmodule最后,我将介绍如何实现图片显示。

一种基于FPGA的高速图像采集及显示电路设计

1 9

一

种基于 F G P A的高速图像采集及显示电路设计

De i f Hi —s e d Vi o Ac ust n An Dip a r utBa e o P sgn o gh— p e de q iio d i s ly Ci i c s d n F GA

选 用 的 接 收 芯 片是 DS 0 R 8 , 最 高 数 据 传输 速 率 可 以达 到 9 C 2 6其

该 F G 进 行 配 置和 验 证 , 试 表 明该 设 计 不仅 实现 了 图像 高 速 采 集和 显 示 , 使 图像 清 晰 、 PA 测 且 系统 稳 定 可 靠 。

关 键 词 :P F GA, Cl CP 总线 , 图像 采 集

Ab ta t s rc

Th si u e Ca Ln nera e nd e de gn s d m ik it f c a DVI o r al e i -s ed i a qust d t e i hgh pe vdeo c iion an diply.hi z i s a T s pap itodu es er nr c t e y tm of i a quiion nd h s se vdeo c st a diply a d i s a b se on PGA,h ws o F s o h w t s m pl m o e he a e dul ba ed s on Cam Lnk n e ce i it da an DVI s a o e d diply m dul wor d. d de An ba ed n s o CP bu ,i Cl shgh- ee i a da a ex h ge et e c sp d m ge t c an b we n ompu e an i tr d mag e ci ui wa r aied. EP 30 7 4 FP r t c s el z 2S F6 21 GA o t m p y i u e t n i d ery h de i . e es manfses h fAl Co an s s d o co fg an v i te er f sgnTh t t i t te e de i n tonl eaied i sgn o y r l z hgh—s ee vdeo a p d i cqust a d iion n diply, talo m a de ea ,y tm r i l i s a bu s de vi o cl rs se el e ab Ke wo d : P y r s F GA. Cl s, de a quiion CP bu vi o c st i

毕业设计-基于FPGA的VGA显示

VGA显示器控制电路论文前言VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。

利用FPGA 芯片和EDA设计方法,可以因地制宜,根据用户的特定需要,设计出针对性强的VGA显示控制器,不仅能够大大的降低成本,还可以满足生产实践中不断变化的用户需要,产品升级换代方便迅速。

在本设计中采用Altera公司的EDA软件工具Quartus II,并以Cyclone II 系列的FPGA的器件作为主实现硬件平台的设计。

一、FPGA的原理FPGA 是Filed Progranmmable Gate Array的缩写,即现场可编程逻辑阵列。

FPGA是在CPLD的基础上发展起来的新型高性能可编程逻辑器件它一般采用SRAM工艺,也有一些专用器件采用Flash工艺或反熔丝(Anti_Fuse)工艺等。

FPGA的集成度很高,其器件密度从数万系统门到数千万系统门不等,可以完成极其复杂的时序与组合逻辑电路功能,适用于高速、高密度的高端数字逻辑电路设计领域。

FPGA的基本组成部分有可编程输入/输出单元,基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元、内嵌专用硬核等。

FPGA 的主要器件供应商有Xilinx、 Altera、 Lattice、 Actel和 Atmel 等。

二、 VGA转换接口的简单描述本设计另外自制VGA接口电路。

VGA时序控制模块是整个显示控制器的关键部分,最终的输出信号行、场同步信号必须严格按照VGA时序标准产生相应的脉冲信号。

对于普通的VGA显示器,其引出线的共含5个信号:G,R,B(三基色信号),HS(行同步信号),VS(场同步信号)。

在五个信号时序驱动时,VGA显示器要严格遵循“VGA工业标准”,即640Hz×480 Hz×60Hz模式。

下图(1)为VGA显示控制器控制CRT显示器VGA(Video Graphic Array)接口,即视频图形阵列,也叫做D-Sub接口,是15针的梯形插头,分3排,每排5个,传输模拟信号。

基于FPGA的LED显示屏VGA同步图像采集设计

基于FPGA 的L E D 显示屏VGA 同步图像采集设计朱如龙(南京信息职业技术学院,江苏省南京市210013)【摘 要】 介绍了以现场可编程门阵列(FPG A )为核心芯片的发光二极管(LE D )视频图形阵列(VG A )同步图形采集系统的设计。

该系统采用数字视频转换芯片,将输出的显卡上的红、绿、蓝信号及各种同步控制信号转换成数字信号,并由FPG A 作为控制器将这些数字信号存入RAM 中,根据需要进行预处理,如进行γ校正、产生读、写地址、RAM 时序等,以便能快速地提取各种有效的显示及控制数据,传送至LE D 屏体控制板中。

关键词:FPG A ,LE D 显示屏,VG A 同步,γ校正中图分类号:T N873.9;T N911.73收稿日期:2004207201;修回日期:20042072010 引 言发光二极管(LE D )显示屏按显示颜色可分为单色、双色、全彩色几种,按显示灰度级可分为无灰度和16级、64级、256级等。

对于面积比较大、有灰度要求的显示屏,现今普遍采用的是用计算机控制,借助视频采集卡完成视频图像采集,LE D 显示屏显示内容与显示器同步。

在整个显示系统中,视频采集卡的质量是决定显示系统性能的关键。

一般,视频采集卡设计时较多采用小规模集成电路,而本文介绍的视频采集卡设计方案基于现场可编程门阵列(FPG A )为核心芯片。

与前者相比,基于FPG A 设计的视频采集卡具有设计灵活、可现场编程、便于调试、功耗降低等特点,使系统可靠性得到较大的提高。

1 VGA 同步显示屏的工作原理LE D 显示屏系统包括显示屏控制系统、显示屏体、电源、框架结构等几部分。

其组成如图1所示。

显示屏显示的文字、图像、动画、视频等与计算机显示器全同步运行。

两者之所以同步,是因为显示屏上显示的数据由显示卡经视频卡转换而来,再由LE D 采集发送卡将数据进行转换、存储及灰度等级划分,由分区控制板分配至各显示模块。

基于FPGA的视频图像采集与显示系统设计

YANG Qi n。ZHOU Yu n - f e i +,HU Yo n g - b i n g

( S c h o o l o f Me c h a n i c a l S c i e n c e a n d En g i n e e r i n g,H u a z h o n g Un i v e r s i t y o f S c i e n c e a n d Te c h n o l o g y ,W u h a n 4 3 0 0 7 4 ,C h i n a )

Ab s t r a c t :As CC D c a me r a a n a l o g s i g n a l d a t a i s e n o r mo u s a n d F PGA’ S p a r a l l e l p r o c e s s i n g c a p a b i l i t y i s p o we r f u l ,A p r o j e c t i s

2 0 1 3年 6月

计算机 工程 与设计

C OMPUTE R E NGI NE ERI NG AND DES I GN

J u n - 2 0 1 3

V0 1 . 3 4 NO . 6

第3 4卷

第 6期

基于FPGA的图像的采集与显示

基于FPGA图像的采集与显示学生姓名:学生学号:院(系):电气信息工程学院年级专业:指导教师:助理指导教师:二〇一五年五月摘要随着科技社会的飞速发展,数字图像采集与处理系统在科学研究、工业生产,日常生活等众多领域得到越来越广泛的应用,具有广阔的应用前景和研究价值。

在今天,具有图像显示功能的电子产品越来越多,由可视电话、数码相机,ipad 等消费电子产品到门禁系统、数字视频监视等工业控制以及安防产品,处处显示着数字图像采集与处理系统的重要性。

而针对于图像的采集与处理ARM、DSP、FPGA各有所长,其中FPGA的并行高速精确的处理在通信领域、图像处理、大屏显示等方面有着得天独厚的优势。

基于FPGA可编程器件的可编程特性,采用FPGA进行设计的图形采集系统有良好的可扩展性和相对稳定的硬件结构,利用软件编程和硬件逻辑电路来实现图像采集的软件算法,在很大程度上能够提高图像识别速度和系统的体积,大大节约了生产成本。

本次设计利用OV(OmniVision)公司生产的CMOS 7670摄像头进行图像的的采集以及简单的处理,Hynix公司的SDRAM芯片H57V2562GTR—75C做图像的临时存储,FPGA芯片采用的是Altera公司旗下的Cyclone系列芯片第四代产品EP4CE6F17C8N,利用其并行高速精确的优势实现640*480*60fps,每秒共30M带宽的VGA显示。

此次设计的目的是为了将数字图像采集与显示等功能集成在一块单板上。

利用本系统的电路板对图像进行采集、缓存以及通过VGA实现实时显示,在使用过程中摄像头能够正常实现图像采集,SDRAM能够顺利完成图像的存储与读取,FPGA芯片以及程序能够保证整个系统正常运行,并且在VGA显示时图像没有错位和乱码的产生。

关键词图像的实时采集与显示,FPGA,VGA显示ABSTRACTWith the rapid development of science and technology society, the digital image acquisition and processing system in scientific research, industrial production, daily life and so on many fields more and more widely used, has a broad application prospect and research value.Today, which has the function of image shows more and more electronic products, by video phone, digital camera, the consumer electronics products such as the entrance guard system, industrial control, such as digital video surveillance and security products, shows the importance of digital image acquisition and processing system.And for image acquisition and processing of ARM, DSP, FPGA strengths, including the FPGA parallel high-speed precise processing in the field of communication, image processing, display, etc, has a unique advantage.Based on the FPGA programmable features of programmable devices, using FPGA to design the graphic collection system has good scalability and relatively stable hardware structure, software programming and hardware logic circuit is used to realize image acquisition software algorithms, in the very great degree can improve the recognition speed and the volume of the system, greatly saves the cost of production.This design using the OV (OmniVision) company produces 7670 CMOS camera image acquisition and processing, simple Hynix SDRAM chip H57V2562GTR - 75 c for temporary storage of the image and the FPGA chip USES Altera company's fourth generation product EP4CE6F17C8 Cyclone series chip, using the advantage of its parallel high-speed precise realization of 640 * 480 * 60 FPS,VGA display, a total of 30 m bandwidth per second.The purpose of this design is to integrate the function such as digital ima ge acquisition and display on a single board.The circuit of this system is used to analyse the image acquisition, caching, and through the VGA display in re al time, in the process of using normal camera is able to achieve image acqui sition, SDRAM would be able to complete the image storage and read, the FP GA chip, and procedures to ensure the normal operation of the whole system, and when the VGA display image without dislocation and garbled.Key words image real-time acquisition and display, the FPGA, VGA display目录摘要 (I)ABSTRACT................................................................................................................................. I I1 绪论 (1)1.1 课题背景 (1)1.2 国内外研究现状、水平 (1)1.3 图像采集技术的发展趋势 (2)2 方案论证与选择 (4)2.1 系统方案设计 (4)2.2 系统方案选择 (5)2.3 本课题的技术指标及主要任务 (5)3 系统的硬件设计 (7)3.1 系统原理及设计框图 (7)3.2 FPGA 芯片的选择与其性能分析 (7)3.1.1 FPGA概述 (7)3.1.2 Cyclone系列芯片介绍 (7)3.3 FPGA 最小系统设计 (10)3.3.1 复位电路设计 (10)3.3.2 内部时钟与外部时钟设计 (11)3.3.3 JTAG下载接口及其保护电路设计 (12)3.4 摄像头的选择及其性能分析 (13)3.4.1 OV7670摄像头 (13)3.4.2 摄像头功能框图 (14)3.4.3 摄像头模块 (16)3.5 SDRAM的选择及其性能分析 (17)3.6 VGA接口设计 (19)4 系统的软件设计 (22)4.1 Verilog编程语言介绍 (22)4.2 整体设计思想 (22)4.3 系统主要结构框图以及功能介绍 (23)4.4 SDRAM工作状态机设计 (24)5 仿真设计与波形 (25)5.1 Quartus开发工具的简介 (25)5.2 逻辑分析仪介绍 (26)5.3 逻辑分析仪捕获波形展示 (27)5.4 效果图展示 (28)结论 (29)参考文献 (30)附录A:原理图模块展示 (31)附录B:程序代码 (35)致谢........................................................................................................... 错误!未定义书签。

基于FPGA的VGA显示实验方法

实

验 室 LABORATORY

科 学 SC I EN CE

第 13卷 第 5 期 V o l 13 N o 5

2010年 10 月 O ct 2010

基于 FPGA 的 VGA 显示实验方法

徐吉锋

( 浙江财经学院 信息学院 , 浙江 杭州

表 2 VGA 显示实验接口定义

[ 7]

[ 9] [ 8]

input c lk _25m; input rst_n; 口信号 output hsync ; output vsync ;

/ / 25MH z / /低 电平复位, FPGA 与 VGA 接 / /行同步信号 / /场 同步信号 / /RGB = 000 黑 色; / /RGB = 100 红 色;

[ 5]

SYNC。 3 . 1 字符取模 要显示字符或图像 , 首先需要获得字模数据 , 一 般使用字模软件来获取 , 例如 PCTOLCD2002 软件。 该字模软件用 1B I T 代表一个像素的色彩, 用户可以 根据需要来决定这 1B I T 数据 ( 0 或 1) 代表的色彩。 如需显示图像可使用相关软件把图像转换得到字模 数据存入 ROM 即可。为便于说 明显示方法 , 特以 字符 FPGA 为例, 如下: F ( 0) P( 1) G( 2) A ( 3)

[ 2]

实现 VGA 显示可以有多种方法 , 例如使用基于 N ios II嵌入式处理器来调用 RAM 中的字模等

[ 5- 6]

。

考虑到实验的通用 性, 采用 Verilog 语言 设计 VGA 控制器访问 存有字模数据的 ROM, 并输出到 VGA 显示的方法。

1

电子信息工程专业基于FPGA的SD卡图像的VGA显示毕业设计论文

本科毕业设计(论文) 论文题目:基于FPGA的SD卡图像的VGA显示摘要基于FPGA的SD卡图像的VGA显示,是利用可编程逻辑器件将图像的数据通过VGA 线实现图像的显示控制的,详细说明了在显示控制器中VGA的基本功能作用和其工作原理。

此次设计是在Xilinx公司的ise 14.7软件环境下,使用 Verilog语言来编写程序模块设计,实现SD卡图像的VGA显示控制设计。

要在最终的电脑显示屏上获得图像显示,需通过开发板上电,先读取SD卡中的图像数据并把它存储在DDR3中,然后再将DDR3的图像数据通过VGA线显示到的屏幕上。

传统的图像显示是将数据传送到计算机上,在显示屏上直接显示。

在此过程中,需要信号不断控制图片的数据,这将很大程度上造成CPU资源的浪费,而且系统也脱离不了计算机,造成显示控制的灵活性降低。

但是伴随可编程逻辑器件(FPGA)技术的发展,设计者采用EDA设计方法便可以实现针对性的VGA显示控制,可以脱离计算机来控制系统,并且能够满足实践生产的需要,大大降低了投入成本,产品的更新换代更加迅速方便,推动了行业的发展。

关键词:可编程逻辑器件;VGA ;显示控制AbstractSD card based on FPGA image of VGA display, is the use of programmable logic devices of the image data through the VGA line image display control, in VGA display controller is described in detail the basic functions and its working principle.In Xilinx ise 14.7 software environment, use Verilog language to write the SD card image of VGA display control design, completed the FPGA modular design.Achieve VGA display control, need to electricity, on the development board to read SD card of the image data and store it in DDR3, then continuously read DDR3 image data through the VGA line show on the screen.The traditional image display is to transfer the data to computer, displayed on the screen, in this process, the image data the CPU needs constant control signal, it will largely wastes the CPU resources, but also from the computer system, which reduces the display control flexibility.But along with the development of the programmable logic device (FPGA) technology, the designers use EDA design method can realize the VGA display of the targeted control, can from computer to control system, and can meet the needs of practical production, greatly reduces the cost, upgrading of products is more convenient quickly, promote the development of the industry.Keywords:Programmable logic devices ; VGA ;display control目录前言 (1)第1章 VGA概述 (2)1.1 VGA显示技术的发展概况 (2)1.2 VGA显示接口 (3)1.3 VGA显示原理 (4)1.4 VGA时序 (5)第2章 FPGA简介及设计流程 (8)2.1 FPGA简介 (8)2.2 FPGA设计流程 (8)2.3 Verilog简介 (111)2.4 Xilinx ise14.7简介 (122)第3章设计方案 (14)3.1 设计的主要内容 (144)3.2 设计原理 (155)第4章系统实现 (16)4.1 VGA显示控制模块 (16)4.2 MIG IP控制器 (19)4.2.1 MIG IP介绍 (19)4.2.2 MIG IP的生成 (21)4.3 Image2Lcd和winhex工具的使用 (256)4.4 SD卡顶层设计模块 (269)4.5 顶层设计 (34)4.6 程序下载和设计结果 (345)4.6.1 IMPACT软件进行程序的烧写 (345)4.6.2 设计结果 (347)第5章结束语 (39)参考文献 (41)致谢 (42)附录 (43)前言随着现代化科技的发展,信息化时代的到来,以计算机为核心的电子信息技术正在迅速的发展,各种各样的电子产品进入大众的视野,人们很大一部分的视觉信息都说是通过各种电子显示产品获得的,所以对电子显示设备的需求也越来越多,在众多因素的影响与要求下,对电子技术的要求也越来越高,某种程度上来讲,也促进了电子显示技术的飞速发展。

基于fpga的vga显示

——基于FPGA的VGA显示姓名:王青鹏学号:200661175班级:电子0604日期:200910201.实验目的 (3)2.实验要求 (3)3.实验原理 (3)3.1VGA时序信号 (3)3.2VGA显示时序图 (4)3.3关键参数 (5)3.4VGA显示工作过程 (5)3.5整体设计思路及过程 (6)3.6管脚分配及下载 (15)4.实验心得体会 (16)FPGA的VGA显示一.实验目的1.熟悉和掌握时序控制电路的设计方法。

2.了解VGA显示器的工作时序及其控制电路的工作原理。

3.培养分析系统、进行模块设计及独立解决问题的能力。

二.实验要求1.设计VGA显示器的控制电路,使之控制显示器,完成相应的显示功能。

2.使用一个按钮mod(低有效),使VGA显示器在3种(或4种)不同的显示模式间切换。

使用一个按钮reset,将控制器恢复模式00。

模式00:将屏幕均分,从左到右,依次显示八种不同的颜色。

模式01:将屏幕均分,从上到下,依次显示八种不同的颜色。

模式10:将屏幕均分为8*8棋盘格。

模式11:复位模式,屏幕全黑。

3.利用GW48实验开发系统实现设计的编程下载.三.实验原理3.1VGA时序信号H_SYNC:水平同步信号(负脉冲),每个水平扫描周期显示器刷新V_SYNC:垂直同步信号(负脉冲),每个垂直扫描周期显示器刷新一帧;RGB[2..0]:颜色信号,R——红色信号;G——绿色信号;B——蓝色信号。

其对应颜色关系如下表所示。

3.2VGA显示器的时序图垂直刷新循环3.3关键参数1.实验板上的晶振提供全局时钟信号(50MHz),通过分频得到时钟信号clk25M(fclk=25MHz)作为输入时钟。

2.刷新1个像素所需时间Tpixel=1/fclk=40ns;3.刷新一行所需时间Trow=Tpixel*640+guard bands=25.6us+B +C+E=32.2us;4.一个垂直扫描周期内包含480个水平扫描周期,完成一帧的刷新。

基于FPGA的图像采集及VGA显示

该控制字是判断行、场同步信号和有效数据 的依据,必须准确检测出这个控制字,方法是:在 时钟的上升沿对SAA7113输出的VPO数据进 行采样,当连续采到的3个B为“FF 00 00”时,即 可判断下一个B为时序控制字,然后根据下一个 采到的数据判断出当前帧的状态,并输出给后续 模块。后续模块根据各控制位的电平及跳变情况 确定后面各控制信号的转换。

154

交通信息与安全2009年第4期第27卷总150期

基于FPGA的图像采集及VGA显示*

郑容朱宏辉

(武汉理工大学物流工程学院武汉430063)

摘要根据汽车自动防撞系统前端图像采集模块对实时性处理要求高的特点,提出了1种基于

FPGA的图像采集及VGA显示系统的设计方案。系统中FPGA主要完成对AD芯片的配置,从数字

素点之间的方向性来计算像素点插值的示意图:

r(k-I,n一2)r(k-1,n一1)r(k·l,H)r(k—l,n+1)r(“1,肿2) 第々~1行

燮厂V,-/jX,≯..该.r、给涂p 插值{弛

式孓毽一)

第々+1行

J(斛l·”。2)y(H1,n。1)y(肛1,”)y(肛l,n+1)Y(k+l,肘2:

图2修正沿自适应算法示意图

图中:Yi—Iy(忌一1,行一2+i)一y(是+1,咒+2一

i)I(i=0,1,2,3,4),分别表示以Y(k,竹)为中点

的对角线上像素点上的亮度之差。其中亮度之差

最小的对角线表示具有最强的方向性。当插值最

小的对角线确定后,插值就在该对角线方向上进

行。即如果yf最小,则:

y(志,咒)=(I y(七一1,以一2+i)+

保留,无需配置

H

H

H

基于FPGA的VGA显示设计报告

正文一,VGA时序标准VGA是一种常用的显示输出接口,采用行场扫描控制结合RGB三色合成原理,输出显示信号。

每个VGA接口为15针接口,分三行排布,每行5针。

如图所示:图1.1 VGA接口15针并未全部使用,有效的信号线共5根,即红绿蓝三基色信号线:R,G,B,每线电压从0V到0.71V变化,表示无色到饱和,依据电平高低,显示颜色的饱和程度。

行同步控制信号,Hsync,控制每行扫描像素的有效和失效。

场同步:Vsync,控制场方向,即整个图像显示过程的时间长度,场同步中的显示部分的时间长度,等于每行扫描时间的总和。

在不同刷新频率下,显示每个像素的时间是不同的,相同刷新频率下,每个像素显示时间是固定的,所以,不同的每个像素写入时间,导致了分辨率的不同。

因为VGA的显示是逐行扫描,每行从左到右扫描,到了行尾,回归到下一行的行头,继续向尾部扫描。

所以,显示原理是逐次写入每行的像素数据,直到整幅图像显示成功为止。

VGA显示的数据是不能锁存的,所以必须一次又一次的连续输入数据,72Hz的刷新率下,一秒钟显示72幅图像,所以,需要连续写入72幅图像,才能达到一秒的显示效果。

所以,VGA显示图像,要反反复复写入图像数据,才能得到持续的显示效果。

图1.2 VGA接口线序VGA显示,无法做到类似于TFT液晶屏的定点写入,VGA是扫描式暂时显示,所以时序显得尤为重要,时序出现失误,图像会出现走形,无法达到准确效果。

而显示的时序控制主要依靠两条数据通道:行同步和场同步,即Hsync和Vsync,其控制了扫描显示的起点和终点,同时控制扫描起点的时间,通过时间的控制,达到确定的显示效果。

具体的控制时序图如下:图1.3 VGA 同步时序VGA显示中,以每个像素写入时间作为FPGA时钟周期,所以每个时钟周期写入一组RGB像素值。

逐行写入,所以每行数据显示的结果,拼凑成一帧图像,72Hz下,每秒显示72帧图像。

由于本设计要求静态显示效果,所以,我们只定义一帧的数据,最后无限循环执行即可。

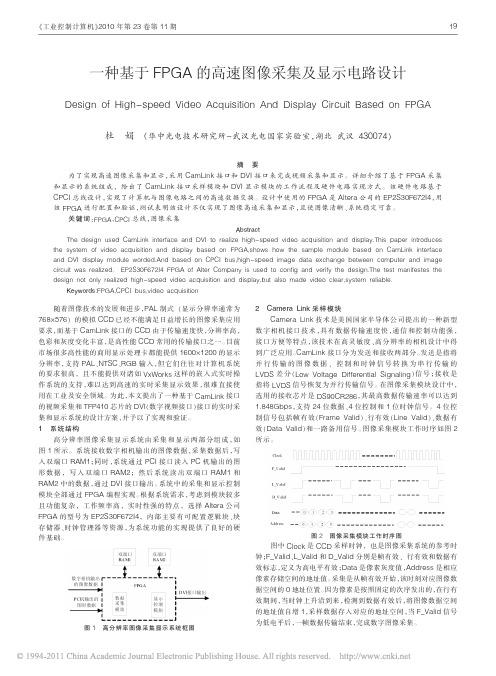

一种基于FPGA的高速图像采集及显示电路设计

《工业控制计算机》2010年第23卷第11期随着图像技术的发展和进步,PAL制式(显示分辨率通常为768×576)的模拟CCD已经不能满足日益增长的图像采集应用要求,而基于CamLink接口的CCD由于传输速度快,分辨率高,色彩和灰度变化丰富,是高性能CCD常用的传输接口之一。

目前市场很多高性能的商用显示处理卡都能提供1600×1200的显示分辨率,支持PAL、NTSC、RGB输入,但它们往往对计算机系统的要求很高,且不能提供对诸如VxWorks这样的嵌入式实时操作系统的支持,难以达到高速的实时采集显示效果,很难直接使用在工业及安全领域。

为此,本文提出了一种基于CamLink接口的视频采集和TFP410芯片的DVI(数字视频接口)接口的实时采集和显示系统的设计方案,并予以了实现和验证。

1系统结构高分辨率图像采集显示系统由采集和显示两部分组成,如图1所示。

系统接收数字相机输出的图像数据,采集数据后,写入双端口RAM1;同时,系统通过PCI接口读入PC机输出的图形数据,写入双端口RAM2;然后系统读出双端口RAM1和RAM2中的数据,通过DVI接口输出。

系统中的采集和显示控制模块全部通过FPGA编程实现。

根据系统需求,考虑到模块较多且功能复杂,工作频率高,实时性强的特点,选择Altera公司FPGA的型号为EP2S30F672I4,内部主要有可配置逻辑块、块存储器、时钟管理器等资源,为系统功能的实现提供了良好的硬件基础。

图1高分辨率图像采集显示系统框图2Camera Link采样模块Camera Link技术是美国国家半导体公司提出的一种新型数字相机接口技术,具有数据传输速度快,通信和控制功能强,接口方便等特点,该技术在高灵敏度、高分辨率的相机设计中得到广泛应用。

CamLink接口分为发送和接收两部分。

发送是指将并行传输的图像数据、控制和时钟信号转换为串行传输的LVDS差分(Low Voltage Differential Signaling)信号;接收是指将LVDS信号恢复为并行传输信号。

基于FPGA的VGA图形显示

电子信息工程专业综合设计(报告)(课程设计)题目基于FPGA的VGA图形显示二级学院电气与电子工程学院专业电子信息工程班级学生学号同组指导教师时间基于FPGA的VGA图形显示摘要:本次的题目是基于FPGA的VGA图形显示,实现VGA图像显示与控制。

本文介绍的主要容围绕着显示特定图片,且图片可受控制的相关原理与方法展开。

根据VGA显示原理,利用VHDL 作为逻辑描述手段,设计了一种基于现场可编程器件FPGA的VGA接口控制器。

实现VGA图像显示控制器是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

FPGA的嵌入式系统中能代替VGA的专用显示芯片,节约硬件成本,节省计算机处理时间,加快数据处理速度并具有显示面积大,色彩丰富、承载信息量大、接口简单等优点。

除此以外FPGA 芯片和EDA设计方法的使用,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,可不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要。

关键字:FPGA VGA 图像控制器一、前言本次课程设计主要是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

VGA是IBM于1987年提出的一个使用模拟信号的电脑显示标准。

在性能上,VGA 将16色模式的分辨率提高到了640×480,同时VGA新提供了一种具有320×200分辨率、256种颜色的图形模式,且所显示的每一种颜色都可从262144(18位)种颜色中选择,VGA的这种色彩显示能力对微机图形/图象软件的发展起到了很大的促进作用先后分别经历了EGA, EGA, VGA, SVGA, XGA, SXGA, UXGA, QXGA, WQXGA, QSXGA, WQSXGA, QUXGA, WQUXGA, 1080P。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R,G,B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

基于FPGA的图像采集与VGA显示系统

龙源期刊网

基于FPGA的图像采集与VGA显示系统

作者:朱奕丹,方怡冰

来源:《计算机应用》2011年第05期

摘要:针对传统的PCI图像采集卡的弊端,利用Altera公司的DE2开发平台,设计了基于现场可编程门阵列(FPGA)的图像采集与VGA显示系统。

该系统以嵌入了NiosⅡ软核的可编程逻辑芯片FPGA作为控制器,以图像传感器、数字存储器、视频D/A转换器、VGA显示接口等作为FPGA外设,利用可编程片上系统(SOPC)技术实现对FPGA及其外设的编程与控制,

最终实现对实时图像的采集、处理与显示。

设计结果表明,利用SOPC技术实现的电子系统具有设计方法灵活高效、可移植性强、易于实现高速数据采集、通用性好等优势。

关键词:可编程片上系统技术;现场可编程门阵列;DE2;NiosⅡ;CMOS图像传感器;视频D/A转换器;VGA显示接口。

基于FPGA的VGA显示

`timescale 1ns / 1ps/////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date:// Design Name:// Module Name:// Project Name:// Target Device:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 ‐ File Created// Additional Comments:///////////////////////////////////////////////////////////////////// /////////////module vga_dis(clk,rst_n,hsync,vsync,vga_r,vga_g,vga_b);input clk; //50MHzinput rst_n; //低电平复位output hsync; //行同步信号output vsync; //场同步信号output vga_r;output vga_g;output vga_b;//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐reg[10:0] x_cnt; //行坐标reg[9:0] y_cnt; //列坐标always @ (posedge clk or negedge rst_n)if(!rst_n) x_cnt <= 11'd0;else if(x_cnt == 11'd1039) x_cnt <= 11'd0; else x_cnt <= x_cnt+1'b1;always @ (posedge clk or negedge rst_n)if(!rst_n) y_cnt <= 10'd0;else if(y_cnt == 10'd665) y_cnt <= 10'd0;else if(x_cnt == 11'd1039) y_cnt <= y_cnt+1'b1;//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐wire valid; //有效显示区标志assign valid = (x_cnt >= 11'd187) && (x_cnt < 11'd987)&& (y_cnt >= 10'd31) && (y_cnt < 10'd631);wire[9:0] xpos,ypos; //有效显示区坐标assign xpos = x_cnt‐11'd187;assign ypos = y_cnt‐10'd31;//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐reg hsync_r,vsync_r; //同步信号产生always @ (posedge clk or negedge rst_n)if(!rst_n) hsync_r <= 1'b1;else if(x_cnt == 11'd0) hsync_r <= 1'b0; //产生hsync信号 else if(x_cnt == 11'd120) hsync_r <= 1'b1;always @ (posedge clk or negedge rst_n)if(!rst_n) vsync_r <= 1'b1;else if(y_cnt == 10'd0) vsync_r <= 1'b0; //产生vsync信号else if(y_cnt == 10'd6) vsync_r <= 1'b1;assign hsync = hsync_r;assign vsync = vsync_r;//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐//显示一个矩形框wire a_dis,b_dis,c_dis,d_dis; //矩形框显示区域定位assign a_dis = ( (xpos>=200) && (xpos<=220) )&& ( (ypos>=140) && (ypos<=460) );assign b_dis = ( (xpos>=580) && (xpos<=600) )&& ( (ypos>=140) && (ypos<=460) );assign c_dis = ( (xpos>=220) && (xpos<=580) )&& ( (ypos>140) && (ypos<=160) );assign d_dis = ( (xpos>=220) && (xpos<=580) )&& ( (ypos>=440) && (ypos<=460) );//显示一个小矩形wire e_rdy; //矩形的显示有效矩形区域assign e_rdy = ( (xpos>=385) && (xpos<=415) )&& ( (ypos>=285) && (ypos<=315) );//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐//r,g,b控制液晶屏颜色显示,背景显示蓝色,矩形框显示红蓝色assign vga_r = valid ? e_rdy : 1'b0;assign vga_g = valid ? (a_dis | b_dis | c_dis | d_dis) : 1'b0; assign vga_b = valid ? ~(a_dis | b_dis | c_dis | d_dis) : 1'b0;endmodule。

基于FPGA的VGA图像显示控制器设计

基于FPGA的VGA图像显示控制器设计第1页一.实验简介本实验介绍了一种利用可编程逻辑器件实现VGA图像显示控制的方法,阐述了VGA 图像显示控制器中VGA显像的基本原理以及功能演示,利用可编程器件FPGA设计VGA 图像显示控制的VHDL设计方案,并在Altera公司的QuartusII软件环境下完成VGA 模块的设计。

而且给出了VGA模块的设计思路和顶层逻辑框图。

最终实现VGA图像显示控制器,VGA图像控制器是一个较大的数字系统,传统的图像显示的方法是在图像数据传输到计算机,并通过显示屏显示出在传输过程中,将图像数据的CPU需要不断的信号控制,所以造成CPU的资源浪费,系统还需要依靠计算机,从而减少了系统的灵活性。

FPGA芯片和EDA设计方法的使用,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要,产品的升级换代和方便迅速。

二.任务要求2.1课题要求设计一个VGA 图像显示控制器。

1.显示模式为640×480×60Hz 模式;2.用拨码开关控制R、G、B(每个2 位),使显示器可以显示64 种纯色;3.在显示器上显示横向彩条信号(至少6 种颜色);4.在显示器上显示纵向彩条信号(至少8 种颜色);5.在显示器上显示自行设定的图形、图像等。

2.2设计目标根据课题要求,实验中将目标进行了细化,叙述如下:1.设定4种显示模式:横彩模式、纵彩模式、纯色模式、用户模式;第2页2.拨码开关最低两位SW1~SW0控制4种模式的切换;3.拨码开关高6位SW7~SW2每两位分别控制RGB显示64种纯色;4.横向和纵向彩条均设置为8种内置的颜色;5.用户模式中分3种子模式:1)子模式1是沿固定轨迹运动模式,固定图形沿水平方向运动,行运动到边界后折回到下一行继续水平运动;2)子模式2是反弹球模式,固定图形在矩形屏幕做内直线运动,到边界后沿反射角方向反弹,周而复始;3)子模式3是受控运动模式,使用上下左右4个按键控制固定图形在屏幕内的运动方向;4)子模式间的切换由一个单独的按键进行控制,按键按下后顺序切换子模式。

基于FPGA的VGA彩条图像显示

基于FPGA的VGA彩条图像显示1. 设计的任务及内容在电子电路领域中,设计自动化工具已经被广大电子工程师所接受,它必将取代人工设计方法并成为主要的设计手段。

目前,Verilog语言已经成为各家EDA工具和集成电路厂商认同和共同推广的标准化硬件描述语言,随着科学技术的迅猛发展,电子工业界经历了巨大的飞跃。

集成电路的设计正朝着速度快、性能高、容量大、体积小和微功耗的方向发展,这种发展必将导致集成电路的设计规模日益增大。

该实训的设计是用Verilog语言硬件描述语言设计出一个VGA图象显示控制器,用Verilog 硬件描述语言进行编程,把Verilog语言描述的VGA图象显示控制器所需的程序在QuartusⅡ软件环境下进行模拟仿真,以此来验证所设计的结果是否满足设计的要求。

在结果符合要求的情况下把Verilog程序下载到FPGA器件上,利用FPGA器件内部存储器存储所需要的数据,再通过VGA接口输出到显示器上,从而达到设计的要求。

VGA显示器因为其输出信息量大,输出形式多样等特点已经成为现在大多数设计的常用输出设备,FPGA以其结构的优势可以使用很少的资源产生VGA的各种控制信号。

CRT显示器作为一种通用型显示设备,如今已广泛应用于我们的工作和生活中。

与嵌入式系统中常用的显示器件相比,它具有显示面积大、色彩丰富、承载信息量大、接口简单等优点,如果将其应用到嵌入式系统中,可以显著提升产品的视觉效果。

如今随着液晶显示器的出现,越来越多的数字产品开始使用液晶作为显示终端。

但基于VGA标准的显示器仍是目前普及率最高的显示器[1]。

若驱动此类显示器,需要很高的扫面频率,以及极短的处理时间,正是由于这些特点,所以可以用FPGA来实现对VGA显示器的驱动。

本次专业课程设计即选用FPGA 来实现VGA的显示。

随着FPGA的不断发展及其价格的不断下降,FPGA的可编程逻辑设计的应用优势逐渐显现出来。

现在,越来越多的嵌入式系统选择了基于FPGA的设计方案。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的图像采集及VGA显示3郑 容 朱宏辉(武汉理工大学物流工程学院 武汉430063)摘 要 根据汽车自动防撞系统前端图像采集模块对实时性处理要求高的特点,提出了1种基于FP GA的图像采集及V GA显示系统的设计方案。

系统中FP GA主要完成对AD芯片的配置,从数字图像信号中提取时序信息和亮度信号,实现去隔行操作以及产生标准的V GA时序等。

实验表明,该方案在满足图像质量要求的同时,较好地兼顾了实时性需求。

关键词 FP GA;N IOS II;图像采集;V GA中图分类号:TP274 文献标志码:A DOI:10.3963/j.ISSN167424861.2009.04.036 随着汽车工业的发展,汽车安全性技术的研究已由被动式安全技术发展到主动式安全技术,“汽车自动防撞系统”正是当前主动式安全技术的研究热点。

作为汽车自动防撞系统的前端图像采集模块,需对采集到的图像数据进行实时处理,其特点是数据量大,实时性要求高。

嵌入式技术的发展为解决上述难题提供了重要的技术支持。

目前,嵌入式数字图像处理技术主要有基于专用芯片、基于DSP和基于FP GA3种处理方式[1]。

基于专用芯征方式的灵活性和系统可更改性差,不适合前期未成熟产品的开发工作。

基于DSP的方式在吞吐量,运行速度,系统结构的可重配性,功能升级等方面存在约束,也不适合用在前端图像采集系统中。

基于FP GA的方式除了FP GA芯片本身的灵活性外,还有以下几点优势:(1)FP GA单片逻辑门数越来越多,内嵌功能越来越强,体积越来越小;(2)FP GA有完整的多平台设计环境,还可以利用第三方的综合、仿真工具;(3)Quart usⅡ的设计方法十分灵活,支持多种编辑方式,具备L PM模块,可调用SOPC Builder完成Nio s系统的配置、生成,还提供了Nios系统的软件开发环境;(4)可进行静态重复编程和动态在系统重配;(5)可在FP GA内部生成外围器件连接模块,简化外围器件的电路和功能,提高电路的稳定性[223]。

系统总体方案系统采用Altera公司的CycloneII系列FP2 GA(EP2C20Q240C8)作为主控制器,该芯片具有18752个L E,240kB的内部RAM容量,26个内嵌乘法器单元,4个模拟锁相环等[4],广泛应用于汽车电子、消费电子、音/视频处理、通信以及测试测量等终端产品市场。

系统还包括:32MB SDRAM,4MB NOR FL ASH,一路调试用串口,视频AD+DA,以及40芯扩展DSP接口等,硬件结构如图1所示。

图1 系统硬件结构系统通过CCD摄像头获取外界图像信号,经视频AD芯片转换成数字信号后输出至FP GA 中。

在FP GA中构建了AD接口模块、去隔行模块、V GA显示模块和N IOS II处理器模块,其中AD接口模块完成从接收到的图像数据中提取有效的亮度信号和时序控制信息,供后续模块使用;去隔行模块完成将摄像头输出的隔行图像数据按收稿日期:2008212215 修回日期:2009206223 3国家自然科学基金项目(批准号:50878132)、住房和城乡建设部2008年科学技术项目(批准号:20082K922)资助作者简介:郑 容(1982),硕士研究生.研究方向:智能控制与嵌入式系统.E2mail:zrynn@照一定的算法转换成逐行输出的图像格式;V GA 显示模块完成标准V GA(640×480,60Hz)时序信号输出以及与视频DA芯片的连接;系统中各模块的控制及外部芯片的初始化均由N IOS处理器模块实现。

各模块的具体实现2.1 视频AD接口模块本系统使用的视频解码芯片为菲利普公司的SAA7113,它是1种集成了解码、采样和量化于一体,并且支持隔行扫描、多种数据输出格式的视频解码器,内置了A/D转换电路、预处理电路及I2C(inter2integrated circuit)接口[5],通过I2C接口对内部寄存器进行配置,即可实现对芯片内部电路的控制。

SAA7113在工作之前需通过I2C总线对其内部寄存器进行配置,系统中采用N IOS处理器来模拟I2C时序。

首先通过SOPC Builder为该N IOS处理器添加2个双向的IO口(分别用来模拟SDA和SCL),然后利用N IOS II ID E中自带的底层驱动来对它们进行操作,比如需要通过SDA引脚向外部写’1’,可以采用如下的语句[6]: IOWR_AL TERA_AVALON_PIO_DIRECTION(SDA_ BASE,0x0);IOWR_AL TERA_AVALON_PIO_DA TA(SDA_BASE, 0x1);在上述函数中,SDA_BASE为对应于SDA 引脚的寄存器,第1条语句的作用是将SDA引脚设置为输出模式,第2条语句的作用是将SDA引脚置为“1”。

如果要从SDA引脚读入数据,必须首先将SDA引脚设置为输入模式。

本系统中,CCD摄像机输出的是N TSC信号,因此,在配置SAA7113时应按照N TSC制式进行配置,否则可能工作不正常。

表1为本系统中SAA7113的寄存器配置值。

SAA7113配置完成后,输出位宽为8bit的表1 SAA7113各寄存器配置值地 址配置值0~1500H08H C0H33H00H00H E0H0D H B8H01H80H47H40H00H01H2A H 15~3138H0CH E8H00H00H00H00H00H00H00H00H00H00H00H00H00H 32~4700H00H00H00H00H00H00H00H00H00H00H00H00H00H00H00H 48~6300H00H00H00H00H00H00H00H00H00H00H00H00H00H00H00H 64~7902H FF H FF H FF H FF H FF H FF H FF H FF H FF H FF H FF H FF H FF H FF H FF H 80~95FF H FF H FF H FF H FF H FF H FF H FF H00H00H0A H80H00H00H00H00H 96~127保留,无需配置YUV4:2:2格式的视频信号,前8位输出亮度信号,后8位输出色度信号。

当输入视频信号为N TSC制式时,SAA7113输出30帧/s图像,每帧图像按照先奇行后偶行的顺序传输。

SAA7113的时序信息由4B组成,即“FF00003”。

其中3为时序控制字,具体含义如表2所示。

表2 SAA7113时序控制字bit位76543210含义固定为“1”1:偶场1:场消隐1:行消隐0:奇场0:有效数据0:行有效保留,不应赋值 该控制字是判断行、场同步信号和有效数据的依据,必须准确检测出这个控制字,方法是:在时钟的上升沿对SAA7113输出的V PO数据进行采样,当连续采到的3个B为“FF0000”时,即可判断下一个B为时序控制字,然后根据下一个采到的数据判断出当前帧的状态,并输出给后续模块。

后续模块根据各控制位的电平及跳变情况确定后面各控制信号的转换。

2.2 去隔行操作SAA7113是按照先奇场后偶场的顺序输出的,即隔行输出,而本系统采用V GA显示,因此需要进行去隔行操作。

目前普遍采用的去隔行算法主要有组合帧法、帧内行平均法、修正沿自适应法和运动补偿法4种算法。

组合帧法是将隔行扫描的奇偶场信号直接拼接,以2倍场频输出。

这种方法未对数据进行复杂的处理,容易实现,对静态图像处理较好;帧内平均法是对同一场的上下2行求平均值的方法来计算插值,达到去隔行的目的,这种去隔行算法实现比较方便,但对画面清晰度损伤较大,会导致锯齿状边沿的产生;修正沿自适应法利用沿的方向相关性对图像进行去隔行,这种算法可以消除图像的锯齿状沿,但在画面细节的显示方面略有不足;运动补偿滤波算法去隔行效果较好,但算法复杂。

本系统主要用于采集高速运动的画面,后期还要完成各种图像的识别,因此对算法的要求是:去隔行后的图像不应出现虚影和错位,且物体的边缘不出现锯齿状沿。

综合分析各算法的优缺点和实现的难易程度,决定采用修正沿自适应法来进行去隔行处理。

修正沿自适应算法的思想是利用相邻行像素点的方向相关性来计算插值。

图2给出了利用像素点之间的方向性来计算像素点插值的示意图:图2 修正沿自适应算法示意图图中:Yi =|Y (k -1,n -2+i )-Y (k +1,n +2-i )|(i =0,1,2,3,4),分别表示以Y (k ,n )为中点的对角线上像素点上的亮度之差。

其中亮度之差最小的对角线表示具有最强的方向性。

当插值最小的对角线确定后,插值就在该对角线方向上进行。

即如果Y i 最小,则:Y (k ,n )=(|Y (k -1,n -2+i )+Y (k +1,n +2-i )|)/2 为实现上述算法,按照图3所示的框图完成了相应代码的编写。

图3 算法框图由于从隔行向逐行转变后,数据量提高了1倍,相应的时钟频率也需要提高,首先通过1个FIFO 将原始隔行数据的速率从13.5M/s 提升至25M/s ,然后将该数据送至FIFO1,当FIFO1完成1行数据的存储后,内部逻辑即开始从FIFO1中读取数据送至FIFO2,同时从FIFO2中读取上1行的第1个数据,一路直接通过二选一MU X 输出,一路与FIFO1中的第1个数据一同送至插值运算模块,插值运算模块即可算出第1个插值,然后存于FIFO3中待输出。

当FIFO2中的数据输出完毕后,FIFO3中也已存满1行经插值运算得到的值,此时二选一MU X 选择FIFO3作为输出,如此往复,即可完成逐行数据输出。

2.3 VG A 显示本系统采用高速、高精度视频DAC 芯片CS7123完成图像数据的数模转换。

该芯片内部包括3路10位电流导引(current steering )结构的DAC ,最大采样速度240M Hz ,是1个3路高速数模转换器的单片集成电路。

对于V GA 显示器而言,当输入的R 、G 、B 信号相等时显示图像为灰度图像,因此,本系统将处理后的亮度数字信号同时输出给CS7123的R 、G 和B 接口,即可在显示器上显示出灰度图像。

标准的V GA 时序如图4和图5所示[6]。

图中Ta 时间段为同步脉冲,Tb 、Tc 、Te 和Tf 为消隐期,Td 为信号有效期,时序驱动在V GA 图像显示设计中尤为重要,稍有偏差,则显示不正常,甚至会损坏显示器,因此应严格按照V GA 的扫描时序进地设计。

行同步头行图像行周期对应位置T fT aTbTcT dTeT g时间(Pixels )8964086408800图4 行扫描时序图及要求(单位:像素)行同步头行图像行周期对应位置T f T aTbTcT dTeT g时间(Pixels )222584808525图5 场扫描时序图及要求(单位:像素) 实验结果与分析图6(a )为系统的输入图像,(b )为去隔行处理后的输出图像。