基于FPGA的VGA显示 论文

基于FPGA的VGA接口显示的设计与实现

编号基于FPGA的VGA接口显示的设计与实现Design and implementation of VGAinterface based on FPGA display学生姓名王雪专业控制科学与工程学号S120400520指导教师杨晓慧学院电子信息工程学院二〇一三年六月摘要利用现场可编程逻辑器件FPGA产生VGA时序信号和彩条图像信号,并将其作为信号源,应用于彩色等离子显示器的电路开发,方便彩色等离子显示器驱动控制电路的调试。

FPGA芯片具有可靠性高、编程灵活、体积小等优点,实验经过软硬件调试,最终在显示器上显示彩条正确图像。

利用此原理,可以设计更多的彩色图像,且可将采集的图像进行实时显示,将此作为信号源,应用于显示器电路的开发或某些嵌入式系统中,进行视频设备的调试与性能分析或系统中信号处理模块的调试与性能分析等。

关键词:FPGA VGA接口时序控制彩条信号AbstractVGA-timing signals and color strip image were obtained by using FPGA.The signals were used as sources when developing the circuits of color plasma display panel, and it took great convenience to the debugging of the driving and controlling circuit of color plasma display panel.The FPGA chip has the advantages of high reliability, small volume, flexible programming,just because of this,the test could achieve the desired results,display scree displays color bar signals.According to this principle, we can design color image more, and make the image real-time display, such as the signal source, used in display circuit development or some embedded systems, video equipment debugging and performance analysis of the system signal processing module debugging and performance analysis.Keywords:FPGA, VGA interface,timing control, color bar signals目录摘要 (1)Abstract (2)第一章引言 (4)第二章VGA显示接口的方案设计和原理 (5)2.1 VGA接口 (5)2.2 VGA显示原理 (5)2.3 VGA信号时序 (6)2.4 VGA显示方案实现 (7)第三章系统模块设计 (8)3.1系统模块原理图 (8)3.2 分频模块 (8)3.3 VGA彩条信号产生模块 (8)3.4 实验结果 (12)第四章结论 (13)致谢 (14)参考文献 (15)第一章引言视频图形阵列(VGA)作为一种标准的显示接口已经得到广泛的应用。

基于FPGA的VGA彩色图片的显示现场可编程门阵列

论文摘要:本论文依据VGA接口原理采用了Verilog HDL语言对Altera的Cyclone系列的FPGA进行了设计,通过MATLAB 二值化得到图片颜色的数据,将得到的数据存储到ROM中,然后读取ROM中的数据直接送到显示器,节省了计算机的处理过程,加快了数据的处理速度,节约了硬件成本。

此方案可以广泛应用于各种仪器,数字视频系统、高分辨率的彩色图片图像处理、视频信号再现等。

论文关键词:现场可编程门阵列,图像控制器,只读存储引言VGA接口显示器是计算机系统以及智能仪器中重要的显示终端设备。

标准的VGA接口需要提供以下几组基本的信号:行同步信号Hsync场同步信号Vsync以及红黄蓝3路模拟信号。

因此要使数字图像信息在VGA接口显示器正确、完整地显示,就涉及到了时序的构建和数字图像信息的模拟化两方面。

如果接口前端无可供利用的时序信息,那么就可参照有关标准来构造时序,这可利用可编程器件很方便地实现;另外由于VGA是一个模拟的接口标准,因此数字图像信息模拟化可用视频DA转换器来实现。

VGA标准是当前最常用的视频显示标准,还包括SVGA、XVGA等子标准。

本文主要以640×480,60Hz下VGA显示标准为例,实现一个满足多方面需求的VGA显示终端接口。

设计可应用于图像处理、视频信号再现、数据可视化分析等方面,实现方法和器件的选取以及设计应用列举都具有典型的代表意义。

理论分析VGA显示接口的硬件设计和原理(1)基本原理说明这次系统设计使用的显示器是满足VGA标准的常用的彩色显示器,由CRT(阴极射线管)构成,彩色由G、R、B(绿:Green,红:Red,蓝:Blue)三基色组成。

显示则用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB三基色,合成一个彩色像素。

硬件选用了AnalogDevice公司的ADV7123。

ADV7123由三个10位高速DAC 组成,最高时钟速率为240MHZ,即可以达到最高240MS/s的数据吞吐率。

浅论FPGA的VGA汉字显示系统设计与实现

浅论FPGA的VGA汉字显示系统设计与实现摘要:提出一种基于Xilinx的Spartan一3E的FPGA显示方案,由于FPGA芯片具有可靠性高、编程灵活、体积小等优点,采用其控制VGA 接口进行汉字显示,有效地解决了通用处理器控制VGA接口显示汉字的缺点。

对新方案进行理论分析和实验,结果证明该方案达到了预期效果。

XX 关键词:显示绘图陈列;现场可编程门陈列;VGA汉字显示XX随着科技的,VGA汉字显示系统的应用范围越来越广泛,传统的VGA字符显示方案是通过通用处理器控制VGA接口显示字符信息的,这种显示方案是以通用处理器为核心的处理系统,整个系统体积大、可靠性不高且灵活性差,不适合便携设备的设计.而FPGA芯片具有可靠性高、编程灵活和体积小等特点,因此用FPGA技术来实现VGA汉字显示可以有效解决传统技术中的缺点。

XXFPGA管脚**丰富,运行速度快,可以实现大规模的系统设计,而且由于FPGA具有可重构能力和抗干扰能力强等优点,使其越来越多地应用于控制领域.利用FPGA控制VGA显示汉字,可使汉字显示脱离Pc机的控制,构建体积小、功耗低的**种嵌入式系统,可应用在人机界面、地面勘测、电子设备、智能仪表和性能监测等方面。

XX1、VGA汉字显示XXVGA的汉字显示是利用VGA的显示原理,使用正确的时序信号对VGA 接口相应管脚进行控制输出RGB颜色信息来显示相应的字符信息,其中VGA显示原理及时序信号的控制必须遵循VGA的标准。

显示处理前端中的SRAM 中存储的每一位数据对应相应LCD显示屏上一个像素点的亮和灭, 1 表示亮,0表示灭.在显示设备上显示汉字也就是按照汉字的点阵图向显示器上输出1或0的高低电平,从而在显示器上显示出具体的汉字 .2、VGA显示控制器的FPGA实现FPGA芯片作为**控制器控制整个系统的处理,根据自顶向下的设计流程,按照层次化、结构化的设计方法可以将FPGA系统划分为以下几个模块:顶层模块、分频模块、VGA控制模块、存储功能模块和RAM读取控制模块。

基于FPGA的VGA显示系统的设计与实现

责任编辑:叶雷

基于FPGA的VGA显示系统的设计与实现

Design and implementation of VGA display system based on FPGA

陈启武 白天蕊 西南交通大学 信息科学与技术学院(四川 成都 610031)

基色信号实现图像的正确显示。

图像显示控制模块vga_control_module.v的部分代码如

下:

module vga_control_module

(

input CLK, RSTn, Ready_Sig;

input [10:0] Column_Addr_Sig, Row_Addr_Sig,

input [63:0] Rom_Data;

摘要:针对VGA(视频图形阵列)接口显示器的检测需求,设计了一种基于Altera FPGA的VGA显示系统。详细介 绍了VGA显示的原理,采用硬件描述语言Verilog完成了VGA显示所需的驱动时序和图像存储相关模块的设计,并 对整个系统进行了综合仿真,验证了设计的正确性。仿真与测试结果表明,该设计可以在简单的情况下实现图像 或字符显示,节约了硬件成本,还可以满足不同显示标准的需要。 关键词:VGA;图像显示;FPGA;设计实现 DOI: 10.3969/j.issn.1005-5517.2016.2.013

此外,FPGA电路的可重构性,为系统功能的优化和升级以及

功能拓展提供

了很大的设计

空间。因此,

由FPGA完成

VGA图像的显

示和控制,较

好的实现了图

图1 VGA接口电路

像数据处理的

实时性和可靠性,具有成本低、结构简单、应用灵活的优点, 可以广泛应用于视频和计算机的显示技术领域。

基于FPGA的VGA图象信号发生器设计

VGA(视频图形阵列)作为一种标准的显示接口在视频和计算机领域得到了广泛的应用。

VGA图像信号发生器是电视台、电视机生产企业、电视维修人员常用的仪器,其主要功能就是产生标准的图像测试信号。

VGA图像信号发生器的设计涉及到图像数据的处理,对电路的工作速度和性能要求较高,VGA工业标准要求的时钟频率高达25MHz,使用传统的电子电路设计方法是难以实现的。

采用专用的视频处理芯片,其设计技术难度大、开发成本高。

本文采用FPGA+MCU方案,利用了Cyclone系列的FPGA高达上百兆的工作频率特性为图像数据处理提供了良好的实时性,其内部集成的数字锁相环为系统的工作时钟提供的良好的稳定性,其内部嵌入的存储器可以存储一定容量的图像信息,丰富的I/O资源可以随即扩展外接大容量存储器的特性,因此由 FPGA完成对图像数据的处理及产生行场扫描时序信号。

很好地实现了图象数据处理的实时性和稳定性,达到了性能与价格的完美统一。

此外,FPGA的电路可重构性,为系统功能更改和升级以及功能扩展提供了很大的设计空间。

由微控制器完成功能设置与控制,如键盘扫描,模式选择与显示控制等。

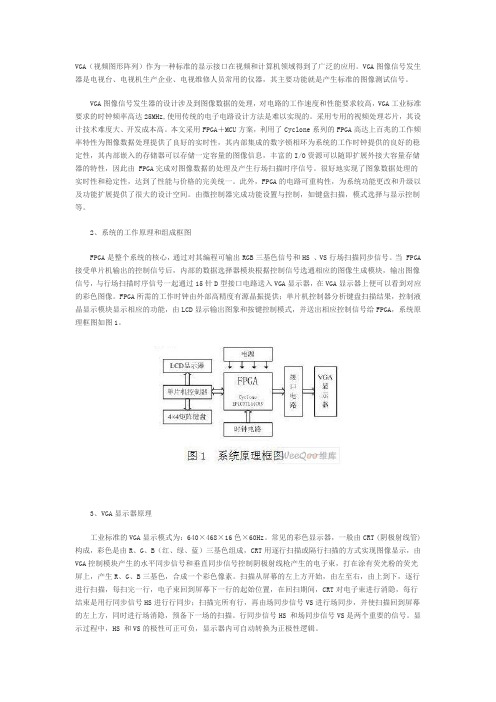

2、系统的工作原理和组成框图FPGA是整个系统的核心,通过对其编程可输出RGB三基色信号和HS 、VS行场扫描同步信号。

当 FPGA 接受单片机输出的控制信号后,内部的数据选择器模块根据控制信号选通相应的图像生成模块,输出图像信号,与行场扫描时序信号一起通过15针D型接口电路送入VGA显示器,在VGA显示器上便可以看到对应的彩色图像。

FPGA所需的工作时钟由外部高精度有源晶振提供;单片机控制器分析键盘扫描结果,控制液晶显示模块显示相应的功能,由LCD显示输出图象和按键控制模式,并送出相应控制信号给FPGA,系统原理框图如图1。

3、VGA显示器原理工业标准的VGA显示模式为:640×468×16色×60Hz。

常见的彩色显示器,一般由CRT (阴极射线管)构成,彩色是由R、G、B(红、绿、蓝)三基色组成,CRT用逐行扫描或隔行扫描的方式实现图像显示,由VGA控制模块产生的水平同步信号和垂直同步信号控制阴极射线枪产生的电子束,打在涂有荧光粉的荧光屏上,产生R、G、B三基色,合成一个彩色像素。

FPGA的串口通讯VGA显示 文献综述 1111

基于FPGA的串口通讯与VGA显示文献综述关键词:VGA显示VHDL 串口通讯FPGA引言视频采集卡不仅能用于影像处理,还可以用一台显示器同时显示、监控多台主机的内容,达到实时控制多台主机的目的。

随着数字影像技术的不断发展,使得视频采集卡的需求不断增加,在电子通信与信息处理领域得到广泛应用。

而传统的视频采集卡硬件实现复杂,难于向便携、嵌入的方向发展。

因此,设计一种硬件简单、使用方便、便于嵌入到系统中的视频信号采集电路具有重要的意义。

随着FPGA(现场可编程门阵列)集成度的增加、功耗和价格的不断降低,现在的视频采集卡的实现可以由FPGA来实现。

本文设计的VGA(视频图形阵列)显示模式和像素频率的识别方法,可以作为由FPGA实现的视频采集卡的一个模块,并且应用中具有可靠性高、性能稳定、调试简单、可扩展性好及设计成本低等特点。

1 VGA显示原理随着显示技术的不断发展,在业界制定了多种显示协议标准。

根据分辨率和刷新频率的不同,显示模式的发展可分为:VGA(640×480像素);SVGA(高级VGA,800×600像素);XGA(可扩展图形阵列,1 024×768像素)。

本文可以识别各种刷新频率的上述显示模式,并得到像素频率值,进一步应用于A/D转换器采样模块处理中。

常见的彩色显示器一般由CRT(阴极射线管)构成,彩色是由R(红)、G(绿)、B(蓝)3色组成。

显示是采用逐行扫描的方式,阴极射线枪发出的电子束打在涂有荧光粉的荧光屏上,产生RGB三色基,最后合成一个彩色图像。

从荧幕的左上方开始向右扫描,每扫完一行图像电子束回到下一行的最左端,每行结束后电子枪回扫的过程中进行消隐。

然后从新开始行扫描,消隐……,直到扫到荧幕的右下方,电子束回到荧幕的左上方从新开始新的图像扫描,并且在回到荧幕左上方的过程中进行消隐。

在消隐过程中不发射电子束。

每一行扫描结束时,用HS(行同步)信号进行同步;扫描完所有的行后用VS(场同步)信号进行同步。

基于FPGA的单片机VGA显示

科 技信 息

— 黑龙 江—

基于 F G P A的单片机 V A显示 G

摘 要: 介绍一种基于即G A的单片 v A 机 G 显示方案, 利用FG 和扩展 R M设计了 pA A 一个类似点阵LD c 显示的v A显示控制器, 现文 G 可实 字及简单的图 表显示。工作时单片机只需将要显示内 容转时应字 模送入 FG , P A 即可实现相应内 容的显示。 关健词: AV A显示控制; 即G ;C 单片机 单片机具有性能价格比高、功能灵活、 易 引言。 G 英文全称是V e rh 的 V A ioG pi d a c 良 但它在 A a 视频图 列) 一种图 ry ( 形阵 是 像显示 模式。 通 于人机对话、 好的数据处理能力特点, 常的应用是由高级处理器加专用芯片来实现。 做V A G 显示时则存在速度和资源上的问 而 题, 然而并不是每个应用场合都需要高级处理器及 FG 则具有高速、 PA 高可靠以及开发便捷、 规范 在功能上, 单片机与大规模C D L P 有很 较高的显示质量。 针对 8 位单片机的V 显 等优点。 以 示, 采用 即G A设计了 V A接口及显示控制 强的互补性。 G 器。 该方案成本低、 体积小可广泛应用于超市柜 本设计就是采用 FC 和必要的R M做 PA A 接口, 实现了单片机 V A G 显示。显示时单片机 台 计费等低成本应用场合。 将需要显示的内 容转换为类似 LD显示的字 C IV A显示原理 G 常见的V 显示器, A G 一般由C ( T R 阴极射 模, 该显示内 同 容的 位置信息送人连接在 F- P A A 然后F以 的 P 线管) 构成, 彩色是由CRB 绿心rn红: G 上的R M相应存储单元中。 、、 ( e, e A G 值以一定的频率送 R , B e三基色组成。 d e 蓝: u) l 显示是用逐行扫描 从 R M中取出相应 R B 的 方式解决, 极射线枪发出电 阴 子束打在涂有 出, 实现v 显示的 场扫描。 A G 行、 使得单片机像 荧光粉的荧光屏上, R B三基色, 产生 G 合成一 控制点阵液晶 一样方便地控制V A G 显示。 图2 单片机与 FG P A接口 框图 . 3 A M读写控制。 2R 由于本设计只为单片 个彩色像素。 扫描从屏幕的 左上方开始, 从左到 3FG 程序设计 PA 本设计中F( P A主要完成三个工作, ; 单片 机提供简单的显示, 右, 从上到下, 进行扫描, 每扫完一行, 电子束回 为降低硬件开发成本, 将一 R M读写接口、G V A扫描控制, 个象素信息压缩为3i 这样 V 显示器就可 到屏幕的 左边下一行的起始位置, 在这期间, 机数据接口、A bt 。 以 以显示八种颜色, 已完全满足该系 统要求。 本设 C 对电子束进行消隐, T R 每行结束时, 用行同 下面分别对各模块进行介绍。 步信 号进行行同 扫描 步; 完所有行, 用场同 步信 8 2 A 3 即以 与单片机接口。 . 1 本方案设计中, 计采用了三块 1 K的R M来分别存储每个 号进行场同步, 并使扫描回到屏幕的左上方, 单 片 机 采 用 A l 司 的 A 8C5 D 象素的RcB 同 e m t 公 T9 W 5 o 、、 值。 时进行场消隐, 预备下一场的扫描。 此设计中的 A R M数据 由单片机写人, 盯s 5W 通过A C、nw 、 g sD C 比、sR 、 EP ( o口 数 对于普通的V A显示器, G 其引出线共含 5 据地址复 同即G 芯片 PA 如采用双口R M Da R M) A (u 一 八 将会 l 用) A 相连接。L : AE地址锁 FG 读出, 个信号:、 : R认B三基色信号;S行同步信号; 存信号。 : H: s C 片选信号。 D读信号。 R写信 使设 R: w : 计非常 简单方便。 然而由 于双口R M A 价 号。A 一 D : O D A 7数据地址复用信号。A 、S 格较高, E L C、 为降低成本, 本设计巧妙利用 FC 采 P六 v: 步 s 场同 信号。 对于 5 个信号的时序驱动, 对于 V A显 R 、 EA 一 D 的 G A 即利用 FC PA DW 、D A 7 时序 参见文 l。 用单口R M实现了双口的功能。 O 关系 献[ ] 本 模块的 设计思想是, 首先在每个A 下 的高速性能, 比 示器要严格遵循 ‘G 工业标准” V , A ,即创O x 先产生一个高速脉冲, 分时复 用 地址, 当此时锁存地址与目的地 R M总线。在高速脉冲高电平期间即G 对 A A 8x0Z 406H 模式。 通常我们用的显示器都满足工 降沿锁存 印 口 业标准, 因此我们设计V A G 控制器时要参考显 址匹配时, 开始检测 R 、 E当出现有效沿时 R M进行写操作, DW , A 将单片机送来得数存人对应 示器的技术规格。如图 1 V A 是 G 行扫描、 场扫 分别对印 口 进行读写操作。 这样利用单片机的 R M单元。在其低电平期间 FG R、 冉 P A对 l M进 描的时序图: A E R 、 E做敏感信号控制 FG L 、DW P A中设置的 行读操作, 取出数据到存人 F以 内部生成的 P 显示缓存中。 G B 行 消隐 R 图像 行 消隐 丫 下 一场 图像 此处之所以要将读出的数据进行缓存是 因为上面所说的: 一个象素由R 三个比特颜 B G 色信息构成。 这三比 特分别存在三 A 块R M中, I T c T e l 由于 读取只能按照字节读取, 设计中三 故本 块 祠- 一 一 - - -一 一一一一一 一 -一几 一一 . 一 一  ̄ - - - 一 一 一 一一 一— 一 一 一 下 R M的地址线并接在 F A上, A G P 使得存取地址 行扫描时序要湘像素 ( 即输出一像苏 l l 护x 的时间间隔): e T晰 同 a 步头): 几:4 T : T ( % 0 。 S d 行图像): 。T : f 8 冈 e ST: 相同。 FC 读一次R M即可同时获得 这样 P A A 八 T ( 像): : 行图 0 8 个象素点的颜色信息, 降低了系统对 R M A存 取速度的 要求。这样则需要在 FG 读取一 P A 字 GR 场 消 隐 B 图像 场 消隐 X 下一场 图像 节数据后应先将其缓存到 FG 部的寄存器 P A内 中, 然后按 V A时序要求高速送出, G 从而实现

基于FPGA的VGA图像显示系统的设计

基于FPGA的VGA图像显示系统的设计杜宗展;王振河;冯迎春【期刊名称】《现代电子技术》【年(卷),期】2015(38)16【摘要】As a standard display interface,VGA(video graphics array)has been widely used. According to the principles of VGA and FPGA(field programmable gate array),the designed VGA interface based on FPGA can send the data to the dis-play directly,and grayscale of the output image was added to this design. Compared to the traditional design,there is no com-puter processing procedure in the design,which can save the expense of hardware and enhance the speed of data processing. It is widely used to the domain of video display.%VGA(视频图形阵列)是一种标准的显示接口,被广泛应用.根据VGA,FPGA(现场可编程门阵列)的作用原理,设计的基于FPGA的VGA 接口可以直接将数据送至显示器,同时增添了关于输出图像灰度等级的设计.与传统设计相比,该设计没有计算机的处理过程,可节省硬件成本,加快数据处理速度,被广泛应用到视频显示领域.【总页数】5页(P95-99)【作者】杜宗展;王振河;冯迎春【作者单位】山东大学电气工程学院,山东济南 250061;山东电力集团公司检修公司,山东济南 250061;山东电力集团公司检修公司,山东济南 250061【正文语种】中文【中图分类】TN919-34;TP391.8【相关文献】1.基于FPGA的VGA图像显示系统的设计与实现 [J], 周卓然;徐道连;吕凤飞;付少华2.基于FPGA的VGA图像显示控制的设计和实现 [J], 李云;刘桂华3.基于FPGA的VGA图像显示及控制系统的设计与实现 [J], 李营;吕兆承;陈帅;权循忠4.基于FPGA的VGA图像显示设计 [J], 桂淮濛5.基于FPGA的UART控制VGA图像显示器设计 [J], 李营; 范静静; 权循忠; 吕兆承; 陈帅因版权原因,仅展示原文概要,查看原文内容请购买。

基于fpga的vga图像显示控制器设计__本科毕业设计论文

基于FPGA的VGA图像显示控制器设计第1页一.实验简介本实验介绍了一种利用可编程逻辑器件实现VGA图像显示控制的方法,阐述了VGA 图像显示控制器中VGA显像的基本原理以及功能演示,利用可编程器件FPGA设计VGA 图像显示控制的VHDL设计方案,并在Altera公司的QuartusII软件环境下完成VGA 模块的设计。

而且给出了VGA模块的设计思路和顶层逻辑框图。

最终实现VGA图像显示控制器,VGA图像控制器是一个较大的数字系统,传统的图像显示的方法是在图像数据传输到计算机,并通过显示屏显示出在传输过程中,将图像数据的CPU需要不断的信号控制,所以造成CPU的资源浪费,系统还需要依靠计算机,从而减少了系统的灵活性。

FPGA芯片和EDA设计方法的使用,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要,产品的升级换代和方便迅速。

二.任务要求2.1课题要求设计一个VGA 图像显示控制器。

1.显示模式为640×480×60Hz 模式;2.用拨码开关控制R、G、B(每个2 位),使显示器可以显示64 种纯色;3.在显示器上显示横向彩条信号(至少6 种颜色);4.在显示器上显示纵向彩条信号(至少8 种颜色);5.在显示器上显示自行设定的图形、图像等。

2.2设计目标根据课题要求,实验中将目标进行了细化,叙述如下:1.设定4种显示模式:横彩模式、纵彩模式、纯色模式、用户模式;第2页2.拨码开关最低两位SW1~SW0控制4种模式的切换;3.拨码开关高6位SW7~SW2每两位分别控制RGB显示64种纯色;4.横向和纵向彩条均设置为8种内置的颜色;5.用户模式中分3种子模式:1)子模式1是沿固定轨迹运动模式,固定图形沿水平方向运动,行运动到边界后折回到下一行继续水平运动;2)子模式2是反弹球模式,固定图形在矩形屏幕做内直线运动,到边界后沿反射角方向反弹,周而复始;3)子模式3是受控运动模式,使用上下左右4个按键控制固定图形在屏幕内的运动方向;4)子模式间的切换由一个单独的按键进行控制,按键按下后顺序切换子模式。

基于FPGA的VGA视频显示的设计与实现

机 电产 品 开 笈 与钏 崭

VOI . 2 9, NO. 6 Nov . , 20 1 6

基于 F P GA的 V GA视频显 示的设计与 实现

赵 誉 婷

( 公 安 部 第一 研 究 所 ,北 京 1 0 2 2 0 0 )

摘 要 : 论 文 介 绍 了 基 于 F P GA 芯 片 Cy c l o n e I I I 的 VG A 视 频 显 示 的 设 计 与 实 现 。 重 点 阐 述 并 解 决 了设 计

据存 储 采 用 S DR A M, 并 实 现 了常 见标 准 显 示格 式 S X G A

( 1 2 8 0 x 1 0 2 4 @6 0 H z ) 的视 频 显 示 。本 文 采 用 C y c l o n e I I I

中遇到 的难 点 : S DRAM 控 制模 块设 计 、 视 频 显 示时序 设 计及 高速 电路设 计 。 实现 了标 准格 式 s x-

GA 模 式 的 视 频 显 示 。

关 键 词 :F P G A ;Cy c l o n e ;S DKA M ; 高 速 电 路 设 计 ;VGA 时序

0 引言

模 拟 视 频传 输 标 准 V G A 接 口【 l j 提 供 了 一种 简 单 、 低

成 本 的连 接显示 器 , 显 示 图像和 信息 的方 法 。 作为 一种 标

1 S DR AM 控 制 模 块 的设 计

1 . 1 SD R AM 的 控 制

本文采用 了 S D R A M 芯 片MT 4 8 L C 3 2 M1 6 A 2 【 引 。S D R A M

ZHA 0 Yu 一死 几 g

( T h e F i r s t I n s i t t u t e o f Mi n i s t r y o f P u b l i c S e c u r i t y o f P . R. C, Be i j i n g 1 0 2 2 0 0, Ch i n a )

基于FPGA的VGA的字符显示

基于FPGA的VGA的字符显⽰题⽬基于FPGA的字符显学⽣姓名指导⽼师学院专业班级1、背景随着电路设计技术的进步,微处理器和微控制器的处理能⼒得到很⼤的提⾼,但是其输出显⽰能⼒却⽐较弱。

还不如普通的PC机的显⽰能⼒,严重制约了其发展。

⽽本⽂提出的基于FPGA的VGA字符显⽰则能很好提⾼其输出显⽰能⼒。

VGA(Video Graphics Array)是IBM在1987年随PS/2机⼀起推出的⼀种视频传输标准,具有分辨率⾼、显⽰速率快、颜⾊丰富等优点,在显⽰器领域得到了⼴泛的应⽤。

近年来FPGA在嵌⼊式系统中得到了⼴泛应⽤,本实验对基于FPGA的VGA显⽰系统进⾏了研究,该系统可以很好的实现VGA 字符的显⽰和控制,系统具有成本低、结构简单、应⽤灵活的优点,具有⼴泛应⽤前景。

基于FPGA的VGA接⼝原理如图l所⽰,图中基于FPGA的VGA接⼝原理如图l所⽰,图中由FPGA产⽣的数据信号经过D/A转换为相应的VGA信号,送到VGA适配器。

1.1 FPGA的发展和其他可编程逻辑器件⼀样,FPGA也由未完成的逻辑阵列所组成,通过将这些逻辑阵列连接到⼀起来完成⼀定的功能。

像PAL⼀样,各个阵列单元之间的相互连接是可以编程的。

下⾯介绍FPGA的发展过程。

1985年,Xilinx公司推出了世界上第⼀款FPGA。

推出的这款FPGA包括两个器件和⽀持布同布线的设计⼯具。

FPGA的发展⾮常快,在不到10年的时间⾥,时钟频率就从不到10MHz 提⾼到100MHz.设计规则已经达到亚微⽶级别,FPGA芯⽚的规模也从⼏千门增加到2万多等效门。

⼤量功能强⼤易⽤的软件⼯具也相继推出,使得FPGA很快占领了电⼦设计领域很⼤的⼀块市场。

20世纪80年代推出的FPGA可以说是Intel公司于1971年推出第⼀款商⽤微处理器的延续。

那个时期,典型的微处理器系统包含微处理器、存储器和⼀些特殊功能的中⼩规模(MSI/SSI)器件。

为追求更佳的件能、更⼩的尺⼨、更低的成本、更快的错误恢复能⼒、⾼可靠性以及更快更易使⽤的原型,集成电路的设计者都意识到⼀定会有⼀种器件要取代当时的中⼩规模电路。

基于FPGA的VGA显示接口的研究与设计

基于FPGA 的V GA 显示接口的研究与设计陈姚节 卢建华(武汉科技大学 武汉430081)摘 要 V GA (视频图形阵列)作为一种标准的显示接口得到广泛的应用。

文章依据V GA 显示的原理,“抛弃”V GA 显示专用芯片,采用FPGA (现场可编程门阵列)设计V GA 接口可以将要显示的数据直接送到显示器,节省了计算机的处理过程,加快了数据的处理速度,节约了硬件成本。

关键词 FPGA ;V GA ;显示接口中图分类号:T P 365.1 文献标识码:BAbstract :A s a standard disp lay in terface ,V GA has been w idely u sed .A cco rding to the p rinci p le of V GA disp lay ,to discard the ch i p fo r V GA disp lay and u se FPGA to design a V GA in terface can send the data directly on to the screen fo r disp lay ,w h ich cu ts dow n the p rocess of PC ,thu s qu icken ing the speed of data p rocess and saving the expen se of the hardw are .Key words :FPGA ;V GA ;disp lay in terface收稿日期:2005201207 3国家高新技术研究发展计划项目资助(2003AA 414011)1 FPGA 的原理CPLD 、FPGA 是在PAL 、GAL 等基础上发展起来的一种具有丰富的可编程I O 引脚、逻辑宏单元、门电路以及RAM 空间的可编程逻辑器件,几乎所有应用门阵列、PLD 和中小规模通用数字集成电路的场合均可应用FPGA 和CPLD 器件。

基于FPGA的VGA显示控制设计

引言基于FPGA的VGA显示控制设计1 引言1.1 选题背景CRT显示器作为一种通用型显示设备,如今已广泛应用于我们的工作和生活中。

与嵌入式系统中常用的显示器件相比,它具有显示面积大、色彩丰富、承载信息量大、接口简单等优点,如果将其应用到嵌入式系统中,可以显著提升产品的视觉效果。

如今随着液晶显示器的出现,越来越多的数字产品开始使用液晶作为显示终端。

但基于VGA标准的显示器仍是目前普及率最高的显示器[1]。

若驱动此类显示器,需要很高的扫面频率,以及极短的处理时间,正是由于这些特点,所以可以用FPGA来实现对VGA 显示器的驱动。

本次专业课程设计即选用FPGA来实现VGA图片的显示。

随着FPGA的不断发展及其价格的不断下降,FPGA的可编程逻辑设计的应用优势逐渐显现出来。

现在,越来越多的嵌入式系统选择了基于FPGA的设计方案。

在基于FPGA的大规模嵌入式系统设计中,为实现VGA显示功能,既可以使用专用的VGA接口芯片如SPX7111A等,也可以设计和使用基于FPGA的VGA接口软核。

虽然使用VGA 专用芯片具有更稳定的VGA时序和更多的显示模式可供选择等优点,但设计和使用VGA接口软核更具有以下优势:(1)使用芯片更少,节省板上资源,减小布线难度;(2)当进行高速数据传输时,具有更小的高频噪声干扰;(3)FPGA(现场可编程门阵列)设计VGA接口可以将要显示的数据直接送到显示器,节省了计算机的处理过程,加快了数据的处理速度,节约了硬件成本。

1.2 目的和意义显示绘图阵列(video graphic array,VGA)接口,他作为一种标准的显示接口得到了广泛的应用。

VGA接口大多应用在显示器与显卡之间;同时还可以用用在擦二色等离子电视输入图像的模数转换上;VGA接口同样也是LCD液晶显示设备的标准接口[2]。

可编程逻辑器件随着微电子制造工艺的发展取得了长足的进步[3]。

早期的器件只能存储少量的数据,完成简单的逻辑功能;发展到现在,可以完成复杂的逻辑功能,速度更块,规模更大,功耗更低。

基于FPGA的VGA显示设计及仿真实现

本科毕业论文(设计)论文题目:基于FPGA的VGA显示设计及仿真实现姓名:XXX学号:XXX班级:XXX年级:XXX专业:通信工程学院:信息工程学院指导教师:XXX完成时间:XXXX 年X月XX 日作者声明本毕业论文(设计)是在导师的指导下由本人独立撰写完成的,没有剽窃、抄袭、造假等违反道德、学术规范和其他侵权行为。

对本论文(设计)的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

因本毕业论文(设计)引起的法律结果完全由本人承担。

毕业论文(设计)成果归XXX所有。

特此声明。

作者专业:作者学号:作者签名:年月日基于FPGA的VGA显示设计及仿真实现XXXThe Design and Implementation of the VGA display based on FPGAXXXX 年X月XX 日摘要本文简述了VGA显示的特点和工作原理,重点介绍了采用自顶向下层次化、模块化的设计方法,在FPGA上实现VGA的显示设计。

显示绘图阵列(video graphic array,VGA)接口是LCD液晶显示设备的标准接口,VGA具有分辨率高、显示速率快、颜色丰富等优点。

显示器因为其输出信息量大,输出形式多样等特点已经成为现在大多数设计的常用输出设备。

在FPGA的设计中可以使用很少的资源,就产生VGA各种信号,再加上VHDL语言灵活的描述方法以及与硬件无关的特点,使得使用VHDL语言基于FPGA芯片实现VGA 显示控制成为研究的方向。

本文对基于VHDL的VGA的显示控制进行了研究,并设计了VGA显示器彩条信号发生器。

所做的主要工作为:(1)在设计中采用了自顶向下的层次化、模块化的设计思想,将整个接口划分为多个模块,利用VHDL语言的描述方法进行了各个功能模块的设计,最终完成了VGA显示的系统设计。

(2)运用ISE软件进行仿真。

关键词:VHDL;VGA;ISE;彩条信号AbstractThis paper briefly describes the characteristics and working principle of VGA display, focus on using the top-down hierarchical and modular design method, realization of VGA display design on FPGA.Display graphics array (video graphic array, VGA) interface is a standard interface LCD liquid crystal display device, VGA with high resolution, fast display rate, color rich, etc. Display output because of its large amount of information, the output forms characteristics has become the most commonly used output device design now.In the design of FPGA can use less resources, and produce VGA signals, flexible coupled with VHDL language description method and has nothing to do with the hardware characteristics, make use of VHDL language based on the FPGA chip to realize VGA display control become the direction of research.In this paper, based on VHDL VGA display control is studied, and VGA display color bar signal generator is designed. The main work done as follows:(1)In the design USES the top-down hierarchical, modular design thought, will the whole interface is divided into several modules, use of VHDL language description method for the design of each functional module, finally completed the VGA display system design.(2) Using ISE software simulation.Keywords: VHDL ;VGA; ISE; Color bar signal目录1 概述............................................................................................................ - 1 -1.1 本选题研究的目的及意义......................................................................................... - 1 -1.2 本选题国内外研究状况综述 (2)1.3 本选题研究的主要内容............................................................................................. - 1 -2 VGA显示的理论研究 (4)2.1 VGA显示特点 (4)2.2 VGA显示原理 (4)3 ISE工具概述 ................................................................................................ - 7 -3.1 硬件描述语言............................................................................................................. - 7 -3.2 ISE使用方法............................................................................................................. - 13 -4 VGA显示的设计与仿真............................................................................ - 17 -4.1 模块结构设计........................................................................................................... - 17 -4.2 VHDL代码设计............................................................................... 错误!未定义书签。

电子信息工程专业基于FPGA的SD卡图像的VGA显示毕业设计论文

本科毕业设计(论文) 论文题目:基于FPGA的SD卡图像的VGA显示摘要基于FPGA的SD卡图像的VGA显示,是利用可编程逻辑器件将图像的数据通过VGA 线实现图像的显示控制的,详细说明了在显示控制器中VGA的基本功能作用和其工作原理。

此次设计是在Xilinx公司的ise 14.7软件环境下,使用 Verilog语言来编写程序模块设计,实现SD卡图像的VGA显示控制设计。

要在最终的电脑显示屏上获得图像显示,需通过开发板上电,先读取SD卡中的图像数据并把它存储在DDR3中,然后再将DDR3的图像数据通过VGA线显示到的屏幕上。

传统的图像显示是将数据传送到计算机上,在显示屏上直接显示。

在此过程中,需要信号不断控制图片的数据,这将很大程度上造成CPU资源的浪费,而且系统也脱离不了计算机,造成显示控制的灵活性降低。

但是伴随可编程逻辑器件(FPGA)技术的发展,设计者采用EDA设计方法便可以实现针对性的VGA显示控制,可以脱离计算机来控制系统,并且能够满足实践生产的需要,大大降低了投入成本,产品的更新换代更加迅速方便,推动了行业的发展。

关键词:可编程逻辑器件;VGA ;显示控制AbstractSD card based on FPGA image of VGA display, is the use of programmable logic devices of the image data through the VGA line image display control, in VGA display controller is described in detail the basic functions and its working principle.In Xilinx ise 14.7 software environment, use Verilog language to write the SD card image of VGA display control design, completed the FPGA modular design.Achieve VGA display control, need to electricity, on the development board to read SD card of the image data and store it in DDR3, then continuously read DDR3 image data through the VGA line show on the screen.The traditional image display is to transfer the data to computer, displayed on the screen, in this process, the image data the CPU needs constant control signal, it will largely wastes the CPU resources, but also from the computer system, which reduces the display control flexibility.But along with the development of the programmable logic device (FPGA) technology, the designers use EDA design method can realize the VGA display of the targeted control, can from computer to control system, and can meet the needs of practical production, greatly reduces the cost, upgrading of products is more convenient quickly, promote the development of the industry.Keywords:Programmable logic devices ; VGA ;display control目录前言 (1)第1章 VGA概述 (2)1.1 VGA显示技术的发展概况 (2)1.2 VGA显示接口 (3)1.3 VGA显示原理 (4)1.4 VGA时序 (5)第2章 FPGA简介及设计流程 (8)2.1 FPGA简介 (8)2.2 FPGA设计流程 (8)2.3 Verilog简介 (111)2.4 Xilinx ise14.7简介 (122)第3章设计方案 (14)3.1 设计的主要内容 (144)3.2 设计原理 (155)第4章系统实现 (16)4.1 VGA显示控制模块 (16)4.2 MIG IP控制器 (19)4.2.1 MIG IP介绍 (19)4.2.2 MIG IP的生成 (21)4.3 Image2Lcd和winhex工具的使用 (256)4.4 SD卡顶层设计模块 (269)4.5 顶层设计 (34)4.6 程序下载和设计结果 (345)4.6.1 IMPACT软件进行程序的烧写 (345)4.6.2 设计结果 (347)第5章结束语 (39)参考文献 (41)致谢 (42)附录 (43)前言随着现代化科技的发展,信息化时代的到来,以计算机为核心的电子信息技术正在迅速的发展,各种各样的电子产品进入大众的视野,人们很大一部分的视觉信息都说是通过各种电子显示产品获得的,所以对电子显示设备的需求也越来越多,在众多因素的影响与要求下,对电子技术的要求也越来越高,某种程度上来讲,也促进了电子显示技术的飞速发展。

基于FPGA的VGA和HDMI视频拼接系统设计毕业设计论文

基于FPGA的VGA和HDMI视频拼接系统设计摘要随着图像显示技术的快速发展,图像用户界面和人机交互界面正朝着智能化、高速化、大屏幕化方向迈进。

目前图像显示系统多数是采用早期的专用处理芯片,其运算速度和设计灵活性一般都较低。

FPGA 的发展为图像存储与显示系统的高速和高集成度提供了新的方法和解决思路,FPGA 本身拥有着强大的逻辑资源,并利用片外的配置资源和模块化的设计思路,可实现图像存储与显示系统。

论文采用 Altera 公司推出的Cyclone IV FPGA,结合该系列芯片的结构特点,对其功能以及配置方式做了详细的说明,并简要的介绍了系统设计中所涉及的软硬件开发环境和显示原理,重点研究基于 FPGA 的图像信号剪切、存储和显示,系统采用基于FPGA的高速阵列的信号处理模式,提出了一种基于硬件的图像存储与显示的视频拼接显示方法。

该设计以 FPGA 为数字处理的核心,分为图像处理模块、图像存储模块和图像显示模块,通过处理输入的视频信号,把视频剪切成两部分,分别以VGA和HDMI在两个显示器里分别显示,实现了视频的拼接显示功能。

关键字:FPGA VGA HDMI 拼接显示VGA and HDMI video splicing FPGA-based displayABSTRACTAs the image shows the rapid development of technology, graphical user interface and interactive interface is moving intelligent, high-speed, large screen direction. At present, the majority of the image display system is the use of dedicated processing chip early, usually its speed of operation and design flexibility are low.FPGA development for high-speed and highly integrated image storage and display system provides a new approach and solution ideas, FPGA itself has a powerful logic resources and use off-chip resource allocation and modular design ideas can be realized Images storage and display system.Thesis, Altera has introduced Cyclone IV FPGA, combined with the structural characteristics of the chips and their functions as well as a detailed configuration instructions, and a brief description of the system involved in the design of hardware and software development environment and display principle focus Cut image signal based on FPGA, storage and display, the system uses the signal processing FPGA-based high-speed mode arrays, we propose a hardware-based image storage and display method for displaying video splicing.The digital processing designed to FPGA core, divided into an image processing module, an image storage module and an image display module, by processing the input video signal, the video cut into two parts, respectively in the two VGA monitors and HDMI Lane respectively display, to achieve a video mosaic display function.Key words: FPGA VGA HDMI Tiled Display目录1 绪论 ........................................................... 错误!未定义书签。

课程设计-基于fpga的vga图形显示大学论文

电子信息工程专业综合设计(报告)(课程设计)题目基于FPGA的VGA图形显示二级学院电气与电子工程学院专业电子信息工程班级学生姓名学号同组姓名指导教师时间基于FPGA的VGA图形显示摘要:本次的题目是基于FPGA的VGA图形显示,实现VGA图像显示与控制。

本文介绍的主要内容围绕着显示特定图片,且图片可受控制的相关原理与方法展开。

根据VGA显示原理,利用VHDL作为逻辑描述手段,设计了一种基于现场可编程器件FPGA的VGA接口控制器。

实现VGA图像显示控制器是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

FPGA的嵌入式系统中能代替VGA的专用显示芯片,节约硬件成本,节省计算机处理时间,加快数据处理速度并具有显示面积大,色彩丰富、承载信息量大、接口简单等优点。

除此以外FPGA芯片和EDA设计方法的使用,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,可不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要。

关键字:FPGA VGA 图像控制器一、前言本次课程设计主要是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

VGA是IBM于1987年提出的一个使用模拟信号的电脑显示标准。

在性能上,VGA将16色模式的分辨率提高到了640×480,同时VGA新提供了一种具有320×200分辨率、256种颜色的图形模式,且所显示的每一种颜色都可从262144(18位)种颜色中选择,VGA的这种色彩显示能力对微机图形/图象软件的发展起到了很大的促进作用先后分别经历了EGA, EGA, VGA, SVGA, XGA, SXGA, UXGA, QXGA, WQXGA, QSXGA, WQSXGA, QUXGA, WQUXGA, 1080P。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R,G,B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VGA显示器控制电路论文前言VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。

利用FPGA 芯片和EDA设计方法,可以因地制宜,根据用户的特定需要,设计出针对性强的VGA显示控制器,不仅能够大大的降低成本,还可以满足生产实践中不断变化的用户需要,产品升级换代方便迅速。

在本设计中采用Altera公司的EDA软件工具Quartus II,并以Cyclone II系列的FPGA的器件作为主实现硬件平台的设计。

一、FPGA的原理FPGA 是Filed Progranmmable Gate Array的缩写,即现场可编程逻辑阵列。

FPGA是在CPLD的基础上发展起来的新型高性能可编程逻辑器件它一般采用SRAM工艺,也有一些专用器件采用Flash工艺或反熔丝(Anti_Fuse)工艺等。

FPGA的集成度很高,其器件密度从数万系统门到数千万系统门不等,可以完成极其复杂的时序与组合逻辑电路功能,适用于高速、高密度的高端数字逻辑电路设计领域。

FPGA的基本组成部分有可编程输入/输出单元,基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元、内嵌专用硬核等。

FPGA 的主要器件供应商有Xilinx、 Altera、 Lattice、 Actel和 Atmel 等。

二、 VGA转换接口的简单描述本设计另外自制VGA接口电路。

VGA时序控制模块是整个显示控制器的关键部分,最终的输出信号行、场同步信号必须严格按照VGA时序标准产生相应的脉冲信号。

对于普通的VGA 显示器,其引出线的共含5个信号:G,R,B(三基色信号),HS(行同步信号),VS(场同步信号)。

在五个信号时序驱动时,VGA显示器要严格遵循“VGA工业标准”,即640Hz×480 H z×60Hz模式。

下图(1)为VGA显示控制器控制CRT显示器VGA(Video Graphic Array)接口,即视频图形阵列,也叫做D-Sub接口,是15针的梯形插头,分3排,每排5个,传输模拟信号。

VGA接口采用非对称分布的15针连接方式,其工作原理:是将显存内以数字格式存储的图像(帧)信号在RAMEAC里经过模拟调制成模拟高频信号,然后再输出到显示设备成像。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

对于模拟显示设备,如模拟CRT显示器,信号被直接送到相应的处理电路,驱动控制显像生成图像。

而对于LCD、DLP扥数字显示设备,显示设备中需配置相应的A/D (模拟/数字)转换器,将模拟信号转变为数字信号。

在经过D/A和A/D2次转换后,不可避免地造成了一些图像细节的损失。

VGA接口应用于CRT显示器无可厚非,但用于连接液晶之类的显示设备,则转换过程的图像损失会使显示效果略微下降。

VGA接口的引脚分配如下图(1)所示图(1)三、主要功能模块设计注:主要模块为三块,一个二分频模块,一个VGA时序和行点位置模块,一个图形生成模块,本来想利用老师提供的方案进行制作,但在按键去抖模块以及按键累计模块没有能完成,故更改方案,换用读取拨动开关的模式来选择模式显示。

1.1 VGA时序控制模块(vgaxm.v)功能:根据VGA显示器的工作原理,提供同步信号(H_SYNC和V_SYNC)及像素位置信息。

设计思路:根据VGA显示器的工作原理,以垂直同步信号的出现时刻作为时间的起点(原点),根据时序图算出每一个关键时间点所需的计数器最大值,据此输出H_SYNC和V_SYNC,在此基础上对扫描的行数及像素点数进行计数,从而输出像素位置信息。

1.1.1VGA的时序详细讲解对于VGA显示器,每个像素点的输出频率为25.175MHZ,本实验采用50MHz的时钟信号,经过模块divider(二分频模块)的分频得到25MHz的时钟输入信号。

依据VGA时序标准,行同步信号HS,行周期为32.2us,也就是H_sync(行)的周期;场同步信号VS,场周期为16.89ms,也就是V_sync(一帧)的周期。

刷新1个像素所需时间Tpixel = 1/ fclk =40ns;从(b)水平刷新循环中,可以知道刷新一行所需时间公式:Trow = B+C+D+E=Tpixel ⨯ 640 + guard bands = 25.6μs + B + C +E = 32.2μs;引入h_count[9..0]:用于Trow(25MHz)的定时计数,计数清零时由时序可得下面计算式子:h_countend:同时可以从该时序图确定p_begin_time和p_end_time的像素点pixel开始计数以及清零计数的时间,计算式子如下:p_begin_time :p_end_time :还能得出行扫描h_sync在h_count从0~805计数期间,从第几计数开始为电平变化。

图中,B=3.77us就是说在h_count计数起到3.77us到来之间行信号h_sync 保持低电平,在3.77us到32.2us之间为高电平,刚好为一个行信号周期。

以下是计算式子(hsync_end代表h_sync的低电平截止时间范围):hsync_end:程序简单描述如下:h_count计数:always @( posedge clk) //25MHZ// 在垂直刷新循环内,当h_count计到规定的最大值805时,则清零;否则加1计数h_sync的电平变化:assign h_sync_pulse_w = (h_count < hsync_end); //从h_count计数到94(3.77us)为1,95~805为0 在v_sync负脉冲宽度内,v_sync_pulse_w为高电平assign h_sync=~h_sync_pulse_w;(a)垂直刷新循环从(a)垂直刷新循环,可以知道刷新完480行,并完成一帧所需时间Tscreen =P+Q+R+S= Trow ⨯ 480 + guard bands = 15.456ms+ P + Q + S = 16. 89ms引入v_count[18..0] :用于Tscreen的定时计数,每当h_count计数满805,v_count计数加1一次;计数清零时由时序可得下面计算式子(v_countend为v_count计数清零值):v_countend:同时可以从该时序图确定h_begin_time和h_end_time的行计数line开始计数以及清零计数的时间,计算式子如下:h_begin_time :h_end_time :还能得出场扫描v_sync在v_count从0~525计数期间,从第几计数开始为电平变化。

图中,P=64us就是说在v_count计数起到64us到来之间场信号v_sync 保持低电平,在64us到16. 89ms之间为高电平,刚好为一个场信号周期(一帧)。

以下是计算式子(vsync_end代表v_sync的低电平截止时间范围):vsync_end:程序简单描述如下:v_count计数:always @ (posedge clk )// 当垂直刷新循环结束(满480)时v_count清零;否则当h_count计到规定的最大值(805)时加1计数;v_sync的电平变化:assign v_sync_pulse_w = (v_count < vsync_end); //从v_count从0计数到2(64us)为1 3~525为0 在h_sync负脉冲宽度内,h_sync_pulse_w为高电平assign v_sync=~v_sync_pulse_w;1.1.2提供行列以及格线计数值行或列计数:line 和pixel;格线计数器:line_cnt,pixel_cnt,strip_cnt(1)line[8..0]:用于对行数(1~480行)计数,其clk等于水平同步信号h_sync 的下降沿;(2)pixel [9..0] :用于对每行的像素点数(1~640个点)计数,其clk等于输入时钟fclk25M。

/* 3. line[8..0]对像素所处行计数*/always @ (negedge h_sync )//h_sync的下降沿触发line计数。

//当h_begin_time ≦v_count≦h_end_time,且当line≦480时,则line加1计数;//否则line清零。

/* 4. pixel[9..0]对像素所处列计数*/always @ (posedge clk )/*当1≦line≦480(必须有此条件,否则pixel在h_sync来后B+C时间之后即开始加1计数,而此时line=0),且p_begin_time≦h_count≦p_end_time,且pixel ≦640时,则pixel加1计数;*///否则pixel清零。

(3)output[4:0] line_cnt; //用于棋盘格1的水平格线计数32进制,32.2uss计数一次(4)output[5:0] pixel_cnt; //用于棋盘格1的垂直格线计数64进制40ns计数一次(5)output[5:0] strip_cnt; //用于横彩条2的水平格线计数64个6432.2uss计数一次2.1生成图形子模块注:RGB[2..0]:颜色信号,R——红色信号;G——绿色信号;B——蓝色信号。

其对应颜色关系如下表所示。

功能:根据时序控制子模块输出的像素位置信息,在不同的显示模式下,输出不同的颜色信号。

设计思路:采用case语句,来确定不同的显示模式;在每种显示模式下,采用if-else 语句,根据像素所处的位置(即line和pixel的范围),来确定输出不同的颜色信号。

对棋盘格1、横彩条2的格线的判断不用枚举的方法,而是根据vgacore2.v 输出的格线计数器line_cnt、pixel_cnt和strip_cnt的大小,用if-else语句简单地实现。

本模块主要的图形生成程序简述如下:/* 2. 根据cnt值产生不同的显示图形*/always @ (posedge clk )beginif( line>9'd0 & line<=9'd480 & pixel>9'd0 & pixel<=10'd640) //若在有begin 效区域内case(cnt)0:begin/*(1)模式1:4大图形块*/1:begin/*(2)模式2:竖彩条*/2:begin/*(3)模式3:横彩条*/3:begin/*(4)模式4:棋盘格1 16*16 */4:begin/*(5)模式5:小横彩条*/5:begin/*(6)模式6:棋盘格2 30*40 */endcaseendelse rgb=3‘b000;//超出有效区域,则为黑色end2.1.1VGA竖彩条发生和横彩条发生竖彩条发横模块根据像素点计数器的h_count的计数值来产生彩条,其流程图如(a)所示。