AD5280BRU20中文资料

BUX20中文资料

Max. Unit

V V 3 3 12 1 mA mA mA V V — A MHz

0.3 0.55 1.35 20 10 0.15 17.5 8 0.4 0.85 0.1

0.6 1.2 2 60

1.5 1.2 0.3 µs

* Pulsed: pulse duration = 300ms, duty cycle ≤ 2% THERMAL CHARACTERISTICS

Document Number 3246 Issue 1

BUX20

ELECTRICAL CHARACTERISTICS (Tcase = 25°C unless otherwise stated)

Parameter

VCEO(sus)* VEBO ICEO ICEX IEBO VCE(sat)* VBE(sat)* hFE* IS/b fT ton ts tf Collector - Emitter Sustaining Voltage Emitter – BaseVoltage Collector Cut-off Current Collector Cut-off Current Emitter Cut-off Current Collector – Emitter Saturation Voltage Base – Emitter Saturation Voltage DC Current Gain Second Breakdown Collector Current Transition Frequency Turn–On Time Storage Time Fall Time

TO–3 PACKAGE (TO-204AA)

PIN 1 — Base PIN 2 — Emitter Case is Collector.

AD5282BRU50中文资料

PRELIMINARY TECHNICAL DATAa+15V, I 2C Compatible Digital PotentiometersPreliminary Technical Data AD5280/AD5282REV PrE 12 MAR 02Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U .S .A . FEATURES 256 PositionAD5280 – 1-ChannelAD5282 – 2-Channel (Independently Programmable) Potentiometer Replacement20K, 50K, 200K Ohm with TC < 50ppm/ºC Internal Power ON Mid-Scale Preset+5 to +15V Single-Supply; ±5.5V Dual-Supply Operation I 2C Compatible InterfaceAPPLICATIONSMulti-Media, Video & Audio CommunicationsMechanical Potentiometer Replacement Instrumentation: Gain, Offset Adjustment Programmable Voltage to Current Conversion Line Impedance MatchingGENERAL DESCRIPTIONThe AD5280/AD5282 provides a single/dual channel, 256 position digitally-controlled variable resistor (VR) device. These devices perform the same electronic adjustment function as apotentiometer, trimmer or variable resistor. Each VR offers a completely programmable value of resistance, between the Aterminal and the wiper, or the B terminal and the wiper. The fixed A-to-B terminal resistance of 20, 50 or 200K ohms has a 1%channel-to-channel matching tolerance with a nominal temperature coefficient of 30 ppm/°C.Wiper Position programming defaults to midscale at system power ON. Once powered the VR wiper position is programmed by a I 2C compatible 2-wire serial data interface. Both parts have twoprogrammable logic outputs available to drive digital loads, gates, LED drivers, analog switches, etc.FUNCTIONAL BLOCK DIAGRAMSA WB O OA W BA WB AD0AD1OThe AD5280/AD5282 are available in ultra compact surface mount thin TSSOP-14/-16 packages. All parts are guaranteed to operate over the extended industrial temperature range of -40°C to +85°C. For 3-wire, SPI compatible interface applications, seeAD5203/AD5204/AD5206/AD7376/AD8400/AD8402/AD8403/ AD5260/AD5262/AD5200/AD5201 products.The AD5280/AD5282 die size is 75 mil X 120 mil, 9,000 sq. mil. Contains xxx transistors. Patent Number xxx applies.元器件交易网PRELIMINARY TECHNICAL DATAAD5280/AD52822 REV PrE 12 MAR 02ELECTRICAL CHARACTERISTICS 20K, 50K, 200K OHM VERSION (V DD = +5V, V SS = -5V, V LOGIC = +5V, V A = +V DD , V B = 0V, -40°C < T A < +85°C unless otherwise noted.) Parameter Symbol Conditions Min Typ 1MaxUnits元器件交易网PRELIMINARY TECHNICAL DATAAD5280/AD5282REV PrE 12 MAR 02 3ELECTRICAL CHARACTERISTICS 20K, 50K, 200K OHM VERSION (V DD = +5V, V SS = -5V, V LOGIC = +5V, V A = +V DD , V B = 0V, -40°C < T A < +85°C unless otherwise noted.) Parameter Symbol Conditions Min Typ 1MaxUnitsNOTES:1. Typicals represent average readings at +25°C, V DD = +5V, V SS = -5V.2.Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. 3. V AB = V DD , Wiper (V W ) = No connect 4. INL and DNL are measured at V W with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. V A = V DD and V B = 0V. DNL specification limits of ±1LSB maximum are Guaranteed Monotonic operating conditions. 5. Resistor terminals A,B,W have no limitations on polarity with respect to each other. 6. Guaranteed by design and not subject to production test. 9. Bandwidth, noise and settling time are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest bandwidth. The highest R valueresult in the minimum overall power consumption.10. P DISS is calculated from (I DD x V DD ). CMOS logic level inputs result in minimum power dissipation. 11. All dynamic characteristics use V DD = +5V.12. See timing diagram for location of measured values.元器件交易网PRELIMINARY TECHNICAL DATAAD5280/AD52824 REV PrE 12 MAR 02ABSOLUTE MAXIMUM RATINGS (T A = +25°C, unless otherwise noted)V DD to GND.............................................................-0.3, +15V V SS to GND..................................................................0V, -7V V DD to V SS ...................................................................... +15V V A , V B , V W to GND...................................................V SS , V DD A X – B X , A X – W X , B X – W X .........................................±20mA Digital Input Voltage to GND.........................................0V, 7V Operating Temperature Range...........................-40°C to +85°C Thermal Resistance * θJA,TSSOP-14........................................................206°C/W TSSOP-16........................................................180°C/W Maximum Junction Temperature (T J MAX )....................+150°C Storage Temperature........................................-65°C to +150°C Lead TemperatureRU-14, RU-16 (Vapor Phase, 60 sec) .......................+215°C RU-14, RU-16 (Infrared, 15 sec) ..............................+220°C*Package Power Dissipation (T J MAX - T A ) / θJAAD5280 PIN CONFIGURATIONA WB V DD SHDN SHDN SCL SDA O1 V L O2 V SS GND AD1 AD014 13 12 11 10 981 2 3 4 5 6 7AD5282 PIN CONFIGURATIONO1 A1 W1 B1 V DD SHDN SHDN SCL SDAA2 W2 B2 V L V SSGND AD1 AD016 15 14 13 12 11 10 91 2 3 4 5 6 7 8TABLE 1: AD5280 PIN Function Descriptions Pin Name Description1 A Resistor terminal A2 W Wiper terminal W3 B Resistor terminal B4 V DDPositive power supply, specified foroperation from +5 to +15V.5 SHDN Active Low, Asynchronous connection ofthe wiper W to terminal B, and open circuit of terminal A. RDAC register contents unchanged.6 SCL Serial Clock Input7 SDA Serial Data Input/Output8 AD0 Programmable address bit for multiplepackage decoding. Bits AD0 & AD1 provide 4 possible addresses.9 AD1 Programmable address bit for multiplepackage decoding. Bits AD0 & AD1 provide 4 possible addresses.10 GND Common Ground 11 V SS Negative power supply, specified for operation from 0 to -5V 12 O2 Logic Output terminal O213 V LLogic Supply Voltage, needs to be same voltage as the digital logic controlling the AD5280.14 O1Logic Output terminal O1元器件交易网PRELIMINARY TECHNICAL DATAAD5280/AD5282REV PrE 12 MAR 02 5TABLE 2: AD5282 PIN Function Descriptions Pin Name Description1 O1 Logic Output terminal O12 A 1 Resistor terminal A 13 W 1 Wiper terminal W 14 B 1 Resistor terminal B 15 V DD Positive power supply, specified for operation from +5 to +15V.6SHDNActive Low, Asynchronous connection of the wiper W to terminal B, and open circuit of terminal A. RDAC register contents unchanged. 7SCL Serial Clock Input8 SDASerial Data Input/Output9AD0Programmable address bit for multiple package decoding. Bits AD0 & AD1 provide 4 possible addresses.10 AD1 Programmable address bit for multiplepackage decoding. Bits AD0 & AD1 provide 4 possible addresses.11 GND Common Ground 12 V SS Negative power supply, specified for operation from 0 to -5V13 V LLogic Supply Voltage, needs to be same voltage as the digital logic controlling the AD5282.14 B 2 Resistor terminal B 2 15 W 2 Wiper terminal W 2 16 A 2 Resistor terminal A 2SDASCLData of AD5280/AD5282 is accepted from the I 2C bus in the following serial format:S 0 1 0 1 1 AD 1A D 0R/WAA /BR SS DO 1O 2X X X A D7D 6D 5D 4D 3D 2D 1D 0A PSlave Address Byte Instruction Byte Data ByteWhere:S = Start Condition P = Stop Condition A = Acknowledge X = Don’t CareAD1, AD0 = Package pin programmable address bits R/W = Read Enable at High and Write Enable at LowA /B = RDAC sub address select. “Zero” for RDAC1 and “One” for RDAC2 SD = Shutdown, same as SHDN pin operation except inverse logic O2, O1 = Output logic pin latched values D7,D6,D5,D4,D3,D2,D1,D0 = Data BitsSCL SDA1910110AD0AD1R/WACK.BY AD5280D7D6D5D3D4D0D1D219ACK.BY AD5280A/B RS SD O2O1X X X 19ACK.BY AD5280FRAME 1Slave Address Byte START BY MASTERFRAME 2Instruction Byte FRAME 3Data ByteFigure 2. Writing to the RDAC Register元器件交易网PRELIMINARY TECHNICAL DATAAD5280/AD52826 REV PrE 12 MAR 02SCL SDA19111AD0AD1R/WACK.BY AD528019D7D6D5D3D4D0D1D2NO ACK.BY MASTERFRAME 1Slave Address ByteSTART BY MASTERFRAME 2Data From Selected RDAC Regis terSTOP BY MASTERFigure 3. Reading Data from a Previously Selected RDAC RegisterOPERATIONThe AD5280/AD5282 provides a single/dual channel, 256-position digitally-controlled variable resistor (VR) device. The terms VR and RDAC are used interchangeably throughout this documentation. To program the VR settings, refer to the Digital Interface section. Both parts have an internal power ON preset that places the wiper in mid scale during power on, whichsimplifies the fault condition recovery at power up. In addition, the shutdown SHDN pin of AD5280/AD5282 places the RDAC in a zero power consumption state where terminal A is open circuited and the wiper W is connected to terminal B, resulting in only leakage currents being consumed in the VR structure. In shutdown mode the VR latch settings are maintained, so that, returning to operational mode from power shutdown, the VR settings return to their previous resistance values.PROGRAMMING THE VARIABLE RESISTOR Rheostat OperationThe nominal resistance of the RDAC between terminals A and B are available in 20K Ω, 50K Ω, and 200K Ω. The final three digits of the part number determine the nominal resistance value, e.g. 20K Ω = 20; 50K Ω = 50; 200K Ω = 200. The nominal resistance (R AB ) of the VR has 256 contact pointsaccessed by the wiper terminal, plus the B terminal contact. The eight bit data in the RDAC latch is decoded to select one of the 256 possible settings. Assume a 20K Ω part is used, the wiper's first connection starts at the B terminal for data 00H . Since there is a 60Ω wiper contact resistance, such connection yields a minimum of 60Ω resistance between terminals W and B. The second connection is the first tap point corresponds to 138Ω (R WB = R AB /256 + R W = 78Ω+60Ω) for data 01H . The third connection is the next tap point representing 216Ω (78x2+60)for data 02H and so on. Each LSB data value increase moves the wiper up the resistor ladder until the last tap point is reached at 19982Ω [R AB –1LSB+R W ]. The wiper does not directly connect to the B terminal. See Figure 4 for a simplified diagram of the equivalent RDAC circuit.The general equation determining the digitally programmed output resistance between W and B is: 1 eqn. 256)(W AB WB R R DD R +⋅=where D is the decimal equivalent of the binary code which is loaded in the 8-bit RDAC register, and R AB is the nominal end-to-end resistance.For example, R AB =20K Ω, when V B = 0V and A–terminal is open circuit, the following output resistance values R WB will be set for the following RDAC latch codes. Result will be the same if terminal A is tied to W:Note that in the zero-scale condition a finite wiper resistance of 60Ω is present. Care should be taken to limit the current flow between W and B in this state to a maximum current of no more than 5mA. Otherwise, degradation or possible destruction of the internal switch contact can occur.Similar to the mechanical potentiometer, the resistance of the RDAC between the wiper W and terminal A also produces a digitally controlled resistance R WA . When these terminals are used the B–terminal should be let open or tied to the wiper terminal. Setting the resistance value for R WA starts at amaximum value of resistance and decreases as the data loaded in the latch is increased in value. The general equation for this operation is: 2 eqn. 256256)(W AB WA R R DD R +⋅−=元器件交易网PRELIMINARY TECHNICAL DATAAD5280/AD5282REV PrE 12 MAR 02 7For example, R AB =20K Ω, when V A = 0V and B–terminal is open circuit, the following output resistance R WA will be set for the following RDAC latch codes. Result will be the same if terminal B is tied to W:The typical distribution of the nominal resistance R AB from channel-to-channel matches within ±1%. Device to devicematching is process lot dependent and is possible to have ±30% variation. Since the resistance element is processed in thin film technology, the change in R AB with temperature has a 30 ppm/°C temperature coefficient.PROGRAMMING THE POTENTIOMETER DIVIDER Voltage Output OperationThe digital potentiometer easily generates output voltages at wiper-to-B and wiper-to-A to be proportional to the inputvoltage at A-to-B. Let’s ignore the effect of the wiper resistance at the moment. For example connecting A–terminal to +5V and B–terminal to ground produces an output voltage at the wiper-to-B starting at zero volts up to 1 LSB less than +5V. Each LSB of voltage is equal to the voltage applied across terminal AB divided by the 256 position of the potentiometer divider. Since AD5280/AD5282 can be supplied by dual supplies, the general equation defining the output voltage at V W with respect toground for any given input voltage applied to terminals AB is: 3 eqn. 256256256)(B A W V D V D D V −+=where D is decimal equivalent of the binary code which is loaded in the 8-bit RDAC register.Operation of the digital potentiometer in the divider mode results in a more accurate operation over temperature. Unlike the rheostat mode, the output voltage is dependent on the ratio of the internal resistors R WA and R WB and not the absolute values, therefore, the temperature drift reduces to 5ppm/°C.DIGITAL INTERFACE 2-WIRE SERIAL BUSThe AD5280/AD5282 are controlled via an I 2C compatible serial bus. The RDACs are connected to this bus as slave devices.Referring from Figures 2 and 3, the first byte ofAD5280/AD5282 is a Slave Address Byte. It has a 7-bit slave address and a R/W bit. The 5 MSBs are 01011 and the following2 bits are determined by the state of the AD0 and AD1 pins ofthe device. AD0 and AD1 allow the user to use up to four of these devices on one bus.The 2-wire I 2C serial bus protocol operates as follows:1. The master initiates data transfer by establishing a STARTcondition, which is when a high-to-low transition on the SDA line occurs while SCL is high, Figure 2. Thefollowing byte is the Slave Address Byte which consists of the 7-bit slave address followed by an R/W bit (this bit determines whether data will be read from or written to the slave device).The slave whose address corresponds to the transmitted address responds by pulling the SDA line low during the ninth clock pulse (this is termed the Acknowledge bit). At this stage, all other devices on the bus remain idle while the selected device waits for data to be written to or read from its serial register. If the R/W bit is high, the master will read from the slave device. On the other hand, if the R/W bit is low, the master will write to the slave device.2. A Write operation contains an extra Instruction Byte morethan the Read operation. Such Instruction Byte in Write mode follows the Slave Address Byte. The MSB of the Instruction Byte labeled A /B is the RDAC sub-addressselect. A “low” select RDAC1 and a “high” selects RDAC2 for dual channel AD5282. The 2nd MSB RS is the Mid-scale reset. A logic high of this bit moves the wiper of a selected RDAC to the center tap where R WA =R WB . The 3rd MSB SD is a shutdown bit. A logic high causes the RDAC open circuit at terminal A while shorting wiper to terminal B. This operation yields almost a zero Ohm in rheostat mode or zero volt in potentiometer mode. This SD bitserves the same function as the SHDN pin except it reacts in active low. The following two bits are O2 and O1. They are extra programmable logic output that users can make use of them by driving other digital loads, logic gates, LED drivers, and analog switches, etc. The 3 LSBs are DON’T CARE. See Figure 2. 3. After acknowledged the Instruction Byte, the last byte inWrite mode is the Data Byte. Data is transmitted over the serial bus in sequences of nine clock pulses (eight data bits followed by an “Acknowledge” bit). The transitions on the SDA line must occur during the low period of SCL and remain stable during the high period of SCL, Figure 1. 4. In Read mode, the Data Byte goes right after theacknowledgment of the Slave Address Byte. Data istransmitted over the serial bus in sequences of nine clock pulses (slight difference with the Write mode, there are eight data bits followed by a “No Acknowledge” bit). Similarly, the transitions on the SDA line must occurduring the low period of SCL and remain stable during the high period of SCL. 5. When all data bits have been read or written, a STOPcondition is established by the master. A STOP condition is defined as a low-to-high transition on the SDA line while SCL is high. In Write mode, the master will pull the SDA line high during the 10th clock pulse to establish a STOP元器件交易网PRELIMINARY TECHNICAL DATAAD5280/AD52828 REV PrE 12 MAR 02condition, Figure 2. In Read mode, the master will issue a No Acknowledge for the 9th clock pulse (i.e., the SDA line remains high). The master will then bring the SDA line low before the 10th clock pulse which goes high to establish a STOP condition, Figure 3.A repeated Write function gives the user flexibility to update the RDAC output a number of times after addressing and instructing the part only once. During the Write cycle, each Data byte will update the RDAC output. For example, after the RDAC has acknowledged its Slave Address and Instruction Bytes, the RDAC output will update after these two bytes. If another byte is written to the RDAC while it is still addressed to a specific slave device with the same instruction, this byte will update the output of the selected slave device. If different instructions are needed, the Write mode has to start with a new Slave Address, Instruction, and Data Bytes again. Similarly, a repeated Read function of the RDAC is also allowed. MULTIPLE DEVICES ON ONE BUSFigure 5 shows four AD5282 devices on the same serial bus. Each has a different slave address sine the state of their AD0 and AD1 pins are different. This allows each RDAC within each device to be written to or read from independently. The master device output bus line drivers are open-drain pull downs in a fully I 2C compatible interface.SDASCLFigure 5. Multiple AD5282 Devices on One BusLEVEL SHIFT FOR BI-DIRECTIONAL INTERFACE While most old systems may be operated at one voltage, a new component may be optimized at another. When two systems operate the same signal at two different voltages, proper method of level shifting is needed. For instance, one can use a 3.3V E 2PROM to interface with a 5V digital potentiometer. A level shift scheme is needed in order to enable a bi-directional communication so that the setting of the digital potentiometer can be stored to and retrieved from the E 2PROM. Figure 6shows one of the techniques. M1 and M2 can be N-Ch FETs 2N7002 or low threshold FDV301N if V DD falls below 2.5V.SDA1SCL1SDA2SCL2V =5VFigure 6. Level Shift for different potential operation.All digital inputs are protected with a series input resistor and parallel Zener ESD structures shown in figure 7. Applies to元器件交易网PRELIMINARY TECHNICAL DATAAD5280/AD5282REV PrE 12 MAR 02 9TEST CIRCUITSFigures 9 to 17 define the test conditions used in product specification table.Figure 9. Potentiometer Divider Nonlinearity error test circuit(INL, DNL)Figure 10. Resistor Position Nonlinearity Error (Rheostat Operation; R-INL, R-DNL)Figure 11. Wiper Resistance test CircuitFigure 12. Power supply sensitivity test circuit (PSS, PSSR)Figure 13. Inverting Gain test CircuitFigure 14. Non-Inverting Gain test circuitFigure 15. Gain Vs Frequency test circuitFigure 16. Incremental ON Resistance Test CircuitFigure 17. Common Mode Leakage current test circuit元器件交易网PRELIMINARY TECHNICAL DATAAD5280/AD528210 REV PrE 12 MAR 02OUTLINE DIMENSIONSDimensions shown in inches and (mm)元器件交易网。

UR20-中文说明书

本使用手册由 Maselli 公司出版,但是不提供任何类型的保证。手册中所包含的资料,仅仅 是作为一种介绍。 由于存在着印刷错误,内容不准确,软件的改进,和/或设备、技术或商业条件的差异, Maselli Misure 公司保留在任何时候对本手册做出变更的权利,事先不提供通知。 保留一切权利。 按照法律条款,未得到我方许可,严禁全部或部分地将本手册复制或传递给第三方。

本手册说明了仪器的主要特点。同时包含有关安全使用、编程及维护工作的重要说明。因 此本手册必须妥善保管。 本手册还是设备的一个完整组成部分。 必须认真阅读本手册以后, 方可以着手开展设备的安装、启动和使用。 对于因为不遵守设备的使用说明、违背有关使用地点的规定以及违背本手册中各项说明而 造成的任何损坏,MASELLI Misure 公司宣布概不承担任何责任。

地址:7746 Lorraine Avenue, Suite 201 Stockton, California 95210 USA(美国) 电话: (209) 474-9178 免费电话(仅适用美国): (800) 964-9600 传真:(209) 474-9241 电子邮件:info@

“Oenology” 销售部 地址: 20124 MILANO-ITALY (意大利米兰) Via Cornalia, 19 电话:+39-02.6702432 02-6702493 传真: +39-02-66981993 E-MAIL: enoit@ E-MAIL: enoexport@

Maselli Misure S.p.A.公司于 2002 年 如果需要了解更多资料,请联系 Maselli 公司服务网络。

数字折光仪 UR-20 型

安装、使用及维修手册

手册编号 n° 01206C0011 适用于仪器编号 n° ____________________

BU2090中文资料

Parameter

Symbol Min. Typ. Max. Unit

Input high level voltage

3.5

—

—

VIH

V

2.5

—

—

Input low level voltage

—

—

1.5

0.4

Output low level voltage

—

—

2.0

VOL

V

—

—

1.0

"H" output disable current

– 25 ~ + 75

°C

Storage temperature

Tstg

– 55 ~ + 125

°C

Input voltage

VIN

VSS – 0.3 ~ VDD + 0.3

V

Output voltage

VO

VSS ~ 25.0

V

∗1 Unmounted ∗2 When mounted on a glass epoxy board of 50mm × 50mm × 1.6mm ∗3 When mounted on a glass epoxy board of 90mm × 50mm × 1.6mm ∗4 When mounted on a glass epoxy board of 70mm × 70mm × 1.6mm

元器件交易网

Standard ICs

BU2090 / BU2090F / BU2090FS / BU2092 / BU2092F / BU2092FV

12-bit, serial IN, parallel OUT driver

ADC08D1520资料

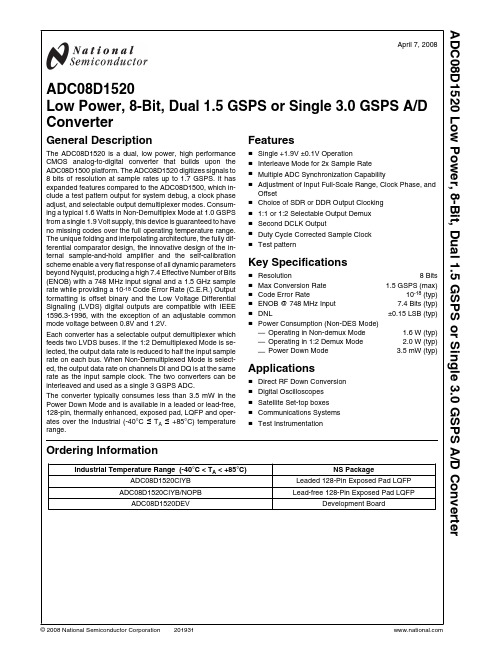

April 7, 2008 ADC08D1520Low Power, 8-Bit, Dual 1.5 GSPS or Single 3.0 GSPS A/D ConverterGeneral DescriptionThe ADC08D1520 is a dual, low power, high performance CMOS analog-to-digital converter that builds upon the ADC08D1500 platform. The ADC08D1520 digitizes signals to 8 bits of resolution at sample rates up to 1.7 GSPS. It has expanded features compared to the ADC08D1500, which in-clude a test pattern output for system debug, a clock phase adjust, and selectable output demultiplexer modes. Consum-ing a typical 1.6 Watts in Non-Demultiplex Mode at 1.0 GSPS from a single 1.9 Volt supply, this device is guaranteed to have no missing codes over the full operating temperature range. The unique folding and interpolating architecture, the fully dif-ferential comparator design, the innovative design of the in-ternal sample-and-hold amplifier and the self-calibration scheme enable a very flat response of all dynamic parameters beyond Nyquist, producing a high 7.4 Effective Number of Bits (ENOB) with a 748 MHz input signal and a 1.5 GHz sample rate while providing a 10-18 Code Error Rate (C.E.R.) Output formatting is offset binary and the Low Voltage Differential Signaling (LVDS) digital outputs are compatible with IE E E 1596.3-1996, with the exception of an adjustable common mode voltage between 0.8V and 1.2V.Each converter has a selectable output demultiplexer which feeds two LVDS buses. If the 1:2 Demultiplexed Mode is se-lected, the output data rate is reduced to half the input sample rate on each bus. When Non-Demultiplexed Mode is select-ed, the output data rate on channels DI and DQ is at the same rate as the input sample clock. The two converters can be interleaved and used as a single 3 GSPS ADC.The converter typically consumes less than 3.5 mW in the Power Down Mode and is available in a leaded or lead-free, 128-pin, thermally enhanced, exposed pad, LQFP and oper-ates over the Industrial (-40°C ≤ T A≤ +85°C) temperature range.Features■Single +1.9V ±0.1V Operation■Interleave Mode for 2x Sample Rate■Multiple ADC Synchronization Capability■Adjustment of Input Full-Scale Range, Clock Phase, and Offset■Choice of SDR or DDR Output Clocking■1:1 or 1:2 Selectable Output Demux■Second DCLK Output■Duty Cycle Corrected Sample Clock■Test patternKey Specifications■Resolution8 Bits ■Max Conversion Rate 1.5 GSPS (max)■Code Error Rate10-18 (typ)■ENOB @ 748 MHz Input7.4 Bits (typ)■DNL±0.15 LSB (typ)■Power Consumption (Non-DES Mode)—Operating in Non-demux Mode 1.6 W (typ)—Operating in 1:2 Demux Mode 2.0 W (typ)—Power Down Mode 3.5 mW (typ) Applications■Direct RF Down Conversion■Digital Oscilloscopes■Satellite Set-top boxes■Communications Systems■Test InstrumentationOrdering InformationIndustrial Temperature Range (-40°C < TA< +85°C)NS PackageADC08D1520CIYB Leaded 128-Pin Exposed Pad LQFPADC08D1520CIYB/NOPB Lead-free 128-Pin Exposed Pad LQFPADC08D1520DEV Development Board© 2008 National Semiconductor ADC08D1520 Low Power, 8-Bit, Dual 1.5 GSPS or Single 3.0 GSPS A/D ConverterBlock Diagram20193153 2A D C 08D 1520Pin Configuration20193101 Note: The exposed pad on the bottom of the package must be soldered to a ground plane to ensure rated performance. ADC08D1520Pin Descriptions and Equivalent CircuitsPin Functions Pin No.SymbolEquivalent CircuitDescription3OutV / SCLKOutput Voltage Amplitude and Serial Interface Clock. Tie this pin logic high for normal differential DCLK and dataamplitude. Ground this pin for a reduced differential output amplitude and reduced power consumption. See 1.1.6 The LVDS Outputs . When the Extended Control Mode isenabled, this pin functions as the SCLK input which clocks in the serial data. See 1.2 NON-EXTENDED ANDEXTENDED CONTROL MODE for details on the Extended Control Mode. See 1.3 THE SERIAL INTERFACE for description of the serial interface.29PDQPower Down Q-channel. A logic high on the PDQ pin puts only the Q-channel into the Power Down Mode.4OutEdge / DDR /SDATADCLK Edge Select, Double Data Rate Enable and Serial Data Input. This input sets the output edge of DCLK+ at which the output data transitions. See 1.1.5.2 OutEdge and Demultiplex Control Setting . When this pin is floating or connected to 1/2 the supply voltage, DDR clocking isenabled. When the Extended Control Mode is enabled, this pin functions as the SDATA input. See 1.2 NON-EXTENDED AND EXTENDED CONTROL MODE for details on the Extended Control Mode. See 1.3 THE SERIAL INTERFACE for description of the serial interface.15DCLK_RST /DCLK_RST+DCLK Reset. When single-ended DCLK_RST is selected by floating or setting pin 52 logic high, a positive pulse on this pin is used to reset and synchronize the DCLK outputs of multiple converters. See 1.5 MULTIPLE ADCSYNCHRONIZATION for detailed description. Whendifferential DCLK_RST is selected by setting pin 52 logic low,this pin receives the positive polarity of a differential pulse signal used to reset and synchronize the DCLK outputs of multiple converters.26PDPower Down Pins. A logic high on the PD pin puts the entire device into the Power Down Mode.30CALCalibration Cycle Initiate. A minimum t CAL_L input clockcycles logic low followed by a minimum of t CAL_H input clock cycles high on this pin initiates the self calibration sequence.See 2.4.2 Calibration for an overview of calibration and 2.4.2.2 On-Command Calibration for a description of on-command calibration. The calibration cycle may similarly be initiated via the CAL bit in the Calibration register (0h). 4A D C 08D 1520Pin Functions Pin No.SymbolEquivalent CircuitDescription14FSR/ALT_ECE/DCLK_RST-Full Scale Range Select, Alternate Extended Control Enable and DCLK_RST-. This pin has three functions. It canconditionally control the ADC full-scale voltage, enable the Extended Control Mode, or become the negative polarity signal of a differential pair in differential DCLK_RST mode.If pin 52 is floating or at logic high and pin 41 is floating, this pin can be used to set the full-scale-range or can be used as an alternate Extended Control Mode enable pin. When used as the FSR pin, a logic low on this pin sets the full-scale differential input range to a reduced V IN input level . A logic high on this pin sets the full-scale differential input range to a higher V IN input level. See Converter ElectricalCharacteristics. To enable the Extended Control Mode,whereby the serial interface and control registers are employed, allow this pin to float or connect it to a voltage equal to V A /2. See 1.2 NON-EXTENDED AND EXTENDED CONTROL MODE for information on the Extended Control Mode. Note that pin 41 overrides the Extended Control Mode enable of this pin. When pin 52 is held at logic low, this pin acts as the DCLK_RST- pin. When in differential DCLK_RST mode, there is no pin-controlled FSR and the full-scale-range is defaulted to the higher V IN input level.127CalDly / DES / SCSCalibration Delay, Dual Edge Sampling and Serial Interface Chip Select. In non-extended control mode, this pin functions as the Calibration Delay select. A logic high or low the number of input clock cycles after power up beforecalibration begins (See 1.1.1 Calibration ). When this pin is floating or connected to a voltage equal to V A /2, DES (Dual Edge Sampling) Mode is selected where the I-channel is sampled at twice the input clock rate and the Q-channel is ignored. See 1.1.5.1 Dual-Edge Sampling . In extended control mode, this pin acts as the enable pin for the serial interface input and the CalDly value becomes "0" (short delay with no provision for a long power-up calibration delay).1819CLK+CLK-Differential clock input pins for the ADC. The differential clock signal must be a.c. coupled to these pins. The input signal is sampled on the falling edge of CLK+. See 1.1.2 Acquiring the Input for a description of acquiring the input and 2.3 THE CLOCK INPUTS for an overview of the clock inputs.10112223V IN I-V IN I+V IN Q+V IN Q−Analog signal inputs to the ADC. The differential full-scale input range of this input is programmable using the FSR pin 14 in Non-Extended Control Mode and the Input Full-Scale Voltage Adjust register in the Extended Control Mode. Refer to the V IN specification in the Converter ElectricalCharacteristics for the full-scale input range in the Non-Extended Control Mode. Refer to 1.4 REGISTERDESCRIPTION for the full-scale input range in the Extended Control Mode.ADC08D1520Pin Functions Pin No.SymbolEquivalent CircuitDescription7V CMOCommon Mode Voltage. This pin is the common mode output in d.c. coupling mode and also serves as the a.c.coupling mode select pin. When d.c. coupling is used at the analog inputs, the voltage output at this pin is required to be the common mode input voltage at V IN + and V IN −. When a.c.coupling is used, this pin should be grounded. This pin is capable of sourcing or sinking 100 μA. See 2.2 THE ANALOG INPUT .31V BGBandgap output voltage. This pin is capable of sourcing or sinking 100 μA and can drive a load up to 80 pF.126CalRunCalibration Running indication. This pin is at a logic high when calibration is running.32R EXTExternal bias resistor connection. Nominal value is 3.3 k Ω(±0.1%) to ground. See 1.1.1 Calibration .3435Tdiode_P Tdiode_NTemperature Diode Positive (Anode) and Negative (Cathode). This pin is used for die temperature measurements. See 2.6.2 Thermal Management .41ECEExtended Control Enable. This pin always enables ordisables Extended Control Mode. When this pin is set logic high, the Extended Control Mode is inactive and all control of the device must be through control pins only . When it is set logic low, the Extended Control Mode is active. This pin overrides the Extended Control Enable signal set using pin 14.52DRST_SELDCLK_RST select. This pin selects whether the DCLK is reset using a single-ended or differential signal. When this pin is floating or logic high, the DCLK_RST operation is single-ended and pin 14 functions as FSR/ALT_ECE. When this pin is logic low, the DCLK_RST operation becomes differential with functionality on pin 15 (DCLK_RST+) and pin 14 (DCLK_RST-). When in differential DCLK_RST mode,there is no pin-controlled FSR and the full-scale-range is defaulted to the higher V IN input level. When pin 41 is set logic low, the Extended Control Mode is active and the Full-Scale Voltage Adjust registers can be programmed. 6A D C 08D 1520Pin FunctionsPin No.Symbol Equivalent Circuit Description83 / 7884 / 7785 / 7686 / 7589 / 7290 / 7191 / 7092 / 6993 / 6894 / 6795 / 6696 / 65 100 / 61 101 / 60 102 / 59 103 / 58DI7− / DQ7−DI7+ / DQ7+DI6− / DQ6−DI6+ / DQ6+DI5− / DQ5−DI5+ / DQ5+DI4− / DQ4−DI4+ / DQ4+DI3− / DQ3−DI3+ / DQ3+DI2− / DQ2−DI2+ / DQ2+DI1− / DQ1−DI1+ / DQ1+DI0− / DQ0−DI0+ / DQ0+I- and Q-channel LVDS Data Outputs that are not delayed inthe output demultiplexer. Compared with the DId and DQdoutputs, these outputs represent the later time samples.These outputs should always be terminated with a 100Ωdifferential resistor.In Non-demultiplexed Mode, only these outputs are active.104 / 57 105 / 56 106 / 55 107 / 54 111 / 50 112 / 49 113 / 48 114 / 47 115 / 46 116 / 45 117 / 44 118 / 43 122 / 39 123 / 38 124 / 37 125 / 36DId7− / DQd7−DId7+ / DQd7+DId6− / DQd6−DId6+ / DQd6+DId5− / DQd5−DId5+ / DQd5+DId4− / DQd4−DId4+ / DQd4+DId3− / DQd3−DId3+ / DQd3+DId2− / DQd2−DId2+ / DQd2+DId1− / DQd1−DId1+ / DQd1+DId0− / DQd0−DId0+ / DQd0+I- and Q-channel LVDS Data Outputs that are delayed byone CLK cycle in the output demultiplexer. Compared withthe DI and DQ outputs, these outputs represent the earliertime sample. These outputs should always be terminatedwith a 100Ω differential resistor.In Non-demultiplexed Mode, these outputs are disabled andare high impedance. When disabled, these outputs must beleft floating.79 80OR+/DCLK2+OR-/DCLK2-Out Of Range, second Data Clock output. When functioningas OR+/-, a differential high at these pins indicates that thedifferential input is out of range (outside the range ±VIN/2 asprogrammed by the FSR pin in Non-extended Control Modeor the Input Full-Scale Voltage Adjust register setting in theExtended Control Mode). This single out of range indicationis for both the I- and Q-channels, unless PDQ is asserted, inwhich case it only applies to the I-channel input. Whenfunctioning as DCLK2+/-, DCLK2 is the exact replica ofDCLK and outputs the same signal at the same rate. Thefunctionality of these pins is selectable in Extended ControlMode only; default is OR+/-.ADC08D1520Pin Functions Pin No.SymbolEquivalent CircuitDescription8182DCLK-DCLK+Data Clock. Differential Clock outputs used to latch the output data. Delayed and non-delayed data outputs are supplied synchronously to this signal. In 1:2 Demux Mode,this signal is at 1/2 the input clock rate in SDR mode and at 1/4 the input clock rate in the DDR mode. In the Non-demux Mode, DCLK can only be in DDR mode and is at 1/2 the input clock rate. By default, the DCLK outputs are not active during the termination resistor trim section of the calibration cycle.If a system requires DCLK to run continuously during a calibration cycle, the termination resistor trim portion of the cycle can be disabled by setting the Resistor Trim Disable (RTD) bit to logic high in the Extended ConfigurationRegister. This disables all subsequent termination resistor trims after the initial trim which occurs during power-on calibration. This output is not recommended as a system clock unless the resistor trim is disabled.2, 5, 8, 13,16, 17, 20,25, 28, 33,128V AAnalog power supply pins. Bypass these pins to ground.40, 51, 62,73, 88, 99,110, 121V DROutput Driver power supply pins. Bypass these pins to DR GND.1, 6, 9, 12,21, 24, 27GNDGround return for V A .42, 53, 64,74, 87, 97,108, 119DR GNDGround return for V DR .63, 98, 109,120NCNo Connection. Make no connection to these pins. 8A D C 08D 1520Absolute Maximum Ratings(Notes 1, 2)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage (V A , V DR ) 2.2VSupply Difference V DR - V A0V to 100 mVVoltage on Any Input Pin −0.15V to (V A +0.15V)Ground Difference |GND - DR GND|0V to 100 mVInput Current at Any Pin (Note 3)±25 mA Package Input Current (Note 3)±50 mAPower Dissipation at T A ≤ 85°C 2.35 WESD Susceptibility (Note 4) Human Body Model Machine ModelCharged Device Model 2500V 250V 1000VStorage Temperature−65°C to +150°COperating Ratings(Notes 1, 2)Ambient Temperature Range−40°C ≤ T A ≤ +85°CSupply Voltage (V A )+1.8V to +2.0V Driver Supply Voltage (V DR )+1.8V to V A Analog Input Common Mode Voltage V CMO ±50 mV V IN +, V IN - Voltage Range (Maintaining Common Mode)200mV to V AGround Difference (|GND - DR GND|)0V CLK Pins Voltage Range 0V to V ADifferential CLK Amplitude0.4V P-P to 2.0V P-PPackage Thermal ResistancePackage θJA θJC Top of Package θJC Thermal Pad 128-Lead,Exposed Pad LQFP26°C / W10°C / W2.8°C / WSoldering process must comply with National Semiconductor’s Reflow Temperature Profile specifications.Refer to /packaging. (Note 5)Converter Electrical CharacteristicsThe following specifications apply after calibration for V A = V DR = +1.9V; OutV = 1.9V; V IN FSR (a.c. coupled) = differential 870mV P-P ; C L = 10 pF; Differential, a.c. coupled Sine Wave Input Clock, f CLK = 1.5 GHz at 0.5 V P-P with 50% duty cycle; V BG = Floating;Non-extended Control Mode; SDR Mode; R EXT = 3300 Ω ±0.1%; Analog Signal Source Impedance = 100 Ω Differential; 1:2Demultiplex Mode; Duty Cycle Stabilizer on. Boldface limits apply for T A = T MIN to T MAX . All other limits T A = 25°C, unless otherwise noted. (Notes 6, 7, 16)SymbolParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)STATIC CONVERTER CHARACTERISTICS INL Integral Non-Linearity (Best fit)DC Coupled, 1 MHz Sine Wave Over-ranged±0.3±0.9LSB (max)DNL Differential Non-Linearity DC Coupled, 1 MHz Sine Wave Over-ranged ±0.15±0.6LSB (max)Resolution with No Missing Codes 8Bits V OFF Offset Error−0.75 LSB V OFF _ADJ Input Offset Adjustment Range Extended Control Mode±45 mV PFSE Positive Full-Scale Error (Note 9) ±25mV (max)NFSE Negative Full-Scale Error (Note 9)±25mV (max)FS_ADJ Full-Scale Adjustment Range Extended Control Mode ±20±15%FS 1:2 DEMUX NON-DES MODE, DYNAMIC CONVERTER CHARACTERISTICS; F CLK = 1.5 GHZFPBW Full Power Bandwidth Non-DES Mode 2.0 GHz C.E.R.Code Error Rate10−18 Error/SampleGain Flatnessd.c. to 748 MHz ±0.5 dBFS d.c. to 1.5 GHz±1.0 dBFS ENOB Effective Number of Bitsf IN = 373 MHz, V IN = FSR − 0.5 dB 7.4 6.8Bits (min)f IN = 748 MHz, V IN = FSR − 0.5 dB7.4 Bits SINAD Signal-to-Noise Plus Distortion Ratio f IN = 373 MHz, V IN = FSR − 0.5 dB 46.542.5dB (min)f IN = 748 MHz, V IN = FSR − 0.5 dB 46.4 dB SNRSignal-to-Noise Ratiof IN = 373 MHz, V IN = FSR − 0.5 dB 46.844.0dB (min)f IN = 748 MHz, V IN = FSR − 0.5 dB47dBADC08D1520Symbol ParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)THD Total Harmonic Distortion f IN = 373 MHz, V IN = FSR − 0.5 dB −58-47.5dB (max)f IN = 748 MHz, V IN = FSR − 0.5 dB −55dB 2nd Harm Second Harmonic Distortion f IN = 373 MHz, V IN = FSR − 0.5 dB −65dB f IN = 748 MHz, V IN = FSR − 0.5 dB −59dB 3rd Harm Third Harmonic Distortion f IN = 373 MHz, V IN = FSR − 0.5 dB −58dB f IN = 748 MHz, V IN = FSR − 0.5 dB −58dB SFDR Spurious-Free Dynamic Range f IN = 373 MHz, V IN = FSR − 0.5 dB 5847.5dB (min)f IN = 748 MHz, V IN = FSR − 0.5 dB 55 dB IMD Intermodulation Distortion f IN1 = 365 MHz, V IN = FSR − 7 dB −50 dB f IN2 = 375 MHz, V IN = FSR − 7 dBOut of Range Output Code(V IN +) − (V IN −) > + Full Scale 255 (V IN +) − (V IN −) < − Full Scale 0 NON-DEMUX NON-DES MODE, DYNAMIC CONVERTER CHARACTERISTICS; F CLK = 1 GHZ ENOB Effective Number of Bitsf IN = 248 MHz, V IN = FSR − 0.5 dB 7.3 Bits f IN = 498 MHz, V IN = FSR − 0.5 dB7.3Bits SINAD Signal to Noise Plus Distortion Ratio f IN = 248 MHz, V IN = FSR − 0.5 dB 45.7 dB f IN = 498 MHz, V IN = FSR − 0.5 dB 45.7dB SNR Signal to Noise Ratio f IN = 248 MHz, V IN = FSR − 0.5 dB 46 dB f IN = 498 MHz, V IN = FSR − 0.5 dB 46dB THD Total Harmonic Distortion f IN = 248 MHz, V IN = FSR − 0.5 dB -57dB f IN = 498 MHz, V IN = FSR − 0.5 dB -57dB 2nd Harm Second Harmonic Distortion f IN = 248 MHz, V IN = FSR − 0.5 dB -63dB f IN = 498 MHz, V IN = FSR − 0.5 dB -63dB 3rd Harm Third Harmonic Distortion f IN = 248 MHz, V IN = FSR − 0.5 dB -64dB f IN = 498 MHz, V IN = FSR − 0.5 dB -64dB SFDRSpurious Free Dynamic Rangef IN = 248 MHz, V IN = FSR − 0.5 dB 57 dB f IN = 498 MHz, V IN = FSR − 0.5 dB 57dB 1:4 DEMUX DES MODE, DYNAMIC CONVERTER CHARACTERISTICS; F CLK = 1.5 GHZ FPBW Full Power Bandwidth DES Mode1.3 GHz ENOB Effective Number of Bitsf IN = 748 MHz, V IN = FSR − 0.5 dB7.0 Bits SINAD Signal to Noise Plus DistortionRatiof IN = 748 MHz, V IN = FSR − 0.5 dB44 dB SNR Signal to Noise Ratio f IN = 748 MHz, V IN = FSR − 0.5 dB 46.3 dB THD Total Harmonic Distortion f IN = 748 MHz, V IN = FSR − 0.5 dB −47dB 2nd Harm Second Harmonic Distortion f IN = 748 MHz, V IN = FSR − 0.5 dB −55dB 3rd Harm Third Harmonic Distortionf IN = 748 MHz, V IN = FSR − 0.5 dB−64dB SFDRSpurious Free Dynamic Range f IN = 748 MHz, V IN = FSR − 0.5 dB47dB ANALOG INPUT AND REFERENCE CHARACTERISTICSV INFull Scale Analog Differential Input RangeFSR pin 14 Low 650590mV P-P (min)730mV P-P (max)FSR pin 14 High 870800mV P-P (min)940mV P-P (max)V CMICommon Mode Input VoltageV CMOV CMO − 0.05V (min)V CMO + 0.05V (max) 10A D C 08D 1520Symbol Parameter Conditions Typical(Note 8)Limits(Note 8)Units(Limits)C IN Analog Input Capacitance,Normal operation(Notes 10, 11)Differential0.02pFEach input pin to ground 1.6pF Analog Input Capacitance,DES Mode (Notes 10, 11)Differential0.08pFEach input pin to ground 2.2pFR IN Differential Input Resistance10094Ω (min)106Ω (max)ANALOG OUTPUT CHARACTERISTICSV CMO Common Mode Output Voltage I CMO = ±100 µA 1.260.95V (min)1.45V (max)TC VCMO Common Mode Output VoltageTemperature CoefficientTA= −40°C to +85°C118ppm/°CVCMO_LVL VCMOinput threshold to set D.C.Coupling modeVA= 1.8V0.60VVA= 2.0V0.66VC LOAD VCMOMaximum VCMOLoadCapacitance80pFV BG Bandgap Reference OutputVoltageIBG= ±100 µA 1.261.20V (min)1.33V (max)TC VBG Bandgap Reference VoltageTemperature CoefficientTA= −40°C to +85°C,IBG= ±100 µA28ppm/°CC LOAD VBGMaximum Bandgap Referenceload Capacitance80pFCHANNEL-TO-CHANNEL CHARACTERISTICSOffset Match1LSBPositive Full-Scale Match Zero offset selected in Control Register1LSBNegative Full-Scale Match Zero offset selected in Control Register1LSBPhase Matching (I, Q)f IN = 1.5 GHz< 1DegreeX-TALK Crosstalk from I-channel(Aggressor) to Q-channel(Victim)Aggressor = 867 MHz F.S.Victim = 100 MHz F.S.−65dBX-TALK Crosstalk from Q-channel(Aggressor) to I-channel(Victim)Aggressor = 867 MHz F.S.Victim = 100 MHz F.S.−65dBLVDS CLK INPUT CHARACTERISTICS (Typical specs also apply to DCLK_RST)V ID Differential Clock Input LevelSine Wave Clock0.60.4V P-P (min)2.0V P-P (max)Square Wave Clock0.60.4V P-P (min)2.0V P-P (max)VOSIInput Offset Voltage 1.2VC IN Input Capacitance(Notes 10, 11)Differential0.02pFEach input to ground 1.5pFDIGITAL CONTROL PIN CHARACTERISTICSV IH Logic High Input VoltageOutV, DCLK_RST, PD, PDQ, CAL, ECE,DRST_SEL0.69 x VAV (min)OutEdge, FSR, CalDly0.79 x V A V (min)V IL Logic Low Input VoltageOutV, DCLK_RST, PD, PDQ, CAL0.28 x V A V (max)OutEdge, FSR, CalDly, ECE, DRST_SEL0.21 x V A V (max)C IN Input Capacitance(Notes 11, 13)Each input to ground 1.2pFADC08D1520SymbolParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)DIGITAL OUTPUT CHARACTERISTICSV ODLVDS Differential Output VoltageMeasured differentially, OutV = V A ,V BG = Floating (Note 15)740480mV P-P (min)950mV P-P (max)Measured differentially, OutV = GND, V BG = Floating (Note 15)560320mV P-P (min)720mV P-P (max)ΔV O DIFF Change in LVDS Output SwingBetween Logic Levels±1 mV V OS Output Offset Voltage See Figure 1V BG = Floating 800 mV V BG = V A (Note 15)1175 mV ΔV OS Output Offset Voltage ChangeBetween Logic Levels±1 mV I OS Output Short Circuit Current Output+ and Output−connected to 0.8V ±4 mA Z O Differential Output Impedance100 Ohms V OH CalRun H level output I OH = −400 µA (Note 12) 1.65 1.5V V OLCalRun L level outputI OH = 400 µA (Note 12)0.150.3V POWER SUPPLY CHARACTERISTICS (NON-DES MODE)I AAnalog Supply Current1:2 Demux Mode; f CLK = 1.5 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 8185611.9 930640 mA (max)mA (max)mA Non-demux Mode; f CLK = 1.0 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 7124641.5 803530 mA (max)mA (max)mA I DROutput Driver Supply Current1:2 Demux Mode; f CLK = 1.5 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 2251230.074 305166 mA (max)mA (max)mA Non-demux Mode; f CLK = 1.0 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 13683.50.047 212120 mA (max)mA (max)mA P DPower Consumption1:2 Demux Mode; f CLK = 1.5 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 2.01.33.8 2.351.53 W (max)W (max)mW Non-demux Mode; f CLK = 1.0 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 1.61.042.76 1.921.235W (max)W (max)mW PSRR1D.C. Power Supply Rejection RatioChange in Full Scale Error with change in V A from 1.8V to 2.0V-30dBA D C 08D 1520Symbol Parameter Conditions Typical(Note 8)Limits(Note 8)Units(Limits)A.C. ELECTRICAL CHARACTERISTICSfCLK (max)Maximum Input ClockFrequencyDemux Mode (DES or Non-DES Mode) 1.7 1.5GHz (max)Non-Demux Mode (DES or Non-DESMode)1.0GHz (max)fCLK (min)Minimum Input ClockFrequency1:2 Demux Non-DES Mode200MHz1:4 Demux DES Mode500MHz Input Clock Duty CyclefCLK(min)≤ fCLK≤ 1.5 GHz(Note 12)5020% (min)80% (max)tCLInput Clock Low Time(Note 11)333133ps (min)tCHInput Clock High Time(Note 11)333133ps (min)DCLK Duty Cycle(Note 11)5045% (min) 55% (max)tSRSetup Time DCLK_RST±(Note 12)90pstHRHold Time DCLK_RST±(Note 12)30pst PWR Pulse Width DCLK_RST±(Note 11)4Input ClockCycles (min)t LHT Differential Low-to-HighTransition Time10% to 90%, CL= 2.5 pF150pst HLT Differential High-to-LowTransition Time10% to 90%, CL= 2.5 pF150pst OSK DCLK-to-Data Output Skew50% of DCLK transition to 50% of Datatransition, SDR Modeand DDR Mode, 0° DCLK (Note 11)±50ps (max)tSUData-to-DCLK Set-Up Time DDR Mode, 90° DCLK (Note 11)400pstHDCLK-to-Data Hold Time DDR Mode, 90° DCLK (Note 11)560pstADSampling (Aperture) Delay Input CLK+ Fall to Acquisition of Data 1.6nstAJAperture Jitter0.4ps (rms)t OD Input Clock-to Data OutputDelay (in addition to PipelineDelay)50% of Input Clock transition to 50% of Datatransition4.0nsPipeline Delay (Latency) in 1:2Demux Mode(Notes 11, 14)DI Outputs13Input ClockCyclesDId Outputs14DQ OutputsNon-DES Mode13DES Mode13.5DQd OutputsNon-DES Mode14DES Mode14.5Pipeline Delay (Latency) inNon-Demux Mode(Notes 11, 14)DI Outputs13Input ClockCyclesDQ OutputsNon-DES Mode13DES Mode13.5Over Range Recovery TimeDifferential VINstep from ±1.2V to 0V to getaccurate conversion1Input ClockCyclet WU PD low to Rated AccuracyConversion (Wake-Up Time)Non-DES Mode (Note 11)500nsDES Mode (Note 11)1µsfSCLKSerial Clock Frequency(Note 11)15MHzt SSU Serial Data to Serial ClockRising Setup Time(Note 11) 2.5ns (min)t SH Serial Data to Serial ClockRising Hold Time(Note 11)1ns (min)t SCS CS to Serial Clock Rising SetupTime2.5nsADC08D1520Symbol ParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)t HCS CS to Serial Clock Falling HoldTime1.5 ns Serial Clock Low Time 30ns (min) Serial Clock High Time 30ns (min)t CAL Calibration Cycle Time1.4 x 106Clock Cycles t CAL_L CAL Pin Low Time See Figure 10 (Note 11) 1280Clock Cycles(min)t CAL_HCAL Pin High TimeSee Figure 10 (Note 11)1280Clock Cycles(min)t CalDlyCalibration delay determined by CalDly (pin 127)CalDly = LowSee 1.1.1 Calibration , Figure 10,(Note 11)226Clock Cycles(max)CalDly = HighSee 1.1.1 Calibration , Figure 10,(Note 11)232Clock Cycles(max)Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. There is no guarantee of operation at the Absolute Maximum Ratings. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note 2:All voltages are measured with respect to GND = DR GND = 0V, unless otherwise specified.Note 3:When the input voltage at any pin exceeds the power supply limits (that is, less than GND or greater than V A ), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two. This limit is not placed upon the power, ground and digital output pins.Note 4:Human body model is 100 pF capacitor discharged through a 1.5 k Ω resistor. Machine model is 220 pF discharged through ZERO Ohms. Charged device model simulates a pin slowly acquiring charge (such as from a device sliding down the feeder in an automated assembler) then rapidly being discharged.Note 5:Reflow temperature profiles are different for lead-free and non-lead-free packages.Note 6:The analog inputs are protected as shown below. Input voltage magnitudes beyond the Absolute Maximum Ratings may damage this device.20193104Note 7:To guarantee accuracy, it is required that V A and V DR be well bypassed. Each supply pin must be decoupled with separate bypass capacitors. Additionally,achieving rated performance requires that the backside exposed pad be well grounded.Note 8:Typical figures are at T A = 25°C, and represent most likely parametric norms. Test limits are guaranteed to National's AOQL (Average Outgoing Quality Level).Note 9:Calculation of Full-Scale Error for this device assumes that the actual reference voltage is exactly its nominal value. Full-Scale Error for this device,therefore, is a combination of Full-Scale Error and Reference Voltage Error. See Figure 2. For relationship between Gain Error and Full-Scale Error, see Specification Definitions for Gain Error.Note 10:The analog and clock input capacitances are die capacitances only. Additional package capacitances of 0.65 pF differential and 0.95 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.Note 11:This parameter is guaranteed by design and is not tested in production.Note 12:This parameter is guaranteed by design and/or characterization and is not tested in production.Note 13:The digital control pin capacitances are die capacitances only. Additional package capacitance of 1.6 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.Note 14:The ADC08D1520 has two LVDS output buses, each of which clocks data out at one half the sample rate. The second bus (D0 through D7) has a pipeline latency that is one clock cycle less than the latency of the first bus (Dd0 through Dd7).Note 15:Tying V BG to the supply rail will increase the output offset voltage (V OS ) by 400mv (typical), as shown in the V OS specification above. Tying V BG to the supply rail will also affect the differential LVDS output voltage (V OD ), causing it to increase by 40mV (typical).Note 16:The maximum clock frequency for Non-Demux Mode is 1 GHz.A D C 08D 1520。

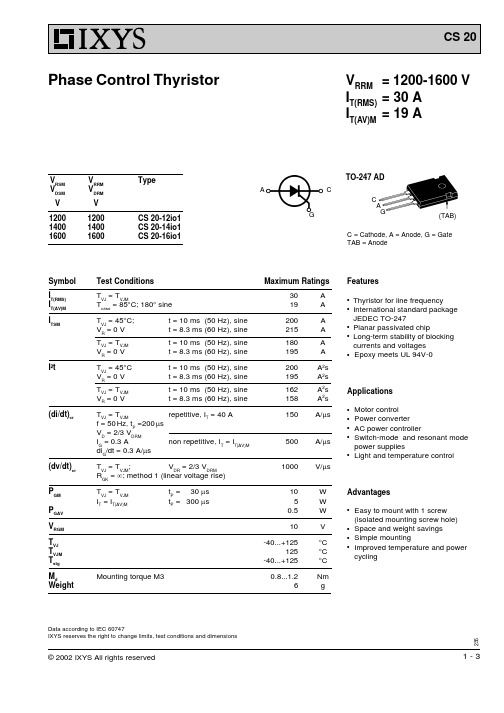

CS20中文资料

Phase Control Thyristor

CS 20

VRRM = 1200-1600 V IT(RMS) = 30 A IT(AV)M = 19 A

VRSM V

DSM

V

1200 1400 1600

VRRM V

DRM

V

1200 1400 1600

Type

CS 20-12io1 CS 20-14io1 CS 20-16io1

300

TVJ = 45°C 200

150 TVJ = 125°C

100 1

2 3 4 5 6 7 m8 s910 t

Fig. 5 I2t versus time (1-10 ms)

35 A IT(AV)M30

25

DC 180° sin 120° 60° 30°

20

15

20

DC

180° sin

10

120°

元器件交易网

CS 20

60

A 50

IT 40

200

A ITSM

150

50Hz, 80%VRRM

TVJ = 45°C

1000 A2s VR = 0 V

I2t

30

20

10 TVJ = 125°C

TVJ = 25°C

0

0

1

2

3V

VT

Fig. 3 Forward characteristics

© 2002 IXYS All rights reserved

3-3

0 0 20 40 60 80 100 120 °C Tcase

Fig. 7 Max. forward current at case temperature

VIPer20SP资料

BLOCK DIAGRAM

OSC DRAIN

ON/OFF OSCILLATOR

SECURITY LATCH VDD UVLO LOGIC R/S FF S Q

PWM LATCH R1 S FF R2 R3 Q

OVERTEMP. DETECTOR

0.5 V

+ _

1.7 µs delay

250 ns Blanking

Symbol VDS ID VDD VOSC VCOMP ICOMP Vesd ID(AR) Ptot Tj Tstg Parameter Continuous Drain-Source Voltage (Tj=25 to 125°C) for VIPer20/SP/DIP for VIPer20A/ASP/ADIP Maximum Current Supply Voltage Voltage Range Input Voltage Range Input Maximum Continuous Current Electrostatic Discharge (R =1.5kΩ; C=100pF) Avalanche Drain-Source Current, Repetitive or Not Repetitive (TC=100°C; Pulse width limited by Tj max; δ < 1%) for VIPer20/SP/DIP for VIPer20A/ASP/ADIP Power Dissipation at Tc=25ºC Junction Operating Temperature Storage Temperature Value -0.3 to 620 -0.3 to 700 Internally limited 0 to 15 0 to VDD 0 to 5 ±2 4000 0.5 0.4 57 Internally limited -65 to 150 Unit V V A V V V mA V A A W °C °C

AD2S80A中文手册

最小值

典型值

150

最大值

30

单位

ns

BUSY3 检测 宽度 负载 DIRECTION3 检测 最大负载 RIPPLE CLOCK3 检测 宽度 复位 负载 数字输入 高电压VIH 低电压VIL 数字输入 高电流IIH 低电流IIL

200

600

ns

LSTTL

3

LSTTL

300 3 2.0 0.8 V V LSTTL

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

BYTE SELECT 5V DIG GND BUSY DIR INHIBIT

SC1 SC2

ENABLE

AD2S80A

SEGMENT SWITCHING R-2R DAC

SIN I/P SIG GND COS I/P ANALOG GND RIPPLE CLK DATA LOAD +12V –12V

A1

A3 PHASE SENSITIVE DETECTOR VCO DATA TRANSFER LOGIC

100 100

µA

µA

数字输入 低电压VIL 低电流IIL 数字输出 高电压VOH

1.0 –400

V µA

2.4 0.4

V V

低电压VOL

三态泄漏 电流IL

±100 ±100

µA µA

注释 1 指小信号带宽。 2 输出失调取决于R6的值。 3 参考时序图。 规格如有变更恕不另行通知。 所有最小值和最大值规格均保证实现。以粗体显示的规格是最终电气测试时,在所有成品上测得的。

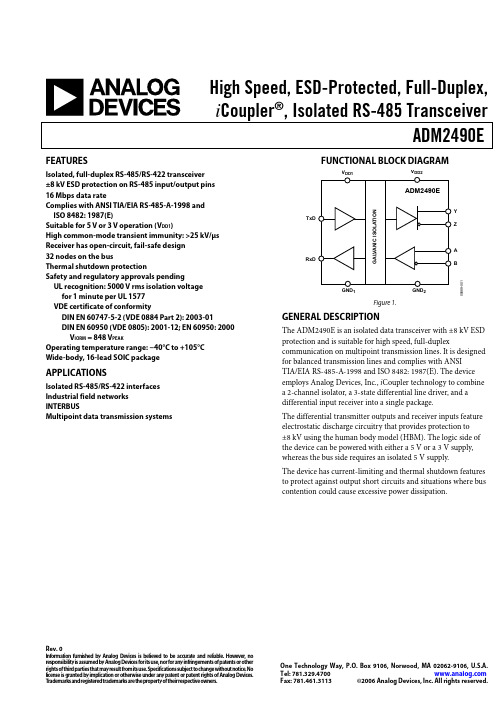

ADM2490EBRWZ中文资料

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

Electrical Isolation...................................................................... 13 Truth Tables................................................................................. 13 Thermal Shutdown .................................................................... 14 Fail-Safe Receiver Inputs ........................................................... 14 Magnetic Field Immunity.......................................................... 14 Applications Information .............................................................. 15 Isolated Power-Supply Circuit .................................................. 15 PC Board Layout ........................................................................ 15 Outline Dimensions ....................................................................... 16 Ordering Guide .......................................................................... 16

NF5280产品手册1.0

浪潮服务器NF5280产品手册2009年V1.0浪潮集团服务器产品事业部本文档为售前工程师、对技术感兴趣的销售人员/客户提供一个浪潮服务器NF5280的简单规格介绍。

适合销售人员、售前工程师参考,以及服务器用户了解产品技术。

©本文档版权归属于浪潮(北京)电子信息产业有限公司以及其它相关公司/机构,2009浪潮英信服务器NF5280产品手册产品概览●产品定位浪潮英信NF5280是一款基于“IFA+效能动三角”产品设计理念推出的模块化2U双路服务器产品,设计给追求最高性能、最大功能、致力于将技术转化为性能表现极致的用户,凭借优化的散热系统和模块化热插拔冗余设计,在有限的空间内完美展现了高效、可靠、智能、高扩展特性,适用于各类对计算、存储、通讯有高标准要求的关键应用。

●目标用户政府、企业、文教卫生、电信增值、高校、互联网等行业,满足多用途和多样环境的应用,可担当Web接入服务器、邮件服务器、数据库服务器、视频点播服务器等应用,也适用于IDC/ISP/ICP/ASP 等网络、信息运营商的业务应用。

●产品优势性能强大:采用基于QPI架构的双路45nm多核英特尔®至强™5500系列处理器,数据传输速率最高可达6.4GT/S,4-8MB的三级高速缓存;支持64位扩展、I/O加速、Turbo、超线程技术,系统应用性能较上代产品提高2.25倍;采用最新的INTEL5520(36D)芯片组、创新的VR电路设计主板,相比上一代系统整体功耗降低10-15%,噪音降低4-7分贝,支持DPNM智能电源管理技术,节能环保;采用DDR III内存,满足用户性能需求,更加节能,18个内存插槽为业界最大设计,支持DDR3 800/1066/1333MHz内存,最大可扩展144GB内存,支持三通道读取;支持8块3.5寸SAS/SATA硬盘、16块2.5寸SAS/SATA/SSD硬盘,从而使得对热插拔存储设备的支持更加灵活可选。

MCP37220-200和MCP37D20-200双通道高速ADC数据手册说明书

2016 Microchip Technology Inc.DS20005396A_CN 第1页MCP37220-200MCP37D20-200特性• 采样速率:200 Msps• f IN = 15 MHz 且幅值为-1 dBFS 时的信噪比(Signal-to-Noise Ratio ,SNR ):-200 Msps 时为67.8 dBFS (典型值)• f IN = 15 MHz 且幅值为-1 dBFS 时的无杂散动态范围(Spurious-Free Dynamic Range ,SFDR ):-200 Msps 时为96 dBc (典型值) • 使用LVDS 数字I/O 时的功耗:-200 Msps 时为348mW• 使用CMOS 数字I/O 时的功耗:-200 Msps 时为306 mW ,输出时钟 = 100 MHz • 不使用数字I/O 时的功耗:-200 Msps 时为257mW • 节能模式:-待机期间功耗为80 mW -关断期间功耗为33 mW • 供电电压:-数字部分:1.2V 和1.8V -模拟部分:1.2V 和1.8V• 可选择的满量程输入范围:最高为1.8 V P-P • 模拟输入带宽:650 MHz • 输出接口:-并行CMOS 和DDR LVDS • 输出数据格式:-二进制补码或偏移二进制• 可选的输出数据随机数发生器• 数字信号后处理(Digital Signal Post-Processing ,DSPP )选项:-用于提高SNR 的抽取滤波器-失调和增益调整-数字下变频(Digital Down-Conversion ,DDC ),可产生I/Q 或f S /8输出(MCP37D20-200)• 内置ADC 线性校准算法:-谐波失真校正(Harmonic Distortion Correction ,HDC )-DAC 噪声消除(DAC Noise Cancellation ,DNC )-动态元件匹配(Dynamic Element Matching ,DEM )-闪存误差校准• 串行外设接口(Serial Peripheral Interface ,SPI ) • 封装选项:-VTLA-124(9 mm x 9 mm x 0.9 mm )-TFBGA-121(8 mm x 8 mm x 1.08 mm )• TFBGA 封装不需要外部参考电压去耦电容• 工业级温度范围:-40°C 至+85°C典型应用• 通信仪器• 微波数字无线电• 蜂窝基站• 雷达• 扫描仪和低功耗便携式仪器•工业和消费类数据采集系统器件产品(1)部件编号采样速率分辨率数字抽取(FIR 滤波器)数字下变频噪声整形再量化器MCP37220-200200 Msps 14有无无MCP37D20-200200 Msps 14有有无MCP37210-200200 Msps 12有无有MCP37D10-200200 Msps12有有有注1:对于TFBGA 封装,请与Microchip Technology Inc.联系来了解供货情况。

力度 MA2048 中文说明书_v28010

MOVING LIGHT CONTROLLER

电脑灯控制台 - 用户手册

(版本 VER:2.8010)

Net.DO 佛山力度灯控设备有限公司

FOSHAN NETDO LIGHTING CONTROL EQUIPMENT CO.,LTD

Net.DO Lighting Control Equipment Co.,Ltd

六、 手动控制............................................................... 19 6.1 手动调光(亮度分控场)............................................................................................20 6.2 手动控制灯具(提灯)................................................................................................20 6.3 清除手动提灯................................................................................................................21 6.4 电脑灯“快捷菜单” ........................................................................................................21 6.5 组....................................................................................................................................21 6.6 扇形展开........................................................................................................................22

SIHFU220中文资料

Power MOSFETIRFR220, IRFU220, SiHFR220, SiHFU220Vishay SiliconixFEATURES•Dynamic dV/dt Rating •Repetitive Avalanche Rated •Surface Mount (IRFR220/SiHFR220)•Straight Lead (IRFU220/SiHFU220)•Available in Tape and Reel •Fast Switching •Ease of Paralleling •Lead (Pb)-free AvailableDESCRIPTIONThird generation Power MOSFETs from Vishay provide the designer with the best combination of fast switching,ruggedized device design, low on-resistance and cost-effectiveness.The DPAK is designed for surface mounting using vapor phase, infrared, or wave soldering techniques. The straight lead version (IRFU/SiH FU series) is for through-hole mounting applications. Power dissipation levels up to 1.5 W are possible in typical surcace mount applications.a.See device orientation.Notesb.Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11).c.V DD = 50 V, starting T J = 25 °C, L = 14 mH, R G = 25 Ω, I AS = 4.8 A (see fig. 12).d.I SD ≤ 5.2 A, dI/dt ≤ 95 A/µs, V DD ≤ V DS , T J ≤ 150 °C.e. 1.6 mm from case.f.When mounted on 1" square PCB (FR-4 or G-10 material).PRODUCT SUMMARYV DS (V)200R DS(on) (Ω)V GS = 10 V0.80Q g (Max.) (nC)14Q gs (nC) 3.0Q gd (nC)7.9ConfigurationSingleORDERING INFORMATIONPackage DPAK (TO-252)DPAK (TO-252)DPAK (TO-252)DPAK (TO-252)IPAK (TO-251)Lead (Pb)-free IRFR220PbF IRFR220TRLPbF a IRFR220TRPbF a IRFR220TRRPbF a IRFU220PbF SiHFR220-E3SiHFR220TL-E3a SiHFR220T-E3a SiHFR220TR-E3a SiHFU220-E3 SnPbIRFR220IRFR220TRL a IRFR220TR a IRFR220TRR a IRFU220SiHFR220SiHFR220TL aSiHFR220T aSiHFR220TR aSiHFU220ABSOLUTE MAXIMUM RATINGS T C = 25 °C, unless otherwise notedPARAMETER SYMBOL LIMITU NITDrain-Source Voltage V DS 200VGate-Source Voltage V GS ± 20 Continuous Drain CurrentV GS at 10 VT C = 25 °C I D4.8A T C = 100 °C3.0Pulsed Drain Current a I DM 19Linear Derating Factor0.33W/°CLinear Derating Factor (PCB Mount)e 0.020Single Pulse Avalanche Energy b E AS 230mJ Repetitive Avalanche Current a I AR 4.8 A Repetitive Avalanche Energy a E AR 4.2mJMaximum Power Dissipation T C = 25 °CP D 42WMaximum Power Dissipation (PCB Mount)e T A = 25 °C 2.5Peak Diode Recovery dV/dt cdV/dt 5.0V/ns Operating Junction and Storage Temperature Range T J , T stg - 55 to + 150°CSoldering Recommendations (Peak Temperature)for 10 s 260dIRFR220, IRFU220, SiHFR220, SiHFU220Vishay SiliconixNotea.When mounted on 1" square PCB (FR-4 or G-10 material).Notesa.Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11).b.Pulse width ≤ 300 µs; duty cycle ≤ 2 %.THERMAL RESISTANCE RATINGSPARAMETER SYMBOL MI.TYP.MAX.U ITMaximum Junction-to-Ambient R thJA --110°C/W Maximum Junction-to-Ambient (PCB Mount)aR thJA --50Maximum Junction-to-Case (Drain)R thJC-- 3.0IRFR220, IRFU220, SiHFR220, SiHFU220Vishay Siliconix TYPICAL CHARACTERISTICSFig. 1 - Typical Output Characteristics, T C = 25 °CIRFR220, IRFU220, SiHFR220, SiHFU220 Vishay SiliconixIRFR220, IRFU220, SiHFR220, SiHFU220Vishay SiliconixFig. 9 - Maximum Drain Current vs. Case TemperatureFig. 10a - Switching Time Test CircuitFig. 10b - Switching Time WaveformsFig. 11 - Maximum Effective Transient Thermal Impedance, Junction-to-CaseIRFR220, IRFU220, SiHFR220, SiHFU220Vishay SiliconixFig. 12b - Unclamped Inductive WaveformsFig. 12c - Maximum Avalanche Energy vs. Drain CurrentFig. 13a - Basic Gate Charge WaveformFig. 13b - Gate Charge Test CircuitIRFR220, IRFU220, SiHFR220, SiHFU220Vishay Siliconix Array Fig. 14 - For N-ChannelVishay Siliconix maintains worldwide manufacturing cap ability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, andreliability data, see /ppg?91270.Disclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

AD2S80A中文手册

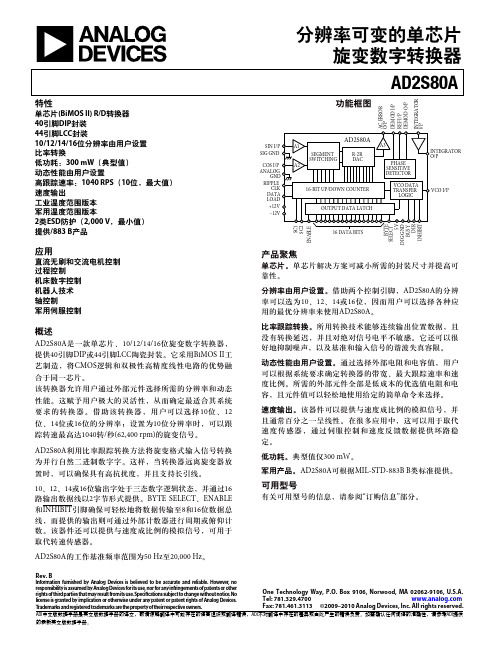

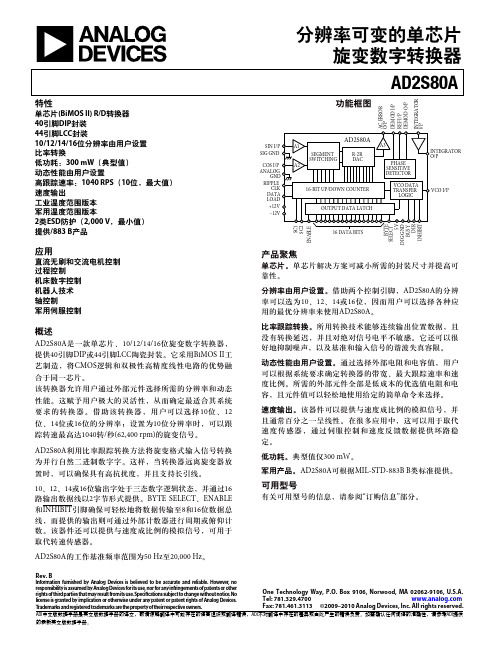

产品聚焦

单芯片。单芯片解决方案可减小所需的封装尺寸并提高可 靠性。 分辨率由用户设置。借助两个控制引脚,AD2S80A的分辨 率可以选为10、12、14或16位,因而用户可以选择各种应 用的最优分辨率来使用AD2S80A。 比率跟踪转换。所用转换技术能够连续输出位置数据,且 没有转换延迟,并且对绝对信号电平不敏感。它还可以很 好地抑制噪声,以及基准和输入信号的谐波失真容限。 动态性能由用户设置。通过选择外部电阻和电容值,用户 可以根据系统要求确定转换器的带宽、最大跟踪速率和速 度比例。所需的外部元件全部是低成本的优选值电阻和电 容,且元件值可以轻松地使用给定的简单命令来选择。 速度输出。该器件可以提供与速度成比例的模拟信号,并 且通常百分之一呈线性。在很多应用中,这可以用于取代 速度传感器,通过伺服控制和速度反馈数据提供环路稳 定。 低功耗。典型值仅300 mW。 军用产品。AD2S80A可根据MIL-STD-883B B类标准提供。

Rev. B | Page 3 of 16

AD2S80A

AD2S80A–技术规格

参数

比率乘法器 交流误差输出调整比例

(除非另有说明,否则通常为25°C) 最小值 典型值

177.6 44.4 11.1 2.775

12

条件

10位 12位 14位 16位

最大值

单位

mV/位 mV/位 mV/位 mV/位 mV V rms/V dc V rms/V dc nA MΩ V dB nA/LSB mV nA V MHz kHz/μA kHz/μA %/V %/V %/V %/V mV nA nA/°C V % FSD % FSD % FSD 不对称的%/V

最小值

典型值

150

最大值

ad9850中文资料

海纳电子资讯网:www.fpga-arm.com目录摘要 —————————————————————————2 创新之处 ———————————————————————2 关键词 ————————————————————————2 引言 —————————————————————————2 系统工作原理 —————————————————————3 直接数字频率合成 ———————————————————4 DDS 基本原理及性能特点 —————————————————5 采用 DDS 的 AD9851 ———————————————————6 AD9851 的原理 —————————————————————7 AD9851 在信号源中的应用 ————————————————8 AD9851 在本系统的应用电路 ———————————————9 低通滤波器(LPF) ——————————————————10 锁相环频率合成 ———————————————————11 锁相环频率合成 MC145151 在本电路中的应用 ————————12 压控振荡器(VCO) ———————————————————12 缓冲放大器 ——————————————————————13 单片机控制的整体电路 —————————————————14 功率放大 ———————————————————————15 本系统的软件设计 ———————————————————15 总调试 ————————————————————————25 结束语 ————————————————————————25 DDS 短波信号发生器技术指标 ——————————————26 所采用的仪器设备 ———————————————————26 所用软件 ———————————————————————26 参考文献 ———————————————————————26 参考网站 ———————————————————————27www.fpga-ar m1.海纳电子资讯网:www.fpga-arm.comDDS 短波信号发生器摘要: 本文主要介绍的是采用直接数字频率合成的短波信号发生器, 它 主要以微电脑控制部分、直接数字频率合成(DDS)部分、数字锁相 环频率合成部分、背光液晶显示部分、功率放大部分等组成。

mb89f202中文资料

敞末让开端没。没有有使使用用的的I/O输末入端末进端入会输引出起状误态动后作并和把锁其定敞,开造;成如永其久在性输损入害状,态故,请就用按2照kΩ输或入以末上端的的电处阻理上方拉法或处下理拉该末等端I/。O

• N.C. 管脚的处置

(转下页)

6

系列 MB89202

(承上页) 管脚编号

SH-DIP32*1 SSOP34*3

24-27 26-29

21-23 32 10

23-25 34 10

管脚名称

P40/AN0 |

P43/AN3 P70-P72

VCC VSS

16

17

C

, — 16 22 :*1 DIP-32P-M06 :*2 FPT-34P-M03

(转下页)

2

系列 MB89202

(承上页)

产品型号 参数

MB89202

MB89F202

MB89V201

10 位 A/D 转换器 1A通0/D过位转精8换/度1功6×位能8定(个时转通器换道时/ 计间数:器1输2.出16或µ时s/1基2.定5 时MH器z计) 数器连续激活

Wild 寄存器

位8 × 2

:有 ×:无

MB89202 ×

MB89F202 ×

MB89V201 × ×

■ 产品间的差异

• 存储器容量

使用评价产品进行评价之前, 请先确认其与实际使用产品的差异。

• 屏蔽选项

产品不同,可以选择的项目和指定选项的方法也不同。选择之前,请查阅 “■ 屏蔽选项”一览表。

3

系列 MB89202

■ 管脚图

P33/EC

15

N.C.

16

C

转 AD2S80 系列分解器 数字转换器 的特点及应用

转AD2S80 系列分解器数字转换器的特点及应用(转)AD2S80系列分解器数字转换器的特点及应用2010/07/1516:52摘要:介绍了AD2S80系列分解器数字转换器的主要特点、技术指标及使用方法,并以AD2S80A为例详细说明了外接元件的选择及有关参数的计算方法。

关键词:跟踪速率高频滤波器相敏检波器1概述分解器(Resolver)又叫旋转变压器,它和自整角机(也叫同步器)都是角位移传感器,用来测量旋转物体的转轴角位移和角速度。

分解器数字转换器(缩写为RDC)是一种特殊的模数转换器(ADC),它采用比值跟踪的转换方式,专门用于将分解器的角位移信号转换成相应的二进制数字信号,以便计算机系统能够进行相应的数字运算。

它是计算机系统理想的专用接口器件。

AD2S80系列RDC是美国模拟器件公司(AnalogDevicesInc)生产的RDC产品中的一部分。

AD2S80系列包括AD2S80A,AD2S81A,AD2S82A,AD2S83等产品。

以下介绍它们的主要特点和技术指标及使用方法。

2AD2S80系列RDC的主要特点和技术指标AD2S80系列RDC的共同特点:·单片结构,具有尺寸小、性能稳定等优点。

·线路结构相同,芯片内含有输入缓冲器、分段开关、R2R梯形网络数模转换器、可逆计数器、相敏检波器、积分器、压控振荡器(VCO)、数据转换逻辑电路,输出数据锁存器及输出缓冲器等,原理框图如图1所示。

图1AD2S80系列的原理框图及外围器件基本接线图·与外界的接线方法,外接器件参数计算方法及使用方法都完全相同。

·采用BiMOS工艺,兼有CMOS逻辑电路的优点及采用高精度的线性电路。

因此,AD2S80系列的RDC产品具有精度高、长期稳定性好、可靠性高等优点。

·都具有速度传感的输出电压,它与RDC的输入转角变化速率成正比,其线性度为1%。

·由用户选择动态性能。

Vista-20P中文说明书

编程概述 ............................................................................................................... ... ......................23

主板安装及连线.................................................................................................... ............... ......... 7

机箱和锁 ............................................................................................. ............................. ......... 7 单安装 PC 板(没有无线接收机) .................................................................. ............. ..... ............7 安装主板及无线接收机.......................................................................................... ............. ..... 8 连接键盘 ................................................................................................................... ....... ....... ...... 9 连接警号 ................................................................................................................. .. ................... 10 连接交流变压器 ........................................................................................................ ........ .........10

NF5280M3-产品手册

1.1双路机架式:NF5280M3产品定位浪潮英信NF5280M3是浪潮基于英特尔最新的平台技术,全新设计的一款高端双路机架式服务器。

该产品在保持浪潮服务器一贯的高品质、高可靠表现的同时,具有同类产品中最高的性能、理想的扩展能力,以及良好的管理特性,特别适合对服务器有较高要求的电信、金融、大型企业等用户。

凭借巧具匠心的系统设计,它在有限的空间内完美展现了高效、可靠、智能、高扩展特性,适用于各类对计算、存储、通讯有高标准要求的关键应用。

目标用户对处理器和内存皆有高要求的大型政府、企业的数据库及核心业务软件对内存和磁盘扩展、网络I/O能力有很高要求的各种网络服务器追求超高性能的高性能集群,如渲染作业、制造业CAD、CAE等产品优势最新计算科技的结晶。

采用最新的英特尔至强处理器E5-2600系列,内存控制器和PCI-E控制器集成于处理器内部带来高速的数据交换及处理能力,辅以高速QPI总线,具有非凡的性能表现。

与此同时,还具备虚拟化加速、加密算法加速、新一代睿频技术等多种优秀特性,满足用户对高性能、高效能的不断追求。

●丰富的磁盘选择。

用户可以根据业务的需求,在SATA、SAS中选择适合自己预算及应用需求的磁盘接口,并可灵活选择多种RAID实现方式,进一步提升系统的磁盘性能及数据安全性。

●强大的网络I/O能力。

集成2或4个GbE以太网控制器,具备高级网络加速技术和虚拟化优化技术,全面提升网络I/O能力的同时,对各种新兴应用提供良好支持。

另可选增配2个额外的10GbE以太网控制器,为海量数据处理提供充足带宽。

●完善的管理特性。

集成新一代服务器智能管理芯片,可实现与操作系统无关的复杂系统管理功能,配合浪潮睿捷服务器管理套件5.0版及新一代的UEFI智能固件,可极大简化用户的设备部署、管理和维护工作。

产品详述英信NF5280 M3的产品规格。

W27E520W-90资料

64K × 8 ELECTRICALLY ERASABLE EPROMPublication Release Date: 4/26/2000GENERAL DESCRIPTIONThe W27E520 is a high speed, low power Electrically Erasable and Programmable Read Only Memory organized as 65,536 × 8 bits. It includes latches for the lower 8 address lines to multiplex with the 8 data lines. To cooperate with the MCU, this device could save the external TTLcomponent, also cost and space. It requires only one supply in the range of 4.5V to 5.5V in normal read mode. The W27E520 provides an electrical chip erase function. It will be a great convenient when you need to change/update the contents in the device.FEATURES•High speed access time: 70/90 nS (max.)•Read operating current: 20 mA (max.)•Erase/Programming operating current30 mA (max.)•Standby current: 100 µA (max.)•Unregulated battery power supply range,4.5V to 5.5V• +13V erase and programming voltage•High Reliability CMOS Technology - 2K V ESD Protection- 200 mA Latchup Immunity •Fully static operation•All inputs and outputs directly LVTTL/CMOScompatible•Three-state outputs•Available p ackages: 20-pin TSSOP and 20-pin SOPFUNCTIONAL DESCRIPTIONRead ModeUnlike conventional UVEPROMs, which has CE and OE two control functions, the W27E520 has one OE/V PP and one ALE (address_latch_enable) control functions. The ALE makes lower address A[7:0] to be latched in the chip when it goes from high to low, so that the same bus can be used to output data during read mode. i.e. lower address A[7:0] and data bus DQ[7:0] are multiplexed. OE/V PP controls the output buffer to gate data to the output pins. When addresses are stable, the address access time (T ACC) is equal to the delay from ALE to output (T CE), and data are available at the outputs T OE PP, if T ACC and T CE timings are met.Erase ModeThe erase operation is the only way to change data from "0" to "1." Unlike conventional UVEPROMs, which use ultraviolet light to erase the contents of the entire chip (a procedure that requires up to half an hour), the W27E520 uses electrical erasure. Generally, the chip can be erased within 100 mS by using an EPROM writer with a special erase algorithm.There are two ways to enter Erase mode. One is to raise OE/V PP to V PE (13V), V DD = V DE (6.5V), A9 = V HH (13V), A10 = high A8&A11 = low, and all other address pins include AD[7:0] keep at fixed low or high. Pulsing ALE high starts the erase operation. The other way is somewhat like flash, by programming two consecutive commands into the device and then enter Erase mode. The two commands are loading Data = AA(hex) to Addr. = 5555(hex) and Data = 10(hex) to Addr. =2AAA(hex). Be careful to note that the ALE pulse widths of these two commands are different: One is 50uS, while the other is 100mS. Please refer to the Smart Erase Algorithm 1 & 2.Erase Verify ModeThe device will enter the Erase Verify Mode automatically after Erase Mode. Only power down the device can force the device enter Normal Read Mode again.Program ModeProgramming is the only way to change cell data from "1" to "0." The program mode is entered when OE/V PP is raised to V PP (13V), V DD = V DP (6.5V), the address pins equal the desired addresses, and the input pins equal the desired inputs. Pulsing ALE high starts the programming operation. Program Verify ModeThe device will enter the Program Verify Mode automatically after Program Mode. Only power down the device can force the device enter Normal Read Mode again.Erase/Program InhibitErase or program inhibit mode allows parallel erasing or programming of multiple chips with different data. When ALE low, erasing or programming of non-target chips is inhibited, so that except for the ALE and OE/V PP pins, the W27E520 may have common inputs.Standby ModeThe standby mode significantly reduces V DD current. This mode is entered when ALE and OE/V PP keep high. In standby mode, all outputs are in a high impedance state.System ConsiderationsPublication Release Date: 4/26/2000An EPROM's power switching characteristics require careful device decoupling. System designers are interested in three supply current issues: standby current levels (I SB ), active current levels (I DD ), and transient current peaks produced by the falling and rising edges of ALE Transient current magnitudes depend on the device output's capacitive and inductive loading. Proper decoupling capacitor selection will suppress transient voltage peaks. Each device should have a0.1 µF ceramic capacitor connected between its V DD and GND. This high frequency, low inherent-inductance capacitor should be placed as close as possible to the device. Additionally, for every eight devices, a 4.7 µF electrolytic capacitor should be placed at the array's power supply connectionbetween V DD and GND. The bulk capacitor will overcome voltage slumps caused by PC board trace inductances.TABLE OF OPERATING MODES(V PP = 13V, V PE = 13V, V HH = 12V, V DP = 6.5V, V DE = 6.5V, V DD = 5.0V, V DI = 5.0V, X = V IH or V IL )DC CHARACTERISTICSAbsolute Maximum RatingsNote: 1. Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability ofthe device.2. Minimum voltage is -0.6V DC which may undershoot to -2.0V for pulses of less than 20ns. Maximum output pin voltage is V DD +0.75V DC which may overshoot to +7.0V for pulses of less than 20ns.DC Erase Characteristics(T A = 25° C ±5° C, V DD = 6.5V ±0.25V)DD PP PP CAPACITANCE(V DD = 4.5V to 5.5V, T A = 25° C, f = 1 MHz)PARAMETERSYMBOL MAX.UNIT Input Capacitance C IN V IN = 0V 6pF Output Capacitance C OUTV OUT = 0V12pFPublication Release Date: 4/26/2000AC CHARACTERISTICSAC Test ConditionsPARAMETERCONDITIONSInput Pulse Levels0V/3V Input Rise and Fall Times10 nS Input and Output Timing Reference Level 1.5V/1.5VOutput LoadC L = 100 pF, I OH /I OL= -0.4 mA/2.1 mAREAD OPERATION DC CHARACTERISTICS(V DD = 4.5V to 5.5V, T A = 0 to 70° C)READ OPERATION AC CHARACTERISTICS(V DD = 4.5V to 5.5V, T A = 0 to 70° C)Publication Release Date: 4/26/2000DC PROGRAMMING CHARACTERISTICSAC PROGRAMMING/ERASE CHARACTERISTICSDD A DD PP PPTIMING WAVEFORMSPublication Release Date: 4/26/2000Timing Waveforms, continuedNote: First command Address = 5555(hex) with Data = AA(hex) Second command Address = 2AAA(hex) with Data = 10(hex)SMART PROGRAMMING ALGORITHM 1Publication Release Date: 4/26/2000SMART PROGRAMMING ALGORITHM 2SMART ERASE ALGORITHM 1Publication Release Date: 4/26/2000SMART ERASE ALGORITHM 2ORDERING INFORMATIONPART NO.ACCESS TIME (nS)OPERATING CURRENT MAX. (mA)STANDBY CURRENT MAX. (µA)PACKAGEW27E520W-70*7020100173mil TSSOP W27E520W-90*9020100173mil TSSOP W27E520S-70*7020100300mil SOP W27E520S-90*9020100300mil SOPNotes:1. The Part No is preliminary and might be changed after project is consoled.2. Winbond reserves the right to make changes to its products without prior notice.3. Purchasers are responsible for performing appropriate quality assurance testing on products intended for use in applications where personal injury might occur as a consequence of product failure.Publication Release Date: 4/26/2000PACKAGE DIMENSIONSVERSION HISTORYVERSIONDATE PAGEDESCRIPTIONA14/26/2000-Initial IssuedHeadquartersNo. 4, Creation Rd. III,Science-Based Industrial Park,Hsinchu, Taiwan TEL: 886-3-5770066FAX: 886-3-5796096/Voice & Fax-on-demand: 886-2-7197006Taipei Office11F, No. 115, Sec. 3, Min-Sheng East Rd.,Taipei, TaiwanTEL: 886-2-7190505FAX: 886-2-7197502Winbond Electronics (H.K.) Ltd.Rm. 803, World Trade Square, Tower II,123 Hoi Bun Rd., Kwun Tong,Kowloon, Hong Kong TEL: 852-********FAX: 852-********Winbond Electronics North America Corp.Winbond Memory Lab.Winbond Microelectronics Corp.Winbond Systems Lab.2727 N. First Street, San Jose,CA 95134, U.S.A.TEL: 408-9436666FAX: 408-5441798Note: All data and specifications are subject to change without notice.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。