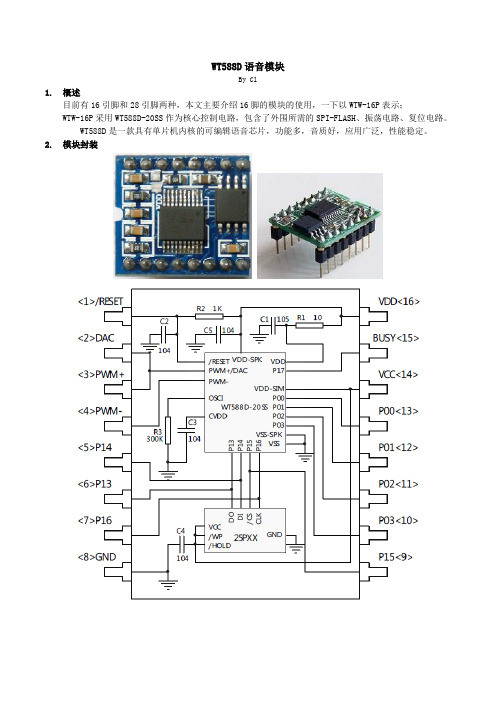

T85BDBDBB中文资料

WT588D芯片及模块详细资料

12.6.2、语音及命令码对应表 ....................................................................... 17

12.6.3、语音地址对应关系 ......................................................................... 17

12.6.4、三线串口控制时序 ......................................................................... 17

12.6.5、程序范例 ................................................................................. 18

13、控制时序 ............................................................................................. 19

13.1、控制时序框图 ................................................................................... 19

12.3、3×8 矩阵按键控制模式........................................................................... 13

12.4、并口控制模式 ................................................................................... 13

T85BDCDBB中文资料

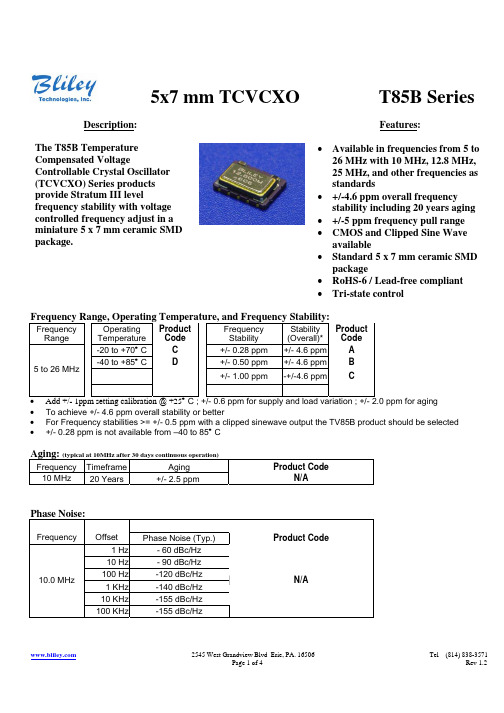

5x7 mm TCVCXO T85B Series Description:The T85B Temperature Compensated Voltage Controllable Crystal Oscillator (TCVCXO) Series products provide Stratum III level frequency stability with voltage controlled frequency adjust in a miniature 5 x 7 mm ceramic SMD package.Features: •Available in frequencies from 5 to26 MHz with 10 MHz, 12.8 MHz,25 MHz, and other frequencies asstandards•+/-4.6 ppm overall frequency stability including 20 years aging •+/-5 ppm frequency pull range •CMOS and Clipped Sine Wave available•Standard 5 x 7 mm ceramic SMD package•RoHS-6 / Lead-free compliant •Tri-state controlFrequency Range, Operating Temperature, and Frequency Stability:Frequency RangeOperatingTemperatureProductCodeFrequencyStabilityStability(Overall)*ProductCode -20 to +70° C C +/- 0.28 ppm +/- 4.6 ppm A-40 to +85° C D +/- 0.50 ppm +/- 4.6 ppm B+/- 1.00 ppm -+/-4.6 ppm C5 to 26 MHz•Add +/- 1ppm setting calibration @ +25° C ; +/- 0.6 ppm for supply and load variation ; +/- 2.0 ppm for aging•To achieve +/- 4.6 ppm overall stability or better•For Frequency stabilities >= +/- 0.5 ppm with a clipped sinewave output the TV85B product should be selected•+/- 0.28 ppm is not available from –40 to 85° CAging: (typical at 10MHz after 30 days continuous operation)Frequency Timeframe Aging Product Code10 MHz 20 Years +/- 2.5 ppm N/APhase Noise:Frequency Offset Phase Noise (Typ.) Product Code1 Hz - 60 dBc/Hz10 Hz - 90 dBc/Hz100 Hz -120 dBc/Hz1 KHz -140 dBc/Hz10 KHz -155 dBc/Hz10.0 MHz100 KHz -155 dBc/HzN/A2545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571 Page 1 of 4 Rev 1.2Supply Voltage (Vs):Power Supply (Vs) +3.3 Vdc +/-10%+5.0 Vdc +/-10%Product CodeCDCurrent Consumption:CMOS Clipped Sine WaveSupply Current 6 mA 3.5 mAEnvironmental:Storage Temperature-55 to +125° COutput Waveform:CMOS Clipped Sine WaveHCMOS Output Levels (15pf load) "0" < 0.1(Vs); "1" > 0.9(Vs) Output Level 0.8 V p-p min.Rise / Fall Time <10ns (10% to 90%) Duty Cycle 45 to 55% @ 50% Logic 1 Product Code A BPulling Range:Tuning Range None (TCXO)+/- 5 ppmProduct CodeAB*Note: Only +/- 5 ppm minimum pull is available as a TCVCXOOrdering Options:Operating Temperature Frequency Stability Supply VoltageOutput WaveformPulling RangeOperating Frequency C A C A AD B D B B Cxx.xxxxMHz 2545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571T85B C A C A B 10.0000MHzProduct Selection Code (refer to the above example):This part is RoHs compliant; -20 to +70° C, +/- 0.28 ppm, 3.3 volt CMOS output with +/- 5 ppm pull, 10MHz operating frequency** Not all combinations are available in this product.Outline Drawing & Pin Out:Page 2 of 4 Rev 1.22545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571 Page 3 of 4 Rev 1.2How to Order This Product:Contact Bliley Technologies with Product Selection Code from Ordering Options Section above.Attn:Sales @ BlileyFax: 814-833-2712Phone: 814-838-3571Email: info@Web: Date: ____________From:Name: ____________________ Company: ___________________Fax: ______________________ Phone: _____________________Email: _________________________________________________Quantities to Quote: ______________ Target Price: $___________Application / Reference #: _________________________________2545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571 Page 4 of 4 Rev 1.2。

多普达t8588使用说明书

色,或是外壳生锈、过热或发出异

味时,请勿使用。

V

请仔细阅读

警告:不正确地更换电池, 可能发生爆炸的危险。更换 时务必使用指定的电池。应 按照您当地的法规,将用 过的电池交到回收站或正 确弃置。

• 如误吞电池,请立刻就医。 • 电池漏液时:

• 请勿让漏出的液体直接接触身 体任何部位或衣物。如果已经接 触到,请立刻用干净的清水冲 洗沾到漏液之处,并寻求医疗 协助。

请务必将设备与其它磁性设 备(例如机械表或测量仪器) 之间保持适当距离。

针对心律调节器

心律调节器的功能可能会受

到设备的干扰。请务必将设 备与心律调节器保持适当距

XI

离。无论任何情况,请勿将

设备放在衬衫或外套前方的

口袋。

请仔细阅读

如需关于其它主动植入式医 疗器材的详细信息,请向医 生咨询,以便确认此类主动 植入式器材是否会受到磁性 的干扰。

目录

限制赔偿

依据现行法律允许的最大范围,任何情 况下,多普达与其供应商不对使用者或 第三方赔偿任何直接、间接、特殊、偶 然的、无法避免的损害或损失,包括但 不限于对在合约履行与侵权行为中可能

请仔细阅读

发生的收入损失、信誉损失、商业机会 产品到桌上型或笔记型电脑。在连接产

损失、资料损失、利益损失、履行或不 品至电脑之前,确认电脑已妥善接地。

免责条款

对于预装或捆绑于本产品中的任何游 戏、应用程序包括相应文件(以下简称 软件),或通过本产品取得的视听资 料、内容、服务以及相关文件资料,包 括但不限于任何图像、照片、动画、录 像、录音、音乐、文字,(以下简称服 务)皆由相应软件/服务提供商(以下 简称提供商)负责其合法、真实和准

确,并由提供商保证不违反国家法律、 法规、公共道德及侵犯任何第三方之合 法权益。提供商保证所提供软件和服务

TH2810B LRC 电桥说明书

在进行维护时应注意不要触碰带有 220V 强电的部件,防止电击危险。绝对禁止打开

机箱时进行一般的元件测试(除维修调整外)。 警告

不要在带电情况下插拔元器件及连接线,防止元器件或仪器不必要的损坏。不允许 连续不停地开关仪器,以免引起程序紊乱从而造成校正数据、用户存储数据的丢失。

TU

UT

1.3 工作环境 ................................................................................................................... 1-5

TU

UT

1.3.1 环境温度与湿度 ............................................................................................. 1-5

TU

UT

2.2.3 测试信号电平 ................................................................................................ 2-4

TU

UT

2.2.4 显示方式 ...................................................................................................... 2-4

TU

UT

1.2.8 测试速度 ........................................................................................................ 1-4

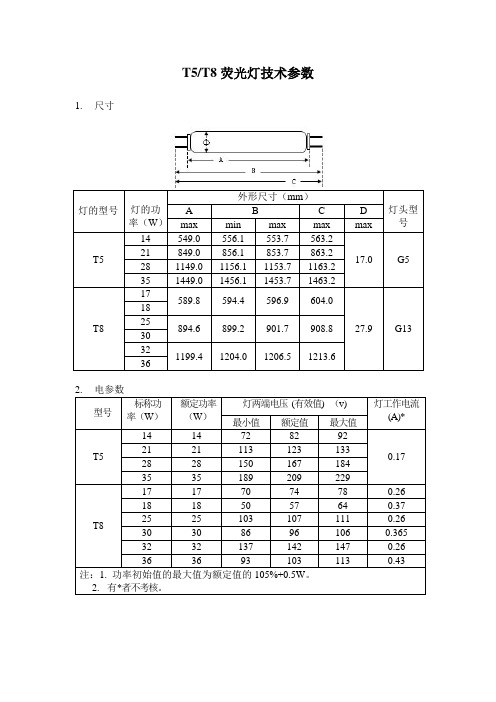

(可直接使用)T5T8荧光灯技术参数.doc

25

1600

1750

1750

1700

1900

1900

32

2250

2400

2400

2400

2500

2500

功率(W)

卤粉

三基色(80)

18

960

1110

1150

1250

1300

1300

30

1720

2025

2100

2100

2250

2250

36

2400

2650

2760

3000

3100

3100

注:光通量最小值为额定值的92%。

14

14

72

82

92

0.17

21

21

113

123

133

28

28

150

167

184

35

35

189

209

229

T8

17

17

70

74

78

0.26

18

18

50

57

64

0.37

25

25

103

107

111

0.26

30

30

86

96

106

0.365

32

32

137

142

147

0.26

36

36

93

103

113

0.43

注:1.功率初始值的最大值为额定值的105%+0.5W。

2.有*者不考核。

3.光通量

型号

功率(W)

70系列

用户手册

dopod C858 用户手册2006.12多普达通讯有限公司敬告:在操作本机之前请阅读下述内容在提示不能使用手机的场合,如医院、飞机机舱内、加油站、怕无线干扰的地方,请您关闭本设备!在飞机上除了打开飞行模式外,请关闭整个设备的电源。

插入SIM 卡时请确保外接电源已经断开,且SIM 卡放置到位。

第一次充电请充满8小时。

在充电的过程中,请不要从手机上取下电池,以防损伤设备。

本机型不具有防水功能,请您注意防水,保持手机的干燥。

如果自行打开或者损伤外壳将不再享受保修服务。

请使用由多普达公司指定的附件和认可的第三方软件,否则如果设备出现问题多普达公司将不承担任何责任。

请注意保护好手机屏幕,防止磨损或挤伤。

此类损伤均被认为是人为损坏。

请及时备份数据!多普达公司不承担因产品故障导致信息丢失而造成的一切直接或间接损失。

尤其在更换电池前更加需要备份数据。

本设备中包含有一个锂电池电池。

如果电池处理不当,将会有着火和燃烧的危险。

不要分解、挤压、刺穿电池,不要短路电池外部的接头,更不要将其投入火中或者水中。

不要试图打开或者维修该电池,只能使用产品指定的电池来进行更换。

请正确处理电池不要随意丢弃。

由于软件版本更新而造成界面和功能变更,恕不另行通知。

友情提示:亲爱的用户,由于多普达智能手机内含一套完整的电脑系统,类似于个人电脑的系统架构和运行规则。

1.充足的系统内存,将有助于手机良好高效的运行,所以建议您每天至少重新启动手机一次,以彻底清空内存,恢复系统至最佳状态。

2.请正确合理地使用您的手机内存,建议您不要同时运行过多的程序,否则将使手机运行速度变慢。

如发生此类情况,建议您重新启动手机,即可恢复如初。

注意:对于预装或捆绑于本机中的任何游戏、应用程序包括相应文件(以下简称软件),或通过本机取得的视听资料、内容、服务以及相关文件资料,包括但不限于任何图像、照片、动画、录像、录音、音乐、文字,(以下简称服务)皆由相应软件/服务提供商(以下简称提供商)负责其合法、真实和准确,并由提供商保证不违反国家法律、法规、公共道德及侵犯任何第三方之合法权益。

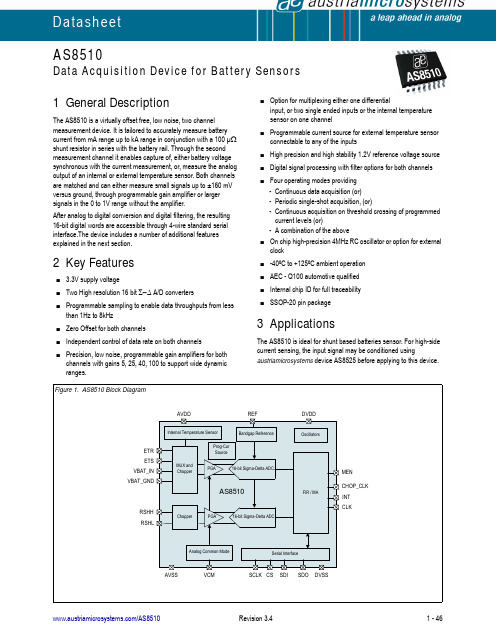

AS8510 DB;中文规格书,Datasheet资料

AS8510Data Acquisition Device for Battery SensorsDatasheet1 General DescriptionThe AS8510 is a virtually offset free, low noise, two channel measurement device. It is tailored to accurately measure battery current from mA range up to kA range in conjunction with a 100 µΩ shunt resistor in series with the battery rail. Through the second measurement channel it enables capture of, either battery voltage synchronous with the current measurement, or, measure the analog output of an internal or external temperature sensor. Both channels are matched and can either measure small signals up to ±160 mV versus ground, through programmable gain amplifier or larger signals in the 0 to 1V range without the amplifier.After analog to digital conversion and digital filtering, the resulting 16-bit digital words are accessible through 4-wire standard serial interface.The device includes a number of additional features explained in the next section.2 Key Features3.3V supply voltageTwo High resolution 16 bit Σ−Δ A/D convertersProgrammable sampling to enable data throughputs from lessthan 1Hz to 8kHzZero Offset for both channelsIndependent control of data rate on both channels Precision, low noise, programmable gain amplifiers for bothchannels with gains 5, 25, 40, 100 to support wide dynamic ranges.Option for multiplexing either one differentialinput, or two single ended inputs or the internal temperature sensor on one channelProgrammable current source for external temperature sensorconnectable to any of the inputsHigh precision and high stability 1.2V reference voltage source Digital signal processing with filter options for both channels Four operating modes providing-Continuous data acquisition (or)-Periodic single-shot acquisition, (or)-Continuous acquisition on threshold crossing of programmed current levels (or)-A combination of the aboveOn chip high-precision 4MHz RC oscillator or option for external clock-40ºC to +125ºC ambient operation AEC - Q100 automotive qualified Internal chip ID for full traceability SSOP-20 pin package3 ApplicationsThe AS8510 is ideal for shunt based batteries sensor. For high-side current sensing, the input signal may be conditioned usingaustriamicrosystems device AS8525 before applying to this device.Contents1 General Description (1)2 Key Features (1)3 Applications (1)4 Pin Assignments (4)4.1 Pin Descriptions (4)5 Absolute Maximum Ratings (6)6 Electrical Characteristics (7)6.1 Operating Conditions (7)6.2 DC/AC Characteristics for Digital Inputs and Outputs (7)6.3 Detailed System and Block Specifications (8)6.3.1 Electrical System Specifications (8)6.4 Current Measurement Ranges (across 100µΩ shunt resistor) (9)6.4.1 Differential Input Amplifier for Current Channel (10)6.4.2 Differential Input Amplifier for Voltage Channel (11)6.4.3 Sigma Delta Analog to Digital Converter (12)6.4.4 Bandgap Reference Voltage (12)6.4.5 Internal (Programmable) Current Source for External Temperature Measurement (13)6.4.6 CMREF Circuit (VCM) (14)6.4.7 Internal AVDD Power-on Reset (14)6.4.8 Internal DVDD Power-on Reset (14)6.4.9 Low Speed Oscillator (14)6.4.10 High Speed Oscillator (15)6.4.11 External Clock (15)6.4.12 Internal Temperature Sensor (15)6.5 System Specifications (16)7 Detailed Description (17)7.1 Current Measurement Channel (17)7.2 Voltage/Temperature Measurement Channel (17)7.3 Digital Implementation of Measurement Path (18)7.4 Modes of Operation (18)7.4.1 Normal Mode 1 (NOM1) (19)7.4.2 Normal Mode 2 (NOM2) (20)7.4.3 Standby Mode1 (SBM1) (21)7.4.4 Standby Mode2 (SBM2) (21)7.5 Reference-Voltage (22)7.6 Oscillators (22)7.7 Power-On Reset (22)7.8 4-Wire Serial Port Interface (22)7.8.1 SPI Frame (23)7.8.2 Write Command (23)7.8.3 Read Command (24)7.8.4 Timing (25)7.8.5 SPI Interface Timing (26)7.9 Control Register (27)7.9.1 Standby Mode - Power Consumption (38)7.9.2 Initialization Sequence at Power ON (38)7.9.3 Soft-reset Using Bit D[7] of Reset Register 0x09 (39)7.9.4 Reconfiguring Gain Setting of PGA (40)7.9.5 Configuring the Device During Normal Mode (40)7.10 Low Side Current Measurement Application (41)8 Package Drawings and Markings (42)8.1 Recommended PCB Footprint (43)9 Ordering Information (45)4 Pin AssignmentsFigure 2. Pin Assignments (Top View)4.1 Pin DescriptionsTable 1. Pin DescriptionsPin NumberPin Name Pin Type Description1RSHH Analog inputPositive Differential input for current channel 2RSHL Negative differential input for current channel3REFAnalog outputInternal reference voltage to sigma-delta ADC; connect 100nF to AVSS from this pin.4VCM Common Mode voltage to the internal measurement path; connect 100nF to AVSS from this pin.5AVDD Supply pad +3.3V Analog Power-supply 6AVSS 0V Power-supply analog 7ETR Analog input Voltage channel single ended input 8ETS 9VBAT_IN Battery voltage (high) input 10VBAT_GNDBattery voltage (low) input11CS Digital input with pull-up Chip select with an internal pull-up resistor (SPI Interface)12SCLK Digital input Clock signal (SPI Interface)13SDODigital outputSerial Data Input (SPI Interface)14DVSS Supply pad0V Digital Ground 15DVDD+3.3V Digital Supply16CHOP_CLKDigital outputChop Clock used in High side measurements to synchronize external chopper.(As an example, when AS8525 is used to condition the input signal to the input range of AS8510, the chop clock is used by AS8525.)17MENDigital output issued during the Standby Mode (SBM) to signal the short duration of data sampling. This signal is useful in the case of a High Side Measurement application.(For example: This signal is used by AS8525 device to wake-up and enable the measurement path.)18SDI Digital input Data signal (SPI Interface)19CLK Digital I/OBy default this pin is the internal clock output which can be used by a Microcontroller. The internal clock may also be disabled as an output by programming Register 08. To use an external Clock, Register 08 has to be programmed. 20INTDigital outputActive High Interrupt to indicate data is readyTable 1. Pin DescriptionsPin NumberPin Name Pin Type DescriptionDatasheet - A b s o lu t e M a x im u m R a ti n g s5 Absolute Maximum RatingsStresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 7 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Table 2. Absolute Maximum RatingsParameter Min Max Units NotesElectrical ParametersDC supply voltage (AVDD and DVDD)-0.35VInput voltage (V IN)-0.3AVDD + 0.3DVDD + 0.3VInput current (latchup immunity)(I SCR)-100100mA AEC - Q100 - 004 Electrostatic DischargeElectrostatic discharge (ESD) all pins±2kV AEC - Q100 - 002 Continuous Power DissipationTotal power dissipation(all supplies and outputs) (P t)50mW SSOP20 in still air, soldered on JEDEC standard board @ 125º ambient, static operation with no time limitTemperature Ranges and Storage ConditionsStorage temperature (T STRG)-50125ºCJunction temperature (T J)130ºCThermal resistance (R thJC)80K/W JEDEC standard test board, 0 air velocityPackage body temperature (T BODY)260ºCNorm: IPC/JEDEC J-STD-020The reflow peak soldering temperature (body temperature) is specified according IPC/ JEDEC J-STD-020 “Moisture/Reflow Sensitivity Classification for Nonhermetic Solid StateSurface Mount Devices”.The lead finish for Pb-free leaded packages ismatte tin (100% Sn).Humidity non-condensing585%6 Electrical Characteristics6.1 Operating Conditions6.2 DC/AC Characteristics for Digital Inputs and OutputsAll pull-up and pull-down have been implemented with active devices. SDO has been measured with 10pF load.Table 3. Operating Conditions Symbol ParameterConditions Min Max Units AVDD Positive analog supply voltage3.0 3.6V AVSS 0V Ground00V A - D Difference in analog and digital supplies0.1V DVDD Positive digital supply 2.97 3.63V DVSS 0V Digital Ground 00V T AMB Ambient temperature -40125ºC I SUPP Supply current 5.5mA f CLKSystem clock frequency11.Nominal clock frequency from external or internal oscillator.4.096MHzTable 4. INTSymbol Parameter ConditionsMin TypMax Units I LEAK Tri-state leakage current -1+1µA V OH High level output voltage 2.5V V OL Low level output voltage0.4V I OOutput Current4mATable 5. CS InputSymbol Parameter ConditionsMin TypMaxUnits V IH High level input voltage 2.0V V IL Low level input voltage 0.8V I LEAK Input leakage current -1+1µA Ipu Pull up currentCS pulled to DV DD = 3.3V-150-15µATable 6. SDISymbol Parameter ConditionsMin TypMaxUnits V IH High level input voltage 2.0V V IL Low level input voltage 0.8V I LEAKInput leakage current-1+1µATable 7. SDO OutputSymbol Parameter Conditions Min Typ Max Units V OH High level output voltage Isource = 8mA 2.5V V OL Low level output voltage Isink = 8mA 0.4VI o Output Current8mA Table 8. CHOP_CLK OutputSymbol Parameter Conditions Min Typ Max Units V OH High level output voltage 2.5V V OL Low level output voltage0.4VI o Output Current4mA Table 9. CLK I/O with Input Schmitt Trigger and Output BufferSymbol Parameter Conditions Min Typ Max Units V IH High level input voltage DV DD = 3.3V 2.4V V IL Low level input voltage DV DD = 3.3V 1.0VI LEAK Input leakage current-1+1µAI PD Pull down current CLK pulled to DVSS10100µAI o Output Current4mAV OH High level output voltage 2.5V V OL Low level output voltage0.4V Table 10. SCLK with Input Schmitt TriggerSymbol Parameter Conditions Min Typ Max Units V IH High level input voltage DV DD = 3.3V 2.4V V IL Low level input voltage DV DD = 3.3V 1.0VI LEAK Input leakage current-1+1µA Table 11. MEN OutputSymbol Parameter Conditions Min Typ Max Units V OH High level output voltage 2.5V V OL Low level output voltage0.4VI O Output Current2mA6.3 Detailed System and Block Specifications6.3.1 Electrical System Specifications6.4 Current Measurement Ranges (across 100µΩ shunt resistor)Note:The Data Rate at the output can be calculated according to the formula:fsout=2*fchop /R2 (R2 is down sampling ratio taking values 1, 2, 4 up to 32768 as powers of 2)Table 12. Electrical System SpecificationsSymbol ParameterMinTyp Max Units NotesIDD NOM Current consumption normal mode 3 5.5mA IDD SBMCurrent consumption standby mode40µAAverage of NORMAL Mode Power consumption over a period of 10sec when the device is in STANDBY ModeTable 13. Current Measurement RangesSymbol ParameterImax [A]Vsh [mV]PGA Gain Nominal Data Rate (f OUT )V INADC 1[mV]1.V INADC = Vsh * Gain, gain deviations to be considered according to Table 15 and Table 16.PSR 2[dB]2.AVDD, DVDD of 3.3V with ±5% variation.I10 Input current range of 10A in NOM ±10±1100@ 1 kHz ±10060I200Input current range of 200A in NOM ±200±2040@ 1 kHz ±80060I400Input current range of 400A in NOM ±400±4025@ 1 kHz ±100060I1500Input current range of 1500A in NOM ±1500±1505@ 1 kHz ±75060I1Input current range of 1A in SBM33.For low power current monitoring, single shot measurement is performed with internal oscillator.±1±0.1100@ 1 Hz ±1060I10Input current range of 10A in SBM3±10±1100@ 1 Hz ±10060I200Input current range of 200A in SBM3±200±2040@ 1 Hz±80060Table 14. Valid Combinations of the Chopper Clock, Oversampling Clock and Decimation RatiosOver Sampling FrequencyChopper FrequencyDecimation Ratio1MHz 2kHz 642MHz 2kHz 642MHz 2kHz 1282MHz4kHz646.4.1 Differential Input Amplifier for Current ChannelNotes:1. Leakage test accuracy is limited by tester resource accuracy and tester hardware.2. For gain 100 PGA input common mode is 0V and the minimum supply is3.15V.3. The measurement ranges are referred only by the gain of input amplifier, while other parameters such as bandwidth etc. are pro-grammed independently.4. This parameter is not measured directly in production. It is measured indirectly via gain measurements of the whole path. It is guaran-teed by design.5. Pole frequency of input amplifier changes with GAIN. The number is valid for the gain at G1, while the bandwidth will be higher for other ranges. This parameter is not measured in production.6. Based on device evaluation. Not tested.7. These offsets are cancelled if chopping enabled (default).8. Noise density calculated by taking system bandwidth as 150Hz.9. Refer to Measurement Ranges shown in Table 13.10. No impact on the measurement path. If the chopping is enabled, both the offset and offset drift will be eliminated.11. For negative input voltages up to -160mV below ground, Input leakage is typically -20nA @ 65ºC due to forward conductance of protection diode.Table 15. Differential Input Amplifier for Current ChannelSymbol Parameter Conditions Min Typ Max Units V IN _AMP Input voltage range RSHH and RSHL-160+160mV I IN _AMP Input current1, 11RSHH and RSHL@ +160mV input voltage at 125ºC with PGA-50250nA ICM Absolute input voltage range2-160+300mVG = G1Gain1 3, 4, 9I10100G = G2Gain2 3, 4, 9I20040G = G3Gain3 3, 4, 9I40025G = G4Gain43, 4, 9I15005e Gain deviation i = 1, 2, 3, 40.9 * Gi 1.1 * Gif P _AMP Pole frequency4, 515kHzεT1Gain drift with temperature 6-20ºC to +65ºCGain 5, 25, referenced to roomtemperature±0.3%V OSDRIFT Offset drift with temperature 7, 10350µVVos Input referred offset7, 10After trim,for temperature range -20 to +65ºC350µV Vos_ch Chopping enabled0LSB VNdin Noise density4, 825nV/√Hz THD Total harmonic distortion For 150 Hz input signal 70dB分销商库存信息: AMSAS8510 DB。

TLC085中文资料

元器件交易网

TLC080, TLC081, TLC082, TLC083, TLC084, TLC085, TLC08xA FAMILY OF WIDEĆBANDWIDTH HIGHĆOUTPUTĆDRIVE SINGLE SUPPLY OPERATIONAL AMPLIFIERS

Copyright 2000−2004 Texas Instruments Incorporated

1

元器件交易网

SLOS254D − JUNE 1999 − REVISED FEBRUARY 2004

TLC080, TLC081, TLC082, TLC083, TLC084, TLC085, TLC08xA FAMILY OF WIDEĆBANDWIDTH HIGHĆOUTPUTĆDRIVE SINGLE SUPPLY OPERATIONAL AMPLIFIERS

−40°C to 125°C

† This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., TLC084CDR).

Panasonic Toughbook T8 商品说明书

Windows®. Life without Walls™. Panasonic recommends Windows 7. THE TOUGHBOOK T8Durable, long-lasting battery with touchscreen LCD.In your world, your workday is ever-lasting. Presenting the next-generation mobile computing solution for people on the move. The business-rugged Toughbook® T8 is ultra-portable and weighs in at a lightweight 3.3 lbs., yet is rugged enough to withstand the drops and bangs of your busy day. Add to that increased security and remote management with an Intel® Core®2 vPro™ processor, easy-to-use circular scrolling, a spill-resistantkeyboard and touchpad, Wi-Fi, optional embedded Gobi™ mobile broadband and long battery life, and you get a laptop that lets you do more than you ever expected. Now if we could only lighten your workload.sOfTwarE• Genuine Windows® 7 Professional1• S etup, Diagnostics, PC Information Viewer, Online Reference Manual, Adobe®Reader, Hard Disk Data Erase Utility, Recovery DVD, Display Image Rotation CPU• I ntel® Core™2 SU9600 vPro™ Processor– Processor speed 1.6GHz– 3MB L2 cache– 800MHz FSBsTOraGE & MEMOrY• 2GB SDRAM (DDR2-667) standard, expandable to 4GB2(PC2-5300 memory is required)• 250GB hard drive (shock-mounted, flex-connect and removable)3 DIsPLaY• 12.1" 1024 x 768 XGA touchscreen LCD• External video support up to 1920 x 1200 at 16.7 million colors• Intel® GS45 (GMA 4500MHD video controller), max. 1024MB UMA VRAM on XP4• Anti-glare screen treatmentaUDIO• Intel® high-definition audio compliant• Integrated speaker• Convenient keyboard volume controls (Fn+F5/F6 keys)KEYBOarD & INPUT• Touchscreen LCD• Integrated stylus holder• 83-key with dedicated Windows® key• Electrostatic touchpad with circular scrollingEXPaNsION sLOTs• PC card type II x 1• SD card (SDHC)INTErfaCE• Docking connector 50-pin• External video D-sub 15-pin• Headphones/speaker Mini-jack stereo• Microphone/line in Mini-jack stereo• USB 2.0 (x 3) 4-pin• 10/100/1000 Ethernet RJ-45• 56K Modem RJ-11wIrELEss• Optional integrated Gobi™ mobile broadband• Intel® Wireless WiFi Link 5100 802.11a/b/g/draft-n• Bluetooth® v2.1 + EDR (Class 1); not available with fingerprint reader• S ecurity– Authentication: LEAP, WPA, 802.1x, EAP-TLS, EAP-FAST, PEAP– Encryption: CKIP, TKIP, 128-bit and 64-bit WEP, Hardware AES• Slide on/off switchPOwEr sUPPLY• Lithium ion battery pack (typical 5800mAh, minimum 5400mAh)• Battery operation: 5.5-8 hours5• Battery charging time: 5 hours off, 6.5 hours on5• A C Adapter: AC 100V-240V 50/60Hz, auto sensing/switching worldwidepower supply• Pop-up, on-screen battery status reportingPOwEr MaNaGEMENT• Suspend/Resume Function, Hibernation, Standby, ACPI BIOS• Economy modesECUrITY fEaTUrEs• Password Security: Supervisor, User, Hard Disk Lock• Cable lock slot• Trusted platform module (TPM) security chip v.1.2• Computrace® theft protection agent in BIOS6• Optional fingerprint reader (eliminates Bluetooth®)warraNTY• 3-year limited warranty, parts and laborDIMENsIONs & wEIGHT• 8.4"(L) x 10.7"(W) x 1.4"/1.9"(H) front/rear• 3.3 lbs.THE PaNasONIC TOUGHBOOK T8.1.800.662.3537 / /toughbookFinancing options now available from Panasonic Finance Solutions;please call number above for more details.Panasonic is constantly enhancing product specifications and accessories. Specifications subject to change without notice. Trademarks are property of their respective owners. ©2010 Panasonic Corporation of North America. All rights reserved.■ Touchscreen LCD■ Magnesium Alloy Case with Rubber Hand Strap■ Drop and Spill-resistant■ Circular Scrolling■ Mobile Broadband-ready DesignINTEGraTED OPTIONs7• Gobi™ mobile broadband (EV-DO Rev. A, HSPA)• F ingerprint reader (eliminates Bluetooth®)aCCEssOrIEs7• AC Adapter (3-pin) CF-AA1633AM• Lithium Ion Battery Pack CF-VZSU51W• 4-Bay Battery Charger CF-VCBT71U• LIND Car Adapter 120W CF-LNDDC120• LIND Car Adapter 120WMounting Bracket CF-LNDBRK120• LIND Car/AC Adapter 90W(with USB port) CF-LNDACDC90• LIND Shutdown Timer CF-LNDLPT• I nfoCase Always-on T8 Case TBCTSAOCS-P• I nfoCase Business-ruggedTop-loading Case TBCBRTL-P• I nfoCase ComUniversal Roller TBCRLR-P• I nfoCase Backpack TBCBPK-P• E xternal USB Combo Drive(DVD-ROM/CD-RW) CF-VDRRT3U• Memory Cards– 1GB DDR2 CF-TTWMBA801GE– 2GB DDR2 CF-TTWMBA802GE• Mini Dock Box Replicator CF-VEBU05BU• 12.1" LCD Protector Film CF-VPF02U• R eplacement Stylus withTether Hole CF-VNP003UPlease consult your reseller or Panasonic representative before purchasing.A full set of Windows XP drivers are available at /toughbook/support. Total usable memory will be less depending upon actual system configuration.H ard drive removal should only be attempted by a technician withthe proper equipment. 1GB = 1,000,000,000 bytes.M ax with standard RAM. The size of the VRAM cannot be set by the userand varies by operating system as well as size of RAM. Vista max. VRAMis 797MB with 2GB of memory, or 1551MB with 4GB of memory.B attery performance features such as charge time and life span canvary according to the conditions under which the computer and batteryare used. Battery operation and recharge times will vary based on many factors, including screen brightness, applications, features, power management, battery conditioning and other customer preferences.R equires software and activation to enable theft protection.A ccessories and Integrated Options may vary depending on yournotebook configuration.ssT8 11/10。

835B中文资料

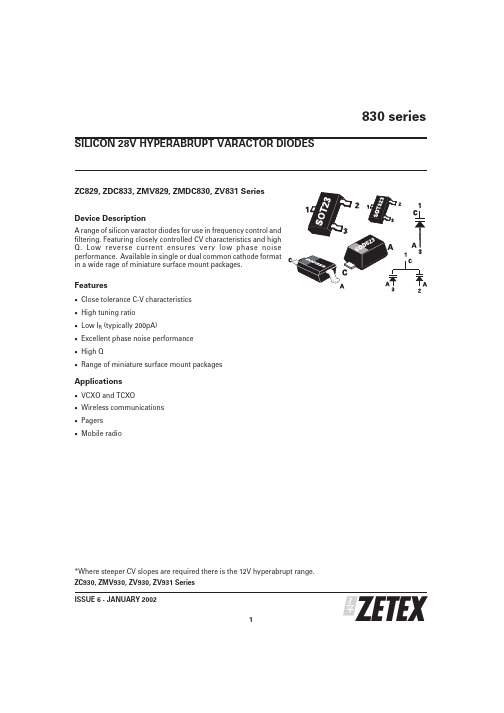

ZC829, ZDC833, ZMV829, ZMDC830, ZV831 Series Device DescriptionA range of silicon varactor diodes for use in frequency control and filtering.Featuring closely controlled CV characteristics and high Q.Low reverse current ensures very low phase noise performance.Available in single or dual common cathode format in a wide rage of miniature surface mount packages.Features·Close tolerance C-V characteristics ·High tuning ratio ·Low I R (typically 200pA)·Excellent phase noise performance ·High Q·Range of miniature surface mount packagesApplications·VCXO and TCXO·Wireless communications ·Pagers ·Mobile radio*Where steeper CV slopes are required there is the 12V hyperabrupt range.ZC930, ZMV930, ZV930, ZV931 Series 830 seriesISSUE 6 - JANUARY 20021SILICON 28V HYPERABRUPT VARACTOR DIODES830 seriesISSUE 6 - JANUARY 20022PARTCapacitance (pF)V R =2V,f=1MHzMin Q V R =3V f=50MHzCapacitance RatioC 2/C 20at f=1MHzMIN.NOM.MAX.MIN.MAX.829A 7.388.29.02250 4.3 5.8829B 7.798.28.61250 4.3 5.8830A 9.010.011.0300 4.5 6.0830B 9.510.010.5300 4.5 6.0831A 13.515.016.5300 4.5 6.0831B 14.2515.015.75300 4.5 6.0832A 19.822.024.2200 5.0 6.5832B 20.922.023.1200 5.0 6.5833A 29.733.036.3200 5.0 6.5833B 31.3533.034.65200 5.0 6.5834A 42.347.051.7200 5.0 6.5834B 44.6547.049.35200 5.0 6.5835A 61.268.074.8100 5.0 6.5835B 64.668.071.4100 5.0 6.5836A 90.0100.0110.0100 5.0 6.5836B95.0100.0105.0100 5.06.5TUNING CHARACTERISTICS at Tamb = 25°CPARAMETER SYMBOLMAX UNIT Forward currentI F 200mA Power dissipation at T amb =25ЊC SOT23P tot 330mW Power dissipation at T amb =25ЊC SOD323P tot 330mW Power dissipation at T amb =25ЊC SOD523P tot250mW Operating and storage temperature range-55to +150ЊCABSOLUTE MAXIMUM RATINGSPARAMETERCONDITIONS MIN.TYP.MAX.UNIT Reverse breakdown voltage I R =10uA 25V Reverse voltage leakageV R =20V 0.220nA Temperature coefficient of capacitanceV R =3V,f =1MHz300400ppCm/ЊCELECTRICAL CHARACTERISTICS at Tamb = 25°C830 seriesTYPICAL CHARACTERISTICSISSUE 6 - JANUARY 20023830 seriesISSUE 6 - JANUARY 20024O R D E R C O D E S A N D P A R T M A R K I N GR E E L C O D ER E E L S I Z ET A P E W I D T HQ U A N T I T Y P E R R E E LT A7i n c h (180m m )8m m3000T C13i n c h (330m m )8m m 10000T A P E A N D R E E L I N F O R M A T I O NT h e o r d e r c o d e s a r e s h o w n a s T A w h i c h i s f o r 7i n c h r e e l s .F o r 13i n c h r e e l s s u b s t i t u t e T C i n p l a c e o f T A i n t h e o r d e r c o d e .ISSUE 6 - JANUARY 20025830 seriesSOT23 PACKAGE DIMENSIONSSOD323 PACKAGE DIMENSIONSZetex plcFields New Road ChaddertonOldham, OL9 8NP United KingdomTelephone (44) 161 622 4422Fax: (44) 161 622 4420Zetex GmbHStreitfeldstraße 19D-81673 München GermanyTelefon: (49) 89 45 49 49 0Fax: (49) 89 45 49 49 49Zetex Inc700 Veterans Memorial Hwy Hauppauge, NY11788USATelephone: (631) 360 2222Fax: (631) 360 8222Zetex (Asia) Ltd3701-04Metroplaza, Tower 1Hing Fong Road Kwai Fong Hong KongTelephone: (852) 26100 611Fax: (852) 24250 494These offices are supported by agents and distributors in major countries world-wide.This publication is issued to provide outline information only which (unless agreed by the Company in writing)may not be used,applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned.The Company reserves the right to alter without notice the specification,design,price or conditions of supply of any product or service.For the latest product information,log on to©Zetex plc 2001830 series6ISSUE 6 - JANUARY 2002DIM MILLIMETRES MIN.MAX A ᎏ0.800A10.0000.100A20.6000.800b10.1600.300c 0.0800.220D 0.7000.900E 1.500 1.700E1 1.100 1.300L 0.2000.400L10.1700.230⍜1Њ4Њ10ЊSOD523 PACKAGE DIMENSIONSSOD323 PACKAGE DIMENSIONS。

ART T8 八通道变压器隔离器说明书

ART T8Universal Eight Channel Transformer IsolatorIMPORTANT SAFETY INSTRUCTION – READ FIRSTThis symbol, wherever it appears, alerts you to important operating and maintenanceinstructions in the accompanying literature. Please Read the manual.Read instructions:Retain these safety and operating instructions for future reference. Heed all warnings printed here and on the equipment. Follow the operating instructions printed in this user guide.Do not open:There are no user serviceable parts inside. Refer any service work to qualified technical personnel only.Moisture:To reduce the risk of fire or electrical shock do not expose the unit to rain, moisture or use in damp or wet conditions. Do not place container of liquid on it, which may spill into any openings.Environment:Protect from excessive dirt, dust, heat, and vibration when operating and storing. Avoid tobacco ash, drink spillage and smoke, especially that associated with smoke machines.Handling:To prevent damage to the controls and cosmetics avoid rough handling and excessive vibration. Protect the controls from damage during transit. Use adequate padding if you need to ship the unit. To avoid injury to yourself or damage to the equipment take care when lifting, moving or carrying the unit. Servicing:Refer servicing to qualified technical personnel only.INTRODUCTIONThank you for purchasing the ART T8 Universal Eight Channel Transformer Isolator. This is a rock solid, road-worthly 8 channel transformer isolator. “Hum” in an audio system is often caused by loop effects which act like antennas. These loops can easily pick up a 60Hz ( or higher harmonic) hum created by electrical wiring. Typically, these loops are connected via grounds, more commonly called “ ground loops”. The safest way to eliminate unwanted noise is with the T8.The T8 is a quality totally passive audio interface that uses eight high performance low distortion transformers to totally separate input and output signal grounds, thereby isolating two systems and reducing hum and ground-loop noise. The T8’s audio transformers have an extremely flat and wide frequency response and can handle high signal levels while maintaining an isolated balanced output. This gives the T8 a very clean and neutral sound with a wide variety of signal sources. The transformers are wound for 1:1 unity gain and are designed for use with impedances from 600 Ohms to 100k Ohms.What further sets the T8 apart from other lesser isolation boxes is its connection versatility. We have provided XLR, ¼” phone, and RCA type phono connections on all inputs and outputs. This allows it to easily fit into virtually any audio system and be the clean patch point between all types of systems. All ¼” and RCA phono jacks are on the front and all XLR jacks are on the rear. You can use any combination and since the jacks are directly paralleled you can also use them as signal taps or as a signal splitter.The T8’s mounting ears are reversible so you can have either the ¼” and RCA phono jacks on the front or the XLRs on the front. This maximizes flexibility in cabling your system. Whether you need an interface between a computer based audio workstation and your monitor system, isolation on long cable runs in a fixed installation, isolation of multiple signal sources from your recording equipment, or in many cases, just a safer connection between two audio systems, the T8 can accommodate. The 19” 1U black all steel case and its all passive design allow the T8 to provide years of trouble free service in Live Sound, Permanent/Fixed Install, D.J., and virtually any PA application. It is equally valuable in a variety of studio and AV applications. Its full feature set, rugged construction, and high-end specifications make the T8 the obvious choice.APPLICATIONS:LIVE SOUND, D.J.Long unbalanced cables are more susceptible to picking up hum , Using the T8 to help balance these and eliminate any hum.When DJs set up for different jobs there is a potential to pick up hum due to the differences in house wiring, using a T8 Eliminates the potential for hum.MIXERS/FIXED INSTALLS/RECORDING/BROADCAST/VIDEOUse the T8 to eliminate ground loops when using multiple mixers.Taking mixer unbalanced sends and achieving true balanced monitor outputs.Using the T8 between video/broadcast rigs eliminates the potential for hum and loop noise.POWER AMPLIFIERSHum, ground loop noise can be created between multiple amplifiers. This can be eliminated using the T8 on each of the amplifiers input lines.COMPUTERSUsing a T8 can eliminate unwanted ground loops created between the computers and your audio input equipment.You can also use the T8 to balance the unbalanced inputs and outputs from your computers sound card.WARRANTY INFORMATIONLimited WarrantyApplied Research and Technology will provide warranty and service for this unit in accordance with the following warrants:Applied Research and Technology, (A R T) warrants to the original purchaser that this product and the components thereof will be free from defects in workmanship and materials for a period of three years from the date of purchase. Applied Research and Technology will, without charge, repair or replace, at its option, defective product or component parts upon prepaid delivery to the factory service department or authorized service center, accompanied by proof of purchase date in the form of a valid sales receipt.Exclusions:This warranty does not apply in the event of misuse or abuse of the product or as a result of unauthorized alterations or repairs. This warranty is void if the serial number is altered, defaced, or removed.A R T reserves the right to make changes in design or make additions to or improvements upon this product without any obligation to install the same on products previously manufactured.A R T shall not be liable for any consequential damages, including without limitation damages resulting from loss of use. Some states do not allow limitations of incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific rights and you may have other rights, which vary, from state to state.For units purchased outside the United States, an authorized distributor of Applied Research and Technology will provide service.SERVICEThe following information is provided in the unlikely event that your unit requires service.1) Be sure that the unit is the cause of the problem. Check to make sure that all cables are connected correctly, and the cables themselves are in working condition.2) If you find the unit to be at fault, write down a complete description of the problem, including how and when the problem occurs.3) Contact our Customer Service Department at (716) 297-2920 for your Return Authorization number or questions regarding technical assistance or repairs. Customer Service hours are 9:00 AM to 5:00 PM Eastern Time, Monday through Friday.4) Pack the unit in its original carton or a reasonable substitute. The packing box is not recommended as a shipping carton. Put the packaged unit in another box for shipping. Print the RA number clearly on the outside of the shipping box. Print your return shipping address on the outside of the box.5) Include with your unit: a return shipping address (we cannot ship to a P.O. Box), a copy of your purchase receipt, a daytime phone number, and a description of the problem.6) Ship your unit (keep your manual!) to: Yorkville Sound 4625 Witmer Industrial Estate, Niagara Falls New York 14305Specifications:Frequency Response: 10Hz –50kHz, +/-0.5dB @ +4dBu1kHz,@+18dBu,<0.1% @ 100Hz, +24dBu Ref: 0dBu = 0.775VRMSTHD:0.01%TypicalChannel Separation 90dB typicaltypical60dBCMRR:Phase Error less than 5%, 20Hz – 20kHzInsertion Loss: 0.4dB @ 100k Ohm Load, 5.5dB @ 600 Ohm LoadInput Connections: XLR female balanced, ¼” TRS balanced, and RCA type phono jacksOutput Connection: XLR male balanced, ¼” TRS balanced, and RCA type phono jacksPassivePower Requirements: TotallyDimensions: 1.75”H x 19”W x 3.75”D (44.5mm x 482.6mm x 95mm)(1.7kg)lbs.3.75Weight:。

T852 SBK TABLET 使用手册.pdf_1698058757.2742531说明书

In The Home on The GoT852 SBK TABLETTABLE OF CONTENTSFCC Warning (1)Unpack (2)Rotate (3)Use in the car (4)Charge (5)Use.......... .. (6)Power key. (7)Navigate (8)Organize (10)Select languages (12)Connect to online service (13)Getting started with the T852 SBK system (14)Why use a Google account (15)Google play (16)Play Store (17)Connect to a Hight-definition TV(HDTV) (18)Connect to your PC (19)IR/FM Debug (20)Warranty (21)FCC WarningThis device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.Any Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.Note: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:--Reorient or relocate the receiving antenna.--Increase the separation between the equipment and receiver.--Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.--Consult the dealer or an experienced radio/TV technician for help.FCC Radiation Exposure Statement:This equipment complies with FCC RF radiation exposure limits set forth for an uncontrolled environment.This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.UnpackIn The Car In The Home on The GoOWNER’S MANUALT852 SBK TABLETOpenFolding Arm With Rotary Base.。

MT8985资料

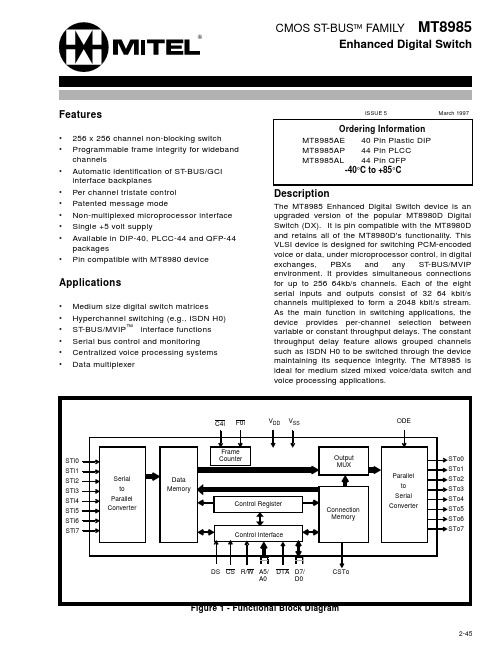

®Features•256 x 256 channel non-blocking switch •Programmable frame integrity for wideband channels•Automatic identification of ST-BUS/GCI interface backplanes•Per channel tristate control•Patented message mode•Non-multiplexed microprocessor interface •Single +5 volt supply•Available in DIP-40, PLCC-44 and QFP-44 packages•Pin compatible with MT8980 device Applications•Medium size digital switch matrices •Hyperchannel switching (e.g., ISDN H0)•ST-BUS/MVIP™ interface functions •Serial bus control and monitoring •Centralized voice processing systems •Data multiplexer DescriptionThe MT8985 Enhanced Digital Switch device is an upgraded version of the popular MT8980D Digital Switch (DX). It is pin compatible with the MT8980D and retains all of the MT8980D's functionality. This VLSI device is designed for switching PCM-encoded voice or data, under microprocessor control, in digital exchanges, PBXs and any ST-BUS/MVIP environment. It provides simultaneous connections for up to 256 64kb/s channels. Each of the eight serial inputs and outputs consist of 32 64 kbit/s channels multiplexed to form a 2048 kbit/s stream. As the main function in switching applications, the device provides per-channel selection between variable or constant throughput delays. The constant throughput delay feature allows grouped channels such as ISDN H0 to be switched through the device maintaining its sequence integrity. The MT8985 is ideal for medium sized mixed voice/data switch and voice processing applications.Figure 1 - Functional Block Diagram STo0 STo1 STo2 STo3 STo4 STo5 STo6 STo7Serialto Parallel ConverterDataMemoryFrameCounterControl RegisterControl InterfaceOutputMUXConnectionMemoryParalleltoSerialConverterCS R/W A5/A0DTA D7/D0CSToC4i F0i V DD V SS ODESTi0STi1STi2STi3STi4STi5STi6STi7DSISSUE 5March 1997MT8985Enhanced Digital Switch CMOS ST-BUS™ FAMIL YOrdering InformationMT8985AE40 Pin Plastic DIPMT8985AP44 Pin PLCCMT8985AL44 Pin QFP-40°C to +85°C元器件交易网2-45MT89852-46Figure 2 - Pin ConnectionsPin DescriptionPin #Name Description40DIP44PLCC 44QFP1240DT AData Acknowledgement (Open Drain Output). This active low output indicates that a data bus transfer is complete. A pull-up resistor is required at this output.2-93-57-1141-431-5STi0-STi7ST-BUS Input 0 to 7 (Inputs). Serial data input streams. These streams have 32channels at data rates of 2.048 Mbit/s.10126V DD +5 Volt Power Supply rail.11137F0iFrame Pulse (Input): This input accepts and automatically identifies framesynchronization signals formatted according to different backplane specifications such as ST -BUS and GCI.12148C4iClock (Input). 4.096 MHz serial clock for shifting data in and out of the data streams.13-1815-1719-219-1113-15A0-A5Address 0 to 5 (Inputs).These lines provide the address to MT8985 internalregisters.192216DSData Strobe (Input). This is the input for the active high data strobe on themicroprocessor interface. This input operates with CS to enable the internal read and write generation.202317R/WRead/Write (Input). This input controls the direction of the data bus lines (D0-D7)during a microprocessor access.DTA STi0STi1STi2STi3STi4STi5STi6STi7VDD F0i C4i A0A1A2A3A4A5DS CSTo ODE STo0STo1STo2STo3STo4STo5STo6STo7VSS D0D1D2D3D4D5D6D7CS1654324443424140789101112131415163938373635343332313023181920212224252627281729STi3STi4STi5STi6STi7VDD F0i C4i A0A1A2STo3STo4STo5STo6STo7VSS D0D1D2D3D4N C S T i 1D T A O D E S T o 1N CS T i 2S T i 0C S T o S T o 0S T o 2N C A 4D S C S D 6N CA 3A 5R /W D 740 PIN PLASTIC DIP44 PIN PLCC2345678910111213141516171819201R/W4039383736353433323130292827262524232221D 5394443424140383736353412345678910333231302928272625241712131415161819202122112344 PIN QFPSTi3STi4STi5STi6STi7VDD F0i C4i A0A1A2N C A 4D S C S D 6N CA 3A 5R /W D 7D 5STo3STo4STo5STo6STo7VSS D0D1D2D3D4N C S T i 1D T A O D E S T o 1N CS T i 2S T i 0C S T o S T o 0S T o 2元器件交易网MT89852-47212418CSChip Select (Input).Active low input enabling a microprocessor read or write of control register or internal memories.22-2925-2729-3319-2123-27D7-D0Data Bus 7 to 0 (Bidirectional).These pins provide microprocessor access to datain the internal control register, connect memory high, connect memory low and datamemory.303428V SSGround Rail.31-3835-3941-4329-3335-37STo7-STo0ST-BUS Outputs 7 to 0 (Three-state Outputs). Serial data output streams. Thesestreams are composed of 32 channels at data rates of 2.048 Mbit/s.394438ODE Output Drive Enable (Input). This is an output enable for the STo0 to STo7 serialoutputs. If this input is low STo0-7 are high impedance. If this input is high each channel may still be put into high impedance by software control.40139CSTo Control ST-BUS Output (Output).This output is a 2.048 Mb/s line which contains256 bits per frame. The level of each bit is controlled by the contents of the CSTo bit in the Connect Memory high locations.6, 18,28,4012,2234,44NCNo Connection.Pin DescriptionPin #Name Description40DIP44PLCC 44QFPFunctional DescriptionWith the integration of voice, video and data servicesinto the same network, there has been an increasing demand for systems which ensure that data at N x 64Kbit/s rates maintain frame sequence integrity while being transported through time slot interchange circuits. Existing requirements demand time slot interchange devices performing switching with constant throughput delay while guaranteeing minimum delay for voice channels.The MT8985 device provides both functions and allows existing systems based on the MT8980D to be easily upgraded to maintain the data integrity while multiple channel data are transported. The device is designed to switch 64 kbit/s PCM or N x 64kbit/s data. The MT8985 can provide both frame integrity for data applications and minimum throughput switching delay for voice applications on a per channel basis.By using Mitel Message mode capability, the microprocessor can access input and output time slots on a per channel basis to control devices such as the MITEL MT8972, ISDN Transceivers and T1/CEPT trunk interfaces through the ST -BUS interface.Different digital backplanes can be accepted by the MT8985 device without user's intervention. The MT8985 device provides an internal circuit thatautomatically identifies the polarity and format of frame synchronization input signals compatible to ST -BUS and GCI interfaces.Device OperationA functional block diagram of the MT8985 device is shown in Figure 1. The serial ST -BUS streams operate continuously at 2.048 Mb/s and are arranged in 125µs wide frames each containing 32 8-bit channels. Eight input (STi0-7) and eight output (STo0-7) serial streams are provided in the MT8985device allowing a complete 256 x 256 channel non-blocking switch matrix to be constructed. The serial interface clock for the device is 4.096 MHz, as required in ST -BUS and GCI specifications.Data MemoryThe received serial data is converted to parallel format by the on-chip serial to parallel converters and stored sequentially in a 256-position Data Memory. The sequential addressing of the Data Memory is generated by an internal counter that is reset by the input 8 kHz frame pulse (F0i) marking the frame boundaries of the incoming serial data streams.Depending on the type of information to be switched,the MT8985 device can be programmed to perform元器件交易网MT89852-48time slot interchange functions with different throughput delay capabilities on a per-channel basis.For voice applications, the variable delay mode can be selected ensuring minimum throughput delay between input and output data. In multiple or grouped channel data applications, the constant delay mode can be selected maintaining the integrity of the information through the switch.Data to be output on the serial streams may come from two sources: Data Memory or Connect Memory.Locations in the Connect Memory, which is split into HIGH and LOW parts, are associated with particular ST -BUS output streams. When a channel is due to be transmitted on an ST -BUS output, the data for the channel can either be switched from an ST -BUS input (connection mode) or it can be originated from the microprocessor (message mode). If a channel is configured in connection mode, the source of the output data is the Data Memory. If a channel is configured in message mode, the source of the output data is the Connect Memory Low. Data destined for a particular channel on the serial output stream is read from the Data or Connect Memory Low during the previous channel time slot. This allows enough time for memory access and internal parallel to serial conversion.Connection and Message ModesIn connection mode, the addresses of input source for all output channels are stored in the Connect memory Low. The Connect Memory Low locations are mapped to each location corresponding to an output 64 kb/s channel. The contents of the Data memory at the selected address are then transferred to the parallel to serial converters. By having the output channel to specify the input channel through the connect memory, the user can route the same input channel to several output channels, allowing broadcasting facility in the switch.In message mode the CPU writes data to the Connect Memory Low locations which correspond to the output link and channel number. The contents of the Connect Memory Low are transferred to the parallel to serial converter one channel before it is to be output. The Connect Memory Low data is transmitted each frame to the output until it is changed by the CPU.The per-channel functions available in the MT8985are controlled by the Connect Memory High bits,which determine whether individual output channels are selected into specific conditions such as:message or connection mode, variable or constant throughput delay modes, output drivers enabled or inthree-state condition. In addition, the Connect Memory High provides one bit to allow the user to control the state of the CSTo output pin.If an output channel is set to three-state condition,the TDM serial stream output will be placed in high impedance during that channel time. In addition to the per-channel three-state control, all channels on the TDM outputs can be placed in high impedance at one time by pulling the ODE input pin in LOW. This overrides the individual per-channel programming on the Connect Memory High bits.The Connect Memory data is received via the Microprocessor Interface at D0-D7 lines. The addressing of the MT8985 internal registers, Data and Connect memories is performed through address input pins and some bits of the device's Control register. The higher order address bits come from the Control register, which may be written or read through the microprocessor interface. The lower order address bits come directly from the external address line inputs. For details on the device addressing, see Software Control and Control register description.Serial Interface TimingThe MT8985 master clock (C4i) is a 4.096 MHz allowing serial data link configuration at 2.048 Mb/s to be implemented. The MT8985 frame synchronization pulse can be formatted according to ST -BUS or GCI interface specifications; i.e., the frame pulse can be active in HIGH (GCI) or LOW (ST -BUS). The MT8985 device automatically detects the presence of an input frame pulse and identifies the type of backplane present on the serial interface.Upon determining the correct interface connected to the serial port, the internal timing unit establishes the appropriate serial data bit transmit and sampling edges. In ST -BUS mode, every second falling edge of the 4.096 MHz clock marks a bit boundary and the input data is clocked in by the rising edge, three quarters of the way into the bit cell. In GCI mode,every second rising edge of the 4.096 MHz clock marks the bit boundary while data sampling is performed during the falling edge, at three quarters of the bit boundaries.Delay through the MT8985The transfer of information from the input serial streams to the output serial streams results in a delay through the MT8985 device. The delay through the MT8985 device varies according to the mode selected in the V/C bit of the connect memory high.元器件交易网MT89852-49Variable Delay modeThe delay in this mode is dependent only on the combination of source and destination channels and it is not dependent on the input and output streams.The minimum delay achievable in the MT8985 device is 3 time slots. In the MT8985 device, the information that is to be output in the same channel position as the information is input (position n), relative to frame pulse, will be output in the following frame (channel n, frame n+1). The same occurs if the input channel has to be output in the two channels succeeding (n+1 and n+2) the channel position as the information is input.The information switched to the third timeslot after the input has entered the device (for instance, input channel 0 to output channel 3 or input channel 30 to output channel 1), is always output three channels later.Any switching configuration that provides three or more timeslots between input and output channels,will have a throughput delay equal to the difference between the output and input channels; i.e., the throughput delay will be less than one frame. Table 1shows the possible delays for the MT8985 device in Variable Delay mode:Table 1Constant Delay ModeIn this mode frame integrity is maintained in all switching configurations by making use of a multiple Data-Memory buffer technique where input channels written in any of the buffers during frame N will be read out during frame N+2. In the MT8985, the minimum throughput delay achiev-able in Constant Delay mode will be 32 time slots; for example, when input time slot 32 (channel 31) is switched to output time slot 1 (channel 0). Likewise, the maximum delay is achieved when the first time slot in a frame (channel 0) is switched to the last time slot in the frame (channel 31), resulting in 94 time slots of delay.To summarize, any input time slot from input frame N will be always switched to the destination time slot onInput ChannelOutput Channel Throughput Delay n m=n, n+1 orn+2m-n + 32 timeslots n m>n+2m-n time slotsnm<n 32-(n-m) time slotsoutput frame N+2. In Constant Delay mode, the device throughput delay is calculated according to the following formula:DELAY = [32 + (32 - IN) + (OUT - 1)];(expressed in number of time slots)Where:IN is the number of the input time slot (from 1 to 32).OUT is the number of the output time slot (from 1 to 32).Microprocessor PortThe MT8985 microprocessor port has pin compatibility with Mitel MT8980 Digital Switch device providing a non-multiplexed bus architecture. The parallel port consists of an 8 bit parallel data bus (D0-D7), six address input lines (A0-A5) and four control lines (CS, DS, R/W and DT A). This parallel microport allows the access to the Control registers,Connection Memory High, Connection Memory Low and the Data Memory. All locations are read/written except for the data memory which can be read only.Accesses from the microport to the connection memory and the data memory are multiplexed with accesses from the input and output TDM ports. This can cause variable Data Acknowledge delays (DT A).In the MT8985 device, the DTA output provides a maximum acknowledgement delay of 800 ns for read/write operations in the Connection Memory.However, for operations in the Data Memory (Message Mode), the maximum acknowledgement delay can be 1220 ns.Figure 3 - Address Memory MapNote: "x" Don’t careSoftware ControlThe address lines on the microprocessor interface give access to the MT8985 internal registers and memories. If the A5,A1,A0 address line inputs areA5A4A3A2A1A0LOCATION 011111111X 00•••••1X 00•••••1X 00•••••1000•••••1001•••••1Control Register Channel 0Channel 1•••••Channel 31元器件交易网MT89852-50Figure 4 - Control Register Bitsx = Don’t care BIT NAME DESCRIPTION7SMSplit Memory.When 1, all subsequent reads are from the Data Memory and writes are to the Connection Memory Low, except when the Control Register is accessed again. The Memory Select bits need to be set to specify the memory for the operations. When 0, the Memory Select bits specify the memory for subsequent operations. In either case, the Stream Address Bits select the subsection of the memory which is made available.6MEMessage Enable. When 1, the contents of the Connection Memory Low are output on the Serial Output streams except when in High Impedance. When 0, the Connection Memory bits for each channel determine what is output.4-3MS1-MS0Memory Select Bits.The memory select bits operate as follows:0-0 - Not to be used0-1 - Data Memory (read only from the CPU)1-0 - Connection Memory Low 1-1 - Connection Memory High2-0STA2-0Stream Address Bits 2-0. The number expressed in binary notation on these bits refers to the input or output ST -BUS stream which corresponds to the subsection of memory made accessible for subsequent operations.SMMEXMS1MS0STA2STA1STA076543210LOW, then the MT8985 Internal Control Register is addressed (see Figure 3). If A5 input line is HIGH,then the remaining address input lines are used to select Memory subsections of 32 locations corresponding to the number of channels per input or output stream. As explained in the Control register description, the address input lines and the Stream Address bits (STA) of the Control register give the user the capability of selecting all positions of the MT8985 Data and Connect memories.The data in the Control register consists of Split memory and Message mode bits, Memory select and Stream Address bits (see Figure 4). The memory select bits allow the Connect Memory HIGH or LOW or the Data Memory to be chosen, and the Stream Address bits define an internal memory subsections corresponding to input or output ST -BUS streams.Bit 7 (Split Memory) of the Control register allows split memory operation whereby reads are from the Data memory and writes are to the Connect Memory LOW.The Message Enable bit (bit 6) places every output channel on every output stream in message mode;i.e., the contents of the Connect Memory LOW(CML) are output on the ST -BUS output streams once every frame unless the ODE input pin is LOW.If ME bit is HIGH, then the MT8985 behaves as if bits 2 (Message Channel) and 0 (Output Enable) of every Connect Memory HIGH (CMH) locations were set to HIGH, regardless of the actual value. If ME bit is LOW, then bit 2 and 0 of each Connect Memory HIGH location operates normally. In this case, if bit 2of the CMH is HIGH, the associated ST -BUS output channel is in Message mode. If bit 2 of the CMH is LOW, then the contents of the CML define the source information (stream and channel) of the time slot that is to be switched to an output.If the ODE input pin is LOW, then all serial outputs are high-impedance. If ODE is HIGH, then bit 0(Output Enable) of the CMH location enables (if HIGH) or disables (if LOW) the output drivers for the corresponding individual ST -BUS output stream and channel.The contents of bit 1 (CSTo) of each Connection Memory High location (see Figure 5) is output on CSTo pin once every frame. The CSTo pin is a 2048Mbit/s output which carries 256 bits. If CSTo bit is set HIGH, the corresponding bit on CSTo output is元器件交易网MT89852-51Figure 5 - Connection Memory High Bitsx = Don’t careFigure 6 - Connection Memory Low BitsBIT NAME DESCRIPTION6V/C Variable/Constant Throughput Delay Mode. This bit is used to select between Variable (LOW) and Constant Delay (HIGH) modes on a per-channel basis.2MCMessage Channel. When 1, the contents of the corresponding location in Connection Memory Low are output on the corresponding channel and stream. When 0, the contents of the programmed location in Connection Memory Low act as an address for the Data Memory and so determine the source of the connection to the location’s channel and stream.1CSTo CSTo Bit. This bit drives a bit time on the CSTo output pin.OEOutput Enable. This bit enables the output drivers on a per-channel basis. This allows individual channels on individual streams to be made high-impedance, allowing switch matrices to be constructed. A HIGH enables the driver and a LOW disables it.BIT NAME DESCRIPTION7-5SAB2-0*Source Stream Address bits. These three bits are used to select eight source streams for the connection. Bit 7 of each word is the most significant bit.4-0*CAB4-0*Source Channel Address bits 0-4. These five bits are used to select 32 different source channels for the connection (The ST -BUS stream where the channel is present is defined by bits SAB2-0). Bit 4 is the most significant bit.*If bit 2 of the corresponding Connection High location is 1 or if bit 6 of the Control Register is 1, then these entire 8 bits are output on the channel and stream associated with this location. Otherwise, the bits are used as indicated to define the source of the connection which is output on the channel and stream associated with this location.XV/CXXXMCCSToOE76543210SAB2SAB1SAB0CAB4CAB3CAB2CAB1CAB076543210transmitted in HIGH. If CSTo bit is LOW, the corresponding bit on the CSTo output is transmitted in LOW. The contents of the 256 CSTo bits of the CMH are transmitted sequentially on to the CSTo output pin and are synchronous to the ST -BUS streams. To allow for delay in any external control circuitry the contents of the CSTo bit is output one channel before the corresponding channel on the ST -BUS streams. For example, the contents of CSTo bit in position 0 (ST0, CH0) of the CMH, is transmitted synchronously with ST -BUS channel 31, bit 7. The contents of CSTo bit in position 32 (ST1, CH0) of the CMH is transmitted during ST -BUS channel 31 bit 6.Bit V/C (Variable/Constant Delay) on the Connect Memory High locations allow per-channel selectionbetween Variable and Constant throughput delay capabilities.Initialization of the MT8985On initialization or power up, the contents of the Connection Memory High can be in any state. This is a potentially hazardous condition when multiple MT8985 ST -BUS outputs are tied together to form matrices, as these outputs may conflict. The ODE pin should be held low on power up to keep all outputs in the high impedance condition.元器件交易网MT89852-52Figure 7 - Typical Exchange, PBX or Multiplexer ConfigurationS/UBasic Rate Line CardMT8930/31MT8910MT8972ST-BUSTo other linesLayers2 & 3EntityMT8940/MT8941ROUTINGMATRIXMT8985’sMH89760/MH89790MT8920µCST-BUSST-BUST1/E1LinkTo other linesPrimary Rate CardCPUDuring the microprocessor initialization routine, the microprocessor should program the desired active paths through the matrices, and put all other channels into the high impedance state. Care should be taken that no two connected ST-BUS outputs drive the bus simultaneously. When this process is complete, the microprocessor controlling the matrices can bring the ODE signal high to relinquish high impedance state control to the CMH b0s. ApplicationsTypical Exchange, PBX or MultiplexerFigure 7 shows a typical implementation of line cards being interconnected through a central routing matrix that can scale up in channel capacity to accommodate different number of ports depending on the application. In a configuration where the switched services utilize concatenated or grouped time slots to carry voice, data and video (channels of 128, 256 Kb/s, ISDN H0 and others), the central routing matrix has to guarantee constant throughput delay to maintain the sequence integrity between input and output channels. Figure 7 shows an example where the MT8985 device guarantees data integrity when data flows from the T1/E1 to the S/U interface links and vice-versa. Modern technologies available today such as Frame Relay network using dedicated fractional T1 are one of the key applications for the MT8985 device.Low Latency Isochronous NetworkIn today's local working group environment, there is an increasing demand for solutions on interconnection of desktop and telephone systems so that mixed voice, data and video services can be grouped together in a reliable network allowing the deployment of multimedia services. Existing multimedia applications require a network with元器件交易网MT89852-53Figure 8a - Private Isochronous NetworkAccess to Public NetworkAnalog Connections• • • • • •ISDN Desktopsn x 64Connections (e.g. Video)Isochronous NetworkServer 1Server 2Server 3Server 4T1T1E1• • • • • •• • • • • •T1/E1(2B+D)predictable data transfer delays that can be implemented at a reasonable cost. The Low Latency Isochronous Network is one of the alternatives that system designers have chosen to accommodate this requirement (see Figure 8a). This network can be implemented using existing TDM transmission media devices such as ISDN Basic (S or U) and Primary rates trunks (T1 and CEPT) to transport mixed voice and data signals in grouped time slots; for example,2B channels in case of ISDN S or U interfaces or up to 32 channels in case of a CEPT link.Figure 8b shows a more detailed configuration whereby several PCs are connected to form an Isochronous network. Several services can be interconnected within a single PC chassis through the standardized Multi Vendor Integration Protocol (MVIP). Such an interface allows the distribution and interconnection of services like voice mail, integrated voice response, voice recognition, LAN gateways,key systems, fax servers, video cards, etc.The information being exchanged between cards through the MVIP interface on every computer as well as between computers through T1 or CEPT links is, in general, of mixed type where 64Kb/s and N*64Kb/s channels are grouped together. When such a mixed type of data is transferred between cards within one chassis or from one computer to another, the sequence integrity of the concatenated channels has to be maintained. The MT8985 device suits this application and can be used to form a complete non-blocking switch matrix of 512 channels (see Figure 9). This allows 8 pairs of ST -BUS streams to be dedicated to the MVIP side whereas the remaining 8 pairs are used for local ancilliary functions in typical dual T1/E1 interface applications (Figure 10).Another application of the MT8985 in an MVIP environment is to build an ISDN S-interface card (Figure 11). In this card, 7 pairs of ST -BUS streams are connected to the MVIP interface while the remaining pair is reserved for the interconnection of MITEL MT8930 (SNIC), MT8992 (H-PHONE) and the MVIP interface.元器件交易网MT89852-54Figure 8b - Implementation of an Isochronous Network Using Mitel ComponentsServer 1MH89760BMH89790BST-BUSMT8985s(x4)MT8930BMT8930B••••••••••••MVIPBUSISDNS-InterfaceLocal T1/E1 LinkMVIPBUSServer 3(256 PORTSWITCH MODULE)Server 3MH89760B/790BMH89760B/790BMH89760B/790BST-BUS MT8985s(x4)HDLCMT8985MT8985MT8985MT8985ST-BUS MH89760BMH89790BDual T1/E1 CardMH89760BMH89790BMT8972BorANALOGMT8985s(x4)Server 2MVIPBUSST-BUSTo Video, Data,Fax ServicesLocal Environment Network Access••••••Local T1/E1 LinkT1E1 To Video, Data, Fax and other servicesPublic元器件交易网。

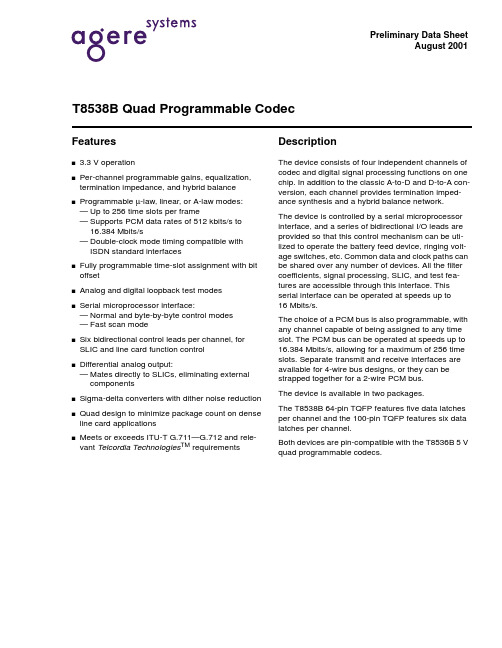

T8538B资料