HR24A-9DRA4SA2200B中文资料

DDR-240系列产品说明书

■ Applications

Bus,tram,metro or railway system Industrial control system Semi-conductor fabrication equipment Factory automation Electro-mechanical Wireless network Telecom or datacom system

EN50155:2017-Comply with S1 level

OVERLOAD

Normally works within 150% rated output power for more than 3 seconds and then constant current protection 105~135% Note.5 rated output power with auto-recovery

MTBF

484.9K hrs min. Telcordia SR-332 (Bellcore) ; 189.9K hrs min. IL-HDBK-217F (25℃)

OTHERS DIMENSION

40*125.2*113.5mm (W*H*D)

OPERATING ALTITUDE Note.7 2000 meters

SAFETY STANDARDS

IEC 62368-1 (LVD, except for 67.2~154Vin), EAC TP TC 004, AS/NZS 62368.1 approved; Design refer to UL508

WITHSTAND VOLTAGE

I/P-O/P:4KVdc I/P-FG:2.5KVdc O/P-FG:0.71KVdc

ATTINY24A中文资料

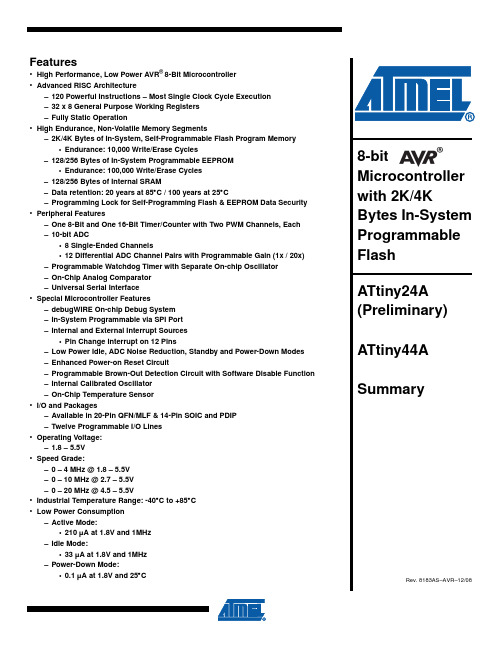

Features•High Performance, Low Power AVR® 8-Bit Microcontroller•Advanced RISC Architecture–120 Powerful Instructions – Most Single Clock Cycle Execution–32 x 8 General Purpose Working Registers–Fully Static Operation•High Endurance, Non-Volatile Memory Segments–2K/4K Bytes of In-System, Self-Programmable Flash Program Memory•Endurance: 10,000 Write/Erase Cycles–128/256 Bytes of In-System Programmable EEPROM•Endurance: 100,000 Write/Erase Cycles–128/256 Bytes of Internal SRAM–Data retention: 20 years at 85°C / 100 years at 25°C–Programming Lock for Self-Programming Flash & EEPROM Data Security •Peripheral Features–One 8-Bit and One 16-Bit Timer/Counter with Two PWM Channels, Each–10-bit ADC•8 Single-Ended Channels•12 Differential ADC Channel Pairs with Programmable Gain (1x / 20x)–Programmable Watchdog Timer with Separate On-chip Oscillator–On-Chip Analog Comparator–Universal Serial Interface•Special Microcontroller Features–debugWIRE On-chip Debug System–In-System Programmable via SPI Port–Internal and External Interrupt Sources•Pin Change Interrupt on 12 Pins–Low Power Idle, ADC Noise Reduction, Standby and Power-Down Modes –Enhanced Power-on Reset Circuit–Programmable Brown-Out Detection Circuit with Software Disable Function –Internal Calibrated Oscillator–On-Chip Temperature Sensor•I/O and Packages–Available in 20-Pin QFN/MLF & 14-Pin SOIC and PDIP–Twelve Programmable I/O Lines•Operating Voltage:–1.8 – 5.5V•Speed Grade:–0 – 4 MHz @ 1.8 – 5.5V–0 – 10 MHz @ 2.7 – 5.5V–0 – 20 MHz @ 4.5 – 5.5V•Industrial Temperature Range: -40°C to +85°C•Low Power Consumption–Active Mode:•210 µA at 1.8V and 1MHz–Idle Mode:•33 µA at 1.8V and 1MHz–Power-Down Mode:•0.1 µA at 1.8V and 25°C 8-bit Microcontrollerwith 2K/4KBytes In-System ProgrammableATtiny24A (Preliminary)ATtiny44A28183AS–AVR–12/08ATtiny24A/44A1.Pin ConfigurationsFigure 1-1.Pinout of ATtiny24A/44A1.1Pin Descriptions1.1.1VCCSupply voltage.1.1.2GNDGround.1.1.3Port B (PB3...PB0)Port B is a 4-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source RESET pin, program (‘0’) RSTDISBL fuse. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.1234567141312111098VCC(PCINT 8/XT AL1/CLKI) PB0(PCINT9/XTAL2) PB1(PCINT11/RE S ET/dW) PB 3(PCINT10/INT0/OC0A/CKOUT) PB2(PCINT7/ICP/OC0B/ADC7) PA7(PCINT6/OC1A/S DA/MO S I/DI/ADC6) PA6GNDPA0 (ADC0/AREF/PCINT0)PA1 (ADC1/AIN0/PCINT1)PA2 (ADC2/AIN1/PCINT2)PA 3 (ADC 3/T0/PCINT 3)PA4 (ADC4/U S CK/S CL/T1/PCINT4)P A5 (ADC5/DO/MI S O/OC1B/PCINT5)PDIP/S OIC12345QFN/MLF15141312112019181716678910NOTEBottom p a d s ho u ld b e s oldered to gro u nd.DNC: Do Not ConnectD N C D N C G N D V C C D N CPA7 (PCINT7/ICP/OC0B/ADC7)PB2 (PCINT10/INT0/OC0A/CKOUT)PB 3 (PCINT11/RE S ET/dW)PB1 (PCINT9/XTAL2)PB0 (PCINT 8/XTAL1/CLKI)P A 5D N C D N C D N C P A 6Pin 16: P A6 (PCINT6/OC1A/S DA/MO S I/DI/ADC6)Pin 20: P A5 (ADC5/DO/MI S O/OC1B/PCINT5)(ADC4/U S CK/S CL/T1/PCINT4) PA4(ADC 3/T0/PCINT 3) PA 3(ADC2/AIN1/PCINT2) PA2(ADC1/AIN0/PCINT1) PA1(ADC0/AREF/PCINT0) PA038183AS–AVR–12/08ATtiny24A/44APort B also serves the functions of various special features of the ATtiny24A/44A as listed in Section 10.2 “Alternate Port Functions” on page 57.Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running and provided the reset pin has not been disabled. The min-imum pulse length is given in Table 20-4 on page 176. Shorter pulses are not guaranteed to generate a reset.The reset pin can also be used as a (weak) I/O pin.1.1.5Port A (PA7...PA0)Port A is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active,even if the clock is not running.Port A has alternate functions as analog inputs for the ADC, analog comparator, timer/counter,SPI and pin change interrupt as described in “Alternate Port Functions” on page 57.48183AS–AVR–12/08ATtiny24A/44A2.OverviewATtiny24A/44A are low-power CMOS 8-bit microcontrollers based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATtiny24A/44A achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.Figure 2-1.Block DiagramThe AVR core combines a rich instruction set with 32 general purpose working registers. All 32registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than con-ventional CISC microcontrollers.58183AS–AVR–12/08ATtiny24A/44AThe ATtiny24A/44A provides the following features: 2K/4K byte of In-System Programmable Flash, 128/256 bytes EEPROM, 128/256 bytes SRAM, 12 general purpose I/O lines, 32 general purpose working registers, an 8-bit Timer/Counter with two PWM channels, a 16-bit timer/coun-ter with two PWM channels, Internal and External Interrupts, a 8-channel 10-bit ADC,programmable gain stage (1x, 20x) for 12 differential ADC channel pairs, a programmable Watchdog Timer with internal oscillator, internal calibrated oscillator, and four software select-able power saving modes. Idle mode stops the CPU while allowing the SRAM, Timer/Counter,ADC, Analog Comparator, and Interrupt system to continue functioning. ADC Noise Reduction mode minimizes switching noise during ADC conversions by stopping the CPU and all I/O mod-ules except the ADC. In Power-down mode registers keep their contents and all chip functions are disbaled until the next interrupt or hardware reset. In Standby mode, the crystal/resonator oscillator is running while the rest of the device is sleeping, allowing very fast start-up combined with low power consumption.The device is manufactured using Atmel’s high density non-volatile memory technology. The on-chip ISP Flash allows the Program memory to be re-programmed in-system through an SPI serial interface, by a conventional non-volatile memory programmer or by an on-chip boot code running on the AVR core.The ATtiny24A/44A AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators and Evaluation kits.68183AS–AVR–12/08ATtiny24A/44A3.About3.1ResourcesA comprehensive set of drivers, application notes, data sheets and descriptions on development tools are available for download at /avr.3.2Code ExamplesThis documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documen-tation for more details.For I/O Registers located in the extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI”instructions must be replaced with instructions that allow access to extended I/O. Typically, this means “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. Note that not all AVR devices include an extended I/O map.3.3Data RetentionReliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.3.4DisclaimerTypical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device has been characterized.78183AS–AVR–12/08ATtiny24A/44A4.Register SummaryAddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page0x3F (0x5F)SREG I T H S V N Z C Page 80x3E (0x5E)SPH ––––––SP9SP8Page 100x3D (0x5D)SPL SP7SP6SP5SP4SP3SP2SP1SP0Page 100x3C (0x5C)OCR0B Timer/Counter0 – Output Compare Register B Page 830x3B (0x5B)GIMSK –INT0PCIE1PCIE0––––Page 490x3A (0x5A GIFR –INTF0PCIF1PCIF0––––Page 500x39 (0x59)TIMSK0–––––OCIE0B OCIE0A TOIE0Page 830x38 (0x58)TIFR0––––OCF0BOCF0A TOV0Page 830x37 (0x57)SPMCSR ––RSIG CTPB RFLB PGWRTPGERS SPMEN Page 1560x36 (0x56)OCR0A Timer/Counter0 – Output Compare Register A Page 820x35 (0x55)MCUCR BODS PUD SE SM1SM0BODSE ISC01ISC00Pages 35, 49, and 650x34 (0x54)MCUSR ––––WDRF BORF EXTRF PORF Page 430x33 (0x53)TCCR0B FOC0A FOC0B ––WGM02CS02CS01CS00Page 810x32 (0x52)TCNT0Timer/Counter0Page 820x31(0x51)OSCCAL CAL7CAL6CAL5CAL4CAL3CAL2CAL1CAL0Page290x30 (0x50)TCCR0A COM0A1COM0A0COM0B1COM0B0–WGM01WGM00Page 780x2F (0x4F)TCCR1A COM1A1COM1A0COM1B1COM1B0–WGM11WGM10Page 1060x2E (0x4E)TCCR1B ICNC1ICES1–WGM13WGM12CS12CS11CS10Page 1080x2D (0x4D)TCNT1H Timer/Counter1 – Counter Register High Byte Page 1100x2C (0x4C)TCNT1L Timer/Counter1 – Counter Register Low Byte Page 1100x2B (0x4B)OCR1AH Timer/Counter1 – Compare Register A High Byte Page 1100x2A (0x4A)OCR1AL Timer/Counter1 – Compare Register A Low Byte Page 1100x29 (0x49)OCR1BH Timer/Counter1 – Compare Register B High Byte Page 1100x28 (0x48)OCR1BL Timer/Counter1 – Compare Register B Low BytePage 1100x27 (0x47)DWDR DWDR[7:0]Page 1510x26 (0x46)CLKPR CLKPCE–––CLKPS3CLKPS2CLKPS1CLKPS0Page 300x25 (0x45)ICR1H Timer/Counter1 - Input Capture Register High Byte Page 1110x24 (0x44)ICR1L Timer/Counter1 - Input Capture Register Low BytePage 1110x23 (0x43)GTCCR TSM ––––––PSR10Page 1140x22 (0x42)TCCR1C FOC1A FOC1B ––––––Page 1090x21 (0x41)WDTCSR WDIF WDIE WDP3WDCE WDE WDP2WDP1WDP0Page 430x20 (0x40)PCMSK1––––PCINT11PCINT10PCINT9PCINT8Page 500x1F (0x3F)Reserved ––––––––0x1E (0x3E)EEARL EEAR7EEAR6EEAR5EEAR4EEAR3EEAR2EEAR1EEAR0Page 200x1D (0x3D)EEDR EEPROM Data RegisterPage 210x1C (0x3C)EECR ––EEPM1EEPM0EERIE EEMPE EEPE EERE Page 210x1B (0x3B)PORTA PORTA7PORTA6PORTA5PORTA4PORTA3PORTA2PORTA1PORTA0Page 650x1A (0x3A)DDRA DDA7DDA6DDA5DDA4DDA3DDA2DDA1DDA0Page 650x19 (0x39)PINA PINA7PINA6PINA5PINA4PINA3PINA2PINA1PINA0Page 660x18 (0x38)PORTB ––––PORTB3PORTB2PORTB1PORTB0Page 660x17 (0x37)DDRB ––––DDB3DDB2DDB1DDB0Page 660x16 (0x36)PINB ––––PINB3PINB2PINB1PINB0Page 660x15 (0x35)GPIOR2General Purpose I/O Register 2Page 220x14 (0x34)GPIOR1General Purpose I/O Register 1Page 220x13 (0x33)GPIOR0General Purpose I/O Register 0Page 220x12 (0x32)PCMSK0PCINT7PCINT6PCINT5PCINT4PCINT3PCINT2PCINT1PCINT0Page 510x11 (0x31))Reserved –0x10 (0x30)USIBR USI Buffer Register Page 1270x0F (0x2F)USIDR USI Data RegisterPage 1230x0E (0x2E)USISR USISIF USIOIF USIPF USIDC USICNT3USICNT2USICNT1USICNT0Page 1280x0D (0x2D)USICR USISIE USIOIE USIWM1USIWM0USICS1USICS0USICLK USITC Page 1280x0C (0x2C)TIMSK1––ICIE1––OCIE1B OCIE1A TOIE1Page 1110x0B (0x2B)TIFR1––ICF1––OCF1BOCF1ATOV1Page 1120x0A (0x2A)Reserved –0x09 (0x29)Reserved –0x08 (0x28)ACSR ACD ACBG ACO ACI ACIE ACIC ACIS1ACIS0Page 1290x07 (0x27)ADMUX REFS1REFS0MUX5MUX4MUX3MUX2MUX1MUX0Page 1440x06 (0x26)ADCSRA ADENADSCADATEADIFADIEADPS2ADPS1ADPS0Page 1460x05 (0x25)ADCH ADC Data Register High Byte Page 1480x04 (0x24)ADCL ADC Data Register Low BytePage 1480x03 (0x23)ADCSRB BIN ACME –ADLAR–ADTS2ADTS1ADTS0Page 130, Page 1480x02 (0x22)Reserved –0x01 (0x21)DIDR0ADC7D ADC6D ADC5D ADC4D ADC3D ADC2D ADC1D ADC0D Page 131, Page 1490x00 (0x20)PRR––––PRTIM1PRTIM0PRUSIPRADCPage 3688183AS–AVR–12/08ATtiny24A/44ANote:1.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addressesshould never be written.2.I/O Registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In theseregisters, the value of single bits can be checked by using the SBIS and SBIC instructions.3.Some of the Status Flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBIinstructions will only operation the specified bit, and can therefore be used on registers containing such Status Flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.98183AS–AVR–12/08ATtiny24A/44A5.Instruction Set SummaryMnemonicsOperandsDescriptionOperation Flags#ClocksARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add two RegistersRd ← Rd + RrZ,C,N,V,H 1ADC Rd, Rr Add with Carry two Registers Rd ← Rd + Rr + C Z,C,N,V,H 1ADIW Rdl,K Add Immediate to Word Rdh:Rdl ← Rdh:Rdl + K Z,C,N,V,S 2SUB Rd, Rr Subtract two RegistersRd ← Rd - Rr Z,C,N,V,H 1SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H 1SBC Rd, Rr Subtract with Carry two Registers Rd ← Rd - Rr - C Z,C,N,V,H 1SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H 1SBIW Rdl,K Subtract Immediate from Word Rdh:Rdl ← Rdh:Rdl - K Z,C,N,V,S 2AND Rd, Rr Logical AND RegistersRd ← Rd • Rr Z,N,V 1ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V 1OR Rd, Rr Logical OR RegistersRd ← Rd v Rr Z,N,V 1ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V 1EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V 1COM Rd One’s Complement Rd ← 0xFF − Rd Z,C,N,V 1NEG Rd Two’s Complement Rd ← 0x00 − Rd Z,C,N,V,H 1SBR Rd,K Set Bit(s) in Register Rd ← Rd v KZ,N,V 1CBR Rd,K Clear Bit(s) in Register Rd ← Rd • (0xFF - K)Z,N,V 1INC Rd Increment Rd ← Rd + 1Z,N,V 1DEC Rd DecrementRd ← Rd − 1 Z,N,V 1TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V 1CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V 1SER Rd Set Register Rd ← 0xFF None 1BRANCH INSTRUCTIONSRJMP kRelative Jump PC ← PC + k + 1None 2IJMP Indirect Jump to (Z)PC ← Z None 2RCALL kRelative Subroutine Call PC ← PC + k + 1None 3ICALL Indirect Call to (Z)PC ←Z None 3RET Subroutine Return PC ← STACK None 4RETI Interrupt Return PC ← STACKI 4CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None 1/2/3CP Rd,Rr CompareRd − Rr Z, N,V,C,H 1 CPC Rd,Rr Compare with CarryRd − Rr − C Z, N,V,C,H 1CPI Rd,K Compare Register with Immediate Rd − KZ, N,V,C,H 1SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b)=0) PC ← PC + 2 or 3 None 1/2/3SBRS Rr, b Skip if Bit in Register is Set if (Rr(b)=1) PC ← PC + 2 or 3None 1/2/3SBIC P, b Skip if Bit in I/O Register Cleared if (P(b)=0) PC ← PC + 2 or 3 None 1/2/3SBIS P, b Skip if Bit in I/O Register is Set if (P(b)=1) PC ← PC + 2 or 3None 1/2/3BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC ←PC+k + 1None 1/2BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC ←PC+k + 1None 1/2BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None 1/2BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None 1/2BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None 1/2BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None 1/2BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None 1/2BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None 1/2BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None 1/2BRPL k Branch if Plusif (N = 0) then PC ← PC + k + 1None 1/2BRGE k Branch if Greater or Equal, Signed if (N ⊕ V= 0) then PC ← PC + k + 1None 1/2BRLT k Branch if Less Than Zero, Signed if (N ⊕ V= 1) then PC ← PC + k + 1None 1/2BRHS k Branch if Half Carry Flag Set if (H = 1) then PC ← PC + k + 1None 1/2BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC ← PC + k + 1None 1/2BRTS k Branch if T Flag Set if (T = 1) then PC ← PC + k + 1None 1/2BRTC k Branch if T Flag Cleared if (T = 0) then PC ← PC + k + 1None 1/2BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None 1/2BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC ← PC + k + 1None 1/2BRIE k Branch if Interrupt Enabled if ( I = 1) then PC ← PC + k + 1None 1/2BRID k Branch if Interrupt Disabled if ( I = 0) then PC ← PC + k + 1None 1/2BIT AND BIT-TEST INSTRUCTIONSSBI P,b Set Bit in I/O Register I/O(P,b) ←1None 2CBI P,b Clear Bit in I/O Register I/O(P,b) ← 0None 2LSL Rd Logical Shift Left Rd(n+1) ← Rd(n), Rd(0) ← 0Z,C,N,V 1LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0Z,C,N,V 1ROLRd Rotate Left Through CarryRd(0)←C,Rd(n+1)← Rd(n),C ←Rd(7)Z,C,N,V1108183AS–AVR–12/08ATtiny24A/44AROR Rd Rotate Right Through CarryRd(7)←C,Rd(n)← Rd(n+1),C ←Rd(0)Z,C,N,V 1ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n=0..6Z,C,N,V 1SWAP Rd Swap Nibbles Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0)None 1BSET s Flag Set SREG(s) ← 1SREG(s)1BCLR s Flag ClearSREG(s) ← 0 SREG(s)1BST Rr, b Bit Store from Register to T T ← Rr(b)T 1BLD Rd, bBit load from T to Register Rd(b) ← T None 1SEC Set Carry C ←1C 1CLC Clear Carry C ← 0 C 1SEN Set Negative Flag N ←1N 1CLN Clear Negative Flag N ← 0 N 1SEZ Set Zero Flag Z ← 1Z 1CLZ Clear Zero Flag Z ← 0 Z 1SEI Global Interrupt Enable I ←1I 1CLI Global Interrupt Disable I ← 0 I 1SES Set Signed Test Flag S ← 1S 1CLS Clear Signed Test FlagS ← 0 S 1SEV Set Twos Complement Overflow.V ← 1V 1CLV Clear Twos Complement Overflow V ← 0 V 1SET Set T in SREG T ←1T 1CLT Clear T in SREGT ← 0T 1SEH Set Half Carry Flag in SREGH ←1H 1CLHClear Half Carry Flag in SREGH ← 0H 1DATA TRANSFER INSTRUCTIONS MOV Rd, Rr Move Between RegistersRd ← Rr None 1MOVW Rd, Rr Copy Register Word Rd+1:Rd ← Rr+1:Rr None 1LDI Rd, K Load Immediate Rd ← KNone 1LD Rd, X Load Indirect Rd ← (X)None 2LD Rd, X+Load Indirect and Post-Inc.Rd ← (X), X ← X + 1None 2LD Rd, - X Load Indirect and Pre-Dec.X ← X - 1, Rd ← (X)None 2LD Rd, Y Load IndirectRd ← (Y)None 2LD Rd, Y+Load Indirect and Post-Inc.Rd ← (Y), Y ← Y + 1None 2LD Rd, - Y Load Indirect and Pre-Dec.Y ← Y - 1, Rd ← (Y)None 2LDD Rd,Y+q Load Indirect with Displacement Rd ← (Y + q)None 2LD Rd, Z Load Indirect Rd ← (Z)None 2LD Rd, Z+Load Indirect and Post-Inc.Rd ← (Z), Z ← Z+1None 2LD Rd, -Z Load Indirect and Pre-Dec.Z ← Z - 1, Rd ← (Z)None 2LDD Rd, Z+q Load Indirect with Displacement Rd ← (Z + q)None 2LDS Rd, k Load Direct from SRAM Rd ← (k)None 2ST X, Rr Store Indirect(X) ← RrNone 2ST X+, Rr Store Indirect and Post-Inc.(X) ← Rr, X ← X + 1None 2ST - X, Rr Store Indirect and Pre-Dec.X ← X - 1, (X) ← Rr None 2ST Y, Rr Store Indirect(Y) ← RrNone 2ST Y+, Rr Store Indirect and Post-Inc.(Y) ← Rr, Y ← Y + 1None 2ST - Y, Rr Store Indirect and Pre-Dec.Y ← Y - 1, (Y) ← Rr None 2STD Y+q,Rr Store Indirect with Displacement (Y + q) ← Rr None 2ST Z, Rr Store Indirect(Z) ← RrNone 2ST Z+, Rr Store Indirect and Post-Inc.(Z) ← Rr, Z ← Z + 1None 2ST -Z, Rr Store Indirect and Pre-Dec.Z ← Z - 1, (Z) ← Rr None 2STD Z+q,Rr Store Indirect with Displacement (Z + q) ← Rr None 2STS k, RrStore Direct to SRAM (k) ← Rr None 2LPM Load Program Memory R0 ← (Z)None 3LPM Rd, Z Load Program MemoryRd ← (Z)None 3LPM Rd, Z+Load Program Memory and Post-Inc Rd ← (Z), Z ← Z+1None 3SPM Store Program Memory (z) ← R1:R0None IN Rd, P In Port Rd ←P None 1OUT P, Rr Out PortP ← Rr None 1PUSH Rr Push Register on Stack STACK ← Rr None 2POP Rd Pop Register from Stack Rd ← STACKNone 2MCU CONTROL INSTRUCTIONSNOP No Operation None1SLEEP Sleep(see specific descr. for Sleep function)None 1WDR Watchdog Reset (see specific descr. for WDR/Timer)None 1BREAKBreakFor On-chip Debug Only NoneN/AMnemonicsOperandsDescriptionOperationFlags#Clocks118183AS–AVR–12/08ATtiny24A/44A6.Ordering InformationNotes:1.This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering informationand minimum quantities.2.Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). AlsoHalide free and fully Green.6.1ATtiny24ASpeed (MHz)Power SupplyOrdering Code (1)Package (2)Operational Range 201.8 - 5.5VA Ttiny24A-SSU A Ttiny24A-PU A Ttiny24A-MU A Ttiny24A-MMH14S114P320M120M2Industrial (-40°C to 85°C)Package Type14S114-lead, 0.150" Wide Body, Plastic Gull Wing Small Outline Package (SOIC)14P314-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)20M120-pad, 4 x 4 x 0.8 mm Body, Quad Flat No Lead / Micro Lead Frame Package (QFN/MLF)20M220-pad, 3 x 3 x 0.85 mm Body, Very Thin Quad Flat No Lead Package (VQFN)128183AS–AVR–12/08ATtiny24A/44ANotes:1.This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering informationand minimum quantities.2.Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). AlsoHalide free and fully Green.6.2ATtiny44ASpeed (MHz)Power SupplyOrdering Code (1)Package (2)Operational Range 201.8 - 5.5VA Ttiny44A-SSU A Ttiny44A-PU A Ttiny44A-MU A Ttiny44A-MMH14S114P320M120M2Industrial (-40°C to 85°C)Package Type14S114-lead, 0.150" Wide Body, Plastic Gull Wing Small Outline Package (SOIC)14P314-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)20M120-pad, 4 x 4 x 0.8 mm Body, Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF)20M220-pad, 3 x 3 x 0.85 mm Body, Very Thin Quad Flat No Lead Package (VQFN)138183AS–AVR–12/08ATtiny24A/44A7.Packaging Information7.120M1148183AS–AVR–12/08ATtiny24A/44A7.220M2158183AS–AVR–12/08ATtiny24A/44A7.314P3168183AS–AVR–12/08ATtiny24A/44A7.414S1178183AS–AVR–12/08ATtiny24A/44A8.ErrataThe revision letters in this section refer to the revision of the corresponding ATtiny24A/44A device.8.1ATtiny24A8.1.1Rev. GNot sampled.8.1.2Rev. FNot sampled.188183AS–AVR–12/08ATtiny24A/44A8.2ATtiny44A8.2.1Rev. FNo known errata.8.2.2Rev. ENot sampled.198183AS–AVR–12/08ATtiny24A/44A9.Datasheet Revision History9.1Rev A. 12/081.Initial revision. Created from document 8006H.2.Updated "Ordering Information" on page 17 and page 18. Pb-plated packages are nolonger offered and there are no separate ordering codes for commercial operation range, the only available option now is industrial. Also, updated some order codes to reflect changes in leadframe composition and added VQFN package option.3.Updated data sheet template.4.Removed all references to 8K device.5.Updated characteristic plots of section “Typical Characteristics”, starting on page 182.6.Added characteristic plots:–“Internal Bandgap Voltage vs. Supply Voltage” on page 202–“Internal Bandgap Voltage vs. Temperature” on page 2027.Updated sections:–“Features” on page 1–“Power Reduction Register” on page 34–“Analog Comparator” on page 128–“Features” on page 132–“Operation” on page 133–“Starting a Conversion” on page 134–“ADC Voltage Reference” on page 139–“Speed Grades” on page 1748.Updated Figures:–“Program Memory Map” on page 15–“Data Memory Map” on page 169.Update Tables:–“Device Signature Bytes” on page 161–“DC Characteristics. T A = -40°C to +85°C” on page 173–“Additional Current Consumption for the different I/O modules (absolute values)” on page 182–“Additional Current Consumption (percentage) in Active and Idle mode” on page 1838183AS–AVR–12/08HeadquartersInternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131USATel: 1(408) 441-0311Fax: 1(408) 487-2600Atmel AsiaUnit 1-5 & 16, 19/FBEA Tower, Millennium City 5418 Kwun Tong Road Kwun Tong, Kowloon Hong KongTel: (852) 2245-6100Fax: (852) 2722-1369Atmel Europe Le Krebs8, Rue Jean-Pierre Timbaud BP 30978054 Saint-Quentin-en-Yvelines Cedex FranceTel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Support avr@Sales Contact/contactsLiterature Requests /literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL ’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL ’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2008 Atmel Corporation. All rights reserved. Atmel ®, logo and combinations thereof, AVR ® and others are registered trademarks or trade-marks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

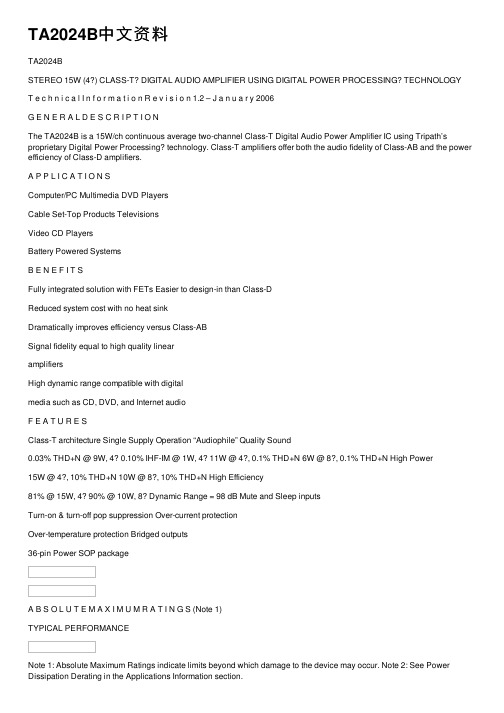

TA2024B中文资料

TA2024B中⽂资料TA2024BSTEREO 15W (4?) CLASS-T? DIGITAL AUDIO AMPLIFIER USING DIGITAL POWER PROCESSING? TECHNOLOGYT e c h n i c a l I n f o r m a t i o n R e v i s i o n 1.2 – J a n u a r y 2006G E N E R A L D E S C R I P T I O NThe TA2024B is a 15W/ch continuous average two-channel Class-T Digital Audio Power Amplifier IC using Tripath’s proprietary Digital Power Processing? technology. Class-T amplifiers offer both the audio fidelity of Class-AB and the power efficiency of Class-D amplifiers.A P P L I C A T I O N SComputer/PC Multimedia DVD PlayersCable Set-Top Products TelevisionsVideo CD PlayersBattery Powered SystemsB E N E F I T SFully integrated solution with FETs Easier to design-in than Class-DReduced system cost with no heat sinkDramatically improves efficiency versus Class-ABSignal fidelity equal to high quality linearamplifiersHigh dynamic range compatible with digitalmedia such as CD, DVD, and Internet audioF E A T U R E SClass-T architecture Single Supply Operation “Audiophile” Quality Sound0.03% THD+N @ 9W, 4? 0.10% IHF-IM @ 1W, 4? 11W @ 4?, 0.1% THD+N 6W @ 8?, 0.1% THD+N High Power15W @ 4?, 10% THD+N 10W @ 8?, 10% THD+N High Efficiency81% @ 15W, 4? 90% @ 10W, 8? Dynamic Range = 98 dB Mute and Sleep inputsTurn-on & turn-off pop suppression Over-current protectionOver-temperature protection Bridged outputs36-pin Power SOP packageA B S O L U T E M A X I M U M R A T I N G S (Note 1)TYPICAL PERFORMANCENote 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Note 2: See Power Dissipation Derating in the Applications Information section.O P E R A T I N G C O N D I T I O N S(Note 4)Note 3: Recommended Operating Conditions indicate conditions for which the device is functional. See Electrical Characteristics for guaranteed specific performance limits.T H E R M A L C H A R A C T E R I S T I C SE L E C T R I C A L C H A R A C T E R I S T I C SSee Test/Application Circuit. Unless otherwise specified, V DD = 12V, f = 1kHz, Measurement Bandwidth = 22kHz, R L = 4?, T A = 25 °C, Package heat slug soldered to 2.8 square-inch PC pad.Note: Minimum and maximum limits are guaranteed but may not be 100% tested.P I N D E S C R I P T I O NT A 2024B P I N O U TFAULTPGND2NC NC VDD2OUTM2OUTM1VDD1NC VDDA NC PGND1CPUMP DCAP2AGND3BIASCAP INV2OAOUT2MUTE INV1OAOUT1V5A AGND2OVERLOADBREF AGND1V5DDCAP136-pin Power SOP Package(Top View)+5VGEN OUTP1VDD1VDD2OUTP2DGND NC SLEEPPin Function Description2, 3DCAP2, DCAP1Charge pump switching pins. DCAP1 (pin 3) is a free running 300kHz square wave between VDDA and DGND (12Vpp nominal). DCAP2 (pin 2) is level shifted 10 volts above DCAP1 (pin 3) with the same amplitude (12Vpp nominal), frequency, and phase as DCAP1. 4, 9 V5D, V5A Digital 5VDC, Analog 5VDC 5, 8, 17 AGND1, AGND2,AGND3 Analog Ground6 REFInternal reference voltage; approximately 1.0 VDC.7 OVERLOADB A logic low output indicates the input signal has overloaded the amplifier. 10, 14 OAOUT1, OAOUT2Input stage output pins.11, 15 INV1, INV2Single-ended inputs. Inputs are a “virtual” ground of an inverting opamp with approximately 2.4VDC bias.12 MUTE When set to logic high, both amplifiers are muted and in idle mode. When low (grounded), both amplifiers are fully operational. If left floating, the device stays in the mute mode. This pin should be tied to GND if not used. 16 BIASCAP Inputstage bias voltage (approximately 2.4VDC).18 SLEEP When set to logic high, device goes into low power mode. If not used, this pin should be grounded19FAULTA logic high output indicates thermal overload, or an output is shorted to ground, or another output.20, 35 PGND2, PGND1 Power Grounds (high current)22 DGND Digital Ground. Connect to AGND locally (near the TA2024B). 24, 27; 31, 28 OUTP2 & OUTM2; OUTP1 & OUTM1 Bridged output pairs25, 26, 29, 30 VDD2, VDD2 VDD1, VDD1 Supply pins for high current H-bridges, nominally 12VDC. 13, 21, 23, 32, 34NC Not connected. Not bonded internally. 33 VDDA Analog 12VDC 36 CPUMP Charge pump output (nominally 10V above VDDA) 1 5VGEN Regulated 5VDC source used to supply power to the input section (pins 4 and 9).A P P L I C A T I O N /T E S T C I R C U I TAll Diodes Motorola MBRS130T3* Use C o = 0.22µF for 8 Ohm loadsNote: Analog and Digital/Power Grounds must be connected locally at the TA2024BAnalog Ground Digital/Power GroundE X T E R N A L C O M P O N E N T S D E S C R I P T I O N(Refer to the Application/Test Circuit)T Y P I C A L P E R F O R M A N C EA P P L I C A T I O N I N F O R M A T I O NL a y o u t R e c o m m e n d a t i o n sThe TA2024B is a power (high current) amplifier that operates at relatively high switchingfrequencies. The outputs of the amplifier switch between the supply voltage and ground at high speeds while driving high currents. This high-frequency digital signal is passed through an LC low-pass filter to recover the amplified audio signal. Since the amplifier must drive the inductive LC output filter and speaker loads, the amplifier outputs can be pulled above the supply voltage and below ground by the energy in the output inductance. To avoid subjecting the TA2024B to potentially damaging voltage stress, it is critical to have a good printed circuit board layout. It is recommended that Tripath’s layout and application circuit be used for all applications and only be deviated from after careful analysis of the effects of any changes. Please contact TripathTechnology for further information regarding reference design material regarding the TA2024B.O u t p u t S t a g e l a y o u t C o n s i d e r a t i o n s a n d C o m p o n e n t S e l e c t i o n C r i t e r i a Proper PCB layout and component selection is a major step in designing a reliable TA2024Bpower amplifier. The supply pins require proper decoupling with correctly chosen components to achieve optimal reliability. The output pins need proper protection to keep the outputs from going below ground.The above layout shows ideal component placement and routing for channel 1 (the same design criteria applies to channel 2). This shows that C3, a 0.1uF surface mount 0805 capacitor, should be the first component placed and must decouple VDD1 (pins 29 and 30) directly to PGND1(pin35). C2, a low ESR, electrolytic capacitor, should also decouple VDD1 directly to PGND1.Both C2 and C3 may decouple VDD1 to a ground plane, but it is critical that the return path to the PGND1 pin of theTA2024B, whether it is a ground plane or a trace, be a short and direct low impedance path. Effectively decoupling VDD will shunt any power supply trace length inductance.The diodes and inductors shown are for channel 1’s outputs. D1 and L2 connect to the OUTP1 pin and D2 and L3 connect to the OUTM1 pin of the TA2024B. Each output must have a Schottky or Ultra Fast Recovery diode placed near the TA2024B, preferably immediately after thedecoupling capacitors and use short returns to PGND1. These low side diodes, D1 and D2, will prevent the outputs from going below ground. To be optimally effective they must have a short and direct return path to its proper ground pin (PGND1) of the TA2024B. This can be achieved with a ground plane or a trace.The output inductors, L2 and L3, should be placed close to the TA2024B without compromising the locations of the closely placed supply decoupling capacitors and output diodes. The purposeof placing the output inductors close to the TA2024B output pins is to reduce the trace length of the switching outputs. This will aid in reducing radiated emissions.Please see the External Component Description section on page 6 for more details on the above-mentioned components. The Application/ Test Circuit refers to the low side diodes as D O , The high side diodes as D H , and both supply decoupling capacitors as C SW .T A 2024B A m p l i f i e r G a i nThe ideal gain of the TA2024B is set by the ratio of two external resistors, R I and R F , and is given by the following formula: IF I O R R12V V ?=where V I is the input signal level and V O is the differential output signal level across the speaker. Please note that V O is 180° out of phase with V I .The ideal gain of the TA2024B is 12V/V, whereas typical values are: A V = 11.5V/V for 4? and 11.7V/V for 8?.P r o t e c t i o n C i r c u i t sThe TA2024B is guarded against over-temperature and over-current conditions. When thedevice goes into an over-temperature or over-current state, the FAULT pin goes to a logic HIGH state indicating a fault condition. When this occurs, the amplifier is muted, all outputs are TRI-STATED, and will float to 1/2 of V DD .O v e r -t e m p e r a t u r e P r o t e c t i o nAn over-temperature fault occurs if the junction temperature of the part exceeds approximately 155°C. The thermal hysteresis of the part is approximately 45°C, therefore the fault will automatically clear when the junction temperature drops below 110°C.O v e r -c u r r e n t P r o t e c t i o nAn over-current fault occurs if more than approximately 7 amps of current flows from any of the amplifier output pins. This can occur if the speaker wires are shorted together or if one side of the speaker is shorted to ground. An over-current fault sets aninternal latch that can only be cleared if the MUTE pin is toggled or if the part is powered down. Alternately, if the MUTE pin is connected to the FAULT pin, the HIGH output of the FAULT pin will toggle the MUTE pin and automatically reset the fault condition.O v e r l o a dThe OVERLOADB pin is a 5V logic output. When low, it indicates that the level of the input signal has overloaded the amplifier resulting in increased distortion at the output. The OVERLOADB signal can be used to control a distortion indicator light or LED through a simple buffer circuit, as the OVERLOADB cannot drive an LED directly.S l e e p P i nThe SLEEP pin is a 5V logic input that when pulled high (>3.5V) puts the part into a low quiescent current mode. This pin is internally clamped by a zener diode to approximately 6V thus allowing the pin to be pulled up through a large valued resistor (1meg ? recommended) to V DD . To disable SLEEP mode, the sleep pin should be grounded.F a u l t P i nThe FAULT pin is a 5V logic output that indicates various fault conditions within the device.These conditions include: low supply voltage, low charge pump voltage, low 5V regulator voltage, over current at any output, and junction temperature greater than approximately 155°C. All faults except overcurrent all reset upon removal of the condition. The FAULT output is capable of directly driving an LED through a series 2k ? resistor. If the FAULT pin is connected directly to the MUTE input an automatic reset will occur in the event of an over-current condition.P o w e r D i s s i p a t i o n D e r a t i n gFor operating at ambient temperatures above 25°C the device must be derated based on a 150°C maximum junction temperature, TJMAX as given by the following equation:JAA JMAXDISS )T T (P θ?=where…PDISS = maximum power dissipationTJMAX = maximum junction temperature of TA2024B TA = operating ambient temperatureθJA = junction-to-ambient thermal resistance Where θJA of the package is determined from the following graph:In the above graph Copper Area is the size of the copper pad on the PC board to which the heat slug of the TA2024B is soldered. The heat slug must be soldered to the PC Board to increase the maximum power dissipation capability of theTA2024B package. Soldering will minimize the likelihood of an over-temperature fault occurring during continuous heavy load conditions. The vias used for connecting the heatslug to the copper area on the PCB should be 0.013” diameter.P e r f o r m a n c e M e a s u r e m e n t s o f t h e T A 2024BThe TA2024B operates by generating a high frequency switching signal based on the audio input. This signal is sent through a low-pass filter (external to the Tripath amplifier) that recovers an amplified version of the audio input . The frequency of the switching pattern is spread spectrum and typically varies between 100kHz and 1.0MHz, which is well above the 20Hz –20kHz audio band. The pattern itself does not alter or distort the audio input signal but it does introduce some inaudible components.J AThe measurements of certain performance parameters, particularly noise related specifications such as THD+N, are significantly affected by the design of the low-pass filter used on the output as well as the bandwidth setting of the measurement instrument used. Unless the filter has a very sharp roll-off just beyond the audio band or the bandwidth of the measurement instrument is limited, some of the inaudible noise components introduced by the Tripath amplifiers switching pattern will degrade the measurement.One feature of the TA2024B is that it does not require large multi-pole filters to achieve excellent performance in listening tests, usually a more critical factor than performance measurements. Though using a multi-pole filter may remove high-frequency noise and improve THD+N type measurements (when they are made with wide-bandwidth measuring equipment), these same filters degrade frequency response. The TA2024B Evaluation Board uses the Test/Application Circuit in this data sheet, which has a simple two-pole output filter and excellent performance in listening tests. Measurements in this data sheet were taken using this same circuit with a limited bandwidth setting in the measurement instrument.P A C K A G E I N F O R M A T I O NThe package for the TA2024B is a 36-Lead Power Small Outline Package (PSOP), similar to JEDEC outline MO-166, variation AE. Tripath currently has two suppliers for this package. We recommend that the exposed copper heatslug width for the PCB design be at least 7.3mm wide to accommodate the heatslug width variation for each package. Package dimensions are based on millimeters. Measurements in inches are provided as reference only.Outline and mechanical data for PSOP36DIM MIN MAX DIM MIN MAXBSCE1 11.00A - 3.600A1 0.100 - E2 - 2.900 A2 3.000 3.300 E3 6.300 7.300 A3 0.025 0.152 E4 2.700 2.900BSC E5 - 1.000D 15.90D1 9.000 13.000 L 0.800 1.100REF D2 - 1.100 L1 1.60D3 - 1.000 L2 0.350BSCE 14.200 BSC All DIM measured in mmThis is a product in development. Tripath Technology, Inc. reserves the right to make any changes without further notice to improve reliability, function and design.Tripath and Digital Power Processing are trademarks of Tripath Technology. Other trademarks referenced in this document are owned by their respective companies.Tripath Technology, Inc. reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Tripath does not assume any liability arising out of the application of use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.TRIPATH’S PRODUCT ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFESUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN CONSENT OF THEPRESIDENT OF TRIPATH TECHONOLOGY, INC.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implantinto the body, or (b) support or sustain life, and whose failure to perform, when properly used inaccordance with instructions for use provided in this labeling, can be reasonably expected to resultin significant injury of the user.2. A critical component is any component of a life support device or system whose failure to performcan be reasonably expected to cause the failure of the life support device or system, or to affect itssafety or effectiveness.C o n t a c t I n f o r m a t i o nT R I P A T H T E C H N O L O G Y,I N C2560 Orchard Parkway, San Jose, CA 95131408.750.3000 - P408.750.3001 - FFor more Sales Information, please visit us @ /doc/7caf2e651eb91a37f1115cf3.html /cont_s.htm For more Technical Information, please visit us @ /doc/7caf2e651eb91a37f1115cf3.html /data.htm。

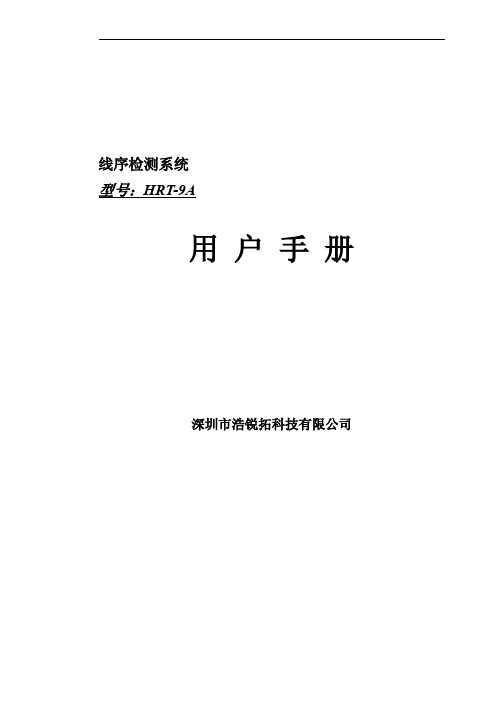

HRT-9A操作说明

产品简介:线束生产过程中需要按照正确的颜色排序。以往通过人工来判别检测,会产 生漏检和错检。 而通过我公司全自动线束颜色排序检测仪的检测, 可以自动判别线束顺序是 否有误和是否有脱线掉线头及插错空位等情况。我司开发的“全自动线束颜色排序检测仪” 采用高性能工业相机和高分辨率的工业镜头, 配合先进的图像处理功能实现了线束彩色线序 的全自动检测。

1.2 技术规范

检测项目: (一) 检测线缆线束内不同颜色的连接线排放顺序是否正确。 (二) 检测连接线所插孔位是否正确 检测速度:取决于放料速度,最大 3 次/秒 检测结果分析:可以自动统计不良率并保存到 U 盘以供统计分析 不良品处理:声音报警并于显示器上指示 OK 或者 NG,可 I/O 输出 设备供电

原理及操作流程

2.1 原理

系统首先拍摄正确的线材的图片,利用该图片作为模板,与检测时拍摄的图片作对比。 来辨别产品的合格与否。 HRT-9A 利用 CCD 机器视觉辨别技术,通过浩锐拓专用算法进行线束颜色识别,对比 预设的参数,判断是否符合预设标准,输出结果 检测内容: 自动识别线束颜色顺序排位 自动判断线束是否错位 产品可以正面放也可以反面摆放,仪器自动识别正反面 自动统计检测过程.算出产品良率.并对检测过程进行保存 同时也可对其他特征进行检测(需评估)

线序检测系统

型号:HRT-9A

用 户 手 册

深圳市浩锐拓科技有限公司

版权声明

本产品的所有部分,包括本手册及配件等,其知识产权归深圳 市浩锐拓科技有限公司(以下简称浩锐拓)所有。未经浩锐拓公司书 面许可,不得任意仿制、拷贝、眷抄或转译。除此之外,本手册的内 容及产品规格,有因改良而不经预告变更的情况,请在使用前用最新 的手册确认功能、性能,如需更多资讯请向浩锐拓科技查询。

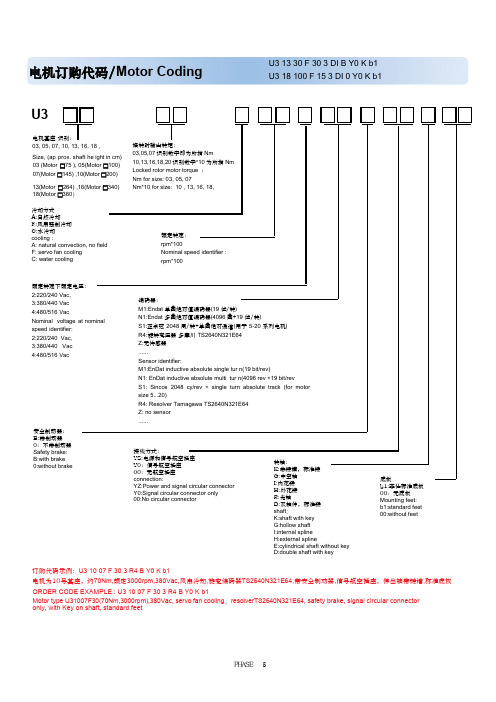

菲仕电机部分选型资料

接线方式: YZ:电源和信号航空插座 Y0:信号航空插座 00:无航空插座 connection: YZ:Power and signal circular connector Y0:Signal circular connector only 00:No circular connector

0RWRU□ 0RWRU□

0RWRU□ 0RWRU□

18(Motor □360)

堵转时输出转矩: 识别数字即为所指 1P 识别数字* 为所指 1P /RFNHGURWRUPRWRUWRUTXH : 1PIRUVL]H

25'(5&2'((;$03/(8)5% <0 K E 0RWRUW\SH8) 1PUSP 9DFVHUYRIDQFRoling,UHVROYHU761(VDIHW\EUDNHsignal circular connector only, ZLWK.H\RQVKDIWstandard feet

最大值/Maximum Values

最大转矩/Max. Torque

最大电流/Max. Current (peak value)

380V时最大速度 Max. Saturation Speed @ 380Vac 480V时最大速度 Max. Saturation Speed @ 480Vac

最大机械速度/Max. Mechanical Speed

重量/Mass

MBr

[Kg]

18

惯量/Inertia

JBr [Kgcm²]

200

电机增加的长度/ddditional motor lenght Lenght [mm]

NRD24-SR-SI 系列减速比恒定位电机驱动器说明书

NRD24-SR-SIActuador de carrera reducida proporcionalpara la motorización de válvulas de asiento decarrera reducida de Siemens en sistemas decalefacción, ventilación y climatización• Fuerza de actuación 500 N• Tensión nominal AC/DC 24 V• Control proporcional 0...10 V• Carrera nominal 5.5 mmDatos técnicosDatos eléctricos Tensión nominal AC/DC 24 VFrecuencia nominal50/60 HzObservación sobre rango de tensión nominal AC 19.2...28.8 V / DC 21.6...28.8 VConsumo de energía en funcionamiento 1 WConsumo de energía para dimensionado 2.5 VAConexión de la alimentación / control Cable 1 m, 4x 0.75 mm²Funcionamiento en paralelo Si (tenga en cuenta los datos defuncionamiento)Datos de funcionamiento Fuerza de actuación del motor500 NMargen de trabajo Y0...10 VImpedancia de entrada100 kΩMargen de trabajo Y variable 2...10 VSeñal de salida (posición) U0...10 VNota de señal de salida U Max. 1 mAPrecisión de posición±5%Accionamiento manual Desembrague temporal y permanente con elbotón rotativo en la carcasaCarrera nominal 5.5 mmTiempo de giro del motor140 s / 5.5 mmDuty cycle value75% (= tiempo activo 140 s / tiempo defuncionamiento 187 s)Nivel de potencia sonora, motor35 dB(A)Indicador de posición Placa de escala reversibleDatos de seguridad Clase de protección IEC/EN III, Tensión extra-baja de seguridad (SELV)Grado de protección IEC/EN IP40CEM CE según 2014/30/UETipo de acción Tipo 1Tensión de resistencia a los impulsos0.8 kVGrado de polución3Humedad ambiente Máx. 95% de RH, sin condensaciónTemperatura ambiente0...50°C [32...122°F]Temperatura de almacenamiento-30...80°C [-22...176°F]Mantenimiento sin mantenimientoPeso Peso0.48 kgColores de la carcasa Carcasa naranjaNRD24-SR-SIDatos técnicos•••••Notas de seguridadEste dispositivo ha sido diseñado para su uso en sistemas estacionarios de calefacción,ventilación y aire acondicionado y no se debe utilizar fuera del campo específico de aplicación, especialmente en aviones o en cualquier otro tipo de transporte aéreo.Sólo especialistas autorizados deben realizar la instalación. Cualquier regulación legal al respecto debe ser tenida en cuenta durante la instalación.El actuador debe estar protegido frente a la humedad. No está indicado para aplicaciones en exterior.El dispositivo no contiene piezas que pueda reparar o sustituir el usuario.El dispositivo contiene componentes eléctricos y electrónicos y no se puede desechar con los residuos domésticos. Deben tenerse en cuenta todas las normas y requerimientos locales vigentes.Modo de funcionamiento Montaje directo y sencillo Accionamiento manualAlta fiabilidad funcionalCaracterísticas del productoEl actuador se conecta a una señal de control estándar de 0...10 V y se mueve hasta la posición definida por la señal de control.Montaje directo y sencillo en la válvula con una tuerca moleteada.Es posible realizar un accionamiento manual con una palanca. Desembrague temporalpresionando el selector rotativo. Al presionar y girar a la vez el selector rotativo 90° en sentido horario, se produce un desembrague permanente.El actuador se encuentra protegido contra sobrecargas y se detiene automáticamente cuandoalcanza el final de carrera.Colores de los hilos:1 = negro 2 = rojo 3 = blanco 5 = naranjaInstalación eléctricaAlimentación del transformador de aislamiento de seguridad.Es posible realizar una conexión en paralelo de otros actuadores. Respete los datos de funcionamiento.El actuador se activa con una señal de control estándar de 0...10 V.Esquema de conexionadoAC/DC 24 V, proporcionalNRD24-SR-SI Controles de funcionamiento e indicadoresDimensiones。

24lc256系列中文

I2C™ 串行 EEPROM 系列数据手册

特征:

• 容量从 128 位到 512 千位 • 24AAXX 器件单电源供电,工作电压低至 1.8V • 低功耗 CMOS 技术: - 1 mA 典型工作电流 - 1 µA 典型待机电流 (工业级温度) • 2 线串行接口总线,兼容 I2C™ • 施密特触发器输入以抑制噪声 •输出斜率控制以消除接地反弹 • 兼容 100 kHz (1.8V)和 400 kHz (≥ 2.5V)两 种传输速率 • 24FCXX 器件工作频率为 1 MHz • 自定时擦/写周期 (包括自动擦除) • 页写入缓冲器 • 大部分器件具有硬件写保护功能 • 具有工厂编程 (QTP)功能 • 静电保护电压 > 4,000V • 擦写次数可达 1,000,000 次 • 数据保存超过 200 年 • 8 引脚 PDIP、SOIC、 TSSOP 和 MSOP 封装 • 5 引脚 SOT-23 封装 (大部分容量为 1 到 16 千位的 器件) • 提供 8 引脚 2x3mm 和 5x6mm DFN 封装 • 扩展工作温度范围: - 工业级 (I) : -40°C 到 +85°C - 汽车级 (E) :-40°C 到 +125°C

2005 Microchip Technology Inc.

DS21930A_CN 第 3 页

24AAXX/24LCXX/24FCXX

2.0 电气特性

绝对最大额定值 (†)

VCC .............................................................................................................................................................................6.5V 相对于 Vss 的所有输入和输出 ............................................................................................................ -0.6V 到 VCC +1.0V 存储温度 ................................................................................................................................................. -65°C 到 +150°C 环境温度 (使用电源时) ........................................................................................................................ -40°C 到 +125°C 所有引脚静电保护 ....................................................................................................................................................................≥ 4 kV

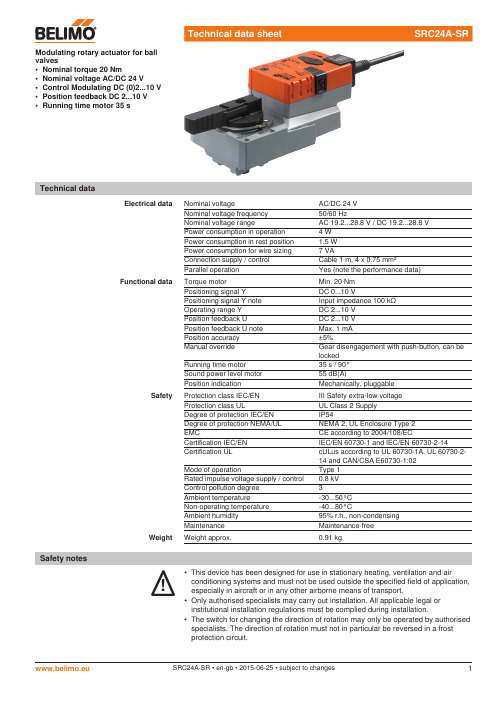

SRC24A-SR模态旋转伺服器说明书

Modulating rotary actuator for ballvalves• Nominal torque 20 Nm• Nominal voltage AC/DC 24 V• Control Modulating DC (0)2...10 V• Position feedback DC 2...10 V• Running time motor 35 sTechnical dataElectrical data Nominal voltage AC/DC 24 VNominal voltage frequency50/60 HzNominal voltage range AC 19.2...28.8 V / DC 19.2...28.8 VPower consumption in operation 4 WPower consumption in rest position 1.5 WPower consumption for wire sizing7 VAConnection supply / control Cable 1 m, 4 x 0.75 mm²Parallel operation Yes (note the performance data)Functional data Torque motor Min. 20 NmPositioning signal Y DC 0...10 VPositioning signal Y note Input impedance 100 kΩOperating range Y DC 2...10 VPosition feedback U DC 2...10 VPosition feedback U note Max. 1 mAPosition accuracy±5%Manual override Gear disengagement with push-button, can belockedRunning time motor35 s / 90°Sound power level motor55 dB(A)Position indication Mechanically, pluggableSafety Protection class IEC/EN III Safety extra-low voltageProtection class UL UL Class 2 SupplyDegree of protection IEC/EN IP54Degree of protection NEMA/UL NEMA 2, UL Enclosure Type 2EMC CE according to 2004/108/ECCertification IEC/EN IEC/EN 60730-1 and IEC/EN 60730-2-14Certification UL cULus according to UL 60730-1A, UL 60730-2-14 and CAN/CSA E60730-1:02Mode of operation Type 1Rated impulse voltage supply / control0.8 kVControl pollution degree3Ambient temperature-30...50°CNon-operating temperature-40...80°CAmbient humidity95% r.h., non-condensingMaintenance Maintenance-freeWeight Weight approx.0.91 kgSafety notes!• This device has been designed for use in stationary heating, ventilation and airconditioning systems and must not be used outside the specified field of application,especially in aircraft or in any other airborne means of transport.• Only authorised specialists may carry out installation. All applicable legal orinstitutional installation regulations must be complied during installation.• The switch for changing the direction of rotation may only be operated by authorisedspecialists. The direction of rotation must not in particular be reversed in a frostprotection circuit.• The device may only be opened at the manufacturer’s site. It does not contain any parts that can be replaced or repaired by the user.• Cables must not be removed from the device.• The device contains electrical and electronic components and must not be disposed of as household refuse. All locally valid regulations and requirements must be observed.Product featuresPrinciple of operationThe actuator is connected with a standard modulating signal of DC 0...10V and travels to the position defined by the positioning signal. Measuring voltage U serves for the electrical display of the valve position 0...100% and as slave control signal for other actuators.Simple direct mountingStraightforward direct mounting on the ball valve with only one central screw. The assembly tool is integrated in the plug-in position indication. The mounting orientation in relation to the ball valve can be selected in 90° steps.Manual overrideManual override with push-button possible (the gear is disengaged for as long as the button is pressed or remains locked).High functional reliability The actuator is overload protected, requires no limit switches and automatically stops when the end stop is reached.Adjustable angle of rotationAdjustable angle of rotation with mechanical end stops.AccessoriesDescriptionType Electrical accessoriesAuxiliary switch, add-on, 1 x SPDT S1A Auxiliary switch, add-on, 2 x SPDTS2A Feedback potentiometer 140 Ohm, add-on P140A Feedback potentiometer 200 Ohm, add-on P200A Feedback potentiometer 500 Ohm, add-on P500A Feedback potentiometer 1 kOhm, add-on P1000A Feedback potentiometer 2.8 kOhm, add-on P2800AFeedback potentiometer 5 kOhm, add-onP5000AElectrical installation!Notes• Connection via safety isolating transformer.• Parallel connection of other actuators possible. Observe the performance data.• Direction of rotation switch is covered. Factory setting: Direction of rotation Y2.Wiring diagramsAC/DC 24 V, modulatingTV VCable colours:1 = black 2 = red 3 = white 5 = orangeRotary actuator, Modulating, AC/DC 24 V, 20 Nm, Running time motor 35 sSafety notesOverride control (frost protection circuit)TCable colours:1 = black 2 = red 3 = white 5 = orangeDimensions [mm]Dimensional drawingsFurther documentation• Overview Valve-actuator combinations• Data sheets for ball valves• Installation instructions for actuators and/or ball valves • General notes for project planningRotary actuator, Modulating, AC/DC 24 V, 20 Nm, Running time motor 35 sElectrical installation。

车型校对

Modicon TM3DM24R产品数据手册说明书

i s c l a im e r : T h i s d o c u m e n t a t i o n i s n o t i n t e n d e d a s a s u b s t i t u t e f o r a n d i s n o t t o b e u s e d f o r d e t e r m i n i n g s u i t a b i l i t y o r r e l i a b i l i t y o f t h e s e p r o d u c t s f o r s p e c i f i c u s e r a p p l i c a t i o n s MainRange of productModicon TM3Product or component typeDiscrete I/O module Range compatibility Modicon M241Modicon M221Modicon M251Discrete input number 16 input conforming to IEC 61131-2 Type 1Discrete input logic Sink or source (positive/negative)Discrete input voltage 24 VDiscrete input current 7 mA for inputDiscrete output type Relay normally openDiscrete output number 8Discrete output logic Positive or negativeDiscrete output voltage 24 V DC for relay output240 V AC for relay outputDiscrete output current2000 mA for relay output ComplementaryDiscrete I/O number24Current consumption 5 mA at 5 V DC via bus connector at state off0 mA at 24 V DC via bus connector at state on0 mA at 24 V DC via bus connector at state off65 mA at 5 V DC via bus connector at state onDiscrete input voltage type DCVoltage state1 guaranteed 15...28.8 V for inputCurrent state 1 guaranteed >= 2.5 mA for inputVoltage state 0 guaranteed 0...5 V for inputCurrent state 0 guaranteed <= 1 mA for inputInput impedance 3.4 kOhmResponse time4 ms for turn-on4 ms for turn-off500 V AC between output and internal logicNon-insulated between outputs500 V AC between input and internal logic1500 V AC between input groups and output groups750 V AC between open contactMarking CEMounting support Top hat type TH35-15 rail conforming to IEC 60715Top hat type TH35-7.5 rail conforming to IEC 60715Plate or panel with fixing kitHeight90 mmDepth84.6 mmWidth42.9 mmEnvironmentStandards EN/IEC 61010-2-201EN/IEC 61131-2Product certifications C-TickcULusResistance to electrostatic discharge 4 kV (on contact) conforming to EN/IEC 61000-4-28 kV (in air) conforming to EN/IEC 61000-4-2Resistance to electromagnetic fields10 V/m at 80 MHz...1 GHz conforming to EN/IEC 61000-4-33 V/m at 1.4 GHz...2 GHz conforming to EN/IEC 61000-4-31 V/m at2 GHz...3 GHz conforming to EN/IEC 61000-4-3 Resistance to magnetic fields30 A/m at 50...60 Hz conforming to EN/IEC 61000-4-8 Resistance to fast transients 2 kV for relay output conforming to EN/IEC 61000-4-41 kV for I/O conforming to EN/IEC 61000-4-4Surge withstand 1 kV for input in common mode conforming to EN/IEC 61000-4-52 kV for output in common mode conforming to EN/IEC 61000-4-5Resistance to conducted disturbances, induced by radio frequency fields 10 Vrms at 0.15...80 MHz conforming to EN/IEC 61000-4-63 Vrms at spot frequency (2, 3, 4, 6.2, 8.2, 12.6, 16.5, 18.8, 22, 25 MHz) conforming to Marine specification (LR, ABS, DNV, GL)Electromagnetic emission Radiated emissions, test level: 40 dBμV/m QP with class A, condition of test: 10 m (radio frequency:30...230 MHz) conforming to EN/IEC 55011Radiated emissions, test level: 47 dBμV/m QP with class A, condition of test: 10 m (radio frequency:230 MHz...1 GHz) conforming to EN/IEC 55011Ambient air temperature for operation-10...55 °C for horizontal installation-10...35 °C for vertical installationAmbient air temperature for storage-25...70 °CRelative humidity10...95 % without condensation in operation10...95 % without condensation in storageIP degree of protection IP20 with protective cover in placePollution degree2Operating altitude0...2000 mStorage altitude0...3000 mVibration resistance 3.5 mm (vibration frequency: 5...8.4 Hz) on DIN rail3 gn (vibration frequency: 8.4...150 Hz) on DIN rail3.5 mm (vibration frequency: 5...8.4 Hz) on panel3 gn (vibration frequency: 8.4...150 Hz) on panelShock resistance15 gn (test wave duration:11 ms)Product end of life instructionsAvailableEnd of life manual(*)8.5 mm/0.33 in. when the clamp is pulled out.Incorrect Mounting(1)Install a mounting strip Mounting Hole LayoutWiring Diagram (Source)(*)Type T fuse (1)The COM0, COM1 and COM2 terminals are not connected internally.(2)To improve the life time of the contacts, and to protect from potential inductive load damage, it is recommended to connect a free wheeling diode in parallel t (A)Sink wiring (positive logic)(C)Source wiring (positive logic)Wiring Diagram (Sink)(*)Type T fuse (1)The COM0, COM1 and COM2 terminals are not connected internally.(2)To improve the life time of the contacts, and to protect from potential inductive load damage, it is recommended to connect a free wheeling diode in parallel t (B)Source wiring (negative logic)(D)Sink wiring (negative logic)。

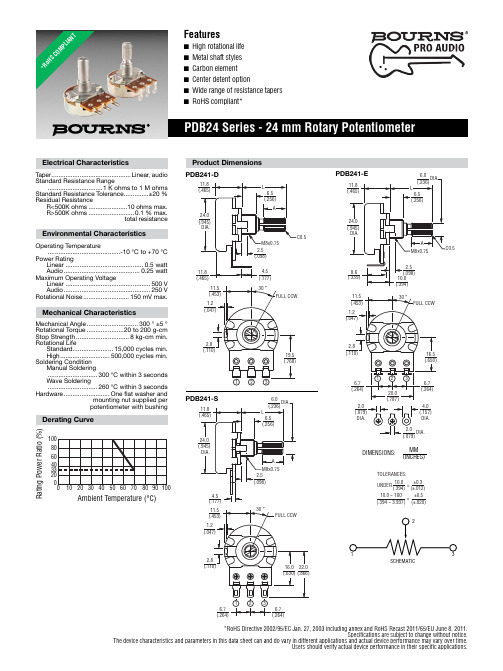

PDB24系列24mm旋转潜力电阻器说明书

Features■ High rotational life ■ Metal shaft styles ■ Carbon element ■ Center detent option■ Wide range of resistance tapers ■ RoHS compliant**RoHS Directive 2002/95/EC Jan. 27, 2003 including annex and RoHS Recast 2011/65/EU June 8, 2011.Specifi cations are subject to change without notice.The device characteristics and parameters in this data sheet can and do vary in different applications and actual device performance may vary over time.Users should verify actual device performance in their specifi c applications.Electrical CharacteristicsTaper .............................................Linear, audioStandard Resistance Range...............................1 K ohms to 1 M ohms Standard Resistance Tolerance ..............±20 %Residual ResistanceR<500K ohms ......................10 ohms max. R>500K ohms ..........................0.1 % max. total resistanceEnvironmental CharacteristicsOperating Temperature.........................................-10 °C to +70 °C Power Rating Linear ............................................0.5 watt Audio ...........................................0.25 watt Maximum Operating Voltage Linear ................................................500 V Audio .................................................250 V Rotational Noise ..........................150 mV max.Mechanical CharacteristicsMechanical Angle .............................300 ° ±5 °Rotational Torque .....................20 to 200 g-cm Stop Strength ..............................8 kg-cm min.Rotational Life Standard .......................15,000 cycles min. High ............................500,000 cycles min.Soldering Condition Manual Soldering............................300 °C within 3 seconds Wave Soldering............................260 °C within 3 seconds Hardware ..........................O ne fl at washer and mounting nut supplied per potentiometer with bushingDerating CurveAmbient Temperature (°C)204050607080901003010020334060801000R a t i n g P o w e r R a t i o (%)Product Dimensions PDB241-DUNDER=10.0(.394)TOLERANCES:±0.3(±.012)=10.0 ~ 100(.394 ~ 3.937)±0.5(±.020)DIMENSIONS:MM(INCHES)SCHEMATIC*Ro H SC OM P L I A N TSpecifi cations are subject to change without notice.The device characteristics and parameters in this data sheet can and do vary in different applications and actual device performance may vary over time.Users should verify actual device performance in their specifi c applications.Product DimensionsDIMENSIONS:MM(INCHES)REV . 02/15F TypeP TypeK TypeL 20.0(.787)25.0(.984)30.0(1.181)F12.0(.472)12.0(.472)12.0(.472)L 20.0(.787)25.0(.984)30.0(1.181)A 10.0(.394)12.0(.472)12.0(.472)D1.5(.059) 2.5(.098) 4.0(.157)L20.0(.787)25.0(.984)30.0(1.181)How To OrderPDB24 1 - E 4 25 K - 103 A2ModelNo. of Sections• 1 = Single Section/ Standard Rotational Life • 2 = Single Section/ High Rotational Life Terminal Confi guration (Pin Layout)(see individual drawings) • E = Solder Lugs Rear Facing • S = Solder Lugs Down Facing • D = PC Pins Front Facing Detent Option• 2 = Center Detent • 4 = No Detents Standard Shaft Length • 20 = 20 mm • 25 = 25 mm • 30 = 30 mm Shaft Style• K = Metal Knurled Type Shaft 18 Toothed Serration Type • F = Metal Flatted Shaft • P = Metal Plain Shaft Resistance Code (See Table)Resistance Taper (See Taper Chart)Taper Series followed by Curve Number Other styles available.Standard Resistance TableResistance Resistance (Ohms) Code 1,000 102 2,000 202 5,000 502 10,000 103 20,000 203 50,000 503 100,000 104 200,000 204 250,000 254 500,000 504 1,000,000 105TapersA Series TapersT e r m i n a l 1-2 O u t p u t V o l t a g eT e r m i n a l 1-3 I n p u t V o l t a g eX 100 (%)Rotational Travel (%)C Series TapersT e r m i n a l 1-2 O u t p u t V o l t a g eT e r m i n a l 1-3 I n p u t V o l t a g eX 100 (%)Rotational Travel (%)B Series TapersRotational Travel (%)8090T e r m i n a l 1-2 O u t p u t V o l t a g e T e r m i n a l 1-3 I n p u t V o l t a g eX 100 (%Applications■ Various commercial applications ■ Electric guitars■ Sound processing equipment ■ Guitar and sound system amplifi ers ■ Appliances。

24VAC±20% 50 60Hz 9.5VA电源驱动型电机说明书

† Use flexible metal conduit. Push the listed conduit fitting device over the actuator’s cable to butt against the enclosure. Screw in conduit connector. Jacket the actuators input wiring with listed flexible conduit. Properly terminate the conduit in a suitable junction box. Rated impulse Voltage 800V. Type of action 1. Control pollution degree 3.AVKX24-3On/Off, Floating Point, Electronic Fail-Safe, Linear, 24 VD a t e c r e a t e d , 11/03/2016 - S u b j e c t t o c h a n g e . © B e l i m o A i r c o n t r o l s (U S A ), I n c .Meets cULus requirements without the need of an electrical groundconnection.Provide overload protection and disconnect as required.Actuators may be connected in parallel. Power consumption and inputimpedance must be observed.Control signal may be pulsed from either the Hot (Source) or Common(Sink) 24 VAC line.Actuators may be connected in parallel if not mechanically linked. Powerconsumption and input impedance must be observed.Actuators with plenum cable do not have numbers; use color codes instead.!WARNING! LIVE ELECTRICAL COMPONENTS!During installation, testing, servicing and troubleshooting of this product, it may be necessary to work with live electrical components. Have a qualified licensed electrician or other individual who has been properly trained in handling live electrical components perform these tasks. Failure to follow all electrical safety precautions when exposed to live electrical components could result in death or serious injury.AVKX24-3On/Off, Floating Point, Electronic Fail-Safe, Linear, 24 VD a t e c r e a t e d , 11/03/2016 - S u b j e c t t o c h a n g e . © B e l i m o A i r c o n t r o l s (U S A ), I n c .。

ATTINY24A-SSU中文资料