PO125中文资料

ADS1250资料

ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. BurrBrown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection methods.

1kHz Input; 0.1dBΒιβλιοθήκη below FSat DC

90

VREF = 4.096V ±0.1V 60

1 ±200

IOH = –500µA IOL = 500µA

V V V V

V = +5VDC V = +5VDC

100 +85 +100

VDC mA mA mW °C °C

–40 –60

NOTES: (1) In order to achieve the converter’s full-scale range, the input must be fully differential. If the input is single-ended (+VIN or –VIN is fixed), then the full-scale range is one-half that of the differential range. (2) Applies to full-differential signals. (3) The common-mode rejection test is performed with a 100mV differential input.

车载诊断技术OBD

EOBD(European On-Board Diagnostics),简称OBD(On-Board Diagnostics),即“车载诊断技术”或简称“车载诊断”。

欧I和欧II排放法规阶段的发动机管理系统都带有车载故障诊断功能,但是在欧III排放法规中,OBD隐含着专门用於排放控制的意思,根据定义,它是“用於排放控制的车载诊断系统”,而且必须能够通过储存在计算机存储器中的失效代码来识别故障的可能范围。

美国加利福尼亚州率先于1994年以立法的形式提出了利用车载诊断技术对排放控制装置实行故障监测的要求,称为OBDⅡ。

后来,欧洲也制订了从2000年跟欧III同时生效的指令70/220/EEC(98/69/EC)附件XI。

该指令适用于欧III和欧IV排放法规,内容包括:1. 所有车辆必须装备OBD系统,其设计、制造和安装应能确保车辆在整个生命期内识别劣化类型和故障类型。

2. 当排放控制系统(与发动机电子管理系统以及排气系统或蒸发物控制系统中,任何与排放有关、向电子控制单元提供输入信号或从电子控制单元接受输出信号的零部件)失效导致排放超过规定的极限值(下文称为失效限值)时,OBD系统必须指示它们的失效。

3. 汽油机OBD系统必须监测下列项目:三效催化转化器;发动机在一定工况区域内出现的缺火;氧传感器劣化;排放控制系统中其它一旦失效就会导致排放超过失效限值的零部件;排放控制系统中传感器和执行器电路是否接通;对于蒸发排放物控制系统中的炭罐控制阀,至少应监测其电路是否接通。

4. 每次发动机起动时,都必须开始一系列的诊断检测。

5. OBD系统应带有能让驾驶者感知故障存在的故障指示器,该器件只能用於指示启动了紧急程序或跛行回家程序(发动机管理系统发生故障时放弃部分控制功能,在不完备的状态下勉强维持车辆行驶的功能)。

排放一旦超过失效限值,发动机控制进入永久性排放失效模式(发动机管理控制器永久性地切换到以设定值代替一种失效零部件或系统输入信号的情形。

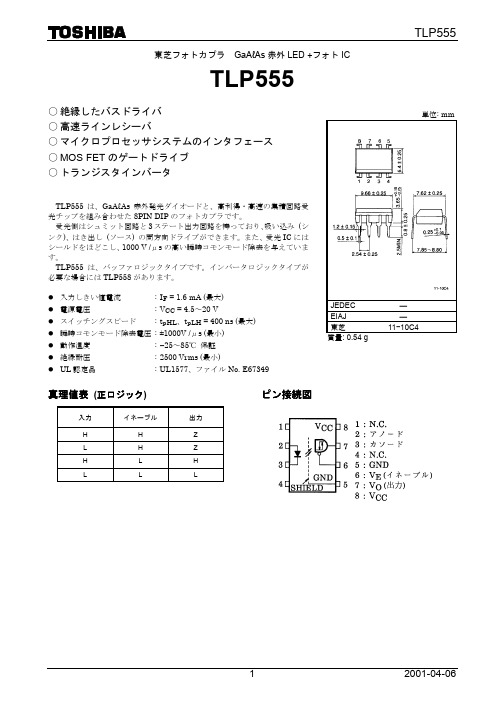

2N2222中文资料_数据手册_参数

Product specification

2N2222; 2N2222A

SYMBOL

PARAMETER

CONDITIONS

MIN. MAX. UNIT

Switching times (between 10% and 90% levels); see Fig.2

DISCRETE SEMICONDUCTORS

DATA SHEET

M3D125

2N2222; 2N2222A NPN switching transistors

Product specification Supersedes data of September 1994 File under Discrete Semiconductors, SC04

DC current gain 2N2222A

IE = 0; VCB = 60 V IE = 0; VCB = 60 V; Tamb = 150 °C IC = 0; VEB = 3 V IC = 0.1 mA; VCE = 10 V IC = 1 mA; VCE = 10 V IC = 10 mA; VCE = 10 V IC = 150 mA; VCE = 1 V; note 1 IC = 150 mA; VCE = 10 V; note 1 IC = 10 mA; VCE = 10 V; Tamb = −55 °C

SYMBOL

PARAMETER

Rth j-a Rth j-c

thermal resistance from junction to ambient thermal resistance from junction to case

CONDITIONS in free air

dcp010505中文资料

DCP01B 列微型1W 隔离非稳压DC / DC 转换器特征q 高达85%效率q 热保护q 设备到设备同步q 短路保护q EN55022 B 级EMC 性能q UL1950认证组件q JEDEC PDIP-14和鸥翼式套餐应用q q q qPOINT-OF-使用的电源转换消除接地环路数据采集工业控制仪器q 测试设备说明该DCP01B 系列是1W,不规范,隔离式DC / DC 转换器.需要最少的外部组件,包括芯片设备保护,DCP01B 系列提供额外的功能,如输出禁用和开关频率的同步.其采用了高度集成的封装设计成果在高度可靠的产品的功率密度40W/in 3(2.4W/cm 3).这些功能的结合和小尺寸使得DCP01B 适用于广泛的应用范围.SYNCOUT800kHz Oscillator÷2ResetV OUTPower Stage0VSYNCINWatch-dog/start-upPSU Thermal ShutdownV SPower Controller ICI BIAS0VInternational Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132//®版权的©2000, Texas Instruments, Incorporated PDS-1586C1Printed in U.S.A. September, 2000DCP01B技术指标At TA= +25°C, unless otherwise specified.DCP01B SERIESPARAMETER OUTPUT PowerRippleVoltage vs TempVoltage LINE RegulationSWITCHING/SYNCHRONIZATION Oscillator Frequency (f OSC )Sync Input Low Sync Input CurrentDisable TimeCapacitance Loading on SYNC RELIABILITY DemonstratedShutdown Current TEMPERATUOperatingINPUT VOLTAGE (V)V SPRODUCT DCP010505B DCP010505DB DCP010512B DCP010512DB DCP010515B DCP010515DB DCP011512DB DCP011515DB DCP012415DB DCP012405BMIN 4.54.54.54.54.54.513.513.521.621.6TYP 55555515152424MAX 5.55.55.55.55.55.516.516.526.426.4MIN 4.75±4.2511.4±11.414.25±14.25±11.4±14.25±14.254.75OUTPUT VOLTAGE (V)V NOM75% LOAD(2)TYP 5±512±1215±15±12±15±155MAX 5.25±5.7512.6±12.615.75±15.75±12.6±15.75±15.755.2510% TO 100% LOAD (3)TYP 19182119261911121013MAX 31323837424139393523LOADREGULATION (%)–40NO LOAD CURRENT (mA)I Q0% LOADTYP 20222940344219201714100% LOADTYP 80818582828578807677Switching Frequency = fOSC/2V SYNC = +2V External T A = +55°C1503+100EFFICIENCY (%)7523751s Flash Test 60s Test, UL1950(1)CONDITIONS 100% Full LoadO/P Capacitor = 1µF, 50% LoadRoom to ColdRoom to Hot–101118000.4MIN TYP 0.97200.0460.01610MAX UNITSW mVp-p %/°C %/°C %kVrms kVrms%/1% of VSkHzV µA µs pF FITS °C mA°CBARRIERCAPACITANCE (pF)C ISOV ISO = 750VRMSTYP 3.63.85.14.03.84.72.52.53.82.5NOTES: (1) During UL1950 recognition tests only. (2) 100% Load Current = 1W/V NOMTYP. (3) Load regulation = (VOUTat 10% Load – VOUTat 100% Load)/VOUTat 75% Load.绝对最大额定值Input Voltage:5V Input Models .................................................................................. 7V 24V Input Models .............................................................................. 18V 15V Input Models .............................................................................. 29V Storage Temperature ...................................................... –60°C to +125°C Lead Temperature (soldering, 10s) ................................................. 270°C静电放电敏感度这种集成电路可ESD 而损坏.Burr-Brown 建议所有集成电路与适当的预防措施进行处理.如果不遵守正确的搬运和安装程序,可以造成损坏.ESD 损害的范围可以从细微的性能下降,完成设备故障.精密集成电路可能更容易受到损害,因为非常小的参数变化可能导致设备不能满足其公布的规格.订购信息DCP01Basic Model Number: 1W Product Voltage Input:5V InVoltage Output:5V Out Dual Output:Model Revision:Package Code:P = PDIP-14P-U = PDIP-14 Gull-Wing®0505 ( D ) ( B ) ()DCP01B2引脚配置(单DIP和鸥翼)Top View DIP 引脚配置(双DIP和鸥翼)Top View DIPVS 0V 1214 SYNCINVS0V1214 SYNCIN DCP01B0V+VOUTNC 5678SYNCOUT0V+VOUT–VOUT567DCP01DB8SYNCOUTPIN定义(单DIP)PIN #12567814PIN NAMEVS0V0V+VOUTNCSYNCOUTSYNCINDESCRIPTIONVoltage InputInput Side CommonOutput Side Common+Voltage OutNot ConnectedUnrectified Transformer OutputSynchronization PinPIN定义(双DIP)PIN #12567814PIN NAMEVS0V0V+VOUT–VOUTSYNCOUTSYNCINDESCRIPTIONVoltage InputInput Side CommonOutput Side Common+Voltage Out–Voltage OutUnrectified Transformer OutputSynchronization Pin包装/订货信息PACKAGE DRAWING NUMBER010-1010-2010-1010-2010-1010-2010-1010-2010-1010-2010-1010-2010-1010-2010-1010-2010-1010-2010-1010-2SPECIFIEDTEMPERATURERANGE–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°C–40°Ctotototototototototototototototototototo+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°C+100°CPACKAGEMARKINGDCP010505BPDCP010505BP-UDCP010512BPDCP010512BP-UDCP010515BPDCP010515BP-UDCP012405BPDCP012405BP-UDCP010505DBPDCP010505DBP-UDCP010512DBPDCP010512DBP-UDCP010515DBPDCP010515DBP-UDCP011512DBPDCP011512DBP-UDCP011515DBPDCP011515DBP-UDCP012415DBPDCP012415DBP-UORDERINGNUMBER(1)DCP010505BPDCP010505BP-U/700DCP010512BPDCP010512BP-U/700DCP010515BPDCP010515BP-U/700DCP012405BPDCP012405BP-U/700DCP010505DBPDCP010505DBP-U/700DCP010512DBPDCP010512DBP-U/700DCP010515DBPDCP010515DBP-U/700DCP011512DBPDCP011512DBP-U/700DCP011515DBPDCP011515DBP-U/700DCP012415DBPDCP012415DBP-U/700TRANSPORTMEDIARailsTape and ReelRailsTape and ReelRailsTape and ReelRailsTape and ReelRailsTape and ReelRailsTape and ReelRailsTape and ReelRailsTape and ReelRailsTape and ReelRailsTape and ReelPRODUCTSingleDCP010505BP DCP010505BP-U DCP010512BP DCP010512BP-U DCP010515BP DCP010515BP-U DCP012405BP DCP012405BP-U DualDCP010505DBP DCP010505DBP-U DCP010512DBP DCP010512DBP-U DCP010515DBP DCP010515DBP-U DualDCP011512DBP DCP011512DBP-U DCP011515DBP DCP011515DBP-U DCP012415DBP DCP012415DBP-UPACKAGEDIP-14 DIP-14 Gull-WingDIP-14 DIP-14 Gull-WingDIP-14 DIP-14 Gull-WingDIP-14 DIP-14 Gull-WingDIP-14 DIP-14 Gull-WingDIP-14 DIP-14 Gull-WingDIP-14 DIP-14 Gull-WingDIP-14 DIP-14 Gull-WingDIP-14 DIP-14 Gull-WingDIP-14 DIP-14 Gull-WingNOTE: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /700 indicates 700 devices per reel). Ordering 700 piecesof “DCP010505BP-U/700” will get a single 700-piece Tape and Reel.The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumesno responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to changewithout notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrantany BURR-BROWN product for use in life support devices and/or systems.®3DCP01B典型性能曲线At TA= +25°C, unless otherwise noted.DCP010505BOUTPUT RIPPLE vs LOAD (20MHz BW)504540Ripple (mVp-p)5.5DCP010505B VOUTvs VS5.45.35.25.11µF Ceramic 4.7µF Ceramic 10µF Ceramic35VOUT(V)302520151050102030405060708090100Load (%)5.04.94.84.74.64.54.44.54.64.74.84.95.0V S (V)5.1 5.2 5.3 5.4 5.5DCP010505B VOUTvs LOAD5.85.75.65.55.45.35.25.15.04.94.84.7102030405060708090100Load (%)55102060Efficiency (%)DCP010505B EFFICIENCY vs LOAD8580757065VOUT(V)30405060708090100Load (%)DCP010505DB VOUTvs LOAD5.85.75.65.55.45.35.25.15.04.94.84.7102030405060708090100Load (%)55102060Efficiency (%)DCP010505DB EFFICIENCY vs LOAD85+V OUT –V OUT80757065VOUT(V)30405060708090100Load (%)®DCP01B4h t p s :/s h o p 29717632.t a o b a o .c o m /s h o p /v i e w _s h o p .h t m ?s p m =a 313o .201708b a n .c a t e g o r y .d 53.2f 0d 380T a b P o S &my t m e n u =md i a n p u &u s e r _n u m b e r _i d =11563490DCP010515B VOUTvs LOAD1817.517VOUT(V)DCP010515B EFFICIENCY vs LOAD85807516.51615.51514.514102030405060708090100Load (%)Efficiency (%)7065605550102030405060708090100Load (%)®5DCP01B典型性能曲线At TA= +25°C, unless otherwise noted.(续)DCP010512B VOUTvs LOAD14.51413.5DCP010512B EFFICIENCY vs LOAD908580Efficiency (%)V OUT(V)7570656055501312.51211.511102030405060708090100Load (%)102030405060708090100Load (%)DCP010512DB VOUTvs LOAD14.514.013.5858075DCP010512DB EFFICIENCY vs LOADEfficiency (%)+V OUT –V OUT10203040506070809010013.0VOUT(V)12.512.011.511.010.510.00Load (%)7065605550102030405060708090100Load (%)DCP010515B VOUTvs LOAD1817.517VOUT(V)DCP010515B EFFICIENCY vs LOAD85807516.51615.51514.514102030405060708090100Load (%)Efficiency (%)7065605550102030405060708090100Load (%)®5DCP01Bh t p s :/s h o p 29717632.t a o b a o .c o m /s h o p /v i e w _s h o p .h t m ?s p m =a 313o .201708b a n .c a t e g o r y .d 53.2f 0d 380T a b P o S &my t m e n u =md i a n p u &u s e r _n u m b e r _i d =11563490。

74VHC125_04中文资料

1/12November 2004s HIGH SPEED: t PD = 3.8ns (TYP.) at V CC = 5V sLOW POWER DISSIPATION:I CC = 4 µA (MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28% V CC (MIN.)s POWER DOWN PROTECTION ON INPUTS sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 8mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 125s IMPROVED LATCH-UP IMMUNITY sLOW NOISE: V OLP = 0.8V (MAX.)DESCRIPTIONThe 74VHC125 is an advanced high-speed CMOS QUAD BUS BUFFERS fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.The device requires the 3-STATE control input G to be set high to place the output in to the high impedance state.Power down protection is provided on all inputs and 0 to 7V can be accepted on inputs with no regard to the supply voltage. This device can be used to interface 5V to 3V.All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.74VHC125QUAD BUS BUFFERS (3-STATE)Figure 1: Pin Connection And IEC Logic SymbolsTable 1: Order CodesPACKAGE T & R SOP 74VHC125MTR TSSOP74VHC125TTR74VHC1252/12Figure 2: Input Equivalent CircuitTable 2: Pin DescriptionTable 3: Truth TableX : Don‘t CareZ : High ImpedanceTable 4: Absolute Maximum RatingsAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions isnot impliedTable 5: Recommended Operating Conditions1) V IN from 30% to 70% of VCCPIN N°SYMBOL NAME AND FUNCTION 1, 4, 10, 131G to 4G Output Enable Inputs 2, 5, 9, 121A to 4A Data Inputs 3, 6, 8, 111Y to 4Y Data Outputs 7GND Ground (0V)14V CCPositive Supply VoltageA G Y X H Z L L L HLHSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7.0V V I DC Input Voltage -0.5 to +7.0V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current - 20mA I OK DC Output Diode Current ± 20mA I ODC Output Current± 25mA I CC or I GND DC V CC or Ground Current± 50mA T stgStorage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2 to 5.5V V I Input Voltage 0 to 5.5V V O Output Voltage 0 to V CC V T op Operating Temperature-55 to 125°C dt/dvInput Rise and Fall Time (note 1) (V CC = 3.3 ± 0.3V) (V CC = 5.0 ± 0.5V)0 to 1000 to 20ns/V74VHC1253/12Table 6: DC SpecificationsTable 7: AC Electrical Characteristics (Input t r = t f = 3ns)(*) Voltage range is 3.3V ± 0.3V (**) Voltage range is 5.0V ± 0.5VSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V3.0 to 5.50.7V CC0.7V CC0.7V CCV ILLow Level Input Voltage2.00.50.50.5V3.0 to 5.50.3V CC0.3V CC0.3V CCV OHHigh Level Output Voltage2.0I O =-50 µA 1.9 2.0 1.9 1.9V3.0I O =-50 µA 2.9 3.0 2.9 2.94.5I O =-50 µA 4.4 4.54.4 4.43.0I O =-4 mA 2.58 2.48 2.44.5I O =-8 mA 3.943.83.7V OLLow Level Output Voltage2.0I O =50 µA 0.00.10.10.1V3.0I O =50 µA 0.00.10.10.14.5I O =50 µA 0.00.10.10.13.0I O =4 mA 0.360.440.554.5I O =8 mA 0.360.440.55I OZHigh Impedance Output Leakage Current5.5V I = V IH or V IL V O = V CC or GND ±0.25± 2.5± 2.5µA I I Input Leakage Current0 to 5.5V I = 5.5V or GND ± 0.1± 1± 1µA I CCQuiescent Supply Current5.5V I = V CC or GND44040µA SymbolParameterTest ConditionValueUnitV CC (V)C L (pF)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t PLH t PHLPropagation Delay Time3.3(*)15 5.68.0 1.09.5 1.09.5ns 3.3(*)508.111.5 1.013.0 1.013.05.0(**)15 3.8 5.5 1.0 6.5 1.0 6.55.0(**)50 5.37.5 1.08.5 1.08.5t PLZ t PHZOutput DisableTime 3.3(*)15R L = 1 K Ω 5.48.0 1.09.5 1.09.5ns 3.3(*)50R L = 1 K Ω7.911.5 1.013.0 1.013.05.0(**)15R L = 1 K Ω 3.6 5.1 1.0 6.0 1.0 6.05.0(**)50R L = 1 K Ω 5.17.1 1.08.0 1.08.0t PZL t PZH Output EnableTime3.3(*)50R L = 1 K Ω9.513.2 1.015.0 1.015.0ns 5.0(**)50R L = 1 K Ω6.18.81.010.01.010.074VHC1254/12Table 8: Capacitive Characteristics1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /4 (per circuit)Table 9: Dynamic Switching Characteristics1) Worst case package.2) Max number of outputs defined as (n). Data inputs are driven 0V to 5.0V, (n-1) outputs switching and one output at GND.3) Max number of data inputs (n) switching. (n-1) switching 0V to 5.0V. Inputs under test switching: 5.0V to threshold (V ILD ), 0V to threshold (V IHD ), f=1MHz.SymbolParameterTest ConditionValue UnitT A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 6101010pF C OUT OutputCapacitance8pF C PDPower Dissipation Capacitance (note 1)16pF SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V OLP Dynamic Low Voltage Quiet Output (note 1, 2) 5.0C L = 50 pF0.30.8V V OLV -0.8-0.3V IHD Dynamic High Voltage Input (note 1, 3) 5.0 3.5VV ILDDynamic Low Voltage Input (note 1, 3)5.0 1.5V74VHC1255/12Figure 3: Test CircuitC L =15/50pF or equivalent (includes jig and probe capacitance)R L = R1 = 1K Ω or equivalentR T = Z OUT of pulse generator (typically 50Ω)Figure 4: Waveform - Propagation Delays (f=1MHz; 50% duty cycle)TESTSWITCH t PLH , t PHL Open t PZL , t PLZ V CC t PZH , t PHZGND74VHC125Figure 5: Waveform - Output Enable And Disable Time (f=1MHz; 50% duty cycle)6/1274VHC1257/12DIM.mm.inch MIN.TYPMAX.MIN.TYP.MAX.A 1.35 1.750.0530.069A10.10.250.0040.010A2 1.10 1.650.0430.065B 0.330.510.0130.020C 0.190.250.0070.010D 8.558.750.3370.344E 3.84.00.1500.157e 1.270.050H 5.8 6.20.2280.244h 0.250.500.0100.020L 0.4 1.270.0160.050k 0°8°0°8°ddd0.1000.004SO-14 MECHANICAL DATA0016019D74VHC1258/12DIM.mm.inchMIN.TYPMAX.MIN.TYP.MAX.A 1.20.047A10.050.150.0020.0040.006A20.81 1.050.0310.0390.041b 0.190.300.0070.012c 0.090.200.0040.0089D 4.95 5.10.1930.1970.201E 6.2 6.4 6.60.2440.2520.260E1 4.34.4 4.480.1690.1730.176e 0.65 BSC0.0256 BSCK 0˚8˚0˚8˚L0.450.600.750.0180.0240.030TSSOP14 MECHANICAL DATAcEbA2A E1D1PIN 1 IDENTIFICATIONA1LKe0080337D74VHC125 Tape & Reel SO-14 MECHANICAL DATAmm.inchDIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992C12.813.20.5040.519D20.20.795N60 2.362T22.40.882Ao 6.4 6.60.2520.260Bo99.20.3540.362Ko 2.1 2.30.0820.090Po 3.9 4.10.1530.161P7.98.10.3110.3199/1274VHC125Tape & Reel TSSOP14 MECHANICAL DATAmm.inch DIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992 C12.813.20.5040.519 D20.20.795N60 2.362T22.40.882 Ao 6.7 6.90.2640.272 Bo 5.3 5.50.2090.217 Ko 1.6 1.80.0630.071 Po 3.9 4.10.1530.161 P7.98.10.3110.31910/1274VHC125 Table 10: Revision HistoryDate Revision Description of Changes 12-Nov-20047Order Codes Revision - pag. 1.11/1274VHC125Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronicsAll other names are the property of their respective owners© 2004 STMicroelectronics - All Rights ReservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America12/12。

OPA512中文资料

CIRCUIT q SMALL TO-3 PACKAGE

DESCRIPTION

The OPA512 is a high voltage, very-high current operational amplifier designed to drive a wide variety of resistive and reactive loads. Its complementary class A/B output stage provides superior performance in applications requiring freedom from cross-over distortion. User-set current limit circuitry provides protection to the amplifier and load in fault conditions. A resistor-programmable voltage-current limiter circuit may be used to further protect the amplifier from damaging conditions.

IO = 80mA IO = 5A

±(|VS| – 5) ±(|VS| – 5)

10

2V Step

2

2.5

4

Specified Temp. Range

G=1

Specified Temp. Range

G > 10

±(|VS| – 7)

*

*

15

*

OPA4340中文资料

–0.3 80 70 66

±0.2

±0.2

8 25 3

92 84 80

1013 || 3 1013 || 6

±10 ±60 ±10

(V+) +0.3

OPEN-LOOP GAIN Open-Loop Voltage Gain

TA = –40°C to +85°C

TA = –40°C to +85°C

TA = –40°C to +85°C

TA = –40°C to +85°C

TA = –40°C to +85°C

TA = –40°C to +85°C Short-Circuit Current Capacitive Load Drive

POWER SUPPLY Specified Voltage Range Operating Voltage Range Quiescent Current (per amplifier)

and 8-pin DIP packages. The quad (OPA4340) packages are the space-saving SSOP-16 surface mount, SO-14 surface mount, and the 14-pin DIP. All are specified from –40°C to +85°C and operate from –55°C to +125°C. A SPICE macromodel is available for design analysis.

IO = 0, VS = +5V

θJA

106

124

106

74LS125中文资料

TRUTH TABLES LS125A

INPUTS E L L H D L H X OUTPUT L H (Z) INPUTS E H H L D L H X OUTPUT L H (Z)

LS126A ORDERING INFORMATION

SN54LSXXXJ SN74LSXXXN SN74LSXXXD Ceramic Plastic SOIC

14

8

B

1 7

2.

DIMENSION L" TO CENTER OF LEADS WHEN FORMED PARALLEL.

3.

DIMENSION B" DOES NOT INCLUDE MOLD FLASH.

4. 5.

ROUNDED CORNERS OPTIONAL. 646 05 OBSOLETE, NEW STANDARD 646 06.

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS (TA = 25°C)

Limits Symbol tPLH tPLH tPHL tPHL tPZH Output Enable Time to HIGH Level Output Enable Time to LOW Level Output Disable Time from HIGH Level Output Disable Time from LOW Level Propagation Delay, Data to Output Parameter LS125A LS126A LS125A LS126A LS125A LS126A LS125A LS126A LS125A LS126A LS125A LS126A Min Typ 9.0 9.0 7.0 8.0 12 16 15 21 Max 15 15 ns 18 18 20 ns 25 25 ns 35 20 ns 25 20 ns 25 FIgures 3, 5 Figures 4, 5 VCC = 5.0 V CL = 5.0 pF RL = 667 Ω Figures 3, 5 Figures 4, 5 VCC = 5.0 V CL = 45 pF RL = 667 Ω Figure 2 Unit Test Conditions

RP05-1215DF中文资料

POWERLINE - DC/DC-Converter

F-Ser., 5W, DIP24, Regul. 2:1 Wide Input Range (Single & Dual Output) Telecom/Networking applications 5 Watts in DIP24 Package 2:1 Wide Input Range Include 3.3VDC Output 19-18V, 18-36V and 36-75V Input Typical Efficiency up to 80% Regulated Outputs

● ● ● ● ● ●

Low Profile, 10.2 mm Height No Derating to 70°C No other Components required Over Current Protection, Continuous MTBF 1.131 x 106 Hours Through Hole and SMD-Pinning

Input Voltage Range 12V types nominal 24V types nominal 48V types nominal 9-18V 18-36V 36-75V Pi Type ±2% ±2% 75mVp-p max. ±1% p-p of Vout max. ±0.2% max. ±0.2% max. ±0.5% 1.0% See Selection Guide Table ±0.02%/°C Continuous 100kHz, min. 1600VDC, min. 3000VDC, min. 109 Ω min. 300pF max. -25°C to +71°C -55°C to +105°C 100°C max. Free-air Convection Non-Conductive Black Plastik 1.131 x 106 Hours 31.8 x 20.3 x 10.2 mm

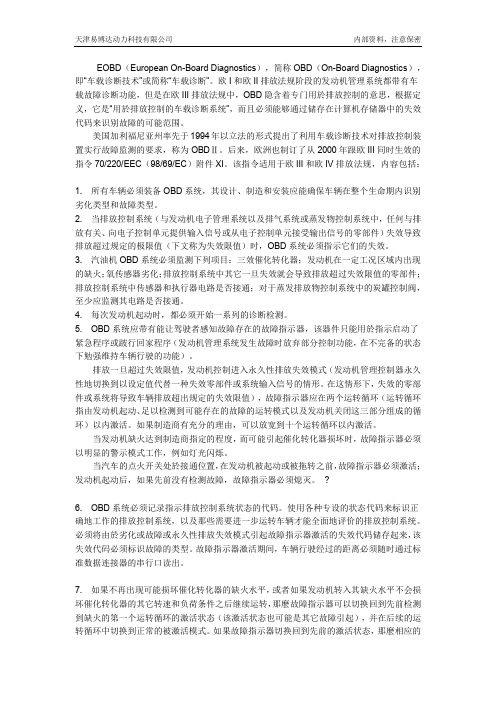

TLP2530中文资料

Resistance (input-output)

Capacitance (input-output)

IF1 = IF2 = 0mA

ICCH

VO1 = VO2 = Open

¾

VCC = 15V

VF

IF = 16mA, Ta = 25°C

元器件交易网

TLP2530,TLP2531

TOSHIBA Photocoupler GaAℓAs Ired & Photo IC

TLP2530, TLP2531

Degital Logic Isolation

Line Receiver

Power Supply Control

7

VCC = 4.5V, Ta = 25°C

(Note 6)

19

IF = 16mA, VO = 0.5V

5

VCC = 4.5V

(Note 6)

15

IF = 16mA, IO = 1.1mA VCC = 4.5V

¾

IF = 16mA, IO = 2.4mA VCC = 4.5V

¾

IF = 0mA, VO = VCC = 5.5V Ta = 25℃

Schematic

IF1 + VF1 1

2 IF2

+ VF2 4

3

ICC VCC

IO1 8 7 VO1

IO2 VO2

6 GND

5

1

2002-09-25

元器件交易网

TLP2530,TLP2531

Maximum Ratings

Characteristic

5TTP中文资料

0.492

0.64

5.25

5.81

0.79

5TT (P) 1

-R

1A

0.270

0.52

8.63

9.6

0.85

5TT (P) 1.25 -R 1.25A

0.206

0.44

13.1

14.6

0.91

5TT (P) 1.5 -R

1.5A

0.140

0.39

18.3

20.5

0.96

5TT (P) 1.6 -R

1.6A

Far East Office Bel Fuse Ltd. 8F/8 Luk Hop Street San Po Kong Kowloon, Hong Kong Tel: 852-2328-5515 Fax: 852-2352-3706

European Office Bel Fuse Europe Ltd. Preston Technology Management Centre Marsh Lane, Preston PR1 8UD Lancashire, U.K Tel: 44-1772-556601 Fax: 44-1772-888366

0.120

0.37

19.7

22.2

0.97

5TT (P) 2

-R

2A

0.080

0.32

29.9

33.7

1.03

5TT (P) 2.5 -R

2.5A

0.060

0.27

45.2

51.3

1.10

5TT (P) 3

-R

3A

0.043

0.23

55.6

63.3

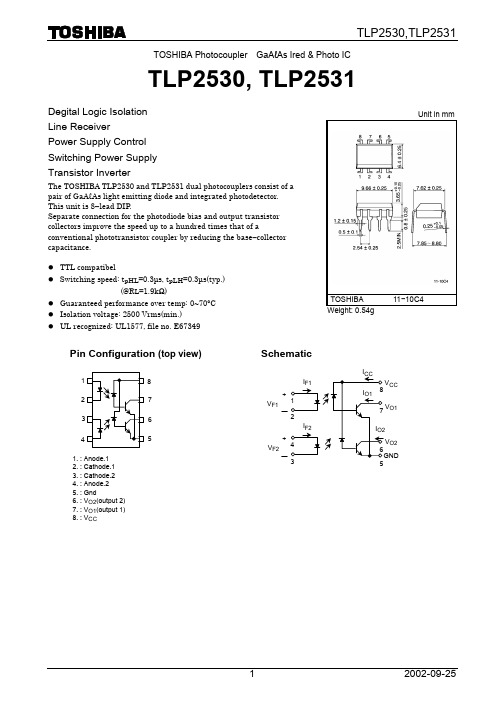

TLP555中文资料

TLP555

注: 8 ピンと 5 ピンの間に、バイパス用のコンデンサ 0.1μF をつける必要があります。

最大定格 (Ta = 25℃)

項目

発 直流順電流

光 過 渡 パ ル ス 順 電 流 (注 1) 側

直流逆電圧

出

力

電

流

ピ ー ク 出 力 電 流 (注 2)

受

出

力

電

圧

光

電

源

電

圧

側 3 ステートイネーブル電圧

2

2001-04-06

推奨動作条件

項目

記号

最小 標準 最大 単位

入力ハイレベル電流、ON 入力ローレベル電圧、OFF

電

源

電

圧

ハイレベルイネーブル電圧

ローレベルイネーブル電圧 フ ァ ン ア ウ ト (TTL 負荷)

動

作

温

度

IF (ON) VF (OFF)

VCC VEH VEL

N Topr

2*

―

0

―

出 力 許 容 損 失 (注 3)

全 許 容 損 失 (注 4)

動

作

温

度

保

存

温

度

は ん だ 付 け 温 度 (10 秒 ) **

絶

縁

耐

圧

(AC1 分間、R.H.≦60%、Ta = 25℃)

(注 5)

記号

IF IFPT VR IO IOP VO VCC VE PO PT Topr Tstg Tsol

BVS

1.0

1.7

V

― mV /℃

10 μA

―

pF

100 μA

74LCX125中文资料

1/12September 2004s 5V TOLERANT INPUTS AND OUTPUTS sHIGH SPEED:t PD = 5.2 ns (MAX.) at V CC = 3VsPOWER DOWN PROTECTION ON INPUTS AND OUTPUTSsSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 24mA (MIN) at V CC = 3Vs PCI BUS LEVELS GUARANTEED AT 24 mA sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 2.0V to 3.6V (1.5V Data Retention)sPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 125sLATCH-UP PERFORMANCE EXCEEDS 500mA (JESD 17)sESD PERFORMANCE:HBM > 2000V (MIL STD 883 method 3015); MM > 200VDESCRIPTIONThe 74LCX125 is a low voltage CMOS QUAD BUS BUFFER fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology. It is ideal for low power and highspeed 3.3V applications; it can be interfaced to 5V signal environment for both inputs and outputs.The device requires the 3-STATE control input G to be set high to place the output in to the high impedance state.It has same speed performance at 3.3V than 5V AC/ACT family, combined with a lower power consumption.All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.74LCX125LOW VOLTAGE CMOS QUAD BUS BUFFER (3-STATE)WITH 5V TOLERANT INPUTS AND OUTPUTSFigure 1: Pin Connection And IEC Logic SymbolsTable 1: Order CodesPACKAGE T & R SOP 74LCX125MTR TSSOP74LCX125TTR74LCX1252/12Figure 2: Input And Output Equivalent CircuitTable 2: Pin DescriptionTable 3: Truth TableX : Don’t CareZ : High ImpedanceTable 4: Absolute Maximum RatingsAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied1) I O absolute maximum rating must be observed 2) V O< GNDPIN N°SYMBOL NAME AND FUNCTION 1, 4, 10, 131G TO 4G Output Enable Input 2, 5, 9, 121A TO 4A Data Inputs 3, 6, 8, 111Y TO 4Y Data Outputs 7GND Ground (0V)14V CCPositive Supply VoltageA G Y X H Z L L L HLHSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7.0V V I DC Input Voltage-0.5 to +7.0V V O DC Output Voltage (OFF State or High Impedance)-0.5 to +7.0V V O DC Output Voltage (High or Low State) (note 1)-0.5 to V CC + 0.5V I IK DC Input Diode Current- 50mA I OK DC Output Diode Current (note 2)- 50mA I O DC Output Current± 50mA I CC DC Supply Current per Supply Pin ± 100mA I GND DC Ground Current per Supply Pin ± 100mA T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°C74LCX1253/12Table 5: Recommended Operating Conditions1) Truth Table guaranteed: 1.5V to 3.6V 2) V IN from 0.8V to 2V at V CC = 3.0VTable 6: DC SpecificationsSymbol ParameterValue Unit V CC Supply Voltage (note 1) 2.0 to 3.6V V I Input Voltage0 to 5.5V V O Output Voltage (OFF State or High Impedance)0 to 5.5V V O Output Voltage (High or Low State)0 to V CC V I OH , I OL High or Low Level Output Current (V CC = 3.0 to 3.6V)± 24mA I OH , I OL High or Low Level Output Current (V CC = 2.7V)± 12mA T op Operating Temperature-55 to 125°C dt/dvInput Rise and Fall Time (note 2)0 to 10ns/VSymbolParameterTest ConditionValueUnitV CC (V)-40 to 85 °C -55 to 125 °C Min.Max.Min.Max.V IH High Level Input Voltage2.7 to3.62.02.0V V IL Low Level Input Voltage0.80.8VV OHHigh Level Output Voltage2.7 to3.6I O =-100 µA V CC -0.2V CC -0.2V2.7I O =-12 mA 2.2 2.23.0I O =-18 mA 2.4 2.4I O =-24 mA 2.22.2V OLLow Level Output Voltage2.7 to3.6I O =100 µA 0.20.2V 2.7I O =12 mA 0.40.43.0I O =16 mA 0.40.4I O =24 mA 0.550.55I I Input Leakage Current2.7 to3.6V I = 0 to 5.5V ± 5± 5µA I off Power Off Leakage Current0V I or V O = 5.5V 1010µA I OZ High Impedance Output Leakage Current2.7 to3.6V I = V IH or V IL V O = 0 to V CC ± 5± 5µA I CC Quiescent Supply Current2.7 to3.6V I = V CC or GND 1010µA V I or V O = 3.6 to 5.5V ± 10± 10∆I CCI CC incr. per Input2.7 to3.6V IH = V CC - 0.6V500500µA74LCX1254/12Table 7: Dynamic Switching Characteristics1) Number of outputs defined as "n". Measured with "n-1" outputs switching from HIGH to LOW or LOW to HIGH. The remaining output is measured in the LOW state.Table 8: AC Electrical Characteristics1) Skew is defined as the absolute value of the difference between the actual propagation delay for any two outputs of the same device switch-ing in the same direction, either HIGH or LOW (t OSLH = | t PLHm - t PLHn |, t OSHL = | t PHLm - t PHLn |)2) Parameter guaranteed by designTable 9: Capacitive Characteristics1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /4 (per gate)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25 °C Min.Typ.Max.V OLP Dynamic Low Level Quiet Output (note 1)3.3C L = 50pFV IL = 0V, V IH = 3.3V0.8V V OLV-0.8SymbolParameterTest ConditionValueUnitV CC (V)C L (pF)R L (Ω)t s = t r (ns)-40 to 85 °C -55 to 125 °C Min.Max.Min.Max.t PLH t PHL Propagation Delay Time2.750500 2.5 6.0 6.9ns3.0 to 3.6 1.0 5.2 1.0 6.0t PZL t PZH Output Enable Time to HIGH and LOW level2.7505002.51.0 6.0 1.0 6.9ns 3.0 to 3.6 1.0 5.0 1.0 6.0t PLZ t PHZ Output Disable Time to HIGH and LOW level2.750500 2.5 1.0 6.0 1.0 6.9ns3.0 to 3.6 1.05.0 1.06.0t OSLH t OSHLOutput To Output Skew Time (note1, 2)3.0 to 3.6505002.51.01.0ns SymbolParameterTest ConditionValue UnitV CC (V)T A = 25 °C Min.Typ.Max.C IN Input Capacitance 3.3V IN = 0 to V CC 5pF C OUT Output Capacitance3.3V IN = 0 to V CC 10pF C PDPower Dissipation Capacitance (note 1)3.3f IN = 10MHz V IN = 0 or V CC37pF74LCX1255/12Figure 3: Test CircuitC L = 50 pF or equivalent (includes jig and probe capacitance)R L = R1 = 500Ω or equivalentR T = Z OUT of pulse generator (typically 50Ω)Figure 4: Waveform - Propagation Delay (f=1MHz; 50% duty cycle)TESTSWITCH t PLH , t PHL Open t PZL , t PLZ 6V t PZH , t PHZGND74LCX125Figure 5: Waveform - Output Enable And Disable Time (f=1MHz; 50% duty cycle)6/1274LCX1257/12DIM.mm.inch MIN.TYPMAX.MIN.TYP.MAX.A 1.35 1.750.0530.069A10.10.250.0040.010A2 1.10 1.650.0430.065B 0.330.510.0130.020C 0.190.250.0070.010D 8.558.750.3370.344E 3.84.00.1500.157e 1.270.050H 5.8 6.20.2280.244h 0.250.500.0100.020L 0.4 1.270.0160.050k 0°8°0°8°ddd0.1000.004SO-14 MECHANICAL DATA0016019D74LCX1258/12DIM.mm.inchMIN.TYPMAX.MIN.TYP.MAX.A 1.20.047A10.050.150.0020.0040.006A20.81 1.050.0310.0390.041b 0.190.300.0070.012c 0.090.200.0040.0089D 4.95 5.10.1930.1970.201E 6.2 6.4 6.60.2440.2520.260E1 4.34.4 4.480.1690.1730.176e 0.65 BSC0.0256 BSCK 0˚8˚0˚8˚L0.450.600.750.0180.0240.030TSSOP14 MECHANICAL DATAcEbA2A E1D1PIN 1 IDENTIFICATIONA1LKe0080337D74LCX125 Tape & Reel SO-14 MECHANICAL DATAmm.inchDIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992C12.813.20.5040.519D20.20.795N60 2.362T22.40.882Ao 6.4 6.60.2520.260Bo99.20.3540.362Ko 2.1 2.30.0820.090Po 3.9 4.10.1530.161P7.98.10.3110.3199/1274LCX125Tape & Reel TSSOP14 MECHANICAL DATAmm.inch DIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992 C12.813.20.5040.519 D20.20.795N60 2.362T22.40.882 Ao 6.7 6.90.2640.272 Bo 5.3 5.50.2090.217 Ko 1.6 1.80.0630.071 Po 3.9 4.10.1530.161 P7.98.10.3110.31910/1274LCX125 Table 10: Revision HistoryDate Revision Description of Changes 15-Sep-20045Ordering Codes Revision - pag. 1.11/1274LCX125Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronicsAll other names are the property of their respective owners© 2004 STMicroelectronics - All Rights ReservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America12/12。

2N2222A中文资料_数据手册_参数

Objective specification Preliminary specification Product specification

This data sheet contains target or goal specifications for product development. This data sheet contains preliminary data; supplementary data may be published later. This data sheet contains final product specifications.

TO-18

1997 May 29

6

EUROPEAN PROJECTION

ISSUE DATE 97-04-18

Philips Semiconductors

NPN switching transistors

Product specification

2N2222; 2N2222A

DEFINITIONS

Data sheet status

SYMBOL

PARAMETER

Rth j-a Rth j-c

thermal resistance from junction to ambient thermal resistance from junction to case

CONDITIONS in free air

MIN.

MAX.

UNIT

−

60

Product specification

2N2222; 2N2222A

LIMITING VALUES In accordance with the Absolute Maximum Rating System (IEC 134).

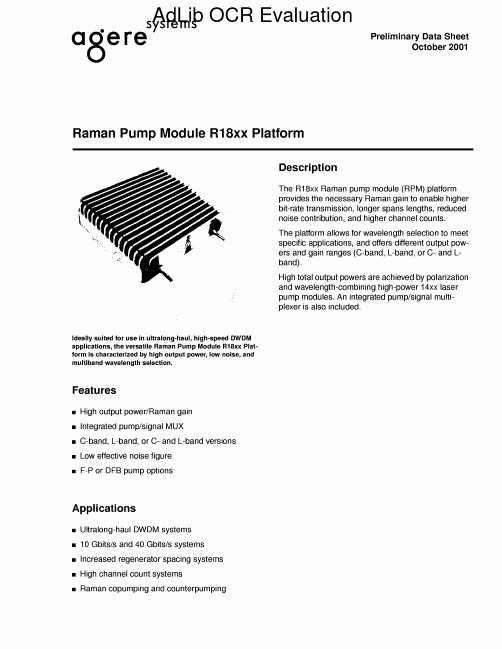

R18xx中文资料

Operating Case Temperature Range

I

Electrical/Optical Characteristics

Table 1 . Electrical and Optical Characteristics, C- and L-Band Versions Parameter Wavelength Range : C-band Version L-band Version Total Pump Output Power Degree of Polarization Power Dissipation Effective Noise Figure : C-band Version L-band Version Gain Gain Flatness Po Piss NF Symbol Min 1528 1570 550 10 Typ 5 -2 -3 Max 1562 1612 35 1 Unit nm nm mW W dB dB dB dB

PUMP3 : X2 PBC PUMP4 : X2 ELECTRICAL PORT SIGNAL I OPTICAL + PORT OUT

1-1320F

1

PIN

Agere Systems Inc.

元器件交易网

Raman Pump Module R18xx Platform

IEC is a registered trademark of The International Electrotechnical Commission .

For additional information, contact your Agere Systems Account Manager or the following: INTERNET: http ://www.agere .com E-MAIL: docmaster@ N . AMERICA: Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286 1-800-372-2447, FAX 610-712-4106 (In CANADA : 1-800-553-2448, FAX 610-712-4106) ASIA : Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, Kowloon Tel. (852) 3129-2000, FAX (852) 3129-2020 CHINA: (86) 21-5047-1212 (Shanghai), (86) 10-6522-5566 (Beijing), (86) 755-695-7224 (Shenzhen) JAPAN : (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 778-8833, TAIWAN : (886) 2-2725-5858 (Taipei) EUROPE : Tel. (44) 7000 624624, FAX (44) 1344 488 045

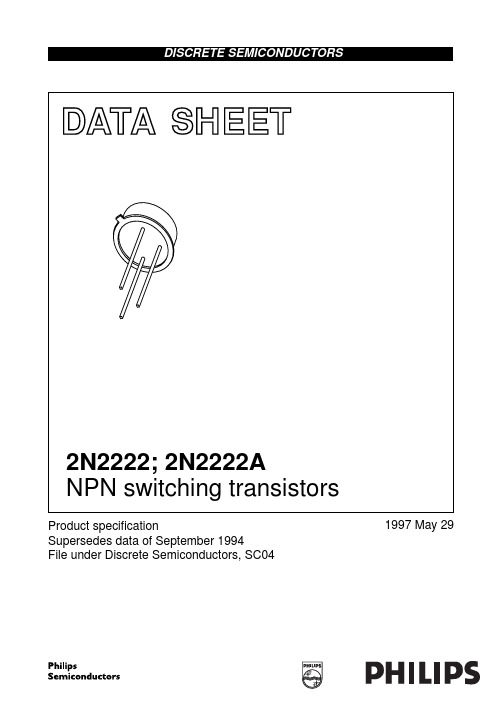

ODB是什么

汽车名词解释:什么是OBD?OBD是英文On-Board Diagnostics的缩写,中文翻译为“车载自动诊断系统”。

这个系统将从发动机的运行状况随时监控汽车是否尾气超标,一旦超标,会马上发出警示。

当系统出现故障时,故障(MIL)灯或检查发动机(Check Engine)警告灯亮,同时动力总成控制模块(PCM)将故障信息存入存储器,通过一定的程序可以将故障码从PCM中读出。

根据故障码的提示,维修人员能迅速准确地确定故障的性质和部位。

从20世纪80年代起,美、日、欧等各大汽车制造企业开始在其生产的电喷汽车上配备 OBD,初期的OBD没有自检功能。

比OBD更先进的OBD-Ⅱ在20世纪90年代中期产生,美国汽车工程师协会(SAE)制定了一套标准规范,要求各汽车制造企业按照OBD-Ⅱ的标准提供统一的诊断模式,在20世纪90年末期,进入北美市场的汽车都按照新标准设置OBD。

OBD-Ⅱ与以前的所有车载自诊断系统不同之处在于有严格的排放针对性,其实质性能就是监测汽车排放。

当汽车排放的一氧化碳(CO)、碳氢化合物(HC)、氮氧化合物(NOx)或燃油蒸发污染量超过设定的标准,故障灯就会点亮报警。

虽然OBD-Ⅱ对监测汽车排放十分有效,但驾驶员接受不接受警告全凭“自觉”。

为此,比OBD-Ⅱ更先进的OBD-Ⅲ产生了。

OBD-Ⅲ主要目的是使汽车的检测、维护和管理合为一体,以满足环境保护的要求。

OBD-Ⅲ系统会分别进入发动机、变速箱、ABS等系统ECU(电脑)中去读取故障码和其它相关数据,并利用小型车载通讯系统,例如GPS导航系统或无线通信方式将车辆的身份代码、故障码及所在位置等信息自动通告管理部门,管理部门根据该车辆排放问题的等级对其发出指令,包括去哪里维修的建议,解决排放问题的时限等,还可对超出时限的违规者的车辆发出禁行指令。

因此,OBD-Ⅲ系统不仅能对车辆排放问题向驾驶者发出警告,而且还能对违规者进行惩罚。

据了解,国内合资汽车厂近年来引进的一些车型在欧洲也有生产销售,它们本身就配备有OBD并达到了欧III甚至欧IV标准,国产后往往会减去或关闭OBD,一方面是节约成本,也为了避免在油品质量不达标的情况下因OBD报警而引发麻烦。

TPA3120D2PWPR资料

FEATURES DESCRIPTIONAPPLICATIONSTPA3120D2SIMPLIFIED APPLICATION CIRCUITTPA3120D2SLOS507C–MARCH2007–REVISED MAY2007 25-W STEREO CLASS-D AUDIO POWER AMPLIFIER•25-W/ch into a4-ΩLoad from a27-V Supply The TPA3120D2is a25-W(per channel)efficient,Class-D audio power amplifier for driving stereo •20-W/ch into a4-ΩLoad from a24-V Supplyspeakers in a single-ended configuration or a mono •Operates from10V to30Vbridge-tied speaker.The TPA3120D2can drive •Efficient Class-D Operation Eliminates Need stereo speakers as low as4Ω.The efficiency of the for Heat Sinks TPA3120D2eliminates the need for an external heatsink when playing music.•Four Selectable,Fixed Gain Settings•Internal Oscillator(No External Components The gain of the amplifier is controlled by two gain Required)select pins.The gain selections are20,26,32,36dB.•Single Ended Analog InputsThe patented start-up and shut-down sequences •Thermal and Short-Circuit Protection withminimize"pop"noise in the speakers without Auto Recoveryadditional circuitry.•Space-Saving Surface Mount24-pin TSSOPPackage•TelevisionsPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©2007,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.PVCCLSDPVCCLMUTELINRINBYPASSAGNDAGNDPVCCRVCLAMPPVCCRPGNDLPGNDLLOUTBSLAVCCAVCCGAIN0GAIN1BSRROUTPGNDRPGNDRTPA3120D2SLOS507C–MARCH2007–REVISED MAY2007These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.PWP(TSSOP)PACKAGE(TOP VIEW)TERMINAL FUNCTIONSTERMINALI/O/P DESCRIPTION24-PINNAME(PWP)Shutdown signal for IC(low=disabled,high=operational).TTL logic levels with compliance to SD2IAVCC.RIN6I Audio input for right channel.LIN5I Audio input for left channel.GAIN018I Gain select least significant bit.TTL logic levels with compliance to AVCC.GAIN117I Gain select most significant bit.TTL logic levels with compliance to AVCC.Mute signal for quick disable/enable of outputs(high=outputs switch at50%duty cycle,low= MUTE4Ioutputs enabled).TTL logic levels with compliance to AVCC.BSL21I/O Bootstrap I/O for left channel.PVCCL1,3P Power supply for left channel H-bridge,not internally connected to PVCCR or AVCC.LOUT22O Class-D1/2-H-bridge positive output for left channel.PGNDL23,24P Power ground for left channel H-bridge.VCLAMP11P Internally generated voltage supply for bootstrap capacitors.BSR16I/O Bootstrap I/O for right channel.ROUT15O Class-D1/2-H-bridge negative output for right channel.PGNDR13,14P Power ground for right channel H-bridge.PVCCR10,12P Power supply for right channel H-bridge,not connected to PVCCL or AVCC.AGND9P Analog ground for digital/analog cells in core.AGND8P Analog Ground for analog cells in core.Reference for pre-amplifier inputs.Nominally equal to AVCC/8.Also controls start-up time via BYPASS7Oexternal capacitor sizing.AVCC19,20P High-voltage analog power supply.Not internally connected to PVCCR or PVCCLConnect to ground.Thermal Pad should be soldered down on all applications to properly Thermal Pad Die Pad Psecure device to printed wiring board.2Submit Documentation FeedbackABSOLUTE MAXIMUM RATINGSDISSIPATION RATINGSRECOMMENDED OPERATING CONDITIONSTPA3120D2 SLOS507C–MARCH2007–REVISED MAY2007over operating free-air temperature range(unless otherwise noted)(1)VALUE UNITV CC Supply voltage AVCC,PVCC–0.3to36VV I Logic input voltage SD,MUTE,GAIN0,GAIN1–0.3to V CC+0.3VV IN Analog input voltage RIN,LIN-0.3to7V Continuous total power dissipation See Dissipation Rating TableT A Operating free-air temperature range–40to85°CT J Operating junction temperature range–40to150°CT stg Storage temperature range–65to150°CR L Load resistance(Minimum value) 3.2ΩHuman body model(all pins)±2ESD Electrostatic Discharge kVCharged-device model(all±500pins)(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operations of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.PACKAGE(1)(2)T A≤25°C DERATING FACTOR T A=70°C T A=85°C24-pin TSSOP 4.16W33.3mW/°C 2.67W 2.16W(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIwebsite at .(2)The PowerPAD must be soldered to a thermal land on the printed circuit board.See the PowerPAD Thermally Enhanced Packageapplication note(SLMA002).MIN MAX UNITV CC Supply voltage PVCC,AVCC1030VV IH High-level input voltage SD,MUTE,GAIN0,GAIN12VV IL Low-level input voltage SD,MUTE,GAIN0,GAIN10.8VSD,V I=V CC,V CC=30V125I IH High-level input current MUTE,V I=V CC,V CC=30V125µAGAIN0,GAIN1,V I=V CC,V CC=24V125SD,V I=0,V CC=30V1I IL Low-level input current MUTE,V I=0V,V CC=30V1µAGAIN0,GAIN1,V I=0V,V CC=24V1T A Operating free-air temperature–4085°C3Submit Documentation FeedbackDC CHARACTERISTICSAC CHARACTERISTICSTPA3120D2SLOS507C–MARCH 2007–REVISED MAY 2007T A =25°C,V CC =24V,R L =4Ω(unless otherwise noted)PARAMETERTEST CONDITIONSMINTYP MAX UNIT Class-D output offset voltage |V OS |(measured differentially in BTL V I =0V,A V =36dB 7.550mV mode as shown in Fig 30)V (BYPASS)Bypass output voltage No loadAVCC/8V I CC(q)Quiescent supply current SD =2V,MUTE =0V,No load 2337mA I CC(q)Quiescent supply current in MUTE =0.8V,No load 23mA mute modeI CC(q)Quiescent supply current in SD =0.8V ,No load0.391mA shutdown mode r DS(on)Drain-source on-state 200m ΩresistanceGAIN0=0.8V 182022GAIN1=0.8VGAIN0=2V 242628GGaindBGAIN0=0.8V 303234GAIN =2VGAIN0=2V343638Mute AttenuationV I =1Vrms-82dB T A =25°C,V CC =24V,R L =4Ω(unless otherwise noted)PARAMETERTEST CONDITIONSMINTYP MAXUNIT V CC =24,V ripple =200mV PP 100Hz –48ksvrSupply ripple rejection dBGain =20dB1kHz–52V CC =24V,R L =4Ω,f =1kHz 16Output Power at 1%THD+NV CC =24V,R L =8Ω,f =1kHz 8P OWV CC =24V,R L =4Ω,f =1kHz 20Output Power at 10%THD+NV CC =24V,R L =8Ω,f =1kHz 10R L =4Ω,f =1kHz,P O =10W 0.08%Total harmonic distortion +THD+N noiseR L =8Ω,f =1kHz,P O =5W 0.08%85µV 20Hz to 22kHz,A-weighted filter,V nOutput integrated noise floor Gain =20dB-80dBV CrosstalkP O =1W,f =1kHz;Gain =20dB -60dB Max Output at THD+N <1%,f =1kHz,SNRSignal-to-noise ratio 99dB Gain =20dBThermal trip point 150°C Thermal hysteresis30°C f OSCOscillator frequency230250270kHz 4Submit Documentation FeedbackFUNCTIONAL BLOCK DIAGRAMBSLPVCCLBSR PVCCRTPA3120D2SLOS507C–MARCH 2007–REVISED MAY 20075Submit Documentation FeedbackTYPICAL CHARACTERISTICSf −Frequency −Hz2010010k T H D +N T o t a l H a r m o n i c D i s t o r t i o n + N o i s e %--0.11020k 10.01f −Frequency −Hz201001k10k T H D +N T o t a l H a r m o n i c D i s t o r t i o n + N o i s e %--0.11020k10.01f −Frequency −Hz201001k10k T H D +N T o t a l H a r m o n i c D i s t o r t i o n + N o i s e %--0.11020k10.01P −Output Power −WO 10 m100 m 110T H D +N T o t a l H a r m o n i c D i s t o r t i o n + N o i s e %--140100.010.1TPA3120D2SLOS507C–MARCH 2007–REVISED MAY 2007All tests are made at frequency =1kHz unless otherwise noted.TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsFREQUENCYFREQUENCYFigure 1.Figure 2.TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsFREQUENCYOUTPUT POWERFigure 3.Figure 4.6Submit Documentation FeedbackT H D +N - T o t a l H a r m o n i c D i s t o r t i o n + N o i s e - %P −Output Power −WO1010 m100 m 11040-100201001 k20kf −Frequency −HzC r o s s t a l k d B-10k -90-80-70-60-50-40-30-20-100-300200-200-100100f −Frequency −HzG a i n d B-P h a s e -o-100f −Frequency −Hz-90-80-70-60-50-40-30-20-100C r o s s t a l k d B-TPA3120D2SLOS507C–MARCH 2007–REVISED MAY 2007TYPICAL CHARACTERISTICS (continued)All tests are made at frequency =1kHz unless otherwise noted.TOTAL HARMONIC DISTORTION +NOISECROSSTALKvsvsOUTPUT POWERFREQUENCYFigure 5.Figure 6.CROSSTALKGAIN/PHASEvsvsFREQUENCYFREQUENCYFigure 7.Figure 8.7Submit Documentation Feedbackf −Frequency −HzG a i n d B-P h a s e -oV −Supply Voltage −VSS P O u t p u t P o w e r WO --2228432126821418101620243026V - Supply Voltage - V SS P - O u t p u t P o w e r - WO 16263012107141820222428171615141312111096185432P −Output Power −WO 616E f f i c i e n c y %-80201010030040602050709024810121418TPA3120D2SLOS507C–MARCH 2007–REVISED MAY 2007TYPICAL CHARACTERISTICS (continued)All tests are made at frequency =1kHz unless otherwise noted.GAIN/PHASEOUTPUT POWERvsvsFREQUENCYSUPPLY VOLTAGEFigure 9.A.Dashed line represents thermally limited region.Figure 10.OUTPUT POWEREFFICIENCYvsvsSUPPLY VOLTAGEOUTPUT POWERFigure 11.Figure 12.8Submit Documentation FeedbackP −Output Power −WO E f f i c i e n c y %-8010100300406020507090P −Output Power −WO I −S u p p l y C u r r e n t −AC C 1232404081620242836-120201001 k20kf −Frequency −HzP o w e r S u p p l y R e j e c t i o n R a t i o d B-10k -110-100-90-80-70-500-40-30-20-10-600.702.557.51012.51517.52022.525P - Output Power - WO I - S u p p l y C u r r e n t -AC C TPA3120D2SLOS507C–MARCH 2007–REVISED MAY 2007TYPICAL CHARACTERISTICS (continued)All tests are made at frequency =1kHz unless otherwise noted.EFFICIENCYSUPPLY CURRENTvsvsOUTPUT POWEROUTPUT POWERFigure 13.Figure 14.SUPPLY CURRENTPOWER SUPPLY REJECTION RATIOvsvsOUTPUT POWERFREQUENCYFigure 15.Figure 16.9Submit Documentation Feedbackf −Frequency −Hz201001k10k T H D +N T o t a l H a r m o n i c D i s t o r t i o n + N o i s e %--0.11020k10.010.001P −Output Power −WO 10 m100 m 110T H D +N T o t a l H a r m o n i c D i s t o r t i o n + N o i s e %--140100.010.1-200400-1000100200300-30-20-10f - Frequency - HzP h a s e - °G a i n - d BV −Supply Voltage −VSS P O u t p u t P o w e r WO --40550651520301025354560505TPA3120D2SLOS507C–MARCH 2007–REVISED MAY 2007TYPICAL CHARACTERISTICS (continued)All tests are made at frequency =1kHz unless otherwise noted.TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsFREQUENCYOUTPUT POWERFigure 17.Figure 18.GAIN/PHASEOUTPUT POWERvsvsFREQUENCYSUPPLY VOLTAGEFigure 19.A.Dashed line represents thermally limited region.Figure 20.10Submit Documentation FeedbackP −Output Power −WO 32E f f i c i e n c y %-8040101003040602050709048162024283612-140201001 k20kf −Frequency −HzP o w e r S u p p l y R e j e c t i o n R a t i o d B-10k -120-100-80-60-40-200SLOS507C–MARCH 2007–REVISED MAY 2007TYPICAL CHARACTERISTICS (continued)All tests are made at frequency =1kHz unless otherwise noted.EFFICIENCYPOWER SUPPLY REJECTION RATIOvsvsOUTPUT POWERFREQUENCYFigure 21.Figure 22.APPLICATION INFORMATIONCLASS-D OPERATIONTraditional Class-D ModulationScheme+V CC 0 VOutput CurrentOutput Current+V CC 0 V +V CC 0 V+V CC0 V -VCCDifferential Voltage Across SpeakerSupply PumpingSLOS507C–MARCH 2007–REVISED MAY 2007This section focuses on the class-D operation of the TPA3120D2.The TPA3120D2operates in AD mode.There are two main configurations that may be used.For stereo operation,the TPA3120D2should be configured in a single-ended (SE)half bridge amplifier.For mono applications,TPA3120D2may be used as a bridge tied load (BTL)amplifier.The traditional class-D modulation scheme,which is used in the TPA3120D2BTL configuration,has a differential output where each output is 180degrees out of phase and changes from ground to the supply voltage,V CC .Therefore,the differential prefiltered output varies between positive and negative V CC ,where filtered 50%duty cycle yields 0V across the load.The class-D modulation scheme with voltage and current waveforms are shown in Figure 23and Figure 24.Figure 23.Class-D Modulation for TPA3120D2SE ConfigurationFigure 24.Class-D Modulation for TPA3120D2BTL ConfigurationOne issue encountered in single ended (SE)class D amplifier designs is supply pumping.Power supply pumping is a rise in the local supply voltage due to energy being driven back to the supply by operation of the Class D amplifier.This phenomenon is most evident at low audio frequencies and when both channels are operating at the same frequency and phase.At low levels,power supply pumping results in distortion in the audio output due to fluctuations in supply voltage.At higher levels,pumping can cause the overvoltage protection to operate,which temporarily shuts down the audio output.Gain setting via GAIN0and GAIN1inputs INPUT RESISTANCEInputSignalf =12Z Cpi i(1)SLOS507C–MARCH2007–REVISED MAY2007 APPLICATION INFORMATION(continued)There are several things which can be done to relieve the power supply pumping.The lowest impact is to operate the two inputs out of phase180°and reverse the speaker connections.Since most audio is highly correlated,this causes the supply pumping to be out of phase and not as severe.If this is not enough,the amount of bulk capacitance on the supply will need to be increased.Also,improvement is realized by hooking other supplies to this node which sinks some of the excess current.Power supply pumping should be tested by operating the amplifier at low frequencies and high output levels.The gain of the TPA3120D2is set by two input terminals,GAIN0and GAIN1.The gains listed in Table1are realized by changing the taps on the input resistors and feedback resistors inside the amplifier.This causes the input impedance(Z I)to be dependent on the gain setting.The actual gain settings are controlled by ratios of resistors,so the gain variation from part-to-part is small.However,the input impedance from part-to-part at the same gain may shift by±20%due to shifts in the actual resistance of the input resistors.For design purposes,the input network(discussed in the next section)should be designed assuming an input impedance of8kΩ,which is the absolute minimum input impedance of the TPA3120D2.At the higher gain settings,the input impedance could increase as high as72kΩTable1.Gain SettingINPUT IMPEDANCEAMPLIFIER GAIN(dB)(kΩ)GAIN1GAIN0TYPICAL TYPICAL002010012615103230113660Changing the gain setting can vary the input resistance of the amplifier from its smallest value,10kΩ±20%,to the largest value,60kΩ±20%.As a result,if a single capacitor is used in the input high-pass filter,the–3dB or cutoff frequency may change when changing gain steps.The–3-dB frequency can be calculated using e the Z I values given in Table1.INPUT CAPACITOR,C If =c 12Z C p i i-3 dBf c(2)C =i 12Z f p i c(3)Single Ended Output Capacitor,C OSLOS507C–MARCH 2007–REVISED MAY 2007In the typical application,an input capacitor (C I )is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation.In this case,C I and the input impedance of the amplifier (Z I )form a high-pass filter with the corner frequency determined in Equation 2.The value of C I is important,as it directly affects the bass (low-frequency)performance of the circuit.Consider the example where Z I is 20k Ωand the specification calls for a flat bass response down to 20Hz.Equation 2is reconfigured as Equation 3.In this example,C I is 0.4µF;so,one would likely choose a value of 0.47µF as this value is commonly used.If the gain is known and is constant,use Z I from Table 1to calculate C I .A further consideration for this capacitor is the leakage path from the input source through the input network (C I )and the feedback network to the load.This leakage current creates a dc offset voltage at the input to the amplifier that reduces useful headroom,especially in high gain applications.For this reason,a low-leakage tantalum or ceramic capacitor is the best choice.When polarized capacitors are used,the positive side of the capacitor should face the amplifier input in most applications as the dc level there is held at 2V,which is likely higher than the source dc level.Note that it is important to confirm the capacitor polarity in the application.Additionally,lead-free solder can create dc offset voltages and it is important to ensure that boards are cleaned properly.In single ended (SE)applications,the DC blocking capacitor forms a high pass filter with speaker impedance.The frequency response rolls of with decreasing frequency at a rate of 20dB/decade.The cutoff frequency is determined byfc =1/2πC O Z LTable 2shows some common component values and the associated cutoff frequencies:Table mon Filter ResponsesC SE -DC Blocking Capacitor (µF)Speaker Impedance (Ω)f c =60Hz (-3dB)f c =40Hz(-3dB)f c =20Hz(-3dB)46801000220083304701000Output Filter and FrequencyResponsePower Supply Decoupling,C SBSN and BSP CapacitorsSLOS507C–MARCH 2007–REVISED MAY 2007For the best frequency response,a flat passband output filter (second order Butterworth)may be used.The output filter components consist of the series inductor and capacitor to ground at the LOUT and ROUT pins.There are several possible configurations depending on the speaker impedance,and whether the output configuration is single ended (SE)or bridge tied load (BTL).Table 3list the recommended values for the filter components.It is important to use a high quality capacitor in this application.A rating of at least X7R is required.Table 3.Recommended Filter Output ComponentsOutput Configuration Speaker Impedance (Ω)Filter Inductor (µH)Filter Capacitor (nF)422680Single Ended (SE)8473904101500Bridge Tied Load (BTL)822680Figure 25.BTL Filter Configuration Figure 26.SE Filter ConfigurationThe TPA3120D2is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure that the output total harmonic distortion (THD)is as low as possible.Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker.The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads.For higher frequency transients,spikes,or digital hash on the line,a good low equivalent-series-resistance (ESR)ceramic capacitor,typically 0.1µF to 1µF placed as close as possible to the device V CC lead works best.For filtering lower frequency noise signals,a larger aluminum electrolytic capacitor of 470µF or greater placed near the audio power amplifier is recommended.The 470-µF capacitor also serves as local storage capacitor for supplying current during large signal transients on the amplifier outputs.The PVCC terminals provide the power to the output transistors,so a 470-µF or larger capacitor should be placed on each PVCC terminal.A 10-µF capacitor on the AVCC terminal is adequate.These capacitors need to be properly derated for voltage and ripple current rating to insure reliability.The half H-bridge output stages use only NMOS transistors.Therefore,they require bootstrap capacitors for the high side of each output to turn on correctly.A 220-nF ceramic capacitor,rated for at least 25V,must be connected from each output to its corresponding bootstrap input.Specifically,one 220-nF capacitor must be connected from LOUT to BSL,and one 220-nF capacitor must be connected from ROUT to BSR.The bootstrap capacitors connected between the BSx pins and corresponding output function as a floating power supply for the high-side N-channel power MOSFET gate drive circuitry.During each high-side switching cycle,the bootstrap capacitors hold the gate-to-source voltage high enough to keep the high-side MOSFETs turned on.VCLAMP CapacitorVBYP Capacitor SelectionSHUTDOWN OPERATIONMUTE OperationUSING LOW-ESR CAPACITORSSHORT-CIRCUIT PROTECTIONSLOS507C–MARCH 2007–REVISED MAY 2007To ensure that the maximum gate-to-source voltage for the NMOS output transistors is not exceeded,one internal regulator clamps the gate voltage.One 1-µF capacitor must be connected from VCLAMP (pin 11)to ground and must be rated for at least 16V.The voltages at the VCLAMP terminal may vary with V CC and may not be used for powering any other circuitry.The scaled supply reference (VBYP)nominally provides an AVCC/8internal bias for the preamplifier stages.The external capacitor for this reference (C BYP )is a critical component and serves several important functions.During start-up or recovery from shutdown mode,C BYP determines the rate at which the amplifier starts.The start up time is proportional to 0.5sec per microfarad.Thus,the recommended 1µF cap results in a start-up time of approximately 500msec.The second function is to reduce noise produced by the power supply caused by coupling with the output drive signal.This noise could result in degraded power supply rejection and THD +N.The circuit is designed for a C BYP value of 1µF for best pop performance.The inputs caps should be the same value.A ceramic or tantalum low-ESR capacitor is recommended.The TPA3120D2employs a shutdown mode of operation designed to reduce supply current (I CC )to the absolute minimum level during periods of nonuse for power conservation.The SHUTDOWN input terminal should be held high (see specification table for trip point)during normal operation when the amplifier is in use.Pulling SHUTDOWN low causes the outputs to mute and the amplifier to enter a low-current state.Never leave SHUTDOWN unconnected,because amplifier operation would be unpredictable.For the best power-up pop performance,place the amplifier in the shutdown or mute mode prior to applying the power supply voltage.The MUTE pin is an input for controlling the output state of the TPA3120D2.A logic high on this terminal causes the outputs to run at a constant 50%duty cycle.A logic low on this pin enables the outputs.This terminal may be used as a quick disable/enable of outputs when changing channels on a television or transitioning between different audio sources.The MUTE terminal should never be left floating.For power conservation,the SHUTDOWN terminal should be used to reduce the quiescent current to the absolute minimum level.Low-ESR capacitors are recommended throughout this application section.A real (as opposed to ideal)capacitor can be modeled simply as a resistor in series with an ideal capacitor.The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit.The lower the equivalent value of this resistance,the more the real capacitor behaves like an ideal capacitor.The TPA3120D2has short-circuit protection circuitry on the outputs that prevents damage to the device during output-to-output shorts and output-to-GND shorts after the filter and output capacitor (at the speaker terminal.)Directly at the device terminals,the protection circuitry prevents damage to device during output-to-output,output-to-ground,and output-to-supply.When a short circuit is detected on the outputs,the part immediately disables the output drive.This is an unlatched fault.Normal operation is restored when the fault is removed.THERMAL PROTECTIONPRINTED-CIRCUIT BOARD(PCB)LAYOUT SLOS507C–MARCH2007–REVISED MAY2007Thermal protection on the TPA3120D2prevents damage to the device when the internal die temperatureexceeds150°C.There is a±15°C tolerance on this trip point from device to device.Once the die temperatureexceeds the thermal set point,the device enters into the shutdown state and the outputs are disabled.This isnot a latched fault.The thermal fault is cleared once the temperature of the die is reduced by30°C.The devicebegins normal operation at this point with no external system interaction.Because the TPA3120D2is a class-D amplifier that switches at a high frequency,the layout of the printed-circuitboard(PCB)should be optimized according to the following guidelines for the best possible performance.•Decoupling capacitors—The high-frequency0.1µF decoupling capacitors should be placed as close to the PVCC(pins1,3,10,and12)and AVCC(pins19and20)terminals as possible.The VBYP(pin7)capacitorand VCLAMP(pin11)capacitor should also be placed as close to the device as rge(220µF orgreater)bulk power supply decoupling capacitors should be placed near the TPA3120D2on the PVCCL andPVCCR terminals.•Grounding—The AVCC(pins19and20)decoupling capacitor and VBYP(pin7)capacitor should each be grounded to analog ground(AGND,pins8and9).The PVCCx decoupling capacitors and VCLAMP capacitors should each be grounded to power ground(PGND,pins13,14,23,and24).Analog ground and power ground should be connected at the thermal pad,which should be used as a central ground connection or star ground for the TPA3120D2.•Output filter—The reconstruction filter(L1,L2,C9,and C16)should be placed as close to the output terminals as possible for the best EMI performance.The capacitors should be grounded to power ground.•Thermal Pad—The thermal pad must be soldered to the PCB for proper thermal performance and optimal reliability.The dimensions of the thermal pad and thermal land are described in the mechanical section at the back of the data sheet.See TI Technical Briefs SLMA002and SLOA120for more information about using the thermal pad.For recommended PCB footprints,see figures at the end of this data sheet.For an example layout,see the TPA3120D2Evaluation Module(TPA3120D2EVM)User Manual,(SLOU189).Both the EVM user manual and the thermal pad application note are available on the TI Web site at.。

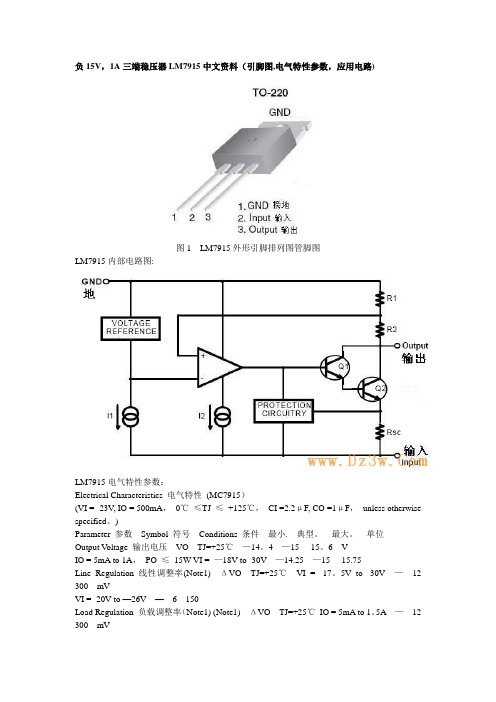

LM7915中文资料

负15V,1A三端稳压器LM7915中文资料(引脚图,电气特性参数,应用电路)图1 LM7915外形引脚排列图管脚图LM7915内部电路图:LM7915电气特性参数:Electrical Characteristics 电气特性(MC7915)(VI = -23V, IO = 500mA,0℃≤TJ ≤+125℃,CI =2.2μF, CO =1μF,unless otherwise specified。

)Parameter 参数Symbol 符号Conditions 条件最小. 典型。

最大。

单位Output Voltage 输出电压VO TJ=+25℃—14。

4 —15 -15。

6 VIO = 5mA to 1A,PO ≤15W VI = —18V to -30V —14.25 —15 -15.75Line Regulation 线性调整率(Note1) ΔVO TJ=+25℃VI = -17。

5V to -30V —12 300 mVVI = -20V to —26V — 6 150Load Regulation 负载调整率(Note1) (Note1) ΔVO TJ=+25℃IO = 5mA to 1。

5A —12 300 mVTJ =+25℃IO = 250mA to 750mA — 4 150Quiescent Current 静态电流IQ TJ =+25℃— 3 6 mAQuiescent Current Change 静态电流变化ΔIQ IO = 5mA to 1A —0。

05 0.5 mAVI = -18。

5V to -30V —0.1 1Temperature Coefficient of VD 温度系数ΔV o/ΔT IO = 5mA - -0.9 —mV/℃Output Noise V oltage 输出噪声电压VN f = 10Hz to 100KHz TA =+25℃- 250 —μVRipple Rejection 纹波抑制RR f = 120Hz ΔVI = 10V 54 60 - dBDropout V oltage 电压差VD TJ=+25℃IO = 1A — 2 —VShort Circuit Current 短路电流ISC TJ =+25℃, VI = -35V - 300 - mAPeak Current 峰值电流IPK TJ =+25℃— 2.2 - A三端稳压集成电路极限参数:Parameter 参数Symbol 符号Value 数值单位Input V oltage输入电压(for VO =5V to 18V)VI 35 V(for VO =24V)VI 40 VThermal Resistance Junction-Cases 热阻(结到壳)(TO-220)RθJC 5 ℃/WThermal Resistance Junction—Air热阻(结到空气)(TO—220)RθJA 65 ℃/WOperating Temperature Range工作温度范围TOPR 0 ~ +125 ℃Storage Temperature Range储存温度范围TSTG —65 ~ +150 ℃LM7915应用电路:图8 LM7915典型应用电路图9 与78XX系列三端稳压构成的正负对称输出电压应用电路图TO-220封装尺寸:。

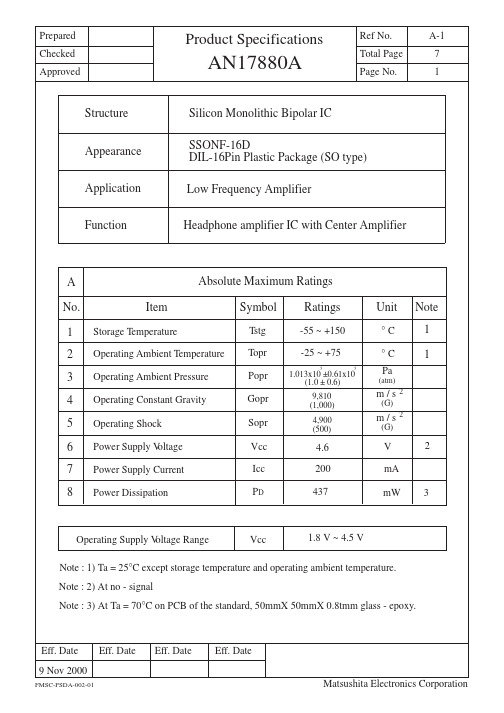

AN17880A资料

Unit

°C °C Pa

(atm)

Note 1 1

2 2

Operating Ambient Temperature Operating Ambient Pressure Operating Constant Gravity Operating Shock Power Supply V oltage Power Supply Current Power Dissipation

Eff. Date 9 Nov 2000

FMSC-PSDA-002-01

Eff. Date

Eff. Date

Eff. Date Matsushita Electronics Corporation

元器件交易网

Prepared Checked Approved

Product Specifications

Eff. Date Matsushita Electronics Corporation

元器件交易网

Prepared Checked Approved

Product Specifications

Ref No. Total Page Page No.

F-1 7 6

AN17880A

Eff. Date

Eff. Date Matsushita Electronics Corporation

+

9

+

10µF

+

22µF

+

10k

+

+

-

-

-

10k

+

IN1

元器件交易网

Prepared Checked Approved