异步通信接口的设计

基于FPGA/CPLD的通用异步通信接口UART的设计

2 整体与各部分 功能详述

U R 处理的是并行数据转为串行信号和串行转为并行, AT

但并不是简单地转换 。分析 U R A T的结构 , 以看 出 U R 可 A T主 要 由数据总线 接 口、 制逻 辑和状态 接 口、 控 波特率发生 器 、 发 送逻辑和接 收逻辑等 部分组成 , 各部分间关系如 图 2 。 .

维普资讯

僵J拄木 与僵J佑 I I

基 于 F G / P D的 通 用 异 通 信 接 口 U R P A CL 步 A T的 设 计

TeD s no U R ( n e a A ycr os ee e Tas ie) a do P MC L h e g f A T U i r l s h nu ci r r m tr bs nF G P D i v s n o R v n t e

GA C L , P D,ii eat b t f e —u tm tgaeC rut o iigE i tSt tiueo micso I ert i i。c mbnn DA wt nB C L i o s u th ii h r s n c h P Dw lc nt c edg l r t t yt q iMya dep de t . sat l nrd csameh d t ei at ae ntepo rmma l gcd - a ss m ue n x einl r ceit ue to odsg u r b sdo h rga l e y i o n bel i e o vc i e矸, , P .T ecr u c o fUA T i n gae nF矗 CP D.T l d inicu e h rnmie L gc GA C I h oefn t no i R sit rtdi 1 e L ns e g n ldsteTa s t r o i、 s t t c ie o i a dteB u rt n rtr lfn t naegv nb HD rei lme tt no ei 、i la h Reev rL gcn a daeGe eao .Al u ci r ie yV L. h e h o mpe na o f sg s i d n mu -

hidl 异步回调实现原理

hidl 异步回调实现原理hidl(HAL Interface Definition Language)是Android系统中用于定义硬件抽象层(HAL)接口的一种语言。

HAL是Android系统与硬件之间的接口层,它负责处理底层硬件和操作系统之间的通信。

hidl异步回调是hidl中一种实现异步通信机制的方式,本文将介绍hidl异步回调的原理和实现。

我们来了解一下什么是异步回调。

在传统的同步通信中,调用者发起一个请求后,会一直等待返回结果,直到接收到结果后才继续执行下一步操作。

而在异步通信中,调用者发起一个请求后,不需要等待结果返回,可以继续执行其他操作。

当结果返回时,通过回调函数的方式通知调用者。

hidl异步回调的实现原理如下:1. 定义回调接口:在hidl中,定义一个回调接口,该接口包含了需要返回的结果和对应的回调函数。

回调函数通常是在请求发起者的上下文中执行的。

2. 注册回调函数:在发起请求之前,需要将回调函数注册到对应的服务对象中。

这样当结果返回时,服务对象就可以调用注册的回调函数来通知请求发起者。

3. 发起异步请求:在调用者的代码中,通过服务对象调用对应的异步请求函数。

这些函数通常使用异步关键字来标识,例如异步函数可能是以“async”开头的。

在调用异步请求函数时,需要传递回调接口对象作为参数。

4. 处理异步请求:在服务对象中,当收到异步请求时,会在后台线程中处理请求。

在请求处理完成后,服务对象会调用注册的回调函数来通知请求发起者。

5. 回调函数执行:当注册的回调函数被调用时,请求发起者的上下文会被切换到回调函数的执行上下文中。

这样可以在回调函数中处理返回的结果,例如更新UI界面或执行其他操作。

通过上述步骤,hidl异步回调可以实现在发起请求后,不阻塞调用者的操作,同时在结果返回时及时通知调用者。

这种机制可以提高系统的响应速度和效率。

总结一下,hidl异步回调是Android系统中一种实现异步通信机制的方式。

基于TMSMS320C6713异步串口通信的设计与实现

.. _

6 一_o

瞰DR ±rJ R2。Irr R 上*

I)X l

lI TIIN Tl01JT 14

L -0 丁 -O'- 0

10 髓瑚 T:0UT 二 . 0 D 三

oND . ..一-J

上 --0 上 一o .旦. ---0

啦 上

广L /

趣 0ND

片 的更新和发展 以及 CPU运算速度 的不断提高 , 接收到 的信号是 同步信号 。本设计在 McBSP与

芯片的性价比也越来越 高 。因此 DSP在通信 、家 串 口之 间加 了一 个 电 平 转 换 芯 片 MXA3232,把

电 、医疗 器 械 、电力 、组 合 导航 等 领 域 发 挥着 重 要 rrrL电平 转 换 为 RS232之 后 才 能 实 现异 步 串 口。

70

机 电技术

2016年 4月

基 于 TMS320C6713异 步 串口通信 的设计与实现

刘 义 王 玲 赵艳 霞 郝永平

(沈 阳理工大学 兵器科学技术研究 中心 ,辽宁 沈阳 110159) 摘 要 :为 了解决 TMS320C6713没有异 步串 口通信 的问题 ,文 中介绍 两种方法来 实现 串ISl异步通信 :多通道缓 冲串 行 接 口(McBSP)和增 强型直接存储器存取 (EDMA);多通道缓 冲串行接 口(McBSP)和 MAX3111。经实验验证这两种方案 不但解决 了TMS320C6713芯片只有 同步串 口而不能进行异步传输 的问题 ,而且 软 、硬件设计 比较简单 、成本低 ,便于实现。 关键词 :TMS320C6713;异步串 口通信 ;McBSP;MAX3111 中图分类号 :TP211 文献标识码 :A 文章编号 :1672—4801(2016)02—070—04

USART通信接口设计实验

UART_Data = 0; } } }

四、实验现象和结果

1、把串口线和 PC 机连接起来,运行程序后,通过串口调试软件发送 ASCII 码字符(需 要以回车键结尾)到单片机实验板,单片机实验板接收到从串口调试软件发送过来的 ASCII

实验四 UART 通信接口设计实验

一、实验目的

1、理解用异步串行通信进行 RS232 通信的原理并能掌握其方法及编程;

2、学习使用定时器 T1 做波特率发生器,掌握计算波特率的方法。

二、实验仪器

1、自制的 C8051f410 实验开发板 1 块

2、直流稳压电源、示波器

各1台

3、仿真器(U-EC6)

1只

码字符后,又将同样的字符回送给串口调试软件,这样串口调试软件可以看到返回同样的字

符,如果收发的字符相同,则说明 PC 机与单片机实验板之间的通信成功,如下图所示。

注: 串口通信波特率、位数据位、停止位、校验等参数设置值参考上图。

五、预习要求

1、读懂程序; 2、预先给出修改代码,以便更快更好的得出实验结果;

4、PC 机

1台

三、实验内容

实验任务:编写程序将单片机的 P0.4、P0.5 口配置为串口 0 通信口,将 PC 机发送给

c8051f410 的数据原样发回 PC 机,程序中用“0x0d”作为帧尾标志。

PC 端发送、接收可采用串口接收软件“串口调试助手 V2.1”。

在程序中通过交叉开关配置 TX0,RX0 分别到 P0.4、P0.5 引脚,由于 I/O 口是 TTL 电 平信号,需要通过 MAX232 转换为 RS-232 电平后才能与 PC 机连接,连接电路如上图所示。

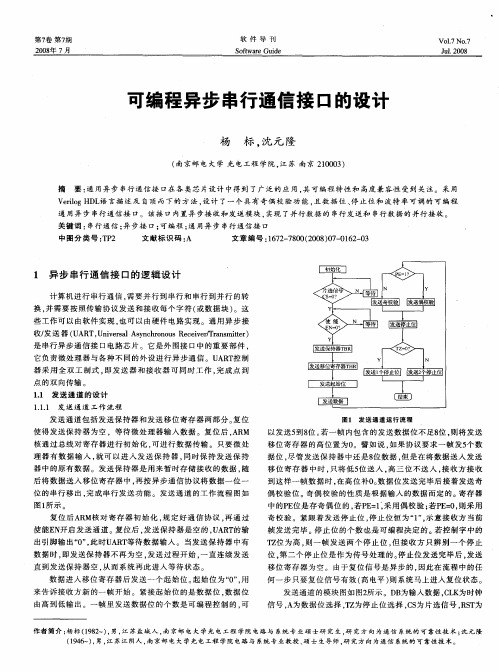

基于VK3366的DSP异步串行通信的设计

基于VK3366的DSP异步串行通信的设计作者:杨侃余辉黄艳辉陈淑凤来源:《现代电子技术》2013年第12期摘要:介绍了异步串口扩展芯片VK3366的性能特点,设计了基于数字信号处理器件TMS320C6713B并口与VK3366扩展多串口的硬件电路方案,且在CCS 3.0环境下完成了TMS320C6713B初始化VK3366的软件编程。

电路设计实现了系统高效多串口通信扩展,增强了系统通信接口控制能力。

关键词: TMS320C6713B; VK3366;异步串口扩展;通信接口中图分类号: TN911⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)12⁃0106⁃03随着数字信号处理技术和集成电路技术的不断发展,数字信号处理器的可靠性也越来越高,应用亦越来越广。

在DSP应用系统中通常需要由DSP接受上位机的控制信号或进行下位机通信,最常见的方式是采用异步串行接口RS 232或RS4 22来实现。

本文的信号采集模块采用TMS320C6713B芯片为例,但没有集成UART接口,因此进行扩展异步串口通讯芯片或者配置McBSP以实现与其他串行设备高速异步通信。

本文选择异步串口扩展芯片VK3366进行扩展。

1 数据采集硬件系统设计数据采集电路系统主要包括:数据信号处理TMS320C6713B子系统、AIC32音频采集电路子系统和异步串口扩展芯片VK3366系统等,其逻辑框图如图1所示。

音频采集电路子系统负责采集外部语音信号,数字信号处理器TMS320C6713B子系统进行采集数据的信号处理,VK3366子系统负责系统接口扩展进行数据传输。

1.1 数字信号处理器子系统TMS320C6713B(简称C6713)是美国德州仪器公司(TI)推出一款32位浮点型高速数字处理器DSP,它可在300 MHz的时钟频率下实现1 800 MIPS/2 400 MFLOPS的定点和浮点运算,极大满足了高速数据采集与实时控制系统对信号处理速度的要求。

UART

数据方向和通信速度

数据传输可以首先从最低有效位(LSB)开始。然而,有些UART允许灵活选择先发送最低有效位或最高有效位(MSB)。

UART是通用异步收发器(异步串行通信口)的英文缩写,它包括了RS232、RS499、RS423、RS422和RS485等接口标准规范和总线标准规范,即UART是异步串行通信口的总称。

而RS232、RS499、RS423、RS422和RS485等,是对应各种异步串行通信口的接口标准和总线标准,它规定了通信口的电气特性、传输速率、连接特性和接口的机械特性等内容

3.UART是硬的,而RS232是软的

1.UART是种接口,而RS232则是电平协议UART的全称:Universal Asynchronous Receiver and Transmitter 通用异步收发器

RS232则是用-5V--12V表示逻辑1,用+5V-+12V表示逻辑0。RS232是负逻辑。

2.UART是物理设备,RS232则是一种串行接口的标准,不严格时也可以特指该标准的串行通讯口。

什么是 ቤተ መጻሕፍቲ ባይዱART

UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收。在嵌入式设计中,UART用来与PC进行通信,包括与监控调试器和其它器件,如EEPROM通信。

UART通信

UART首先将接收到的并行数据转换成串行数据来传输。消息帧从一个低位起始位开始,后面是7个或8个数据位,一个可用的奇偶位和一个或几个高位停止位。接收器发现开始位时它就知道数据准备发送,并尝试与发送器时钟频率同步。如果选择了奇偶,UART就在数据位后面加上奇偶位。奇偶位可用来帮助错误校验。

DSP与PC机之间异步串行接口设计

D P技 术 S

读取 ) 。在 数据 输 出过 程 中,D S P把 要 输 出的字 符

(n a gI n te Gru o,t. A yn o &Se l o pC .Ld) r

[ src] hsp p rnrd c spo l xsigi d u l—u k t e l tr la ig ma hn n f c c iv d Ab t tT i a e t u e rbe e i n o beb c e e maei kn c iea de e t he e a i o ms t n wh at a

止位【。 2 1

韩 月秋 ( 9 6 ) 男,教 授 ,博士研 究生导 师,研 究方 向 13一,

为 雷达 信 号 处 理 和 I 设 计 ; C

陈 禾 ,女 ,副教授 ,硕士研 究生导 师,从 事 A C设计 及 SI 数字 集成 电路 的开发 与研 宄。

6料堆塌方和皮带打滑措施

维普资讯

D P技术 S

D SP与 P C机之向异齿串行接口设计

周 勇 ,韩 月秋 ,陈 禾

( 京理 工 大 学 电子工程 系 ,北京 l 0 8 ) 北 0 1 0

[ 摘要] 阐述 了D P通过 R 一3 一 S S 2 2 C与P C机的异 步串行通信原理 ,并给 出了 实现异步串 行通信的硬件接 口

0. 5次 。 由于 行 走小 车和 大 车 的启停 过 程采 用 变频 技 术, 使 车体振 动 有效 降 低 ,大 车进 给量 稳定 、斗 轮 取 料 量 稳 定 , 取 料 过 程 中 斗 轮 传 动 装 置 受 力 均 匀 , 机 械 故 障 有 效 降 低 , 设 备 维 修 量 降 低 。 由于 DT 0 2 0中文操 作 员界 面的使 用, 各种故 障能够及 时 显 示, 电 气维修 人 员根 据 故 障进 行维 护 , 有效 降低 维 修 时 间, 提 高 了设 备 作 业 率 。

EMI原理图

EMI原理图

嵌入式微控制器接口(EMI)是一种用于连接微控制器和其他

外部设备的通信接口。

常见的EMI接口包括串口通信和并行

接口。

串口通信是一种通过单一的数据线进行数据传输的接口。

它可以通过两种方式进行通信:同步和异步。

在同步通信中,发送方和接收方的时钟信号保持同步。

在异步通信中,数据被分成固定的块进行传输,并且每个块之间有固定的时间间隔。

并行接口是一种通过多个数据线同时传输数据的接口。

它可以实现更高的数据传输速率,但需要更多的引脚和更复杂的硬件设计。

为了实现EMI接口,需要在微控制器和外部设备之间进行数

据格式的匹配。

例如,在串口通信中,需要定义数据的位数、数据的顺序和校验位等。

在并行接口中,需要确定数据的位数、引脚分配和时序等。

在EMI接口中,还可以使用中断来提高通信的效率。

中断是

一种机制,允许微控制器在执行其他任务时同时接收外部设备发送的数据。

为了实现可靠的EMI通信,还需要考虑电气特性,例如信号

的干扰、电压的幅度和电源噪声等。

为了减少这些问题,可以采取屏蔽、阻抗匹配和地线隔离等措施。

总之,EMI是一种重要的通信接口,它在嵌入式系统中的应用非常广泛。

需要合理设计和实现EMI接口,以实现微控制器和外部设备之间的可靠数据传输。

基于CPLD的异步串行接口芯片设计

基于CPLD的异步串行接口芯片设计【摘要】针对传统的异步串行接口设计方法,本文提出了通过VHDL语言在CPLD(复杂的可编程逻辑器件)上实现异步串行接口的设计方法。

并通过MAXplus软件对软件程序仿真验证和硬件实测,结果表明,此电路工作正确可靠,灵活性强,能满足设计要求。

【关键词】复杂可编程逻辑器件;异步串行接口0 引言串行通信接口在CPU和外部设备或者微处理器与外设进行通信之间扮演着十分重要的角色。

其主要基本功能是在系统总线和I/O设备之间传输信号,提供缓冲作用,以满足接口两边的时序要求。

传统的异步串行通信接口一般采用专用的接口芯片实现。

例如串行通信接口8251A,而在现代数字系统设计中要求相对较少的芯片的数量以减少其硬件开销、缩小系统体积、降低能源消耗、提高系统的性能和可靠性。

因此CPLD的出现,为异步串行通信接口的设计提供了一种新的途径。

CPLD具有高速、成本低廉、设计周期短和应用灵活等特点,可以实现专用集成电路。

本设计通过VHDL语言在CPLD上进行编程实现异步串行接口,实验表明正确可靠,灵活性强。

1 异步串行接口的CPLD设计及实现方法数据传输的通信协议是对数据传输的约定,包括定时、控制、格式化和数据表示法。

串行通信是指数据是一位一位按顺序传送的通信方式,其突出优点是只需要一对传输线(利用电话线就可作为传输线),这样就大大降低了传送成本,特别适用于远距离通信。

其缺点就是传送速度较低。

异步传输是把每个字符看作以个独立的信息,并且字符出现在数据流中的相对时间是任意的。

然而在每个字符中的各位以预定的固定时钟传送。

因此其实质是在字符内部是同步的,而在字符间是异步的。

1.1 CPLD简介复杂可编程逻辑器件CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路,其基本设计方法是借助EDA软件,用原理图、状态机、布尔表达式、硬件描述语言等方法,生成相应的目标文件,用编程器和下载电缆用目标器件实现设计的数字系统。

FPGA接口设计研究

FPGA接口设计研究1EMIF16接口异步通信模式根据控制信号的特性,EMIF16在异步通信时有三种模式可选,分别是写触发模式(WEmode)、片选触发模式(CEmode)与外部等待模式(Extend-edWaitmode)。

其中,写触发模式默认通过驱动的3通道,其对应的地址空间为0x7C000000-0x7FFFFFFF,且不能伴随其他模式一同使用。

片选触发模式具备较强灵活性,能够适用于4个存取片区。

外部等待模式允许外部设备灵活插入异步硬件等待时间,本设计中采用了外部等待模式,具体读写时序如图2~3所示。

图2中,EM_*即对应1.1中提及的EMIF*信号,“14”代表等待信号EM_WAIT的建立时间,即EM_WAIT必须在/EM_OE跳高前(4E+3)ns内有效,才能正常插入外部等待;“11”代表外部等待的延迟时间,即EM_WAIT无效后/EM_OE的有效延迟时间,最大不超过(4E+3)ns;“2”代表EM_WAIT有效与无效时间最短时间为2E;其中E代表EMIF16的一个时钟周期。

图3中,EM_*同样对应1.1中提及的EMIF*信号,“28”代表等待信号EM_WAIT的建立时间,即EM_WAIT必须在/EM_WE跳高前(4E+3)ns内有效,才能正常插入外部等待;“25”代表外部等待的延迟时间,即EM_WAIT无效后/EM_WE的有效延迟时间,最大不超过(4E+3)ns;“2”代表EM_WAIT有效与无效时间最短时间为2E;其中E代表EMIF16的一个时钟周期。

2系统设计框架EMIF16接口的电平方式均为1.8VLVCMOS,根据系统需求,需转换成3.3VLVTTL以及最终的TTL电平模式,而作为中转站的FPGA则需兼具1.8VLVCMOS电平方式与3.3VLVTTL电平方式,最终转换成系统需求的TTL电平。

系统框图如图4所示。

设计中还需考虑系统的速度匹配:8核DSP外部输入的CORE_CLK时钟频率为100MHz,经设置DSP内部锁相环,将TMS320C6678的核心工作频率倍频至1GHz,EMIF16的工作频率为主频的1/6,即166.67MHz。

试析恶劣环境下异步串行接口电路的设计

6科技创新导报S T y I 2007N O .35Sci e nc e a nd Tec hno l o gy I nn ov at i on H e r al d工业技术科技创新导报自20世纪50年代以来,国外出现的各种军事武器系统,都要求系统中应用的各类计算机体积小、重量轻、可靠性高,同时又能抗各种恶劣自然环境与使用环境。

嵌入式计算机系统中,已广泛地应用于各种军事领域中。

在嵌入式计算机系统中,异步串行接口是与其他设备交换信息的通道,几乎所有的系统设计都要用到它,因此,接口电路设计的好坏直接关系到系统的可靠性。

设计时,要使异步串行接口能够阻断外界静电、噪声等对系统的影响,满足系统在恶劣环境中使用的要求。

异步串行接口单元需要设计接口电路才能与其他设备进行通信。

接口电路的实现有很多方法:可以用分立元件实现,但电路较为复杂;也可以使用集成芯片。

目前,有许多适合各种环境使用的M AXI M 公司的接口芯片可供选择。

下面介绍两种采用M AXI M 公司芯片实现的用于抗恶劣环境的接口电路,可防止外界对系统的影响。

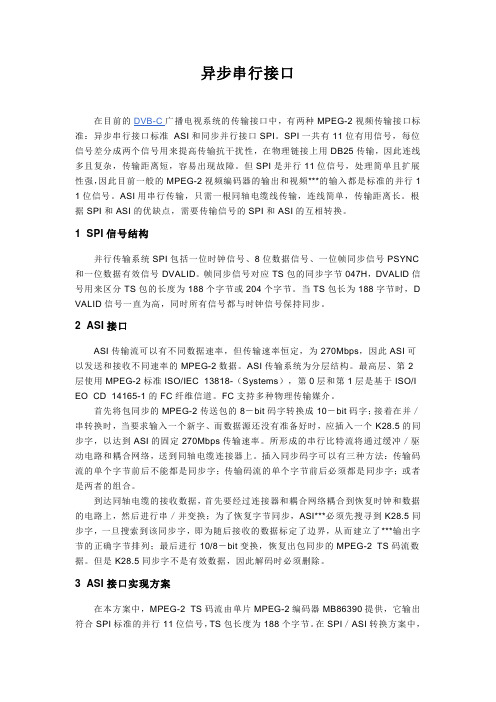

1抗静电冲击的接口电路用M A X202E 芯片实现的接口电路如图1所示。

M AX202E 为RS -232两路发送,两路接收,单一+5V 供电,可用于恶劣环境下。

每个发送器输出端和接收器输入端都抗±15K V 的静电冲击,其中具体指标为抗±15K V 人体静电、抗±8KV 的接触放电、抗±15KV 的空气间隙放电,满足E I A/T I A -232E 和CCI TTV .28规范,传输率高达120kb/s 。

由于单一+5V 供电,芯片内部自带电压转换装置。

+5V ~±10V 电压转换靠双路充放电压变换器实现:首先,充放电电压变换器通过电容C1将+5V 电压转换为+10V 电压,并将+10V 电压储存在V +输出滤波电容C 3中,然后通过电容C 2将+10V 电压转换为-10V,并将-10V 电压储存在V -输出滤波电容C4中。

RS422、485的设计与应用

RS-422/485的设计与应用摘要RS-422/485 是美国电子工业协会 (electronic industries al-liance,EIA)在 20 世纪 70 年代末推出的数字通讯电气标准。

该标准采用平衡驱动差分接收电路,最大传输速率 10 Mb/s,最大传输距离 1200 m,其中 RS-422 为全双工,RS-485 为半双工串行通信接口标准RS一422/48,具有显著的优点:抗干扰能力强,传输距离远,传送汽率高,因而在分布式控制系统和工业局部网络中得到日益广泛地应用。

RS-422/485 只对接口的电气特性作了规定,没有规定接插件、传输电缆和通讯协议,因此,在实际工程和应用中,用户根据实际情况自行设计,给实际应用带来了许多问题。

从物理层、传输层和应用层角度提出了设计和应用的要求,提出了构造串行异步通讯接口的方法,从而规范了 RS422/485 的设计。

而RS-422/485在众多领域中也开始运用的越来越多,比如:火力发电自动化系统,电隔离,串行口等。

并且利用率高,操作方便。

关键词:RS-422/485 串行通信接口标准AbstractRS-422/485 al-liance electronic (EIA), the Electronic Industry Association (industries) in the end of 1970s, the introduction of digital communication electrical standards. The standard adopts the balanced drive differential receiver circuit, the maximum transmission rate of 10 Mb/s, the maximum transmission distance of 1200 m, RS-422 for full duplex, RS-485 for the half duplex serial communication interface standard RS a 422/48, has significant advantages: strong anti-interference ability, transmission distance, high transmission rate, and thus in the distributed control system and industrial local network has been widely used. RS-422 / 485 only to the interface electrical characteristics specified, no provisions of connectors, cables and communication protocols. Therefore, in practical engineering and application, the user according to the actual situation of self-designed, to the actual application brought many problems. From the viewpoint of physical layer, transport layer and application layer, the design and application of the design and application of serial asynchronous communication interface is proposed, which can regulate the design of RS422/485. And RS-422/485 in many areas also began to use more and more, such as: thermal power automation system, electrical isolation, serial port, etc.. And the utilization rate is high, the operation is convenient.Key words: RS-422/485serial communication interface standard目录一、实验目的 (1)二、实验条件 (1)2.1开发软件 (1)2.2实验设备 (1)三、原理及其应用 (1)3.1 应用 (1)3.2原理 (1)3.2.1物理层 (1)3.2.2传输层 (3)3.2.3应用层 (4)4.1软件设计 (4)4.2 硬件设计 (5)五、实验结果分析与总结 (6)参考文献 (7)一、实验目的RS-422/485 电气标准被广泛应用于近距离数字系统之间的数据传输。

异步串行接口

异步串行接口在目前的DVB-C广播电视系统的传输接口中,有两种MPEG-2视频传输接口标准:异步串行接口标准ASI和同步并行接口SPI。

SPI一共有11位有用信号,每位信号差分成两个信号用来提高传输抗干扰性,在物理链接上用DB25传输,因此连线多且复杂,传输距离短,容易出现故障。

但SPI是并行11位信号,处理简单且扩展性强,因此目前一般的MPEG-2视频编码器的输出和视频***的输入都是标准的并行1 1位信号。

ASI用串行传输,只需一根同轴电缆线传输,连线简单,传输距离长。

根据SPI和ASI的优缺点,需要传输信号的SPI和ASI的互相转换。

1 SPI信号结构并行传输系统SPI包括一位时钟信号、8位数据信号、一位帧同步信号PSYNC 和一位数据有效信号DVALID。

帧同步信号对应TS包的同步字节047H,DVALID信号用来区分TS包的长度为188个字节或204个字节。

当TS包长为188字节时,D VALID信号一直为高,同时所有信号都与时钟信号保持同步。

2 ASI接口ASI传输流可以有不同数据速率,但传输速率恒定,为270Mbps,因此ASI可以发送和接收不同速率的MPEG-2数据。

ASI传输系统为分层结构。

最高层、第2层使用MPEG-2标准ISO/IEC 13818-(Systems),第0层和第1层是基于ISO/I EO CD 14165-1的FC纤维信道。

FC支持多种物理传输媒介。

首先将包同步的MPEG-2传送包的8-bit码字转换成10-bit码字;接着在并/串转换时,当要求输入一个新字、而数据源还没有准备好时,应插入一个K28.5的同步字,以达到ASI的固定270Mbps传输速率。

所形成的串行比特流将通过缓冲/驱动电路和耦合网络,送到同轴电缆连接器上。

插入同步码字可以有三种方法:传输码流的单个字节前后不能都是同步字;传输码流的单个字节前后必须都是同步字;或者是两者的组合。

到达同轴电缆的接收数据,首先要经过连接器和耦合网络耦合到恢复时钟和数据的电路上,然后进行串/并变换;为了恢复字节同步,ASI***必须先搜寻到K28.5同步字,一旦搜索到该同步字,即为随后接收的数据标定了边界,从而建立了***输出字节的正确字节排列;最后进行10/8-bit变换,恢复出包同步的MPEG-2 TS码流数据。

异步接口 轮训 与 回调-概述说明以及解释

异步接口轮训与回调-概述说明以及解释1.引言1.1 概述概述部分是对整篇文章的总体介绍,给读者提供一个整体的理解。

在异步接口、轮询和回调的主题下,概述部分应该简要概括这些概念的含义和重要性。

以下是可能的概述内容:第1.1节概述在现代的计算机应用程序中,异步接口、轮询和回调是非常重要的概念。

异步接口是指允许程序在进行某些操作时不必等待其完成,而是可以继续执行其他任务的一种机制。

这种机制对于提高程序的性能和响应能力非常重要。

轮询是一种常用的异步机制,它通过不断地查询某个资源的状态来实现任务的完成。

轮询可以应用于许多场景,例如在网络通信中检查数据的到达、在操作系统中等待进程的完成等。

回调是另一种常见的异步机制,它允许一个函数在某个事件发生时被调用。

回调函数在事件驱动的编程模型中非常常见,例如在用户界面开发中响应按钮点击事件、在网络编程中处理收到的数据等。

本文将详细介绍异步接口、轮询和回调的原理和用法。

首先我们将探讨异步接口的概念和优势。

然后,我们将详细解释轮询的工作原理和应用场景。

最后,我们将介绍回调函数的概念,以及它在不同领域的应用。

通过深入理解异步接口、轮询和回调,读者将能够更好地应用这些概念来优化自己的程序,并提高程序的性能和可靠性。

在接下来的章节中,我们将逐步展开对这些概念的详细讨论,希望读者通过阅读本文能够对这些关键概念有一个全面的了解。

1.2 文章结构文章结构部分的内容主要是对整篇文章的结构进行介绍和概括。

在本文中,文章可以分为引言、正文和结论三个部分。

引言部分主要包括概述、文章结构和目的。

其中,概述部分简要介绍了异步接口、轮训和回调的概念和作用;文章结构部分即本节所在的位置,用于介绍整篇文章的结构和内容安排;目的部分说明了本文旨在解释异步接口、轮训和回调的概念及其应用场景。

正文部分分为三个小节,分别对应了异步接口、轮训和回调的介绍。

其中,异步接口部分主要讲解了异步编程的概念、原理和优势;轮训部分解释了轮询的概念、使用场景和实现方式;回调部分介绍了回调函数的定义、使用方法和常见应用场景。

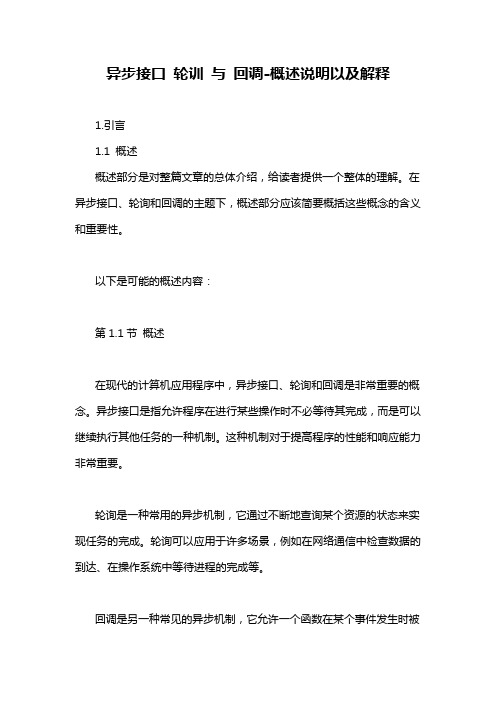

可编程异步串行通信接口的设计

VO. 7 1 No. 7 J12 0 u. 0 8

可编程 异步 串行通信接 口的设计

杨 标 . 元 隆 沈

( 京邮 电大 学 光 电工程 学 院 , 苏 南京 200 ) 南 江 1 0 3

摘

要 : 用异步 串行通 信接 口在 各 类芯 片设 计 中得到 了广泛 的应 用 , 可编 程特 性和 高度 兼 容性 受到 关 注。采 用 通 其

图l 示 。 所 复 位 后 A M核 对 寄 存 器 初 始 化 , 定 好 通 信 协 议 . 通 过 R 规 再

图 1 发 送 通 道 运行 流 程

以发 送5 5 。 到8 若一 帧 内包含 的发送 数据 位不 足8 。 位 则将发 送 移位 寄存 器 的高位 置为0 。譬 如说 , 如果协 议要 求一 帧发 5 数 个 据位 , 管 发送保 持器 中还 是8 尽 位数 据 。 但是 在将数 据送 人发 送

奇 校 验 。 紧 跟 着 发 送 停 止 位 , 止 位 恒 为 “ ” 示 意 接 收 方 当 前 停 1.

使 能E N开启 发送 通道 。复位 后 , 送保 持器是 空 的 , AR 的输 发 U T

帧发 送完 毕 。 止位 的个 数也 是 可编程决 定 的。若控 制字 中的 停 T 位为高, Z 则一 帧 发送 两个 停 止位 , 接收 方 只辨 别一 个停 止 但

当引脚信号为低时采样时钟是clk16它的频率是波特率时钟的16倍若8个周期采样的结果都是0则有效的起始位被检测到并将起始位存入接收移位寄存器中接着采样数据位奇偶位和停止位它们都是在16倍的采样周期clk16处进行采样

第7 第 7 卷 期

2 0 年 7月 08

软 件 导 刊

So t r fwa eGude i

异步串行通信接口

1-12

联系方式:

CAN结构 结构

STM32的bxCAN的主要特点 的 的主要特点

北京源智天下科技有限公司

1-13

联系方式:

CAN模式 模式

STM32的bxCAN具有 种模式: 的 具有7种模式 具有 种模式:

北京源智天下科技有限公司

1-3

联系方式:

USART特征描述 特征描述

STM32的数据字长 的数据字长 通信格式

北京源智天下科技有限公司

1-4

联系方式:

USART发送器 发送器

USART发送配置过程如下: 发送配置过程如下: 发送配置过程如下

北京源智天下科技有限公司

1-6

联系方式:

USART增强功能 增强功能

LIN模式 模式 USART同步模式 同步模式 USART单线半双工通信 单线半双工通信 USART的智能卡功能 的智能卡功能 USART的IrDA模式 的 模式 USART的DMA通信 的 通信

USART的编程方法 的编程方法

库函数: 库函数: – USART_DeInit函数 函数 – USART_Init函数 函数 – USART_StrucInit函数 函数 – USART_Cmd函数 函数 – USART_ITConfig函数 函数 – USART_DMACmd函数 函数 – USART_SetAddress函数 函数 – USART_WakeUpConfig函数 函数 – USART_ReceiverWakeUpCmd函数 函数 – USART_LINBreakDetectionConfig函数 函数 – USART_LINCmd函数 函数 – USART_SendData函数 函数

USART结构 结构

伺服系统中多路异步串行通信接口的设计与应用

7 6・

《 测控技 术1 2 0 1 3年 第 3 2卷第 6期

伺服 系统中多路异步 串行通信接 口的设计与应用

刘新玮 ,李洪文 , 邓永停 , 乔

( 1 . 中国科学院 长春光学精密机械 与物 理研究所 , 吉林 长春

兵

1 0 0 0 3 9 )

1 3 0 0 3 3 ; 2 . 中国科 学院 研究生 院, 北京

f e r mi s s i o n o f t h e s e r v o c o n t r o ly wo r d s : T L1 6C 7 52 B; MCU;CP LD; s e r v o c o n t r o l ; UART

摘要: 为 了满足 伺服 控制 系统 的 高精 度 和 实 时性 要 求 , 设 计 了基 于 高速 单 片机 和 C P L D的 伺 服控 制 系

统。该伺 服 系统 不仅 要 与两轴 编码 器进行 通信 , 而且 还要 向上 位机 传 送 电机 的控 制 信 息 以及控 制 器 的

参数传 输 , 而单 片 机 系统 只 有 两 路 异 步 串行 通 信 接 口, 为 了满 足 系统 通 信 的 需要 , 利用 T I公 司 的

中 图分 类 号 : T P 2 7 1 . 5 文献 标识码 : A 文章 编号 : 1 0 0 0— 8 8 2 9 ( 2 0 1 3 ) 0 6— 0 0 7 6— 0 4

De s i g n a nd Ap pl i c a t i o n o f M ul t i pl e Un i v e r s a l As y nc h r o n o u s Re c e i v e r

Abs t r a c t : I n o r de r t o s a t i s f y t h e de ma n d s o f p r e c i s i o n a n d r e a l — t i me i n s e r v o c o n t r o l s y s t e m. t h e s y s t e m b a s e d o n t h e MCU a n d CPL D i S d e s i g n e d. Th e s e r v o c o n t r o l s y s t e m i S n o t o n l y t o c o mmu n i c a t e wi t h t wo e n c o d e r s . b u t a l s o t r a ns f e r c o n t r o l d a t a a n d pa r a me t e r s wi t h u p p e r c o mp u t e r .Bu t MCU o n l y h a s t wo UARTs . Fo r s a t i s f y i n g t h e s y s t e m c o mmu n i c a t i o n . t h e TL1 6 C7 52 B c h i p o f T e x a s I n s t r u me n t s i S u s e d t o d e s i g n t wo e x t r a UARTs . Ex . pe r i me n t a l r e s u l t s i n di c a t e t h a t t h e t wo e x t r a UARTs a r e wo r k i n g s i mp l e a n d s t a bl y a n d c a n a c h i e v e d a t a t r a n s —

PowerPC8270数据处理模块的异步总线接口设计

SDRAM、Flash等叫CPM分担嵌入式PowerPC内核的外围工 作任务,支持丰富的协议和接口,包含3路FCC接口、4路SCC 接口、2路SMC接口、1路SPI接口和1路I2C接口X,由于 其良好的可升级性、高集成度和低功耗等特性,该处理器已在

各类嵌入式计算机系统中广泛使用叫

连接器的异步总线接口,实现处理器与外部多个异步总线从 设备的通信。

2异步总线硬件接口

PowerPC8270数据处理模块内韶60X总线设计如图2所 示:PowerPC8270处理器芯片内部集成存储控制器,外接60X 总线接口(32位地址、64位数据);模块上的SDRAM、FLASH、 NVRAM存储芯片和FPGA直接挂接在60X总线上;60X总 线经过FPGA译码、隔离,形成异步总线接口直连底板连接器,

用于模块的对外通信。

60X总线控制器

PowerPC8270

FCC SCC | | SCC |

FPGA

复位拧制 片选译砒 上迫配置

2 RS232 2

路 以

路

算掳电电源路

太

网

2

+5V

连接器

图1 PowerPC8270数据处理模块结构

图2 60X总线关联框图 75

信息通信

2.1 60X总线 PowerPC8270处理器芯片的存储控制器拥有三种基本

式的拓扑结构,并且对地址线、数据线和时钟信号做等长处 理和阻抗控制。

PowerPC8270数据处理模块的FLASH、NVRAM和 FPGA串接在60X总线上,存储控制器均采用60X-GPCM状 态机模式,16位数据访问宽度。其中,系统FLASH挂接在 PowerPC8270处理器芯片的片选CSO上,用户FLASH挂接在 片选CS2上NVRAM挂接在片选CS3 ±;FPGA的内部寄存 器挂接在片选CS4上,片选CS5和CS6引入FPGA译码分配 给异步总线从设备;通过配置60X总线的片选访问,可调整对 应设备的访问时序。多个芯片进行PCB布线时,按器件类型 FLASH、NVRAM、FPGA先后顺序串联,地址线和数据线在器

异步串行通信的点对点型

异步串行通信的点对点型点对点型通信方式是DNC系统中最早采用的通信方式,它是基于RS232C/RS422串口来实现的,拓扑构造为星形,通信速率一般在IlO〜960Obit/s之间。

这种接口的通信协议通常分为三层,即物理层、链路层和应用层。

物理层相当于实际的物理联接,它实现通信介质上的比特流的传输。

链路层采用异步通信协议,它将数据开展帧格式的转换,提交物理层开展服务,或对物理层送到的帧开展检错处理,交给上层。

异步协议的特征是字符间的异步定时。

它将8位的字符看作一个独立信息,字符在传送的数据流中出现的相对时间是任意的。

但每一字符中的各位却以预定的时钟频率传送,即字符内部是同步的,字符间是异步的。

异步协议的检错主要利用字符中的奇偶校验位。

应用层就是具体的报文应答信号,往往由控制器厂家自行制定。

点对点的连接简单,成本低。

由于大部分计算机和数控机床都具有串行通信接口,所以实现起来比较方便。

但这种连接也有以下缺点:(1)传输距离短。

如RS232C的传输距离不超过50m,20mA 电流环和RS422/RS423的传输距离为IOOOnI左右。

(2)传输不够可靠。

这些接口和连接电缆的抗干扰能力较差,而且其传输过程的检错功能较弱。

(3)传输速率低,实时性差,响应速度慢。

(4)由于一台计算机不可能提供很多串行接口,所连设备数量有限,因此整个系统的规模就不可能很大。

(5)每台设备都需一条来自DNC主机的通信电缆,因此整个系统的电缆费用很大,而且导致系统环境的复杂性也大大增加。

(6)系统扩展不容易。

当系统需扩大时,不但要修改系统软件,而且也要更改硬件。

为了克服上述缺陷,人们提出了多种技术手段来满足DNC技术的发展需求。

早期主要采用的两种方式如图1所示。

第一种是DNC主机通过多路串口转换器实现与多台CNC机床的通信(图1(a)),但存在构造复杂、成本高、可靠性低等不利因素。

第二种是DNC主机通过智能多串口卡分别连结多台CNC机床(图1(b)),其构造连结虽然简单,但需开发智能通信软件,提高了成本。

多通道异步串行通信接口电路的设计

多通道异步串行通信接口电路的设计

刘丽

【期刊名称】《电脑开发与应用》

【年(卷),期】1999(000)008

【总页数】2页(P43-44)

【作者】刘丽

【作者单位】

【正文语种】中文

【中图分类】TP311

【相关文献】

1.异步串行通信接口电路的VHDL语言设计 [J], 刘兰石;郭建英;王长清

2.同步多通道数据输出和输入智能接口电路 [J], 邓力;刘和平;叶一麟;胡丹

3.多通道单片测温接口电路的设计 [J], 尹信琴;杜清珍

4.一种高质量的多通道I2S与TDM128音频信号转换接口电路设计 [J], 黄骏雄;江先阳;常胜

5.基于Android的物联型异步串行通信系统设计 [J], 郝纯刚;安康;黄文华

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要如今电子技术获得了飞速的发展,在其推动下,电子产品几乎渗透到社会的各个领域,有力地推动了社会生产的发展,同时也使现代电子产品性能进一步提高,产品更新换代节奏加快。

EDA技术在进入21世纪后,得到了很大的发展,其基本特征是采用高级语言描述,具有系统仿真和综合能力。

其VHDL语言设计的源文件,可以采用类似于C语言书写形式,并使用结构设计方法。

本文从现代信息社会的现状、需要及未来的发展趋势出发,对EDA这一目前流行的电子设计技术进行了深入的研究,结合科研和教学实例,研究它的应用。

描述了VHDL 语言及其基本特点, 讨论了VHDL 语言在EDA 中的诸多优点,对Quartus II开发软件做了基本介绍。

简述了Cyclone系列可编程逻辑器件的结构和功能。

本设计采用VHDL语言完成了异步通信接口的设计。

VHDL是一种硬件电路语言,可以利用VHDL语言来设计数字芯片,来完成各项功能。

在通信中,常常要进行数据的传输,数据的串并变换等等,用VHDL语言实现很方便。

异步通信接口是用来接收和发送数据帧的,可分为接受部分(用于接受数据)和发送部分(用于发送数据)。

关键词:VHDL;Quartus II;异步通信;接收机;发送机AbstractNowadays,the electronic technology has obtained the rapid development,under its impetus,Electronic products are nearly seeped society's each domain.The electronic technology powerfully impels the development of social product,simultaneously also makes the modern electronic products performance further to enhance, the product renewal rhythm is also quickly.The EDA technology into the 21st century,obtained the very big development, its basic characteristic uses the higher order langu age description, has the system’s simulation and the synthesizing capacity. The VHDL language designs the source document to be possible to use is similar with the C language written form, and uses the structural design method.In this paper, from the modern information society status, needs and future development trend of starting on the EDA. The popular electronic design technology has been conducted in-depth research, combination of research and teaching case studies its application. Describes the language and its basic characteristics of the VHDL language, discussed the many advantages of it in the EDA, Development of the Quartus II software to do a basic introduction.The Cyclone series of programmable logic devices is described the structure .This design uses the VHDL language completed the asynchronous communication interface design。

The VHDL is a kind of hardware electric circuit language, can make use of the language of VHDL to design the numerical chip, To complete all functions. In communications, usually need to carry on the data to deliver, the string of the data combines the transformation,and so on。

With VHDL language implementation is very convenient。

Asynchronous communication interface is used for sending and receiving data frames。

Can be divided into accept part(Used to accept data)and the sending part(Used to send data)。

Keywords: VHDL; Quartus II; different step correspondence;receiver;send out the machine目录1 绪论 (1)1.1 EDA技术的概念 (1)1.2 EDA技术的发展史 (1)1.3 EDA设计流程 (1)1.4 EDA技术的主要内容 (3)1.5 EDA技术的发展趋势 (6)1.6 EDA技术的应用 (7)1.6.1 EDA技术的应用形式 (7)1.6.2 EDA技术的应用场合 (7)2 VHDL硬件描述语言 (9)2.1 VHDL语言概述 (9)2.1.1 VHDL语言简介 (9)2.1.2 VHDL语言的特点 (9)2.1.3 VHDL语言的优点 (11)2.1.4 VHDL程序设计约定 (11)2.2 VHDL程序基本结构 (11)2.2.1 实体 (12)2.2.2 结构体 (13)2.2.3 库 (15)2.2.4 程序包 (15)2.2.5 配置 (16)3 QuartusⅡ开发系统简介 (17)3.1 QuartusⅡ软件介绍 (17)3.2 QuartusⅡ软件的特点 (17)3.3 QuartusⅡ软件可编程设计流程 (19)4 可编程逻辑器件 (22)4.1 可编程逻辑器件的发展简介 (22)4.2 可编程逻辑器件的分类 (23)4.3 现场可编程门阵列(FPGA)简介 (23)4.3.1 Cyclone器件 (25)4.3.2 Cyclone的特性和电路设计 (27)4.3.3 Cyclone的配置 (28)4.3.4 硬件电路板构成和管脚接口表 (30)4.4 复杂可编程逻辑器件CPLD简介 (30)5 VHDL语言实现异步通信接口的设计 (31)5.1 异步通信接口的设计要求 (31)5.2 异步通信接口的设计原理 (31)5.2.1 异步信息传送格式 (31)5.2.2 异步通信接口的接收机部分 (32)5.2.3 异步通信接口的发送机部分 (36)5.3 异步通信接口的设计内容 (36)5.3.1 异步通信接口的接收部分设计 (36)5.3.2 异步通信接口的发送部分设计 (43)5.3.3 异步通信接口的总体设计 (45)结论 (50)致谢 (51)参考文献 (52)附录A (53)附录B (62)1 绪论1.1 EDA技术的概念EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

1.2 EDA技术的发展史EDA技术伴随着计算机、集成电路、电子系统设计的发展,经历了计算机辅助设计(CAD:Computer Assist Design)、计算机辅助工程设计(CAE:Computer Assist Engineering Design)和电子设计自动化(EDA:Electronic Design Automation)三个发展阶段。

1. 20世纪70年代为计算机辅助设计CAD阶段。

2. 20世纪80年代为计算机辅助工程设计CAE阶段。

3. 20世纪90年代为电子系统设计自动化EDA阶段。

未来的EDA技术将向广度和深度两个方向发展,EDA技术将会超越电子设计的范畴进入其他领域,随着基于EDA的片上系统(SOC:System On Chip)设计技术的发展,软硬功能库的建立以及基于超高速硬件描述语言(VHDL:Very-High-Speed Integrated Circuit Hardware Description Language)自顶向下设计理念的确立,未来的电子系统的设计与规划将不再是电子工程师们的专利。

有专家认为,21世纪将是EDA技术快速发展的时期,并且EDA技术将是对21世纪产生重大影响的十大技术之一。

1.3 EDA设计流程利用EDA技术进行电路设计的大部分工作是在EDA软件工作平台上进行的,EDA设计流程如图1.1所示。

EDA 设计流程包括设计准备、设计输入、设计处理、器件编程和设计完成5个步骤,以及相应的功能仿真、时序仿真和器件测试3个设计验证过程。

1.设计准备设计准备是指设计者在进行设计之前,依据任务要求,对确定系统所要完成的功能及复杂程度、器件资源的利用和所需成本等做的准备工作,如进行方案论证、系统设计和器件设计输入等。

2.设计输入设计输入是将设计的系统或电路按照EDA 开发软件要求的某种形式表示出来,并送入计算机的过程。

设计输入方式有多种,包括图形输入方式,波形输入方式,采用硬件描述语言的文本输入方式,或者采用文本和图形两者混合的设计输入方式。