Automatic Tracking of Multiple Pedestrians with Group Formation and

Advanced Micro Devices, Inc.

To appear in ACM Transactions on Computer SystemsA General Framework for Prefetch Scheduling in Linked Data Structures and its Application to Multi-Chain PrefetchingSEUNGRYUL CHOIUniversity of Maryland,College ParkNICHOLAS KOHOUTEVI Technology LLC.SUMIT PAMNANIAdvanced Micro Devices,Inc.andDONGKEUN KIM and DONALD YEUNGUniversity of Maryland,College ParkThis research was supported in part by NSF Computer Systems Architecture grant CCR-0093110, and in part by NSF CAREER Award CCR-0000988.Author’s address:Seungryul Choi,University of Maryland,Department of Computer Science, College Park,MD20742.Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage,the ACM copyright/server notice,the title of the publication,and its date appear,and notice is given that copying is by permission of the ACM,Inc.To copy otherwise,to republish, to post on servers,or to redistribute to lists requires prior specific permission and/or a fee.c 2001ACM1529-3785/2001/0700-0001$5.00ACM Transactions on Computer Systems2·Seungryul Choi et al.Pointer-chasing applications tend to traverse composite data structures consisting of multiple independent pointer chains.While the traversal of any single pointer chain leads to the seri-alization of memory operations,the traversal of independent pointer chains provides a source of memory parallelism.This article investigates exploiting such inter-chain memory parallelism for the purpose of memory latency tolerance,using a technique called multi-chain prefetching. Previous works[Roth et al.1998;Roth and Sohi1999]have proposed prefetching simple pointer-based structures in a multi-chain fashion.However,our work enables multi-chain prefetching for arbitrary data structures composed of lists,trees,and arrays.This article makesfive contributions in the context of multi-chain prefetching.First,we intro-duce a framework for compactly describing LDS traversals,providing the data layout and traversal code work information necessary for prefetching.Second,we present an off-line scheduling algo-rithm for computing a prefetch schedule from the LDS descriptors that overlaps serialized cache misses across separate pointer-chain traversals.Our analysis focuses on static traversals.We also propose using speculation to identify independent pointer chains in dynamic traversals.Third,we propose a hardware prefetch engine that traverses pointer-based data structures and overlaps mul-tiple pointer chains according to the computed prefetch schedule.Fourth,we present a compiler that extracts LDS descriptors via static analysis of the application source code,thus automating multi-chain prefetching.Finally,we conduct an experimental evaluation of compiler-instrumented multi-chain prefetching and compare it against jump pointer prefetching[Luk and Mowry1996], prefetch arrays[Karlsson et al.2000],and predictor-directed stream buffers(PSB)[Sherwood et al. 2000].Our results show compiler-instrumented multi-chain prefetching improves execution time by 40%across six pointer-chasing kernels from the Olden benchmark suite[Rogers et al.1995],and by3%across four pared to jump pointer prefetching and prefetch arrays,multi-chain prefetching achieves34%and11%higher performance for the selected Olden and SPECint2000benchmarks,pared to PSB,multi-chain prefetching achieves 27%higher performance for the selected Olden benchmarks,but PSB outperforms multi-chain prefetching by0.2%for the selected SPECint2000benchmarks.An ideal PSB with an infinite markov predictor achieves comparable performance to multi-chain prefetching,coming within6% across all benchmarks.Finally,speculation can enable multi-chain prefetching for some dynamic traversal codes,but our technique loses its effectiveness when the pointer-chain traversal order is highly dynamic.Categories and Subject Descriptors:B.8.2[Performance and Reliability]:Performance Anal-ysis and Design Aids;B.3.2[Memory Structures]:Design Styles—Cache Memories;C.0[Gen-eral]:Modeling of computer architecture;System Architectures; C.4[Performance of Sys-tems]:Design Studies;D.3.4[Programming Languages]:Processors—CompilersGeneral Terms:Design,Experimentation,PerformanceAdditional Key Words and Phrases:Data Prefetching,Memory parallelism,Pointer Chasing CodeA General Framework for Prefetch Scheduling·3performance platforms.The use of LDSs will likely have a negative impact on memory performance, making many non-numeric applications severely memory-bound on future systems. LDSs can be very large owing to their dynamic heap construction.Consequently, the working sets of codes that use LDSs can easily grow too large tofit in the processor’s cache.In addition,logically adjacent nodes in an LDS may not reside physically close in memory.As a result,traversal of an LDS may lack spatial locality,and thus may not benefit from large cache blocks.The sparse memory access nature of LDS traversal also reduces the effective size of the cache,further increasing cache misses.In the past,researchers have used prefetching to address the performance bot-tlenecks of memory-bound applications.Several techniques have been proposed, including software prefetching techniques[Callahan et al.1991;Klaiber and Levy 1991;Mowry1998;Mowry and Gupta1991],hardware prefetching techniques[Chen and Baer1995;Fu et al.1992;Jouppi1990;Palacharla and Kessler1994],or hybrid techniques[Chen1995;cker Chiueh1994;Temam1996].While such conventional prefetching techniques are highly effective for applications that employ regular data structures(e.g.arrays),these techniques are far less successful for non-numeric ap-plications that make heavy use of LDSs due to memory serialization effects known as the pointer chasing problem.The memory operations performed for array traver-sal can issue in parallel because individual array elements can be referenced inde-pendently.In contrast,the memory operations performed for LDS traversal must dereference a series of pointers,a purely sequential operation.The lack of memory parallelism during LDS traversal prevents conventional prefetching techniques from overlapping cache misses suffered along a pointer chain.Recently,researchers have begun investigating prefetching techniques designed for LDS traversals.These new LDS prefetching techniques address the pointer-chasing problem using several different approaches.Stateless techniques[Luk and Mowry1996;Mehrotra and Harrison1996;Roth et al.1998;Yang and Lebeck2000] prefetch pointer chains sequentially using only the natural pointers belonging to the LDS.Existing stateless techniques do not exploit any memory parallelism at all,or they exploit only limited amounts of memory parallelism.Consequently,they lose their effectiveness when the LDS traversal code contains insufficient work to hide the serialized memory latency[Luk and Mowry1996].A second approach[Karlsson et al.2000;Luk and Mowry1996;Roth and Sohi1999],which we call jump pointer techniques,inserts additional pointers into the LDS to connect non-consecutive link elements.These“jump pointers”allow prefetch instructions to name link elements further down the pointer chain without sequentially traversing the intermediate links,thus creating memory parallelism along a single chain of pointers.Because they create memory parallelism using jump pointers,jump pointer techniques tolerate pointer-chasing cache misses even when the traversal loops contain insufficient work to hide the serialized memory latency.However,jump pointer techniques cannot commence prefetching until the jump pointers have been installed.Furthermore,the jump pointer installation code increases execution time,and the jump pointers themselves contribute additional cache misses.ACM Transactions on Computer Systems4·Seungryul Choi et al.Finally,a third approach consists of prediction-based techniques[Joseph and Grunwald1997;Sherwood et al.2000;Stoutchinin et al.2001].These techniques perform prefetching by predicting the cache-miss address stream,for example us-ing hardware predictors[Joseph and Grunwald1997;Sherwood et al.2000].Early hardware predictors were capable of following striding streams only,but more re-cently,correlation[Charney and Reeves1995]and markov[Joseph and Grunwald 1997]predictors have been proposed that can follow arbitrary streams,thus en-abling prefetching for LDS traversals.Because predictors need not traverse program data structures to generate the prefetch addresses,they avoid the pointer-chasing problem altogether.In addition,for hardware prediction,the techniques are com-pletely transparent since they require no support from the programmer or compiler. However,prediction-based techniques lose their effectiveness when the cache-miss address stream is unpredictable.This article investigates exploiting the natural memory parallelism that exists between independent serialized pointer-chasing traversals,or inter-chain memory parallelism.Our approach,called multi-chain prefetching,issues prefetches along a single chain of pointers sequentially,but aggressively pursues multiple independent pointer chains simultaneously whenever possible.Due to its aggressive exploitation of inter-chain memory parallelism,multi-chain prefetching can tolerate serialized memory latency even when LDS traversal loops have very little work;hence,it can achieve higher performance than previous stateless techniques.Furthermore,multi-chain prefetching does not use jump pointers.As a result,it does not suffer the overheads associated with creating and managing jump pointer state.Andfinally, multi-chain prefetching is an execution-based technique,so it is effective even for programs that exhibit unpredictable cache-miss address streams.The idea of overlapping chained prefetches,which is fundamental to multi-chain prefetching,is not new:both Cooperative Chain Jumping[Roth and Sohi1999]and Dependence-Based Prefetching[Roth et al.1998]already demonstrate that simple “backbone and rib”structures can be prefetched in a multi-chain fashion.However, our work pushes this basic idea to its logical limit,enabling multi-chain prefetching for arbitrary data structures(our approach can exploit inter-chain memory paral-lelism for any data structure composed of lists,trees,and arrays).Furthermore, previous chained prefetching techniques issue prefetches in a greedy fashion.In con-trast,our work provides a formal and systematic method for scheduling prefetches that controls the timing of chained prefetches.By controlling prefetch arrival, multi-chain prefetching can reduce both early and late prefetches which degrade performance compared to previous chained prefetching techniques.In this article,we build upon our original work in multi-chain prefetching[Kohout et al.2001],and make the following contributions:(1)We present an LDS descriptor framework for specifying static LDS traversalsin a compact fashion.Our LDS descriptors contain data layout information and traversal code work information necessary for prefetching.(2)We develop an off-line algorithm for computing an exact prefetch schedulefrom the LDS descriptors that overlaps serialized cache misses across separate pointer-chain traversals.Our algorithm handles static LDS traversals involving either loops or recursion.Furthermore,our algorithm computes a schedule even ACM Transactions on Computer SystemsA General Framework for Prefetch Scheduling·5when the extent of dynamic data structures is unknown.To handle dynamic LDS traversals,we propose using speculation.However,our technique cannot handle codes in which the pointer-chain traversals are highly dynamic.(3)We present the design of a programmable prefetch engine that performs LDStraversal outside of the main CPU,and prefetches the LDS data using our LDS descriptors and the prefetch schedule computed by our scheduling algorithm.We also perform a detailed analysis of the hardware cost of our prefetch engine.(4)We introduce algorithms for extracting LDS descriptors from application sourcecode via static analysis,and implement them in a prototype compiler using the SUIF framework[Hall et al.1996].Our prototype compiler is capable of ex-tracting all the program-level information necessary for multi-chain prefetching fully automatically.(5)Finally,we conduct an experimental evaluation of multi-chain prefetching us-ing several pointer-intensive applications.Our evaluation compares compiler-instrumented multi-chain prefetching against jump pointer prefetching[Luk and Mowry1996;Roth and Sohi1999]and prefetch arrays[Karlsson et al.2000], two jump pointer techniques,as well as predictor-directed stream buffers[Sher-wood et al.2000],an all-hardware prediction-based technique.We also inves-tigate the impact of early prefetch arrival on prefetching performance,and we compare compiler-and manually-instrumented multi-chain prefetching to eval-uate the quality of the instrumentation generated by our compiler.In addition, we characterize the sensitivity of our technique to varying hardware stly,we undertake a preliminary evaluation of speculative multi-chain prefetching to demonstrate its potential in enabling multi-chain prefetching for dynamic LDS traversals.The rest of this article is organized as follows.Section2further explains the essence of multi-chain prefetching.Then,Section3introduces our LDS descriptor framework.Next,Section4describes our scheduling algorithm,Section5discusses our prefetch engine,and Section6presents our compiler for automating multi-chain prefetching.After presenting all our algorithms and techniques,Sections7and8 then report on our experimental methodology and evaluation,respectively.Finally, Section9discusses related work,and Section10concludes the article.2.MULTI-CHAIN PREFETCHINGThis section provides an overview of our multi-chain prefetching technique.Sec-tion2.1presents the idea of exploiting inter-chain memory parallelism.Then, Section2.2discusses the identification of independent pointer chain traversals. 2.1Exploiting Inter-Chain Memory ParallelismThe multi-chain prefetching technique augments a commodity microprocessor with a programmable hardware prefetch engine.During an LDS computation,the prefetch engine performs its own traversal of the LDS in front of the processor,thus prefetching the LDS data.The prefetch engine,however,is capable of traversing multiple pointer chains simultaneously when permitted by the application.Conse-quently,the prefetch engine can tolerate serialized memory latency by overlapping cache misses across independent pointer-chain traversals.ACM Transactions on Computer Systems6·Seungryul Choi et al.<compute>ptr = A[i];ptr = ptr->next;while (ptr) {for (i=0; i < N; i++) {a)b)}<compute>ptr = ptr->next;while (ptr) {}}PD = 2INIT(ID ll);stall stall stallINIT(ID aol);stall stallFig.1.Traversing pointer chains using a prefetch engine.a).Traversal of a single linked list.b).Traversal of an array of lists data structure.To illustrate the idea of exploiting inter-chain memory parallelism,wefirst de-scribe how our prefetch engine traverses a single chain of pointers.Figure1a shows a loop that traverses a linked list of length three.Each loop iteration,denoted by a hashed box,contains w1cycles of work.Before entering the loop,the processor ex-ecutes a prefetch directive,INIT(ID ll),instructing the prefetch engine to initiate traversal of the linked list identified by the ID ll label.If all three link nodes suffer an l-cycle cache miss,the linked list traversal requires3l cycles since the link nodes must be fetched sequentially.Assuming l>w1,the loop alone contains insufficient work to hide the serialized memory latency.As a result,the processor stalls for 3l−2w1cycles.To hide these stalls,the prefetch engine would have to initiate its linked list traversal3l−2w1cycles before the processor traversal.For this reason, we call this delay the pre-traversal time(P T).While a single pointer chain traversal does not provide much opportunity for latency tolerance,pointer chasing computations typically traverse many pointer chains,each of which is often independent.To illustrate how our prefetch engine exploits such independent pointer-chasing traversals,Figure1b shows a doubly nested loop that traverses an array of lists data structure.The outer loop,denoted by a shaded box with w2cycles of work,traverses an array that extracts a head pointer for the inner loop.The inner loop is identical to the loop in Figure1a.In Figure1b,the processor again executes a prefetch directive,INIT(ID aol), causing the prefetch engine to initiate a traversal of the array of lists data structure identified by the ID aol label.As in Figure1a,thefirst linked list is traversed sequentially,and the processor stalls since there is insufficient work to hide the serialized cache misses.However,the prefetch engine then initiates the traversal of subsequent linked lists in a pipelined fashion.If the prefetch engine starts a new traversal every w2cycles,then each linked list traversal will initiate the required P T cycles in advance,thus hiding the excess serialized memory latency across multiple outer loop iterations.The number of outer loop iterations required to overlap each linked list traversal is called the prefetch distance(P D).Notice when P D>1, ACM Transactions on Computer SystemsA General Framework for Prefetch Scheduling·7 the traversals of separate chains overlap,exposing inter-chain memory parallelism despite the fact that each chain is fetched serially.2.2Finding Independent Pointer-Chain TraversalsIn order to exploit inter-chain memory parallelism,it is necessary to identify mul-tiple independent pointer chains so that our prefetch engine can traverse them in parallel and overlap their cache misses,as illustrated in Figure1.An important question is whether such independent pointer-chain traversals can be easily identi-fied.Many applications perform traversals of linked data structures in which the or-der of link node traversal does not depend on runtime data.We call these static traversals.The traversal order of link nodes in a static traversal can be determined a priori via analysis of the code,thus identifying the independent pointer-chain traversals at compile time.In this paper,we present an LDS descriptor frame-work that compactly expresses the LDS traversal order for static traversals.The descriptors in our framework also contain the data layout information used by our prefetch engine to generate the sequence of load and prefetch addresses necessary to perform the LDS traversal at runtime.While compile-time analysis of the code can identify independent pointer chains for static traversals,the same approach does not work for dynamic traversals.In dynamic traversals,the order of pointer-chain traversal is determined at runtime. Consequently,the simultaneous prefetching of independent pointer chains is limited since the chains to prefetch are not known until the traversal order is computed, which may be too late to enable inter-chain overlap.For dynamic traversals,it may be possible to speculate the order of pointer-chain traversal if the order is pre-dictable.In this paper,we focus on static LDS ter in Section8.7,we illustrate the potential for predicting pointer-chain traversal order in dynamic LDS traversals by extending our basic multi-chain prefetching technique with specula-tion.3.LDS DESCRIPTOR FRAMEWORKHaving provided an overview of multi-chain prefetching,we now explore the al-gorithms and hardware underlying its implementation.We begin by introducing a general framework for compactly representing static LDS traversals,which we call the LDS descriptor framework.This framework allows compilers(and pro-grammers)to compactly specify two types of information related to LDS traversal: data structure layout,and traversal code work.The former captures memory refer-ence dependences that occur in an LDS traversal,thus identifying pointer-chasing chains,while the latter quantifies the amount of computation performed as an LDS is traversed.After presenting the LDS descriptor framework,subsequent sections of this article will show how the information provided by the framework is used to perform multi-chain prefetching(Sections4and5),and how the LDS descriptors themselves can be extracted by a compiler(Section6).3.1Data Structure Layout InformationData structure layout is specified using two descriptors,one for arrays and one for linked lists.Figure2presents each descriptor along with a traversal code exampleACM Transactions on Computer Systems8·Seungryul Choi etal.a).b).Bfor (i = 0 ; i < N ; i++) {... = data[i].value;}for (ptr = root ; ptr != NULL; ) { ptr = ptr->next;}Fig.2.Two LDS descriptors used to specify data layout information.a).Array descriptor.b).Linked list descriptor.Each descriptor appears inside a box,and is accompanied by a traversal code example and an illustration of the data structure.and an illustration of the traversed data structure.The array descriptor,shown in Figure 2a,contains three parameters:base (B ),length (L ),and stride (S ).These parameters specify the base address of the array,the number of array elements traversed by the application code,and the stride between consecutive memory ref-erences,respectively.The array descriptor specifies the memory address stream emitted by the processor during a constant-stride array traversal.Figure 2b illus-trates the linked list descriptor which contains three parameters similar to the array descriptor.For the linked list descriptor,the B parameter specifies the root pointer of the list,the L parameter specifies the number of link elements traversed by the application code,and the ∗S parameter specifies the offset from each link element address where the “next”pointer is located.The linked list descriptor specifies the memory address stream emitted by the processor during a linked list traversal.To specify the layout of complex data structures,our framework permits descrip-tor composition.Descriptor composition is represented as a directed graph whose nodes are array or linked list descriptors,and whose edges denote address generation dependences.Two types of composition are allowed.The first type of composition is nested composition .In nested composition,each address generated by an outer descriptor forms the B parameter for multiple instantiations of a dependent inner descriptor.An offset parameter,O ,is specified in place of the inner descriptor’s B parameter to shift its base address by a constant offset.Such nested descriptors cap-ture the memory reference streams of nested loops that traverse multi-dimensional data structures.Figure 3presents several nested descriptors,showing a traversal code example and an illustration of the traversed multi-dimensional data structure along with each nested descriptor.Figure 3a shows the traversal of an array of structures,each structure itself containing an array.The code example’s outer loop traverses the array “node,”ac-cessing the field “value”from each traversed structure,and the inner loop traverses ACM Transactions on Computer SystemsA General Framework for Prefetch Scheduling·9a).b).c).for (i = 0 ; i < L 0 ; i++) {... = node[i].value;for (j = 0 ; j < L 1 ; j++) {... = node[i].data[j];}}for (i = 0 ; i < L 0 ; i++) {down = node[i].pointer;for (j = 0 ; j < L 1 ; j++) {... = down->data[j];}}node for (i = 0 ; i < L 0 ; i++) {for (j = 0 ; j < L 1 ; j++) {... = node[i].data[j];}down = node[i].pointer;for (j = 0 ; j < L 2 ; j++) {... = down->data[j];}}node Fig.3.Nested descriptor composition.a).Nesting without indirection.b).Nesting with indirection.c).Nesting multiple descriptors.Each descriptor composition appears inside a box,and is accompanied by a traversal code example and an illustration of the composite data structure.each embedded array “data.”The outer and inner array descriptors,(B,L 0,S 0)and (O 1,L 1,S 1),represent the address streams produced by the outer and inner loop traversals,respectively.(In the inner descriptor,“O 1”specifies the offset of each inner array from the top of each structure).Figure 3b illustrates another form of descriptor nesting in which indirection is used between nested descriptors.The data structure in Figure 3b is similar to the one in Figure 3a,except the in-ner arrays are allocated separately,and a field from each outer array structure,“node[i].pointer,”points to a structure containing the inner array.Hence,as shown in the code example from Figure 3b,traversal of the inner array requires indirect-ing through the outer array’s pointer to compute the inner array’s base address.In our framework,this indirection is denoted by placing a “*”in front of the inner descriptor.Figure 3c,our last nested descriptor example,illustrates the nestingACM Transactions on Computer Systems10·Seungryul Choi et al.main() { foo(root, depth_limit);}foo(node, depth) { depth = depth - 1; if (depth == 0 || node == NULL)return;foo(node->child[0], depth);foo(node->child[1], depth);foo(node->child[2], depth);}Fig.4.Recursive descriptor composition.The recursive descriptor appears inside a box,and is accompanied by a traversal code example and an illustration of the tree data structure.of multiple inner descriptors underneath a single outer descriptor to represent the address stream produced by nested distributed loops.The code example from Fig-ure 3c shows the two inner loops from Figures 3a-b nested in a distributed fashion inside a common outer loop.In our framework,each one of the multiple inner array descriptors represents the address stream for a single distributed loop,with the order of address generation proceeding from the leftmost to rightmost inner descriptor.It is important to note that while all the descriptors in Figure 3show two nesting levels only,our framework allows an arbitrary nesting depth.This permits describ-ing higher-dimensional LDS traversals,for example loop nests with >2nesting depth.Also,our framework can handle non-recurrent loads using “singleton”de-scriptors.For example,a pointer to a structure may be dereferenced multiple times to access different fields in the structure.Each dereference is a single non-recurrent load.We create a separate descriptor for each non-recurrent load,nest it under-neath its recurrent load’s descriptor,and assign an appropriate offset value,O ,and length value,L =1.In addition to nested composition,our framework also permits recursive compo-sition .Recursively composed descriptors describe depth-first tree traversals.They are similar to nested descriptors,except the dependence edge flows backwards.Since recursive composition introduces cycles into the descriptor graph,our frame-work requires each backwards dependence edge to be annotated with the depth of recursion,D ,to bound the size of the data structure.Figure 4shows a simple recursive descriptor in which the backwards dependence edge originates from and terminates to a single array descriptor.The “L”parameter in the descriptor spec-ifies the fanout of the tree.In our example,L =3,so the traversed data structure is a tertiary tree,as shown in Figure 4.Notice the array descriptor has both B and O parameters–B provides the base address for the first instance of the descriptor,while O provides the offset for all recursively nested instances.In Figures 2and 4,we assume the L parameter for linked lists and the D parame-ter for trees are known a priori,which is generally not ter in Section 4.3,we discuss how our framework handles these unknown descriptor parameters.In addi-ACM Transactions on Computer Systems。

智能门锁说明书

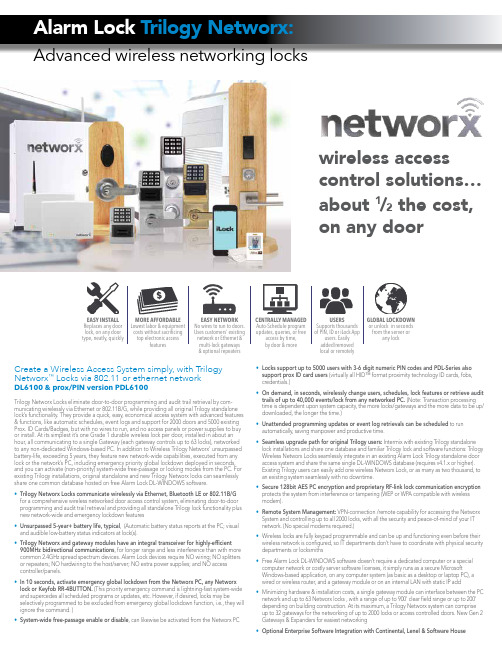

Create a Wireless Access System simply, with Trilogy Networx™ Locks via 802.11 or ethernet networkDL6100 & prox/PIN version PDL6100Trilogy Networx Locks eliminate door-to-door programming and audit trail retrieval by com-municating wirelessly via Ethernet or 802.11B/G, while providing all original Trilogy standalone lock’s functionality. They provide a quick, easy, economical access system with advanced features & functions, like automatic schedules, event logs and support for 2000 doors and 5000 existing Prox. ID Cards/Badges, but with no wires to run, and no access panels or power supplies to buy or install. At its simplest it’s one Grade 1 durable wireless lock per door, installed in about an hour, all communicating to a single Gateway (each gateway controls up to 63 locks), networked to any non-dedicated Windows-based PC. In addition to Wireless Trilogy Networx’ unsurpassed battery-life, exceeding 5 years, they feature new network-wide capabilities, executed from any lock or the network’s PC, including emergency priority global lockdown deployed in seconds, and you can activate (non-priority) system-wide free-passage or locking modes from the PC. For existing Trilogy installations, original standalone and new Trilogy Networx locks can seamlessly share one common database hosted on free Alarm Lock DL-WINDOWS software.•Trilogy Networx Locks communicate wirelessly via Ethernet, Bluetooth LE or 802.11B/G for a comprehensive wireless networked door access control system, eliminating door-to-door programming and audit trail retrieval and providing all standalone Trilogy lock functionality plus new network-wide and emergency lockdown features•Unsurpassed 5-year+ battery life, typical, (Automatic battery status reports at the PC; visual and audible low-battery status indicators at lock(s).•Trilogy Networx and gateway modules have an integral transceiver for highly-efficient 900MHz bidirectional communications, for longer range and less interference than with more common 2.4GHz spread spectrum devices. Alarm Lock devices require NO wiring; NO splitters or repeaters; NO hardwiring to the host/server; NO extra power supplies; and NO access controller/panels.•In 10 seconds, activate emergency global lockdown from the Networx PC, any Networx lock or Keyfob RR-4BUTTON. (This priority emergency command is lightning-fast system-wide and supercedes all scheduled programs or updates, etc. However, if desired, locks may be selectively programmed to be excluded from emergency global lockdown function, i.e., they will ignore the command. )•System-wide free-passage enable or disable, can likewise be activated from the Networx PC • Locks support up to 5000 users with 3-6 digit numeric PIN codes and PDL-Series also support prox ID card users (virtually all HID™ format proximity technology ID cards, fobs, credentials.)• On demand, in seconds, wirelessly change users, schedules, lock features or retrieve audit trails of up to 40,000 events/lock from any networked PC. (Note: Transaction processing time is dependent upon system capacity, the more locks/gateways and the more data to be up/ downloaded, the longer the time.)• Unattended programming updates or event log retrievals can be scheduled to run automatically, saving manpower and productive time.• Seamless upgrade path for original Trilogy users: Intermix with existing Trilogy standalone lock installations and share one database and familiar Trilogy lock and software functions: Trilogy Wireless Networx Locks seamlessly integrate in an existing Alarm Lock Trilogy standalone door access system and share the same single DL-WINDOWS database (requires v4.1.x or higher). Existing Trilogy users can easily add one wireless Networx Lock, or as many as two thousand, to an existing system seamlessly with no downtime.• Secure 128bit AES PC encryption and proprietary RF-link lock communication encryption protects the system from interference or tampering (WEP or WPA compatible with wireless modem).• Remote System Management: VPN-connection /remote capability for accessing the Networx System and controlling up to all 2000 locks, with all the security and peace-of-mind of your IT network. (No special modems required.)• Wireless locks are fully keypad programmable and can be up and functioning even before their wireless network is configured, so IT departments don’t have to coordinate with physical security departments or locksmiths• Free Alarm Lock DL-WINDOWS software doesn’t require a dedicated computer or a special computer network or costly server software licenses, it simply runs as a secure Microsoft Windows-based application, on any computer system (as basic as a desktop or laptop PC), a wired or wireless router, and a gateway module or on an internal LAN with static IP add• Minimizing hardware & installation costs, a single gateway module can interface between the PC network and up to 63 Networx locks , with a range of up to 900’ clear field range or up to 200’ depending on building construction. At its maximum, a Trilogy Networx system can comprise up to 32 gateways for the networking of up to 2000 locks or access controlled doors. New Gen 2 Gateways & Expanders for easiest networking• Optional Enterprise Software Integration with Continental, Lenel & Software Housewireless accesscontrol solutions…about 1/2 the cost,on any doorEASY INSTALL Replaces any door lock, on any door type, neatly, quicklyMORE AFFORDABLELowest labor & equipmentcosts without sacrificingtop electronic accessfeaturesEASY NETWORKNo wires to run to doors.Uses customers’ existingnetwork or Ethernet &multi-lock gateways& optional repeatersCENTRALLY MANAGEDAuto-Schedule programupdates, queries, or freeaccess by time,by door & moreUSERSSupports thousandsof PIN, ID or iLock Appusers. Easilyadded/removedlocal or remotelyGLOBAL LOCKDOWNor unlock in secondsfrom the server orany lock345 Bayview Ave, Amityville, New York 117011-800-ALA-LOCK • Fax 631-789-3383Trilogy and Networx is a trademark of Alarm Lock.© NAPCO 11/2017 ALA489EAL-IME2 Gen. 2 GatewayThe Trilogy Networx AL Generation Gateway, interfaces Networx locks with a PC network via a hardwire Ethernet connection. It is very similar in function to the original hardwired NetworxGateway Modules, but is enhanced with additional extended potential range, supporting up to seven(7) Expanders (model AL-IME2-EXP Expanders). Each Expander can extend the AL-IME2 Gateway’s coverage area by approximately 100 feet. Also both Gen. 2 Gateways and matching Expanders have a new modern styling, andthree LED indicators, blending into any décor.AL-IM2-80211 Gen. 2 802.11 GatewaySimilar to model above, but this 802.11 Gateway Module includes a bi-directional radio, andinterfaces Networx locks with a PC network with hardwire Ethernet and wireless 802.11. It is very similar in function to the original 802.11 Networx Gateway Modules, but is enhanced with additional extended potential range, supporting up to seven (7) Expanders (model AL-IME2-EXP Expanders). Each Expander can extend the AL-IM2-80211 Gateway’s coverage area by approximately 100 feet.AL-IME2-POE Gen. 2 GatewayThe Trilogy Networx AL-IME2-POE (Power Over Ethernet)Hardwired Gateway interfaces Networx locks with a PC network with hardwire Power-Over-Ethernet. It is very similar in function to the original hardwired Networx Gateway Modules, but is enhanced with alternative power, and additional extended potential range, supporting up to seven (7) Expanders (model AL-IME2-EXP Expanders).AL-IME2-EXP ExpanderTrilogy ® Networx ™ Expander extends the coverage area of a Gen 2 Series Gateways to Trilogy Networx Locks within a PC network, allowing greater distances for the placement of up to a maximum rated capacity of 63 Networx locks per Version 2 Gateway.AL-IME2-PIE Plug-in ExpanderThe Trilogy ® Networx ™ Plug-In Expander extends the coverage area of a Generation 2 Series AL-IME2 Gateway to Trilogy Networx Locks within a PC network, allowing greater 802.11 distances for the placement of up to a maximum rated capacity of 63 networx locks per Version 2 Gateway.ORIGINAL GATEWAYS AVAILABLE ‡‡AL-IM80211 Hardwire/Wireless Gateway, interfaces up to 63 Networx locks with PC network with hardwired Ethernet and wireless 802.11. AC Xformer supplied; ceiling/wall mount.AL-IME Hardwire Gateway similar to above, but using hardwired connection to the network via RJ45 Ethernet cable. AL-IME-USB Portable USB Gateway.AL-IMEPOE Hardwire Gateway Interface Module + POE, as above, but using hardwired Ethernet and Power Over Ethernet (POE). Connects directly to a network via Ethernet cable. ‡‡Important: For enterprise integration consult technical documentation to match proper AL hardware (Gateways, Expanders,etc.) with enterprisesoftware Versions supported.Trilogy, Networx, ArchiTech & iLock and ** Continental CardAccess or CA4K™ CardAccess are trademarks of Alarm Lock, a division of Napco.**Other marks remain the intellectual properties of their respective companies.• Wall- or ceiling-mountable, compact gateway modules are available in wireless/hardwired and wired-only versions (with Power Over Ethernet (POE) option). The hybrid model connects using either 802.11, Ethernet cable or 100Base-TX (using RJ45 Jack); the wired versions use an RJ-45 Ethernet cable. Networx communications support both wired Ethernet 10BaseT and wireless 802.11.• For the fastest most reliable networked system, in discovery setup mode, the system will locate and DL-WINDOWS will display each lock’s signal strength at each installed gateway, so you can select it and optimize reliable communications and eliminate guesswork.• Lock programming, user- and usage-data are stored locally at the battery-powered lock for uninterrupted door access usage in a power outage or server offline situation.Enterprise Networks, Real-Time Performance• Networx locks can be used as wireless, single-door controllers in real time too• Use with Contintental Access ® CA3000 , CA4K ®, or Lenel OnGuard ® Integrated Access Control & VideoSecurity and Software House Connected Partner ® Program Platforms ‡‡Trilogy Networx Lock Specifications:• Weatherproof locks for indoor/outdoor use with wide operating temperature range (-31 to 151˚ degrees F).• Cylindrical models boast industrial strength BHMA Grade 1 durability and all models feature vandal-resistant all-metal keypad for PIN codes.• PDL versions, HID Prox. Reader. • ADA-compliant leversets.• Easy-to-install modified ANSI A115 Series door prep; easily and neatly retrofit standard cylindrical knobsets and mechanical standalone locks, in under an hour. Non-handed • 3 hour UL fire-rated deadlatch.• Supports 1-5/8 to 1-7/8” door thickness; 2-3/4” backset (2-3/8” available.)• Manual key override standard; most IC cores alss supported on interchangeable core models.• Wide choice of 3 Architectural finishes (US3 polished brass, 26D satin chrome,10B duronodic) and IC core preps (6-7pin). Ordering Information:PDL6100 Cylindrical Trilogy Networx ™ PIN/Prox. Wireless Access Control Lock with built in HID proximity ID card reader, full-metal digital keypad, integral bi-directional radio, 4-C cell battery-operated (batts. supplied), serial number ID card, standard format SCI keyway for manual key override, 4-7/8” ASA Strike (incldd).DL6100 Cylindrical Trilogy ® Networx PIN-Code Wireless Access Control Lock, as above, with full-metal digital keypad only.PDL6500 Mortise version Networx PIN/Prox. lock, similar to 6100 Series above.DL6500 Mortise version Networx PIN-code only lock, similar to 6100 Series above.DL-WINDOWS Free Alarm Lock Trilogy Microsoft Windows-based software application, v4.0.1 or higher, supports Trilogy Networx and Trilogy standalone locks, with single database. No-charge, downloadable online at Network InterfaceINTERFACE: Ethernet 10Base-T or 100Base-TX (using RJ45 Jack)PROTOCOLS: TCP/IP , UDP/IP , DHCP 802.11 Wireless Specifications WIRELESS STANDARDS : IEEE 802.11b; 802.11g FREQUENCY RANGE : 2.412 - 2.484 GHzOUTPUT POWER: 14 dBm + 1.5 dBm/-1.0 dBmMAXIMUM RECEIVE LEVEL: -10dBm (with PER < 8%)DATA RATES WITH AUTOMATIC FALLBACK: 54Mbps - 1Mbps RANGE: Up to 328 feet indoorsMODULATION TECHNIQUES: OFDM, DSSS, CCK, DQPSK, DBPSK, 64 QAM, 16 QAMINTERFACE: Wireless 802.11b, 802.11g and 10/100 Ethernet PROTOCOLS: TCP/IP , UDP/IP , DHCP SECURITY• IEEE 802.11 - PSK with AES Encryption 128-bit Encryption • 128-bit AES Rijndael encryption AL Radio Link• 900 MHz GFSK, 50 channels, 10mW power output VOLTAGE: 5 - 6 volts AC/DCOPERATING TEMPERATURE: -20˚ to 60˚C (-4˚ to 140˚F)STORAGE: -40˚ to 85˚C (-40˚ to 185˚F)AVERAGE POWER CONSUMPTION:• 1300 mW (WLAN mode; maximum data rate)• 300 mW (WLAN mode; idle)• 750 mW (Ethernet Mode)PEAK SUPPLY CURRENT: 650 mA INPUT VOLTAGE: 5 - 6 volts AC/DCOPERATING TEMPERATURE: -31 to 151˚ degrees F STORAGE TEMPERATURE: -40˚ to 85˚C (-40˚ to 185˚F)‡‡Important: For enterprise integration consult technical documentation to match proper AL hardware (Gateways, Expanders,etc.) with enterprise software Versions supported.Up to 2000 locks and a PC communicate wirelessly through bidirectional Gateways – eliminating the need for door-to-doorprogramming and audit trail retrieval. System Management with free DL-WINDOWS or Enterprise Solutions:In seconds, globallockdown or unlock can be implemented from any Trilogy lock, even if the DL-WINDOWS computer is inaccessible or totallyoffline!。

多点遗失辅助选择器:midastouch说明书

Package‘midastouch’October13,2022Type PackageVersion1.3Title Multiple Imputation by Distance Aided Donor SelectionDate2016-02-06Maintainer Philipp Gaffert<**********************>Depends R(>=3.2.0)Imports utilsSuggests miceDescription Contains the function mice.impute.midastouch().Technically this func-tion is to be run from within the'mice'package(van Buuren et al.2011),type??mice.It substi-tutes the method'pmm'within mice by'midastouch'.The authors have shown that'midas-touch'is superior to default'pmm'.Many ideas are based on Siddique/Belin2008's MIDAS. License GPL-2|GPL-3LazyLoad yesLazyData yesURL https://www.uni-bamberg.de/fileadmin/uni/fakultaeten/sowi_lehrstuehle/ statistik/Personen/Dateien_Florian/properPMM.pdfNeedsCompilation noAuthor Philipp Gaffert[aut,cre],Florian Meinfelder[aut],V olker Bosch[aut]Repository CRANDate/Publication2016-02-0709:35:46R topics documented:mice.impute.midastouch (2)Index51mice.impute.midastouchPredictive Mean Matching with distance aided selection of donorsDescriptionImputes univariate missing data using predictive mean matchingUsagemice.impute.midastouch(y,ry,x,ridge=1e-05,midas.kappa=NULL,outout=TRUE,neff=NULL,debug=NULL,...)Argumentsy Numeric vector with incomplete datary Response pattern of y(TRUE=observed,FALSE=missing)x Design matrix with length(y)rows and p columns containing complete covari-ates.ridge The ridge penalty applied to prevent problems with multicollinearity.The de-fault is ridge=1e-05,which means that0.001percent of the diagonal is addedto the rger ridges may result in more biased estimates.Forhighly noisy data(e.g.many junk variables),set ridge=1e-06or even lowerto reduce bias.For highly collinear data,set ridge=1e-04or higher.midas.kappa Scalar.If NULL(default)then the optimal kappa gets selected automatically.Alternatively,the user may specify a scalar.Siddique and Belin2008findmidas.kappa=3to be sensible.outout Logical.If TRUE(default)one model is estimated for each donor(leave-one-out principle).For speedup choose outout=FALSE,which estimates one modelfor all observations leading to in-sample predictions for the donors and out-of-sample predictions for the recipients.Mind the inappropriateness,though.neff FOR EXPERTS.Null or character string.The name of an existing environ-ment in which the effective sample size of the donors for each loop(CE it-erations times multiple imputations)is supposed to be written.The effectivesample size is necessary to compute the correction for the total variance as orig-inally suggested by Parzen,Lipsitz and Fitzmaurice2005.The objectname ismidastouch.neff.debug FOR EXPERTS.Null or character string.The name of an existing environmentin which the input is supposed to be written.The objectname is midastouch.inputlist....Other named arguments.DetailsImputation of y by predictive mean matching,based on Rubin(1987,p.168,formulas a and b)and Siddique and Belin2008.The procedure is as follows:1.Draw a bootstrap sample from the donor pool.2.Estimate a beta matrix on the bootstrap sample by the leave one out principle.pute type II predicted values for yobs(nobs x1)and ymis(nmis x nobs).4.Calculate the distance between all yobs and the corresponding ymis.5.Convert the distances in drawing probabilities.6.For each recipient draw a donor from the entire pool while considering the probabilities fromthe model.7.Take its observed value in y as the imputation.ValueNumeric vector of length sum(!ry)with imputationsAuthor(s)Philipp Gaffert,Florian Meinfelder,V olker Bosch2015ReferencesGaffert,P.,Meinfelder,F.,Bosch V.(2015)Towards an MI-proper Predictive Mean Matching,Dis-cussion Paper.https://www.uni-bamberg.de/fileadmin/uni/fakultaeten/sowi_lehrstuehle/ statistik/Personen/Dateien_Florian/properPMM.pdfLittle,R.J.A.(1988),Missing data adjustments in large surveys(with discussion),Journal of Busi-ness Economics and Statistics,6,287–301.Parzen,M.,Lipsitz,S.R.,Fitzmaurice,G.M.(2005),A note on reducing the bias of the approxi-mate bayesian bootstrap imputation variance estimator.Biometrika92,4,971–974.Rubin,D.B.(1987),Multiple imputation for nonresponse in surveys.New York:Wiley.Siddique,J.,Belin,T.R.(2008),Multiple imputation using an iterative hot-deck with distance-based donor selection.Statistics in medicine,27,1,83–102Van Buuren,S.,Brand,J.P.L.,Groothuis-Oudshoorn C.G.M.,Rubin,D.B.(2006),Fully conditional specification in multivariate imputation.Journal of Statistical Computation and Simulation,76,12, 1049–1064.Van Buuren,S.,Groothuis-Oudshoorn,K.(2011),mice:Multivariate Imputation by Chained Equa-tions in R.Journal of Statistical Software,45,3,1–67./v45/i03/ Examples##from R::mice,slightly adapted###do default multiple imputation on a numeric matrixlibrary(midastouch)library(mice)imp<-mice(nhanes,method= midastouch )imp#list the actual imputations for BMIimp$imp$bmi#first completed data matrixcomplete(imp)#imputation on mixed data with a different method per column mice(nhanes2,method=c( sample , midastouch , logreg , norm ))Index∗micemice.impute.midastouch,2mice.impute.midastouch,2midastouch(mice.impute.midastouch),25。

计算机网络(第四版)课后习题(英文)+习题答案(中英文)

ANDREW S. TANENBAUM 秒,约533 msec.----- COMPUTER NETWORKS FOURTH EDITION PROBLEM SOLUTIONS 8. A collection of five routers is to be conn ected in a poi nt-to-poi nt sub net.Collected and Modified By Yan Zhe nXing, Mail To: Betwee n each pair of routers, the desig ners may put a high-speed line, aClassify: E aEasy, M ^Middle, H Hard , DaDeleteGree n: Importa nt Red: Master Blue: VI Others:Know Grey:—Unnecessary ----------------------------------------------------------------------------------------------ML V Chapter 1 In troductio nProblems2. An alter native to a LAN is simply a big timeshari ng system with termi nals forall users. Give two adva ntages of a clie nt-server system using a LAN.(M)使用局域网模型可以容易地增加节点。

如果局域网只是一条长的电缆,且不会因个别的失效而崩溃(例如采用镜像服务-------------------------------------------器)的情况下,使用局域网模型会更便宜。

堆叠自动编码器的优化技巧

自动编码器是一种常用的无监督学习算法,用于学习有效的数据表示。

而堆叠自动编码器(stacked autoencoders)则是一种深度学习模型,通过将多个自动编码器叠加在一起来构建更深层次的表示学习模型。

在实际应用中,堆叠自动编码器可以用于特征提取、降维、重构等任务。

然而,堆叠自动编码器的训练过程相对复杂,需要一些优化技巧来提高训练效果。

本文将探讨堆叠自动编码器的优化技巧。

### 1. 逐层训练堆叠自动编码器由多个自动编码器叠加而成,因此可以采用逐层训练的方法来提高训练效果。

逐层训练的基本思想是先训练第一层自动编码器,然后将其作为输入来训练第二层自动编码器,以此类推。

通过逐层训练,可以避免深层网络训练过程中的梯度消失或梯度爆炸问题,同时也可以更好地初始化模型参数。

### 2. 加入正则化在堆叠自动编码器的训练过程中,往往会出现过拟合的问题。

为了缓解过拟合,可以在训练过程中加入正则化项,如L1正则化、L2正则化或者dropout。

这些正则化技巧可以帮助模型更好地泛化到未见过的数据上,提高模型的鲁棒性。

### 3. 使用稀疏编码稀疏编码是一种有效的特征提取方法,可以帮助自动编码器学习更加鲁棒和有效的表示。

在堆叠自动编码器中,可以通过引入稀疏编码的约束条件,来促使模型学习稀疏的特征表示。

这样可以减少特征之间的冗余信息,提高特征的区分度,从而提高模型的性能。

### 4. 使用更复杂的激活函数自动编码器中常用的激活函数包括sigmoid、tanh和ReLU等,而在堆叠自动编码器中,可以尝试使用更复杂的激活函数来提高模型的表达能力。

例如,可以使用Leaky ReLU、ELU等激活函数来代替传统的激活函数,从而提高模型的非线性拟合能力。

### 5. 调整学习率学习率是影响模型训练效果的重要超参数。

在堆叠自动编码器的训练过程中,可以尝试使用不同的学习率来寻找最优的学习率。

通常可以采用学习率衰减的方法,逐渐减小学习率来提高模型的稳定性和收敛速度。

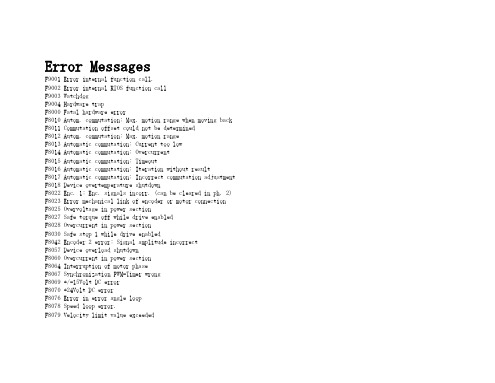

Indradrive 系列 故障代码

Error MessagesF9001 Error internal function call.F9002 Error internal RTOS function callF9003 WatchdogF9004 Hardware trapF8000 Fatal hardware errorF8010 Autom. commutation: Max. motion range when moving back F8011 Commutation offset could not be determinedF8012 Autom. commutation: Max. motion rangeF8013 Automatic commutation: Current too lowF8014 Automatic commutation: OvercurrentF8015 Automatic commutation: TimeoutF8016 Automatic commutation: Iteration without resultF8017 Automatic commutation: Incorrect commutation adjustment F8018 Device overtemperature shutdownF8022 Enc. 1: Enc. signals incorr. (can be cleared in ph. 2) F8023 Error mechanical link of encoder or motor connectionF8025 Overvoltage in power sectionF8027 Safe torque off while drive enabledF8028 Overcurrent in power sectionF8030 Safe stop 1 while drive enabledF8042 Encoder 2 error: Signal amplitude incorrectF8057 Device overload shutdownF8060 Overcurrent in power sectionF8064 Interruption of motor phaseF8067 Synchronization PWM-Timer wrongF8069 +/-15Volt DC errorF8070 +24Volt DC errorF8076 Error in error angle loopF8078 Speed loop error.F8079 Velocity limit value exceededF8091 Power section defectiveF8100 Error when initializing the parameter handlingF8102 Error when initializing power sectionF8118 Invalid power section/firmware combinationF8120 Invalid control section/firmware combinationF8122 Control section defectiveF8129 Incorrect optional module firmwareF8130 Firmware of option 2 of safety technology defectiveF8133 Error when checking interrupting circuitsF8134 SBS: Fatal errorF8135 SMD: Velocity exceededF8140 Fatal CCD error.F8201 Safety command for basic initialization incorrectF8203 Safety technology configuration parameter invalidF8813 Connection error mains chokeF8830 Power section errorF8838 Overcurrent external braking resistorF7010 Safely-limited increment exceededF7011 Safely-monitored position, exceeded in pos. DirectionF7012 Safely-monitored position, exceeded in neg. DirectionF7013 Safely-limited speed exceededF7020 Safe maximum speed exceededF7021 Safely-limited position exceededF7030 Position window Safe stop 2 exceededF7031 Incorrect direction of motionF7040 Validation error parameterized - effective thresholdF7041 Actual position value validation errorF7042 Validation error of safe operation modeF7043 Error of output stage interlockF7050 Time for stopping process exceeded8.3.15 F7051 Safely-monitored deceleration exceeded (159)8.4 Travel Range Errors (F6xxx) (161)8.4.1 Behavior in the Case of Travel Range Errors (161)8.4.2 F6010 PLC Runtime Error (162)8.4.3 F6024 Maximum braking time exceeded (163)8.4.4 F6028 Position limit value exceeded (overflow) (164)8.4.5 F6029 Positive position limit exceeded (164)8.4.6 F6030 Negative position limit exceeded (165)8.4.7 F6034 Emergency-Stop (166)8.4.8 F6042 Both travel range limit switches activated (167)8.4.9 F6043 Positive travel range limit switch activated (167)8.4.10 F6044 Negative travel range limit switch activated (168)8.4.11 F6140 CCD slave error (emergency halt) (169)8.5 Interface Errors (F4xxx) (169)8.5.1 Behavior in the Case of Interface Errors (169)8.5.2 F4001 Sync telegram failure (170)8.5.3 F4002 RTD telegram failure (171)8.5.4 F4003 Invalid communication phase shutdown (172)8.5.5 F4004 Error during phase progression (172)8.5.6 F4005 Error during phase regression (173)8.5.7 F4006 Phase switching without ready signal (173)8.5.8 F4009 Bus failure (173)8.5.9 F4012 Incorrect I/O length (175)8.5.10 F4016 PLC double real-time channel failure (176)8.5.11 F4017 S-III: Incorrect sequence during phase switch (176)8.5.12 F4034 Emergency-Stop (177)8.5.13 F4140 CCD communication error (178)8.6 Non-Fatal Safety Technology Errors (F3xxx) (178)8.6.1 Behavior in the Case of Non-Fatal Safety Technology Errors (178)8.6.2 F3111 Refer. missing when selecting safety related end pos (179)8.6.3 F3112 Safe reference missing (179)8.6.4 F3115 Brake check time interval exceeded (181)Troubleshooting Guide | Rexroth IndraDrive Electric Drivesand ControlsI Bosch Rexroth AG VII/XXIITable of ContentsPage8.6.5 F3116 Nominal load torque of holding system exceeded (182)8.6.6 F3117 Actual position values validation error (182)8.6.7 F3122 SBS: System error (183)8.6.8 F3123 SBS: Brake check missing (184)8.6.9 F3130 Error when checking input signals (185)8.6.10 F3131 Error when checking acknowledgment signal (185)8.6.11 F3132 Error when checking diagnostic output signal (186)8.6.12 F3133 Error when checking interrupting circuits (187)8.6.13 F3134 Dynamization time interval incorrect (188)8.6.14 F3135 Dynamization pulse width incorrect (189)8.6.15 F3140 Safety parameters validation error (192)8.6.16 F3141 Selection validation error (192)8.6.17 F3142 Activation time of enabling control exceeded (193)8.6.18 F3143 Safety command for clearing errors incorrect (194)8.6.19 F3144 Incorrect safety configuration (195)8.6.20 F3145 Error when unlocking the safety door (196)8.6.21 F3146 System error channel 2 (197)8.6.22 F3147 System error channel 1 (198)8.6.23 F3150 Safety command for system start incorrect (199)8.6.24 F3151 Safety command for system halt incorrect (200)8.6.25 F3152 Incorrect backup of safety technology data (201)8.6.26 F3160 Communication error of safe communication (202)8.7 Non-Fatal Errors (F2xxx) (202)8.7.1 Behavior in the Case of Non-Fatal Errors (202)8.7.2 F2002 Encoder assignment not allowed for synchronization (203)8.7.3 F2003 Motion step skipped (203)8.7.4 F2004 Error in MotionProfile (204)8.7.5 F2005 Cam table invalid (205)8.7.6 F2006 MMC was removed (206)8.7.7 F2007 Switching to non-initialized operation mode (206)8.7.8 F2008 RL The motor type has changed (207)8.7.9 F2009 PL Load parameter default values (208)8.7.10 F2010 Error when initializing digital I/O (-> S-0-0423) (209)8.7.11 F2011 PLC - Error no. 1 (210)8.7.12 F2012 PLC - Error no. 2 (210)8.7.13 F2013 PLC - Error no. 3 (211)8.7.14 F2014 PLC - Error no. 4 (211)8.7.15 F2018 Device overtemperature shutdown (211)8.7.16 F2019 Motor overtemperature shutdown (212)8.7.17 F2021 Motor temperature monitor defective (213)8.7.18 F2022 Device temperature monitor defective (214)8.7.19 F2025 Drive not ready for control (214)8.7.20 F2026 Undervoltage in power section (215)8.7.21 F2027 Excessive oscillation in DC bus (216)8.7.22 F2028 Excessive deviation (216)8.7.23 F2031 Encoder 1 error: Signal amplitude incorrect (217)VIII/XXII Bosch Rexroth AG | Electric Drivesand ControlsRexroth IndraDrive | Troubleshooting GuideTable of ContentsPage8.7.24 F2032 Validation error during commutation fine adjustment (217)8.7.25 F2033 External power supply X10 error (218)8.7.26 F2036 Excessive position feedback difference (219)8.7.27 F2037 Excessive position command difference (220)8.7.28 F2039 Maximum acceleration exceeded (220)8.7.29 F2040 Device overtemperature 2 shutdown (221)8.7.30 F2042 Encoder 2: Encoder signals incorrect (222)8.7.31 F2043 Measuring encoder: Encoder signals incorrect (222)8.7.32 F2044 External power supply X15 error (223)8.7.33 F2048 Low battery voltage (224)8.7.34 F2050 Overflow of target position preset memory (225)8.7.35 F2051 No sequential block in target position preset memory (225)8.7.36 F2053 Incr. encoder emulator: Pulse frequency too high (226)8.7.37 F2054 Incr. encoder emulator: Hardware error (226)8.7.38 F2055 External power supply dig. I/O error (227)8.7.39 F2057 Target position out of travel range (227)8.7.40 F2058 Internal overflow by positioning input (228)8.7.41 F2059 Incorrect command value direction when positioning (229)8.7.42 F2063 Internal overflow master axis generator (230)8.7.43 F2064 Incorrect cmd value direction master axis generator (230)8.7.44 F2067 Synchronization to master communication incorrect (231)8.7.45 F2068 Brake error (231)8.7.46 F2069 Error when releasing the motor holding brake (232)8.7.47 F2074 Actual pos. value 1 outside absolute encoder window (232)8.7.48 F2075 Actual pos. value 2 outside absolute encoder window (233)8.7.49 F2076 Actual pos. value 3 outside absolute encoder window (234)8.7.50 F2077 Current measurement trim wrong (235)8.7.51 F2086 Error supply module (236)8.7.52 F2087 Module group communication error (236)8.7.53 F2100 Incorrect access to command value memory (237)8.7.54 F2101 It was impossible to address MMC (237)8.7.55 F2102 It was impossible to address I2C memory (238)8.7.56 F2103 It was impossible to address EnDat memory (238)8.7.57 F2104 Commutation offset invalid (239)8.7.58 F2105 It was impossible to address Hiperface memory (239)8.7.59 F2110 Error in non-cyclical data communic. of power section (240)8.7.60 F2120 MMC: Defective or missing, replace (240)8.7.61 F2121 MMC: Incorrect data or file, create correctly (241)8.7.62 F2122 MMC: Incorrect IBF file, correct it (241)8.7.63 F2123 Retain data backup impossible (242)8.7.64 F2124 MMC: Saving too slowly, replace (243)8.7.65 F2130 Error comfort control panel (243)8.7.66 F2140 CCD slave error (243)8.7.67 F2150 MLD motion function block error (244)8.7.68 F2174 Loss of motor encoder reference (244)8.7.69 F2175 Loss of optional encoder reference (245)Troubleshooting Guide | Rexroth IndraDrive Electric Drivesand Controls| Bosch Rexroth AG IX/XXIITable of ContentsPage8.7.70 F2176 Loss of measuring encoder reference (246)8.7.71 F2177 Modulo limitation error of motor encoder (246)8.7.72 F2178 Modulo limitation error of optional encoder (247)8.7.73 F2179 Modulo limitation error of measuring encoder (247)8.7.74 F2190 Incorrect Ethernet configuration (248)8.7.75 F2260 Command current limit shutoff (249)8.7.76 F2270 Analog input 1 or 2, wire break (249)8.7.77 F2802 PLL is not synchronized (250)8.7.78 F2814 Undervoltage in mains (250)8.7.79 F2815 Overvoltage in mains (251)8.7.80 F2816 Softstart fault power supply unit (251)8.7.81 F2817 Overvoltage in power section (251)8.7.82 F2818 Phase failure (252)8.7.83 F2819 Mains failure (253)8.7.84 F2820 Braking resistor overload (253)8.7.85 F2821 Error in control of braking resistor (254)8.7.86 F2825 Switch-on threshold braking resistor too low (255)8.7.87 F2833 Ground fault in motor line (255)8.7.88 F2834 Contactor control error (256)8.7.89 F2835 Mains contactor wiring error (256)8.7.90 F2836 DC bus balancing monitor error (257)8.7.91 F2837 Contactor monitoring error (257)8.7.92 F2840 Error supply shutdown (257)8.7.93 F2860 Overcurrent in mains-side power section (258)8.7.94 F2890 Invalid device code (259)8.7.95 F2891 Incorrect interrupt timing (259)8.7.96 F2892 Hardware variant not supported (259)8.8 SERCOS Error Codes / Error Messages of Serial Communication (259)9 Warnings (Exxxx) (263)9.1 Fatal Warnings (E8xxx) (263)9.1.1 Behavior in the Case of Fatal Warnings (263)9.1.2 E8025 Overvoltage in power section (263)9.1.3 E8026 Undervoltage in power section (264)9.1.4 E8027 Safe torque off while drive enabled (265)9.1.5 E8028 Overcurrent in power section (265)9.1.6 E8029 Positive position limit exceeded (266)9.1.7 E8030 Negative position limit exceeded (267)9.1.8 E8034 Emergency-Stop (268)9.1.9 E8040 Torque/force actual value limit active (268)9.1.10 E8041 Current limit active (269)9.1.11 E8042 Both travel range limit switches activated (269)9.1.12 E8043 Positive travel range limit switch activated (270)9.1.13 E8044 Negative travel range limit switch activated (271)9.1.14 E8055 Motor overload, current limit active (271)9.1.15 E8057 Device overload, current limit active (272)X/XXII Bosch Rexroth AG | Electric Drivesand ControlsRexroth IndraDrive | Troubleshooting GuideTable of ContentsPage9.1.16 E8058 Drive system not ready for operation (273)9.1.17 E8260 Torque/force command value limit active (273)9.1.18 E8802 PLL is not synchronized (274)9.1.19 E8814 Undervoltage in mains (275)9.1.20 E8815 Overvoltage in mains (275)9.1.21 E8818 Phase failure (276)9.1.22 E8819 Mains failure (276)9.2 Warnings of Category E4xxx (277)9.2.1 E4001 Double MST failure shutdown (277)9.2.2 E4002 Double MDT failure shutdown (278)9.2.3 E4005 No command value input via master communication (279)9.2.4 E4007 SERCOS III: Consumer connection failed (280)9.2.5 E4008 Invalid addressing command value data container A (280)9.2.6 E4009 Invalid addressing actual value data container A (281)9.2.7 E4010 Slave not scanned or address 0 (281)9.2.8 E4012 Maximum number of CCD slaves exceeded (282)9.2.9 E4013 Incorrect CCD addressing (282)9.2.10 E4014 Incorrect phase switch of CCD slaves (283)9.3 Possible Warnings When Operating Safety Technology (E3xxx) (283)9.3.1 Behavior in Case a Safety Technology Warning Occurs (283)9.3.2 E3100 Error when checking input signals (284)9.3.3 E3101 Error when checking acknowledgment signal (284)9.3.4 E3102 Actual position values validation error (285)9.3.5 E3103 Dynamization failed (285)9.3.6 E3104 Safety parameters validation error (286)9.3.7 E3105 Validation error of safe operation mode (286)9.3.8 E3106 System error safety technology (287)9.3.9 E3107 Safe reference missing (287)9.3.10 E3108 Safely-monitored deceleration exceeded (288)9.3.11 E3110 Time interval of forced dynamization exceeded (289)9.3.12 E3115 Prewarning, end of brake check time interval (289)9.3.13 E3116 Nominal load torque of holding system reached (290)9.4 Non-Fatal Warnings (E2xxx) (290)9.4.1 Behavior in Case a Non-Fatal Warning Occurs (290)9.4.2 E2010 Position control with encoder 2 not possible (291)9.4.3 E2011 PLC - Warning no. 1 (291)9.4.4 E2012 PLC - Warning no. 2 (291)9.4.5 E2013 PLC - Warning no. 3 (292)9.4.6 E2014 PLC - Warning no. 4 (292)9.4.7 E2021 Motor temperature outside of measuring range (292)9.4.8 E2026 Undervoltage in power section (293)9.4.9 E2040 Device overtemperature 2 prewarning (294)9.4.10 E2047 Interpolation velocity = 0 (294)9.4.11 E2048 Interpolation acceleration = 0 (295)9.4.12 E2049 Positioning velocity >= limit value (296)9.4.13 E2050 Device overtemp. Prewarning (297)Troubleshooting Guide | Rexroth IndraDrive Electric Drivesand Controls| Bosch Rexroth AG XI/XXIITable of ContentsPage9.4.14 E2051 Motor overtemp. prewarning (298)9.4.15 E2053 Target position out of travel range (298)9.4.16 E2054 Not homed (300)9.4.17 E2055 Feedrate override S-0-0108 = 0 (300)9.4.18 E2056 Torque limit = 0 (301)9.4.19 E2058 Selected positioning block has not been programmed (302)9.4.20 E2059 Velocity command value limit active (302)9.4.21 E2061 Device overload prewarning (303)9.4.22 E2063 Velocity command value > limit value (304)9.4.23 E2064 Target position out of num. range (304)9.4.24 E2069 Holding brake torque too low (305)9.4.25 E2070 Acceleration limit active (306)9.4.26 E2074 Encoder 1: Encoder signals disturbed (306)9.4.27 E2075 Encoder 2: Encoder signals disturbed (307)9.4.28 E2076 Measuring encoder: Encoder signals disturbed (308)9.4.29 E2077 Absolute encoder monitoring, motor encoder (encoder alarm) (308)9.4.30 E2078 Absolute encoder monitoring, opt. encoder (encoder alarm) (309)9.4.31 E2079 Absolute enc. monitoring, measuring encoder (encoder alarm) (309)9.4.32 E2086 Prewarning supply module overload (310)9.4.33 E2092 Internal synchronization defective (310)9.4.34 E2100 Positioning velocity of master axis generator too high (311)9.4.35 E2101 Acceleration of master axis generator is zero (312)9.4.36 E2140 CCD error at node (312)9.4.37 E2270 Analog input 1 or 2, wire break (312)9.4.38 E2802 HW control of braking resistor (313)9.4.39 E2810 Drive system not ready for operation (314)9.4.40 E2814 Undervoltage in mains (314)9.4.41 E2816 Undervoltage in power section (314)9.4.42 E2818 Phase failure (315)9.4.43 E2819 Mains failure (315)9.4.44 E2820 Braking resistor overload prewarning (316)9.4.45 E2829 Not ready for power on (316)。

埃夫特 ER12-4-2000 工业机器人电气使用维护手册说明书

ER12-4-2000 工业机器人电气使用维护手册

目录

第 1 章 安全...............................................................................................................................1 1.1 安全须知................................................................................................................ 1 1.2 安全准则................................................................................................................ 1 1.3 各工作过程中的安全注意事项............................................................................ 2 1.3.1 机器人安装和连接的安全............................................................................ 2 1.3.2 机器人启动前的安全.................................................................................... 3 1.3.3 机器人启动的安全........................................................................................ 4 1.3.4 试车安全........................................................................................................ 4 1.3.5 示教过程中的安全........................................................................................ 5 1.3.6 自动运行时的安全........................................................................................ 6 1.3.7 维修时的安全................................................................................................ 6 1.3.8 点检和维护时的安全.................................................................................... 7

DS2208数字扫描器产品参考指南说明书

-05 Rev. A

6/2018

Rev. B Software Updates Added: - New Feedback email address. - Grid Matrix parameters - Febraban parameter - USB HID POS (formerly known as Microsoft UWP USB) - Product ID (PID) Type - Product ID (PID) Value - ECLevel

-06 Rev. A

10/2018 - Added Grid Matrix sample bar code. - Moved 123Scan chapter.

-07 Rev. A

11/2019

Added: - SITA and ARINC parameters. - IBM-485 Specification Version.

No part of this publication may be reproduced or used in any form, or by any electrical or mechanical means, without permission in writing from Zebra. This includes electronic or mechanical means, such as photocopying, recording, or information storage and retrieval systems. The material in this manual is subject to change without notice.

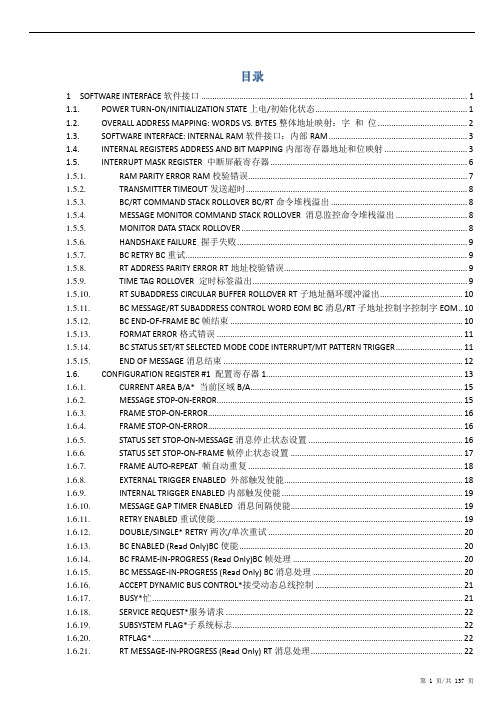

BU_61580寄存器说明中文版

目录

1 SOFTWARE INTERFACE 软件接口 ....................................................................................................................... 1 1.1. POWER TURN-ON/INITIALIZATION STATE 上电/初始化状态 .................................................................... 1 1.2. OVERALL ADDRESS MAPPING: WORDS VS. BYTES 整体地址映射:字 和 位 ........................................ 2 1.3. SOFTWARE INTERFACE: INTERNAL RAM 软件接口:内部 RAM .............................................................. 3 1.4. INTERNAL REGISTERS ADDRESS AND BIT MAPPING 内部寄存器地址和位映射 ..................................... 3 1.5. INTERRUPT MASK REGISTER 中断屏蔽寄存器 ........................................................................................ 6 1.5.1. RAM PARITY ERROR RAM 校验错误..................................

泰尔德尼科阿克双极遥控开关参考指南说明书

Page 16SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE© 2016 Teledyne Coax SwitchesThis guide shows the model numbers for switches by Teledyne Coax Switches. For technical support or custom switches for speci fi c applications, call (800) 351-7368.Example: CCR-33S10-T (Commercial SPDT, S=SMA, 28 Vdc, Failsafe, TTL)All standard switches are RoHS compliant. Contact factory for other options.XXX-XX X X X X - X X X X - X①①OnlySee tables on pages 2–7 for series name.D 7/16 DIN Female K 2.92 mm Female M Mini SMBN N FemaleS SMA Female T TNC FemaleHN High Power Type N FemaleHT High Power TNC Female1 28 Vdc – Failsafe (Normally Open if single-pole multi-throw)2 15 Vdc – Failsafe (Normally Open if single-pole multi-throw)3 12 Vdc – Failsafe (Normally Open if single-pole multi-throw)424 Vdc – Failsafe (Normally Open if single-pole multi-throw)6 28 Vdc – Latching*7 15 Vdc – Latching*8 12 Vdc – Latching*924 Vdc – Latching*3, 4, 5, 6, 7, 8, 9, 0=10 Indicates number of positions on multi-throw switches (skip this number if not single-pole multi-throw)0 No self-cutoff or indicator contacts CIndicator contacts onlyD Self cutoff onlyESelf cutoff and indicator contactsTTTL driver with diodesTD Decoders and TTL driver with diodesRPositive (+) Common. Option not available with T and TD options.NNarrow Body (SPDT switch only)M Moisture SealDCoil Transient Suppression Diode & Polarity Protection DiodeS Sub-D ConnectorAssigned by Engineering*Polarity sensitive Note: Normally Open terminated switches are polarity sensitiveSpace-quali fi ed and custom switches available. Please contact factory for more information.②②③③④⑤⑤⑥⑥⑦⑦⑧⑧⑨⑨⑩⑩。

布林强盗python逻辑

布林强盗python逻辑在Python 中实现布林强盗算法,主要步骤包括定义状态,初始化参数,然后实现模拟运行。

以下是代码示例:Pythonimport random# 定义状态class State:def __init__(self, gold, bandit):self.gold = goldself.bandit = bandit# 初始化参数num_episodes = 10000num_bandits = 10num_actions = 2reward_range = [0, 1]# 初始化强盗状态state = State(0, [random.uniform(reward_range[0], reward_range[1]) for _ in range(num_bandits)])# 模拟运行for episode in range(num_episodes):# 选择行动action = random.randint(0, num_actions - 1)# 获取奖励reward = state.bandit[action]# 更新状态new_state = State(state.gold + reward, [reward if i == action else state.bandit[i] for i in range(num_bandits)])# 打印状态和行动print(f"State: {state}, Action: {action}, Reward: {reward}, New State: {new_state}")state = new_state # 更新状态为新的状态这个代码实现了一个简单的布林强盗算法,模拟了强盗选择一个bandit(强盗的藏匿点)并获得奖励的过程。

在每个episode(一轮),强盗随机选择一个bandit,然后获得该bandit 的奖励,并更新其状态。

堆叠自动编码器的训练方法详解(九)

堆叠自动编码器的训练方法详解自动编码器是一种无监督学习算法,它可以学习数据的有效表示,同时也可以用于特征提取和降维。

堆叠自动编码器(Stacked Autoencoder)是由多个自动编码器组成的深度神经网络模型,其训练方法相对于单个自动编码器更加复杂。

本文将对堆叠自动编码器的训练方法进行详细解析。

第一部分:单个自动编码器的训练在训练堆叠自动编码器之前,首先需要训练单个自动编码器。

自动编码器由编码器和解码器两部分组成,编码器将输入数据映射到隐藏层,解码器将隐藏层的表示映射回输入空间。

训练自动编码器的目标是最小化重构误差,即输入数据与解码器输出的差异。

常用的训练方法包括梯度下降和反向传播算法。

通过反向传播算法,可以计算出相对于重构误差的梯度,然后使用梯度下降算法更新自动编码器的参数。

在训练过程中,可以使用批量梯度下降或随机梯度下降来加速收敛。

第二部分:堆叠自动编码器的训练堆叠自动编码器由多个自动编码器组成,它的训练方法可以分为逐层训练和端到端训练两种方式。

逐层训练是指先训练每个单独的自动编码器,然后将它们堆叠在一起形成深度神经网络。

在逐层训练中,每个自动编码器的输入是上一层自动编码器的隐藏层表示。

通过逐层训练,可以逐步提高整个模型的性能,并且可以避免深度神经网络训练中的梯度消失和梯度爆炸问题。

端到端训练是指直接对堆叠自动编码器进行整体训练,而不是分阶段训练每个单独的自动编码器。

端到端训练可以更好地利用数据的信息,但是训练复杂度更高,需要更多的计算资源和更长的训练时间。

第三部分:正则化和优化在训练堆叠自动编码器时,为了提高模型的泛化能力和避免过拟合,可以采用正则化技术和优化算法。

正则化技术包括L1正则化和L2正则化,它们可以通过惩罚模型复杂度来减少过拟合。

此外,还可以使用dropout技术来随机丢弃隐藏层的部分神经元,以降低模型的复杂度。

优化算法是指在训练过程中寻找最优参数的方法。

除了传统的梯度下降算法,还可以使用动量法、自适应学习率算法等更高级的优化算法来加速训练过程。

悍马汽车部件维修指南说明书

Cutoff Indicator Works........... 49

How Your Front Airbags Work.......................................... 46

CONTINUED

I

v w

Main Menu

Index

Bulb Replacement Back-up Lights ........................... 206 Stop Light ................................... 206 Cargo Area Light ....................... 211 Front Parking Lights................. 205 Front Side Marker Lights......... 204 Headlights .................................. 202 High-mount Brake Light .......... 207 Interior Lights............................ 210 License Plate Lights.................. 209 Side Marker Lights ................... 204 Side Turn Signal Lights ............ 208 Specifications ............................. 251 Turn Signal Lights..................... 203

UVM1.1应用指南及源代码分析_20111211版

6.2. 强大的config .............................................................................................94

6.3. 聚合config变量 .........................................................................................98

写这本书,只是想把自己会的一点东西完全的落于纸上。在努力学习 UVM 的 过程中,自己花费了很多时间和精力。我只想把学习的心得记录下来,希望能够给 后来的人以启发。如果这本书能够给一个人带来一点点的帮助,那么我的努力就不 算是白费。

这本书的前半部分(第 1 到第 9 章)介绍了 UVM 的使用,其用户群较为广泛;

8.2. 搭建一个简单的register model...............................................................129

8.3. 复杂的register model...............................................................................137

函数索引609xvi图目录图11uvm在数字电路设计中的位置3图12uvm对systemverilog的封装4图13简单验证平台5图14uvm验证平台的树形结构6图15实际验证平台7图16packbytes和unpackbytes14图17uvm验证平台中的agent181图21完整的uvm树35图22uvm中常用类的继承关系37图31uvm中的常用phase47图32uvm中所有的phase50图33两个driver位于同一domain57图34两个driver位于不同的domain58图41穿梭的transaction60图51defaultsequence的设置与启动77图52sequencer与driver之间的通信80图53virtualsequence的使用85图61半全局变量93图71monitor与scoreboard的通信104图72使用public成员变量实现通信105图73put操作106图74get操作106xvii图75transport操作107图76component在端口通信中的作用109图77connect关系的建立110图78port与imp的连接111图79portexport与imp的连接115图710使用fifo连接component122图81uvmregfield和uvmreg126图82使用registermodel读取寄存器的流程128图83uvmregfield

自注意力机制多维数据预测 python代码

以下是一个简单的示例,演示了如何使用自注意力机制对多维数据进行预测。

这个示例使用了PyTorch库,并假设数据已经进行了适当的预处理。

python复制代码import torchimport torch.nn as nnimport torch.optim as optimimport numpy as npfrom sklearn.model_selection import train_test_splitfrom sklearn.preprocessing import MinMaxScaler# 加载数据data = np.random.rand(1000, 5) # 假设有1000个样本,每个样本有5个特征X = data[:, :-1] # 特征y = data[:, -1] # 目标值# 数据预处理scaler = MinMaxScaler()X = scaler.fit_transform(X)y = scaler.transform(y.reshape(-1, 1))# 划分训练集和测试集X_train, X_test, y_train, y_test = train_test_split(X, y, test_size=0.2,random_state=42)# 定义模型class AttentionModel(nn.Module):def__init__(self, input_dim, output_dim):super(AttentionModel, self).__init__()self.input_dim = input_dimself.output_dim = output_dimself.fc1 = nn.Linear(input_dim, 128) # 输入层到隐藏层的线性变换self.attention = nn.Linear(128, output_dim) # 自注意力机制self.fc2 = nn.Linear(output_dim, output_dim) # 隐藏层到输出层的线性变换self.relu = nn.ReLU() # 非线性激活函数self.softmax = nn.Softmax(dim=1) # softmax函数,用于归一化权重self.sigmoid = nn.Sigmoid() # sigmoid函数,用于将权重限制在[0,1]之间def forward(self, x):x = self.fc1(x)x = self.relu(x)x = self.attention(x)x = self.softmax(x) # 对权重进行softmax归一化处理x = torch.mm(x, x) # 对每一行元素和对应的列元素进行点积运算,得到自注意力权重矩阵x = self.fc2(x)x = self.sigmoid(x) # 将输出限制在[0,1]之间return xmodel = AttentionModel(X_train.shape[1], 1) # 输入维度为特征数,输出维度为1(因为我们只预测一个值)criterion = nn.MSELoss() # 均方误差损失函数optimizer = optim.Adam(model.parameters(), lr=0.001) # Adam优化器,学习率为0.001# 训练模型for epoch in range(100): # 训练100轮model.train() # 设置模型为训练模式optimizer.zero_grad() # 清空梯度缓存y_pred = model(X_train) # 前向传播,计算预测值loss = criterion(y_pred, y_train) # 计算损失值loss.backward() # 反向传播,计算梯度值optimizer.step() # 更新权重参数,进行一次参数更新操作print('Epoch [{}/{}], Loss: {:.4f}'.format(epoch+1, 100, loss.item())) # 打印训练过程中的损失值,每个epoch输出一次请注意,这是一个简单的示例,实际应用中可能需要进行更复杂的模型设计和调参。

堆叠自动编码器的训练方法详解

堆叠自动编码器的训练方法详解自动编码器(Autoencoder)是一种无监督学习的神经网络模型,其主要目的是学习数据的表示,通常应用于数据降维、特征提取和生成模型等领域。

堆叠自动编码器(Stacked Autoencoder)是由多个自动编码器堆叠而成的深度学习模型,具有更强大的表达能力和特征学习能力。

在本文中,我们将详细介绍堆叠自动编码器的训练方法,并探讨其在实际应用中的一些技巧和注意事项。

一、单层自动编码器的训练在介绍堆叠自动编码器的训练方法之前,首先需要了解单层自动编码器的训练过程。

单层自动编码器由输入层、隐藏层和输出层组成,其中隐藏层的节点数通常少于输入层和输出层的节点数,因此起到了数据降维的作用。

其训练过程通常包括以下几个步骤:1. 数据准备:首先需要准备训练数据集,通常是一个包含大量样本的数据集。

在训练过程中,输入数据会被送入自动编码器的输入层,然后通过隐藏层得到一种数据的表示,最终通过输出层还原到原始的输入数据。

2. 前向传播:在训练过程中,输入数据会通过前向传播的方式传递到隐藏层,然后再通过输出层还原到原始数据。

在这个过程中,需要通过激活函数和权重参数来计算隐藏层的表示和输出层的重构数据。

3. 反向传播:在前向传播之后,需要通过反向传播的方式来更新自动编码器的参数,主要是通过计算损失函数和梯度下降的方式来不断调整权重参数,使得重构数据和原始数据的差距最小化。

4. 参数更新:通过反向传播得到的梯度信息,可以使用各种优化算法来更新自动编码器的参数,比如常用的梯度下降、Adam等算法。

二、堆叠自动编码器的训练堆叠自动编码器是由多个单层自动编码器堆叠而成的深度学习模型,其训练方法相对复杂一些。

在堆叠自动编码器的训练中,通常可以分为以下几个步骤:1. 逐层训练:在堆叠自动编码器的训练中,通常会采用逐层训练的方式来训练每一层的自动编码器。

首先训练第一层的自动编码器,然后将第一层的隐藏层输出作为下一层自动编码器的输入,依次类推。

堆叠自动编码器的预训练策略

堆叠自动编码器的预训练策略随着深度学习技术的不断发展,堆叠自动编码器(stacked autoencoder)作为一种无监督学习方法,在图像识别、自然语言处理等领域取得了显著的成果。

而堆叠自动编码器的预训练策略,更是其成功的关键之一。

本文将探讨堆叠自动编码器的预训练策略,并分析其在深度学习中的作用。

首先,我们需要了解什么是自动编码器。

自动编码器是一种能够学习数据的压缩表示,并且能够通过这个压缩表示进行重构原始数据的神经网络模型。

简单来说,自动编码器可以将输入的数据进行编码,然后再解码还原。

而堆叠自动编码器则是由多个自动编码器层堆叠而成的深层网络结构。

堆叠自动编码器的预训练策略指的是,在进行监督学习任务之前,先利用无监督学习的方式对每一层的自动编码器进行预训练。

这种策略的背后逻辑是,通过逐层地对网络进行预训练,可以使得网络的权重参数逐渐收敛到较好的值,从而提高整个网络的泛化能力和训练速度。

在进行预训练时,通常会使用一种称为贪婪逐层训练(greedy layer-wise training)的方法。

该方法的基本思路是,先训练网络的第一层自动编码器,然后将第一层自动编码器的隐藏层输出作为第二层自动编码器的输入,依次类推,直到所有层的自动编码器都被训练完成。

这样可以保证每一层自动编码器在训练时都能够接收到较好的输入数据,从而提高整个网络的性能。

堆叠自动编码器的预训练策略具有以下几个优势。

首先,通过逐层地进行预训练,可以避免深层网络陷入局部最优解的问题。

因为每一层的预训练都是在前一层的基础上进行的,所以可以更好地引导网络在训练过程中找到全局最优解。

其次,预训练可以提高网络的泛化能力,使得网络对未见过的数据具有更好的适应能力。

这是因为预训练可以有效地学习到数据的潜在表示,从而使得网络能够更好地对数据进行编码和解码。

最后,预训练可以加快网络的训练速度,因为通过逐层地进行预训练可以使得网络的初始权重参数更加接近最优解,从而减少了网络在监督学习阶段的训练时间。

让proe自动搜索不同文件夹中的零件,组件再生失败问题解决方法

让proe自动搜索不同文件夹中的零件,组件再生失败问题解决方

法

1、在磁盘任意位置建立一个文本文件,重命名为“search.pro”;

2、相同位置新建一个文本文件,重命名为“search.bat”,用记事本打开输入内容为:

@echo off

copy /y nul search.pro dir \D:\\Program Files\\PRO-E-START\for /f \ echo.search_path \)

(红色字体为你的工作目录,也就是你经常在此目录下保存零件和装配图的总目录)3、运行search.bat文件,会在search.pro文件中自动写入你工作目录中的所有文件夹(包含子文件夹)的路径,此路径可被pro/e识别。

下面一步就是如何让pro/e识别。

4、打开pro/e-工具-选项,在弹出窗口的左下角输入search_path_file,点击“查找”,

弹出对话框,在“设置值”中填写刚刚生成的“search.pro”文件的路径,

如:“D:\\search.pro\

5、点击”添加/更改“按钮,点确定按钮,重启pro/e.

完成之后你会发现,你的组件不会再扫描失败了,如果在工作目录新增加了文件夹,运行search.bat文件即可。

感谢您的阅读,祝您生活愉快。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。