【SPI】LPC1700系列Cortex-M3_ZLG1

【SPI】LPC1700系列Cortex-M3_ZLG

同步串行外设接口(SPI) LPC1700系列Cortex-M3微控制器SPI 简介与特性1SPI 基本操作2SPI 寄存器结构3SPI 操作流程与示例4SPI 使用注意事项5SPI 是一种同步串行外设接口,允许MCU 与外围设备以串行方式通信。

SPI 控制器使LPC1700系列Cortex-M3能与众多外设通信,从而大大增强了处理器的外设扩展能力。

MOSIMISO SCKSSEL LPC1700SCK :用于同步SPI 接口间数据传输的时钟信号MOSI :单向信号线,数据通过它由主机传输到从机SSEL :指示被选择参与数据传输的从机(低电平有效)MISO :单向信号线,数据通过它由从机传输到主机从机选择串行时钟主机输入从机输出主机输出从机输入SPI 总线可以连接一个主机和多个从机同一时刻只允许主机和一个从机进行通信SPI 总线通信是全双工的SPI 总线从机从机从机从机从机从机LPC1700(主机)SPI 简介与特性1SPI 基本操作2SPI 寄存器结构SPI 操作流程与示例SPI 使用注意事项SPI初始化●时钟极性控制位——CPOL该位决定了SPI总线空闲时,SCK时钟线的电平状态。

CPOL=0,当SPI总线空闲时,SCK时钟线为低电平;CPOL=1,当SPI总线空闲时,SCK时钟线为高电平。

●时钟相位控制位——CPHA该位决定了SPI总线上数据的采样位置。

CPHA=0,SPI总线在时钟线的第1个跳变沿采样数据;CPHA=1,SPI总线在时钟线的第2个跳变沿采样数据。

10SCKMOSI模式一:SCK 空闲时为低,SCK 前沿采样采样结果为:10101010b总线空闲时,SCK 为低电平CPOL=0CPHA=011SCKMOSI模式二:SCK 空闲时为低,SCK 后沿采样采样结果为:01010101b总线空闲时,SCK 为低电平CPOL=0CPHA=11010101SCKMOSI模式三:SCK 空闲时为高,SCK 前沿采样采样结果为:10101010b总线空闲时,SCK 为高电平从SCK 的前沿开始采样CPOL=1CPHA=001010101SCKMOSI模式四:SCK 空闲时为高,SCK 后沿采样采样结果为:01010101b从SCK 的前沿开始采样总线空闲时,SCK 为高电平CPOL=1CPHA=1帧长度:可以设置成8~16位帧格式:设置高位先发送还是低位先发送配置帧长度为8,低位先发送,情形如下所示:1 2 3 4 5 6 7 8帧长度帧格式帧长度为8低位在前P0.0SCKMOSISPI 主机MOSISCKSSELSPI 从机DATA需发送的数据数据编码后发送主机提供时钟DATA从机选择释放从机数据传输完成P0.0SCKMISOSPI 主机MISOSCKSSELSPI 从机需发送的数据DATA从机选择释放从机数据传输完成DATASPI简介与特性SPI基本操作3SPI寄存器结构SPI操作流程与示例SPI使用注意事项数据寄存器(S0SPDR)数据移位寄存器收发模块时钟计数寄存器(S0SPCCR)F PCLK控制寄存器(S0SPCR )中断标志寄存器(S0SPINT) 状态寄存器(S0SPSR)F PCLK 经分频后为收发模块提供时钟信号SPI 初始化配置反映收发模块的状态信息反映传输完成的中断信息SPI 控制器的核心SPI 传输完成发生模式错误Bit4:MODF Bit7:SPIF SPI 中断标志寄存器SPINT[0]置位SPI 控制寄存器SPI 状态寄存器SPI简介与特性SPI基本操作4SPI操作流程与示例SPI使用注意事项void SPIMasterInit (uint8 fdiv){S0SPCR = (1 << 5) |(0 << 7) |(0 << 2) |(0 << 6) |(1 << 4) |(0 << 3); if (fdiv < 8) {fdiv = 8;}S0SPCCR = fdiv & 0xfe; }void SPISlaveInit (void){S0SPCR = (0 << 5) | (0 << 7) |(0 << 2) |(0 << 6) |(1 << 4) |(0 << 3);}主机模式/从机模式不使用中断帧长度为8位先发送高位时钟极性为1时钟相位为0设置时钟频率uint8 MSendData (uint8 ucdata){IO0CLR |= SPI_CS;S0SPDR = ucdata;while ((S0SPSR & 0x80) == 0);IO0SET |= SPI_CS;return (S0SPDR);}void SSendData (uint8 ucdata){S0SPDR = ucdata ;while ((S0SPSR & 0x80) == 0);}选中从机发送数据等待数据发送完成释放从机返回接收到的数据发送数据等待数据发送完成SPI 简介与特性SPI 基本操作SPI 寄存器结构SPI 操作流程与示例4SPI 使用注意事项5⏹连接时,MOSI、MISO不能交叉连接;⏹使用时注意主机和从机的模式设置匹配;⏹SPI主机提供总线时钟;⏹作为主机使用时,SSEL引脚可以作为I/O口使用;指定作为SSEL功能后,则必须无效。

01-第一章Cortex-M3处理器简介 共25页

1.2 Cortex-M3 处理器基本结构

• 处理器核Cortex-M3 • NVIC • Bus Matrix • FPB(Flash Patch and Breakpoint) • DWT • ITM • MPU • ETM • TPIU • SW/SWJ-DP

Cortex-M3核的主要特点

1.3.3 STM32 系列MCU 的优点

• 性能出众而且功能创新的片上外设:STM32 处理 器片上外围的优势来源于双APB 总线结构,其中 有一个高速 APB(速度可达CPU 的运行频率), 连接到该总线上的外设能以更高的速度运行。针 对 MCU 应用中最常见的电机控制,STM32 对片 上外围设备进行一些功能创新。

• 6 个可独立配置的指令比较器,用于转换从 代码空间到系统空间的指令预取,或执行 硬件断点;

• 2 个常量比较器用于转换从代码空间到系统 空间的常量访问。

数据观测与跟踪单元(Data Watchpoint and Trace、DWT)

• DWT 有 4 个比较器可配置为硬件断点、 ETM 触发器、PC 采样事件触发器或数据 地址采样触发器;

• 高度的集成整合:STM32 处理器最大程度地实现 集成,尽可能地减少对外部器件的要求。

• 易于开发,可使产品快速进入市场。

1.3.4 STM32 处理器开发工具

谢谢!

• 硬件跟踪:DWT 产生信息包,由ITM 向外发送;

• 时间戳:ITM 可产生与所发送信息包相关的时间

戳包,并向外发送。

存储器保护单元(Memory Protection Unit,MPU)

• MPU 提供以下支持: • 存储保护;保护区域重叠; • 访问允许控制;向系统传递存储器属性。

zlg翻译的LPC1700中文手册

zlg翻译的LPC1700中文手册广州周立功单片机发展有限公司第1章第1章概述1.1 简介 LPC1700 系列Cortex-M3 微控制器用于处理要求高度集成和低功耗的嵌入式应用。

ARMCortex-M3 是下一代新生内核,它可提供系统增强型特性,例如现代化调试特性和支持更高级别的块集成。

LPC1700 系列 Cortex-M3 微控制器的操作频率可达 100MHz。

ARM Cortex-M3 CPU 具有 3级流水线和哈佛结构,带独立的本地指令和数据总线以及用于外设的稍微低性能的第三条总线。

ARM Cortex-M3 CPU 还包含一个支持随机跳转的内部预取指单元。

LPC1700 系列 Cortex-M3 微控制器的外设组件包含高达512KB 的 Flash 存储器、64KB 的数据存储器、以太网 MAC、 USB 主机/从机/OTG 接口、通道的通用 DMA 控制器、个 UART、 8 4 2 22 条 CAN 通道、2 个 SSP 控制器、SPI 接口、3 个 I C 接口、2-输入和 2-输出的 I S 接口、8 通道的 12 位 ADC、10 位 DAC、电机控制 PWM、正交编码器接口、4 个通用定时器、6-输出的通用 PWM、带独立电池供电的超低功耗 RTC 和多达 70 个的通用 I/O 管脚。

1.2 特性 ARM Cortex-M3 处理器,可在高至 100MHz 的频率存储器保护单元(MPU) ; ARM Cortex-M3 下运行,并包含一个支持 8 个区的内置了嵌套的向量中断控制器(NVIC) ; 具有在系统编程(ISP)和在应用编程(IAP)功能的 512KB 片上 Flash 程序存储器。

把增强型的 Flash 存储加速器和Flash 存储器在 CPU 本地代码/数据总线上的位置进行整合,则 Flash 可提供高性能的代码; 64KB 片内 SRAM 包括: –32KB SRAM 可供高性能 CPU 通过本2 个 16KB SRAM 模块,带独立访问路径,可进行更高地代码/数据总线访问; –吞量的操作。

第2章 LPC1700系列微控制器硬件体系结构

式中FPLLIN表示锁相环的输入时钟频率,FCCO表示电流 控制振荡器(CCO)的输出频率,N和M分别是分频和倍 频系数。

所有100个引脚可以分为5类: 3. 时钟引脚 时钟引脚主要有两类:一个是主振荡器的时钟引脚:XTA L1和XTAL2;另一个是RTC振荡器的时钟引脚:RTCX1和RTCX2。 还有一个引脚CLKOUT和P1.25复用,可以输出处理器内部的各 种时钟,方便用户调试使用。 4. 仿真引脚 仿真引脚也是分成了三类:一类是常用的JATG接口,使 用TDO、TDI、TMS、TRST、TCK和RTCK这几个引脚;一类是SWD 接口,使用SWO、SWDIO和SWDCLK这三个引脚;一类是跟踪接 口,使用TRACEDA[3]、TRACEDA[2]、TRACEDA[1]、TRACEDA[0] 和TRACECLK这几个引脚。

• CPU时钟配置寄存器(CCLKCFG)

功能: PLL0输出时钟必须要经过分频才能提供给CPU使 用,PLL0输出的分频由CCLKCFG寄存器进行控制。当 PLL0被旁路时,相当于1分频。当PLL0正在运行时, 输出必须经过分频以使CPU时钟频率(CCLK)工作在 限定的范围内。

• CPU时钟配置寄存器(CCLKCFG)

• 系统控制和状态寄存器(SCS)

• 内部RC振荡器

内部RC振荡器(IRC)可用作看门狗定时器的时钟 源,也可以用作驱动PLL0和CPU的时钟源。 如果使用USB功能或者CAN通信模块的通信波特率高 于100Kbit/s时,IRC的精度达不到要求,因使用外部晶 体振荡器作为系统时钟源。

典型MCU架构详解与主流MCU介绍

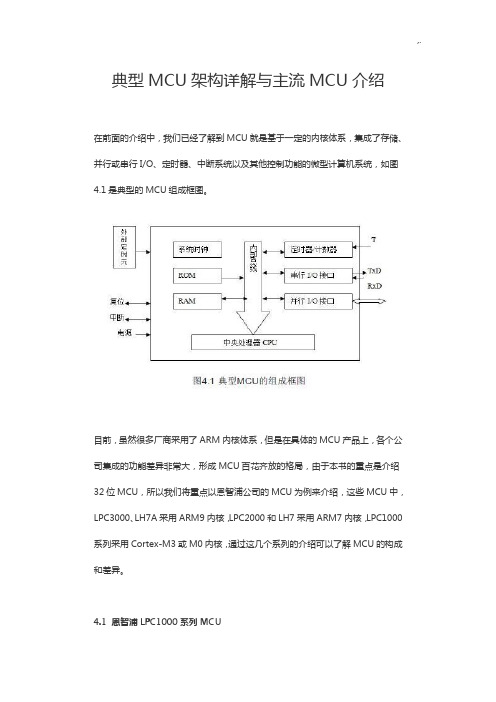

典型MCU架构详解与主流MCU介绍在前面的介绍中,我们已经了解到MCU就是基于一定的内核体系,集成了存储、并行或串行I/O、定时器、中断系统以及其他控制功能的微型计算机系统,如图4.1是典型的MCU组成框图。

目前,虽然很多厂商采用了ARM内核体系,但是在具体的MCU产品上,各个公司集成的功能差异非常大,形成MCU百花齐放的格局,由于本书的重点是介绍32位MCU,所以我们将重点以恩智浦公司的MCU为例来介绍,这些MCU中,LPC3000、LH7A采用ARM9内核,LPC2000和LH7采用ARM7内核,LPC1000系列采用Cortex-M3或M0内核,通过这几个系列的介绍可以了解MCU的构成和差异。

4.1 恩智浦LPC1000系列MCULPC1000系列MCU是以第二代Cortex-M3为内核的微控制器,用于处理要求高度集成和低功耗的嵌入式应用。

采用3级流水线和哈佛结构,其运行速度高达100MHz,带独立的本地指令和数据总线以及用于外设的第三条总线,使得代码执行速度高达1.25MIPS/MHz,并包含一个支持分支预测的内部预取指单元,特别适用于静电设计、照明设备、工业网络、报警系统、白色家电、电机控制等领域。

LPC1000系列MCU又分为LPC1700系列和LPC1300系列,下面我们分开介绍。

4.1.1 LPC1700系列MCU介绍LPC1700系列ARM是以第二代的Cortex-M3为内核,是为嵌入式系统应用而设计的高性能、低功耗的32位微处理器,适用于仪器仪表、工业通讯、电机控制、灯光控制、报警系统等领域。

其操作频率高达100MHz,采用3级流水线和哈佛结构,带独立的本地指令和数据总线以及用于外设的高性能的第三条总线,使得代码执行速度高达1.25MIPS/MHz,并包含一个支持分支预测的内部预取指单元。

LPC1700系列ARM Cortex-M3的外设组件:最高配置包括512KB片内Flash 程序存储器、64KB片内SRAM、8通道GPDMA控制器、4个32位通用定时器、一个8通道12位ADC、一个10位DAC、一路电机控制PWM输出、一个正交编码器接口、6路通用PWM输出、一个看门狗定时器以及一个独立供电的超低功耗RTC。

【GPIO】LPC1700系列

GPIO特性描述|通用输入输出

LPC1700系列Cortex-M3有5组GPIO,多达70个通用I/O 管脚(100管脚封装); 所有GPIO寄存器位于AHB总线上,可以进行高性能的 CPU快速访问,支持Cortex-M3位带操作; 可配置为上拉/下拉电阻、开漏和中继模式; GPIO允许进行DMA数据操作。

设置引脚连接模块

设置下降沿中断 使能GPIO中断 打开全局中断

void GPIO_ISR (void) { if((IO0IntStatF & 0x01) != 0) { 判断是否为P0.0下降沿中断 IO0IntClr = 0x01; 清除中断标志 ...... 用户其它代码 } }

GPIO特性描述|中断

LPC1700系列Cortex-M3的P0和P2还具有中断功能, P0和P2每个引脚都可配置为上升沿、下降沿或边沿中断。

P0.x

LPC1700

P2.x

GPIO中断还具 有掉电唤醒功能

下降沿中断

边沿中断

目

录

1

GPIO简介 GPIO特性描述

2

3 4

GPIO输入输出

GPIO中断

GPIO输入输出|I/O相关寄存器

2

设置下降沿中断使能

清除中断标志

IO0/2IntStatR IOIntStatus

IO0/2IntStatF

GPIO中断|中断操作流程

操作示例——设置P0.0下降沿中断

PINSEL0 &= 0xFFFFFFFC; PINMODE0 &= 0xFFFFFFFC; IO0IntEnF |= 0x01; ISER0 |= (1 << 21); zyIrqEnable();

典型MCU架构详解与主流MCU介绍

v1.0 可编辑可修改典型MCU架构详解与主流MCU介绍在前面的介绍中,我们已经了解到MCU就是基于一定的内核体系,集成了存储、并行或串行I/O、定时器、中断系统以及其他控制功能的微型计算机系统,如图是典型的MCU组成框图。

目前,虽然很多厂商采用了ARM内核体系,但是在具体的MCU产品上,各个公司集成的功能差异非常大,形成MCU百花齐放的格局,由于本书的重点是介绍32位MCU,所以我们将重点以恩智浦公司的MCU为例来介绍,这些MCU中,LPC3000、LH7A采用ARM9内核,LPC2000和LH7采用ARM7内核,LPC1000系列采用Cortex-M3或M0内核,通过这几个系列的介绍可以了解MCU的构成和差异。

恩智浦LPC1000系列MCULPC1000系列MCU是以第二代Cortex-M3为内核的微控制器,用于处理要求高度集成和低功耗的嵌入式应用。

采用3级流水线和哈佛结构,其运行速度高达100MHz,带独立的本地指令和数据总线以及用于外设的第三条总线,使得代码执行速度高达MHz,并包含一个支持分支预测的内部预取指单元,特别适用于静电设计、照明设备、工业网络、报警系统、白色家电、电机控制等领域。

LPC1000系列MCU又分为LPC1700系列和LPC1300系列,下面我们分开介绍。

LPC1700系列MCU介绍LPC1700系列ARM是以第二代的Cortex-M3为内核,是为嵌入式系统应用而设计的高性能、低功耗的32位微处理器,适用于仪器仪表、工业通讯、电机控制、灯光控制、报警系统等领域。

其操作频率高达100MHz,采用3级流水线和哈佛结构,带独立的本地指令和数据总线以及用于外设的高性能的第三条总线,使得代码执行速度高达MHz,并包含一个支持分支预测的内部预取指单元。

LPC1700系列ARM Cortex-M3的外设组件:最高配置包括512KB片内Flash程序存储器、64KB片内SRAM、8通道GPDMA控制器、4个32位通用定时器、一个8通道12位ADC、一个10位DAC、一路电机控制PWM输出、一个正交编码器接口、6路通用PWM输出、一个看门狗定时器以及一个独立供电的超低功耗RTC。

基于Cortex—m3为内核的开发板设计与制作

基于Cortex—m3为内核的开发板设计与制作作者:丁红王怀德来源:《现代电子技术》2012年第18期摘要:为了实现以CortexM3为内核制作一个实验开发板,用于教学、竞赛、工控开发,通过一系列的模拟仿真和研究分析,设计了开发板的电路原理图,分析了以太网的结构、原理、初始化过程,USBOTG的设计思路、电路原理图和初始化过程以及SD卡驱动电路的设计过程,并制作了可实际使用的电路板。

整个开发板主要能够为学生的课程设计、毕业设计、创新活动提供良好平台。

关键词:CortexM3;LPC1768;以太网驱动电路;USBOTG驱动电路;SD卡驱动电路中图分类号:TN91934文献标识码:A文章编号:1004373X(2012)18001903ARMCortexM3处理器是一款具有极高运算能力和中断响应能力的处理器内核,能够实现8位和16位处理器级数的代码存储密度。

该内核体积很小,从而使它的封装更为小型,成本更为低廉,应用更为广泛。

NXP(恩智浦半导体)公司的LPC1700系列ARM是基于CortexM3内核的微控制器,是为嵌入式系统应用而设计的高性能、低功耗的32位微处理器,适用于仪器仪表、工业通信、电机控制、灯光控制、报警系统等领域。

它的操作频率高达120MHz,采用3级流水线和哈佛结构,带独立的本地指令和数据总线,代码执行速度高达1.25MIPS/MHz,同时包含1个支持随机跳转的内部预取指单元[1]。

本文设计了以LPC1768为控制器核心的开发板,完成了以太网、USBOTG、SD卡驱动等控制电路设计及程序驱动设计。

1以太网驱动电路的设计以太网模块包含一个功能齐全的10Mb/s或100Mb/s以太网MAC(媒体访问控制),以太网MAC通过使用DMA硬件加速功能来优化其性能。

以太网模块具有大量的控制寄存器组,可以提供:半双工/全双工操作、流控制、控制帧、重发硬件加速、接收包过滤以及LAN上的唤醒等。

利用分散集中式(ScatterGather)DMA进行自动的帧发送和接收操作,减轻了CPU 的工作量[2]。

NXP_LPC1700 常见问题

广州专卖店

地址:广州市天河区新赛格电子城 203-204 室 电话:(020)87578634 87569917 传真:(020)87578842

南京周立功

地址:南京市珠江路 280 号珠江大厦 1501 室 电话:(025) 68123901 68123902 传真:(025) 68123900

北京周立功

广州周立功单片机科技有限公司

LPC1700 系列微控制器 FAQ

常见问题解答

目录

1. 概述...........................................................................................................................1

销售:

电话:(020)22644249 22644399 22644372 22644261 28872524 28872342 28872349 28872569 28872573 38601786

维修:

电话:(020)22644245

工程技术笔记

©2012 Guangzhou ZLG MCU Technology Co., Ltd. iii

传真:(027)87163755

上海周立功

地址:上海市北京东路 668 号科技京城东座 7E 室 电话:(021)53083452 53083453 53083496 传真:(021)53083491

西安办事处

地址:西安市长安北路 54 号太平洋大厦 1201 室 电话:(029)87881296 83063000 87881295 传真:(029)87880865

2.10 LCD...........................................................................................................................6

【RIT】LPC1700系列Cortex-M3_ZLG

ROCONUMTER 32位计数器

RIMASK 屏蔽寄存器

RIT

RICTRL 控制寄存器 RICOMPVAL 比较寄存器

RIT寄存器

RICTRL 控制寄存器

Bit31~4 保留

RITEN 定时器使能

RITENBR 调试使能

RITENCLR 清零使能

RITINT 中断标志

置1:定时器 使能

置1:调试模式

重复中断定时器(RIT)

LPC1700系列Cortex-M3微控制器

目

录

1

RIT简介 RIT寄存器

2

3

RIT操作

RIT简介

重复中断定时器(RIT)提供了一种在规定的时间间隔产 生中断的方法,不需要使用标准定时器。RIT专用于重复产生 与操作系统中断无关的中断,在需要时也可以用作系统计时器 的备用定时器。

置1:匹配后计 数器清零

置1:清除标志

目

录

1

RIT简介 RIT寄存器

2

3

RIT操作

RIT操作

操作重复中断定时器,初始化为每500ms产生一次中断, 则比较寄存器值计算如下:

FPCLK RICOMPVAL

外设时钟分频

定时时间 =

PLL倍频

12M外部晶振

96M CPU 工作频率

24M外设 总线频率

RICOMPVAL = 24MHz × 0.5s = 12000000

RIT操作

初始化代码:

void ritInit (void) {

PCONP RICTRL = PCONP | (1<<16); = RICTRL | (1<<0);

使能功率控制位 清除中断标志 设置比较值

LPC1700讲义(1)

Cortex-M3中断

• 支持1至240个中断向量 • 最多支持256个中断优先级设置,并且是可 以动态修改的 • Cortex用NMI(不可屏蔽中断)替代了 ARM7TDMI的FIQ(快速中断请求)。除非 系统彻底锁定,否则NMI会在收到请求的第 一时间予以相应

中断延时

• 12周期的中断延时。 6周期用来寄存器压栈,6周期用来取址 • 抢占 当一个中断被响应,中断服务程序正在运 行时,如果产生一个比当前中断优先级更 高的中断,那么就会打断当前中断服务程 序,进入新的中断,产生中断嵌套

LPC1700介绍

• 第二版本的Cortex-M3 core,包括第一版所 有的功能;修正了第一版已知的错误; 120MHz工作频率; Wake-Up中断控制器 • 最大64KB的RAM • 最大512KB的Flash • 支持Flash加速 • 片上集成网卡,USB,CAN

LPC1700介绍

• Full-Speed USB2.0(Host/Device/On-TheGo) • 支持内存保护单元(MPU) • 支持嵌入式跟踪单元 (ETM) • 1uA超低功耗的支持日历功能的实时时钟 • 完整的Debug调试/跟踪

STRONG TECH.

LPC1700 Cortex Microcontrollers

MAX

介绍内容

• Cortex-M3介绍 • NXP LPC1700 Cortex-M3特点

Cortex-M3介绍

• • • • • • 哈弗结构,数据总线与控制总线分离 带有分支预测的3级流水线 采用Thumb-2®指令集 支持硬件除法器和单周期乘法的运算单元 带有唤醒中断控制器的可嵌套中断控制器 遇中断自动保存存储系统状态(保护现 场)

I2 C

【I2S】LPC1700系列Cortex-M3_ZLG1

2

存储器/ 其他外设

DMA控制器

I2S发送/接 收FIFO

void i2sDmaSndInit (void) { PCONP |= 1 << 29; DMACIntTCClear |= 0x03; DMACC1LLI = 0; DMACC1Config |= (0x01 << 11) | (0x05 << 6); DMACC1Control |= (0x04 << 12) | (0x04 << 15) | (0x02 << 18) | (0x02 << 21); DMACC1Control |= 0x80000000; //接下页代码

目

录

1 2 3 4

I2S简介 I2S工作原理 I2S基本操作 I2S之DMA

I S之DMA 之

DMA( Direct Memory Access )——直接存储器访问。在DMA模式下, CPU只须向DMA控制器下达指令,让DMA控制器来处理数据的传送,数据传送 完毕再把信息反馈给CPU,这样就很大程度上减轻了 减轻了CPU资源占有率,可以大 资源占有率, 减轻了 资源占有率 大提高系统效率 。

I S基本操作 基本操作

LPC1700系列Cortex-M3微控制器的I2S基本操作可分为以下五个步骤:

设置I/O连接到I2S 设置主时钟频率

2

设置位速率 设置I2S工作模式 发送或接收数据

设置主时钟频率

发送/接收主时钟速率TX_MCLK/RX_MCLK利用小数波特率发生器 把PCLK经过分频得来。

LPC1700系列Cortex-M3微控制器I2S支持采样频率范围为16KHz~96KHz

lpc1766技术参数

YL-LPC1766开发板介绍芯片资源LPC1700系列芯片使用高性能的ARM® Cortex™-M3 32位的RISC内核,工作频率为100 MHz。

它内置高速存储器(高达512K字节的闪存和64K字节的SRAM),丰富的增强I/O端口和联接到两条APB总线的外设。

该板包含8通道12位的ADC和10位的DAC、4个通用16位定时器、电机控制PWM接口以及多个标准和先进的通信接口:多达3个I2C、SPI、2个I2S、1个SDIO、4个USART、一个USB Host/Device/OTG接口和两个CAN、Ethernet MIC接口LPC1700系列工作于-40°C至+105°C的温度范围,供电电压为2.0V至3.6V。

它的一系列省电模式突显出了它的低功耗的特点。

YL_LPC17XX开发板硬件资源YL-LPC17xx是优龙公司新推出的一款基于NXP公司(恩智浦半导体)LPC1700系列处理器(Cortex-M3 内核V2版)的全功能评估板,主频高达100MHZ。

该评估板含有Ethernet 接口,USB HOST/Device/OTG接口,2个CAN接口和UART接口,SPI液晶屏接口(保留16bit总线接口)主要应用于网络设备,汽车电子,医疗电子,工业控制等方面。

丰富的例程和资源可以帮助您快速的进行项目开发和个人学习。

处理器:LPC1766,主频:100MHz◆256KB FLASH Memory(片内)◆ 64KB SRAM(片内)◆ USB供电/9~12V直流电源供电◆ USB OTG接口◆ USB Device/Host接口◆ RTC( 带后备电池)◆ 10/100M Ethernet 接口◆2路CAN接口◆1路AD转换电位器◆1个3线RS232串行口◆1个9线RS232串行口◆ 2X2矩阵键盘◆2个Led灯◆ 70个I/OPin 用户扩展接口◆1个SD存储卡接口◆ 38Pin TFT- LCD屏接口(支持240*320TFT屏 + 四线触摸)◆ 20Pin JTAG调试接口◆ DAC SpeakerYL_LPC17XX开发板软件资源◆ 触摸屏测试实验例程◆ uC/GUI实验例程◆ GPIO的控制实验,LED(发光二极管)、KEY(按键)等◆ 中断向量配置实验例程NVIC◆ EXTI芯片中断实验调用配置例程◆ ADC模数转换例程◆ 利用CortexM3位块管理功能来读写SRAM中的变量程序◆ CAN实验◆ SD卡测试例程(带文件系统)◆ DEBUG仿真模拟调试例程◆ DAC Speaker 测试例程◆ Blinky综合测试例程◆ LCD_Blinky 实验例程◆ USB测试例程◆ 串口通讯例程◆ Ethernet 测试例程◆ LCD显示例程YL_LPC1766套件包括1)一块已测试好的YL_LPC1766开发板2)用户光盘3)一条9线交叉串口线(2-3交叉)4)一条USB线5)一条交叉网口线6)9V/12V直流电源7)一个精美包装盒关于售后服务及技术支持感谢您选用此开发板,我们对此板保修一年(CPU及中央元件烧损除外)技术支持方式:BBS 论坛支持,时间不限,响应时间是一个工作日。

典型MCU架构详解与主流MCU介绍

典型MCU架构详解与主流MCU介绍在前面的介绍中,我们已经了解到MCU就是基于一定的内核体系,集成了存储、并行或串行I/O、定时器、中断系统以及其他控制功能的微型计算机系统,如图4.1是典型的MCU组成框图。

目前,虽然很多厂商采用了ARM内核体系,但是在具体的MCU产品上,各个公司集成的功能差异非常大,形成MCU百花齐放的格局,由于本书的重点是介绍32位MCU,所以我们将重点以恩智浦公司的MCU为例来介绍,这些MCU中,LPC3000、LH7A采用ARM9内核,LPC2000和LH7采用ARM7内核,LPC1000系列采用Cortex-M3或M0内核,通过这几个系列的介绍可以了解MCU的构成和差异。

4.1 恩智浦LPC1000系列MCULPC1000系列MCU是以第二代Cortex-M3为内核的微控制器,用于处理要求高度集成和低功耗的嵌入式应用。

采用3级流水线和哈佛结构,其运行速度高达100MHz,带独立的本地指令和数据总线以及用于外设的第三条总线,使得代码执行速度高达1.25MIPS/MHz,并包含一个支持分支预测的内部预取指单元,特别适用于静电设计、照明设备、工业网络、报警系统、白色家电、电机控制等领域。

LPC1000系列MCU又分为LPC1700系列和LPC1300系列,下面我们分开介绍。

4.1.1 LPC1700系列MCU介绍LPC1700系列ARM是以第二代的Cortex-M3为内核,是为嵌入式系统应用而设计的高性能、低功耗的32位微处理器,适用于仪器仪表、工业通讯、电机控制、灯光控制、报警系统等领域。

其操作频率高达100MHz,采用3级流水线和哈佛结构,带独立的本地指令和数据总线以及用于外设的高性能的第三条总线,使得代码执行速度高达1.25MIPS/MHz,并包含一个支持分支预测的内部预取指单元。

LPC1700系列ARM Cortex-M3的外设组件:最高配置包括512KB片内Flash程序存储器、64KB片内SRAM、8通道GPDMA控制器、4个32位通用定时器、一个8通道12位ADC、一个10位DAC、一路电机控制PWM输出、一个正交编码器接口、6路通用PWM 输出、一个看门狗定时器以及一个独立供电的超低功耗RTC。

ARM处理器架构进化史

ARM处理器架构进化史随着NXP 发布LPC1700 系列Cortex-M3 内核的MCU,围绕着ARM 新宠Cortex 内核的竞争已经进入白热化。

目前Cortex-M3 处理器内核的授权客户数已达到28 家,包括东芝、ST、Ember、Accent、Actel、ENERGY、ADI、NXP、TI、Atmel、Broadcom、Samsung、Zilog 和Renesas,其中ST、TI、NXP、Atmel 和东芝已经推出基于Cortex-M3 的MCU 产品。

在这5 家中,通过收购Luminary 入局的TI 和ST 属于最先吃螃蟹的人,到现在已经成果初现;NXP 则凭借最新的V2 版内核100MHz 主频的LPC1700 系列大有后来居上之势;至于ATMEL 和TOSHIBA,虽然芯片还没有正式发布推广,但其中原逐鹿的野心也是路人皆知。

可以预见的是,在Cortex-M3 战场,山雨欲来风满楼的现在一定会迎来一个天翻地覆慨而慷的不远将来,而在满城尽戴黄金甲之后,到底谁能够会当临绝顶,一览众山小值得期待。

为什么一向自视甚高坚持玩自己内核的日系厂商也要迫不及待加入ARM 的阵营?为什么一向稳健的ST 宁可用还不太成熟的、不能完全发挥Cortex 威力的V1 版本内核也要迅速把产品推向市场并且投重金在技术支持平台上?为什么多年以来对MCU 领域蜻蜓点水鲜有做为的TI 突然收购Luminary,以横刀立马之势杀入群雄割据的微控制器市场?为什么从ARM7、ARM9、ARM11 一路走来都被批评技术保守不思进取的ARM,在Cortex 面市之后开始放出MCU 架构市场最终只会留下ARM 和Intel 两家的豪言?从图1 的ARM 处理器架构进化史上,我们看到了Cortex 是升级换代产品的含义,但是Cortex-M3 的革命性和超强吸引力,应该是隐藏在以下的一些。

【I2C】LPC1700系列Cortex-M3_ZLG

USB基础知识 基础知识

USB 的四点疑问: 的四点疑问:

1

USB设备插入检测机制

2

USB的描述符及枚举过程

USB基础知识 USB 的描述符 基础知识| 基础知识

一个USB设备通常都包含有设备、配置、接口、端点四个组成部 分。这四个部分是通过描述符来实现各自的功能。

设 备 设备

设备是指一个客观存在 的实体,通过设备描述符说 明USB设备的总体信息。如: USB音频设备。 一个USB设备,仅有一 个设备描述符,设备描述符 决定该设备有多少种配置。

硬件支持主机交换协议( 硬件支持主机交换协议(HNP); ); 完全遵循USB2.0的补充规范 的补充规范:USB 完全遵循 的补充规范 OTG V1.0a; ; 包括HNP和SRP(对话请求协议)所 和 包括 (对话请求协议) 需的可编程的定时器; 需的可编程的定时器; 支持任何遵循OTG收发器规范 收发器规范 支持任何遵循 收发器。 (CEA-2011)V1.0的OTG收发器。 ) 的 收发器

USB音频设备

USB基础知识 USB 的描述符 基础知识| 基础知识

一个USB设备通常都包含有设备、配置、接口、端点四个组成部 分。这四个部分是通过描述符来实现各自的功能。

端 点 设备

端点是USB设备中的实 际物理单元。 USB数据传输就是在主 机和USB设备各个端点之间 进行的。端点描述符定义了 该端点的传输类型。 Usb 设 备 控 制 器

USB主机 主机

D+ DGND

虚线表示连接 之间需阻抗匹BUS V 配 D+

DGND

LPC1700

功能介绍

VBUS:主机向外提供5V电源 ,USB主控制器检 或者D-接了上拉电阻时 当D+或者 接了上拉电阻时 或者 接了上拉电阻 主控制器检 D+ 、D-:差分数据线 : 测有设备插入 GND:地 :

【WDT】LPC1700系列Cortex-M3_ZLG

WDCLKSEL = 0x01;

WDTC

= 0xFF000000;

WDMOD = 0x03;

ISER0

|= (1 << 0);

选择PCLK作为看门狗时钟 设置定时器参数 设置看门狗模式:中断且复位 使能看门狗中断

zyIrqDisable(); WDFEED = 0xAA; WDFEED = 0x55;

二、看门狗定时器原理

其原理是在系统正常工作时,用户程序每隔 一段时间执行喂狗动作,如果系统出错,喂狗间 隔超过看门狗溢出时间,那么看门狗将会产生复 位信号,使微控制器复位。

目录

1

看门狗定时器简介2Βιβλιοθήκη 看门狗定时器结构3

看门狗定时器操作

4

看门狗定时器小结

WDT结构

PCLK IRC RTC

WDTC

定时器常数寄存器

看门狗定时器简介

2

看门狗定时器结构

3

看门狗定时器操作

4

看门狗定时器小结

WDT小结

使用IRC作为时钟源时,看门狗可工作于深度睡眠模式下 错误的或不完整的喂狗序列会令看门狗产生中断/复位 喂狗前建议关闭中断,避免喂狗序列0xAA、0x55不连续 使用看门狗要针对系统本身恰当地设置好溢出时间 根据任务的执行特点,在程序合适的地方喂狗,做到尽量 少占用系统资源,不影响程序执行,又合理适时地喂好看 门狗。

÷4

32位递减计数器

WDTV

WDFEED

当前值寄存器

喂狗寄存器

WDCLKSEL

时钟源选择寄存器

复位

WDMOD

模式寄存器

中断

目录

1

看门狗定时器简介

2

看门狗定时器结构

【UART】LPC1700系列Cortex-M3_ZLG

UART基本操作

UART发送单元 发送单元内部结构

THR

发送移位寄存器

TxFIFO

UnTSR

发 送 单 元

(UnTSR)

发送保持寄存器

(UnTHR)

发送FIFO

UnTHR是发送FIFO的 最高字节。它包含了TX FIFO中的最新字符,可以通 过总线接口对其操作

UART基本操作

UART查询方式发送

uart波特率发生器的时钟源是apb时钟apb时钟经过16分频后将该值保存在除数锁存寄存器dlm与dlluart波特率设置波特率设置那么我们实际所得的波特率是否是精确的9600在公式usfdiv9600中计算结果小数部分被忽略掉实际的波特率为9615uart波特率设置波特率设置启用小数分频后uartn的波特率计算公式为

RS-232特性

最高速率约为20kb/s

传输最大距离约为15m 共模抑制比能力差

PC

RS232 电平 转换

打印机

UART功能应用

RS-485是一种常用远距离和多机通信的串行接口。RS-485只 是定义电压和阻抗,编程方式和普通串口类似,与RS-232主要区别 在于其特性。

RS-485特性

与TTL电平兼容 传输距离实际达1200m 共模抑制比能力强

清除自动波特率相关中断标志 UnACR[8:9]

如果发送的波特率不在这个范围, 则会出现波特率自动超时中断

执行自动波特率中断相关函数 UnIIR[8:9]

UART基本操作

手动波特率配置模式:

波特率设置

UART波特率发生器的时钟源是APB时钟, APB时钟经过16分频后将该值保存在除数锁存寄 存器DLM与DLL

DLM = Dlest[15:8] DLL = Dlest[7:0]

恩智浦半导体推出ARM Cortex-M3微控制器

恩智浦半导体推出ARM Cortex-M3微控制器

佚名

【期刊名称】《电子制作》

【年(卷),期】2008(000)011

【摘要】恩智浦半导体近日推出基于ARMCortexTM-M3处理器的LPC1700系列微控制器。

LPC1700系列微控制器在运行速度高达100MHz时,比目前市场上可供的其他Cortex—M3微控制器产品运行速度更快28%~64%,能够同步操作高带宽通讯周边器件,例如Ethemet、USBOn—The—Go/Host/Device以及CAN。

【总页数】1页(P5)

【正文语种】中文

【中图分类】TP332

【相关文献】

1.恩智浦推出全球首款双电源电压ARMCortex-MO微控制器 [J],

2.恩智浦推出双电源电压ARM Cortex-MO微控制器 [J],

3.恩智浦推出双电源电压ARM Cortex-MO微控制器 [J], 无

4.恩智浦推出32位工业控制系列扩大ARM Cortex-M0微控制器产品组合 [J],

5.恩智浦推出ARM Cortex-M3性能微控制器 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPI初始化 模式介绍 初始化| 初始化

CPOL=0 CPHA=0 模式一:SCK空闲时为低, SCK前沿采样 采样结果为:10101010b 从SCK的前沿 开始采样

总线空闲时, SCK为低电平

SCK

1 MOSI

0

1

0

1

0

1

0

SPI初始化 模式介绍 初始化| 初始化

CPOL=0 CPHA=1 模式二:SCK空闲时为低, SCK后沿采样 采样结果为:01010101b 从SCK的后沿 开始采样

从机选 择 释放从 机

SPI主机

P0.0

SPI从机

SSEL

数据传 输完成

SCK

SCK

需发送 的数据

DATA

MISO MISO

DATA

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

SPI寄存器结构 寄存器结构

FPCLK 时钟计数寄存器 (S0SPCCR) FPCLK经分频后为收 发模块提供时钟信号

选中从机 发送数据 等待数据发送完成 释放从机 返回接收到的数据

void SSendData (uint8 ucdata) { S0SPDR = ucdata; while ((S0SPSR & 0x80) == 0); }

发送数据 等待数据发送完成

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

Bit7:SPIF Bit4:MODF SPI状态寄存器

SPI中断标志寄存器 SPINT[0] 置位

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

SPI操作流程与示例 主机、从机初始化 操作流程与示例|主机、 操作流程与示例

void SPISlaveInit (void) void SPIMasterInit (uint8 fdiv) { { S0SPCR = (0 << 5) | 主机模式/从机模式 主机模式 从机模式 S0SPCR = (1 << 5) | (0 << 7) | 不使用中断 (0 << 7) | (0 << 2) | 帧长度为8位 帧长度为 位 (0 << 2) | (0 << 6) | (0 << 6) | 先发送高位 (1 << 4) | (1 << 4) | 时钟极性为1 时钟极性为 (0 << 3); (0 << 3); 时钟相位为0 时钟相位为 } if (fdiv < 8) { fdiv = 8; 设置时钟频率 } S0SPCCR = fdiv & 0xfe; }

SPI初始化配置 数据寄存器 (S0SPDR) 收发模块 控制寄存器 (S0SPCR) 反映收发模块 的状态信息 状态寄存器 (S0SPSR) 反映传输完成 的中断信息 中断标志寄存器 (S0SPINT) 数据移位寄存器 SPI控制 器的核心

SPI寄存器结构 寄存器结构

SPI控制寄存器

SPI传输完成 发生模式错误

SPI初始化 时钟极性、相位 初始化|时钟极性、 初始化

时钟极性控制位——CPOL

该位决定了SPI总线空闲时,SCK时钟线的电平状态。 CPOL=0,当SPI总线空闲时,SCK时钟线为低电平; CPOL=1,当SPI总线空闲时,SCK时钟线为高电平。

时钟相位控制位——CPHA

该位决定了SPI总线上数据的采样位置。 CPHA=0,SPI总线在时钟线的第1个跳变沿采样数据; CPHA=1,SPI总线在时钟线的第2个跳变沿采样数据。

1 帧长度

2

3

4

5

67Βιβλιοθήκη 8帧长度为8低位在前

帧格式

SPI收发数据 主机发送、从机接收 收发数据|主机发送、 收发数据

从机选 择 释放从 机

SPI主机

主机提 供时钟

P0.0

SPI从机

SSEL

需发送 的数据

SCK

SCK

数据传 输完成

DATA

MOSI MOSI

DATA 数据编码 后发送

SPI收发数据 主机接收、从机发送 收发数据|主机接收、 收发数据

SPI特性 特性

同一时刻只允许主机和一个从机进行通信 SPI总线可以连接一个主机和多个从机 SPI总线通信是全双工的

LPC1700 (主机) 主机)

从机

从机

从机

SPI总线

从机

从机

从机

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

SPI操作流程与示例 数据发送 操作流程与示例| 操作流程与示例

uint8 MSendData (uint8 ucdata) { IO0CLR |= SPI_CS; S0SPDR = ucdata; while ((S0SPSR & 0x80) == 0); IO0SET |= SPI_CS; return (S0SPDR); }

CPOL=1 CPHA=1 模式四:SCK空闲时为高, SCK后沿采样 采样结果为:01010101b 从SCK的前沿 开始采样

总线空闲时, SCK为高电平

SCK

0 MOSI

1

0

1

0

1

0

1

SPI初始化 帧设置 初始化| 初始化

帧长度:可以设置成8~16位 帧格式:设置高位先发送还是低位先发送

配置帧长度为8,低位先发送,情形如下所示:

SPI使用注意事项 使用注意事项

连接时,MOSI、MISO不能交叉连接; 使用时注意主机和从机的模式设置匹配; SPI主机提供总线时钟; 作为主机使用时,SSEL引脚可以作为I/O口使 用;指定作为SSEL功能后,则必须无效。

同步串行外设接口(SPI) 同步串行外设接口

LPC1700系列Cortex-M3微控制器

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

SPI简介 简介

SPI是一种同步串行外设接口,允许MCU与外围设备 以串行方式通信。SPI控制器使LPC1700系列Cortex-M3能 与众多外设通信,从而大大增强了处理器的外设扩展能力。

从机选择 SSEL 串行时钟 SCK

LPC1700

MISO MOSI

主机输入从机输出 主机输出从机输入

SSEL:指示被选择参与数据传输的从机(低电平有效) MISO:单向信号线,数据通过它由从机传输到主机 MOSI:单向信号线,数据通过它由主机传输到从机 SCK:用于同步SPI接口间数据传输的时钟信号

总线空闲时, SCK为低电平

SCK

0 MOSI

1

0

1

0

1

0

1

SPI初始化 模式介绍 初始化| 初始化

CPOL=1 CPHA=0 模式三:SCK空闲时为高, SCK前沿采样 采样结果为:10101010b 从SCK的前沿 开始采样

总线空闲时, SCK为高电平

SCK

1 MOSI

0

1

0

1

0

1

0

SPI初始化 模式介绍 初始化| 初始化