cadence多通道布局总结精要知识点

cadence 学习笔记

1. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。

是什么地方需要设置,哪位大虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

2. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight高亮默认颜色?答:可以在Display->Color/Visibility->Display->Temporary Highlight里修改即可,临时修改颜色可以点Display->Assign Color来实现。

4. 如实现Highlight高亮部分网络,而背景变暗,就像Altium Designer那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer 即可。

5. 快速切换层快捷键答:可以按数字区里的“-”或“+”来换层。

6. OrCAD跟Allegro交互时,出现WARNING [CAP0072] Could not find component to highlight 错误等?答:OrCAD输出网表,Allegro导入网表,确保两者对的上号,然后在Orcad选中元件,再右键Editor Select,即可在Allegro中选中该元件;反过来,在Allegro中要先Highlight某元件,在Orcad中变会选中该元件。

1.ORcad :首先打开orcad和allegro分别占1/2的窗口界面。

然后orcad中Tools/creatnetlist/PCB Editor中Create PCB Editor Netlist下的Options中设置导出网表的路径。

CADENCE PCB设计:布局与布线

号线的放置和布线过程 该约束管理系统是完全集成到PCB 编辑器中 而约束可以随着设计过程的进行而被实时地确认 确认过程的结果是用图形化的方式表示约束条件是否满足 满足约束用绿色显示 不满足约束就用红色显示 这可使设计师可以及时地看到设计的进度 以及因电子数据表中任何设计变动而产生的影响 布图规划与布局约束和规则驱动的方法有利于强大而灵活的布局功能 包括互动和自动的元件布局 工程师或设计师可以在设计输入或布图规划阶段将元件或支电路分配到特定的 区域 可以通过REF 封装方式 相关信号名 零件号码或原理图表/页面号码来过滤或选择元件 当今的电路板上有成千上万种元器件 需要精确的管理 通过实时的器件装配分析和反馈 得以实现器件装配时从整体上来考虑并满足EMS 规则 以提高设计师的设计速度和效率 DFA(可装配型设计)分析 Allegro PCB Design XL 和GXL 有提供 实现了在互动式元件放置时 实时地进图1 Cadence PCB 设计解决方案集成了从简单到复杂PCB 设计所需的所有工具 行DFA 规则检查 基于一个器件类型和封装排列的二维电子表格 DFA 可以实时地检查器件的边到边 边到端或端到端的距离是否违反最小要求 使得PCB 设计师可以同步地放置元器件以实现最优的可布线性 可生产性和信号时序要求 战略规划和设计意图 GRE global rounting environment 由总线互联主导的高度约束 高密度设计可能会花大量时间用于战略性规划和布线 加上当今元件的密度问题 新的信号标准和特定的拓扑结构要求 传统的CAD 工具和技术已经不足以满足捕捉设计师的特定布线意图要求动态铺铜动态铺铜技术提供了实时灌注/修复功能Shape 参数可以被适用于三个不同的方面参数可以被添加到全局shape, 同类shape以及单个shape 中 走线 导孔和元件添加到动态铜皮中 将会按照其形状自动连接或避让 当物体被移去时 形状会自动填充回去 在编辑完成后 动态铺铜不需要批量自动避让 也不需要其它的后期加工步骤RF 设计RF 设计要求包括要比以往更快 更精确地解决高性能/高频率电路 RF/复合信号技术为PCB RF 设计提供了一种完整的 从前端到后端 从原理图到布局到制造的解决方案 RF 技术包含了高级的RF 性能 包括参数化创建和编辑RF 器件的智能布局功能以及一种灵活的图形编辑器 一种双向的IFF 界面提供了RF 电路数据的快速而有效地图3 动态推挤功能让交互式布线非常容易 即便是在最尖端的设计上PCB 制造可以进行全套底片加工 裸板装配和测试输出 包括各种格式的Gerber 274x NC drill 和裸板测试 更重要的是 Cadence 通过其Valor ODB++界面 还包含Valor Universal Viewer 支持业界倡导的Gerber-less 制造 ODB++数据格式可创建精确而可靠的制造数据 进行高质量的Gerber-less 制造 PCB 自动布线器技术自动化的互联环境设计复杂度 密度和高速布线约束的提高使PCB 的手动布线既困难又耗时 复杂的互联布线问题通过强大的 自动化的技术得以解决 这种强大的 经实践证明的自动布线器含有一种批量布线模式 含有众多的用户可定义的布线策略 以及自动的策略调整 互动的布线环境 具有实时互动走线推挤特性 有助于对走线的快速编辑 具有广泛的布图规划功能和完整的元件放置特点的互动式放置环境 使得无需切换应用程序就可以进行放置变更 优化布线 通过使用自动交互式布图规划和放置功能 设计师可以提高布线质量和效率 这与元件布局直接相关 此外 广泛的规则集让设计师可以控制范围广泛的约束 从默认的板级规则到按照线路种类的规则 再到区域规则 Allegro 产品提供的高速布线能力能图4 PCB RF 设计完整的从前端到后端型解决方案图5 高级自动布线技术有效地解决密集型 高约束设计图6 布局编辑器容许你在布线过程的所有阶段评估空间 逻辑流程和拥挤度文档Cadence工具提供了用户向导 前后关联帮助 F1 参考指南 在线教程和多媒体演示等一系列的文档这些文档可以帮助你•通过搜索在线帮助系统寻找你所需要的。

Cadence自学笔记笔记

Cadence⾃学笔记笔记Cadence SPB15.7 快速⼊门视频教程⽬录Capture CIS 原理图及元件库部分第1-15讲第1讲课程介绍,学习⽅法,了解CADENCE软件Cadence下⼏个程序说明Design Entry CIS 系统级原理图设计Design Entry HDL 芯⽚设计Layout plus orcad ⾃带的pcb板布局布线⼯具,功能不是很强⼤,不推荐使⽤Pcb Editor Pcb librarian Cadence带的PCB布局布线封装设计PCB Router pcb⾃动布线Pcb SI SigXplorer Pcb电路板信号完整性仿真OrCAD Capture CIS 对元件管理更⽅便相对于OrCAD CaptureI 放⼤O 缩⼩页⾯属性设置options Design Templateoptions Schematic Page Propertie s第2讲创建⼯程,创建元件库原理图元件库,某元件分成⼏个部分,各部分间浏览ctrl+N ctrl+B元件创建完后修改footprint封装,options Package Properties第3讲分裂元件的制作⽅法1、homogeneous 和heterogeneous 区别homogeneous,芯⽚包含⼏个完全相同的部分选择该模式,画好第⼀个part后,后⾯的part会⾃动⽣成,因为完全⼀样。

但是引脚编号留空了,要⾃⼰再设置引脚编号。

heterogeneous芯⽚包含⼏个功能部分,可按照功能部分分成⼏个部分。

ctrl+N ctrl+B切换分裂元件的各个部分原理图画完之后,要对各元件⾃动编号,在项⽬管理窗⼝选择项⽬,点击tools annotate,在Action下⾯选择相应的动作。

2、创建homogeneous类型元件3、创建heterogeneous类型元件第4讲正确使⽤heterogeneous类型的元件1、可能出现的错误Cannot perform annotation of heterogeneous part J?A(Value RCA_Octal_stack ) part has not been uniquely group(using a common User Property with differing Values) or the device designation has not been chosen2、出现错误的原因分裂元件分成⼏个part,并且⽤了多⽚这样的分裂元件。

Cadnece版图设计技巧总结

Cadence版图设计学习笔记目录Cadence版图设计学习笔记 (1)一、Candence操作 (3)1.进入版图工作环境 (3)2.最常用快捷键 (3)yout环境界面常用操作 (5)二、DESING RULES (6)三、各器件简述 (7)四.版图技巧 (16)1.对敏感线的处理 (16)2.匹配问题的解决 (17)3.噪声问题的处理 (17)4.版图对称性 (18)五、布局布线 (18)六、版图流程 (19)七、ELLA的心得 (20)1.关于电路的问题 (20)2.关于ESD的问题 (20)3.关于滤波电容问题 (22)4.关于天线效应 (23)5.关于电源线和地线问题 (23)6.学会看参考文件 (23)7. 本次流片所画版图 (24)一、Candence操作1.进入版图工作环境1.进入unit :Xmanger1.3..9=》Xbrowser=》EDA4=》用户名=》密码2.界面上右键-》tools-》terminal-》3.在layout目录输入icfb 登陆Candence4.icfb后面加“& ”的作用是之后可以继续在Shell窗口操作命令5.在icfb窗口tools-》library manager-》选择library,cell,view。

6.如果是新建,则FILE-》new里面新建。

7.在icfb窗口的tools-》library path 可以加库2.最常用快捷键f:全景图ctrl+z:放大shift+z:缩小shift+f:详细版图(非symbol)u:undow:上一界面i:调用器件q:看属性r:画矩形p:固定长度的可折线l:lable 标注端口、电源、地等。

所标识的金属层,用该层TEXT层标识。

如,M6层金属则选择M6TEXT层。

s:拉伸收缩Shift+C:把线断开(注意:先选中线,再操作)Shift+M: merge(同上,先选中线)k:标尺shift+k:取消标尺器件旋转:q-》选rotate度数-》Apply对于已选器件:“M“左键右键旋转g:格点鼠标在各格点移动一般不用如果取消,则再按一次“g”shift+x: 进入调用器件的下层shift+b:返回上层F3:在选择了操作命令后,按F3可以显示旋转,宽度调整等被操作器件特性。

Cadence、Allegro学习心得分享

PCB学习心得一、写在前面的话本文将着重介绍一个PCB菜鸟的学习心得,详细的记录每个要点的操作方法和原因,着重将这个过程中学习到的一些东西与大家分享。

同时如发现有任何问题或者是好的方法和建议,请大家指出,共同学习、共同进步!——PCB路漫漫其修远兮,吾将上下而求索接下来将从PCB设计的怎个流程和大家分享二、PCB设计前的准备1.PCB设计之前,请确保原理图的正确性,DRC检测能正常通过,这是必须的a.点击:Tool-->Design Rules Check,如下图所示或者直接点击快捷方式:2具体的每个操作的说明:○1元器件快速排序○2DRC检查(作用同上)○3网表生成○4元器件清单注:元器件生成清单,点击上图中的4,需要在下图位置添加PCB封装属性即可得到元器件清单BOM具体操作为在Header添加tPCB Footprint,在Combined property string添加t{PCB Footprint}2.DRC检测规则按如下规则即可如图的检测规则为默认,如有特殊需求可自行修改!出现最多的“WARNING(ORCAP-1829): Possible pin type conflict ICXX”这个是指CPLD 或者FPGA的IO口方向设置,可以忽略!由于后期可能需求调整IO口的位置,现在操作无意义。

注:1、所选的原理图封装一定要正确,PCB封装同时也应该制作好。

2、原理图的封装应该选择合理,避免在实际的PCB绘制过程中存在问题。

三、DXF文件的导入1.新建一个.brd文件注意:选择Mechanical symbol2.按如下操作File-->Import-->DXF点击Edit后,出现如下的画面,并且按数字的标记操作即可。

3.完成如上两步,点击OK,再点击Import,出现了Dxf文件。

找到板框外形后,点击Edit-->Change,在Options中选择Board Geometry,在子项中选择Outline然后选择一个封闭的外框作为Outline,如下图,然后保存。

cadence 原理图学习笔记

Design Entry CIS :板基设计的原理图设计Design Entry HDL Rules Checker 芯片设计工具Design Entry HDL 芯片设计工具PCB Editor:PCB布局布线的软件PCB Router:自动布线的工具PCB SI:线路板的完整性分析SigXplorer:线路板的完整性分析平时画原理图工具:OrCAD Capture CIS原理图模板设置:创建原理图元件库新建的原理库存储到指定的位置新建元件库元件新建元件的属性,包括名称,索引号,封装,多元件共体,等信息元件库原理图编辑界面单个引脚放置:弹出引脚属性设置阵列引脚放置:单个引脚双击修改属性多个引脚选中后在spreadsheet一起修改。

放置填充多边形按住shift可以画任意角多边形双击调出多边形属性选择实体就好了放置元件方体画方框结束鼠标重复放置命令,右击End Mode 或者Esc元件属性,设置引脚管脚显示等。

元件封装属性修改,原理图与pcb封装的映射就在这里修改。

多元件共体浏览分裂元件浏览。

不规则元件第3讲:分裂元件制作创建Homogereous双运放元件,每个单元件都一摸一样,引脚编号不同,电源脚编号可以重复。

新建元件画好第一个单元件快捷键Ctrl+n 自动生成另一部分单元件。

需要全部重新定义引脚编号。

引脚名称隐藏快捷键Ctrl+b 可以返回查看A部分元件图形。

创建Heterogeneous元件,每部分图形可以不一致。

快捷键Ctrl+n 会完全留空,全部要重新画。

分裂元件整体浏览第4讲分裂元件的自动编号的问题解决。

分裂元件的组定义,在元件库中操作,使同组元件具备同一属性。

第一步:创建元件第二步:给元件创建一个可以区分“分组”的属性完成了单个元件的新属性的创建依次创建同组的其它元件的新属性。

要求同名同参数第三步:在原理图中双击元件使同组的元件都新属性参数相同即可。

配对时不能冲突,比如双运放就只能有两个运放,同一参数有三个运放相同的话就出错了。

cadence学习小结

Cadence学习小结作者:詹书庭一、 cadence和AD的区别1、cadence适合做高端设计,AD(Altium Designer)适合做低端设计,比如51、ARM这些简单的电路板用AD是非常方便的。

2、AD操作简单,上手比cadence更快;cadence功能更强,元件带的属性更多,更适合于复杂设计,其仿真功能也是非常强大的3、做些简单的设计还是推荐大家使用AD,因为AD的PCB库比较齐全,而cadence的封装库大多要自己画,而对于新手来说这个是比较费时和费力的。

还有就是外面的PCB厂商支持AD,也就是不需要自己做光绘文件,而cadence是必须要自己出光绘文件。

二、 cadence15.7和16.5版本的异同1、快捷键不尽相同,不管是在原理图还是在PCB里都有一些快捷键是不一样的,好像在Pspice里是一样的。

2、16.5的仿真(pspice)更强大,自带的例子更多,而15.7几乎没有自己的例子。

这对设计也省事很多。

原理图方面也有些改进,尤其是右键框选可以放大,在个很方便的,在15.7中是没有这个功能的。

PCB方面,已经全部改用allegro设计方式,而15.7的Layout plus可以用于导入AD(protel)PCB文件的导入,而在16.5里面没有这一向,所以16.5的AD向cadence的PCB导入就比较麻烦了。

3、在焊盘设计界面也有所不同,这不是最主要的,我认为最大的改变应该还是在规则方面,16.5全部采用约束管理器,而15.7有一些简便的设置选项,对初学者可能更实用,而16.5则显得更专业,我想这也是软件发展趋势所致。

三、 原理图(1)、新建工程、原理图纸 颜色、格点、放(2)、环境设置:2.1:OptionsPreference大比例、选择方式、文本编辑、版图仿真、杂项设置等 设计模板设置2.2: Options Design Template 自动保存选项设置2.3:Options Autobackup 设置当前工2.4:Options Schematic Page Properties程的纸张尺寸。

cadence技能总结 -回复

cadence技能总结-回复Cadence技能总结Cadence是一款功能强大的电子设计自动化软件套件,广泛应用于集成电路的设计、验证和实现过程中。

作为一个电子工程师,熟练掌握Cadence 技能是非常重要的,它可以帮助我们更高效地完成电路设计和仿真工作。

本文将以“Cadence技能总结”为主题,逐步展开介绍Cadence的使用和技巧,希望能对读者在学习和应用Cadence方面有所帮助。

第一部分:Cadence的基本介绍在本节中,将简要介绍Cadence的基本概念和使用环境。

Cadence是一个综合性的电子设计自动化软件套件,由多个模块组成,包括Schematic Capture、Simulation、Layout、Place & Route等。

它的主要目标是帮助工程师完成从电路设计到物理实现的整个流程。

Cadence通常在Windows或Linux操作系统上运行,并通过图形用户界面(GUI)进行操作。

学习使用Cadence之前,我们需要对其整体框架和基本操作有一个基本的了解。

第二部分:Cadence的Schematic Capture模块Schematic Capture模块是Cadence中最常用的模块之一,它提供了一个图形界面,可帮助工程师绘制原理图。

在本节中,我们将介绍如何使用Schematic Capture模块创建原理图、添加元件和连接电路等基本操作。

同时,还需要了解如何使用Cadence的元件库和设置元件属性等技巧,帮助我们更加高效地绘制电路图。

第三部分:Cadence的Simulation模块Simulation模块是Cadence中用于电路仿真的关键模块,它可以帮助工程师验证设计的功能和性能。

在本节中,我们将介绍如何使用Simulation 模块创建仿真环境、设置仿真参数和运行仿真,以及如何分析仿真结果和对比不同设计方案的优劣等。

同时,还需要了解如何使用Cadence的模拟器和仿真工具库,以及如何调整仿真的时间和准确度等技巧,帮助我们更好地理解和优化电路设计。

Cadence16.5学习笔记之(一)—器件库、原理图

Cadence16.5学习笔记之(一)—器件库、原理图Cadence16.5学习笔记之(一)—器件库、原理图一、简单快捷键R—旋转器件方向(选中时)V—元件的镜像(水平)H—元件的镜像(竖直)F—放置电源G—放置地W—放置连线J—放置节点N—放置网络标号T—放置文本备注(Ctrl + Enter:换行)B—放置总线X—放置电器不连接F4—自动放置线,一直按一直放。

元件的复制:Ctrl + C或按住Ctrl,拖动元件即可。

放置全局网络标号(级联多个原理图):Place—Off-Page Connector放置线、总线时,任意角度走线—按住Shift键,再走线。

二、查找元件、网络连接等对整个工程、或单个的页面进行如下类似操作。

Edit->Browse->Parts:原理图画好了,选中工程,检查、查找定位器件Edit->Browse->Nets:网络连接,对于检查电源连接有帮助Edit->Browse->Off-Page Connector:显示工程中所有,原理图页面之间的网络连接(即归纳显示出所有全局网络标号)Edit->Browse->DRC Markers:DRC检查,显示出DRC电器检查的错误。

(删掉这些错误:Tools->Designe Rules Cheak->Yes->Action->Delete existing DRC marker->Yes)Ctrl + F:搜索定位元件、网络,如在PCB布局、布线时(勾选)。

以下类型选项:Parts:查找元件Nets:查看网络连接Power/GND:查看电源、地的网络连接Flat Nets:查看电源、地的网络连接(功能更强大)三、元件的更新或替换选择工程对话框中的File ->Design Cache->右键->Replace Cach->....->是否保留元件的遗留属性,可以将封装更新过来同样的操作,如果器件库中器件属性有改动,则更新元件(但不能将封装更新过来):File ->Design Cache->右键->Updata Cach四、选中元件1、单个选中、Ctrl + 选中元件、区域选中(整体移动),移动时电气连接是存在的,如果按住Alt再移动,则电气连接断开。

Cadence布局布线技巧

Cadence布局布线技巧Cadence Allegro现在几乎成为高速板设计中实际上的工业标准,最新版本是2011年5月发布的Allegro 16.5。

和它前端产品 Capture 的结合,可完成高速、高密度、多层的复杂 PCB 设计布线工作。

Allegro 有着操作方便、接口友好、功能强大(比如仿真方面,信号完整性仿真、电源完整性仿真都能做。

)、整合性好等诸多优点,在做pcb高速板方面牢牢占据着霸主地位,这个世界上60%的电脑主板40%的手机主板可都是拿Allegro画的,广泛地用于通信领域和PC行业, 它被誉为是高端PCB工具中的流行者。

1、高频信号布线时要注意哪些问题?答:1.信号线的阻抗匹配;2.与其他信号线的空间隔离;3.对于数字高频信号,差分线效果会更好。

2、在布板时,如果线密,孔就可能要多,当然就会影响板子的电气性能,请问怎样提高板子的电气性能?答:对于低频信号,过孔不要紧,高频信号尽量减少过孔。

如果线多可以考虑多层板。

3、是不是板子上加的去耦电容越多越好?答:去耦电容需要在合适的位置加合适的值。

例如,在你的模拟器件的供电端口就进加,并且需要用不同的电容值去滤除不同频率的杂散信号。

4、一个好的板子它的标准是什么?答:布局合理、功率线功率冗余度足够、高频阻抗阻抗、低频走线简洁。

5、通孔和盲孔对信号的差异影响有多大?应用的原则是什么?答:采用盲孔或埋孔是提高多层板密度、减少层数和板面尺寸的有效方法,并大大减少了镀覆通孔的数量。

但相比较而言,通孔在工艺上好实现,成本较低,所以一般设计中都使用通孔。

6、在涉及模拟数字混合系统的时候,有人建议电层分割,地平面采取整片敷铜,也有人建议电地层都分割,不同的地在电源源端点接,但是这样对信号的回流路径就远了,具体应用时应如何选择合适的方法?答:如果你有高频>20MHz 信号线,并且长度和数量都比较多,那么需要至少两层给这个模拟高频信号。

一层信号线,一层大面积地,并且信号线层需要打足够的过孔到地。

Cadence操作技巧总结2:模块化布局

Cadence操作技巧总结2:模块化布局

在⽤allegro软件对pcb进去布局时,有许多结构相同的模块,如果总是⼀直单个布局布线,就会降低速度,如果⽤可以掌握模块复⽤的⽅法,则可以⼤⼤提⾼设计的速度。

第⼀步,在PCB设计中如果涉及两个以上相同的模块时,先点击placementedit进⼊布局模式。

第⼆步,在"find"选项中勾选"symbols",对已布局完成的电源模块进⾏框选,在器件上右键选择" Place replicate create",这⼀步注意⼀定要框选⽬标,再点击右键;

第三步,右键选择"done",空⽩的地⽅左键单击,然后在弹出的窗⼝中设置保存⼀个⽂件名;

第四步,接下来开始使⽤复⽤功能,对另⼀个电源模块进⾏模块复⽤,框选后在器件上右键选择"Place replicate apply",再选择刚刚保存好的⽂件;

第五步,点击上述命令后,就可以看到模块复⽤已完成。

Cadence基本操作、快捷键、基础知识

一、基本操作(一)电路图绘制1、登陆到UNIX系统。

在登陆界面,输入用户名***和密码***** 。

2、Cadence的启动。

登录进去之后,点击Terminal出现窗口,输入icfb命令,启动Cadence软件。

3、根据设计指标及电路结构,估算电路参数。

4、利用Candence原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance或者直接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号,根据不同的仿真电路设置不同的电源参数。

(7)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

如果有,察看CIW窗口的提示。

4、利用Candence原理图的输入。

(二)电路图仿真(1)启动模拟仿真环境。

在comparator schematic窗口,选择Tools-Analog Environment,弹出模拟仿真环境界面。

(2)设置模型库。

(3)设置分析类型。

在仿真窗口,点击Choose Analyses按钮,弹出Choose Analyses窗口,该窗口中列出了各种仿真类型,依次进行各种仿真,如ac、dc、tran,进行交流仿真、直流仿真、瞬态仿真。

(4)设置波形显示工具。

Cadence中有两种波形显示工具:AWD和wavescane,在仿真窗口选择Session-assign,在弹出的窗口中可以选择波形显示工具为AWD或wavescane。

Cadence技巧精品文档13页

Cadence 使用技巧1 orcad转换为cadence的时候电源网络或者其它NET不显示,仅仅高亮在ORCAD 或者cadence PCB环境中取消no_rat属性即可2 orcad做的元件封装,一定不要重名,特别是GND VCC 可以这样使用GND_1 GND_2等以区别3更改覆铜与布线及、焊盘之间距离方法选择Setup->Constraints->选择Spaceing rule set中Set valuses...按钮Shape To Pin (覆铜到管脚)Shape To Via (覆铜到过孔)Shape To Line (覆铜到走线)Shape To Shape(覆铜到覆铜)依据具体情况更改其值。

然后确定退出对话框。

选择Shape->Polygon在版图上画上所要覆铜的区域。

注意在Option选项卡上选择覆铜所在的层。

Shape Fill选择Dynamic copper。

Assign net name 为覆铜添加网络(例如覆铜选GND网络,则覆铜自动和网络名为GND的焊盘相连)选择Shape->Delete Islands,删除覆铜上的孤岛。

4 spb15.5没有提供元件对齐等功能,可以使用网络上的一个制作cadence PCB 封装的插件来实现5 不画原理图直接给管脚定义网络名的方法1.勾选SETUP->USER PREFERENCES->MISC->LOGIC_EDIT_ENABLED2.使用LOGIC〉NET LOGIC6 setup-->user proferences 下面的set pcb_cursor cross 小十字,set pcb _cursor infiniter 这是大十字cadence使用时间不长,虽然画几块板子,和protel 相比有很多不同的地方。

比如在protel PCB中想删除某几个连线,如果全选,就把过孔什么的全选,而在cadence中,是把net text via 等作为不同的属性,任何操作必须制定对象,如移动、删除、查找,必须有确定的类型;使用cadence很不习惯的一点是在连线以及过孔中没有显示网络标号,想知道输入什么还得点击一个显示的操作,而且不能全部显示,而在protel中,过孔以及连线是什么net一目了然。

使用Cadence布局布线常见问题详解

使用Cadence布局布线常见问题详解1.怎样建立自己的元件库?建立了一个新的project后,画原理图的第一步就是先建立自己所需要的库,所采用的工具就是part developer. 首先在建立一个存放元件库的目录(如mylib),然后用写字板打开cds.lib,定义:Define mylib d:\board\mylib(目录所在路径). 这样就建立了自己的库。

在Concept_HDL的component->add,点击search stack,可以加入该库。

2.保存时Save view和Save all view 以及选择Change directory 和不选择的区别?建立好一个元件库时,首先要先保存,保存尽量选择save view。

在concept-HDL中,我们用鼠标左键直接点击器件后,便可以对器件的外形尺寸进行修改,这时如果你再进入part developer做一些修改后,如果选择save all view会回到原来的外形尺寸,而选save view 会保留改动后的外形。

3.如何建part库,怎么改变symbol中pin脚的位置?在project manager中tools/part developer可建立,选择库并定义part name,在symbol 中add symbol,package中add package/addpin,依次输入pin:package中:a,Name : pin’s logical name不能重复b,pin : pin的标号,原理图中backannotate后相应的标号c,pin type: pin脚的类型(input,output等,暂可忽略)d,active:pin的触发类型high(高电平),low(低电平)e,nc:填入空脚的标号f,total:此类型的所有pin脚数g,以下暂略symbol中:a,logical name:对应package中的nameb,type:对应package中的typec,position:pin脚在器件中位置(left , right , top , bottom)d,pintext:pin在器件中显示的name(对应package中的pin,但可重复,比如package中的gnd1和gnd2都可设为gnd)e,active:对应package中的active修改:用part developer打开要修改的器件,*选择edit/restrict changes(若不选择,则器件被保护,修改后存盘无效),一般修改:a,package中相应pin的标号和nameb,pin的active类型c,symbol中各pin脚的顺序(pin脚的顺序在第一次存盘后再次打开会被改变,对于较多pin脚的器件,如232pins,修改较繁琐,故尽力保证的一次的成功率。

CADENCE小知识

CADENCE小知识:我的ALLEGRO 是14.0版本的,FILE——EXPORT——后面就没有看到SUB DRAWING 的命令了。

如果用EDIT——COPY的话又不能把A板的线贴到B板上,我该怎么办?A: 是不是你启动Allegro 时Cadence Product Choices 没选好,要选PCB Dedign Expert 或Alle gro Expert~~~Q: 在ALLEGRO中,找个器件好难啊,他只是点亮器件而光标不移动到器件那里。

请问各为大侠,有没办法可以象POWERPCB 那样,查找零件时光标跟着移动?A:确认将元件点亮后,将鼠标移动至右下角的小显示框中,单击左键,光标即可自动转到所点亮的元件处.Q: 将logic_edit_enabled打开后,只能删除单个的net, logic_edit_enabled打开".是從何處打開???A: 在14.2中的操作:Setup -> User Preferences Editor -> Misc -> logic_edit_enabled然后可以在LOGIC/NET LOGI C 下删除NET。

Q: 想移动元件的某一个PIN ,请问该如何做。

用move 命令,总提示Symbol or drawing m ust have UNFIXED_PINS property。

A: edit -> properties 选中要move Pin的元件的 symbols,增加 UNFIXED_PINS 属性即可。

Q: how can i get rid of the "dynamic length" dialogue box?A: Setup -> User Preferences Editor ->Etch>allegro_etch_length_onQ:请问如何將以删除的PIN NUMBER及SILKSCREEN还原??A:删除此零件,再重新导入~~~或可以直接UPDATE 零件也可以Q:从orcad导入后,place->quickplace,但是出来的元件上面很多丝横,就和铺铜一样,怎么回事?A:把PACKAGE GEOMETRY 的 PLACE_BOUND_TOP 勾掉即可.Q:请问在allegro中,怎様画一条沒有绿漆的綫?A:同样位置再画一根sold mask的线Q:如何将走线的尖角过渡改成圆弧?A:可以直接画圆弧上去,记得勾上replace etch,原来的线就没了或使用slide 命令﹐然后在右邊的tab option選項中的comers改成arc,再去移動線﹐就可以改成圓弧﹗Q: allegro中覆铜的基本步骤是怎样的?A:edit/shape进入shape编辑模式——edit/change net(pick)点上GND net——shape/parameter s设置相关参数(看help)——void/auto进行shape处理——shape/fill退出shape编辑模式。

cadence信号完整性分析精要总结

第1章 高速电路基础要点1、 高速电路的定义:数字逻辑电路的频率达到或超过50MHZ ,而且工作在这个频率之上的电路占整个系统的1/3以上,就可以称为高速电路。

2、 高速信号实质:信号传输时间大于数字信号驱动端上升时间的1/2,则可以认为是高速信号并产生传输线效应,实质是,:传输时间小于上身时间的一半时,那么在本次信号状态改变前,接收端的反射信号就已经到达驱动端,不会引起逻辑错误,反之,大于一半时,接收端的反射信号就可能会与下一次驱动端的输出信号进行叠加,若反射信号很强,就可能会影响下一次输出的正常逻辑。

3、 高信号的确定:Tr 表示信号上升时间,Tpd 表示传输延迟,若Tr>4Tpd,信号在安全区域,若2 Tpd<T r≤4 Tpd,信号在不确定区域,若Tr ≤2 Tpd ,信号落在问题区域,设计需保证信号落在安全区域。

4、 传输线:传输线上由两个具有一定长度的导体组成的回路的连接线,有时也称延迟线,传输线上每一点都有不同的电势。

(可以理解为机械波的振动,或电场吸纳促使电子移动导致电位变化模型,需要时间,故不同点电位不一致,不深按纠)5、 传输线的确定:信号传输路径长度大于信号波长的1%,或接收端元器件是边缘敏感,或系统没有过冲和下冲容限,此时虚认为传输路径是传输线。

(实质:边沿时间、波形变化时间、传输时间三者很接近时就必须考虑为传输线)零碎常识:(1)、PCB 上走线等效电阻阻值约为0.25~0.55Ω(2)、空气电信号传播速度85ps/in ,空气介电常数约为1,真空为1.(2)、FR4内层布线180ps/in ,介电常数为4.5;外层:140~180,2.8~4.56、反射系数:Z L 是当次传播负载端等效阻抗,Z O 当次传播输出端等效阻抗。

ρL =OL O L Z Z Z Z + 7、反射电压:反射系数乘ρL 以输入电压Vi 。

即Vf=ρL *Vi注:上表达式是乘以输入电压,即得反射电压,不在需要与1或原始量进行加减运算。

AltiumDesigner多通道设计整理笔记

AltiumDesigner多通道设计整理笔记使⽤AD画PCB也好⼏年了,⾃认为⽔平⼀般,也没画过多⾼级复杂的板⼦。

虽然早知道AD可以实现多层图纸设计,也知道可以多通道设计。

但由于之前⾃⼰画的板⼦都不算复杂。

偶尔可能会遇到有多通道(两三个),但出于⽐较懒的原因,从来没有尝试过这个功能,宁愿⾃⼰把原理图复制复制再复制,然后对元器件重新编号。

画板⼦时就随便拉⼏条参考线,把元件⼤致摆的差不多,然后⼀块⼀块⼜⼀块的重复布局布线。

但最近遇到了⼀个较为复杂的板⼦,⼀开始还想使⽤笨办法,但发现相当折磨。

⽆奈只得研究⼀下这个多通道设计。

先整⼀个简单的例⼦尝试是否好⽤,⼀开始各种报错,各种不顺,折腾半天后终于算是顺利搞定。

在此把⾃⼰摸索的过程以及遇到的问题分享给⼤家。

个⼈感觉,多通道设计还是有很多好处的。

⽐如:减少重复性⼯作(⽆论是设计原理图还是PCB,⼯作量都⼤⼤降低)。

降低⼈为犯⼀些低级的错误,⽐如某⼀通道个别器件可能会弄错,原理图整体显得简洁美观等等。

第⼀步:先是建⽴⼀个PCB⼯程,然后新建⼀个原理图(⼀个⼦模块的原理图),由于是学习摸索,图省事,我画了⼀个挺简单的图。

第⼆步:再建⽴⼀个新的原理图,然后点击菜单Design》Create symbol from sheet or HDL,弹出如下图所⽰的对话框,选择上⼀步建⽴的⼦模块电路。

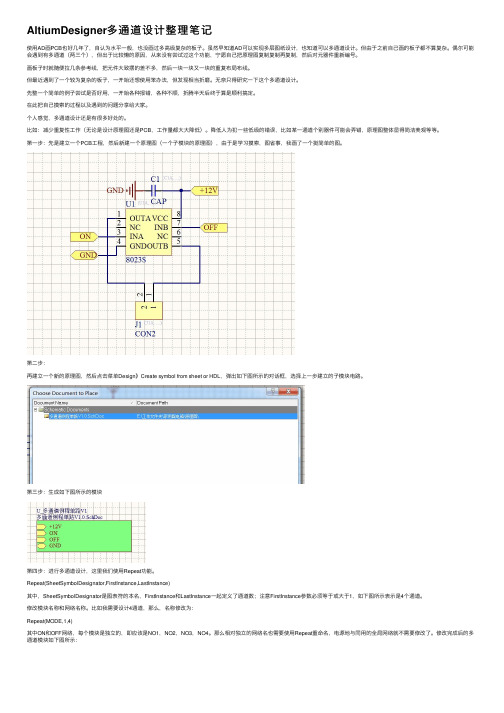

第三步:⽣成如下图所⽰的模块第四步:进⾏多通道设计,这⾥我们使⽤Repeat功能。

Repeat(SheetSymbolDesignator,FirstInstance,LastInstance)其中,SheetSymbolDesignator是图表符的本名,FirstInstance和LastInstance⼀起定义了通道数;注意FirstInstance参数必须等于或⼤于1,如下图所⽰表⽰是4个通道。

修改模块名称和⽹络名称。

⽐如我需要设计4通道,那么,名称修改为:Repeat(MODE,1,4)其中ON和OFF⽹络,每个模块是独⽴的,即应该是NO1,NO2,NO3,NO4。

Cadence网络表总结

Cadence 网络表总结用Capture CIS 画原理图后结果发现工程文件丢失。

不知道是我误删除了还是由于Capture CIS 的bug 问题。

但此时我已将网络表导入了Allegro ,并摆放了一部分元件。

如果重新画原理图重新布局PCB 比较麻烦,于是就按照以前打印的PDF 原理图布线。

可是当布到最后却发现了问题,我想修改原理图的设计时却没有办法了。

比如像下面这图里我想把接地引脚换成数字地(Dgnd ),以前接的是模拟地(Agnd )平时更改一下原理图就可以了,但原理图丢失,这时候就只能去修改cadence 网络表来实现目标。

cadence 网络表包括三个文件:pstchip.dat ,pstxprt.dat ,pstxnet.dat打开之后就知道pstchip.dat 是描述元件的引脚等信息的。

pstxprt.dat 是描述封装信息的,就是指该封装长什么样。

pstxnet.dat 就是描述各个元件之间的网络联系,即把所有的网络表和元件都给列了出来。

想将上面的元件地从Agnd 改到Dgnd ,需要将pstxnet.dat 打开,在里面的NET_NAME'AGND''@ODDETECT.ODDETECT(SCH_1):AGND':C_SIGNAL='@oddetect.oddetect(sch_1):agnd';里找到对应的C46 ,C47,C45 ,C48 的NODE_NAME C47 2'@ODDETECT.ODDETECT(SCH_1):INS229657@DISCR ETE.CAP NP.NORMAL(CHIPS)':'2':;厶・,NODE_NAME C46 2'@ODDETECT.ODDETECT(SCH_1):INS229641@DISCRETE.CAP.NORMAL(CHIPS)':IQI.・厶・,NODE_NAME C48 2'@ODDETECT.ODDETECT(SCH_1):INS546266@DISCRETE.CAP.NORMAL(CHIPS)':'2':;厶・,NODE_NAME C45 2'@ODDETECT.ODDETECT(SCH_1):INS551150@DISCRETE.CAP.NORMAL(CHIPS)':'2':;厶・,剪切至'DGND''@ODDETECT.ODDETECT(SCH_1):DGND':C_SIGNAL='@oddetect.oddetect(sch_1):dgnd'; ................... 这时再重新导入网络表,就就会发现在PCB 里已经更改过了电气的连接关系。

Cadence学习总结

Cadence学习总结Allegro 软件是 Cadence 公司出品的面向中高端企业用户的 PCB 设计软件,主要针对高速、高密度电路板设计,尤其在通讯等领域被广泛应用,目前最新版本号是 16.0。

Allegro 软件导出坐标数据步骤.①Design Entry CIS绘制原理图。

②*HDL:芯片开发时的扳机设计③PCB Editor:PCB板布局布线的工具④PCB Router:自动布线的工具。

⑤PCB SI:电路板完整性仿真。

⑥⑦设置模版Options--Design Template⑧原理图背景设置,设置跳转:options-preferences⑨修改原理图属性:options-Schematic page properties⑩封装的一些设置在:options-user properties11多个部分的元器件显示在一页:view-package12---第一个多个模块功能相同13第二个功能不同14多个部分之间切换:ctrl+n;15同时看多个部分:View--package.16放置期间:place--part17取消所有标注;18自动生成编号:19多个部分冲突,给封装添加一个属性,根据不同修改属性。

20放置的时候,按R按键,可以旋转放置的封装。

21画线快捷键:按W22画线到了终点(终端悬空),双击,如果单击还会继续画。

23画之前,按住shift按键,可以绘制任意角度的线条。

24删除节点,按住S,才能选中焦点。

25放置网络名字,按n26总线的命名:名字一定是英文。

27总线和信号线的要求:2829连接到其他页。

30浏览工程中用到的软件,选中工程中的dns---菜单edit---browse---parts(可以查看有没有忘记编号那些)31电气规则检查:32查看所有网络:dns---edit---browse---nets(双击表格中的网络,可以查看此网络) 33查看页面之间互联的网络:dns---EDIT---browse---off_page(原理图检查非常重要,或者用pans检查也行)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、cadence多通道布局布线(使用模块复用的方式实现)

步骤与关键点:

1、模块生成

module生成

1、在orcad中画好模块的原理图,设定好封装,做好drc,做好元件编号。

2、检查元件属性是否设为current properties,其它设定可能出错。

2、在annotate-->allegro reuse中,选中generate reuse module,renumber design for

using modules,选中unconditional,其它不选。

3、生成netlist.

4、将netlist导入到allegro,布线,布局,若无rename等需要与orcad交互的动作,选tools-->creat modules生成mdd文件.mdd文件的文件名一定要定义为:DSN NAME_ROOT SCHEMATIC NAME.mdd。

DSN NAME为你定义的orcad中的dsn文件名,ROOT SCHEMATIC NAME是这个文件中的页名字。

这里若定义不对,在reuse时找不到mdd文件。

之后跳到第6步。

5、在allegro中export logic,然后在orcad中back annotate,并再次drc。

这一步很关键。

??(实际操作时该步骤未使用)

6、模块制作完成。

使用生成的模块

1、在新的orcad设计中,选place-->herarhical

block,reference中填入BLK?(注意,这里使用BLK是为了与原理图中的U?R?C?区别,保证BLK这个名字专用于moduel,不然在做完allegro后,rename 时,导回到orcad中出问题。

) 在implementation type中选schematic view,在implementtation name中填入先前模块的页名称,在path and file name中选择相应的dsn文件,之后在你的原理图中出现一个block.(实质就是层次原理图的放置方法,只不过需要在原理图中新增层模块框,以免PCB中放入新的模块时无电路与之对应,则线条line会报错)

2、继续其它设计,之后在annotate-->packageing中,选中reset part name to "?",同时选中update occurrences,执行一下,将所有的元件(包括module的name改为?),在annotate-->allegro reuse中,选中renumber design for using modules,选中incremental,选中do not change the page number,选中select modules to mark for框里的内容。

其它不选。

3、drc后,出netlist.

4、导入到allegro后,palce-->manually place,选mudule,instances,将module放入。

注意一下mdd文件路径的设定,不正确会找不到mdd 文件的。

5、在allegro中布好线后,可以rename到arcad中,与正常设计无区别。

6、over.

做reuse时的几个注意事项:

A 如果是多层板的reuse,那么因为生成的module是多层的,所以新的brd在module 放入之前最好也设置成和module一样的层及plane网络设定。

plane不一定要全部设,但像VCC gnd最好设定。

B 如果绘制大规模fpga\dsp\arm\powerpc等的电路,芯片symbol package往往含有多个part,这在reuse时会产生问题。

建议在生成module部分在进行sch设定时,给多part 的symbol package再添加一个属性,例如wzh,然后同一个芯片的package的这个值赋予相同值。

在后续的annotate/pcb editor reuse/property combine 选型中加入{wzh}。

1:当reuse模块已经放在电路中使用,重新修改reuse模块的port口后,在使用的原理中右击这个模块,选synchronize up,则实现修改的同步。

2:在reuse模块中,不能使用room属性,不然可能与使用reuse的电路图混淆。

3: reuse模块中不能使用全局变量,特别是电源和地,使用port口传递数据。

4: reuse模块内部修改后,只要port口没有变,则在使用它的原理图不用同步。

5: 做好的模块文件用在pcb中后,若需要修改这部分文件,在修改完成后,在原pcb中使用update symbol功能,选相应的moddle,之后更新就行了,注意生成mdd文件时,原点的选择,这然更新后一些线会错位。

6:当导入到allegro的模块出现dummy net的错误时,怎么办?

出错的可能原因是由于模块的orcad文件造成的,可能是对原始的orcad取一部分进行修改,这些元件带有原来文件的一些属性。

将相关orcad文件的所有元件和连线copy到一个新的页内,将当前页的内容删除,从刚才copy到新页的内容copy回来,这时看元件的属性

时,没有黄色的部分,按正常步骤重新生成mdd文件,在调用这个模块的orcad文件中,重新编一次元件编号,生成网表,问题解决。

7:当含有reuse的设计导入到allegro并布线完成,若重新修改原理图,比如换一个10pin 的IDC插座到16pin,不能用annotate-->allegro reuse命令,不然生成的网表会导入到allegro 中会出错,不知是什么原因?

答:在原理图设计中,当使用reset to ?后,使用annotate-->allegro reuse命令,将netlist 导出到allegro后,不能再使用使用reset to ?,新增的元件使用increase功能,不要将所有的元件reset to ?,不然会出错。

====================================================================== =============

建议寻找下面的文献阅读。

“Stp_cdnlivesv2006_patrick_modules.pdf”

名称:Using Modules in Allegro PCB Editor Design Reuse for Performance

/search?hl=zh-CN&source=hp&q=Stp_cdnlivesv2006_patrick_module s&btnG=Google+搜索&aq=f&aqi=&aql=&oq=

二、Allergro自定义常用快捷键

1、直接在命令行中输入如下命令:

(1)、定义旋转:funckey r iangle 90

(2)、移动:funckey m move

(3)、镜像:funckey f mirror

上述操作也可以在命令行中输入alias调出env菜单后在该文件中加入上述内容可以达到一样的效果。

2、可以使用alias命令将move等常用快捷键定义为别名,如:

alias m move 此时输入m时相当于输入了move关键字,需要按回车后才能被执行,相

当于仅仅起到替代的作用,而funckey则是直接定义快捷键,一旦定义后不需按回车即可执行操作。

三、层次原理图绘制方法

9、层次原理图中的跳转。