基于DSP和USB总线的高频超声数据采集系统

基于USB接口的高速高精度实时红外视频采集系统设计

基于USB接口的高速高精度实时红外视频采集系统设计赖睿;周慧鑫;刘上乾;杨隆梓

【期刊名称】《红外技术》

【年(卷),期】2005(027)004

【摘要】提出了一种高速高精度实时红外视频处理及采集系统设计,采用高速DSP 芯片对红外视频图像进行非均匀校正,配以传输速度高达480Mb/s的USB2.0接口芯片实现与主机接口,视频图像的显示及后续处理由计算机完成.实验验证了该系统具有高速、高精度、实时性强等特点,适用于高精度的红外视频采集和辐射特性测量.

【总页数】3页(P288-290)

【作者】赖睿;周慧鑫;刘上乾;杨隆梓

【作者单位】西安电子车技大学技术物理学院红外教研室,西安,陕西,710071;西安电子车技大学技术物理学院红外教研室,西安,陕西,710071;西安电子车技大学技术物理学院红外教研室,西安,陕西,710071;西安电子车技大学技术物理学院红外教研室,西安,陕西,710071

【正文语种】中文

【中图分类】TN216

【相关文献】

1.基于红外目标跟踪技术的实时视频采集系统设计 [J], 翟建芳;赵振刚

2.基于DM8148的红外视频采集存储系统设计与实现 [J], 石永彪;黄飞;杨龙;张湧

3.一种基于FPGA的红外视频采集系统设计 [J], 贺贝;张友奖;徐旺生

4.基于乒乓结构的实时视频采集系统设计 [J], 魏志博;章云

5.基于FPGA的视频采集及实时显示系统设计 [J], 李光春;苏沛东;杜世通;柯杰;刘世昌

因版权原因,仅展示原文概要,查看原文内容请购买。

DSP技术课程教学平台用超声波测距系统的设计

卢

贶

部 中断 ( I X NT1中断 ) 在 外 部 中断 处 理 程 序 内, , 将 超声 波返 回时 间 进 行记 录 , 将 相 应 的 超声 传 并 感 器关 闭 。外部 中断 处 理程 序 非 常 简 短 , 设 计 本 只用不 到 2 O条指 令 , 且 TMS 2 F 8 2指令 执 并 30 2 1 行速度 很快 , 因而 即使 因进 入 外部 中断 处 理程 序

图 5 超 声 波接 收 电路

2 . ms 0 6 。软 件 设 计 中涉 及 到 的 外 部 中断 处 理 程 序 和定 时器 中断 处 理 程 序 框 图 如 图 8和 图 9所

其 他 有 测 距 要 求 的领 域 。 关键词 D P技 术 ; 声 波 测 距 ; 统设 计 S 超 系

T 5 . N7 2 6 文献 标 志 码 A 文 章 编 号 1 7 —8 0 ( 0 2 0 —0 4 —0 61 1021)4 03 4 中 图分 类号

在 日常 生产 生 活 中 , 多场 合 如 : 车倒 车 、 很 汽 机 器人 避 障 、 工业 测井 、 水库 液位测 量等 需要 自动

工程 技术

武 汉船 舶职业 技术 学 院学报

21 0 2年第 4期

D P技 术 课 程 教 学 平 台 用 超 声 波 测 距 系 统 的设 计 * S

卢 贶

( 武汉软件 工程 职 业 学院 , 北武 汉 湖

摘 要

40 0 ) 3 2 5

本 文 详 细 介 绍 了基 于 D P技 术课 程 教 学 平 台 用 超声 波 测 距 系 统 。 超声 波测 距 可 用 于 智 能 车 避 障 、 量 物 体 距 S 测

目标 或障碍 物后 反 射 回来 , 经反 射 后 由超声 波 接

基于FPGA和USB接口的超声波信号高速采集卡

基于FPGA和USB接口的超声波信号高速采集卡许西宁;余祖俊【摘要】An AD acquisition card with a sampling rate up to 100 MS/s is needed in the ultrasonic rail flaw detection system, so the high speed ultrasonic signal acquisition card based on FPGA and USB interface is designed. FPGA-based hardware design and programming method, firmware and driver design based on CY7C68013 USB 2.0 chip are introduced in detail. Analog signal acquisition frequency up to 100 MHz, the maximum data transfer rate of 20 MB/s, the acquisition card can acquire ultrasonic signals in real-time without missing data.%在超声波钢轨缺陷检测系统中,需使用采集频率大于100 MHz的AD采集卡,为此设计了应用现场可编程门阵列(Field-Programmable Gate Array,FPGA)和基于USB 2.0接口的超声波信号高速采集卡.文中论述了硬件电路设计方案及程序设计方法,在基于CY7C68013的USB 2.0通用接口芯片上实现了大量数据传输的固件程序设计、驱动程序设计.该采集卡模拟信号采集频率可达100 MHz,数据传输速率大于20 Mb/s,可实时采集超声波信号,运行稳定,无丢包现象.【期刊名称】《北京交通大学学报》【年(卷),期】2011(035)006【总页数】4页(P89-92)【关键词】现场可编程门阵列;USB 2.0;中触发;驱动程序【作者】许西宁;余祖俊【作者单位】北京交通大学机械与电子控制工程学院,北京100044;北京交通大学机械与电子控制工程学院,北京100044【正文语种】中文【中图分类】TP274.2随着我国高速铁路的飞速发展,无缝线路技术得到了广泛的应用.无缝钢轨在外界温度发生变化时,其内部将产生极大的温度应力,如果在钢轨内部存在伤损缺陷点,很容易发生钢轨折断.对于高速铁路无缝线路,实时监测钢轨内部缺陷状态,及时预警维修,是提高高速铁路运行安全的重要保障.目前,在钢轨缺陷检测技术中,超声波无损检测技术应用广泛,超声波接收探头输出的模拟信号中心频率高达2.5 MHz,需使用采集频率大于100 MHz的AD采集卡.目前国内还没有此类产品,国外高速采集卡价格普遍较高,在5万元(人民币)以上.为此我们实验室自主研发了基于FPGA和USB的超声波信号高速采集卡,主要应用在超声波无损检测装置中,采集超声波接收探头输出的信号.1 硬件设计1)AD转换芯片.系统AD转换芯片采用Analog Devices公司的AD9433,它是12位单通道模拟信号采样转换器,具有片上跟踪和保持电路,该产品转换速率高达125MSPS[1],具有优异的动态性能.模拟信号输入至AD9433之间的通道采用了变压器交流耦合电路,这样实现有几个优点:①易于实现模拟信号输入端的阻抗匹配;②可隔离直流分量;③可将单端模拟输入信号转换为差分信号,直接接入AD9433的AIN+、AIN-端.AD9433的编码时钟支持差分或单端输入,为了获得最佳的时钟性能,采用差分输入模式.由FPGA的PLL时钟输出作为AD9433的编码时钟输入,这样能很方便实现数据采集的同步.FPGA的PLL时钟输出为 LVTTL电平信号,AD9433的编码时钟可兼容LVPECL信号,需要进行电平转换,系统采用SY10EPT8L实现.SY10EPT8L可实现LVT TL到差分 LVPECL的信号转换,延时小于600 ps.SY10EPT8L的差分LVPECL信号输出端经电容耦合后,可直接接入AD9433的ENCODE+和ENCODE-管脚.AD9433的AD转换及数据结果输出需要在编码时钟驱动下进行,每个时钟周期启动AD转换一次、输出转换结果一次,启动一次AD转换到输出当前结果之间有8个时钟周期的延时.2)FPGA.AD转换输出结果需要同步读取,系统使用的编码时钟为100 MHz,如此高的同步传输速率采用一般的MCU无法实现,与通用MCU相比,FPGA内部集成锁相环,通过倍频,核心频率可以到几百兆,FPGA的不同逻辑可以并行执行,一个时钟周期可以同时处理不同任务,因此,FPGA具有高速的数据处理能力.系统选用了ALTERA公司的Cyclone系列FPGA——EP1C12,该FPGA有12 060个逻辑单元,52个 M4K RAM,总 RAM位数239 616 bit,2个锁相环,249个用户可用IO管脚[2].FPGA主要完成AD数据高速同步读取、数据缓存、数据传输等任务.3)USB.AD数据采集采用中触发模式,只采集超声波信号中心区域附近的有用信息,每检测到一次超声波信号,采集2 KB的数据,设超声波发射频率为1 kHz,每秒钟有效数据量为2 MB.计算机串口波特率最高可设置为128 000 b/s,采用串口传输模式,每秒钟可输出数据只有12.5 KB,无法满足系统需求.目前,USB 2.0接口在PC的采集系统中得到了广泛的应用,USB 2.0在每个上微帧中最大可传输13个块传输包,每个传输包512 B,每个微帧长固定为125 μ s,其最高传输速率可达 53 MB/s.系统选用Cypress公司推出的USB 2.0控制器CY7C68013,向下完全兼容流行的USB 1.1协议,是USB 2.0的完整解决方案.该芯片包括带8.5 KB片上RAM的高速8051单片机、4 KB FIFO存储器及通用可编程接口(GPIF)、串行接口引擎(SIE)和USB 2.0收发器,无需外加芯片即可完成高速USB传输,性价比较高[3].4)硬件总体结构.FPGA经PLL输出同步时钟至AD9433,在同步时钟驱动下,AD9433进行AD转换,AD9433输出的AD转换结果直接送入FPGA内部FIFO,由FPGA内部接口控制模块控制内部FIFO的写入、读出,通过CY7C68013将采集的数据经USB接口发送给PC机.系统硬件总体结构如图1所示.图1 硬件总体框图Fig.1 Hardware general structure2 FPGA程序设计FPGA程序主要完成读取AD转换结果、数据缓存、通过USB接口将数据发送至PC机等任务.对超声波接收信号的数据采集采用中触发模式[4],从检测到有效信号时刻起,记录当前时刻前后各1 KB的数据,如图2所示.FPGA内部时钟和AD9433编码时钟采用同一时钟源,由FPGA的内部PLL产生,以保证数据同步[5].AD9433输出的AD转换结果,直接送入FPGA内部FIFO,由FPGA内部接口控制模块,控制内部FIFO的写入、读出,当采集到有效数据信号后,再由接口控制模块控制FIFO读出并写入CY7C68013的内部FIFO中.其程序设计原理见图3.整个程序流程分为5个阶段,如图4所示.Stage1:每个CLK的上升沿将一组AD转换结果写入FIFO,共写入2 KB数据. Stage2:每个CLK的上升沿将一组AD转换结果写入FIFO,同时读出一组数据,保持FIFO内部有2 KB的数据,同时检测是否有达到阈值的数据.Stage3:当检测到有效的超声波信号后,边读出边写入,继续存储1 KB的AD转换结果.Stage4:停止将AD结果写入FIFO,并将2 KB的有效数据写入USB接口芯片.图2 中触发采集模式Fig.2 Middle trigger acquisition mode图3 FPGA程序设计原理框图Fig.3 Block diagram of FPGA programming图4 FPGA程序时序图Fig.4 FPGA programming timing diagramStage5:等待USB接口将数据送出.FPGA将FIFO中的数据写入到USB接口芯片的操作比较简单,将CS信号置低,用ADR选通所使用的USB端点号,数据在每个WR的下降沿被写入到该端点的FIFO.3 USB芯片固件程序设计固件程序在CY7C68013内部运行,主要完成USB接口配置、处理USB驱动程序的请求.为了简化固件编程,CYPRESS提供了固件编程框架,只需在此基础上添加少量代码就可以完成固件编程.CYPRESS的固件编程框架主要包括:dscr.a51,FW.C,PERIPH.C等文件[6].其中:Fw.c是固件框架源文件;Periph.c是用户调度函数;Dscr.a51是USB描述符列表. 复位上电时,固件先初始化一些全局变量,接着调用初始化函数TD-Init()初始化设备,循环1 s后重枚举,直到端点0接收到SETUP包退出循环,进入循环语句while,执行任务函数,函数包括:a.TD-POLL()用户任务调度函数;b.如果发现 USB设备请求,则执行对应的USB请求;c.如果发现 USB空闲置位,则调用TD-Suspend()挂起函数,调用成功则内核挂起,直到出现USB远程唤醒信号,调用TD-Resume(),内核唤醒重新进入while循环. FPGA采集的AD数据经过CY7C68013的EP6端点送入USB接口,在固件程序开发时,主要修改Dscr.a51中的USB描述符列表及Periph.c中TD-Init()函数.1)修改Dscr.a51中的USB描述符列表.端点6描述符设置如下:db 7; 描述符长度db 5; 描述符类型5:端点db 86H; 端点6方向:INdb 2; 端点类型:Bulkdb 00H; 最大包长度(LSB)db 02H; 最大包长度(MSB)db 00H;2)修改 TD-Init()函数.程序如下:完成以上修改后,将USB固件程序编译后下载到CY7C68013,程序运行后,CY7C68013工作在Slave FIFO模式,FPGA根据相应ADR将AD转换结果写入EP6的FIFO,PC机应用程序调用驱动程序就可以从EP6中读出AD转换数据.4 USB驱动程序开发USB设备驱动程序的设计是基于WDM(WindowsDriver Model,驱动程序模型)的,主要任务是建立应用程序和CY7C68013的通信通道,将FPGA获取的AD有效数据从相应通道读入PC机.程序使用DriverStudio中的DriverWizards驱动程序向导生成,按照向导进行配置:设定Device ID、Vender ID的值;新建端点 6(m-Endpoint6IN);设置端点6的方向为IN;传输模式为BULK.在基于DriverStudio开发的驱动程序中,向存储器空间读写大量数据一般选用Write/Read函数,Read()函数对应着Win32 API函数中的 ReadFile(),其中参数通过KIrp I传递进来,使用 I.Mdl()声明内存空间,并映射到用户读取数据的缓存区地址,使用I.ReadSize()函数来获取读取数据的长度.在Read()函数中添加以下程序:在编写的应用程序中的调用ReadFile(hDevice,buf,n,&nRead,NULL)函数,可将USB端点6中的数据读入PC机中.5 实验与结论在京沪高速铁路先导段试验现场,安装了此次研制的超声波信号采集卡,在列车高速通过时,采集到的超声波信号脉冲如图5所示.图5 现场采集超声波信号Fig.5 Ultrasonic signal collecting on-site基于FPGA和USB的超声波信号采集卡实现了100 MHz高速模拟信号的采集,并能将有效信号实时传输至PC机显示、存储,便于后续数字信号处理,为钢轨裂纹、断轨检测提供了大量的数据样本.该采集卡还具有较好的推广应用价值,可广泛应用于高频小信号模拟信号的采集系统中.参考文献(References):[1]ANALOG DEVICES Inc.AD9433 device handbook[Z].ANALOG DEVICES Inc,Rev.A,2009.[2]ALTERA.Cyclone device handbook[Z].ALTERA,Volume 1,2005.[3]CYPRESS.EZ-USB FX2 Technical reference manual[Z].CYPRESS,Version 2.1,2001.[4]林莉,李喜孟.超声波频谱分析技术及其应用[M].北京:机械工业出版社,2009:1-25.LIN Li,LI Ximeng.Ultrasonic spectrum analysis andapplication[M].Beijing:China Machine Press,2009:1-25.(in Chinese)[5]黄正谨,徐坚,章小丽,等.CPLD系统设计技术入门与应用[M].北京:电子工业出版社,2002:93-159.HUANG Zhengjin,XU Jian,ZHANG Xiaoli,et al.CPLD system design technology and application[M].Beijing:Publishing House of Electronics Industry,2002:93-159.(in Chinese)[6]王成儒,李英伟.USB 2.0原理与工程开发[M].北京:国防工业出版社,2004:295-340.WANG Chengru,LI B 2.0 principles and engineeringdevelopment[M].Beijing:National Defense Industry Press,2004:295-340.(in Chinese)。

超声波探伤数据采集技术的研究

超声波探伤数据采集技术的研究张玉雷(青岛科技大学,山东青岛266061)蛹要]超声波探伤作为一种重要的无损检测技术已经在国防工业、机械制造等领域获得了广泛应用。

现有的便携式超声波探伤系统通常采用单片机或D SP实现方案,软件设计非常复杂,实现难度大,代码移植和重用比较困难,因此不便于系统的升级和维护。

近年来。

嵌入式技术在许多领域的应用日益广泛,在超声波无损检测领域有着广阔的应用前景。

论文通过对超声波检测技术发展现状的分析.提出了超声波探伤数据采集装置的技术方案。

其次,论文对超声波探伤的基本方法和影响探伤的因素也进行了简单分析。

[关键词]超声波探伤;无损探伤;自动测控;数据采集一般的数据采集卡由于不是针对于超声探伤设计的,因此只能实现对信号采集,而无法做到实时处理。

而在超声波探伤时,对被测物检测到的大量的信息都是无伤的回波信息,而我们往往最关心的是缺陷回波信号,它包含了大量的关于缺陷位置和当量信息。

因此,针对于超声波探伤的数据采集卡就要求必须具备实时的数据处理能力。

系统主要由4部分组成:信号放大电路、模数转换(A心】电路、数据缓存(F I—FO)电路、数字信号处理(D SP)电路。

1信号放大部分超声波接收探头接收到的回波信号在进入~D之前,需要将信号放大。

在超声探伤中使用的超声脉冲信号通常频率较高,因此要放大此类信号就要求运算放大器必须具有较好的带宽(B andw i dt h)和摆率(Sl e w r at e)等特性。

其中~D采样速度和采样精度对于便携式数字超声波探伤系统的性能影响至关重要。

对于10M H z工作频率的超声波探头而言,要保证缺陷的峰值不漏检,至少需要60—80M H z的采样速度。

而传统的数字化探伤系统,由于A/D采样速度只有20—40M H z,通常在采样前增加几级模拟包络滤波器以实现全波、+/一半波检波。

这种包络检波方式滤除了部分缺陷回波,因此给缺陷识别和定量计算带来了很大的困难。

采用DSP的声音采集系统硬件原理及设计(精)

采用DSP的声音采集系统硬件原理及设计声音信号无处不在,同时也包含着大量的信息。

在日常的生产生活中,我们分析声音信号,便可以简化过程,得到我们想要的结果。

随着 DSP芯片的性价比不断攀升,使 DSP得以从军用领域拓展到民用领域,由于 TI公司 DSP5000系列强大的音频压缩能力,语音应用得到了较大的发展。

因此,基于 DSP的声音采集系统的设计与开发具有重要的现实意义。

1系统总体介绍该系统主要应用于工业生产中,通过采集的声音信号与数据库中的数据相比声音信号无处不在,同时也包含着大量的信息。

在日常的生产生活中,我们分析声音信号,便可以简化过程,得到我们想要的结果。

随着 DSP 芯片的性价比不断攀升,使 DSP得以从军用领域拓展到民用领域,由于 TI公司 DSP5000系列强大的音频压缩能力,语音应用得到了较大的发展。

因此,基于 DSP的声音采集系统的设计与开发具有重要的现实意义。

1系统总体介绍该系统主要应用于工业生产中,通过采集的声音信号与数据库中的数据相比较,来检测生产设备的运行状态等。

本系统主要分为以下几个部分:电平转换电路、 AD转换电路、静态存储与动态存储、USB接口以及 JTAG部分。

该系统通过采集声音信号来检测器械的裂纹、密合度等。

将 DSP高速处理数字信号的能力与 USB高速传输数据的能力结合起来,使其服务于工业生产,是该系统的主要设计目的。

系统选用了 TI公司的TMS320VC5402作为该块 PCB的CPU,并将 Philips公司的 PDIUSBD12作为接口芯片,使用 USB1.1协议进行DSP与电脑的通信。

2硬件设计思想人类可以听到的声音信号是范围在 20-20kHz的模拟信号,所以首先需要传感器接收该声音信号,接着需要进行转换,使声音信号由模拟信号变为数字信号。

之后通过分析噪声产生的原因和规律,利用被测信号的特点和相干性,检测被覆盖的声音信号。

在检测方法上有频域信号的相干检测、时域信号的积累平均、离散信号的计数技术、并行检测等方法。

智能仪器课后习题答案

智能仪器课后习题答案1-1 你在学习和生活中,接触、使用或了解了哪些仪器仪表?它们分别属于哪种类型?指出他们的共同之处与主要区别。

选择一种仪器,针对其存在的问题或不足,提出改进设想参考:就测量仪器而言,按测量各种物理量不同可划分为八种:几何量计量仪器、热工量计量仪器、机械量计量仪器、时间频率计量仪器、电磁计量仪器、无线电参数测量仪器、光学与声学测量仪器、电离辐射计量仪器。

1-2 结合你对智能仪器概念的理解,讨论“智能化”的层次。

P2 智能仪器是计算机技术和测量仪器相结合的产物,是含有微型计算机或微处理器的测量(或检测)仪器。

由于它拥有对数据的存储、运算、逻辑判断及自动化操作等功能,具有一定智能的作用(表现为智能的延伸或加强等),因而被称为智能仪器。

P5- P6 智能仪器的四个层次:聪敏仪器、初级智能仪器、模型化仪器和高级智能仪器。

聪敏仪器类是以电子、传感、测量技术为基础(也可能计算机技术和信号处理技术)。

特点是通过巧妙的设计而获得某一有特色的功能。

初级智能仪器除了应用电子、传感、测量技术外,主要特点是应用了计算机及信号处理技术,这类仪器已具有了拟人的记忆、存储、运算、判断、简单决策等功能。

模型化仪器是在初级智能仪器的基础上应用了建模技术和方法,这类仪器可对被测对象状态或行为作出评估,可以建立对环境、干扰、仪器参数变化作出自适应反映的数学模型,并对测量误差(静态或动态误差)进行补偿。

高级智能仪器是智能仪器的最高级别,这类仪器多运用模糊判断、容错技术、传感融合、人工智能、专家系统等技术。

有较强的自适应、自学习、自组织、自决策、自推理能力。

1-3 仪器仪表的重要性体现在哪些方面?P3-5(1)仪器及检测技术已经成为促进当代生产的主流环节,仪器整体发展水平是国家综合国力的重要标志之一(2)先进的科学仪器设备既是知识创新和技术创新的前提,也是创新研究的主题内容之一和创新成就得重要体现形式,科学仪器的创新是知识创新和及时创新的组成部分。

基于FPGA和USB的高速数据实时采集系统的设计和实现

0 引言现代工业自动化的发展日新月异,各个领域对数据采集的质量和速度要求都在不断提高。

传统的数据采集设备多采用固定数据接口如USB、串口、网口、SPI 等,本系统中由于项目特殊需求,需要对高速IO 数据进行实时采集传输,所以不能采用传统的仅以DSP 或ARM 作为控制核心的系统设计[1]。

由于FPGA 具有时钟频率高、内部延时小、开发周期短、运算速度快、编程配置灵活、集成度高、功耗低、内部资源丰富等优点,所以本系统中加入了FPGA 芯片控制。

所以,本文设计了一种 FPGA+STM32+USB3300+上位机架构的高速IO 实时数据采集系统,当前硬件配置最高支持IO 的传输速率为30Mb/s,理论上该系统的速度仅受限于SPI实时分析处理。

1 系统原理及组成1.1 系统框架本系统总体架构如图1所示,主要包含FPGA 硬件缓冲及转换协议模块、STM32数据采集及传输模块、USB3300数据上传模块,上位机实时接收及存储模块。

1.2 系统工作原理系统上电后,用户打开上位机采集界面,启动采集,STM32收到命令以后,开始通过SPI 读取FPGA 数据;收到的数据满一包之后,STM32传输数据到USB3300芯片,该芯片通过USB 驱动上传数据给上位机,上位机监测到数据即读取芯片控制电路,STM32F407核心控制电路和USB3300传输通信电路。

FPGA 控制电路比较简单,因为其编程配置灵活,其大部分IO 口可以根据需要配置,在本系统中该芯片主要作用是IO 数据缓UARTetc. Therefore, the system is compatible with multi interface protocol, fast transmission speed, simple structure, real-time and high reliability. After many tests, it is proved that the system can be applied to high-speed data transmission and acquisition, and can meet the requirements of real-time data transmission.Keywords: FPGA ;STM32;USSB3300;USB ;multi interface protocol ;high-speed ;real-time2.2 STM32和USB3300原理图本系统中STM32及USB3300的电路设计都是采用的数据手册推荐设计,如下图3所示。

一种用于频率估算的USB3.0高速数据传输系统

一种用于频率估算的USB3.0高速数据传输系统

郝艳阳;苏淑靖;裴永浩;冯成林

【期刊名称】《电子器件》

【年(卷),期】2022(45)1

【摘要】针对振动分析和阵列信号处理等领域对高精度频率测量的需求,设计了一种可用于高精度频率估算的USB3.0高速数据传输系统。

该系统以FPGA为系统主控制器,以EZ_USB FX3为USB3.0外设控制器和传输媒介,FPGA内部的时序控制逻辑设计有效避免了对USB局部标志的使用,突破了水印值设置对数据传输速率的限制,最高传输速率可达193.9 Mbyte/s。

PC机端获取源频率数据后通过基于全相位时移相位差频谱校正法的估计算法进行高精度频率估计,其测算精度可达小数点后5位,对高精度频率测量系统的设计实现具有一定的工程应用价值。

【总页数】7页(P33-39)

【作者】郝艳阳;苏淑靖;裴永浩;冯成林

【作者单位】中北大学电子测试技术国家重点实验室

【正文语种】中文

【中图分类】TP301

【相关文献】

1.PET系统中基于USB3.0的高速数据传输

2.高速数据采集系统中USB

3.0数据传输接口设计3.基于 USB3.0的 EMCCD 相机高速数据传输系统的研究

4.基于

USB3.0高速图像数据传输系统设计5.一种适用于实时仿真系统中高速数据传输网络研究

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP和USB的数据采集系统的设计

De i n o t qu sto S s e s d o sg f Da a Ac iii n y t m Ba e n DSP n a d USB

Z HANG F n — n ,ZHO o fn a gf g a U Hu — g,S e ONG L — u ,R i g n n i i EN N n — i g h

0 引 言

在工业控制领域 , 常需要 采集大量 的现 场数据 , 统 的数 传 据采集系统 以工控机为核心 , 现场信号通过 数据采集模块输 入 工控机进行处理 , 整个 系统体积大 、 功耗高 。在环境 恶劣 、 电力 设施 缺乏 的地 区, 如海上 和西 部沙漠地 区的油 气开采 现场 , 传

( ot ol eo eigUnvri f h mi l eh o g , a ga g0 50 , hn ) N rhC l g f in iesyo e c c n l y L n fn 6 2 1 C ia e Bj t C aT o

Ab ta t aa a q ii o y tm s d sg e a e n D P,c n i e ig te d f in i si rd t n ld t c u st n s r c :A d t c u st n s se wa e i n d b s d o S i o sd r h ei e ce n ta i o a aa a q ii o n c i i s s m.T e s se s l ce 5 0 st e c r rc s o ,u e yt e h y tm ee td VC 4 2 a h oe p o e s r s d DMA o t ld t c u st n,t e t c n r aa a q i i o o io h n DMA a d t eCP o l n h U c u d

基于DSP的大功率超声电源的研制

基于DSP的大功率超声电源的研制Design of high power ultrasonic power supply based on DSP(江苏科技大学) 赵磊王建华刘建芸Zhao Lei , Wang Jianhua,Liu Jianyun 摘要:介绍了一种基于DSP的大功率超声电源的原理、总体结构和软硬件设计及其特点。

该电源由高频逆变电路和以高性能DSP芯片TMS320F2812为核心的控制系统组成。

高频逆变电路实现了频率和功率均可调的超声频交流电的输出。

控制系统完成了电参数的实时采集,并执行频率自动跟踪和振幅恒定的控制任务。

软件上,分别使用了可变步长策略和PID算法,以满足上述两个闭环控制的需要。

实验表明,该电源能够很好地驱动超声振动负载,并具有频率跟踪范围宽和负载适应能力强的特点。

关键词:超声电源;频率跟踪;恒幅输出;DSP中图分类号:TN409 文献标识码:BABSTRACT:The principles, design method and characteristics of high power ultrasonic power supply based on DSP are presented in the paper. This device consists of inverter major circuit and control system based on TMS320F2812. The main circuit produces power supersonic AC output with adjustable frequency and changeable power. Control system is responsible for the real -time electrical data acquisition,and it also performs the control of frequency auto-tracking and constant output specific power.In software,variable step strategy and PID are applied to meet the need of above two closed-loop controls. Tests show that this power supply can effectively drive ultrasonic load,and it has a wide range of frequency tracking and high load flexibility.Key words:Ultrasonic Power Supply;frequency tracking;constant output specific power;DSP1、引言近些年,随着机械振动、电力电子技术的飞速发展,功率超声的应用愈来愈广泛,对功率超声电源的研制也提出了越来越高的要求。

基于嵌入式处理器的高精度数据采集系统的设计

基于嵌入式处理器的高精度数据采集系统的设计卢贶【摘要】本文介绍了一种基于ARM处理器的高精度、多通道数据采集系统设计和实现.介绍基于ARM内核的STM32处理器和16位高精度ADC976模数转换芯片电路,以及在液晶显示器上显示采集的数据图形,详细说明了系统的组成原理、主要电路模块设计和系统软件设计.【期刊名称】《武汉船舶职业技术学院学报》【年(卷),期】2018(000)003【总页数】5页(P39-42,53)【关键词】STM32;高精度;数据采集【作者】卢贶【作者单位】武汉软件工程职业学院,湖北武汉 430205【正文语种】中文【中图分类】TP274基于ARM内核的STM32处理器在国内系统设计中得到了较广泛的使用,在各种控制系统设计中,都会见到它的身影。

本设计基于意法半导体公司的微处理器,配合ADI公司的模数转换芯片ADC976,设计了多通道的数据采集系统,经过实际应用,可靠性高,能实现设计所要求的性能。

1 总体设计本设计以STM32F103R8T6处理器数据采集系统主控制器,采用输入光耦隔离,输出继电器隔离,实现8路PLC控制器,具有RS232/RS485通讯接口,实现梯形图下载指令程序。

控制结构可靠,抗通讯干扰能力强,运行稳定。

可运用于工业控制设备机器程序化运行,利于工业现场安装。

系统总体设计框图如图1所示。

图1 系统总体设计框图2 硬件设计处理器外围电路由STM32F103R8T6最小系统和外设组成,STM32F103R8T6最小系统包含电源模块、时钟和复位电路、存储系统(ROM、RAM、Flash),外设包含USB、结构框图如图2。

图2 硬件电路结构框图2.1 主处理器介绍本设计采用超低功耗芯片STM32F103R8T6为主处理器,从整个系统的性价比及功能需求方面来看,STM32处理器是合适的选择。

STM32F103R8T6处理器是CM3架构,性能强,稳定可靠,内部有20K的闪存、64K FLASH、51个通用IO 端口、3路UART的单片机,中心控制模块采用STM32F103R8T6单片机已完全满足设计需要,实现整个PLC系统控制[2]。

5 Gsps高速数据采集系统的设计与实现

5 Gsps 高速数据采集系统的设计与实现摘要:以某高速实时频谱仪为应用背景,论述了5 Gsps 采样率的高速数据采集系统的构成和设计要点,着重分析了采集系统的关键部分高速ADC(analog to digital,模数转换器)的设计、系统采样时钟设计、模数混合信号完整性设计、电磁兼容性设计和基于总线和接口标准(PCI Express)的数据传输和处理软件设计。

在实现了系统硬件的基础上,采用Xilinx 公司ISE 软件的在线逻辑分析仪(ChipScope Pro)测试了ADC 和采样时钟的性能,实测表明整体指标达到设计要求。

给出上位机对采集数据进行处理的结果,表明系统实现了数据的实时采集存储功能。

关键词:高速数据采集;高速ADC;FPGA;PCI Express 高速实时频谱仪是对实时采集的数据进行频谱分析,要达到这样的目的,对数据采集系统的采样精度、采样率和存储量等指标提出了更高的要求。

而在高速数据采集系统中,ADC 在很大程度上决定了系统的整体性能,而它们的性能又受到时钟质量的影响。

为满足系统对高速ADC 采样精度、采样率的要求,本设计中提出一种新的解决方案,采用型号为EV8AQ160 的高速ADC 对数据进行采样;考虑到ADC 对高质量、低抖动、低相位噪声的采样时钟的要求,采用AD9520 为5 Gsps 数据采集系统提供采样时钟。

为保证系统的稳定性,对模数混合信号完整性和电磁兼容性进行了分析。

对ADC 和时钟性能进行测试,并给出上位机数据显示结果,实测表明该系统实现了数据的高速采集、存储和实时后处理。

1 系统的构成高速数据采集系统主要包括模拟信号调理电路、高速ADC、高速时钟电路、大容量数据缓存、系统时序及控制逻辑电路和计算机接口电路等。

图1 所示为5 Gsps 高速数据采集系统的原理框图。

所用ADC 型号为EV8AQ160,8 bit 采样精度,内部集成4 路ADC,最高采样率达5 Gsps,可以工作在多种模式下。

USB DATA

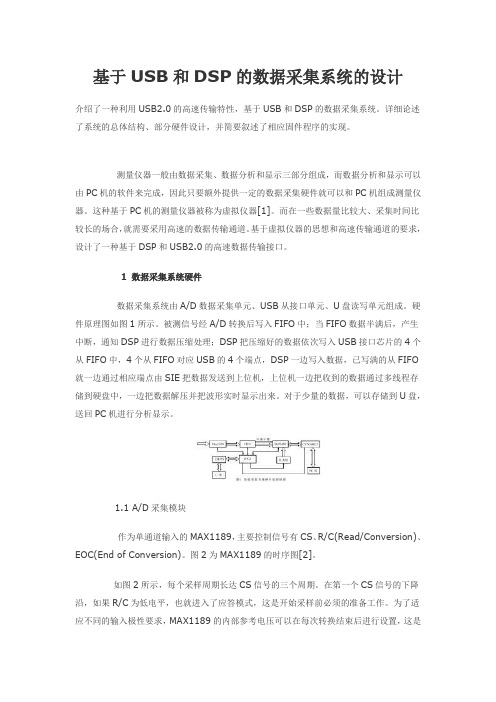

基于USB和DSP的数据采集系统的设计介绍了一种利用USB2.0的高速传输特性,基于USB和DSP的数据采集系统。

详细论述了系统的总体结构、部分硬件设计,并简要叙述了相应固件程序的实现。

测量仪器一般由数据采集、数据分析和显示三部分组成,而数据分析和显示可以由PC机的软件来完成,因此只要额外提供一定的数据采集硬件就可以和PC机组成测量仪器。

这种基于PC机的测量仪器被称为虚拟仪器[1]。

而在一些数据量比较大、采集时间比较长的场合,就需要采用高速的数据传输通道。

基于虚拟仪器的思想和高速传输通道的要求,设计了一种基于DSP和USB2.0的高速数据传输接口。

1 数据采集系统硬件数据采集系统由A/D数据采集单元、USB从接口单元、U盘读写单元组成。

硬件原理图如图1所示。

被测信号经A/D转换后写入FIFO中;当FIFO数据半满后,产生中断,通知DSP进行数据压缩处理;DSP把压缩好的数据依次写入USB接口芯片的4个从FIFO中,4个从FIFO对应USB的4个端点,DSP一边写入数据,已写满的从FIFO 就一边通过相应端点由SIE把数据发送到上位机,上位机一边把收到的数据通过多线程存储到硬盘中,一边把数据解压并把波形实时显示出来。

对于少量的数据,可以存储到U盘,送回PC机进行分析显示。

1.1 A/D采集模块作为单通道输入的MAX1189,主要控制信号有CS、R/C(Read/Conversion)、EOC(End of Conversion)。

图2为MAX1189的时序图[2]。

如图2所示,每个采样周期长达CS信号的三个周期。

在第一个CS信号的下降沿,如果R/C为低电平,也就进入了应答模式,这是开始采样前必须的准备工作。

为了适应不同的输入极性要求,MAX1189的内部参考电压可以在每次转换结束后进行设置,这是通过在第二个CS下降沿时,R/C的高低电平变化来控制的,非常简便。

低电平时,ADC 内部参考电压无需进行转换,这样在开始下一个周期的转换时无需等待电压的变化。

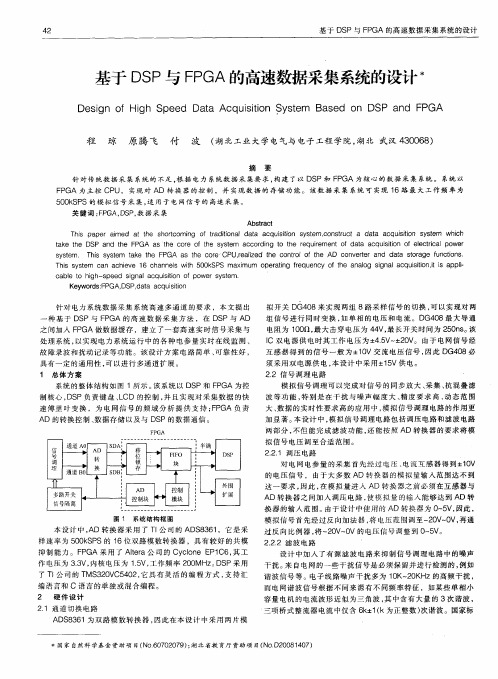

基于DSP与FPGA的高速数据采集系统的设计

拟开关 D 0 G4 8来 实 现 两 组 8路 采样 信 号 的切 换 , 以 实现 对 两 可 组信号进行同时变换 , 如单 相 的 电压 和 电流 。D 0 G4 8最 大 导 通

电阻 为 1 0 最 大 击 穿 电压 为 4 V, 长 开 关 时 间为 2 0 s 该 O Q, 4 最 5 n。

.

程 琼 原腾 飞 付 波 ( 湖北工业大学电气与电子工程学院, 湖北 武汉 4 0 6 ) 3 0 8

摘 要

针 对传 统 数 据 采 集 系统 的 不 足 , 据 电 力 系统 数 据 采 集要 求 , 建 了 以 D P和 F G 为核 心 的数 据 采 集 系统 。 系统 以 根 构 S P A F G 为 主 控 CP P A U, 实现 对 AD 转换 器 的 控 制 ,并 实现 数 据 的存 储 功 能 。 该数 据 采 集 系统 可 实现 1 6路 最 大 工作 频 率 为

4 2

基 于 DS P与 F GA 的高 速 数据 A的高速数据采集系统的设计

y t m B s d n DSP a d P a e o n F GA De i f Hi p e t qust n S se sgn o gh S e d Da a Ac iio i

5 0 SP 0 k S的模 拟信 号采 集 , 用于 电网信 号 的 高速 采 集 。 适 关 键 词 :P F GA, S 数 据采 集 D P,

Ab ta t sr c T s hi pa r i pe amed at h s or om ig of r dion l te h t c n ta t a daa c i t a quiio s sem , nsr t d a st n y t i co tuc a at ac iion y e qust s stm whih i c

基于集成电路的高速数据采集系统设计与实现

基于集成电路的高速数据采集系统设计与实现近年来,随着计算机和通信技术的迅速发展,各种数据采集系统已成为现代工业生产和科学研究的重要组成部分。

而在数据采集系统中,高速数据采集系统则备受瞩目。

本文将介绍一种基于集成电路的高速数据采集系统的设计和实现方法,为读者深入了解和掌握该技术提供一个参考。

一、高速数据采集系统的特点高速数据采集系统最为显著的特点是采样速度快,高精度,可实现实时采集和处理。

同时,该系统的数据存储量大,处理速度快,可用于高速数据的传输、处理和存储。

二、基于集成电路的高速数据采集系统的设计原理该高速数据采集系统主要由采样模块、控制处理模块、数据存储模块和接口模块四个部分组成。

其中,采样模块主要负责采集数据;控制处理模块负责控制采集系统参数和实现数据处理;数据存储模块主要用于存储采集的各种数据;接口模块用于实现采集系统与计算机之间的数据传输。

在设计过程中,需要通过适当的硬件设计和软件开发,使得各个模块之间能够良好地协同工作。

具体来说,需要采用高速A/D转换芯片和高速的数据总线技术,实现高速、精准的信号采集和快速的数据传输和处理。

同时,在控制处理模块中,需要引入专业的数据处理算法和控制策略,从而实现高效、准确的数据处理。

三、高速数据采集系统的实现方法基于集成电路的高速数据采集系统的实现方法有以下几个步骤:1. 确定采集数据的类型和采样速度。

根据实际需求,确定采集数据的类型和采样速度,以满足需要的数据精度和采集效率。

2. 选定高速A/D转换芯片和适配器。

根据采集数据类型和采样速度,选择合适的A/D转换芯片和适配器,以保证数据的精度和采样速度。

3. 设计高速数据采集系统的硬件。

根据数据采集的需求,设计高速数据采集系统的硬件,包括电源、采样模块、控制处理模块、数据存储模块和接口模块等。

4. 开发采集系统的软件。

通过开发采集系统的软件,实现数据采集和处理控制等功能,以满足具体数据采集的需求。

5. 测试数据采集系统的性能。

基于DSP的音频信号处理与放大系统设计(毕业设计)

基于DSP的音频信号处理与放大系统设计一、前言数字信号处理(DSP)技术在音频处理中得到了广泛的应用。

本文旨在设计一个基于DSP的音频信号处理与放大系统,实现对音频信号的处理、调节和放大。

该系统采用了TMS320C6713 DSP芯片作为核心处理器,能够实现高效率、高精度的数字信号处理。

本文将从系统设计的需求出发,分析系统架构、设计参数、算法实现和系统性能等方面进行详细阐述。

二、系统需求分析输入/输出该系统的输入为音频信号,一般来自音频采集器、CD、MP3等设备。

输出为音频放大信号,一般连接至功放、扬声器等设备。

为保证音频信号质量,系统应具有输入阻抗高、噪声低、失真小的特点。

放大输出信号应具有高保真度、低失真度、大输出功率等特点。

系统性能该系统应满足以下要求:(1)输入阻抗:> 10kΩ(2)噪声:< 0.1mV(3)失真:< 0.1%(4)输出功率:> 50W(5)频率响应:20Hz-20kHz(6)信噪比:> 90dB(7)总谐波失真:< 0.5%系统算法系统应支持以下算法:(1)音频采集(2)滤波处理(3)音量调节(4)均衡器(5)混响效果三、系统设计系统架构该系统采用了TMS320C6713 DSP芯片作为核心处理器,外围连接音频采集器、音频处理器、音频放大器等模块。

系统框图如下所示:+--------+ +--------+ +--------+|音频采集器|------->| DSP芯片|------->| 音频放大器|+--------+ +--------+ +--------+|+--------+| 音频处理器|+--------+系统参数(1)输入阻抗:系统采用运放作为输入级,输入阻抗可达到10MΩ以上。

(2)噪声:系统采用低噪声运放,噪声可控制在0.1mV以下。

(3)失真:系统采用高精度ADC/DAC芯片和高质量音频放大器,失真可控制在0.1%以下。

北京理工大学检测与控制研究所2020年度进展

院企风采NRfl北京理工大学检测与控制研究所---------------2020年度进展------------北京理工大学检测与控制研究所以北京理工大学一级国家重点学科(机械工程)和部级重点实验室(先进加工技术国防重点学科实验室)为依托,多年来一直从事无损检测与控制理论与技术的教学和科研工作。

研究所主要面向国防科技工业和国民经济发展的前沿及生产需求,重点开展残余应力超声无损检测与调控技术、(单双)机械手超声检测技术、超声显微扫查检测技术、复杂回转类零件激光测量技术、材料弹性参数与涂层厚度测量技术、机器 视觉检测技术等研究工作。

研究所现有教职工10人,其中博导教授1人、副教 授5人、高级实验师1人、技师3人,在读博士研究生12名,在读硕士研究生30余名。

实验室面积400余平 方米,拥有残余应力超声检测与高能声束调控系统、高频超声显微镜、(单双)机械手超声自动检测系统、嗦栓紧固应力检测系统等多种检测设备。

一年来,研究所承担和完成了国家自然基金重点项目、装备预先研究、国防基础科研、企业横向等科研顶目,取得了多顶科研成果。

本年 度共获授权专利11顶,专著2部,牵头制定国家标准3顶,EI收录论文7篇,SCI收录论文4篇。

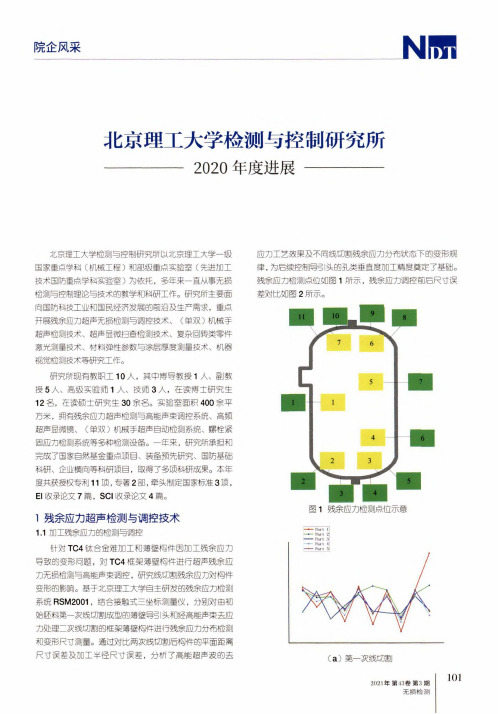

1残余应力超声检测与调控技术1.1加工残余应力的检测与调控针对TC4钛合金难加工和薄壁构件因加工残余应力导致的变形问题,对TC4框架薄壁构件进行超声残余应力无损检测与高能声束调控,研究线切割残余应力对构件变形的影响。

基于北京理工大学自主研发的残余应力检测系统RSM2001,结合接触式三坐标测量仪,分别对由初始胚料第一次线切割成型的薄壁导引头和经高能声束去应力处理二次线切割的框架薄壁构件进行残余应力分布检测和变形尺寸测量。

通过对比两次线切割后构件的平面距离尺寸误差及加工半径尺寸误差,分析了高能超声波的去应力工艺效果及不同线切割残余应力分布状态下的变形规律,为后续控制导引头的孔类垂直度加工精度奠定了基础。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

超声医学即利用超声波的物理特性进行诊断和治疗的一门影像学科,其临床应用范围广泛,目前已成为现代临床医学中不可缺少的诊断方法。 本系统是一个便携式软组织超声诊断仪的一部分,主要功能是高频超声信号采集。其工作机制,是在前端低频脉冲(20Hz~10KHz)的触发下,对由超声换能器产生的高频超声信号(1MHz~20MHz)进行采集,预处理,然后通过USB总线传输给PC机,由软件进行分析、处理。 在本设计方案中,高速CPLD芯片作为数据采集系统的核心部分,相比传统的MCU+ADC方法,CPLD是用硬件信号而不是软件编程来控制ADC,从而在速度上有很大的优势。而目前强大的VHDL编程语言也使得CPLD能很容易地实现预想的功能逻辑。数据处理部分,选用数据处理功能强大、处理速度高的DSP芯片作为CPU。而在与上位机通信方面,采用支持即插即用且成本也相对较低的USB接口。整体系统方面,各个子系统之间的数据传输和同步问题是技术难点。在经过反复比较和测试之后,采取高速存储器作为数据缓冲区的方案。 系统各组成模块 包括三个子系统:CPLD子系统,DSP子系统和USB子系统。其中,CPLD+ADC实现数据采集,DSP则负责数据处理,两者之间通过一片高速RAM来交换数据;USB芯片(AN2131Q)负责把数据通过USB线上传给主机,它和DSP之间通过一片锁存器进行通信。 数据采集子系统(CPLD子系统) 该子系统主要由一片Altera公司的CPLD和一片高速ADC所组成。 由于要采集的超声信号最高频率为20M,根据Nyquist定律,采样频率应该在40MHz以上,为了提高精度,系统采用了ADI公司的AD9283芯片。该芯片最高工作频率为100MHz,经过测试,可很好地满足系统带宽要求。 以往的便携式数据采集系统中,下位机部分ADC-RAM模块往往采用MCU作为CPU来控制,因此,采集频率直接受到MCU速度的制约,而且和RAM存储器的同步也成为问题。经过比较,本系统采用Altera公司的CPLD芯片来控制ADC和RAM,从而很好地解决了时序精度和同步的问题。 CPLD作为控制芯片,实现的功能逻辑为: ● 接到DSP触发信号(START)之后,实现对ADC的控制,发出一个Start信号,ADC开始采样工作; ● 与ADC控制信号同步提供RAM地址计数器(A0~A16)和写信号(/WE),使得每次ADC的结果直接存入RAM并且自动增加地址; ● 当地址计数器达到最大的时候,发出中断信号(RAM_FULL),提示DSP系统RAM已满; CPLD的功能逻辑用VHDL语言实现,其编译、仿真和综合采用Altera官方主页提供的MAXPLUXII Student10.1版,下载电缆自制。 数据处理子系统(DSP子系统) 由于系统在后期升级中,要求对下位机部分的数据进行较为复杂的预处理,同时系统在实时性方面要求较高。因此选用TI公司的TMS320C5409作为数据处理子系统的CPU。 DSP子系统的主要工作流程为: 1) 接到Trigger(由前端换能模块发出)中断(INT0)触发后,拉高START信号通知信号采集模块开始工作,然后进入等待; 2) 接到RAM_FULL中断(INT1)之后,知道RAM已经写满,首先将START信号拉低停止CPLD和ADC。然后开始逐个读RAM中的数据,根据系统要求做相应处理,之后借助锁存器发给AN2131Q; 3) 在本系统中,DSP软件部分的几个函数体包括:主循环;int0中断(前端触发);int1中断(RAM已满)。 通信接口子系统(USB子系统) 该子系统完成的功能,就是通过锁存器接收DSP发过来的数据,然后通过自身的USB控制器嵌入式系统是计算机技术、通信技术、半导体技术、微电子技术、语音图像数据传输技术,甚至传感器等先进技术和具体应用对象相结合后的更新换代产品,反映当代最新技术的先进水平。嵌入式系统是当今非常热门的研究领域,在PC市场已趋于稳定的今天,嵌入式系统市场的发展速度却正在加快。由于嵌入式系统所依托的软硬件技术得到了快速发展,因此嵌入式系统自身获得了快速发展。根据美国嵌入式系统专业杂志RTC报道,在21世纪初的10年中,全球嵌入式系统市场需求量具有比PC市场大10~100倍的商机。有机构估计,全世界嵌入式系统产品潜在的市场将超过1万亿美元。随着技术技术和各种具体的行业应用技术相结合的结果,其中各种软件技术占了嵌入式系统80%的工作量。嵌入式系统不同于一般PC 机上的应用系统,即使是针对不同的具体应用而设计的嵌入式系统之间的差别也很大。嵌入式系统一般功能单一、简单,且在兼容性方面要求不高,但是在大小、成本方面限制较多。可以说,嵌入式系统是不可垄断、需要不断创新的技术。 嵌入式系统历史及发展趋势 事实上,在很早以前,嵌入式这个概念就已经存在了。在通信方面,嵌入式系统在20世纪60年代就用于对电子机械