跨越鸿沟:同步世界中的异步信号

疫情之下,5G等成填补数字鸿沟关键技术阅读答案语文

疫情之下,5G等成填补数字鸿沟关键技术阅读答案语文阅读下面文章,完成问题。

疫情之下,5G等成填补数字鸿沟关键技术张佳欣2020年,世界以更快的速度迎来了数字化转型,重新塑造了技术在我们工作、学习和生活方式中的关键作用。

新冠疫情大流行揭示了一个长期存在的问题:数十亿人仍然没享有上网这一普遍的权利。

事实表明,在疫情“封锁”期间没有互联网接入的穷人正进一步被边缘化。

根据美国联邦通信委员会的调查数据,97%的美国人在城市地区可以获得高速、稳定的连接服务。

在农村这一数字下降到65%-60%。

总体而言,近3000万美国人无法充分受益于数字时代。

根据国际电信联盟的一份报告,在全球范围内,发达国家互联网普及率为87%,发展中国家只有47%,不发达国家只有19%。

大流行期间的远程学习远未普及,被定义为“贫穷”的中小学生(在美国的K-12义务教育体系下)正遭受数字鸿沟之苦。

美国国家教育统计中心的一项研究表明,贫困学生不太可能拥有上网络学校所需的设备;7%的贫困八年级学生没有互联网接入,而非贫困学生的这一比例仅为1.6%。

如果没有可靠的互联网,这些经济不平等将继续加剧。

疫情期间的封锁措施使得许多关键活动转移到了网上,同时也使低收入人群更加难以上网。

凯捷首席运营官艾曼•埃扎特说:互联网已经成为一项基本需求。

它不再是可有可无。

在第一份5G展望系列的报告中,世界经济论坛谈到了移动技术在疫情中发挥的作用:在医疗保健中,提高远程医疗急诊就诊次数490%;在社交活动中,在线游戏增长了75%;在零售方面,全球在线交易量增长了74%。

4G和5G则是背后的技术支撑力量。

去年9月,欧盟委员会明确指出,无论是交通和能源、医疗保健和教育,还是制造业和农业,宽带和5G都为经济的绿色和数字化转型奠定了基础。

因此,没有强大互联网接入的人在学术和经济上都被甩在了后面,全民互联网连接便成为了公平社会的关键组成部分无线技术不再只是对消费者和娱乐很重要;从智能家居系统到自动驾驶汽车,它正迅速成为我们如何连接数字世界中一切事物的关键。

12月 第二期 PPT 跨越鸿沟:大数据从技术到商业价值-东软集团刘长虹

外部数据 精准 营销

业务数据

个性化 推荐

Engine

知识图谱

用户行 为分析

市场

销售

意见挖掘

兴趣发现

用户画像

全站推荐

客户发现

交叉销售

邮件推荐

移动推荐

渠道整合

业务视图

智慧商务的价值

一张一错再错的机票

智慧商务改进点 1. 预订票时,根据LBS 信息第一次校验。 2. 发送确认短信时,根 据上下文交易数据第 二次校验。 3. Call Center接访时, 给予减免,提高客户 满意度、忠诚度。 智慧商务特性 业务(客户) 人性化的 适时的 超出期望的 技术角度 情景感知 实时分析 融合数据

持续计算

消息队列

(点击流数据)

用户关注热点 转化率统计 网页停留时间

内容信息 元数据 交易信息

领域本体库 兴趣图谱库 标签库

Bolt Bolt Bolt 数据转化

Bolt

预测模型 统计模型 分类模型 关联网络

自然语言 中文分词 特征值提取 潜在语义网

文本挖掘 文本虑重 情感分析 标签传播

分类算法 支持向量机 朴素贝叶斯 极限学习机

开发新产品和服务 企业借助数据获取洞 见,支持日常业务, 以服务于现有市场和 客户。瞄准新市场, 创新和设计全新的业 务模式。

数据生态系统视野 企业可以从生态系统 中的其他企业处获得 补充数据。这种生态 系统以适当的合作战 略为基础。

SaCa RealRec 大数据产品实践

Secure Social Active Connected Cloud with Awareness

通过互动社区与学生、 家长交流,答疑解惑、 关爱学生。 从大量数据中感知学生 的知识欠缺,提供实时 的学习建议及内容推荐。

cpu与fpga跨时钟域数据交换的实现问题

munitis#1楼主:cpu与fpga跨时钟域数据交换的实现问题[精华]ARM与fpga(cyclone)之间进行数据传输,这应该属于跨时钟域的范畴,CPU与fpga之间采用三总线的方式进行连接,而CPU连接fpga的数据线、地址线、控制线进入fpga内部就属于异步信号了,该如何考虑呢?我看过一些关于跨时钟域的文献,上面说对于数据交换,实现方法有握手和fifo两种,我想,双口RAM是不是也算一种?另外,我看跨时钟域数据交换,都涉及到两侧的时钟信号,而对于CPU的三总线,并没有输出什么时钟信号,时钟输出是不是必须的呢?问题比较多,不知道说明白没有,请指教一二,谢谢了!riple #2这个问题,基本上很难。

开个玩笑,原理上简单,实现起来有许多要注意的地方,但是不难。

一个提示:从你使用的ARM芯片数据手册的接口时序图入手。

FPGA中的处理方法是可以改的,而接口时序是一定要遵守的。

泛泛而谈很难,把你的芯片接口时序图贴上来吧,主要是寄存器读、写时序,如果用到DMA的话,应该还有DMA读写的时序图。

munitis #3上面是ARM读写外设的时序图,时钟是CPU的,和fpga的内部时钟是两个时钟域,既需要有ARM写入给fpga 内部的寄存器,又需要有ARM读出fpga内部的值,该如何解决跨时钟域的问题呢?munitis #4ARM与fpga的接口是标准的总线型接口,包括DATA,CS,ADDR,RD,WR,这些信号由CPU的时钟控制,对于FPGA来说是异步信号,在进入FPGA内部是不是需要先进行同步,我看过一些文献,这种总线型的跨时钟域,是不能用多个同步器进行同步的,采用的方法有握手信号和FIFO,是不是这样的呢?riple #5我们一步一步来,先实现基本功能,然后优化性能。

第一、我觉得处理这样的接口,采用异步方式比较好。

因为同步接口对FPGA外部电路和内部配置的要求都比较高。

异步接口只要给出充分的时间,外部电路不存在信号完整性问题就很好解决。

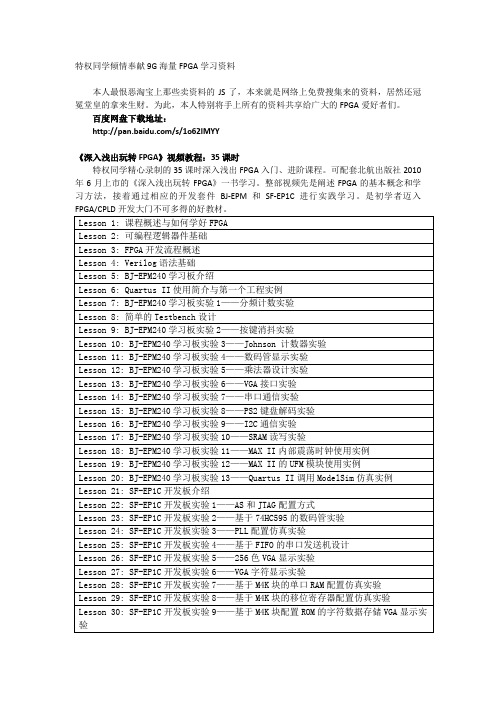

特权同学倾情奉献9G海量FPGA学习资料

特权同学倾情奉献9G海量FPGA学习资料

本人最恨恶淘宝上那些卖资料的JS了,本来就是网络上免费搜集来的资料,居然还冠冕堂皇的拿来生财。

为此,本人特别将手上所有的资料共享给广大的FPGA爱好者们。

百度网盘下载地址:

/s/1o62lMYY

《深入浅出玩转FPGA》视频教程:35课时

特权同学精心录制的35课时深入浅出FPGA入门、进阶课程。

可配套北航出版社2010年6月上市的《深入浅出玩转FPGA》一书学习。

整部视频先是阐述FPGA的基本概念和学习方法,接着通过相应的开发套件BJ-EPM和SF-EP1C进行实践学习。

是初学者迈入

《特权和你一起学NIOS2》视频教程:20课时

特权同学的又一力作,SOPC的设计与底层逻辑设计不同,这部教程完全以另一种方式带领初学者领悟基于FPGA的嵌入式系统设计,同时也希望借助本教程能使大家熟悉在EDS 软件平台上实现NIOS2的编程和开发。

与本视频完全配套同步的图书《爱上FPGA开发——

Altera官方专题视频教程:38课时

特权fpga技术公开课

Altera官方资料(各类手册和应用笔记)(略)

百度网盘下载地址:

/s/1o62lMYY。

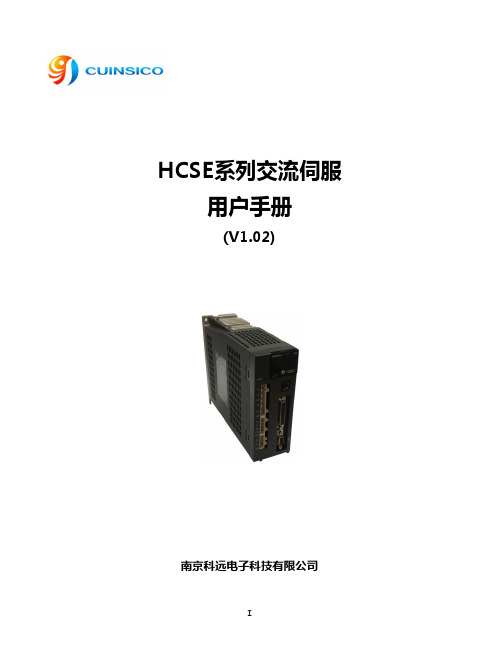

南京科远HCSE系列交流伺服用户手册(V1.02)

若在电源和伺服驱动器输入端之间加装接触器,则不允许用此接触器来控制伺服驱动器的启停。一定需要用该接触器控制 伺服驱动器的启停时,间隔不要小于一个小时。频繁的充放电易降低伺服驱动器内电容的寿命。若输出端和电机之间装有接触 器等开关器件,应确保伺服驱动器在无输出时进行通断操作,否则易造成伺服驱动器内模块损坏。 ■ 三相输入改成两相输入

HCSE系列交流伺服 用户手册

(V1.02)

南京科远电子科技有限公司

I

电机机型设置

用户拿到伺服驱动器和电机第一次运行时,请参照适配机型表(如果适配机型表中没有对 应的电机型号,请根据所用电机的额定转速和额定电流,来选择电机机型),确认电机机型设 置是否正确,如果不正确,运行时电机可能会出现振动或误报警现象,不能达到期望的控制效 果。机型参数为Pn223,属于隐藏参数,需要解锁方能进入,在数码管为“run”、”bb”或报 警状态显示界面下,按“上下下下”(一次UP键,三次DOWN键)即可解锁。机型设置正确后, 需重新上电,方可运行电机。以后如果电机型号有变动,则需重新设置。

1314面板按键操作说明1441按键的名称与功能1442基本模式的选择与操作1543状态显示16431位数据显示内容16432省略符号显示内容1644辅助功能模式下的操作fn17441辅助功能执行模式的用户参数一览及其功能17442显示伺服报警记录18443微动jog模式运行18444用户参数设定值进行初始化1945用户参数设定模式下的操作pn20451用户参数的设定2046监视模式下的操作un21461监视模式一览及其功能21462顺序用输入输出信号的监视显示22463指令脉冲计数器反馈脉冲计数器的监视显示2451试运行2452通用功能的设定25521伺服on设定25522超程设定25523伺服off时的停止方法选择2553位置控制运行25531用户参数的设定26532电子齿轮的设定27533编码器反馈信号输出分频系数27534位置指令28535平滑29537外部扭矩限制3054其他31541旋转检测速度31542超速报警功能31543数字输入接脚di输入滤波使能31544伺服控制信号输入input管脚功能配置

海量FPGA资料下载链接

开发套件SF-EP1C FPGA开发套件相关例程和文档/lib/detail.aspx?id=88172 /lib/detail.aspx?id=88173 /lib/detail.aspx?id=88174 /lib/detail.aspx?id=88175 /lib/detail.aspx?id=88176 /lib/detail.aspx?id=88177 /lib/detail.aspx?id=88178 /lib/detail.aspx?id=88179 /lib/detail.aspx?id=88180 /lib/detail.aspx?id=88181 /lib/detail.aspx?id=88182 /lib/detail.aspx?id=88183 /lib/detail.aspx?id=88184 /lib/detail.aspx?id=88185 /lib/detail.aspx?id=88186 /lib/detail.aspx?id=88187 /lib/detail.aspx?id=88188 /lib/detail.aspx?id=88189 /lib/detail.aspx?id=88190/lib/detail.aspx?id=88191/lib/detail.aspx?id=88192 /lib/detail.aspx?id=88193 /lib/detail.aspx?id=88194 /lib/detail.aspx?id=88195 /lib/detail.aspx?id=88196 /lib/detail.aspx?id=88197 /lib/detail.aspx?id=88198 /lib/detail.aspx?id=88199/lib/detail.aspx?id=88200/lib/detail.aspx?id=88201 /lib/detail.aspx?id=88202 /lib/detail.aspx?id=88203 /lib/detail.aspx?id=88204 /lib/detail.aspx?id=88205 /lib/detail.aspx?id=88206 /lib/detail.aspx?id=88207 /lib/detail.aspx?id=88208 /lib/detail.aspx?id=88209 /lib/detail.aspx?id=88210 /lib/detail.aspx?id=88211 /lib/detail.aspx?id=88212 /lib/detail.aspx?id=88213 /lib/detail.aspx?id=88214 /lib/detail.aspx?id=88215 /lib/detail.aspx?id=88216 /lib/detail.aspx?id=88217 /lib/detail.aspx?id=88218 /lib/detail.aspx?id=88219 /lib/detail.aspx?id=88220 /lib/detail.aspx?id=88221/lib/detail.aspx?id=88223 /lib/detail.aspx?id=88224 /lib/detail.aspx?id=88225 /lib/detail.aspx?id=88226 /lib/detail.aspx?id=88227 /lib/detail.aspx?id=88228 /lib/detail.aspx?id=88229 /lib/detail.aspx?id=88230 /lib/detail.aspx?id=88231 /lib/detail.aspx?id=88232 /lib/detail.aspx?id=88233 /lib/detail.aspx?id=88234 /lib/detail.aspx?id=88235 /lib/detail.aspx?id=88236 /lib/detail.aspx?id=88237 /lib/detail.aspx?id=88238 /lib/detail.aspx?id=88239 /lib/detail.aspx?id=88240 /lib/detail.aspx?id=88241 /lib/detail.aspx?id=88242 /lib/detail.aspx?id=88243 /lib/detail.aspx?id=88244 /lib/detail.aspx?id=88245 /lib/detail.aspx?id=88246 /lib/detail.aspx?id=88247 /lib/detail.aspx?id=88248 /lib/detail.aspx?id=88249 /lib/detail.aspx?id=88250 /lib/detail.aspx?id=88251 /lib/detail.aspx?id=88252 /lib/detail.aspx?id=88253 /lib/detail.aspx?id=88254/lib/detail.aspx?id=88255/lib/detail.aspx?id=88256 /lib/detail.aspx?id=88257 /lib/detail.aspx?id=88258 /lib/detail.aspx?id=88259 /lib/detail.aspx?id=88260 /lib/detail.aspx?id=88261/lib/detail.aspx?id=88262/lib/detail.aspx?id=88263 /lib/detail.aspx?id=88264 /lib/detail.aspx?id=88265/lib/detail.aspx?id=88111 /lib/detail.aspx?id=88112 /lib/detail.aspx?id=88113 /lib/detail.aspx?id=88114 /lib/detail.aspx?id=88115 /lib/detail.aspx?id=88116 /lib/detail.aspx?id=88117 /lib/detail.aspx?id=88118 /lib/detail.aspx?id=88119 /lib/detail.aspx?id=88120 /lib/detail.aspx?id=88121无无/lib/detail.aspx?id=88122 /lib/detail.aspx?id=88123 /lib/detail.aspx?id=88124 /lib/detail.aspx?id=88125 /lib/detail.aspx?id=88126 /lib/detail.aspx?id=88127 /lib/detail.aspx?id=88128 /lib/detail.aspx?id=88129 /lib/detail.aspx?id=88130 /lib/detail.aspx?id=88131 /lib/detail.aspx?id=88132 /lib/detail.aspx?id=88133 /lib/detail.aspx?id=88134 /lib/detail.aspx?id=88135 /lib/detail.aspx?id=88136 /lib/detail.aspx?id=88137 /lib/detail.aspx?id=88138 /lib/detail.aspx?id=88139 /lib/detail.aspx?id=88140 /lib/detail.aspx?id=88141/lib/detail.aspx?id=88145 /lib/detail.aspx?id=88146 /lib/detail.aspx?id=88147 /lib/detail.aspx?id=88148 /lib/detail.aspx?id=88149 /lib/detail.aspx?id=88150 /lib/detail.aspx?id=88151 /lib/detail.aspx?id=88152 /lib/detail.aspx?id=88153 /lib/detail.aspx?id=88154 /lib/detail.aspx?id=88155 /lib/detail.aspx?id=88156 /lib/detail.aspx?id=88157 /lib/detail.aspx?id=88158 /lib/detail.aspx?id=88159 /lib/detail.aspx?id=88160 /lib/detail.aspx?id=88161 /lib/detail.aspx?id=88162 /lib/detail.aspx?id=88163 /lib/detail.aspx?id=88164 /lib/detail.aspx?id=88165。

2024年全球数字化不平等与数字鸿沟

农业领域:数字化 应用滞后,生产效 率较低

教育行业:在线教 育普及,数字化提 升教学效果

医疗健康:数字化 技术提升医疗水平 和服务质量

不同地区间的数字化差距

发达国家与发展 中国家在数字化 发展水平上存在 显著差异

数字鸿沟在不同 地区间呈现出明 显的南北差异

发达国家在数字 化技术应用、基 础设施建设和创 新能力方面具有 明显优势

机遇

社会公平:数字 鸿沟加剧了信息 富集和贫困地区 的差距,影响社

会公平和稳定

教育资源:数字 鸿沟使得部分地 区和家庭的孩子 无法获得优质的 教育资源,影响

教育公平

就业机会:数字 鸿沟限制了部分 人群获取数字技 能和就业机会, 影响个人职业发

展

解决数字鸿沟的挑战

提升数字技能和知识:提供数字教育和 培训,帮助人们掌握必要的数字技能和 知识。

优化数字经济发展环境

加大对数字经济的投入,提高 数字化水平

完善数字基础设施,提高网络 覆盖率和稳定性

鼓励创新,促进数字技术的研 发和应用

加强数字经济的监管,保障数 据安全和隐私保护

推动全球数字合作与交流

推动全球数字合作与交流,共同应对数字鸿沟问题 加强数字基础设施建设,提高互联网普及率和覆盖率 促进数字经济发展,缩小发展中国家与发达国家之间的差距 开展数字教育,提高全民数字素养和技能水平

发展中国家在数 字化发展进程中 面临资金、技术、 人才等多重制约 因素

数字鸿沟对全球 经济的影响

经济增长的制约

缺乏数字技术使一些行业和 企业无法充分发挥潜力

数字鸿沟导致发展中国家与发 达国家之间的经济差距扩大

数字鸿沟限制了创新和技术 进步的传播

数字鸿沟对全球经济增长的 可持续性产生负面影响

马丁路德金演讲

马丁路德金演讲- 我们向何处去南方基督教领袖会议亚特兰大,佐治亚1967年8月16日现在为了回答“我们向何处去”这一问题,也是我们的主题,我们必须首先明确我们的现状。

当初拟定宪法时,一个不可思议的公式规定黑人在纳税和选举权方面只是一个完整人的60﹪。

如今又一个匪夷所思的公式规定黑人是一个完整人的50%。

对于生活中的好事,黑人大约只享有白人所享受的一半;而生活中的不愉快,黑人却要承受白人所面对的两倍。

因此,所有黑人中有一半人住着低标准的住房。

而且黑人的收入只是白人的一半。

每当我们审视生活中的负面经历时,黑人总是占着双倍的分额。

黑人失业者是白人的两倍。

黑人婴儿的死亡率是白人的两倍,从黑人所占的总人口比率上看,在越南死亡的黑人是白人的两倍。

其他领域也有同样惊人的数字。

在小学,黑人比白人落后一至三年,并且在他们种族隔离的学校,学生人均所得到的补贴比白人的学校少得多。

20个上大学的学生中,只有一个是黑人。

在职的黑人中,75﹪的人从事的是粗活。

这就是我们的现状。

我们的出路在哪里?首先,我们必须维护自己的尊严和价值。

我们必须要在一个仍然压迫着我们的体制中站起来,形成牢不可破且有威严的价值感。

我们再不能因为自己是黑人而感到羞耻。

要在几百年来灌输黑人是卑微的、无足轻重的人民心中唤起他们做人的尊严绝非易事。

黑色的描述和黑人的贡献甚至语义学似乎也合谋把黑色的说成是丑陋和卑劣的。

罗杰特分类词典中与黑色相关的同义词有120个,其中至少60个微词匿影藏行,例如,肮脏、煤烟、狰狞的、魔鬼的和令人作呕的。

而与白色相关的同义词约有134个,他们却毫无例外都褒奖洋溢,诸如纯洁、洁净、贞洁和纯真此类词等。

白色的(善意的)谎言总比黑色的(恶意的)谎言要好。

家庭中最为人所不齿的成员被称为“黑羊”(既败家子)。

奥西。

戴维斯曾建议或许应重造英语语言,从而教师将不再迫不得已因教黑人孩子60种方式蔑视自己使他们延续不断怀有不应有的自卑感,而教白人孩子134种方式宠爱自己而使他们继续怀有一种错误的优越感。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

跨越鸿沟:同步世界中的异步信号作者:Mike Stein,Paradigm Works开栏的话从本期起,《EDN CHINA电子设计技术》将正式推出“技术论坛”这个新栏目。

通过这个栏目,我们将向广大读者定期推介来自业界领先的技术供应商的充满了设计灵思的、最前沿的、高质量的技术文章;同时也会采用一系列创新的形式促进设计工程师与技术供应商的沟通与互动。

这样以来,当每个月读者拿到EDN CHINA杂志时,就好象是足不出户参加了一个技术研讨会,享受了一顿丰盛的信息“大餐”。

虽说是“新”栏目,但实际上作为它前身的“技术交流”——原先“技术纵横”中的子栏目——已经与读者相伴很多年了,这种对新技术的传播方式也已经得到了读者和技术供应商双方的认同。

“技术交流”中的文章在上的点击率排名总是名列前茅就是一个很好的例证。

现在我们将“技术交流”升格为一个独立的“技术论坛”栏目,其最主要的用意就是给这个栏目一个更广阔、更自由的发展空间。

而对于“技术交流”栏目所开创的“刊网互动”的形式,我们仍将沿用。

同时我们也将充分利用网络平台为读者提供更富于想象力的交互式的信息服务,比如读者可以将基于某篇文章的启发所迸发出的灵感火花发布到 网站上,经过我们的编辑整理则可以刊登在杂志上与更多的业内同仁分享。

新的栏目是一种新的尝试,当然其发展也需要读者热心的支持。

而实际上你会发现,你的参与意识越强,“技术论坛”所给予你的越丰富——这也正是我们的编辑理想所在。

只有最初级的逻辑电路才使用单一的时钟。

大多数与数据传输相关的应用都有与生俱来的挑战,即跨越多个时钟域的数据移动,例如磁盘控制器、CDROM/DVD 控制器、调制解调器、网卡以及网络处理器等。

当信号从一个时钟域传送到另一个时钟域时,出现在新时钟域的信号是异步信号。

在现代 IC、ASIC 以及 FPGA 设计中,许多软件程序可以帮助工程师建立几百万门的电路,但这些程序都无法解决信号同步问题。

设计者需要了解可靠的设计技巧,以减少电路在跨时钟域通信时的故障风险。

基础从事多时钟设计的第一步是要理解信号稳定性问题。

当一个信号跨越某个时钟域时,对新时钟域的电路来说它就是一个异步信号。

接收该信号的电路需要对其进行同步。

同步可以防止第一级存储单元(触发器)的亚稳态在新的时钟域里传播蔓延。

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。

当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

对任何一种触发器,在时钟触发沿前后的一个小时间窗口内,输入信号必须稳定。

这一时间窗口是多种因素的函数,包括触发器设计、实现技术、运行环境以及无缓冲输出上的负载等。

输入信号陡峭的边沿可以将此窗口减至最小。

随着时钟频率的升高,会出现更多有问题的时间窗口,而随着数据频率的提升,这种窗口的命中概率则会增加。

FPGA 制造商和 IC 晶片厂用“MTBF”来标识合格的触发器,并且确定它们的特性。

“MTBF”(平均无故障时间)用统计方法描述了一个触发器的亚稳态特性,即确定某个触发器出现故障的概率。

在计算 MTBF 时,制造商部分基于输入信号改变导致触发器不稳定期间的时间窗口长度。

另外,MTBF 的计算还使用了输入信号的频率以及驱动触发器的时钟频率。

在一个 ASIC 或 FPGA 库中,每种触发器都有时序要求,以帮助你确定容易出问题的窗口。

“建立时间”(Setup time)是指在时钟沿到来之前,触发器输入信号必须保持稳定的时间。

“保持时间”(Hold time)则是指在时钟沿之后,信号必须保持稳定的时间。

这些指标通常比较保守,以应对电源电压、工作温度、信号质量以及制造工艺等各种可能的差异。

如果一个设计满足了这些时序要求,则触发器出现错误的可能性可以忽略不计。

现代 IC 与 FPGA 设计中使用的综合工具可以保证设计能满足每个数字电路触发器对建立与保持时间的要求。

然而,异步信号却给软件提出了难题。

对新的时钟域来说,从其它时钟域传来的信号是异步的。

大多数综合工具在判定异步信号是否满足触发器时序要求时遇到了麻烦。

因为它们不能确定触发器处于非稳态的时间,所以它们也就不能确定从一个触发器通过组合逻辑到达下一个触发器的总延迟时间。

所以,最好的办法是使用一些电路来减轻异步信号的影响。

信号同步信号同步的目的是防止新时钟域中第一级触发器的亚稳态信号对下级逻辑造成影响。

简单的同步器由两个触发器串联而成,中间没有其它组合电路。

这种设计可以保证后面的触发器获得前一个触发器输出时,前一个触发器已退出了亚稳态,并且输出已稳定。

设计中要注意将两个触发器放得尽可能近,以确保两者间有最小的时滞(clock skew)。

IC 制造厂提供同步单元,帮助完成信号同步工作。

这些单元通常包括一个有非常高增益的触发器,它比普通触发器耗电更高,也比较大。

这种触发器降低了对输入信号建立-保持时间的要求,并且当输入信号导致亚稳态时,它可以防止出现振荡。

另一种同步器单元包括两个触发器,省去了将两个单独触发器靠近放置的工作,也防止设计人员误在两个触发器间加入任何其它的组合逻辑。

为了使同步工作能正常进行,从某个时钟域传来的信号应先通过原时钟域上的一个触发器,然后不经过两个时钟域间的任何组合逻辑,直接进入同步器的第一个触发器中(图 1)。

这一要求非常重要,因为同步器的第一级触发器对组合逻辑所产生的毛刺非常敏感。

如果一个足够长的信号毛刺正好满足建立-保持时间的要求,则同步器的第一级触发器会将其放行,给新时钟域的后续逻辑送出一个虚假的信号。

图1,在一个全同步器电路中,从某个时钟域传来的信号应先通过原时钟域上的一个触发器,然后不经过原触发器和同步器的第一个触发器两个时钟域间的任何组合逻辑,直接进入同步器的第一个触发器中。

一个经同步后的信号在两个时钟沿以后就成为新时钟域中的有效信号。

信号的延迟是新时钟域中的一到两个时钟周期。

一种粗略的估算方法是同步器电路在新时钟域中造成两个时钟周期的延迟,设计者需要考虑同步延迟将对跨时钟域的信号时序造成的影响。

同步器有许多种设计方法,因为一种同步器不能满足所有应用的需求。

同步器的类型基本上有三种:电平、边沿检测和脉冲(表 1)。

虽然还存在着其它类型的同步器,但这三种类型的同步器可以解决设计者遇到的多数应用问题。

在电平同步器中,跨时钟域的信号在新时钟域中要保持高电平或低电平两个时钟周期以上。

这种电路的要求是,在再次成为有效信号前,信号需要先变成无效状态。

每一次信号有效时,接收逻辑都会把它看作一个单个事件,而不管信号的有效状态保持了多久。

这种电路是所有同步器电路的核心。

表 1边沿检测同步器在电平同步器的输出端增加了一个触发器(图 2)。

新增触发器的输出经反相后和电平同步器的输出进行与操作。

这一电路会检测同步器输入的上升沿,产生一个与时钟周期等宽、高电平有效的脉冲。

如果将与门的两个输入端交换使用,就可以构成一个检测输入信号下降沿的同步器。

将与门改为与非门可以构建一个产生低电平有效脉冲的电路。

图2,边沿检测同步器在电平同步器的输出端增加了一个触发器。

当一个脉冲进入更快的时钟域中时,边沿检测同步器可以工作得很好。

这一电路会产生一个脉冲,用来指示输入信号上升或下降沿。

这种同步器有一个限制,即输入脉冲的宽度必须大于同步时钟周期与第一个同步触发器所需保持时间之和。

最保险的脉冲宽度是同步器时钟周期的两倍。

如果输入是一个单时钟宽度脉冲进入一个较慢的时钟域,则这种同步器没有作用,在这种情况下,就要采用脉冲同步器。

脉冲同步器的输入信号是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路(图 3)。

每当翻转电路接收到一个脉冲时,它就会在高、低电平间进行转换,然后通过电平同步器到达异或门的一个输入端,而另一个信号经一个时钟周期的延迟进入异或门的另一端,翻转电路每转换一次状态,这个同步器的输出端就产生一个单时钟宽度的脉冲。

图3,脉冲同步器的输入信号是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路脉冲同步器的基本功能是从某个时钟域取出一个单时钟宽度脉冲,然后在新的时钟域中建立另一个单时钟宽度的脉冲。

脉冲同步器也有一个限制,即输入脉冲之间的最小间隔必须等于两个同步器时钟周期。

如果输入脉冲相互过近,则新时钟域中的输出脉冲也紧密相邻,结果是输出脉冲宽度比一个时钟周期宽。

当输入脉冲时钟周期大于两个同步器时钟周期时,这个问题更加严重。

这种情况下,如果输入脉冲相邻太近,则同步器就不能检测到每个脉冲。

握手与 FIFO在许多应用中,跨时钟域传送的不只是简单的信号,数据总线、地址总线和控制总线都会同时跨域传输。

工程师们用一些其它的手段来处理这些情况,如握手协议和 FIFO 等。

当几个电路不能预知相互的响应时间时,握手方法能让数字电路间实现有效的通信。

例如,仲裁总线结构可以让一个以上的电路请求使用单个的总线,用仲裁方法来决定哪个电路可以获得总线的访问权,例如 PCI 或 AMBA(高级微控制器总线架构)。

每个电路都发出一个请求信号,由仲裁逻辑决定谁是“赢家”。

获胜的电路会收到一个应答,表示它可以访问总线。

该电路于是中断请求,开始使用总线。

不同时钟域电路使用的握手协议有两种基本类型:全握手(Full-handshake)和部分握手(partial-handshake)。

每种类型的握手都要用同步器,每种都各有自己的优缺点。

对全握手信号,双方电路在声明或中止各自的握手信号前都要等待对方的响应(图 4)。

首先,电路 A 声明它的请求信号,然后,电路 B 检测到该请求信号有效后,声明它的响应信号。

当电路 A 检测到响应信号有效后,中止自己的请求信号。

最后,当电路 B 检测到请求无效后,它中止自己的响应信号。

除非电路 A 检测到无效的响应信号,否则它不会再声明新的请求信号。

图4,对全握手信号,双方电路在声明或中止各自的握手信号前都要等待对方的响应。

这种类型的握手使用了电平同步器。

设计人员将这种技术用在如下情况:响应电路(电路 B)需要告知请求电路(电路 A)它可以处理请求。

这种握手方法要求请求电路延迟它的下一个请求,直到它检测到响应信号无效。

可以用经验估算法判断这个协议的时序:信号跨越一个时钟域要花两个时钟周期的时间,信号在跨越多个时钟域前被电路寄存。

全部的时间序列是:A 时钟域中最多五个周期加上 B 时钟域最多六个周期。

全握手类型很强健,因为通过检测请求与响应信号,每个电路都清楚地知道对方的状态。

这种方式的不足之处是完成所有交互的整个过程要花费很多时钟周期。

另一种类型是部分握手,它可以缩短这些事件的过程。