max335

冷热源工程课程设计

《冷热源工程》课程设计计算书题目:姓名:学院:专业:班级:学号:指导教师:2011年7月日目录1.设计原始资料 (2)2.确定冷源方案 (3)2.1方案一 (3)2.2方案二 (4)2.3方案三 (5)2.4方案四 (6)2.5 技术性分析............................................................ . (7)2.6经济性分析 (8)3. 分水器和集水器的选择 (17)3.1分水器和集水器的构造和用途. (17)3.2分水器和集水器的尺寸 (17)3.2.1分水器的选型计算 (17)3.2.2集水器的选型计算 (18)4. 膨胀水箱配置与计算 (16)4.1膨胀水箱的容积计算 (16)4.2膨胀水箱的选型 (16)5.制冷机房水系统设计计算 (9)5.1 冷冻水系统选型和计算 (9)5.1.1冷冻水泵的选型和计算 (9)5.1.1.1水泵流量和扬程的确定 (9)5.1.1.2 水泵型号的确定 (11)5.2 冷却水系统的选型和计算 (12)5.2.1冷却塔的选型 (12)5.2.2冷却水泵的选型计算 (13)6.参考资料 (19)7.个人小结 (20)设计题目嘉兴市百联服饰城制冷机房设计二、原始资料1、空调冷负荷:为:0.8MW(空调总面积6500m2)2、当地可用的能源情况:电:价格:2.5元/度天然气:价格:2.5元/m3;热值:33.45MJ/m3;蒸汽:价格:80元/吨;蒸汽压力为:0.8MPa燃油:价格:6.76元/升;低位发热量均为:42840kJ/kg3、冷冻机房外冷冻水管网总阻力为:0.15 MPa4、土建资料制冷机房建筑平面图(见附图),其中水冷式冷水机组冷却塔高度为:10 m2、确定冷源方案制冷量:0.8 MW*1.2=0.96 MW=960 KW机组的报价按照活塞式7角l 螺杆和离心按照8角l 溴化锂按照九角l2.1方案一:采用30HR 系列水冷式半封闭式普通型活塞式冷水机组表1 30HR-195半封闭式活塞式冷水机组性能参数1)固定费用设备初投资:2⨯35=70(万元) 安装费用:25%⨯70=17.5 (万元) 系统总投资费用L=70+17.5=87.5 (万元) 银行年利率i =5.94% 使用年限n=15年1)1()1(1-++⨯=n ni i i L L =151.08万元 式中:1L —每年系统折旧费用L —系统总投资费用,包括设备初投资和安装费用i —银行年利率2)年度使用费用型号 30HR-195 制冷量(KW)580 台数 2 单价(万元) 35 电机功率(KW)150 冷冻水水量(M3/h) 100 压降(Kpa)36 冷却水水量(M3/h) 125 压降(Kpa)93设备额定供冷功率为150KW ,台数2台,电费2.5元/度,供冷月为6-9月份,按照每天24小时供冷计算年度运行费用=单台供冷功率⨯台数⨯时间⨯电费=150⨯2⨯122⨯24⨯2.5=219.6万元3)设备年度费用设备年度费用=固定费用+年度使用费用=151.08+219.6=370.68万元2.2方案二: 采用SXZ 系列双效蒸汽型溴化锂吸收式冷水机组表2 SXZ-60L.M.H 双效蒸汽型溴化锂吸收式冷水机组性能参数型号 SXZ-60L.M.H制冷量(KW) 580 台数 2 单价(万元) 45 蒸汽耗量(Kg/h) 780 冷冻水 水量(M3/h) 100 压降(Kpa) 80 接管直径(DN)125冷却水 水量(M3/h) 165 压降(Kpa)120接管直径(DN)1501)固定费用设备初投资:2⨯45=90(万元) 安装费用:25%⨯90=22.5 (万元) 系统总投资费用L=90+22.5=112.5 (万元) 银行年利率i =5.94% 使用年限n=15年1)1()1(1-++⨯=n ni i i L L =194.24万元2)年度使用费用单台设备蒸汽耗量为780kg/h,台数2台,蒸汽价格为80元/吨,供冷月为6-9月份,按照每天24小时供冷计算年度运行费用=蒸汽耗量⨯台数⨯时间⨯单价=0.78⨯2⨯80⨯122⨯24=36.54万元3)设备年度费用设备年度费用=固定费用+年度使用费用=36.54+194.24=230.78万元2.3方案三:采用BZ-VI系列燃油型溴化锂吸收式冷水机组表3 BZ-VI50燃油型溴化锂冷水机组性能参数型号BZ-VI50制冷量(KW) 581台数 2单价(万元)45.07轻油耗量(Kg/h) 45低位热值(KJ/Kg) 43054冷冻水水量(M3/h) 100 压降(Kpa) 120 接管直径(DN) 125冷却水水量(M3/h) 163 压降(Kpa) 120 接管直径(DN) 1501)固定费用设备初投资:2⨯45.07=90.14(万元)安装费用:25%⨯90.14=22.54(万元)系统总投资费用L=90.14+22.54=112.68 (万元) 银行年利率i=5.94%使用年限n=15年1)1()1(1-++⨯=nni i i L L =194.55万元 2)年度使用费用单台设备轻油耗量为45kg/h ,台数2台,轻油密度为0.84公斤/升,低位发热量为42840KJ/Kg,轻油价格为6.76元/升,供冷月为6-9月份,按照每天24小时供冷计算年度运行费用=轻油耗量⨯台数⨯时间⨯单价=2⨯122⨯24⨯84.04284043054101⨯⨯⨯6.76=213.13万元3)设备年度费用设备年度费用=固定费用+年度使用费用=213.13+194.55=407.68万元2.4方案四:采用BZ-VI 系列燃气型溴化锂吸收式冷水机组表3 BZ-VI50燃油型溴化锂冷水机组性能参数 型号 BZ-VI50 制冷量(KW) 581 台数 2 单价(万元) 45.07 天然气耗量(Nm3/h) 43 低位热值(KJ/Kg) 46000 冷冻水 水量(M3/h) 100 压降(Kpa) 120 接管直径(DN)125冷却水 水量(M3/h) 163 压降(Kpa) 120 接管直径(DN)1501)固定费用设备初投资:2⨯45.07=90.14(万元) 安装费用:25%⨯90.14=22.54(万元)系统总投资费用L=90.14+22.54=112.68 (万元)银行年利率i =5.94% 使用年限n=15年1)1()1(1-++⨯=nni i i L L =194.55万元 2)年度使用费用单台设备天然气耗量为43Nm3/h ,台数2台,天然气价格为2.5元/m3,热值为33.45MJ/m3,供冷月为6-9月份,按照每天24小时供冷计算 年度运行费用=轻油耗量⨯台数⨯时间⨯单价=2⨯122⨯24⨯334504600093⨯⨯2.5=86.57万元3)设备年度费用设备年度费用=固定费用+年度使用费用=194.55+86.57=281.12万元2.5 技术性分析(一)活塞式冷水机组 (1) 优点:a.用材简单,可用一般金属材料,加工容易,造价低;b.系统装置简单,润滑容易,不需要排气装置;c.采用多机头,高速多缸,性能可得到改善;d.可提供5到12℃左右的冷水,适合于负荷比较分散的建筑群以及制冷量小于580KW 的中小型空调系统;e.属于有极调节。

MAXIM公司部分IC芯片应用简介(续一)

MAXIM公司部分IC芯片应用简介(续一)

王淑霞

【期刊名称】《集成电路应用》

【年(卷),期】2001(000)005

【摘要】7 内含精密电阻网络的单8通道、双4通道校准多路器芯片——MAX4539/MAX4540 单8通道的MAX4539和双4通道的MAX4540是一种具有校准功能的多路转换开关(校准多路器),适用于系统自检及精密型ADC。

它们内置的精密电阻分压网络能够提供精确的V+/2、5/8(V+-V-)、15V_(REF/)4096和4081V_(REF/)/4096(其中V_(REF)为外接基准电压)参考电压。

【总页数】3页(P78-79,83)

【作者】王淑霞

【作者单位】胶南市大场西柳沟村电子开发部,266414

【正文语种】中文

【相关文献】

1.2008~2009年中国纸业部分新建项目简介(续) [J], 郝永涛

2.上海市1996~1999年度部分幼儿教育研究课题简介(续) [J], 董丽楠

3.上海市1996~1999年度部分幼儿教育研究课题简介(续) [J], 董丽楠

4.MAXIM公司部分IC芯片应用简介 [J], 王淑霞

5.机械制造企业作业环境改善项目实例简介(续)(职业病危害防治部分) [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

AM335x 处理器 SDK RTOS 板库端口和启动说明书

Board Porting\Bring up using Processor SDK RTOS for AM335xProcessor SDK RTOS component known as board library consolidates all the board-specific information so that all the modifications made when moving to a new custom platform using the SOC can be made in the source of this library.There are three different components in PRSDK that help in porting and bring up of a custom board:∙Board library updatesa.PLL Clocking and PRCMb.Pin mux Updatec.DDR Configurationd.Peripheral instances updates∙Diagnostics tests∙Boot loader updatesBoard Library Updates in Processor SDK RTOS:PLL ClockingThere are two places where the device PLL configurations are performed when using Processor SDK RTOS and CCS.Debug environment:Debug environment refers to development setup where code is debugged using JTAG emulator on the SOC. The PRSDK software relies on the GEL file that is part of the target configuration to setup the clocks and the DDR for the device. The CCS GEL file for AM335x platforms is located in the CCS package at the location ccsv7\ccs_base\emulation\boards\<boardName>For example for beagle bone black, the files can be found atccsv7\ccs_base\emulation\boards\beaglebone\gelThe GEL is the first piece of software that should be brought up on a custom board.Production environment:Production environment refers to the setup when the base application is booted from a boot media like a flash memory or host interface. In this environment, the bootloader sets performs all the SOC and board initialization and copies the application from flash memory to the device memory.The clock setup in the bootloader code can be located atpdk_am335x_x_x_x\packages\ti\starterware\bootloader\src\am335xUsers can choose to use the platform clocking similar to one of TI reference platforms or can modify them as per their application requirements. By default the PLL settings are setup for OPP_NOM settings (MPU= 600 MHz.)TI provides Clock Tree tool to allow users to simulate the clocking on the SOC. For quick reference of the multiplier and divider settings to change the PLL setting is provided in the spreadsheetAM335x_DPLL_CALCv3.xlsx.After modifying the clocking in the bootloader, users need to rebuild the bootloader using instructions provided in Processor_SDK_RTOS_BOOT_AM335x/AM437xPRCM Modules Enable:PRCM Module Enable is required to turn on the power domain and the clocking to each of the modules on the SOC. The PRCM Enable calls to enable each module are made from the functionBoard_moduleClockInit which is found in the location.pdk_am335x_1_0_9\packages\ti\board\src\bbbAM335x\bbbAM335x.cCheck every instance and peripheral required in the application platform and enable the module in the board library.For example to use three UARTs 0, 1 and 4, ensure that you have the following code as part of the board library setup:/* UART */status = PRCMModuleEnable(CHIPDB_MOD_ID_UART, 0U, 0U);status = PRCMModuleEnable(CHIPDB_MOD_ID_UART, 1U, 0U);status = PRCMModuleEnable(CHIPDB_MOD_ID_UART, 4U, 0U);Note: PRCMEnable function is defined in pdk_am335x_1_0_9\packages\ti\starterware\soc\am335x Pinmux updates in the Board library:Generating a New PinMux Configuration Using the PinMux Utility: This procedure uses the cloud-based pinmux utilityNavigate to ${PDK_INSTALL_DIR}\packages\ti\starterware\tools\pinmux_config\am335x and Load beaglebone_black_configAdd and remove peripheral instances and select the appropriate use cases required for development based on the application platform requirements and resolve all conflicts.Refer Pin_Mux_Utility_for_ARM_MPU_ProcessorsPost Processing steps:1.Change the Category filter to starterware and download the pinmux files am335x_pimnmux.hand am335x_pinmux_data.c2.At the bottom of am335x_pinmux.h change extern pinmuxBoardCfg_t gAM335xPinmuxData[];to extern pinmuxBoardCfg_t gBbbPinmuxData[];3.Change am335x_pinmux_data.c to am335x_beagleboneblack_pinmux_data.c.4.Change gAM335xPinmuxData to gBbbPinmuxData at the end of the file in file5.am335x_beagleboneblack_pinmux_data.c.Replace the existing files with the new files and rebuild the board library using the instructions in the section Rebuilding board Library in Processor SDK RTOS:Updating DDR settings:Similar to clock and PLL settings, DDR initialization is configured in the Debug environment through GEL files and in production environment using bootloader source files.TI provides AM335x_EMIF_Configuration_tips which contains a spreadsheet to enter the timing from the DDR datasheet to compute the EMIF timing number required to initialize DDR.We strongly recommend changing the value and testing using GEL files before using them in the bootloader software. For Sanity test, you can perform read/write tests using CCS Memory Browser or run the diagnostic memory read/write test that we provide in diagnostics package here:PDK_INSTALL_PATH\packages\ti\board\diag\memOnce the DDR timings have been confirmed, you can use the settings in the file:PDK_INSTALL_PATH \packages\ti\starterware\bootloader\src\am335x\sbl_am335x_platform_ddr.c Peripheral initialization:The board library is responsible for most of the SOC initialization but it also setup some board level components such as ethernet PHY and debug UART and I2C for reading board ID from EEPROM. All of the other peripheral instances and initialization needs to be done from the application level.For example for beagleboneblack, the peripheral initialization are performed from the source filepdk_am335x_1_0_9\packages\ti\board\src\bbbAM335x\bbbAM335x_lld_init.cThe debug UART instance, I2C Addresses are set using the file board_cfg.h found under:pdk_am335x_1_0_9\packages\ti\board\src\bbbAM335x\includeDefault UART instance is set to 0 in the board library. The Board initialization will configure the UART instance 0 to send binary log data to serial console using the Board_UARTInit function. If you wish to use more UART instances then we recommend linking in the UART driver in the application and using UART_open() and UART_stdioInit API calls from the application.Each peripheral driver in the Processor SDK RTOS has a SOC configuration that provides the interrupt numbers, base address, EDMA channels which can be updated using the file <peripheral>_soc.c file. This is used as default setup for initializing the driver instance. It can be overridden from the application using peripheral_getSOCInitCfg() and peripheral_setSOCInitCfg()For Example: All instances of UART for AM335x have been mapped in the filepdk_am335x_1_0_9\packages\ti\drv\uart\soc\am335x\UART_soc.cSystem integrators need to ensure that no interrupt numbers and EDMA resource conflicts exist in the SOC configuration for all drivers used in the system.To exercise three UARTs in the system, users can use the following code://Setup Debug UARTboardCfg = BOARD_INIT_PINMUX_CONFIG |BOARD_INIT_MODULE_CLOCK |BOARD_INIT_UART_STDIO;Board_init(boardCfg);// Open Additional UART Instances:/* UART SoC init configuration */UART_initConfig(false);/* Initialize the default configuration params. */UART_Params_init(&uartParams);// Open UART Instance 1uartTestInstance =1;uart1 = UART_open(uartTestInstance, &uartParams);//Open UART Instance 4uartTestInstance = 4;uart4 = UART_open(uartTestInstance, &uartParams);BoardID Detect:TI supports multiple evaluation and reference platforms for AM335x hence the hardware platforms are populated with an EEPROM which contains information that identifies the hardware and its revision. The board library and software components read the boardID and initialize the platform based on the boardID. The BoardID_detect function can be found in the source in the file bbbAM335x_info.c in the board library and board_am335x.c in the bootloader source at:<PDK_INSTALL_PATH>\packages\ti\starterware\board\am335xRebuilding board Library in Processor SDK RTOS:While Creating a new folder for the custom board is an option users can explore, TI recommends that users make there changes in existing board package using either bbbAM335x, evmAM335x oriceAM335x folder to avoid spending additional effort to modify the build files for including the customBord.Once all the update to the board library are completed, the board library can be updated using the following instructions.Instructions to rebuild board library:Setup Processor SDK build environment before following steps provided below.cd pdk_am335x_1_0_9\packagesgmake board_libFor a specific board users are required to provide the LIMIT_BOARDS argument.LIMIT_BOARDS : evmAM335x icev2AM335x iceAMIC110 bbbAM335x skAM335xFor Example for beagleboneblack, users can use the following build option:gmake board_lib LIMIT_BOARDS=bbbAM335xDiagnostics:After the board library is built, we highly recommend that you create a diagnostics package similar to one provided in board library to test different interfaces functionally during board bring up.The diagnostics package can be located at pdk_am335x_1_0_9\packages\ti\board\diag. These are simple bare-metal tests that use peripheral drivers to help functionally validate the pins and interfaces.Documentation for all available diagnostic tests is provided here:/index.php/Processor_SDK_RTOS_DIAGBootloader in Processor SDK RTOS:As part of the production flow, users are required to develop/port flashing and booting utilities so the application can be launched on the custom board with JTAG. TI provides a bootloader mechanism where the ROM bootloader loads a secondary bootloader on the onchip memory that initializes the SOC and DDR and then copies the application into DDR memory.The boot process and flashing tools have been described in detail in the following article that is part of processor SDK RTOS Software developer`s guide:/index.php/Processor_SDK_RTOS_BOOT_AM335x/AM437x#Building_the_B ootloader。

MAX3490摘出资料(部分中文)

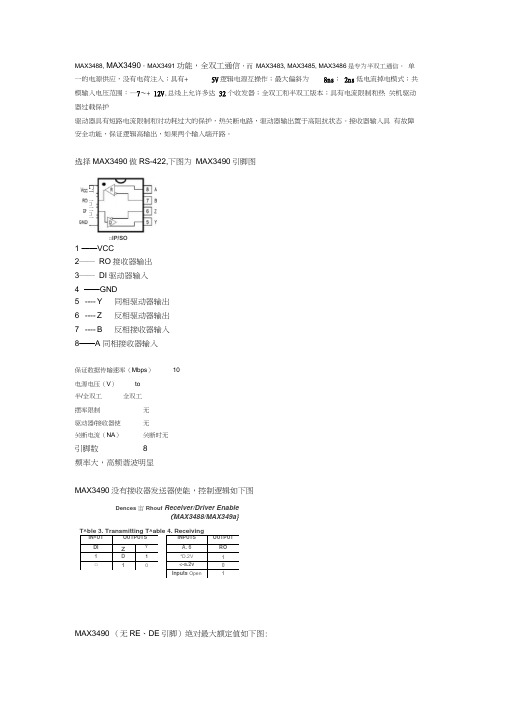

MAX3488, MAX3490,MAX3491 功能,全双工通信,而 MAX3483, MAX3485, MAX3486是专为半双工通信。

单一的电源供应,没有电荷注入;具有+ 5V 逻辑电源互操作;最大偏斜为 8ns ; 2ns 低电流掉电模式;共模输入电压范围:—7〜+ 12V ,总线上允许多达 32个收发器;全双工和半双工版本;具有电流限制和热 关机驱动器过载保护驱动器具有短路电流限制和对功耗过大的保护,热关断电路,驱动器输岀置于高阻抗状态。

接收器输入具 有故障安全功能,保证逻辑高输岀,如果两个输入端开路。

选择MAX3490做RS-422,下图为 MAX3490引脚图1 ——VCC2―― RO 接收器输出 3―― DI 驱动器输入 4 ——GND 5 ---- Y 同相驱动器输出 6 ---- Z 反相驱动器输出 7 ---- B反相接收器输入8——A 同相接收器输入保证数据传输速率(Mbps ) 10电源电压(V ) to 半/全双工 全双工摆率限制 无 驱动器/接收器使 无 关断电流(NA )关断时无引脚数8频率大,高频谐波明显MAX3490没有接收器发送器使能,控制逻辑如下图Dences 宙Rhouf Receiver/Driver Enable(MAX3488/MAX349a}T^ble 3. Transmitting T^able 4. ReceivingMAX3490 (无RE 、DE 引脚)绝对最大额定值如下图:IN^UTOUTPUTSDI zY 1 D 1 □1INPUTSOUTPUTA. 6 RO *D.2V1 <-a.2v0 Inputs Open1□IP/SOE L叵叵DABSOLUTE MAXIMUM RATINGSS U P P 卜F \ 01 ^3 9 e l\/ kill ■ ■ ■ ■ ■■!■■■■■■ iri ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■■ ■ ■ ■ ■ ■ i ■ ■ ■ r ■ ■ ■ ■ ■ ■ ■Control IrpiJ ValLage (RE, D£) ............... .......... ............... -0.3V ta 7V□rtvsr Inpul Voltage (6l).............. .......... .......... ............... -0.3Vtn 7VOnvar Output VcItaQ* (A,気V, ZX - ......................... -7J5V to12.SVftccer^CF Input VaKagc |A, B) . -7.5V to )2 5VReceiver Ojtput Voltage (RO) . . -O.3Vto (Vcc * 0 3V)Gontinucus Power g$ipmTk?n (T R= +70芒|各Pin Pi/Mc DIP 忖申rate 9 09mWU above +70© 72?mW8-Pin SO (<1HW 5 aarrrtVy «bove +7C P C), 471mW14-Rn Plastic DlP(de<m© 10mW fl C above +70忙》... HOOtrMf14-Rn SO (deia1^ fl.SSmW.^C abaw +70*C> __________ UUJllMfOperating Temperalur?MAXU C .............. ......... *........ ... ..................... -.Ot:to +7[TCMAX3d_ _E__”…lh.. “一,. ,.H.…““-“,-H.⑷乜B +85\:Storage Temperafur? Range lo +16[yCbead Tempeiature [wldering lOlMC)..................................... +XD*CMAX3490驱动器的开关特性如下图:DRIVER SWITCHING CHARACTERISTICS-MAX3465h MAX14$0, and MAX3491ri^E:» 3.3M a T*w *25*CJPARAMtFER CONCilTICNS m TVP MA 9(UNITSDrrwf OHtreftfiii OdljMjt Del叩g■ Sdll, Figure 7 122M mDrvcr Wfe-oEiii Ckrlp ui T M7»C r Time hno良L * fiOtl, Flpm 71&25mEtr p临他n M■丫LCfflMCHHiah Lrvtl IpiLM R L * 37(1. F4l/*a T2235m轉、ion Delay Hl0hi&-Lew Leveli IpML R. - ZTflFiflWWE■Jr22 35tp L n - iPHitl □越g*曲m Dtt&Ff吕的却iH^ie S- IPDS R.fc• 27n, FipL<eS E mDRIVER OUTPUT ENABLEJOIS^BLE TIMES {IWS-iflS'IMLW3-431 聞切Dmw CXJtput tnable r me I Q L OW LE^el tfZL Ri= 110SL f^FLFa 10 45 M OEDiwci" OulpiJl EiwN? Trne tg High Len el S FZH Ri ■ 110(1 钿ure $ 45raDrw CMp讥04»^le Time tom Migih Level fi t* 11(X1. F»flL*t940 to POriw D・*l・ Tim from LwLwi tpLE R L* 11IMI. i&40 BO mDTM< dip Lit Errtb^A Tiffii Au墟电叭旳Lx L#v4l tm Rl ■匚如i 10<8W gm 他Qrta&r ErrtBifi Titre frw 电靜©询|a H(;h 4PCH R; - 1inni FigiLiraS®o r»MAX3490CPA(TCto +70'Q8 Ptasttc DIPMAX349OCSA(TCt口+7D B C\8 SOMAX3490C/D crcto+70e c \Dice'MAX349OEPA-4(rc to +85X8 Plastic DIPMAX349OESA■40X10+9598 SOMAX3490引脚配置与典型工作电路,如下图|l巒4e 2 MAA J4ML JWAJC3啲Pin 8 两#挪询事呵Typ"C^ uftMOTE AEANODE O 8LXF砂*师悶ZKSQW诂沖盟F训卜皿咻斥$钵自Ncrv^OfU MAX3490封装尺寸L -15^ Plastic DIPPLASTIC DU AL-IN-LINE PACKAGE(0.300 in.)DIM [HOMES MLLlWETESS MIN MAA MIN MAXA a 200A1ocn&-■"20 12& C 175 3104-iS *3 0D5& Q0» 1.402W0.01S a 022 041 OKoo^ 1 MC DQOB0 0120200 30 &1D0Q&0 09001328E0.300 0 925 A2A E10咖0 310dia7VT e OJOO■■eA D.3H)■*tB Q4P0 10 16 L 0 IU a iso 2923J1 PINSMCHES MJJME1TER3-MN NUM MNI MAXa 0 3430 w BM 891 0140^3513-6719-43 ET lir o.-«Q -B51: 911&.43 010MBS 0i1522 4B 23.24 020 101S104535742454□24 1 14H2B52S DE37 13。

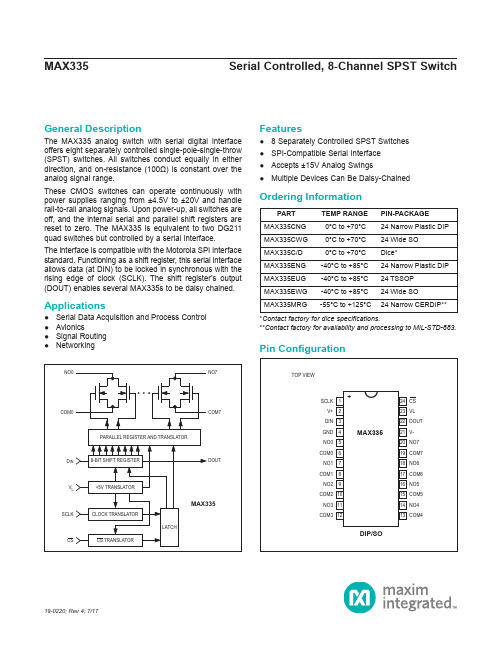

MAX335 CMOS 8-Channel Analog Switch with Serial Di

General DescriptionThe MAX335 analog switch with serial digital interface offers eight separately controlled single-pole-single-throw (SPST) switches. All switches conduct equally in either direction, and on-resistance (100Ω) is constant over the analog signal range.These CMOS switches can operate continuously with power supplies ranging from ±4.5V to ±20V and handle rail-to-rail analog signals. Upon power-up, all switches are off, and the internal serial and parallel shift registers are reset to zero. The MAX335 is equivalent to two DG211 quad switches but controlled by a serial interface.The interface is compatible with the Motorola SPI interface standard. Functioning as a shift register, this serial interface allows data (at DIN) to be locked in synchronous with the rising edge of clock (SCLK). The shift register’s output (DOUT) enables several MAX335s to be daisy chained. Applications●Serial Data Acquisition and Process Control●Avionics●Signal Routing●Networking Features●8 Separately Controlled SPST Switches ●SPI-Compatible Serial Interface●Accepts ±15V Analog Swings●Multiple Devices Can Be Daisy-Chained19-0220; Rev 4; 7/17*Contact factory for dice specifications.**Contact factory for availability and processing to MIL-STD-883.PART TEMP RANGE PIN-PACKAGEMAX335CNG 0°C to +70°C24 Narrow Plastic DIP MAX335CWG 0°C to +70°C24 Wide SOMAX335C/D 0°C to +70°C Dice*MAX335ENG -40°C to +85°C24 Narrow Plastic DIP MAX335EUG -40°C to +85°C24 TSSOPMAX335EWG -40°C to +85°C24 Wide SOMAX335MRG -55°C to +125°C24 Narrow CERDIP** Ordering InformationPin ConfigurationMAX335+241232223214205196187178169151014111312SCLKV+DINGNDNO0COM0NO1COM1NO2COM2NO3COM3CSTOP VIEWDIP/SOVLDOUTV-NO7COM7NO6COM6NO5COM5NO4COM4Voltages Referenced to V-V+ ......................................................................................44V GND ...................................................................................25V V L ................................................(GND - 0.3V) to (V+ + 0.3V) SCLK, CS , DIN, DOUT, NO_, COM_ ...........V- -2V to V+ +2Vor 30mA, whichever occurs firstContinuous Current (any terminal) .....................................30mA Peak Current, NO or COM(pulsed at 1ms, 10% duty cycle MAX) ...........................00mA Continuous Power Dissipation (T A = +70°C) (Note 1) Narrow Plastic DIP(derate 13.33mW/°C above +70°C) ..........................1067mW Wide SO (derate 11.76mW/°C above +70°C) .............941mW Narrow CERDIP (derate 12.50mW/°C above +70°C) ...1000mW TSSOP (derate 12.2mW/°C above +70°C) ........................30mA Operating Temperature RangesMAX335C_ _ ..........................................................0°C to +70°C MAX335E_ _ ......................................................-40°C to +85°C MAX335MRG ...................................................-55°C to +125°C Storage Temperature Range ............................-65°C to +160°C Lead Temperature (soldering, 10sec) .............................+300°C(V L = +5V ±10%, V+ = 15V, V- = -15V, T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)Note 1: All leads are soldered or welded to PC boards.PARAMETERSYMBOLCONDITIONSMINTYPMAXUNITSSWITCHAnalog Signal Range V ANALOG T A = T MIN to T MAX -1515V On-ResistanceR ONV COM = ±10V, I NO = 1mA T A = +25°C 100150Ω200NO Off-Leakage CurrentI NO(OFF)V COM = -14V, V NO = +14V T A = +25°C -10.0021nA -2020V COM = -14V, V NO = +14V T A = +25°C -10.0021-2020COM Off-Leakage CurrentI COM(OFF)V COM = -14V, V NO = +14V T A = +25°C -10.0021nA -2020V COM = -14V, V NO = +14V T A = +25°C -10.0021-2020COM On-Leakage CurrentI COM(ON)V COM = V NO = +14VT A = +25°C -20.012nA -2040V COM = V NO = -14VT A = +25°C-20.012-2040DIGITAL I/ODIN, SCLK, CS Input Logic Threshold HighV IH V L = +5V 2.4V V L = +15V 11DIN, SCLK, CS Input Logic Threshold LowV IL V L = +5V 0.8V V L = +15V3DIN, SCLK, CS Input Current Threshold HighI INH V DIN , V SCLK , V CS = 2.4V-10.031µA V L = +15V, V DIN , V SCLK , V CS = 11V -10.031DIN, SCLK, CS Input Current Threshold Low I INL V DIN , V SCLK , V CS = 0.8V-10.031µA V L = +15V, V DIN , V SCLK , V CS = 3V -10.031DOUT Output Voltage Logic HighV DOUTI DOUT = 0.8mA3.5V LVAbsolute Maximum RatingsStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Electrical Characteristics(V L = +5V ±10%, V+ = 15V, V- = -15V, T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)Note 2: When V L falls below this voltage, all switches are set off and the internal shift register is cleared (all zero).Note 3: Guaranteed, not production tested.PARAMETERSYMBOLCONDITIONSMINTYPMAXUNITSDIGITAL I/ODOUT Output Voltage Logic Low V DOUT I DOUT = -1.6mA 0.4V V L RESET Voltage V LL (Note 2)0.8V V L RESET Voltage V LH T A = +25°C 2.4V SCLK Input HysteresisSCLK HYSTT A = +25°C 100mVSWITCH DYNAMIC CHARACTERISTICS Turn-On Timet ON From rising-edge of CST A = +25°C 200400ns500Turn-Off Time t OFF From rising-edge of CS T A = +25°C 90400ns 500NO Off-Capacitance C NO(OFF)V S = GND, f = 1MHz T A = +25°C 2pF COM Off-Capacitance C COM(OFF)V S = GND, f = 1MHz T A = +25°C 2pF Channel On-Capacitance C COM(ON)V D = V S = GND, f = 1MHzT A = +25°C 8pF Off IsolationOIRR R L = 100Ω, C L = 15pF, V S = 1V RMS , f = 100kHz T A = +25°C 90dB Channel-to-Channel Crosstalk CCRR R L = 50Ω, C L = 15pF, V S = 1V RMS , f = 100kHzT A = +25°C100dB Break-Before-Make Delay T BBM 1525ns Clock Feedthrough at S, D (Note 3)ESCLKD LOAD = S LOAD = 75Ω, measured at S and DT A = +25°C100nV-secPOWER SUPPLIESPower-Supply Voltage Range V+/V-±4.5±20V V L Power-Supply Voltage RangeV L 4.5V+V V+ Supply CurrentI+DIN = CS = SCLK = 0V/5VT A = +25°C 150300µA500V- Supply Current I-DIN = CS = SCLK = 0V/5VT A = +25°C 0.0110µA10V L Supply Current I LDIN = CS = SCLK = 0V/5VT A = +25°C50100µA200Electrical Characteristics (continued)(V L = +5V ±10%, V+ = 15V, V- = -15V, T A = T MIN to T MAX , unless otherwise noted.)Note 4: This specification guarantees that data at D OUT never appears before SCLK’s falling edge.PARAMETERSYMBOL CONDITIONSMIN TYPMAXUNITS SCLK Maximum Frequency f SCLK 2.1MHz Cycle Time t CH + t CL 480ns CS Lead Time t CSS 240ns CS Lag Time t CSH2240ns SCLK High Time t CH 190ns SCLK Low Time t CL 190ns Data-Setup Time t DS 200ns Data-Hold Time t DH 0ns DOUT Data Valid After Falling SCLKt DO50% of SCLK to 10% of DOUT CL = 10pF T A = +25°C240ns 400DOUT Data-Hold Time After Rising SCLK (Note 4)C L = 10pFns Rise Time of DOUT (Note 3)20% V L to 70% V L , C L = 10pF 100ns Allowable Rise Time at DIN, SCLK, CS (Note 3)20% V L to 70% V L , C L = 10pF 2µs Fall Time of DOUT (Note 3)70% V L to 20% V L , C L = 10pF 100ns Allowable Fall Time at DIN, SCLK, CS (Note 3)70% V L to 20% V L , C L = 10pF2µsTiming Characteristics of Serial Digital Interface (Figure 1)(V+ = +15V, V- = -15V, V L = 5V, T A = +25°C, unless otherwise noted.)Typical Operating CharacteristicsR ON vs. V COM AND POWER-SUPPLY VOLTAGEV COM (V)R O N (Ω)100-10501001502002503000-2020DATA-HOLD TIME vs.POWER-SUPPLY VOLTAGEM A X 335t o c 04SUPPLY VOLTAGE (V)D A T A -H O L D T I ME (n s )±20±15±10-40-200204060-60±5CHARGE INJECTION vs. V COMV COM (V)Q (p C )100-10-70-3503570105-105-20155-5-1520R ON vs. V COM AND TEMPERATUREV COM (V)R O N (Ω)100-10501001502002503000-2020DATA-SETUP TIME vs.POWER SUPPLYM A X 335t o c 05SUPPLY VOLTAGE (V)D A T A -SE T U P T I M E (n s )±20±15±101020304050600±5SUPPLY vs. TEMPERATUREM A X 335t o c 08TEMPERATURE (°C)I +, I -, I L (µA )+250.010.111010010000.001-55+125I+I LI-t ON, t OFF vs. V COMV COM (V)t O N , t O F F (n s )151051002003004005006000020LEAKAGE CURRENT vs.TEMPERATUREM A X 335t o c 06TEMPERATURE (°C)O N -L E A K A G E (p A )+125+250.0020.020.22202000.0002-55MINIMUM SCLK PULSE WIDTHvs. POWER SUPPLYM A X 335t o c 09SUPPLY VOLTAGE (V)S C L K (n s )±20±15±101020304050600±5Detailed DescriptionSerial Digital InterfaceBasic OperationRefer to Figure 2. The MAX335 interface can be thought of as an 8-bit shift register controlled by CS. While CS is low, input data appearing at DIN is clocked into the shift register synchronous with SCLK’s rising edge. The data is an 8-bit word, each bit controlling one of eight switches in the MAX335 (Table 1). DOUT is the output of the shift register, with data appearing synchronous with SCLK’s falling edge. Data at DOUT is simply the input data delayed by eight clock cycles.When shifting the input data, D7 is the first bit in and out of the shift register. While shifting data, the switches remain in their original configuration. When the 8 bits of data have been shifted in, CS is brought high. This updates the new switch configuration and inhibits further data from entering the shift register. Transitions at DIN and SCLK have no effect when CS is high, and DOUT holds the last bit in the shift register.The MAX335 three-wire serial interface is compatible with the SPI™ and Microwire™ standards. If interfacing with a Motorola processor serial interface, set CPOL = 0. The MAX335 is considered a slave device (Figures 2 and 3). Upon power-up, the shift register contains all zeros, and all switches are off.The latch that drives the analog switch is only updated on the rising edge of CS when SCLK is low. If SCLK is high when CS rises, the latch will not be updated until SCLK goes low. The CPOL = 1, CPHA = 1 SPI configuration does not update the latch correctly. Daisy ChainingFor a simple interface using several MAX335s, “daisy chain” the shift registers as shown in Figure 5. The CS pins of all devices are connected together, and a stream of data is shifted through the MAX335s in series. When CS is brought high, all switches are updated simultaneously. Additional shift registers may be included anywhere in series with the MAX335 data chain.Addressable Serial InterfaceWhen several serial devices are configured as slaves, addressable by the processor, DIN pins of each MAX335 are connected together (Figure 6). Address decode logic individually controls CS of each slave device. When a slave is selected, its CS is brought low, data is shifted in, and CS is brought high to latch the data. Typically, only one slave is addressed at a time. DOUT is not used. Digital FeedthroughDigital feedthrough energy measures 100nV-sec, which means that with no filtering at the signal channel, feedthrough from a sharply rising clock edge into an unfiltered switch channel can be measured at 1Vp-p for 100ns. However, even 100pF capacitance in the switch channel, when combined with the switch resistance, yields a filter that reduces this transient to 10mVp-p typical. T o reduce digital feedthrough, hysteresis (150mV typ) was added to the SCLK input so triangle or sine waves may be used.PIN NAME FUNCTION1SCLK Serial Clock Input2V+Positive Supply Voltage3DIN Serial Data Input4GND Ground5NOØSwitch 06COMØSwitch 07NO1Switch 18COM1Switch 19NO2Switch 210COM2Switch 211NO3Switch 312COM3Switch 313COM4Switch 414NO4Switch 415COM5Switch 516NO5Switch 517COM6Switch 618NO6Switch 619COM7Switch 720NO7Switch 721V-Negative Supply Voltage 22DOUT Serial Data Output23V L Logic Supply/Reset24CS Chip SelectPin DescriptionFigure 1. Timing DiagramFigure 2. Three-Wire Interface TimingTable 1. Serial-Interface Switch ProgrammingX = Don’t careFigure 3. Connections for Microwire Figure 4. Connections for SPIDATA BITSFUNCTIOND7D6D5D4D3D2D1D00X X X X X X X Switch 7 open (off)1X X X X X X X Switch 7 closed (on)X 0X X X X X X Switch 6 open X 1X X X X X X Switch 6 closed X X 0X X X X X Switch 5 open X X 1X X X X X Switch 5 closed X X X 0X X X X Switch 4 open X X X 1X X X X Switch 4 closed X X X X 0X X X Switch 3 open X X X X 1X X X Switch 3 closed X X X X X 0X X Switch 2 open X X X X X 1X X Switch 2 closed X X X X X X 0X Switch 1 open X X X X X X 1X Switch 1 closed X X X X X X X 0Switch 0 open X XXXXXX1Switch 0 closedFigure 5. Daisy-Chained ConnectionFigure 6. Addressable Serial InterfaceApplications Information8 x 1 MultiplexerTo use the MAX335 as an 8 x 1 multiplexer, tie all drains together (COM0 to COM7); the mux inputs now source each switch (NO0 to NO7). Input a single 0V to +3V pulse at DIN. As this is clocked through the register by SCLK, each switch will sequence on one at a time.4-2 Differential MultiplexerTo use the MAX335 as a 4-2 differential multiplexer, tie COM0 through COM3 together and COM4 through COM7 together. Differential inputs will be the source inputs as follows: (NO0, NO4), (NO1, NO5), (NO2, NO6), (NO3, NO7). Figure 7 shows the serial input control at DIN required to turn on two switches making a differential multiplexer.CS is held low for four clock pulses; the first pulse is clocked into the fifth switch position as the second pulse is clocked into the first switch position. CS is pulled high to update switches; then CS is pulled low, and SCLK advances pulses to S1 and S5 positions, where CS is pulled high to update, etc.SPDT SwitchesTie COM0 to NO1 so that NO0 and COM1 are now inputs and COM0/NO1 is the common output. SP is common output. Up to four SPDT switches can be made from each MAX335. Multiples of four or more can be made by daisy chaining devices. In Figure 8, DIN is a pulse train. Again, CS is held low to clock in pulses and CS is pulled high to update; CS is held low to shift pulses, then pulled high to update, etc.Reset FunctionPulsing V L below +0.8V initiates the power-up reset function. The switches are set to the off position, and the serial shift register is reset to all zeros.Power-Supply OperationThe MAX335 operates with V = ±4.5V to ±20V and V L = +5V. With V- tied to ground, the part operates with V+ = +10V to +30V.The V L supply sets TTL input compatibility at a 1.6V switching threshold. As V L is raised, the switching threshold is raised, so the part is no longer TTL compatible. The MAX335 also operates with a single power supply: V L = V+ and V- = 0V. With V L tied to V+, the V L supply cannot be used as a reset function.Figure 7. Differential Multiplexer Input ControlFigure 8. Serial-Input Control for SPDT SwitchChip TopographyTRANSISTOR COUNT: 387SUBSTRATE CONNECTED TO V+.Package InformationPackage Information (continued)Package Information (continued)REVISION NUMBER REVISIONDATEDESCRIPTIONPAGESCHANGED47/17Updated Min and Typ values of Break-Before-Make Delay inElectrical Characteristics table3Revision HistoryMaxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated’s website at .。

AM335x IBIS Model使用指南说明书

How to use the AM335x IBIS ModelsIntroductionThe AM335x External Memory Interface is a very flexible interface which can be used with LPDDR, DDR2, DDR3, and DDR3L. There are many settings available to fine-tune the signal timing on this interface. These settings include ODT options, pullups, pulldowns, slew rate, etc. IBIS modeling can be used to fine tune the set of options for a given PCB. That said, understanding the mapping between the various IBIS models and the corresponding register configuration options is critical to doing this correctly. This article is intended to help bridge that gap so that AM335x users can properly model their memory interface and program the best options in the AM335x registers. NOTE: TI does not support timing analysis with IBIS simulations. Rather, customers are encouraged to use the IBIS models for Signal Integrity (SI) analysis. As far as the timing goes, please follow the routing guidelines and length/skew matching requirements in the Data Manual.IBIS StructureEvery pin on the device is listed with a corresponding "Selector". For example:P1 DDR_DQS0 Selector_1If you then go and look at the definition of that Selector you will find all of the available models for that given I/O cell. For example:[Model Selector] Selector_1Model_1000 INPUT,1.5V,FULLTERM, 1.00*RExt,IND,5%,DIFF_VREF_FULLTERM_8MA_5PER_1P5 Model_1001 INPUT,1.5V,Half Thevenin, 1.60*RExt,IND,5%,DIFF_VREF_HALFTERM_5MA_5PER Model_1002 INPUT,1.5V,FULLTERM, 0.88*RExt,IND,5%,DIFF_VREF_FULLTERM_9MA_5PER_1P5Each of the models above corresponds to the I/O cell behavior given a specific set of configuration options. Register MappingParameters for a typical modelEach model has the following structure:ReadsModel_xyz INPUT, <voltage>, <ODT>, <Impedance>, <Temperature>, <Voltage-tolerance> WritesModel_xyz 3-STATE, <voltage>, <ODT>, <slew>, <Impedance>, <Temperature>, <Voltage-tolerance>Parameter Options Register Setting TRM Reference<voltage>DDR3L (1.35V), DDR3 (1.5V), orDDR2/LPDDR (1.8V)<ODT>Reads:NOTERM_WEAK_PU_ON,NOTERM_WEAK_PD_ON,NOTERM_WEAK_PUPD_OFF,FULLTERM, Half TheveninWrites: ODT Off DDR_PHY_CTRL_1[reg_phy_rd_local_odt]Table 7-254.DDR_PHY_CTRL_1Register FieldDescriptions<slew>fastest, fast, slow, slowest ddr_cmd0_ioctrl, ddr_cmd1_ioctrl,ddr_cmd2_ioctrl, ddr_data0_ioctrl,ddr_data1_ioctrl ["sr" fields]Table 9-7. DDR Slew Rate Control Settings<Impedance>0.67*RExt0.73*RExt0.8*RExt0.88*RExt1.00*RExt1.14*RExt1.33*RExt1.6*RExt ddr_cmd0_ioctrl, ddr_cmd1_ioctrl,ddr_cmd2_ioctrl, ddr_data0_ioctrl,ddr_data1_ioctrl ["I" fields]Table 9-8. DDRImpedance ControlSettings<Temperature>IND = -40 to 125C, 25C nominal(In IBIS Comments)<Voltage-tolerance>(Power supply tolerance, not a register)5% or 10%Additional considerations for LPDDR vs DDR2LPDDR and DDR2 are both 1.8V interfaces. However, they use different signaling technologies:•LPDDR -> LVCMOS•DDR2 -> SSTLLet’s look at the pin DDR_D4 as an example…N3 DDR_D4 Selector_11So here is the corresponding snippet from Selector_11:|*****************************************************************************************| Usage I/O#1.35/1.5V/1.8V#X#X#BCSHTLTCSCDVPBFZ_SSDHV.PAD| Base model BCSHTLTCSCDVPBFZ_SSDHV|***************************************************************************************** [Model Selector] Selector_11<snip>Model_440 INPUT,1.8V,Pull-up/down off,IND,5%,VREF_NOTERM_PUPD_OFF_5PER_1P8<snip>Model_452 INPUT,1.8V,Pull-up/down off,IND,5%,LVCMOS_PUPD_OFF_5PER_1P8Model_440 and Model_452 above are nearly identical, but that is because both LPDDR and DDR2 are 1.8V interfaces. The final field holds the difference between them. Model_440 is of type VREF_NOTERM which3corresponds to DDR2 with no termination enabled (i.e. SSTL). Model_452 is of type LVCMOS, which is used for LPDDR.The register mapping that corresponds to this selection in the actual hardware is ddr_io_ctrl[mddr_sel]:•mddr_sel=0 -> DDR2/3 (SSTL)•mddr_sel=1 -> LPDDR (LVCMOS)Additional Notes on ioctrl Pin MappingThe ioctrl registers map to the actual pins as follows:Register[bits]Signalsddr_cmd0_ioctrl[9:5]ddr_ck, ddr_cknddr_cmd0_ioctrl[4:0]ddr_ba0, ddr_ba2, ddr_wen, ddr_a[9:8], ddr_a[6:3]ddr_cmd1_ioctrl[4:0]ddr_15, ddr_a[12:10], ddr_a7, ddr_a2, ddr_a0, ddr_ba1, ddr_casn, ddr_rasnddr_cmd2_ioctrl[4:0]ddr_cke, ddr_resetn, ddr_odt, ddr_csn0, ddr_[a14:13], ddr_a1ddr_data0_ioctrl[9:5]ddr_dqs1, ddr_dqsn1ddr_data0_ioctrl[4:0]ddr_d[15:8], ddr_dqm1ddr_data1_ioctrl[9:5]ddr_dqs0, ddr_dqsn0ddr_data1_ioctrl[4:0]ddr_d[7:0], dqm0ExampleIn AM335x EMIF Configuration tips the recommendation is to set all the IOCTRL registers to a value of 0x18B which breaks down as:•SR[9:8] = 01 slow•I[7:5] = 100 0.88*RExt•SR[4:3] = 01 slow•I[2:0] = 011 1.00*RExtAs an example, let's assume you would like to model this type of configuration for your own hardware. And let's assume for this example that you're using DDR3 (1.5V). Finally, we'll do this modeling using 5% power supply tolerance, though it could similarly be modeled using 10% tolerance (i.e. just choose the corresponding model).The IOCTRL settings above correspond to the slew rate for ALL signals being set to "slow". The Impedance is being configured differently for some of the signals. The breakdown of signals controlled by these registers can be found in Table 9-9. DDR PHY to IO Pin Mapping. The register descriptions of the IOCTRL specifies which signals are affected by SR[9:8]/I[7:5]. So in particular, the following use 0.88*RExt:•DQS•DQSn•CK•CKnCorrespondingly the signals above should choose models with Impedance of 0.88*RExt. The others should use1.00*RExt. So in this scenario we would use the following:4Signal Model DescriptionDQS Model_6553-STATE,1.5V,ODT off,slow, 0.88*RExt,IND,5%,SR01_9MA_PADP_5PER_1P5DQS#Model_8473-STATE,1.5V,ODT off,slow, 0.88*RExt,IND,5%,SR01_9MA_PADN_5PER_1P5CK Model_3433-STATE,1.5V,ODT off,slow, 0.88*RExt,IND,5%,SR01_9MA_5PER_1P5CK#Model_3433-STATE,1.5V,ODT off,slow, 0.88*RExt,IND,5%,SR01_9MA_5PER_1P5DQ Model_3523-STATE,1.5V,ODT off,slow, 1.00*RExt,IND,5%,SR01_8MA_5PER_1P5DM Model_3523-STATE,1.5V,ODT off,slow, 1.00*RExt,IND,5%,SR01_8MA_5PER_1P5Note that the write models always have ODT off since in that scenario ODT would be a function of the memory onthe other side. For reads, ODT would be the responsibility of AM335x and so that parameter is configurable for reads:Signal Model DescriptionDQS Model_1002INPUT,1.5V,FULLTERM, 0.88*RExt,IND,5%,DIFF_VREF_FULLTERM_9MA_5PER_1P5DQS#Model_1002INPUT,1.5V,FULLTERM, 0.88*RExt,IND,5%,DIFF_VREF_FULLTERM_9MA_5PER_1P5CK Model_3433-STATE,1.5V,ODT off,slow, 0.88*RExt,IND,5%,SR01_9MA_5PER_1P5CK#Model_3433-STATE,1.5V,ODT off,slow, 0.88*RExt,IND,5%,SR01_9MA_5PER_1P5DQ Model_496INPUT,1.5V,FULLTERM, 1.00*RExt,IND,5%,VREF_FULLTERM_8MA_5PER_1P5DM Model_3523-STATE,1.5V,ODT off,slow, 1.00*RExt,IND,5%,SR01_8MA_5PER_1P5Note that the DDR_CK, DDR_CKN, and DDR_DQM pins are always driven by the AM335x (not the memory) which is why it is of type "3-STATE" (output) for both write and read operations above.Verifying DDR ConfigurationAfter investing the effort to determine the best models for your board, it will be up to the software team to actually make the necessary changes. This final and most critical step of the process is often done improperly! In order to simplify the process, a JTAG based script was created to read important registers on the device and parse the contents to show what's actually being used. Here's how to use download and use this script:1.Download am335x-ddr-analysis.dss [1].unch CCS.3.Create an appropriate target configuration file for connecting to your board.•File -> New -> Target Configuration File•Supply a name/location for the file.•View -> Target Configurations to see the available target configurations (yours should now be among them!).•Double-click your file in the Target Configurations panel to open it for editing.•Select your emulator and processor. Be sure to select a processor and not a board, as we don't want any gel files to be part of the configuration. Save.unch the debugger, but do not connect to any CPUs.•In the Target Configurations window, right-click on your ccxml file and select "Launch Selected Configuration"unch the scripting console by going to View -> Scripting Console.6.Load am335x-ddr-analysis.dss in the scripting console by executing "loadJSFile<path-to-dss-file>/am335x-ddr-analysis.dss".57.It will use the Debug Access Port (DAP) unobtrusively behind the scenes such that the Cortex A8 is never halted.It will generate a am335x-ddr-analysis_yyyy-mm-dd_hhmmss.txt file on your desktop.References[1]https:///sitara-dss-files/am335x-dss-files/blobs/raw/master/am335x-ddr-analysis.dss6 Article Sources and ContributorsHow to use the AM335x IBIS Models Source: /index.php?oldid=235642 Contributors: BradGriffis。

MAX32665 MAX32666 用户指南说明书

MAX32665/MAX32666 USER GUIDE UG6971; Rev 3; 2/2022Abstract: This user guide provides application developers information on how to use the memory and peripherals of the MAX32665/MAX32666 microcontroller. Detailed information for all registers and fields in the device are covered. Guidance is given for managing all the peripherals, clocks, power and startup for the device family.MAX32665/MAX32666 User GuideTable of Contents1.Overview ----------------------------------------------------------------------------------------------------------------- 291.1 Block Diagram ---------------------------------------------------------------------------------------------------------------- 302.Resource Protection Unit (RPU) ------------------------------------------------------------------------------------ 31 2.1 Instances ----------------------------------------------------------------------------------------------------------------------- 31 2.2 Usage --------------------------------------------------------------------------------------------------------------------------- 332.2.1Reset State -------------------------------------------------------------------------------------------------------------------------------- 332.2.2MPU Implementation ------------------------------------------------------------------------------------------------------------------ 332.2.3MPU Protection Fault ------------------------------------------------------------------------------------------------------------------ 332.2.4RPU Protection Fault-------------------------------------------------------------------------------------------------------------------- 332.2.5RPU Fault Handler ----------------------------------------------------------------------------------------------------------------------- 33 2.3 Registers ----------------------------------------------------------------------------------------------------------------------- 342.4 Register Details -------------------------------------------------------------------------------------------------------------- 363.Memory, Register Mapping, and Access ------------------------------------------------------------------------- 40 3.1 Memory, Register Mapping, and Access Overview ----------------------------------------------------------------- 40 3.2 Field Access Definitions ---------------------------------------------------------------------------------------------------- 43 3.3 Standard Memory Regions ------------------------------------------------------------------------------------------------ 443.3.1Code Space -------------------------------------------------------------------------------------------------------------------------------- 443.3.2SRAM Space ------------------------------------------------------------------------------------------------------------------------------- 443.3.3Peripheral Space ------------------------------------------------------------------------------------------------------------------------- 453.3.4External RAM Space -------------------------------------------------------------------------------------------------------------------- 463.3.5External Device Space ------------------------------------------------------------------------------------------------------------------ 463.3.6System Area (Private Peripheral Bus) ---------------------------------------------------------------------------------------------- 463.3.7System Area (Vendor Defined) ------------------------------------------------------------------------------------------------------- 46 3.4 Device Memory Instances ------------------------------------------------------------------------------------------------- 463.4.1Main Program Flash Memory -------------------------------------------------------------------------------------------------------- 463.4.2Cache Memories ------------------------------------------------------------------------------------------------------------------------- 473.4.3Information Block Flash Memory---------------------------------------------------------------------------------------------------- 473.4.4System SRAM ----------------------------------------------------------------------------------------------------------------------------- 473.4.5AES Key and Working Space Memory ---------------------------------------------------------------------------------------------- 483.4.6MAA Key and Working Space Memory -------------------------------------------------------------------------------------------- 483.4.7TPU Memory ------------------------------------------------------------------------------------------------------------------------------ 48 3.5 AHB Interfaces --------------------------------------------------------------------------------------------------------------- 483.5.2AHB Masters ------------------------------------------------------------------------------------------------------------------------------ 48 3.6 Peripheral Register Map --------------------------------------------------------------------------------------------------- 493.6.1APB Peripheral Base Address Map -------------------------------------------------------------------------------------------------- 493.6.2AHB Peripheral Base Address Map ------------------------------------------------------------------------------------------------- 50 3.7 Error Correction Coding (ECC) Module --------------------------------------------------------------------------------- 513.7.1SRAM --------------------------------------------------------------------------------------------------------------------------------------- 513.7.2FLASH --------------------------------------------------------------------------------------------------------------------------------------- 513.7.3Cache --------------------------------------------------------------------------------------------------------------------------------------- 524.System, Power, Clocks, Reset --------------------------------------------------------------------------------------- 53 4.1 Oscillator Sources and Clock Switching -------------------------------------------------------------------------------- 534.1.1Oscillator Implementation ------------------------------------------------------------------------------------------------------------ 554.1.296MHz Internal Main High-Speed Oscillator ------------------------------------------------------------------------------------- 554.1.360MHz Low Power Internal Oscillator --------------------------------------------------------------------------------------------- 554.1.432MHz Bluetooth Radio Oscillator -------------------------------------------------------------------------------------------------- 554.1.57.3728MHz Internal Oscillator ------------------------------------------------------------------------------------------------------- 564.1.632.768kHz External Crystal Oscillator ---------------------------------------------------------------------------------------------- 564.1.78kHz Ultra-Low Power Nano-Ring Internal Oscillator ------------------------------------------------------------------------- 57 4.2 Operating Modes ------------------------------------------------------------------------------------------------------------ 574.2.1ACTIVE Mode ----------------------------------------------------------------------------------------------------------------------------- 584.2.2SLEEP Low Power Mode --------------------------------------------------------------------------------------------------------------- 584.2.3DEEPSLEEP Low Power Mode -------------------------------------------------------------------------------------------------------- 604.2.4BACKUP Low Power Mode ------------------------------------------------------------------------------------------------------------ 62 4.3 Device Resets ----------------------------------------------------------------------------------------------------------------- 634.3.1Peripheral Reset ------------------------------------------------------------------------------------------------------------------------- 664.3.2Soft Reset ---------------------------------------------------------------------------------------------------------------------------------- 664.3.3System Reset, External Reset --------------------------------------------------------------------------------------------------------- 664.3.4Power-On Reset -------------------------------------------------------------------------------------------------------------------------- 66 4.4 Cache --------------------------------------------------------------------------------------------------------------------------- 66 4.5 Instruction Cache Controller ---------------------------------------------------------------------------------------------- 674.5.1Enabling ICC0/ICC1/SFCC -------------------------------------------------------------------------------------------------------------- 674.5.2Flushing the ICC0/ICC1/SFCC Cache ------------------------------------------------------------------------------------------------ 684.5.3Flushing SRCC Cache -------------------------------------------------------------------------------------------------------------------- 68 4.6 Instruction Cache Controller Registers --------------------------------------------------------------------------------- 68 4.7 External RAM SPIXR Cache Controller (SRCC) ------------------------------------------------------------------------ 71 4.8 RAM Memory Management ---------------------------------------------------------------------------------------------- 714.8.2RAM Low Power Modes --------------------------------------------------------------------------------------------------------------- 71 4.9 Miscellaneous Control Registers ----------------------------------------------------------------------------------------- 72 4.10 Miscellaneous Control Registers Details ------------------------------------------------------------------------------- 73 4.11 Single Inductor Multiple Output (SIMO) Power Supply ------------------------------------------------------------ 754.11.1Power Supply Monitor ------------------------------------------------------------------------------------------------------------------ 76 4.12 Single Inductor Multiple Output (SIMO) Registers ------------------------------------------------------------------ 76 4.13 Single Inductor Multiple Output (SIMO) Registers Details -------------------------------------------------------- 78 4.14 Power Sequencer and Always-On Domain Registers --------------------------------------------------------------- 83 4.15 Power Sequencer and Always-On Domain Register Details ------------------------------------------------------- 84 4.16 Global Control Registers (GCR) ------------------------------------------------------------------------------------------- 92 4.17 Global Control Register Details (GCR) ---------------------------------------------------------------------------------- 92 4.18 Function Control Registers ---------------------------------------------------------------------------------------------- 121 4.19 Function Control Register Details ------------------------------------------------------------------------------------- 121 4.20 AES Key Registers ---------------------------------------------------------------------------------------------------------- 1224.21 AES Key Register Details ------------------------------------------------------------------------------------------------- 1225.Interrupts and Exceptions ------------------------------------------------------------------------------------------ 124 5.1 Features ---------------------------------------------------------------------------------------------------------------------- 1245.2 Interrupt Vector Table --------------------------------------------------------------------------------------------------- 1246.General-Purpose I/O and Alternate Function Pins (GPIO) --------------------------------------------------- 128 6.1 Instances --------------------------------------------------------------------------------------------------------------------- 128 6.2 Usage ------------------------------------------------------------------------------------------------------------------------- 1326.2.1Reset State ------------------------------------------------------------------------------------------------------------------------------ 1326.2.2Input Mode Configuration----------------------------------------------------------------------------------------------------------- 1326.2.3Output Mode Configuration -------------------------------------------------------------------------------------------------------- 1326.2.4Alternate Function Configuration ------------------------------------------------------------------------------------------------- 132 6.3 Configuring GPIO (External) Interrupts ------------------------------------------------------------------------------- 1326.3.1GPIO Interrupt Handling ------------------------------------------------------------------------------------------------------------- 1336.3.2Using GPIO for Wake-up from Low Power Modes ---------------------------------------------------------------------------- 133 6.4 Registers --------------------------------------------------------------------------------------------------------------------- 1346.5 Register Details ------------------------------------------------------------------------------------------------------------ 1357.Flash Controller (FLC) ------------------------------------------------------------------------------------------------ 143 7.1 Instances --------------------------------------------------------------------------------------------------------------------- 143 7.2 Usage ------------------------------------------------------------------------------------------------------------------------- 1437.2.1Clock Configuration ------------------------------------------------------------------------------------------------------------------- 1447.2.3Flash Write Width --------------------------------------------------------------------------------------------------------------------- 1447.2.4Flash Write ------------------------------------------------------------------------------------------------------------------------------ 1447.2.5Page Erase ------------------------------------------------------------------------------------------------------------------------------- 1457.2.6Mass Erase ------------------------------------------------------------------------------------------------------------------------------ 145 7.3 Flash Error Correction Coding ------------------------------------------------------------------------------------------ 145 7.4 Flash Controller Registers ----------------------------------------------------------------------------------------------- 1467.5 Flash Controller Register Details --------------------------------------------------------------------------------------- 1468.External Memory ----------------------------------------------------------------------------------------------------- 151 8.1 Overview --------------------------------------------------------------------------------------------------------------------- 151 8.2 SPI Execute-in-Place Flash (SPIXF) ------------------------------------------------------------------------------------- 1518.2.1SPIXF Master Controller -------------------------------------------------------------------------------------------------------------- 1528.2.2SPIXF Master ---------------------------------------------------------------------------------------------------------------------------- 166 8.3 SPI Execute-in-Place RAM (SPIXR) ------------------------------------------------------------------------------------- 1758.3.1SPIXR Master Controller Registers ------------------------------------------------------------------------------------------------ 1768.3.2SPIXR Register Details ---------------------------------------------------------------------------------------------------------------- 176 8.4 SPIXR Cache Controller (SRCC) ----------------------------------------------------------------------------------------- 1868.4.1Features ---------------------------------------------------------------------------------------------------------------------------------- 1868.4.2Enabling the SRCC --------------------------------------------------------------------------------------------------------------------- 1868.4.3Disabling the SRCC -------------------------------------------------------------------------------------------------------------------- 1868.4.4SRCC Registers -------------------------------------------------------------------------------------------------------------------------- 1868.4.5SRCC Register Details ----------------------------------------------------------------------------------------------------------------- 187 8.5 Secure Digital Host Controller ------------------------------------------------------------------------------------------ 1888.5.1Instances --------------------------------------------------------------------------------------------------------------------------------- 1908.5.2SDHC Peripheral Clock Selection --------------------------------------------------------------------------------------------------- 1918.5.3Usage ------------------------------------------------------------------------------------------------------------------------------------- 1918.5.4SD Command Generation ----------------------------------------------------------------------------------------------------------- 1928.5.5SDHC Registers ------------------------------------------------------------------------------------------------------------------------- 1938.5.6SDHC Register Details ---------------------------------------------------------------------------------------------------------------- 1959.Standard DMA (DMA) ------------------------------------------------------------------------------------------------ 232 9.1 Instances --------------------------------------------------------------------------------------------------------------------- 232 9.2 DMA Channel Operation (DMA_CH) ---------------------------------------------------------------------------------- 2339.2.1DMA Channel Arbitration and DMA Bursts ------------------------------------------------------------------------------------- 2339.2.2DMA Source and Destination Addressing --------------------------------------------------------------------------------------- 2339.2.3Data Movement from Source to DMA ------------------------------------------------------------------------------------------- 2349.2.4Data Movement from the DMA to Destination -------------------------------------------------------------------------------- 2359.4 Count-to-Zero (CTZ) Condition ----------------------------------------------------------------------------------------- 236 9.5 Chaining Buffers ----------------------------------------------------------------------------------------------------------- 236 9.6 DMA Interrupts ------------------------------------------------------------------------------------------------------------ 238 9.7 Channel Timeout Detect ------------------------------------------------------------------------------------------------- 238 9.8 Memory-to-Memory DMA ---------------------------------------------------------------------------------------------- 239 9.9 DMA Registers -------------------------------------------------------------------------------------------------------------- 239 9.10 DMA Register Details ----------------------------------------------------------------------------------------------------- 239 9.11 DMA Channel Register Summary -------------------------------------------------------------------------------------- 239 9.12 DMA Channel Registers -------------------------------------------------------------------------------------------------- 2409.13 DMA Channel Register Details ----------------------------------------------------------------------------------------- 24010.Analog-to-Digital Converter (ADC) and Comparators ----------------------------------------------------- 245 10.1 Features ---------------------------------------------------------------------------------------------------------------------- 245 10.2 Instances --------------------------------------------------------------------------------------------------------------------- 245 10.3 Architecture ----------------------------------------------------------------------------------------------------------------- 245 10.4 Clock Configuration ------------------------------------------------------------------------------------------------------- 247 10.5 Power-Up Sequence ------------------------------------------------------------------------------------------------------ 247 10.6 Conversion ------------------------------------------------------------------------------------------------------------------ 248 10.7 Reference Scaling and Input Scaling ---------------------------------------------------------------------------------- 24810.7.1AIN0 – AIN7 Scale Limitations ------------------------------------------------------------------------------------------------------ 24810.7.2Scale Limitations for All Other Input Channels --------------------------------------------------------------------------------- 24810.7.3Data Conversion Output Alignment ---------------------------------------------------------------------------------------------- 24910.7.4Data Conversion Value Equations ------------------------------------------------------------------------------------------------- 24910.7.5Data Limits and Out of Range Interrupts ---------------------------------------------------------------------------------------- 25010.7.6Power-Down Sequence--------------------------------------------------------------------------------------------------------------- 252 10.8 Comparator Operation --------------------------------------------------------------------------------------------------- 252 10.9 Registers --------------------------------------------------------------------------------------------------------------------- 25210.10 Register Details ------------------------------------------------------------------------------------------------------------ 25211.UART ------------------------------------------------------------------------------------------------------------------ 257 11.1 Instances --------------------------------------------------------------------------------------------------------------------- 257 11.2 UART Frame ----------------------------------------------------------------------------------------------------------------- 257 11.3 UART Interrupts ------------------------------------------------------------------------------------------------------------ 258 11.4 UART Baud Rate Clock Source ------------------------------------------------------------------------------------------ 258 11.5 UART Baud Rate Calculation -------------------------------------------------------------------------------------------- 258 11.6 FIFOs -------------------------------------------------------------------------------------------------------------------------- 26011.6.2Receive FIFO Operation -------------------------------------------------------------------------------------------------------------- 260 11.7 UART Configuration and Operation ----------------------------------------------------------------------------------- 260 11.8 Wake-up Time -------------------------------------------------------------------------------------------------------------- 261 11.9 Hardware Flow Control -------------------------------------------------------------------------------------------------- 261 11.10 Registers --------------------------------------------------------------------------------------------------------------------- 26111.11 Register Details ------------------------------------------------------------------------------------------------------------ 26212.I2C Master/Slave Serial Communications Peripheral (I2C) ------------------------------------------------ 270 12.1 I2C Master and Slave Features ------------------------------------------------------------------------------------------ 272 12.2 Instances --------------------------------------------------------------------------------------------------------------------- 272 12.3 I2C Overview ---------------------------------------------------------------------------------------------------------------- 27212.3.1I2C Bus Terminology ------------------------------------------------------------------------------------------------------------------- 27212.3.2I2C Transfer Protocol Operation --------------------------------------------------------------------------------------------------- 27312.3.3START and STOP Conditions -------------------------------------------------------------------------------------------------------- 27312.3.4Master Operation --------------------------------------------------------------------------------------------------------------------- 27312.3.5Acknowledge and Not Acknowledge --------------------------------------------------------------------------------------------- 27312.3.6Bit Transfer Process ------------------------------------------------------------------------------------------------------------------- 274 12.4 I2C Configuration and Usage -------------------------------------------------------------------------------------------- 27412.4.1SCL and SDA Bus Drivers ------------------------------------------------------------------------------------------------------------- 27412.4.2SCL Clock Configurations ------------------------------------------------------------------------------------------------------------ 27512.4.3SCL Clock Generation for Standard, Fast and Fast-Plus Modes ----------------------------------------------------------- 27512.4.4SCL Clock Generation for Hs-Mode ----------------------------------------------------------------------------------------------- 27612.4.5Master Mode Addressing ------------------------------------------------------------------------------------------------------------ 27712.4.6Master Mode Operation ------------------------------------------------------------------------------------------------------------- 27712.4.7Slave Mode Operation --------------------------------------------------------------------------------------------------------------- 28012.4.8Interrupt Sources ---------------------------------------------------------------------------------------------------------------------- 28412.4.9Transmit FIFO and Receive FIFO --------------------------------------------------------------------------------------------------- 28412.4.10Transmit FIFO Preloading ------------------------------------------------------------------------------------------------------- 28512.4.11Interactive Receive Mode (IRXM) --------------------------------------------------------------------------------------------- 28612.4.12Clock Stretching -------------------------------------------------------------------------------------------------------------------- 28712.4.13Bus Timeout ------------------------------------------------------------------------------------------------------------------------- 28712.4.14DMA Control ------------------------------------------------------------------------------------------------------------------------ 288 12.5 Registers --------------------------------------------------------------------------------------------------------------------- 28812.6 Register Details ------------------------------------------------------------------------------------------------------------ 28913.Serial Peripheral Interface (SPI) -------------------------------------------------------------------------------- 303 13.1 Instances --------------------------------------------------------------------------------------------------------------------- 304。

GSM900M无线宽带室内干放(V2.0 )整机调试说明

深圳国人通信有限公司GSM900M无线宽带室内主干放(500mW、1W、2W、5W)GSM900M无线宽带室内从干放(500mW、1W、2W、5W)整机调试说明文件编号:SGR2.012.946TS版本:V1.0生效日期:编制:部门/职位:开发工程师日期:初审:部门/职位:项目经理日期:复审:部门/职位:部门经理日期:批准:部门/职位:总工程师日期:文件更改履历表目录1 范围 (1)2 测量条件 (1)3 测试所需仪器列表 (1)4 测试连接框图 (1)5 测试附加损耗及测试仪器的校准 (3)6 测试内容及规范 (4)6.1 最大输出功率 (4)6.2 ALC自动电平控制 (4)6.3 最大增益 (5)6.4 增益调节范围 (5)6.5 增益调节步长及步长误差 (5)6.6 带外杂散发射 (5)6.7 互调衰减 (5)6.8 输入输出电压驻波比 (6)6.9 时延测试 (6)6.10 带内波动 (6)6.11 环境实验 (7)6.12 动态老化试验 (7)6.13 监控程序烧录 (7)6.13.1 烧录准备工具: (7)6.13.2 烧录步骤 (7)7 中移协议 (11)7.1 中移协议机型 (11)7.2 调试工具 (11)7.3 调试步骤 (11)7.3.1 配置界面 (11)7.3.2 进入主菜单 (13)7.3.3 设备信息 (13)7.3.4 设置参数 (14)7.3.5 告警和状态 (16)7.3.6 实时采样数据 (18)8 联通协议 (19)8.1 联通协议机型 (19)8.2 调试工具 (19)8.3 调试步骤 (19)8.3.1 配置界面 (19)8.3.2 设置类操作 (21)8.3.3 查询类操作 (25)9 注意事项 (28)1 范 围本文件适用于中移和联通协议,具体可参见各自说明。

2 测量条件应在下列正常工作条件下进行测量:- 温度:+15℃~+35℃ - 相对湿度:45~75%3 测试所需仪器列表信号源Agilent E4438C/E4432B 2台频谱分析仪 Agilent E4405B/E4402B 或 ADVANTEST 1台 矢量网络分析仪Agilent 8573ES 1套 噪声系数仪Agilent N8973A 1套 合路器(3dB ) 1个 衰减器30dB( 25W 以上) 2个 衰减器20 dB( 25W 以上) 1个 隔离器 800M-1G2个4 测试连接框图图2 测试功率、增益、ALC、增益调节步长误差等指标连线图图3 驻波测试连接图图4 波动/时延测试连接图5测试附加损耗及测试仪器的校准如图(1)所示,将信号源与直放站输入端口之间的线损校入信号源,将直放站输入端口与频谱分析仪之间的损耗校入频谱分析仪。

AM335x uboot spl分析

AM335x uboot spl分析芯片到uboot启动流程ROM → SPL→ uboot.img简介在335x 中ROM code是第一级的bootlader。

mpu上电后将会自动执行这里的代码,完成部分初始化和引导第二级的bootlader,第二级的bootlader引导第三级bootader,在ti官方上对于第二级和第三级的bootlader由uboot提供。

SPLTo unify all existing implementations for a secondary program loader (SPL) and to allow simply adding of new implementations this generic SPL framework has been created. With this framework almost all source files for a board can be reused. No code duplication or symlinking is necessary anymore.1> Basic ARM initialization2> UART console initialization3> Clocks and DPLL locking (minimal)4> SDRAM initialization5> Mux (minimal)6> BootDevice initialization(based on where we are bootingfrom.MMC1/MMC2/Nand/Onenand)7> Bootloading real u-boot from the BootDevice and passing control to it.uboot spl源代码分析一、makefile分析打开spl文件夹只有一个makefile 可见spl都是复用uboot原先的代码。

Motorola 3.5 kHz 产品说明书

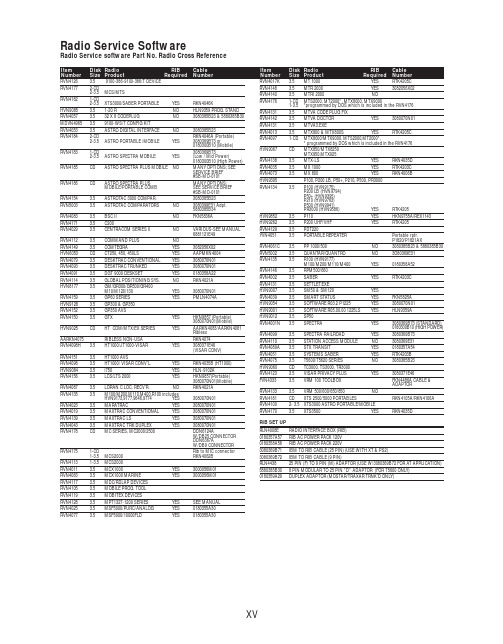

RVN4126 3.59100-386-9100-386/T DEVICERVN41772-CD2-3.5MCS/MTSRVN41821-CD2-3.5XTS3000/SABER PORTABLE YES RKN4046KHVN9085 3.51-20 R NO HLN9359 PROG. STAND RVN4057 3.532 X 8 CODEPLUG NO3080385B23 & 5880385B30 MDVN4965 3.59100-WS/T CONFIG KITRVN4053 3.5ASTRO DIGITAL INTERFACE NO3080385B23RVN41842-CD RKN4046A (Portable) 2-3.5ASTRO PORTABLE /MOBILE YES3080369B73 or0180300B10 (Mobile) RVN41831-CD3080369B732-3.5ASTRO SPECTRA MOBILE YES(Low / Mid Power)0180300B10 (High Power) RVN4185CD ASTRO SPECTRA PLUS MOBILE NO MANY OPTIONS; SEESERVICE BRIEF#SB-MO-0101RVN4186CD ASTRO SPECTRA PLUS MANY OPTIONS;MOBILE/PORTABLE COMB SEE SERVICE BRIEF#SB-MO-0101RVN4154 3.5ASTROTAC 3000 COMPAR.3080385B23RVN5003 3.5ASTROTAC COMPARATORS NO3080399E31 Adpt.5880385B34RVN4083 3.5BSC II NO FKN5836ARVN4171 3.5C200RVN4029 3.5CENTRACOM SERIES II NO VARIOUS-SEE MANUAL6881121E49RVN4112 3.5COMMAND PLUS NORVN4149 3.5COMTEGRA YES3082056X02HVN6053CD CT250, 450, 450LS YES AAPMKN4004RVN4079 3.5DESKTRAC CONVENTIONAL YES3080070N01RVN4093 3.5DESKTRAC TRUNKED YES3080070N01RVN4091 3.5DGT 9000 DESKSET YES0180358A22RVN4114 3.5GLOBAL POSITIONING SYS.NO RKN4021AHVN8177 3.5GM/GR300/GR500/GR400M10/M120/130YES3080070N01RVN4159 3.5GP60 SERIES YES PMLN4074AHVN9128 3.5GP300 & GP350RVN4152 3.5GP350 AVSRVN4150 3.5GTX YES HKN9857 (Portable)3080070N01(Mobile) HVN9025CD HT CDM/MTX/EX SERIES YES AARKN4083/AARKN4081RiblessAARKN4075RIBLESS NON-USA RKN4074RVN4098H 3.5HT1000/JT1000-VISAR YES3080371E46(VISAR CONV)RVN4151 3.5HT1000 AVSRVN4098 3.5HT1000/ VISAR CONV’L.YES RKN4035B (HT1000) HVN9084 3.5i750YES HLN-9102ARVN4156 3.5LCS/LTS 2000YES HKN9857(Portable)3080070N01(Mobile) RVN4087 3.5LORAN C LOC. RECV’R.NO RKN4021ARVN4135 3.5M100/M200,M110,M400,R100 includesHVN9173,9177,9646,9774YES3080070N01RVN4023 3.5MARATRAC YES3080070N01RVN4019 3.5MAXTRAC CONVENTIONAL YES3080070N01RVN4139 3.5MAXTRAC LS YES3080070N01RVN4043 3.5MAXTRAC TRK DUPLEX YES3080070N01RVN4178CD MC SERIES, MC2000/2500DDN6124AW/DB25 CONNECTORDDN6367AW/DB9 CONNECTOR RVN41751-CD Rib to MIC connector 1-3.5MCS2000 RKN4062BRVN41131-3.5MCS2000RVN4011 3.5MCX1000YES3000056M01RVN4063 3.5MCX1000 MARINE YES3000056M01RVN4117 3.5MDC/RDLAP DEVICESRVN4105 3.5MOBILE PROG. TOOLRVN4119 3.5MOBITEX DEVICESRVN4128 3.5MPT1327-1200 SERIES YES SEE MANUALRVN4025 3.5MSF5000/PURC/ANALOG YES0180355A30RVN4077 3.5MSF5000/10000FLD YES0180355A30RVN4017K 3.5MT 1000YES RTK4205CRVN4148 3.5MTR 2000YES3082056X02RVN4140 3.5MTRI 2000NORVN41761-CD MTS2000, MT2000*, MTX8000, MTX90001-3.5*programmed by DOS which is included in the RVN4176RVN4131 3.5MTVA CODE PLUG FIXRVN4142 3.5MTVA DOCTOR YES3080070N01RVN4131 3.5MTVA3.EXERVN4013 3.5MTX800 & MTX800S YES RTK4205CRVN4097 1-CD MTX8000/MTX9000,MTS2000,MT2000*,* programmed by DOS which is included in the RVN4176HVN9067CD MTX850/MTX8250MTX950,MTX925RVN4138 3.5MTX-LS YES RKN4035DRVN4035 3.5MX 1000YES RTK4203CRVN4073 3.5MX 800YES RKN4006BHVN9395 P100, P200 LB, P50+, P210, P500, PR3000RVN4134 3.5P100 (HVN9175)P200 LB (HVN9794)P50+ (HVN9395)P210 (HVN9763)P500 (HVN9941)PR3000 (HVN9586)YES RTK4205HVN9852 3.5P110YES HKN9755A/REX1143 HVN9262 3.5P200 UHF/VHF YES RTK4205RVN4129 3.5PDT220YVN4051 3.5PORTABLE REPEATER Portable rptr.P1820/P1821AXRVN4061C 3.5PP 1000/500NO3080385B23 & 5880385B30 RVN5002 3.5QUANTAR/QUANTRO NO3O80369E31RVN4135 3.5R100 (HVN9177)M100/M200/M110/M400YES0180358A52RVN4146 3.5RPM500/660RVN4002 3.5SABER YES RTK4203CRVN4131 3.5SETTLET.EXEHVN9007 3.5SM50 & SM120YESRVN4039 3.5SMART STATUS YES FKN5825AHVN9054 3.5SOFTWARE R03.2 P1225YES3080070N01HVN9001 3.5SOFTWARE R05.00.00 1225LS YES HLN9359AHVN9012 3.5SP50RVN4001N 3.5SPECTRA YES3080369B73 (STANDARD)0180300B10 (HIGH POWER) RVN4099 3.5SPECTRA RAILROAD YES3080369B73RVN4110 3.5STATION ACCESS MODULE NO3080369E31RVN4089A 3.5STX TRANSIT YES0180357A54RVN4051 3.5SYSTEMS SABER YES RTK4203BRVN4075 3.5T5600/T5620 SERIES NO3080385B23HVN9060CD TC3000, TS3000, TR3000RVN4123 3.5VISAR PRIVACY PLUS YES3080371E46FVN4333 3.5VRM 100 TOOLBOX FKN4486A CABLE &ADAPTORRVN4133 3.5VRM 500/600/650/850NORVN4181CD XTS 2500/5000 PORTABLES RKN4105A/RKN4106A RVN41002- 3.5XTS3000 ASTRO PORTABLE/MOBILERVN4170 3.5XTS3500YES RKN4035DRIB SET UPRLN4008E RADIO INTERFACE BOX (RIB)0180357A57RIB AC POWER PACK 120V0180358A56RIB AC POWER PACK 220V3080369B71IBM TO RIB CABLE (25 PIN) (USE WITH XT & PS2)3080369B72IBM TO RIB CABLE (9 PIN)RLN443825 PIN (F) TO 9 PIN (M) ADAPTOR (USE W/3080369B72 FOR AT APPLICATION) 5880385B308 PIN MODULAR TO 25 PIN ”D” ADAPTOR (FOR T5600 ONLY)0180359A29DUPLEX ADAPTOR (MOSTAR/TRAXAR TRNK’D ONLY)Item Disk Radio RIB Cable Number Size Product Required Number Item Disk Radio RIB Cable Number Size Product Required NumberUtilizing your personal computer, Radio Service Software (RSS)/Customer Programming Software (CPS)/CustomerConfiguration Software (CCS) enables you to add or reprogram features/parameters as your requirements change. RSS/CPS/CCS is compatible with IBM XT, AT, PS/2 models 30, 50, 60 and 80.Requires 640K RAM. DOS 3.1 or later. Consult the RSS users guide for the computer configuration and DOS requirements. (ForHT1000, MT/MTS2000, MTX838/8000/9000, Visar and some newer products —IBM model 386, 4 MEG RAM and DOS 5.0 or higher are recommended.) A Radio Interface Box (RIB) may be required as well as the appropriate cables. The RIB and cables must be ordered separately.Licensing:A license is required before a software (RVN) order is placed. The software license is site specific (customer number and ultimate destination tag). All sites/locations must purchase their own software.Be sure to place subsequent orders using the original customer number and ship-to-tag or other licensed sites; ordering software without a licensed customer number and ultimate tag may result in unnecessary delays. To obtain a no charge license agreement kit, order RPX4719. To place an order in the U.S. call 1-800-422-4210. Outside the U.S., FAX 847-576-3023.Subscription Program:The purchase of Radio ServiceSoftware/Customer Programming/Customer ConfigurationSoftware (RVN & HVN kits) entitles the buyer/subscriber to three years of free upgrades. At the end of these three years, the sub-scriber must purchase the same Radio Service Software kit to receive an additional three years of free upgrades. If the sub-scriber does not elect to purchase the same Radio Service Software kit, no upgrades will be sent. Annually a subscription status report is mailed to inform subscribers of the RSS/CPS/CCS items on our database and their expiration dates.Notes:1)A subscription service is offered on “RVN”-Radio Service Software/Customer Programming/Customer Configuration Software kits only.2)“RVN” software must only be procured through Radio Products and Services Division (RPSD). Software not procured through the RPSD will not be recorded on the subscription database; upgrades will not be mailed.3)Upgrades are mailed to the original buyer (customer number & ultimate tag).4)SP software is available through the radio product groups.The Motorola General Radio Service Software Agreement is now available on Motorola Online. If you need assistance please feel free to submit a “Contact Us” or call 800-422-4210.SMART RIB SET UPRLN1015D SMART RIB0180302E27 AC POWER PACK 120V 2580373E86 AC POWER PACK 220V3080390B49SMARTRIB CABLE (9 PIN (F) TO 9 PIN (M) (USE WITH AT)3080390B48SMARTRIB CABLE (25 PIN (F) TO 9 PIN (M) (USE WITH XT)RLN4488ASMART RIB BATTERY PACKWIRELESS DATA GROUP PRODUTS SOFTWARERVN4126 3.59100-386/9100T DEVICES MDVN4965 3.59100-WS/T CONFIG’TN RVN41173.5MDC/RDLAP DEVICESPAGING PRODUCTS MANUALS6881011B54 3.5ADVISOR6881029B90 3.5ADVISOR ELITE 6881023B20 3.5ADVISOR GOLD 6881020B35 3.5ADVISOR PRO FLX 6881032B30 3.5BR8506881032B30 3.5LS3506881032B30 3.5LS5506881032B30 3.5LS7506881033B10 3.5LS9506881035B20 3.5MINITOR III8262947A15 3.5PAGEWRITER 20008262947A15 3.5PAGEWRITER 2000X 6881028B10 3.5TALKABOUT T3406881029B35 3.5TIMEPORT P7308262947A15 3.5TIMEPORT P930NLN3548BUNIVERSAL INTERFACE KITItem Disk Radio NumberSize Product。

TIAM335x系列处理器6LoWPAN网络参考设计TIDA010032