山东大学08年数字电路期末试卷及答案

数字电子技术期末试卷(2008)(参考答案new)

= AB ⋅ B + D ⋅ CD ⋅ BC + A ⋅ ( ABD) + C + D = AB ⋅ B + D ⋅ CD ⋅ BC + ABD + C + D = AB ⋅ B + D ⋅ CD ⋅ BC + C + D = ⎡⎣ AB + (B + D) + CD⎤⎦ BC + C + D = (B + D)BC + C + D = (B + D)BC + C + D = (B + D)(B + C ) + C + D

= BC + BD + CD + C + D = BC + BD + D + C + D =1

卷总 页第 页

12. Analyze the following sequential circuit (shown in figure 1), derive the logic expressions for flip-flop outputs Q0, Q1, and Y, and determine its state diagrams. (10%)

7

8

9

10

Answer

C

C

B

C

B

B

C

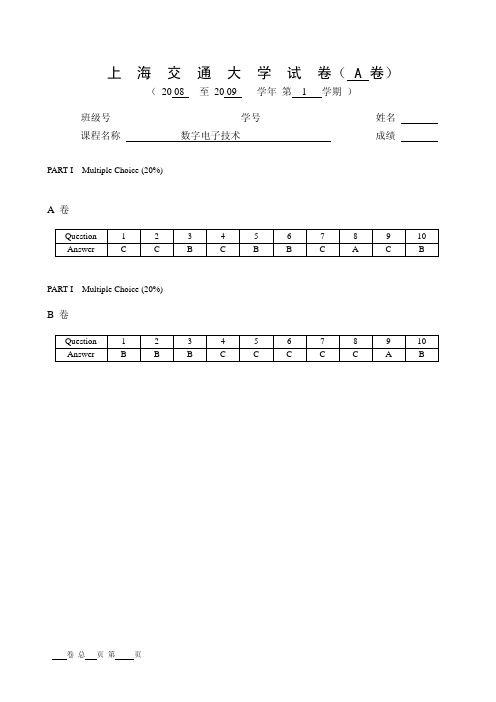

08级数电A(答案)

1

106482804.doc

(15 分) 五、写出下列各触发器的特性方程,并根据图示输入波形画出对应的输出波形。 写出下列各触发器的特性方程,并根据图示输入波形画出对应的输出波形。 ( A

Q n +1 = J Q n + K Q n = ( A ⊕ B )Q + 0Q

n n

= ( A ⊕ B )Q n + Q n = ( A ⊕ B) + Q n

5分 六、 (15 分) 归零逻辑: 归零逻辑:Q3Q2Q1Q0=1011 置数方程: 置数方程: PE = Q3 Q1Q0

0 0 0 0 1 1 1 1

106482804.doc

考试试卷标准答案及评分标准专用纸

A卷

2010 / 2011 学年第 1 学期 课程 数字电子技术 班级 闭卷 姓名

一、单项选择题 (本大题分 10 小题 每小题 2 分,共 20 分) 本大题分 小题,每小题 共 1、(b) 2、(c) 3、(c) 4、(b) 5、(a) 6、(b) 7、(a) 、 、 、 、 、 、 二、(本大题 15 分) 本大题

Y = AB + A C + BC

4分

&

(本大题 四、 本大题 10 分) ( A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 Y 0 1 1 0 1 0 0 1 3分

Y

Y = ∑ m (1,2,4,7) 2 分

Y = Y1 ⋅Y2 ⋅ Y4 ⋅ Y7

8、(b) 9、(c) 10、(b) 、 、

[VIP专享]2008机设数字电路试题A卷答案

![[VIP专享]2008机设数字电路试题A卷答案](https://img.taocdn.com/s3/m/ae5c6088a76e58fafbb0033f.png)

1) B2Ak+22+1=2+15+c51mc+=m5=21c11+m++12+2+1++=212=2+1+2+1+2+2+22+32k+1+2

C. SR 触发器

班级

五

。

总分

。

和 Y = ( AB+CD ) 。

A

B

C

D

& ≥1

(c)

D. 74160 D. T 触发器

阅卷 教师

Y

4分

(第 2 页 共 5 页)

得

分

一、填空题(每空 1 分,共 10 分)

1.1. 十进制数(127)10 转换为十六进制数为 (7F)16

1.2. (+1011)2 的反码为 01011

1.3. 逻辑函数的两种标准形式是 最小项之和 和 最大项之积

,(1101)2 的补码为 10011 。

1.4. 某二进制译码器的输入为 4 位二进制代码,则该译码器共有 16 根输出线。

题

号

得

分

湘潭大学 200 8 年 下学期 2006 级

《数字电路》课程考试试卷

(A 卷) 适用年级专业 2006 级机械设计制造及其自动化

学院

考试方式 闭卷

一二三

学号

专业

四

考试时间 120 分钟

姓名

4.1 4.2 4.3 5.1 5.2

………………………………………………………………………………………………………………

AB BC AC

2分

AB ABC ABC BC ABC ABC ( AB ABC) (BC ABC) ( ABC ABC) 2 分

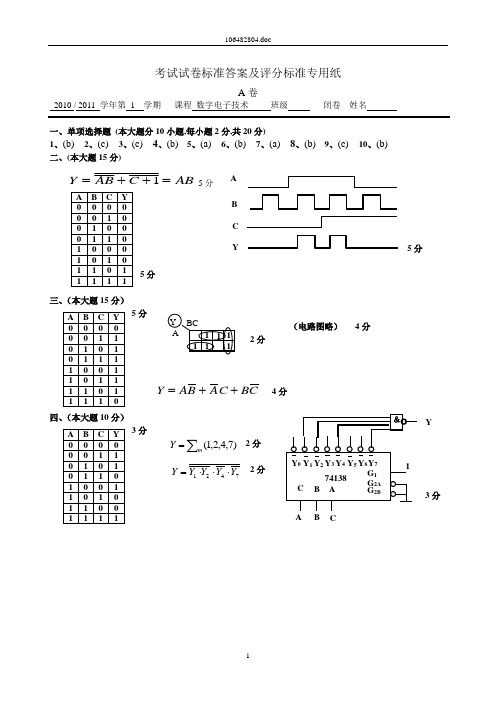

数字电子技术期末考试试题及答案(试卷一)

、 代入规则 对偶规则 反

演规则

、

。

5、为 了 实 现 高 的 频 率 稳 定 度 , 常 采 用 石英晶体

振荡

器 ; 单 稳 态 触 发 器 受 到 外 触 发 时 进 入 暂稳态 态

6、同步 RS 触发器中 R、S 为 高 电平有效,基本 R、S 触发器中 R、S

为低

电平有效

7、在进行 A/D 转换时,常按下面四个步骤进行, 采样 保持 量化 编

码、

、

、。Βιβλιοθήκη 二、选择题(每题 1 分,共 10 分)

1、有八个触发器的二进制计数器,它们最多有(

)种计数状态。

A、8; B、16; C、256; D、64

2、下列触发器中上升沿触发的是( )。

A、主从 RS 触发器;B、JK 触发器;C、T 触发器;D、D 触发器

3、下式中与非门表达式为( d ),或门表达式为(a )。

数字电子技术期末考试试题及答案(试卷一)

目录

数字电子技术期末考试试题及答案(试卷一) ........................................................................... 1 一、填空题(每空 1 分,共 20 分).............................................................................................2 二、选择题(每题 1 分,共 10 分).............................................................................................2 三、判断(每题 1 分,共 10 分):...............................................................................................3 四、数制转化(每题 2 分,共 10 分):.......................................................................................3 五、逻辑函数化简(每题 5 分,共 10 分):...............................................................................3 六、分析电路:(每题 10 分,共 20 分).....................................................................................4 七、设计电路(共 10 分).............................................................................................................4 试题答案(一)...............................................................................................................................5

数字电路试题五套(含答案)汇总

《数字电子技术》试卷一一、 填空(每空1分,共25分)1、(10110)2=( )10=( )16(28)10=( )2=( )16(56)10=( )8421BCD2、最基本的门电路是: 、 、 。

3、有N 个变量组成的最小项有 个。

4、基本RS 触发器的特征方程为_______ ,约束条件是 __.5、若存储器的容量是256×4RAM ,该RAM 有 ___存储单元,有 字,字长_____位,地址线 根。

6、用N 位移位寄存器构成的扭环形计数器的模是________.7、若令JK 触发器的J=K=T 则构成的触发器为_______.8、如图所示,Y= 。

9、如图所示逻辑电路的输出Y= 。

10、已知Y=D AC BC B A ++,则Y = ,Y/= 。

11、组合逻辑电路的特点是_________、___________;与组合逻辑电路相比,时序逻辑电路的输出不仅仅取决于此刻的_______;还与电路 有关。

二、化简(每小题5分,共20分)1、公式法化简++++(1)Y=ABC ABC BC BC A=+++(2)Y ABC A B C2、用卡诺图法化简下列逻辑函数=+++(1)Y BCD BC ACD ABDY=∑+∑(2)(1,3,4,9,11,12,14,15)(5,6,7,13)m d三、设下列各触发器初始状态为0,试画出在CP作用下触发器的输出波形(10分)四、用74LS161四位二进制计数器实现十进制计数器(15分)五、某汽车驾驶员培训班结业考试,有三名评判员,其中A 为主评判员,B 、C 为副评判员,评判时,按照少数服从多数原则,但若主评判员认为合格也可以通过。

试用74LS138和与非门实现此功能的逻辑电路。

(15分)P Q A Q B Q C Q D C T 74LS161 LD CPA B C D CrQ A 、Q B 、Q C 、Q D :数据输出端; A 、B 、C 、D :数据输入端; P 、T :计数选通端;r C :异步复位端;CP :时钟控制输入端;D L :同步并置数控制端;C :位输出端;六、试分析如图电路的逻辑功能,设各触发器的初始状态为0(15分)《数字电子技术》试卷一参考答案一、填空(每空1分,共25分)1、10(22)、16(16);2(11100)、16(1)C ;8421(01010110)BCD 。

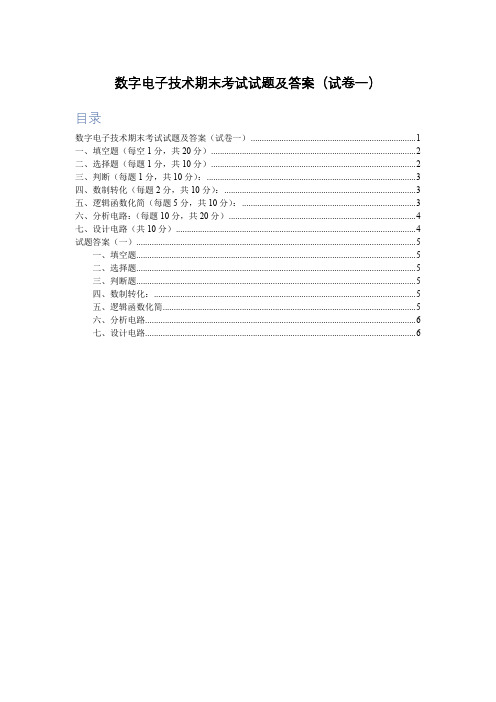

2008年山东大学DSP考试及参考答案

EvaRegs.T1PR=0x2BF1; //周期为150µs=( 11249 + 1 ) / 75MHz

EvaRegs.GPTCONA.bit.T1TOADC=2; //设置EVA(T1)周期匹配启动ADC

EvaRegs.EVAIFRA.bit.T2PINT = 1; //写1清除定时器2的周期中断标志

EvaRegs.T2CNT = 0x0000;

EvaRegs.T2CON.all = 0x1740; //连续增计数,128分频,开启定时器

}

void main(void)

{

InitSysCtrl(); //初始化系统控制寄存器,时钟频率150MHz

IER = 0x0000; //禁止CPU中断

IFR = 0x0000; //清除CPU中断标志

InitPieVectTable(); //初始化PIE中断向量表

EALLOW;

PieVectTable.ADCINT = &adc_isr;

EDIS;

AdcRegs.ADCTRL1.bit.RESET=1;//复位ADC

void InitSysCtrl(void)

{

Uint16 i;

EALLOW; //禁止看门狗模块

SysCtrlRegs.WDCR= 0x0068; //初始化PLL模块

SysCtrlRegs.PLLCR = 0xA; //如果外部晶振为30M,则SYSCLKOUT=30*10/2=150MHz

for(i= 0; i< 5000; i++){}//延时,使得PLL模块能够完成初始化操作

2008级电路期末试卷(答案)

3分

(注:正确写出表达式 P = UI cos ϕ 形式给 2 分) (2) 两组负载总功率:0.6 PT = 42 + 20 = 62 kW QT = Q L = P tan ϕ 1 = 42 tan 53.1° = 56 kvar

tan ϕ 2 = QT = 0.9 , ϕ 2 = 42° PT

1分

λ 2 = cos 42° = 0.74

1分

(3) 由 λ 3 = cos ϕ 3 = 0.9 解得: ϕ 3 = 25.84° 所需并联的电容值: P ( tan ϕ2 − tan ϕ3 ) 62 × 103 × (tan 42° − tan 25.84°) C= T = = 1713.4μF ωU 2 314 × 2202 (注:正确写出公式形式给 3 分) (4) 并联电容后的总电流: PT IT = = 313 A U cos ϕ 3

-5

7分

10VA

6分 3分

5 2 cos ωt + 30 o

6、 10 65 (或 80.62)V

(

)

4分

二、单项选择题:在下列各题中,有四个备选答案,请将其中唯一正确的答案填入题干的括号中。 1. D 2. B 3. C 4. C 5. C 3分 3分 3分 3分 2分

三、非客观题(28 分) 1.(本小题 8 分) 解(1)回路电流法。 选回路电流 I 1 , I 2 , I 3 如图所示:

2

2分 2分

& (由变比关系通过副边电压求解。 (2)求 U ) 0

2

由变比关系可得副边电压

& = 2U & = 2 × (10 − j5) = 20 − j10 V U 2 1 1

2008~2009学年第一学期期末考试试题(A卷).doc

电路分析B 试题 班级 姓名 考号 第 1 页2008~2009学年第一学期期末考试试题(A 卷)题目 一 二 三 四 五 六 七 八 总分数分数 评卷人一、单项选择题:在下列各题中,有四个备选答案,请将其中唯一正确的答案填入题干的括号中。

(本大题共8小题,总计16分)1、图示电路中V1的读数为3V ,V2的读数为4V ,则V 的读数为( ) A. 3V B. 4V C.5V D. 6V2、电路如图所示,电流和电压U 分别为( )A. 1 A ,2VB. 2 A ,20VC. 3 A ,20VD. A ,-10V3、图示电路中,调节电阻的大小使其获得最大功率,当它获得最大功率时,该电路中电压源的供电效率为 ( )A. 50%B. 25 %C. 33.3%D. 83.3%4、图示电路的端口开路电压和电流I分别为( )A. 15 V,2AB. 0 V, 2AC. 9 V, 0.5AD. 9 V, -0.5A5、某支路如图所示,其电压与电流的关系式应为()A. B.C. D.6、图示方框内可能是一个电阻,一个电感,或是一个电容,已知电流)23︒i A,=t+cos(6010电压)t V,则该元件为()+60︒A.电感元件,B.电容元件,C.电阻元件,D.电阻元件,7、图示电路电压U为()A. 9VB. -9VC.1VD. -1V电路分析B 试题班级 姓名 考号 第 2 页8、图示电路在谐振时,电容电压和电阻电压的正确关系式为( )A. 0=-RC U U B. 0=-R C U U C. R C QU U =D. 以上皆非二、在下列各题中,请将题止所要求的解答填入题干中的各横线上方内。

(本大题共6小题,总计24分) (要求尽量写出解题步骤) 1、(2分)图示电路的网孔方程为2、(3分)图示正弦交流电路中,已知()︒-=3010cos 54t u V ,()︒+=3010cos 541t u V ,C =20F ,则电流= 。

大学《数字电路与逻辑设计》期末试卷含答案

大学《数字电路与逻辑设计》试题一、选择、填空、判断题(30分,每空1分)1.和CMOS相比,ECL最突出的优势在于D 。

A.可靠性高B. 抗干扰能力强B.功耗低 D. 速度快2.三极管的饱和深度主要影响其开关参数中的C 。

A.延迟时间t dB. 上升时间t rC. 存储时间t sD. 下降时间t f3.用或非门组成的基本RS触发器的所谓“状态不确定”是发生在R、S 上加入信号D 。

A.R=0, S=0B. R=0, S=1C. R=1, S=0D. R=1, S=14.具有检测传输错误功能的编码是:C 。

A. 格雷码B. 余3码C. 奇偶校验码5.运用逻辑代数的反演规则,求函数F=A̅[B+(C̅D+E̅G)]的反函数F̅:B 。

A.A+B̅C+D̅E+GB.A+B̅(C+D̅)(E+G̅)C.A̅+B(C̅+D)(E̅+G)6.下列叙述中错误的有:C 。

A. 逻辑函数的标准积之和式具有唯一性。

B. 逻辑函数的最简形式可能不唯一。

C. 任意两不同的最小项之和恒等于1。

7. 函数F=(A+B+C̅)(A ̅+D)(C+D)(B+D+E)的最简或与式为:A 。

A.F=(A+B+C ̅)(A ̅+D)(C+D)B.F=(A+B+C ̅)(A ̅+D)C.F=ABC̅+A ̅D+CD 8. 逻辑函数F (A,B,C,D )=∑(1,3,4,5,6,8,9,12,14),判断当输入变量ABCD 分别从(1) 0110→1100,(2) 1111→1010时是否存在功能冒险:B 。

A. 存在,存在 B. 不存在,存在C.不存在,不存在9. 对于K =3的M 序列发生器,反馈函数为Q 2⊕Q 0,则产生M 序列:C 。

A. 1010100 B. 1110101 C. 111010010. 在进行异步时序电路的分析时,由于各个触发器的时钟信号不同,因此我们应该把时钟信号引入触发器的特征方程,对于D 触发器,正确的是:A 。

2007—2008学年 第一学期《数字电子技术》课程考试试卷(B)

2007—2008 2007—2008 学年 第一学期 07 课程考试试卷( 《 数字电子技术 》课程考试试卷(B)

题号 得分

注意:1、本试卷共 4 页 2、考试形式:闭卷 3、考试时间: 120 分钟 4、适用专业: 通信 5、班级、学号、姓名必须写在指定地 一、选择题(每小题 20 分,共 2 分) ( 得分 个。 1. 八 路 数 据 分 配 器 , 其 地 址 输 入 端 有 A.1 B.2 C.3 D.4 2. 为 实 现 将 J K 触 发 器 转 换 为 D 触 发 器 , 应 使 A.J=D,K= D B. K=D,J= D 。 ≤

3.L=Σm(0,1,4,6,9,13)+Σd(2,3,5,7,11,15)

得分

。 三、用四选一数据选择器 74LS153 设计一个 3 变量的多数表决电路。 (每小题 10 分,共 10 分)

B卷

第 2页 共 4 页

得分

四、画波形题(每小题 10 分,共 20 分) 1、主从 JK 触发器的初始状态为 0,CP 和 J、K 信号如图所示,画出其 Q 端波形。 CP J

vO

vC

C

学号

序号

得分

六、如图所示时序逻辑电路,试分析该电路的功能,画出状态图。 (每小题 16 分,共 16 分)

长江大学工程技术学院试卷

班级

姓名

B卷

第 4页 共 4 页

f Im ax

一

二

三

四

五

六

七

总分

阅卷人

序号

。

数字电子技术期末试卷A卷.

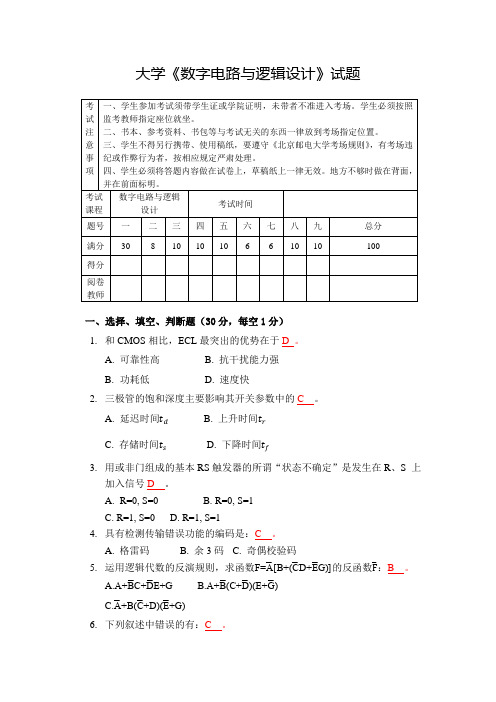

班级(学生填写) 姓名: 学号 命题: 审题 审批: --------------------------------------------------- 密 ---------------------------- 封 --------------------------- 线 -------------------------------------------------(答题不能超出密封线)2008∼2009学年第一学期 数字电子技术基础 科目考试 试题A 卷一、单项选择题(每题2分,共20分)1.由开关组成的逻辑电路如图1所示,设开关A 、B 分别有如图所示为"0"和"1"两个状态,则电灯亮的逻辑式为( )。

(A )B A AB F += (B)AB B A F += (C) B A B A F += (D) AB B A F +=图1 表12.已知某电路的真值表如表1所示,该电路的逻辑关系是( ) (A)F=C (B)F=ABC (C)F=AB+C (D)C C B F +=3.函数)(E D C B A F ⋅⋅+=的反函数F 是( ) (A))(E D C B A ⋅⋅+ (B))(E DC B A ++⋅+ (C))(ED C B A ++⋅+ (D)E D C B A ++⋅+ 4.( )电路在任何时刻只能有一个输出端有效。

(A )二进制译码器 (B )二进制编码器 (C )七段显示译码器 (D )十进制计数器5.分析图示电路的逻辑功能,并选出下列说法中正确的一项:(A)当输入不同时,输出为“1”;当输入相同时,输出为“0” (B)当输入不同时,输出为“0”;当输入相同时,输出为“1” (C)当输入有奇数个“1”时,输出为“1”; 否则为“0” (D)当输入有偶数个“1”时,输出为“1”; 否则为“0”6. 逻辑电路如图所示,输入为 X ,Y ,同它功能相同的是( )。

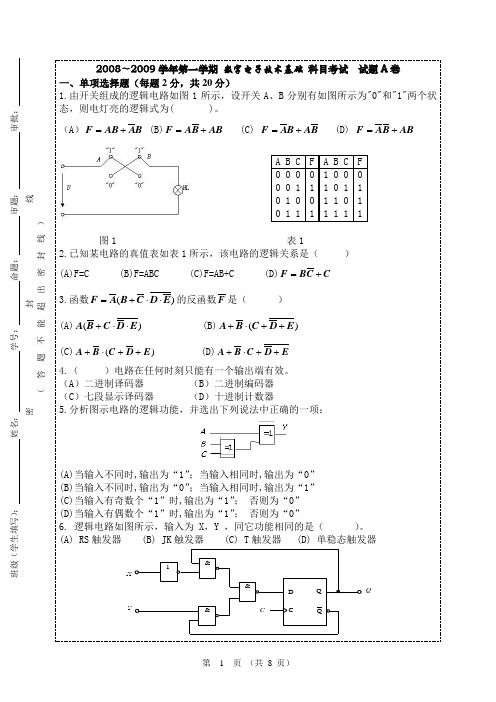

【精品】数字电路期末试题及答案

【精品】数字电路期末试题及答案6 数字电路期末试题及答案6一、选择题1.在数字电路中,下列哪个元件可以用来存储数据?A. 门电路B. 寄存器C. 译码器D. 多路复用器答案:B. 寄存器2.下列哪个逻辑门电路可以实现与非门?A. 与门B. 或门C. 非门D. 异或门答案:C. 非门3.以下哪个选项是正确的?A. 1个字节等于8个位B. 1个字节等于16个位C. 1个字节等于32个位D. 1个字节等于64个位答案:A. 1个字节等于8个位4.在数字电路中,下列哪个元件可以将二进制数据转换为十进制数据?A. 译码器B. 多路复用器C. 寄存器D. 编码器答案:A. 译码器5.在数字电路中,下列哪个元件可以实现多个输入信号的选择?A. 与门B. 或门C. 译码器D. 多路复用器答案:D. 多路复用器二、填空题1.将二进制数1101转换为十进制数________。

答案:132.将十进制数5转换为二进制数________。

答案:1013.在逻辑电路中,当输入信号为0时,与门的输出为________。

答案:04.在逻辑电路中,当输入信号为1时,或门的输出为________。

答案:15.在数字电路中,将两个4位二进制数相加,最多可以得到________位的结果。

答案:5三、简答题1.请解释数字电路中的门电路是如何工作的。

答:门电路是数字电路的基本构建单元,通过接收输入信号并根据特定的逻辑运算规则产生输出信号。

常见的门电路包括与门、或门、非门和异或门等。

与门只有当所有输入信号都为1时,输出信号才为1;或门只有当任意输入信号为1时,输出信号才为1;非门将输入信号取反作为输出信号;异或门只有当输入信号中有且仅有一个为1时,输出信号才为1。

门电路的工作原理是通过逻辑运算实现对输入信号的处理和转换,从而产生所需的输出信号。

2.请解释数字电路中的寄存器的作用和工作原理。

答:寄存器是数字电路中用于存储数据的元件,可以用来暂时存储和保持输入信号的数值。

数字电子技术期末考试试题2答案-2008级

《数字电子技术》考试试卷(第二套)

课程号

考试时间 100 分钟

一、填空题(共30分)

1、(2分)已知带符号二进制数A=(+)B ,则该数用原码表示为A 原

= ,反码表示为A 反= 。

2、(2分)(76)D =( )B = ( 4C )H 。

3、(2分)三态门可能输出的三种状态是低电平、高电平和高阻态_。

4、(2分)在如图所示OD 门构成的电路中,输出函数Z=C AB 。

适用专业年级(方向): 电信、通信、测控、自动化、电气工程、电科、应物2008级

考试方式及要求:

闭卷笔试

西南石油大学试卷第2 页共9 页

西南石油大学试卷第3 页共9 页

西南石油大学试卷第4 页共9 页

西南石油大学试卷第5 页共9 页

图(a)

西南石油大学试卷第6 页共9 页

西南石油大学试卷第7 页共9 页

西南石油大学试卷第8 页共9 页

西南石油大学试卷第9 页共9 页。

2007-2008数字电子技术试卷A答案

2007/2008年第一学期《数字电子技术基础》课程期末考试试卷(A)答案及评分标准姓名: 学号: 专业班级: 总成绩:题号 一 二 三 四 五 总分 得分 核分人一、客观题: 请选择正确答案,将其代号填入( )内;(本大题共10小题,每空2分,共20分)⒈ 当某种门的输入全部为高电平,而使输出也为高电平者,则这种门将是:A .与非门及或非门;B .与门及或门;C .或门及异或门;D .与门及或非门. ( B ) ⒉ 在如下所列4种门电路中,与图示非门相等效的电路是: ( B )⒊ 已知),,,(= , ),,,(54105410M H m F ∏∑=,则函数F 和H 的关系,应 是: ( B )A .恒等;B .反演;C .对偶;D .不确定. ⒋ 若两个逻辑函数恒等,则它们必然具有唯一的:( A )A .真值表;B .逻辑表达式;C .电路图;D .逻辑图形符号. ⒌ 一逻辑函数的最小项之和的标准形式,它的特点是:( C )A .项数最少;B .每个乘积项的变量数最少;C .每个乘积项中,每种变量或其反变量只出现一次;D .每个乘积项相应的数值最小,故名最小项. ⒍ 双向数据总线可以采用( B )构成。

A .译码器;B .三态门;C .与非门;D .多路选择器. ⒎ 在下列逻辑部件中,不属于组合逻辑部件的是( D)。

A .译码器;B .编码器;C .全加器;D .寄存器. ⒏ 八路数据选择器,其地址输入端(选择控制端)有( C )个。

A .8个B .2个C .3个D .4个得分 评卷人 复查人⒐ 为将D 触发器转换为T 触发器,如图所示电路的虚线框内应是( D )。

A .或非门 B .与非门 C .异或门 D .同或门⒑ 为产生周期性矩形波,应当选用( C ).A .施密特触发器B .单稳态触发器C .多谐振荡器D .译码器二、化简下列逻辑函数。

(每题5分,共10分)⒈ 用公式法化简逻辑函数:B A BC A Y += ⒉ 用卡诺图法化简逻辑函数:Y(A ,B,C,D)=∑m(2 ,3,7,8,11,14) 给定约束条件为m 0+m 5+ m 10+m 15 =0 解⒈分)分)114()()((=++++=++++=+=C B B A A B A C B A BA BC A Y解⒉:作出Y 的卡诺图(3分), 化简得:CD D B AC Y ++=(2分)三、非客观题(本题两小题,共20分)⒈ 如图所示为三输入变量的或门和与门的逻辑图.根据两种不同的输入波形(见图b )画出Y 1、Y 2的波形。

山东大学网络教育数字电子技术基础期末考试复习题

7 数字电子技术基础 模拟卷1

一、单项选择题

1、将十进制数56转换成8421BCD 码应是: ( )

A 、(56)10= (0011 1000)8421BCD

B 、(56)10= (0011 1001)8421BCD

C 、(56)10= (0101 1000)8421BC

D D 、(56)10= (0101 0110)8421BCD

2、使晶体三极管工作于饱和区的电压条件是: ( )

A 、发射结正偏,集电结反偏

B 、发射结反偏,集电结反偏

C 、发射结正偏,集电结正偏

D 、发射结反偏,集电结正偏

3、只有当两个输入变量的取值相同时,输出才为1,否则输出为0,这种逻辑关系叫做: ( )

A 、同或

B 、与非

C 、异或

D 、或非

4、在功能表中×的含义是: ( )

A 、表示高电平

B 、表示低电平

C 、高低电平都不可以

D 、高低电平都可以

5、下列4个电路中能实现AB L 逻辑关系的是: ( )

L A

A ≥1&

B B B A L

1

L =1B A =1

A B C D

6、TTL 门电路理论上的逻辑低电平为: ( )

A 、0V

B 、0.3V

C 、1.4V

D 、1.8V

7、下列电路中不属于时序逻辑电路的是: ( )。

山东大学数字电子技术期末试卷及答案.

D 0 D 1 D2 D 3

EP

CO

ET

74161

LD

CP

RD

Q 0 Q1 Q2 Q3

111 1 11 0 111 0

图 5.2

计数 保 持 , CO =0

保持

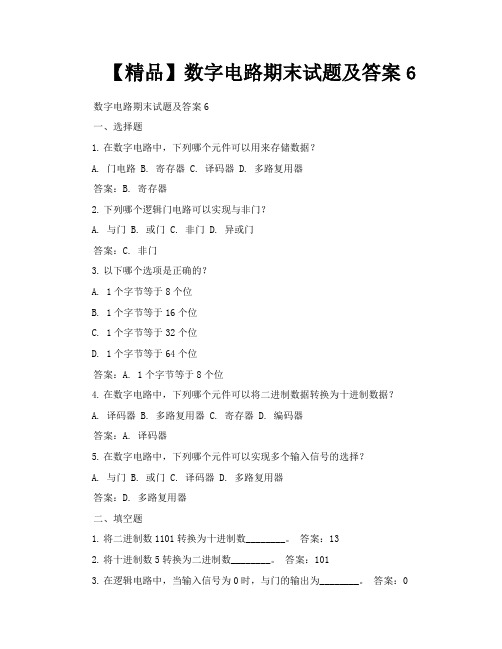

试卷 A_解答

一、选择题(从每小题的四个备选答案中,选出一个正确答案,并将其号码填在括号内, 每小题 2 分,共 20 分)

1. ② 2. ① 3. ③ 4. ① 5. ③ 6. ① 7. ① 8. ④ 9. ④ 10. ①

二、填空题(把正确的内容填在题后的括号内。每空

1 . ∑ m(2,4,6,7,9,11,12,13,15) ∑ m(1,5,7,10,12,14,15) ∏ M(1,5,7,10,12,14,15) ∏ M(0,2,3,4,6,8,9,11,13)

2. PLA, PAL, GAL, CPLD 等 3. 8 , 2 , 2-4

1.8 选 1 数据选择器 CC4512 的逻辑功能如表 4.1 所示。 试写出图 4.1 所示电路输出端 F 的最简与或形式的表达式。 ( 9 分)

INH A 2 A1 A 0

Y

0

0 000

D0

0

0 001

D1

0

0 010

D2

0

0 011

D3

0

0 100

D4

0

高位的借位为 CO。完成对 PLA 逻辑阵列图的编程。 ( 10 分)

D,向

A

或

B

阵 列

C

D

或阵列

CO

图 5.1 PLA 逻辑阵列图

2. 试用 555 定时器设计一个多谐振荡器,要求输出脉冲的振荡频率为 于 60%,积分电容等于 1000 pF 。( 10 分)

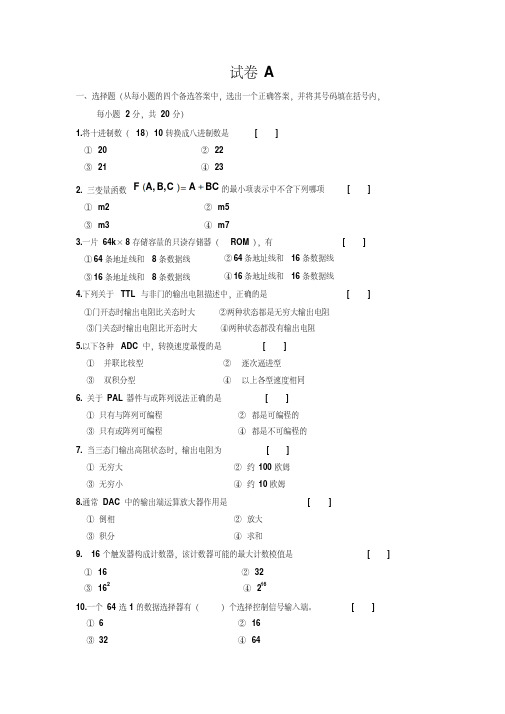

数字逻辑电路期末考试试卷及答案

数字逻辑电路期末考试试卷及答案-CAL-FENGHAI.-(YICAI)-Company One1XXXX大学2007-2008学年第一学期期末考试试题(答案)考试科目:数字逻辑电路试卷类别:3卷考试时间:110 分钟 XXXX学院 ______________系级班姓名学号题号一二三四总分得分一、选择题(每小题2分,共20分)1.八进制(273)8中,它的第三位数2 的位权为___B___。

A.(128)10 B.(64)10 C.(256)10 D.(8)102. 已知逻辑表达式CBCAABF++=,与它功能相等的函数表达式_____B____。

A.ABF=B.CABF+=C.CAABF+=D.CBABF+=3. 数字系统中,采用____C____可以将减法运算转化为加法运算。

A.原码 B.ASCII码 C.补码 D. BCD码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A.与关系B.异或关系C.同或关系D.无法判断得分评卷人装订线内请勿答题235. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6. 与逻辑函数D C B A F +++= 功能相等的表达式为___C_____。

A . D C B A F +++= B . D C B A F +++= C . D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。

8. 如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。

A . 500KHzB .200KHzC . 100KHzD .50KHz9.下列器件中,属于时序部件的是_____A_____。

A.计数器B.译码器C.加法器D.多路选择器10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。