EDA在数字频率计中计数模块里的应用

EDA实验4 频率计

EDA技术参考实验报告实验名称:数字频率计的设计及实现指导老师:沈晓峰2013年11月实验任务四1、实验题目:数字频率计的设计及实现2、实验要求:1)用VHDL完成8位数字频率计的设计, 该频率计要求频率测量范围:1 Hz ~20 MHz;测量误差≤0.1%;具有清零复位功能;频率测量结果用八位数码管稳定显示;用VHDL设计七段LED译码显示电路;2)用实验系统箱实现该频率计,并用数码管显示所测的频率值。

下载该程序验证程序是否正确;3、实验目的:1)学会数字频率计的设计方法2)掌握自顶向下的设计方法,体会其优越性;参考实验报告四一.实验原理与内容1.测频原理若某一信号在T秒时间里重复变化了N 次,则根据频率的定义可知该信号的频率fs 为:fs=N/T 通常测量时间T取1秒或它的十进制时间。

频率计方框图如下:1)时基T 产生电路:提供准确的计数时间T。

晶振产生一个振荡频率稳定的脉冲,通过分频整形、门控双稳后,产生所需宽度的基准时间T的脉冲,又称闸门时间脉冲。

注意:分频器一般采用计数器完成,计数器的模即为分频比。

2)计数脉冲形成电路:将被测信号变换为可计数的窄脉冲,其输出受闸门脉冲的控制。

3)计数显示电路:对被测信号进行计数,显示被测信号的频率。

计数器一般采用多位10 进制计数器;控制逻辑电路控制计数的工作程序:准备、计数、显示、复位和准备下一次测量。

2、具体实现:1) 测频控制逻辑电路(以1 秒为例)2)产生一个1秒脉宽的周期信号;3)对计数器的每一位计数使能进行控制;4)完成下一次测量前的计数器复位;以下是一种可能的时序关系:5)10 进制计数器要求具有计数使能端CNTEN、复位端CLR、进位输出端CO。

3、组件例化图(方框图):注意:用8个十进制计数器实现1MHz 计数。

二.设计文件及编译处理(一)十进制计数器的基本原理计数器在每个时钟的上升沿自加,并且具有自动进位输出的管脚1)计数模块的程序2)计数模块的时序仿真图中的清零和使能信号均发挥作用图中clk为参考时钟;EN为计数使能信号;RESET为测频清零信号。

EDA简易数字频率计设计

EDA简易数字频率计设计摘要EDA(Electronic Design Automation)是电子设计自动化的缩写,是现代电子工业领域中的一种重要工具。

EDA工具可以帮助工程师完成电路设计、仿真、验证和布局等工作,从而提高设计效率和精度。

本文将介绍如何通过EDA工具设计一个简单的数字频率计。

设计原理数字频率计是一种可以实时测量电信号频率的仪器。

其工作原理是利用计数模型,通过计算信号周期数与时间,间隔测算信号频率。

本文设计的数字频率计采用2种常见的计数模型:频率分频计数和门限计数。

频率分频计数频率分频计数法是利用可编程可除模块,将输入的高频脉冲信号分频后,通过计数器来计算脉冲个数,最终计算出信号的频率。

其计数原理如下图所示:图1:频率分频计数法图1:频率分频计数法其中,n为分频系数,f为输入信号频率。

门限计数门限计数法是将输入信号经过比较门限后,产生一个矩形脉冲,再利用计数器计算脉冲个数,最终计算出信号的频率。

其计数原理如下图所示:图2:门限计数法图2:门限计数法其中,T表示输入信号周期,Δt为门限宽度。

设计流程本文采用EDA工具LTspice进行数字频率计的设计。

使用LTspice的原因是它是一款功能强大、易于学习、免费的EDA软件,广泛应用于电路设计和仿真领域。

设计流程如下:1.确定输入信号的电路参数:输入信号频率、振幅、时钟等。

2.选择计算频率的计数模型:这里采用频率分频计数和门限计数2种模型,建立计算模型电路。

3.进行仿真,测试电路的性能:可以通过分析波形图、输出计数结果等方式验证电路的正确性和有效性。

设计实例本文将以一个简单的设计实例来说明如何进行数字频率计的设计。

假设输入信号频率为1 kHz,振幅为5V,计数器工作电压为3.3V,门限计数的门限宽度为10 us,计数模型电路如下图所示:V1 IN 0 PULSE(0 5 0 10n 10n 1u 2u)R1 IN N1 50C1 N1 N2 10nD1 N2 0 DQ1 D Q3 VCC TXR2 TX N3 1megC2 N3 0 1uXU1 Q3 CLK TX DFFXU2 CLK 0 N5 D2R3 D2 N7 10kC3 N7 0 1n以上代码中,V1为输入信号源,R1和C1组成低通滤波器,滤除杂波信号,D1、Q1、R2、C2和D2构成频率分频计数器,XU1和XU2分别为D触发器和门限计数器。

计数器eda实验报告

计数器eda实验报告计数器EDA实验报告引言:计数器是数字电路中常见的基本模块之一,用于计算和记录输入脉冲信号的数量。

在本次实验中,我们将使用EDA工具对计数器进行设计和分析。

通过对计数器的EDA实验,我们旨在深入了解计数器的工作原理和性能特点。

一、实验目的本次实验的目的是通过EDA工具对计数器进行设计和分析,具体包括以下几个方面:1. 了解计数器的基本原理和工作方式;2. 学习使用EDA工具进行电路设计和仿真;3. 分析计数器的性能指标,如最大计数值、计数速度等。

二、实验步骤1. 设计计数器的电路原理图;2. 使用EDA工具进行电路仿真;3. 分析仿真结果,包括计数器的计数规律、计数速度等;4. 调整计数器的参数,观察对计数结果的影响;5. 总结实验结果并提出改进意见。

三、计数器的设计原理计数器是由触发器和逻辑门组成的电路,可以实现对输入脉冲信号的计数功能。

常见的计数器包括二进制计数器、十进制计数器等。

在本次实验中,我们将设计一个4位二进制计数器。

四、EDA工具的使用我们选择使用Xilinx ISE Design Suite进行电路设计和仿真。

该工具具有强大的功能和易于使用的界面,方便我们进行计数器的设计和分析。

五、仿真结果分析通过对计数器的仿真结果进行分析,我们可以得到以下结论:1. 计数器的计数规律:根据计数器的设计原理,我们可以观察到计数器的计数规律为二进制递增。

2. 计数器的计数速度:计数器的计数速度取决于输入脉冲信号的频率和计数器的时钟频率。

通过适当调整时钟频率,我们可以实现不同速度的计数。

六、参数调整与性能改进在实验过程中,我们可以通过调整计数器的参数来改进其性能。

例如,我们可以增加计数器的位数,以提高其计数范围;或者调整计数器的时钟频率,以改变其计数速度。

通过不断优化和改进,我们可以得到更加高效和灵活的计数器设计。

七、实验总结通过本次计数器EDA实验,我们深入了解了计数器的工作原理和性能特点,并学会了使用EDA工具进行电路设计和仿真。

EDA课程设计数字频率计

目录前言 (1)1. 总体设计方案 (2)1.1总体设计方案 (2)2. 单元模块设计 (2)2.1十进制计数器设计 (2)2.1.1 十进制计数器原件cnt10设计 (2)2.1.2 位十进制计数器的顶层设计 (4)2.2闸门控制模块EDA设计 (5)2.2.1 定时信号模块Timer (5)2.2.2 控制信号发生器模块T_con (7)2.3译码显示模块 (8)2.3.1 显示寄存器设计 (8)2.3.2 译码扫描显示电路 (9)2.3.3 译码显示模块的顶层电路设计 (12)3. 软件测试 (13)3.1测试的环境 (13)3.2调试和器件编程 (14)4. 设计总结 (15)5. 参考文献 (15)前言在电子技术高度发展的今天,各种电子产品层出不穷,而频率作为设计的最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程的自动化等优点。

数字频率计是一种用十进制数字显示被测信号频率的数字测量仪器,它的基本功能是测量正弦信号、方波信号、尖脉冲信号以及其它各种单位时间内变化的物理量。

当今国内外厂家生产的数字频率计在功能和性能方面都比较优良,而且还在不断发展中,但其结构比较复杂,价位也比较高,在测量精准度要求比较低的测量场合,使用这些数字频率计就不够经济合算。

我所设计的这款数字频率计能够可靠实现频率显示功能,原理及结构也比较简单本次所做的课程设计就是一个数字频率计,能测量1HZ~9999HZ的矩形波信号,并正确地显示所测信号的频率值。

数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。

随着现场可编程门阵列FPGA 的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

EDA报告(数字频率计)

课程设计说明书课程设计名称:EDA技术课程设计题目:学生姓名:专业:学号:指导教师:胡兵日期:2009年 6月 20 日成绩1 前言1.1序言在电子工程,资源勘探,仪器仪表等相关应用中,频率计是工程技术人员必不可少的测量工具。

频率测量也是电子测量技术中最基本最常见的测量之一。

不少物理量的测量,如转速、振动频率等的测量都涉及到或可以转化为频率的测量。

目前,市场上有各种多功能、高精度、高频率的数字频率计,但价格不菲。

为适应实际工作的需要,本文在简述频率测量的基本原理和方法的基础上,提供一种基于FPGA的数字频率计的设计和实现过程,本方案不但切实可行,而且具有成本低廉、小巧轻便、便于携带等特点。

1.2 设计背景在eda(电子设计自动化)在电子设计中起着越来越重要的作用的时候,我们进行EDA课程设计,以增强我们的动手和综合能力。

我们选择了数字频率计设计这个课题,因为数字频率计的应用范围很广。

数字频率计在测量其他物理量如转速、振动频率等方面也获得广泛应用。

数字频率计的设计方法也有多种,如模拟数字方法,单片机设计,基于fpga用verilog设计方法。

由于Verilog HDL设计有诸多优点,所以我们选择了Verilogs设计方法。

1.3 数字频率计分类国际上数字频率计的分类很多。

按功能分类,因计数式频率计的测量功能很多,用途很广。

所以根据仪器具有的功能,电子计数器有通用和专用之分。

(1)通用型计数器:是一种具有多种测量功能、多种用途的万能计数器。

它可测量频率、周期、多周期平均值、时间间隔、累加计数、计时等;若配上相应插件,就可测相位、电压、电流、功率、电阻等电量;配上适当的传感器,还可进行长度、重量、压力、温度、速度等非电量的测量。

(2)专用计数器:指专门用来测量某种单一功能的计数器。

如频率计数器,只能专门用来测量高频和微波频率;时间计数器,是以测量时间为基础的计数器,其测时分辨力和准确度很高,可达ns数量级;特种计数器,它具有特种功能,如可逆计数器、予置计数器、差值计数器、倒数计数器等,用于工业和白控技术等方面。

EDA数字频率计

课程设计说明书课程设计名称:EDA技术课程设计题目:数字频率计电路设计学生姓名:专业:学号:指导教师:日期:2013年6月 28日成绩摘要数字频率计利用复杂可编程逻辑器件FPGA,VHDL编程将所有功能模块集成在一块芯片上。

功能模块包括时基脉冲发生器、计数器、数据锁存器和显示电路4部分。

设计时先分别设计各功能模块,并调试得到正确仿真结果,然后将各个功能模块组合起来。

最后作整体仿真、下载,得到实物。

由于采用纯数字硬件设计制作,稳定性、可靠性远远高于使用单片机或模拟方式实现的系统,外围电路简单。

该数字频率计达到预期要求,实现了可变量程测量,测量范围1HZ~10KHZ,精度可达0.1Hz。

关键词:数字频率计 FPGA VHDLAbstract:The digital cymometer utilize CPLD (complex programmable logicdevice) integrate several functional modules onto one single chip by programming with VHDL. The five functional modules are timebase generator , counter, data flip-latch and display circuit. First design the functional module and get the expected simulation results, then ensemble them into one. After that the final simulation and download was done and the product can be made. Due to the use of digital hardware designing,the stability and reliability are far more higher compared to those singlechip or anolog implemented system. The digital cymometer could achieve the expected requirement. The measurement range from 0.1Hz to 9999MHz , with the accuracy up to 0.1Hz.Keywords: Digital, symometer , FPGA , VHD L前言所谓频率,就是周期性信号在单位时间(1s)里变化的次数。

EDA9081计数测频模块

EDA9081 计数/测频模块使用说明书山东力创科技有限公司EDA9081 计数/测频模块使用说明书一、EDA9081计数/测频模块主要性能简介EDA9081是EDA9080的升级产品,增加了LC-02十六进制通讯协议及可同时测频率与计数功能,最低频率可测到0.01Hz。

其使用范围得以扩大,如输入流量脉冲信号,则可测出累计流量与瞬时流量。

EDA9081计数/测频模块可测量:2路频率或脉冲计数输入信号。

EDA9081模块可广泛应用于各种工业控制与测量系统中。

它能测量工频频率、流量计量、变送器脉冲输出测量等。

其输出为485总线方式,ASCII码指令集兼容于NuDAM、ADAM等模块,可与其他厂家的控制模块挂在同一485总线上,便于计算机编程。

其功能与技术指标如下:●输入信号:输入:2路独立的光电隔离输入。

应用于计数时:脉冲宽度 >100 uS ,信号高电平5V—24V 。

最大计数值:FFFFFFFFH。

应用于测频时:频率范围为:0.01Hz----3 KHz,输入电压范围为 0.5---1.5 倍标称量程。

●隔离电压:2500V●通讯输出:接口:RS-485接口,二线制,±15KV ESD保护。

协议:双协议,ACSII码格式与LC-02格式。

速率:1200、2400、4800、9600、19200 Bps ,可软件设定。

模块地址:。

●模块电源:+ 8 ~ 30V DC *功耗:典型电流消耗为15 mA。

●工作环境:工作温度:-20℃~70℃;存储温度:-40℃~85℃;相对湿度:-5%~95%不结露●安装方式:DIN导轨卡装体积:122mm *70mm * 43mm二、EDA9081计数/测频模块外形结构图、引脚定义与功能框图1、EDA9081计数/测频模块外形结构图如下:2、EDA9081计数/测频模块引脚定义如下:引脚号名称描述6 INIT* 复位端(功能保留)7 (Y)DATA+ RS-485接口信号正极8 (G)DATA- RS-485接口信号负极9 +VCC 电源正,+10V~30V10 GND 电源负,地11 V1+ 内部未连接,扩展1通道输入时,从此到Vin1+接一电阻,信号从此引脚输入13 Vin1+ 输入1通道信号+14 Vin1- 输入1通道信号-17 V0+ 内部未连接,扩展0通道输入时,从此到Vin0+接一电阻,信号从此引脚输入19 Vin0+ 输入0通道信号+20 Vin0- 输入0通道信号-其他NC 未连接注:LED指示灯:上电后,模块正常运行状态下亮,通讯发数时灭。

EDA实验报告数字频率计

河南工业大学EDA技术实验报告

专业电科班级1202 姓名高兆华学号201216030211

实验地点6316+ 6515 实验日期2014-11-25成绩评定

一、实验项目

简易数字频率计

二、实验目的

根据已经学习的有关知识,如计数器、锁存器、扫描器、译码器、分频器等,再根据频率的定义,我们来设计一个简易的数字频率计,它的计数范围在0~99999999Hz 之间,并让误差尽可能的小,所以根据这个定义我们很容易想到它所用到的核心原理与模块。

三、实验原理

计数器模块:

分频器模块:

数码管显示模块:

32位译码器模块:

电路原理图:

四、仿真结果及分析

五、硬件验证过程及结果分析

我用CLOCK9作为输入频率,用CLOCK0作为待测信号,通过连接CLOCK0上的跳帽可以改变待测信号的频率。

通过验证,基本可以测出待测信号的频率,并且误差范围较小,基本满足了实验要求。

六、实验总结

通过这次频率计的设计,让我对以往所学的模块又进行了一次系统的复习。

因为这是一个比较综合的实验,涉及到的模块知识也比较多。

这就要求我们既要弄懂各个模块的功能和作用,又能够把各个模块相融合。

通过不断的编译仿真,终于得到了我想要的实验结果,同时也系统的将以往所学内容进行了一下总结,这是一次受益匪浅的实践。

EDA技术与应用实践学习内容(数字频率计之分频模块)

技能点十五(数字频率计之分频模块)该模块的主要作用是选择不同的分频进而改变闸门时间以切换频率测量范围。

clk_1k 为外部1KHz 的基准时钟信号,keyin 为档位选择按键,当keyin 的值为为“11”时,基准信号不分频;为“10”时,对基准信号进行10分频,得到频率为100Hz 的脉冲信号;为“01”时,对100Hz 的脉冲信号再进行10分频,得到10Hz 的脉冲信号;为“00”时,对10Hz 的脉冲信号进一步进行10分频,得到1Hz 的脉冲信号。

该模块的接口电路如图 6 - 16所示,相应的VHDL 程序代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY switch IS PORT(clk_1k:IN STD_LOGIC;keyin:IN STD_LOGIC_VECTOR(1 DOWNTO 0);--档位选择开关clkout:OUT STD_LOGIC); --闸门信号(时间)输出 END switch;ARCHITECTURE rtl OF switch ISSIGNAL cnt0,cnt1,cnt2:INTEGER RANGE 0 TO 4;SIGNAL clk_100,clk_10,clk_1:STD_LOGIC;BEGINu1:PROCESS(clk_1k) --对1KHz 进行10分频BEGINIF clk_1k'EVENT AND clk_1k='1' THENIF cnt0=4 THENcnt0<=0;clk_100<=NOT clk_100;ELSEcnt0<=cnt0+1;END IF;END IF;END PROCESS u1;u2:PROCESS(clk_100) --对100Hz 进行10分频BEGINIF clk_100'EVENT AND clk_100='1' THENIF cnt1=4 THENcnt1<=0;clk_10<= NOT clk_10;ELSEcnt1<=cnt1+1;END IF;END IF;END PROCESS u2;u3:PROCESS(clk_10) --对10Hz 进行10分频BEGINIF clk_10'EVENT AND clk_10='1' THENIF cnt2=4 THENcnt2<=0;clk_1<=NOT clk_1;ELSEcnt2<=cnt2+1;END IF;END IF;END PROCESS u3;u4:PROCESS(keyin,clk_1k,clk_100,clk_10,clk_1) --档位选择开关选择不同的闸门时间 BEGINIF keyin="00" THEN clkout<=clk_1;ELSIF keyin="01" THEN clkout<=clk_10;ELSIF keyin="10" THEN clkout<=clk_100;ELSE clkout<=clk_1k;END IF;END PROCESS u4;图 6 - 1档位选择模块 switch inst clk_1k key in[1..0]clkout。

EDA简易数字频率计-课设报告1

《EDA技术》课程设计报告题目:简易数字频率计专业:本组成员:简述随着数字电子技术的发展,频率测量成为一项越来越普遍的工作,因此测频计常受到人们的青睐。

目前许多高精度的数字频率计都采用单片机加上外部的高速计数器来实现,然而单片机的时钟频率不高导致测频速度比较慢,并且在这种设计中,由于PCB版的集成度不高,导致PCB板走线长,因此难以提高计数器的工作频率。

为了克服这种缺点,大大提高测量精度和速度,我们可以设计一种可编程逻辑器件来实现数字频率计。

EDA技术是以大规模可编程逻辑器件为设计载体,以硬件语言为系统逻辑描述的主要方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件设计的电子系统到硬件系统的设计,最终形成集成电子系统或专用集成芯片的一门新技术。

其设计的灵活性使得EDA技术得以快速发展和广泛应用。

以QUARTUSII软件为设计平台,采用VHDL 语言实现数字频率计的整体设计。

EDA技术已经广泛应用于模拟与数字电路系统等许多领域。

电子设计自动化是一种实现电子系统或电子产品自动化设计的技术,它与电子技术,微电子技术的发展密切相关,它吸收了计算机科学领域的大多数最新研究成果,以高性能的计算机作为工作平台,促进了工程发展。

EDA的一个重要特征就是使用硬件描述语言(HDL)来完成的设计文件,VHDL语言是经IEEE确认的标准硬件语言,在电子设计领域受到了广泛的接受。

1.设计概述1.1设计原理在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

数字式频率计的测量原理有两类:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法即测周期法,如周期测频法。

EDA课程设计——数字频率计的设计

《电子设计自动化(EDA)技术》课程设计报告书题目: 数字频率计的VHDL设计姓名:院系:专业:学号:指导教师:完成时间: 年月日课程设计题目、内容、要求目录1 课程设计题目、内容与要求……………………………………1.1 设计内容……………………………………………………1.2 具体要求……………………………………………………2 系统设计…………………………………………………………2.1 设计思路……………………………………………………2.2 系统原理与设计说明3 系统实现…………………………………………………………4 系统仿真…………………………………………………………5 硬件验证(操作)说明…………………………………………6 总结……………………………………………………………7 参考书目………………………………………………………1 课程设计题目、内容与要求1.1课程设计的题目:数字频率计设计1.2课程设计内容:(1)设计一个能测量方波信号的频率计;(2)测量范围是0-999999Hz;(3)结果用十进制数显示。

2 系统设计2.1设计思路:2.1.1 数字频率计是一种用十进制数字显示被测信号频率的数字测量仪器.它的基本功能是测量方波信号及其他各种单位时间内变化的物理量。

本数字频率计采用自顶向下的设计思想,通过闸门提供的1s闸门时间对被测信号进行计数及测出的被测信号的频率,测出的频率再通过译码器译码后输出给显示器显示。

根据系统设计的要求,数字频率计的电路原理框图如下:2.2 系统原理与设计说明系统各个模块的功能如下:2.2.1标准时钟发生电路模块借用实验板上标准时钟发生电路,为计数闸门控制电路提供一个标准8Hz信号。

2.2.2 计数器闸门控制电路模块计数器闸门控制电路就是产生三个控制信号,即计数器复位信号、4位十进制计数器允许计数信号、锁存信号。

2.2.3锁存电路模块锁存电路就是为了让LED数码管在信号来临之前保持计数值不变。

EDA实验四数字频率计实验报告

EDA技术与应用实验报告学院:电气与信息工程学院班级:指导老师:谭会生老师姓名:学号:实验四:数字频率计的设计一.实验目的(1)熟悉artus I/ISE Suite/ispLEVNRI软件的基本使用方法。

(2)熟悉和掌握GW48-CK或其他EDA实验开发系统的使用。

(3)学习VHDL程序中数据对象、数据类型、顺序语句和并行语句的综合使用。

二.实验条件与要求(1)开发软件:Quartus II 9.0(2)实验设备:PC、GW48-CK EDA实验开发系统。

(3)画出系统的原理框图,说明系统中各个主要功能、编写各个VHDL源程序。

画出输入信号波形并调试和仿真。

三.实验内容设计并调试好八位十进制数字频率计,用GW48-CK实验开发系统进行硬件验证(实现应选择拟采用的实验芯片的型号)进行硬件验证。

四.实验设计(1)VHDL源程序1、8位可自加载加法计数器的源程序CNT10.VHD如下--CNT10.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CNT10 ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA:IN STD_LOGIC;CQ:OUT INTEGER RANGE 0 TO 15;CO:OUT STD_LOGIC);END ENTITY CNT10;ARCHITECTURE ART OF CNT10 ISSIGNAL CQI:INTEGER RANGE 0 TO 15;BEGINPROCESS(CLK,CLR,ENA) ISBEGINIF CLR='1'THEN CQI<=0;ELSIF CLK'EVENT AND CLK='1'THENIF ENA='1'THENIF CQI<9 THEN CQI<=CQI+1;ELSE CQI<=0;END IF;END IF;END IF;END PROCESS; PROCESS(CQI) ISBEGINIF CQI=9 THEN CO<='1'; ELSE CO<='0';END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;(3).完成设计文件输入后,保存文件,对文件进行编译和仿真。

基于EDA技术的多功能等精度数字频率计的设计

控制 并通过 F G P A来设计 多功能等精度数字频率计的具体 方法。该频 率计可以兼顾频 率计对 速度 、 资源和测频精度等

各 方 面 的优 化 需 求 。

关键词 :D E A技术 ; 片机 ;等精度 ; 单 频率计 ; P A FG 中 图分 类 号 :N 4 T 7 文 献 标 识 码 : 文 章 编 号 :6 1 7 8 ( 08 0 A 17 — 80 20 )3—02 — 3 0 3 0

D e i n fEq lPr cso e ue c e e s d o EDA c h l g s g o ua e ii n Fr q n y M t r Ba e n Te no o y

Ra e g ng o Ch n mi

( x Istt o ehooy Wui 1 11 C i Wuintu i e fTcnl , x 4 2 ,hn g 2 a)

基 于 E A技 术 的多功 能 等 精 度 数 字频 率 计 的设 计 D

饶 成 明

( 无锡 职业技 术 学院 ,江苏

摘

无锡

242 ) 1 1 1

要 : 对三 种 测 频 方 法 进 行 分 析 的 基 础 上 , 绍 了基 于 E A技 术 的 等精 度 测频 原 理 。给 出采 用 A 8 C 1实现 在 介 D T9 5

o D tc n lg .T ep p r h w e d ti f c ivn o t l n te a pi aino T 9 5 n e in o h f n t n q a n E A h oo e y h a e o st eal o h ei g c n r p l t f 8 C a d d g f s h s a oo h c o A 1 s mu i ci a e u l u ol

基于EDA的数字频率计电路设计

基于EDA的数字频率计电路设计数字频率计是一种用于测量信号频率的电子测量仪器。

它可以将模拟信号转化为数字信号,并通过计算来获得信号的频率。

基于EDA的数字频率计电路设计使用EDA软件和模块来设计和模拟电路。

下面是关于基于EDA的数字频率计电路设计的详细介绍。

设计目标数字频率计主要是用于测量频率,因此设计目标是设计出一个稳定可靠的数字频率计电路,能够准确地测量信号的频率,并输出该信号的频率值。

设计流程1. 确定测量范围在设计数字频率计电路时,首先要确定测量的信号频率范围。

这些参数包括:频率的最低和最高值、测量的精度和分辨率。

2. 选取计数器器件基于EDA的数字频率计电路设计,需要使用一个高速、稳定、计数能力强的计数器器件。

在目前的技术条件下,常用的计数器器件有CD4040、CD4060、CD4024等,这些器件均具有高频率响应、易于使用、可编程等优点。

3. 选取稳压、滤波器件为了保证测试结果的稳定和准确,设计中需要使用稳压器件来消除电源电压的波动对仪器的影响,同时还需使用滤波器件来消除高频干扰带来的影响。

4. 连接计数器并程序设计计数器的连接应根据数据手册来实现,连通后还需要进行程序设计。

程序的设计可以使用模块化思想来进行,将输入、处理、输出等模块化。

5. 仿真验证设计在完成设计后,需要进行仿真验证,检查电路设计是否能够满足设计要求。

6. PCB绘制和电路调试如果仿真验证通过,则需要进行PCB绘制和电路调试。

PCB的设计和制作应根据原理图来完成,完成之后还需进行电路调试,确保电路能够正常工作。

总结基于EDA的数字频率计电路设计,是一项先进的电子技术,它能够利用EDA软件和模块来快速、准确地设计和模拟电路。

在设计电路时,需要考虑到测量的范围、器件的选取、程序的设计、仿真验证和PCB绘制以及电路调试等问题。

该电路的设计和制作过程较为复杂,需要有一定的电子知识和技能才能完成。

基于EDA的四位数码显示频率计

基于EDA的数字频率计的设计[摘要]在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以与便于实现测量过程自动化等优点,是频率测量的重要手段之一。

电子计数器测频有两种方式:一是直接测频法,即在一定闸门时间测量被测信号的脉冲个数;二是间接测频法,如周期测频法。

直接测频法适用于高频信号的频率测量,间接测频法适用于低频信号的频率测量。

本文阐述了用VHDL语言设计了一个简单的数字频率计的过程。

[关键词]EDA;VHDL;数字频率计;波形仿真;1.1 设计要求借助于FPGA/CPLD的开发技术,设计一个4位十进制数字显示的数字式频率计,具体要求如下:(1)4位十进制数字显示的数字式频率计的测量围为1k~9999KHZ,测量单位为KHZ;(2)要求量程能够自动转换,即几十KHZ显示小数点后两位,而几百KHZ 则显示小数点后一位;(3)当输入信号小于1KHZ时,输出全0,当输入大于9999KHZ时,输出显示全H。

1.2方案论证采用FPGA/CPLD芯片作为控制核心单元,完成各功能模块。

首先将被测信号与控制信号加在FPGA/CPLD芯片上,通过在芯片部进行各逻辑操作,完成分频、计数与扫描显示等功能操作,最后通过数码管显示结果。

其原理框架图如下图1-2所示。

图1-2 以FPGA/CPLD为核心的数字频率计第二章频率计的原理与测量方法数字频率计是直接用十进制数字显示被测信号频率的一种测量装置。

它以测量周期的方法对正弦波、方波、三角波的频率进行自动的测量。

所谓频率,就是周期性信号在单位时间(1s)里变化的次数。

若在一定时间间隔T测得的这个周期性信号的重复变化次数N,则其频率可表示为f=N/T;只要知道了N和T就可以求得频率。

若设置闸门信号的时间为1S,则被测频率就是NHz。

EDA技术与应用实践学习内容(数字频率计之计数模块)

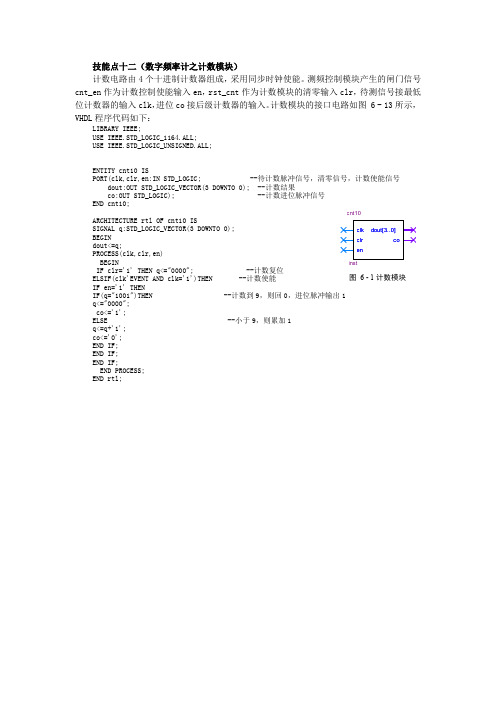

技能点十二(数字频率计之计数模块)计数电路由4个十进制计数器组成,采用同步时钟使能。

测频控制模块产生的闸门信号cnt_en 作为计数控制使能输入en ,rst_cnt 作为计数模块的清零输入clr ,待测信号接最低位计数器的输入clk ,进位co 接后级计数器的输入。

计数模块的接口电路如图 6 - 13所示,VHDL 程序代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY cnt10 ISPORT(clk,clr,en:IN STD_LOGIC; --待计数脉冲信号,清零信号,计数使能信号 dout:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --计数结果co:OUT STD_LOGIC); --计数进位脉冲信号END cnt10;ARCHITECTURE rtl OF cnt10 ISSIGNAL q:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN dout<=q; PROCESS(clk,clr,en)BEGIN IF clr='1' THEN q<="0000"; --计数复位 ELSIF(clk'EVENT AND clk='1')THEN --计数使能IF en='1' THENIF(q="1001")THEN --计数到9,则回0,进位脉冲输出1q<="0000";co<='1';ELSE --小于9,则累加1q<=q+'1';co<='0';END IF;END IF;END IF;END PROCESS;END rtl;图 6 - 1计数模块 cnt10instclk clr en dout[3..0]co。

基于EDA的数字频率计的设计

十进制计数器的程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jishu10 is

port(clk,rst,en:in std_logic;

cq:out std_logic_vector(3 downto 0);

4位十进制计数器的顶层原理图图5

完成4位十进制计数器的原理图编辑以后,即可进行仿真测试和波形分析,其仿真输出波形如图所示,当RST=0、EN=1是其计数值在0到9999之间循环变化,COUT为计数进位输出信号,作为后面的量程自动切换模块的输入脉冲。

脉冲图图6

因此仿真结果正确无误,可将以上设计的4位十进制计数器设置成可调用的元件jishu10_4.sym,以备高层设计中使用,其元件符号图如下图所示。

基于EDA的数字频率计的设计

摘

数字频率计是直接用十进制数字来显示被测信号频率的一种测量装置。它不仅可以测量正弦波、方波、三角波、尖脉冲信号和其他具有周期特性的信号的频率,而且还可以测量它们的周期。经过改装,可以测量脉冲宽度,做成数字式脉宽测量仪;可以测量电容做成数字式电容测量仪;在电路中增加传感器,还可以做成数字脉搏仪、计价器等。因此数字频率计在测量物理量方面应用广泛。本毕业设计用VHDL在CPLD器件上实现数字频率计测频系统,能够用十进制数码显示被测信号的频率,能够测量正弦波、方波和三角波等信号的频率,而且还能对其他多种物理量进行测量。具有体积小、可靠性高、功耗低的特点。数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器。采用VDHL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分以外,其余全部在一片FPGA芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。在不更改硬件电路的基础上,对系统进行各种改进还可以进一步提高系统的性能。该数字频率计具有高速、精确、可靠、抗干扰性强和现场可编程等优点。

数字式频率计的EDA设计

EDA技术设计报告姓名:张骥学号:0967112219班级:测控2009-2学院:信息工程学院数字式频率计的EDA设计1.1 设计要求设计一个能测量方波信号频率的频率计,测量结果用4位十进制数显示,频率测量范围为分为三档。

一档为0~9999Hz;二档为10.0~99.99kHz;三档为100.0~999.9kHz,用4个带小数点数码管显示其频率;并且在超出目前量程档次时报警。

1.2 原理描述频率计是能够测量和显示信号频率的电路。

所谓频率,就是周期性信号在单位时间内变化的次数。

常用的直接测频法有两种,一种是测周期法,一种是测频率法。

测周期法需要有基准系统时钟频率Fs,在待测信号一个周期Tx内,记录基准系统时钟频率的周期数Ns,则被测频率可表示为:Fx=Fs/Ns 测频率法就是在一定时间间隔Tw(该时间定义为闸门时间)内,测得这个周期性信号的重复变换次数为Nx,则其频率可表示为:Fx=Nx/Tw 这两种方法的计数值会产生正负一个字的误差,并且被测精度与计数器中记录的数值Nx有关,为保证测试精度,一般对于低频信号采用测周期法,对于高频信号采用测频率法,直接测频法的时序控制波形图如图所示。

直接测频法的一般思路是:在精确规定计数允许周期T内使能计数器,对被测信号的周期(脉冲)数进行计数,计数允许周期T的长度决定了被测信号频率的范围。

较长的计数允许周期T对低频信号而言有利于改善测量精度,但对于高频信号来说,则会产生溢出;较短的计数允许周期T对低频信号的测量,虽然精度降低,但能测量的最大频率较高,且不会产生溢出。

基于此思路,可得到数字式频率计系统组成框图如图所示图.直接测频法时序控制波形图图.数字式频率计系统组成框图根据图,可以把数字式频率计分为四个部分:即4位十进制计数器模块、闸门控制模块、译码显示模块和脉冲整形模块。

该数字式频率计的精度取决于系统基准时钟,实际设计可采用石英晶体振荡器电路,以便为闸门控制电路产生精确的系统基准时钟。

基于EDA技术的数字频率计的设计

基于EDA技术的数字频率计的设计0 引言EDA 技术是以大规模可编程逻辑器件为设计载体,以硬件语言为系统逻辑描述的主要方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件设计的电子系统到硬件系统的设计,最终形成集成电子系统或专用集成芯片的一门新技术。

其设计的灵活性使得EDA 技术得以快速发展和广泛应用。

本文以Max+PlusⅡ软件为设计平台,采用VHDL 语言实现数字频率计的整体设计。

1 工作原理众所周知,频率信号易于传输,抗干扰性强,可以获得较好的测量精度。

因此,频率检测是电子测量领域最基本的测量之一。

频率计的基本原理是用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率。

通常情况下计算每秒内待测信号的脉冲个数,即闸门时间为1 s。

闸门时间可以根据需要取值,大于或小于1 s 都可以。

闸门时间越长,得到的频率值就越准确,但闸门时间越长,则每测一次频率的间隔就越长。

闸门时间越短,测得的频率值刷新就越快,但测得的频率精度就受影响。

一般取1 s 作为闸门时间。

数字频率计的关键组成部分包括测频控制信号发生器、计数器、锁存器、译码驱动电路和显示电路,其原理框图如图1 所示。

2 设计分析2.1 测频控制信号发生器测频控制信号发生器产生测量频率的控制时序,是设计频率计的关键。

这里控制信号CLK 取为1 Hz,2 分频后就是一个脉宽为1 s 的时钟信号FZXH,用来作为计数闸门信号。

当FZXH 为高电平时开始计数;在FZXH 的下降沿,产生一个锁存信号SCXH,锁存数据后,还要在下次FZXH 上升沿到来之前产生清零信号CLEAR,为下次计数做准备,CLEAR 信号是上升沿有效。

2.2 计数器计数器以待测信号FZXH 作为时钟,在清零信号CLEAR 到来时,异步清零;FZXH 为高电平时开始计数。

本文设计的计数器计数最大值是99 999 999。

2.3 锁存器当锁存信号SCXH 上升沿到来时,将计数器的计数值锁存,这样可由外部的七段译码器译码并在数码管上显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA在数字频率计中计数模块里的应用¹彭惠芹º(山西大同大学工学院,山西大同037003)摘要:计数模块是数字频率计系统的核心模块,频率测量的主要工作由它来完成1本文根据数字频率计的特点,在A ltera公司的FPGA开发平台QuartusÒ中实现,同时采用VHDL硬件描述语言,提出了一种实用性较强的计数模块的设计方案1关键词:数字频率计;CPLD技术;计数模块;自顶向下方法;VHDL语言中图分类号:TN79+2文献标识码:A文章编号:1672-7169(2010)01-0073-03数字频率计是电子设计、仪器仪表、资源勘测等应用领域不可缺少的测量仪器,许多物理量的测量,如振动、转速等的测量都涉及到或可以转化为频率的测量。

传统的数字频率计一般是由分离元件搭接而成。

后来随着单片机的大规模的应用,出现了不少用单片机控制的频率测量系统。

相对于以前用分离元件搭接起来的频率测量系统,单片机控制的频率测量系统在频率测量范围、频率测量精度和频率测量速度上都有了很大的提高。

但由于单片机工作频率的限制、单片机内部计数器位数的限制等因素,由单片机控制的频率测量系统无法在频率测量范围、频率测量精度和频率测量速度上取得重大突破。

若再增加别的器件,以弥补单片机的不足,不仅会大大增加系统的复杂性,而且不利于系统的集成化。

本文所介绍的频率计是在A ltera公司的FP2 GA开发平台QuartusÒ中实现的,计数器的各个模块采用V HDL语言描述。

在一片FPGA里实现了数字频率计的绝大部分功能,它的集成度远远超过了以往的数字频率计。

又由于数字频率计最初的实现形式是用硬件描述语言写成的程序,具有通用性和可重用性,所以在外在的条件(如基准频率的提高,基准频率精度的提高)的允许下,只需对源程序作很小的改动,就可以使数字频率计的精度提高几个数量级。

同时对于频率精度要求不高的场合,可以修改源程序,使之可以用较小的器件实现,从而降低系统的整体造价。

文中重点阐述了数字频率计的总体结构和其中的计数模块的设计方案。

1EDA技术ED A即电子设计自动化,它以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程器件的开发软件及实验室开发系统为设计工具,自动完成软件方式描述的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、布局布线、逻辑仿真,直至完成对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门多学科融合的新技术。

2CPLD技术随着EDA技术的不断发展,当今的EDA技术更多的是指芯片内的电路设计自动化,开发人员完全可以通过自己的电路设计来定制芯片内部的电路功能,使之成为设计者专自己的专用集成电路芯片(ASI C),这就是CPL D技术。

CPLD即复杂可编程逻辑器件技术,其功能之卓越已经令当今的电子工程师们赞叹不已,除了它体积小、容量大、I/O口丰富、易编程和加密等优点外,更突出的特点是其芯片的在系统可编程技术,即I SP 技术,也就是说它不但具有可编程和可再编程的能力,而且只要把器件插在系统内或线路板上,就能对其进行编程或再编程。

3数字频率计的结构本文的数字频率计是在ED A实验开发平台上,利用Cyc l o ne芯片EP1C12Q240C8CPL D进行73¹º收稿日期:2009-11-17作者简介:彭惠芹(1974-),女,山西大同人,硕士,山西大同大学工学院实验师,研究方向:自动化控制。

设计的。

数字频率计系统设计采用了自顶向下(Top_Do wn)的设计方法,由三部分组成:输入整形电路、核心控制电路(FPG A 模块)和输出显示电路,如图1所示。

被测信号经过输入整形电路生成方波输入到FPG A 模块中进行计数处理,FPGA 中的计数模块根据所提供方波的上升沿或下降沿进行计数,计数时间则由时间控制模块来决定,可以根据频率所处的范围来决定档位,然后将计数的结果输出给显示电路,通过静态或动态扫描方式,在数码管上显示所测频率的大小。

本文以3位十进制数字显示的数字式频率计系统为例进行设计。

图1 数字频率计系统4 计数模块计数模块是数字频率计系统的核心模块,频率测量的主要工作由它来完成。

它通过计数器对被测信号在基准时间内进行计数来测量被测信号的频率。

411 计数模块功能计数器为模999十进制加法计数器,可由量程选择信号控制模999计数器的基本频率(比如100kH z 档的基本频率为10H z ,即输入10个脉冲时模999计数器计1)。

当CL R 为高电平时,计数器清零;当CL R 为低电平,并且EN 为高电平时,允许计数。

当计数值大于999时,频率计处于超量程状态,下一次测量时,量程自动增大1档。

当计数值小于099时,频率计处于欠量程状态,下一次测量时,量程自动减小1档。

412 计数模块部分VHDL 程序示例li b rary ieee ;use ieee 1std_l o gi c _11641a l;l use ieee 1std_l o gi c _unsi g ned 1a l;l )))定义集合包entity jishu is )))定义实体port(fin ,en ,clr :in std_logic ;)))3个输入 cd ,cu :out std_logic ;)))2个输出 coun:t out std_logic_vector(11downto 0));end jishu ;arch itecture a of jishu is )))定义结构体 beginprocess(fi n ,en,clr))))计数器进程 variable coun ti n :std_l o gic_vector(11do wnto 0);)))定义该进程中的变量begin if clr=1''thencountin :="000000000000";)))当清零信号c lr 为高电平是,计数器清零elsif fin e 'vent and fi n =1''then If en=1''then countin :=counti n +1; end i;f)))当待测信号fin 和计数使能信号en 为高电平时计数器开始计数if counti n (3do wnto 0)=10 then counti n :=countin+"0110"; end i;fif counti n si d e(7downto 4)=10 then counti n :=countin+"01100000"; end i;fif counti n (11do wnto 8)=10then counti n :=countin+"011000000000"; end i;f end i;f ,,end process ;)))计数器进程结束end a ;5 调试结果分析与结论系统联合调试成功后,将VHDL 设计与N i o s 设计下载到FPG A 芯片中,输入相关信号,并进行有关性能指标的测试,直到满足设计要求为止。

经一系列实际数据的测量和分析,本数字频率计基本达到了设计要求,设计思路和方法是正确的,设计也是成功的。

746结语本文实现了对数字频率计中的计数模块的设计,在ED A实验开发平台上,利用EP1C12Q240C8 CPL D芯片产生所需的数据,再通过数码管显示输出,实验表明其性能良好。

采用这样的设计可以简化硬件的开发和制造过程,而且使硬件体积大大减小,并提高了系统的可靠性。

同时在基本电路模块基础上,不必修改硬件电路,通过修改V HDL源程序,增加一些新功能,满足不同用户的需要,实现数字系统硬件的软件化。

参考文献:[1]王振义.E W B在电子技术中的应用[J].山西大同大学学报(自然科学版),2007,18(1):104-110[2]阎石.数字电子技术基础[M].北京:高等教育出版社,2001:97-110[3]仝庆华.硬件描述语言V HDL教学浅议[J].山西大同大学学报(自然科学版),2007,23(2):97-99[4]曾永西.基于QuartusÒ的两种数字频率计系统设计与比较[J].福建电脑,2008,6:168-169[5]利剑清,宋跃,林明仁等.基于FPGA/SOPC-N iosÒ的频率计数器设计[J].东莞理工学院学报,2008,15(3):53-57[6]孙华锦.基于V HDL语言的电子设计自动化及其应用[D].陕西:西北工业大学,2001[7]金琳.基于ED A技术的频率计系统设计[D].黑龙江:吉林大学,2007[8]张永安.基于CPL D的多功能等精度数字频率计系统的设计[D].内蒙古:内蒙古大学,2004[9]刘明业,叶梅龙,郭玉钗.数字系统自动设计[D].北京:高等教育出版社,1996:25-27[10]招雅兴等.FPGA原理、设计及应用[M].天津:天津大学出版社,1999:21-31Th e app lica tion of EDA on th e coun ter m odule in D igita l frequency coun terPENG H uiqi n(School of Engi n eering,Shanxi DatongU niversity,Datong Shanxi037003)Abstr ac t:The co unter m odu l e is t he kernel modu les of D i gita l frequency counte r.The frequencym easure m en t of the m a j or tasks to be co mp l e ted by it.A ccording to D i gita l frequency counters'characteristi c,t he text i s rea lized on t he Quartus II ofFPG A i n the co mpany A ltera.M odu l es using V HDL language t o descr i be.P roposed one usable stro ng co unter m odu l e desi gn.K ey word s:D i gita l frequency co unter;ED A technolo gy;co unter m odu l e;top-do wn;V HDL language75第1期彭惠芹:ED A在数字频率计中计数模块里的应用。