Kintex7的SERDES的结构图 CPRI应用的应用

CPRI原理及测试解决方案

CPRI原理及测试解决方案(一)( 2010/6/13 14:29 )摘要分布式基站的基本结构与传统一体化基站有很大的不同,它将基站的基带部分(BBU/REC)和射频部分(RRU/RE/RRH)分离,分别作为单独的部分。

这种分布式结构具有配置灵活、工程建设方便、环境适应性强等优点,应用越来越广泛。

为了规范BBU和RRU 之间的接口标准,CPRI(Common Public Radio Interface)协议应运而生。

目前,CPRI 接口的测试已经成为业界关注的焦点。

R&S公司基于其强大的技术实力,于业界首先推出了基于CPRI接口的RRU和BBU测试解决方案,进一步完善了基站领域的测试需求,可以更好地为运营商、基站设备商、直放站厂商和检测机构提供相应的测试服务。

1 引言基站是由多个功能部分组成的,其中最主要的两个部分是基带部分和射频部分。

但在实用传统基站部署的网络中,基站的扩容却是运营商头疼的大问题。

这是由于传统基站的各个模块通常是集成在一起的,例如基带单元和射频单元通常是无法完全分离的,如果在基带单元资源紧张的情况下,需要进行扩容,增加基带单元的同时就必须增加射频单元,这将无法避免地导致射频部分的浪费。

而如果基站可以实现基站内的单元模块化,各模块之间各自独立,在上述情况下,就可以根据实际需要,实现只增加基带资源不增加射频资源的灵活配置,从而节省大量的设备成本。

现在新的3G/4G基站采用了开放架构,主要就是指基站的基带部分和射频部分之间采用了开放式的接口和标准协议,可分开放置;模块化则是开放架构概念的一种延伸,主要指基站的基带部分和射频部分无论从硬件还是软件上都自成一体,具有自己的功能,基带部分和射频部分相互独立。

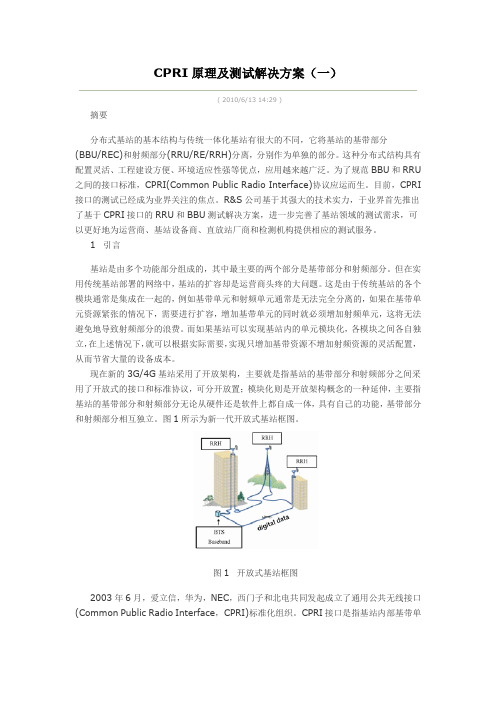

图1所示为新一代开放式基站框图。

图1 开放式基站框图2003年6月,爱立信,华为,NEC,西门子和北电共同发起成立了通用公共无线接口(Common Public Radio Interface,CPRI)标准化组织。

SerDes知识详解一、SerDes的作用

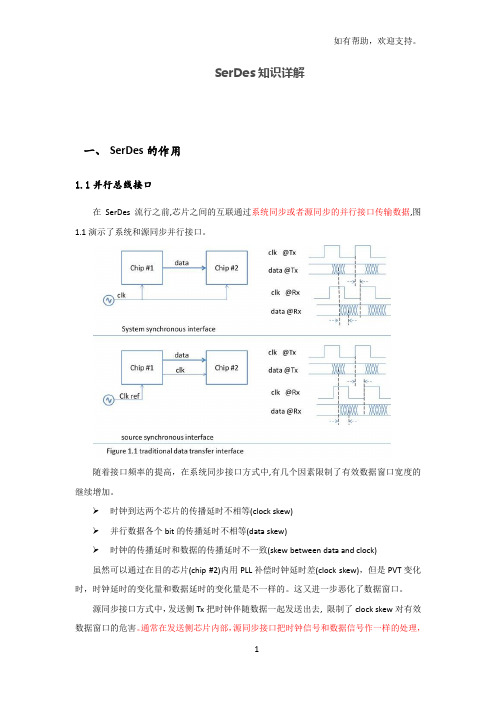

SerDes知识详解一、SerDes的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。

随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。

时钟到达两个芯片的传播延时不相等(clock skew)并行数据各个bit的传播延时不相等(data skew)时钟的传播延时和数据的传播延时不一致(skew between data and clock)虽然可以通过在目的芯片(chip #2)内用PLL补偿时钟延时差(clock skew),但是PVT变化时,时钟延时的变化量和数据延时的变化量是不一样的。

这又进一步恶化了数据窗口。

源同步接口方式中,发送侧Tx把时钟伴随数据一起发送出去, 限制了clock skew对有效数据窗口的危害。

通常在发送侧芯片内部,源同步接口把时钟信号和数据信号作一样的处理,也就是让它和数据信号经过相同的路径,保持相同的延时。

这样PVT变化时,时钟和数据会朝着同一个方向增大或者减小相同的量,对skew最有利。

我们来做一些合理的典型假设,假设一个32bit数据的并行总线,a)发送端的数据skew = 50 ps ---很高的要求b)pcb走线引入的skew = 50ps ---很高的要求c)时钟的周期抖动jitter = +/-50 ps ---很高的要求d)接收端触发器采样窗口= 250 ps ---Xilinx V7高端器件的IO触发器可以大致估计出并行接口的最高时钟= 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz (SDR)。

利用源同步接口,数据的有效窗口可以提高很多。

通常频率都在1GHz以下。

在实际应用中可以见到如SPI4.2接口的时钟可以高达DDR 700MHz x 16bits位宽。

DDR Memory接口也算一种源同步接口,如DDR3在FPGA中可以做到大约800MHz的时钟。

serdes

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。

即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。

这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。

SERDES 10年SERDES技术最早应用于广域网(WAN)通信。

国际上存在两种广域网标准:一种是SONET,主要通行于北美;另一种是SDH,主要通行于欧洲。

这两种广域网标准制订了不同层次的传输速率。

目前万兆(OC-192)广域网已在欧美开始实行,中国大陆已升级到2.5千兆(OC-48)水平。

SERDES技术支持的广域网构成了国际互联网络的骨干网。

SERDES技术同样应用于局域网(LAN)通信。

因为SERDES技术主要用来实现ISO模型的物理层,SERDES通常被称之为物理层(PHY)器件。

以太网是世界上最流行的局域网,其数据传输速率不断演变。

IEEE在2002年通过的万兆以太网标准,把局域网传输速率提高到了广域网的水平,并特意制订了提供局域网和广域网无缝联接的串行WAN PHY。

与此同时,SERDES技术也广泛应用于不断升级的存储区域网(SAN),例如光纤信道。

随着半导体技术的迅速发展,计算机的性能和应用取得了长足进步。

可是,传统并行总线技术——PCI却跟不上处理器和存储器的进步而成为提高数据传输速率的瓶颈。

新一代PCI标准PCI Express正是为解决计算机IO瓶颈而提出的(见表1)。

PCI Express是一种基于SERDES的串行双向通信技术,数据传输速率为2.5G/通道(lane),可多达32通道(lane),支持芯片与芯片和背板与背板之间的通信。

国际互联网络和信息技术的兴起促成了计算机和通信技术的交汇,而SERDES串行通信技术逐步取代传统并行总线正是这一交汇的具体体现。

serdes原理

serdes原理SerDes原理解析什么是SerDesSerDes是一种串行器/解串器(Serializer/Deserializer)的简写,它是一种用于将并行数据转换为串行数据(或者将串行数据转换为并行数据)的集成电路(IC)技术。

在数字通信领域,SerDes常用于高速数据传输和通信接口。

串行数据和并行数据在开始解释SerDes原理之前,我们需要了解串行数据和并行数据的概念。

•串行数据是指将数据位按照顺序一个接一个地发送,每个数据位之间通过时钟信号来区分。

•并行数据是指将多个数据位同时发送,每个数据位占用一个信号线。

SerDes的原理SerDes的主要功能是将并行数据转换为串行数据(Serializer)或将串行数据转换为并行数据(Deserializer)。

它由两部分组成:串行器和解串器。

串行器(Serializer)串行器将并行数据转换为串行数据,实现了数据的串行化。

它的输入为多个并行数据位,输出为一个串行数据流。

串行器的工作流程如下:1.并行输入数据位通过数据处理电路进行编码和加工,以适应传输和接收的要求。

2.经过编码和加工的数据经过串行器内部的串行输出电路,逐位地传输到输出信号线上。

3.在串行器内部,每个数据位之间通过时钟信号来同步。

串行器常用于数据传输的发送端,如计算机内部总线、高速网络通信和存储器接口等领域。

解串器(Deserializer)解串器将串行数据转换为并行数据,实现了数据的解串行化。

它的输入为一个串行数据流,输出为多个并行数据位。

解串器的工作流程如下:1.串行输入数据流通过输入接收电路,逐位地接收到解串器内部。

2.在解串器内部,输入数据流中的每个数据位经过时钟信号的同步和解码处理。

3.解码后的数据经过解串器的并行输出电路,并行地输出到多个数据线上。

解串器常用于数据传输的接收端,如计算机内部总线、高速网络通信和存储器接口等领域。

SerDes的应用SerDes技术在现代通信领域有着广泛的应用,主要体现在以下几个方面:1.高速网络通信:SerDes能够在高速网络中实现可靠的数据传输和接收,提升网络带宽和通信速度。

SERDES FPGA设计手册

编号:版本:页数:共页密级:SERDES FPGA设计手册更改记录注:作者兜福邮箱:,多多交流,共同进步。

目录SERDES FPGA设计手册错误!未定义书签。

目录错误!未定义书签。

1目的错误!未定义书签。

2范围错误!未定义书签。

3术语错误!未定义书签。

4SERDES基础知识错误!未定义书签。

5SERDES应用指南错误!未定义书签。

ISERDES 错误!未定义书签。

ISERDES基元错误!未定义书签。

ISERDES基元的时钟解决方案错误!未定义书签。

OSERDES 错误!未定义书签。

OSERDES组成功能模块错误!未定义书签。

OSERDES基元错误!未定义书签。

OSERDES基元的时钟解决方案错误!未定义书签。

6SERDES应用指南错误!未定义书签。

ISERDES设计错误!未定义书签。

单个ISERDES单元设计(SDR) 错误!未定义书签。

配置参数错误!未定义书签。

设计思想错误!未定义书签。

仿真结果错误!未定义书签。

数据时序错误!未定义书签。

输入数据时序错误!未定义书签。

输出数据时序错误!未定义书签。

单个ISERDES单元设计(DDR) 错误!未定义书签。

配置参数错误!未定义书签。

设计思想错误!未定义书签。

仿真结果错误!未定义书签。

ISERDES宽度扩展错误!未定义书签。

设计实例错误!未定义书签。

仿真结果错误!未定义书签。

OSERDES设计错误!未定义书签。

单个OSERDES单元设计(SDR) 错误!未定义书签。

配置参数错误!未定义书签。

设计思想错误!未定义书签。

仿真结果错误!未定义书签。

基元SDR模式时序错误!未定义书签。

单个OSERDES单元设计(DDR) 错误!未定义书签。

配置参数错误!未定义书签。

设计思想错误!未定义书签。

仿真结果错误!未定义书签。

基元SDR模式时序错误!未定义书签。

OSERDES宽度扩展错误!未定义书签。

设计实例错误!未定义书签。

仿真结果错误!未定义书签。

目的为了学习xilinx serdes原语的使用,以及交流学习经验,在工程项目中方便的应用SERDES进行设计,故编写此文档。

serdes的编码和应用

SerDes的应用形式

• 简化系统板级布线,降低 系统功耗,提高系统稳定 性 ASIC 1

不使用SerDes的系统

ASIC 2

•在系统内部模块之间,以 及系统与系统之间提供高 速数据互SerDes IP核

ASIC 1

SerD es

SerD es

芯片

芯片

ASIC 2

使用单片SerDes的系统

ASIC 1

SerDes在InfiniBand中的应用(续)

以硬IP核的形式存在

于InfiniBand交换机中 建立简洁的传输端口 格局 保证InfiniBand的高 SerDe s 速传输 提供更远的数据传输 距离 使用16通道 3.125Gbps的SerDes 能够提供单项51Gbps 的速率,远远大于12X 传输模式

SerDes将主机架并行的多位信号和主控时钟编为高

速的串行码流,以LVDS信号通过RJ45口和双绞线传 输给备用机架 使所有的FPGA数据均可定义为低驱动电流LVCMOS 信号,极大的降低了FPGA的SSO内部噪声

较大的提高了系统性能,延长了传输距离

SerDes的其他应用

在视频技术领域:应用于DVI接口,提供大规模视频数据

子段写为 十进制

xx

.

y

D 26.2

8B10B编码(续)

2.字符编码表

Dxx.y中的 xx子段 D0 D1 D2 D3 D4 … D31 EDCBA CRDabcdei 100111 011101 101101 110001 110101 … 101011 CRD+ abcdei 011000 100010 010010 110001 001010 … 010100 Dxx.y中的 y子段 D--.0 D--.1 D--.2 D--.3 D--.4 D--.5 D--.6 D--.7 HGF CRDfghj 1011 1001 0101 1100 1101 1010 0110 1110/0111 CRD+ fghj 0100 1001 0101 0011 0010 1010 0110 0001/1000

高速serdes电路结构

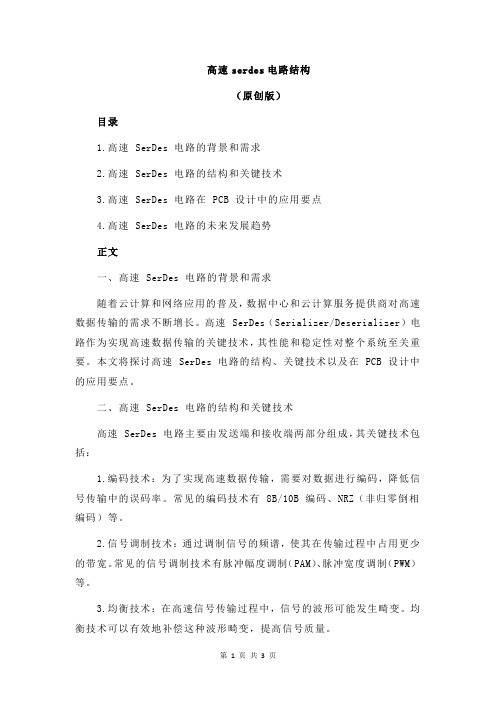

高速serdes电路结构(原创版)目录1.高速 SerDes 电路的背景和需求2.高速 SerDes 电路的结构和关键技术3.高速 SerDes 电路在 PCB 设计中的应用要点4.高速 SerDes 电路的未来发展趋势正文一、高速 SerDes 电路的背景和需求随着云计算和网络应用的普及,数据中心和云计算服务提供商对高速数据传输的需求不断增长。

高速 SerDes(Serializer/Deserializer)电路作为实现高速数据传输的关键技术,其性能和稳定性对整个系统至关重要。

本文将探讨高速 SerDes 电路的结构、关键技术以及在 PCB 设计中的应用要点。

二、高速 SerDes 电路的结构和关键技术高速 SerDes 电路主要由发送端和接收端两部分组成,其关键技术包括:1.编码技术:为了实现高速数据传输,需要对数据进行编码,降低信号传输中的误码率。

常见的编码技术有 8B/10B 编码、NRZ(非归零倒相编码)等。

2.信号调制技术:通过调制信号的频谱,使其在传输过程中占用更少的带宽。

常见的信号调制技术有脉冲幅度调制(PAM)、脉冲宽度调制(PWM)等。

3.均衡技术:在高速信号传输过程中,信号的波形可能发生畸变。

均衡技术可以有效地补偿这种波形畸变,提高信号质量。

4.时钟恢复技术:在接收端,需要从接收到的信号中提取时钟信号,以同步数据传输。

时钟恢复技术包括锁相环(PLL)、时钟数据恢复(CDR)等。

三、高速 SerDes 电路在 PCB 设计中的应用要点在 PCB 设计中,为了保证高速 SerDes 电路的性能和稳定性,需要关注以下几个方面:1.电路布局:高速 SerDes 电路的布局需要满足信号完整性(SI)和电源完整性(PI)的要求。

信号线应尽量短且避免与其他高速信号线交叉,同时注意高速信号线的阻抗匹配。

2.电路隔离:在 PCB 设计中,高速 SerDes 电路应与其他电路模块保持足够的隔离,避免相互干扰。

SerDes知识详解

SerDes知识详解一、SerDes的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。

随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。

时钟到达两个芯片的传播延时不相等(clock skew)并行数据各个bit的传播延时不相等(data skew)时钟的传播延时和数据的传播延时不一致(skew between data and clock)虽然可以通过在目的芯片(chip #2)内用PLL补偿时钟延时差(clock skew),但是PVT变化时,时钟延时的变化量和数据延时的变化量是不一样的。

这又进一步恶化了数据窗口。

源同步接口方式中,发送侧Tx把时钟伴随数据一起发送出去, 限制了clock skew对有效数据窗口的危害。

通常在发送侧芯片内部,源同步接口把时钟信号和数据信号作一样的处理,也就是让它和数据信号经过相同的路径,保持相同的延时。

这样PVT变化时,时钟和数据会朝着同一个方向增大或者减小相同的量,对skew最有利。

我们来做一些合理的典型假设,假设一个32bit数据的并行总线,a)发送端的数据skew = 50 ps ---很高的要求b)pcb走线引入的skew = 50ps ---很高的要求c)时钟的周期抖动jitter = +/-50 ps ---很高的要求d)接收端触发器采样窗口= 250 ps ---Xilinx V7高端器件的IO触发器可以大致估计出并行接口的最高时钟= 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz (SDR)。

利用源同步接口,数据的有效窗口可以提高很多。

通常频率都在1GHz以下。

在实际应用中可以见到如SPI4.2接口的时钟可以高达DDR 700MHz x 16bits位宽。

DDR Memory接口也算一种源同步接口,如DDR3在FPGA中可以做到大约800MHz的时钟。

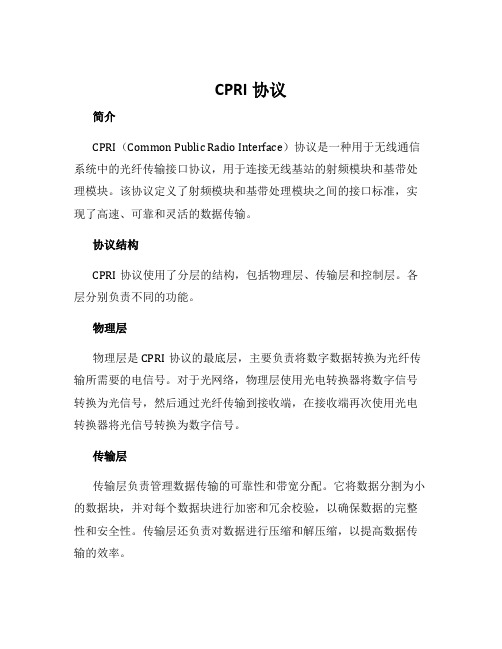

cpri协议

CPRI协议简介CPRI(Common Public Radio Interface)协议是一种用于无线通信系统中的光纤传输接口协议,用于连接无线基站的射频模块和基带处理模块。

该协议定义了射频模块和基带处理模块之间的接口标准,实现了高速、可靠和灵活的数据传输。

协议结构CPRI协议使用了分层的结构,包括物理层、传输层和控制层。

各层分别负责不同的功能。

物理层物理层是CPRI协议的最底层,主要负责将数字数据转换为光纤传输所需要的电信号。

对于光网络,物理层使用光电转换器将数字信号转换为光信号,然后通过光纤传输到接收端,在接收端再次使用光电转换器将光信号转换为数字信号。

传输层传输层负责管理数据传输的可靠性和带宽分配。

它将数据分割为小的数据块,并对每个数据块进行加密和冗余校验,以确保数据的完整性和安全性。

传输层还负责对数据进行压缩和解压缩,以提高数据传输的效率。

控制层控制层负责管理协议的控制和配置。

它定义了信道的建立和释放过程,以及数据传输的优先级和调度策略。

控制层还负责监控链路质量和故障检测,以及协议的错误处理和恢复。

数据传输CPRI协议支持双向数据传输,可以同时传输上行和下行的数据。

上行数据是从射频模块向基带处理模块传输的数据,下行数据是从基带处理模块向射频模块传输的数据。

数据传输通过CPRI帧进行,每帧包含多个时隙,每个时隙包含一个数据单元。

数据单元由一个或多个CPRI帧组成,每个CPRI帧包含一个数据包。

数据包的大小和格式由CPRI协议规定,通常是固定大小的以太网帧。

网络配置CPRI协议支持灵活的网络配置,可以根据实际需求进行定制。

网络配置是通过控制层进行的,协议提供了丰富的配置选项和参数。

网络配置包括带宽分配、信道设置、错误补偿和时钟同步等。

在网络配置过程中,需要进行链路检测和质量评估。

链路检测用于检测光纤传输链路的连接情况和质量,质量评估用于评估链路的信号质量和传输能力。

根据评估结果,可以对网络进行优化和调整。

SERDES电路设计的一点想法

简介随着电子行业技术的发展,特别是在传输接口的发展上,IEEE1284被 USB 接口取代,PATA被 SATA 取代,PCI被 PCI-Express 所取代,无一都证明了传统并行接口的速度已经达到一个瓶颈了,取而代之的是速度更快的串行接口,于是原本用于光纤通信的SerDes技术成为了为高速串行接口的主流。

串行接口主要应用了差分信号传输技术,具有功耗低、抗干扰强,速度快的特点,理论上串行接口的最高传输速率可达到10Gbps以上。

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。

即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。

这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。

这种点对点的通信技术可以提升信号的传输速度,并且降低通信成本。

分类SerDes 结构大致可以分为四类:并行时钟SerDes:将并行宽总线串行化为多个差分信号对,传送与数据并联的时钟。

容易实现。

8B/10B 编码SerDes:将每个数据字节映射到10bit代码,然后将其串行化为单一信号对。

10位代码是这样定义的:为接收器时钟恢复提供足够的转换,并且保证直流平衡(即发送相等数量的‘1’和‘0’)。

这些属性使8B/10BSerDe s能够在有损耗的互连和光纤传输中以较少的信号失真高速运行;嵌入式时钟SerDes:将数据总线和时钟串化为一个串行信号对。

两个时钟位,一高一低,在每个时钟循环中内嵌串行数据流,对每个串行化字的开始和结束成帧,因此这类SerDes也可称为“开始-结束位SerDes”,并且在串行流中建立定期的上升边沿。

由于有效负载夹在嵌入式时钟位之间,因此数据有效负载字宽度并不限定于字节的倍数;位交错SerDes:将多个输入串行流中的位汇聚为更快的串行信号对。

serdes项目实例

serdes项目实例SerDes(Serializer/Deserializer)是一种高速串行接口技术,用于将数据从并行格式转换为串行格式,或者将数据从串行格式转换为并行格式。

SerDes广泛应用于高速通信、数据中心、云计算等领域。

下面是一个简单的SerDes项目实例,使用FPGA实现一个4Gbps的SerDes接口。

1. 项目目标本项目旨在设计并实现一个基于FPGA的4Gbps SerDes接口,用于高速数据传输和通信。

SerDes接口需要能够将FPGA内部的并行数据转换为高速串行数据,并能够在远距离传输后恢复原始数据。

2. 项目设计本项目采用Xilinx Virtex-7系列FPGA,使用其内建的SERDES模块实现SerDes接口。

具体设计如下:并行数据输入:SerDes接口接收FPGA内部的32位并行数据,数据速率为1000MHz。

串行数据输出:SerDes接口将接收到的并行数据转换为高速串行数据,数据速率为4Gbps,通过一对差分线传输。

线路编码:采用8B/10B编码方案,以提高信号的眼图质量和降低误码率。

均衡与去加重:在发送端,使用预加重和去加重技术,以提高信号的传输质量和降低误码率。

时钟管理:SerDes接口内部采用时钟管理单元(CMT),以确保时钟的准确性和稳定性。

3. 项目实现在FPGA上实现SerDes接口需要编写相应的硬件描述语言(HDL)代码,如VHDL或Verilog。

具体实现步骤如下:设计并行数据接收模块,将FPGA内部的并行数据接收并缓存到FIFO中。

设计串行数据发送模块,将FIFO中的数据转换为高速串行数据并发送出去。

设计时钟管理模块,为SerDes接口提供稳定的时钟信号。

设计均衡与去加重模块,在发送端对数据进行预加重和去加重处理,在接收端进行均衡处理。

综合和布局布线:使用Xilinx Vivado工具对设计进行综合和布局布线,生成可下载到FPGA的bit文件。

serdes建链原理

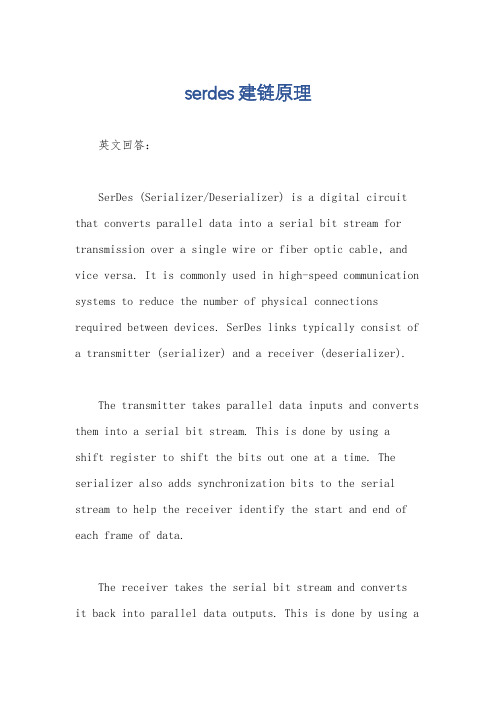

serdes建链原理英文回答:SerDes (Serializer/Deserializer) is a digital circuit that converts parallel data into a serial bit stream for transmission over a single wire or fiber optic cable, and vice versa. It is commonly used in high-speed communication systems to reduce the number of physical connections required between devices. SerDes links typically consist of a transmitter (serializer) and a receiver (deserializer).The transmitter takes parallel data inputs and converts them into a serial bit stream. This is done by using ashift register to shift the bits out one at a time. The serializer also adds synchronization bits to the serial stream to help the receiver identify the start and end of each frame of data.The receiver takes the serial bit stream and converts it back into parallel data outputs. This is done by using ashift register to shift the bits in one at a time. The deserializer also uses the synchronization bits to identify the start and end of each frame of data.SerDes links can operate at very high speeds, up to 100 Gbps or more. They are used in a wide variety of applications, including networking, telecommunications, and data storage.中文回答:串行器/解串器 (SerDes) 工作原理。

高速serdes中常见电路结构

高速serdes中常见电路结构

在高速serdes中,常见的电路结构有:

1. 著名的D-flip-flop(D触发器)电路结构,用于数据的稳定锁存。

2. 预加重器(Pre-emphasis)电路结构,用于对高频信号进行补偿,使其在传输过程中能够保持较好的信号质量。

3. 驱动器(Driver)电路结构,用于提供足够的驱动能力,推动信号通过传输线路。

4. 均衡器(Equalizer)电路结构,用于补偿传输信号中的频率响应失真,提高信号传输的质量。

5. 直流偏置电路(DC biasing circuit)结构,用于将信号的直流偏置设定到正确的工作点。

6. 校准电路(Calibration circuit)结构,用于校准传输线路中的参数,以提高信号传输的准确性和可靠性。

7. 锁定环路(PLL)电路结构,用于生成高精度的时钟信号,实现数据的同步传输。

8. 缓冲器(Buffer)电路结构,用于提高信号的驱动能力和传输能力。

9. 硬件错误校正电路(FEC)结构,用于检测和纠正传输过程中的错误,提高信号的可靠性。

以上是高速serdes中常见的电路结构,它们通过相互配合和优化,实现了高速数据的可靠传输和处理。

高速串行收发器原理及芯片设计

高速串行收发器原理及芯片设计

高速串行收发器(SerDes)是一种用于在半导体芯片之间传输高速数据的电子组件。

它们通常用于将数据从一个芯片传输到另一个芯片,例如在计算机、服务器、移动设备和其他电子设备中。

SerDes能够以高速收发数据,因而在许多应用中都扮演了重要角色。

SerDes的原理是使用交替高低电平的信号,将并行数据转换为串行数据,以便通过单个通道传输。

在接收端,通过解码技术将串行信号转换为并行信号,以便在远端接收所有数据。

为了支持高速传输,SerDes需要使用多种技术。

首先是提供高电流和低电阻的电缆和接口。

其次是使用低功耗的工艺和设计技术,以减少功耗和热量,保证设备在长时间工作时不会损坏。

SerDes芯片的设计要具有高集成度、低功耗、高速度、低噪声等特点。

此外, SerDes芯片还需要具有高度的稳定性,以确保在不同的传输环境(例如热、噪声等)中稳定工作。

为了实现这些目标,SerDes的设计通常结合多种技术,包括测试、仿真、优化设计等等。

总之,高速串行收发器在现代电子设备中扮演了重要的角色,能够支持高速数据传输和接收,为设备之间的数据传输提供了一种高效的解决方案。

SerDes的设计和实现是一项复杂的任务,需要充分考虑各种因素,以确保芯片具有高性能和高可靠性。

用低成本FPGA实现低延迟变化的CPRI

用低成本FPGA实现低延迟变化的CPRI

无线TEM(电信设备创造商)正受到布署基站架构的压力,这就是用更小体积、更低功耗、更低创造成原来建立,部署和运营。

达到此目的的关键策略是从基站中分别出RF接收器和功率,用它们来挺直驱动各自的天线。

这称为拉远技术(RRH)。

通过基于SERDES的公共无线接口(CPRI)将基带数据传回到基站。

本文主要阐述特定的低延迟变幻的设计思想,在低成本上利用SERDES和CPRI IP(学问产权)核实现。

RRH的部署

从“Hotel”基站分别射率(RF)收发器和的优点已经写得无数了,1所示。

但最引人注目的是RRH在功耗、灵便部署、小的固定体积,以及囫囵低成本方面的优点。

图1 射频拉远技术(RRH)计划随着RRH从基站里簇拥出来,运营商必需确保能够校准无线头和hotel BTS之间的系统延时,由于延时信息是用于系统校准的,必需使囫囵往返行程延时最短。

随着级联的RRH,添加了每个RRH跳的变幻,因此这个要求相应增强,针对单程和往返行程,CPRI规范处理这些链路时序的精确性。

针对低延迟变幻的FPGA实现

图2展示了现有的在传统SERDES/PCS实现中的主要功能块,加亮的部分突出了引起延时变幻的主要部分(如例子中展示的RX路径)

图2 传统的CPRI接收器实现计划

延时变幻来自几个单元,诸如模拟SERDES和数字PCS规律,以及实际的软IP本身。

模拟SERDES有相对紧凑的时序;然而,字对齐和桥接FIFO是两个主要的引起大的延时变幻的缘由。

提出一个解决计划前,

第1页共3页。

自适应动态延时调整的SERDES技术在宽带数据传输中的应用

自适应动态延时调整的SERDES技术在宽带数据传输中的应用张峰【摘要】According to the requirement of airborne equipment in wideband communication data link, the serial SERDES transmission technology is researched and an implementation of SERDES is proposed. Based on the Idelay primitives, an adaptive dynamic delay adjustment method is advanced, which eliminates 2. 496 ns time skew between several SERDES lanes within 32 ns. The experiment result shows that the method can achieve a data transmission speed of 850 Mb/s/Lane of 60 lanes,which satisfies the real pro-ject requirement and is transplantable. The research in this paper provides a good example for design of oth-er high-speed multilane data transmission systems.%针对宽带高速数传需求,提出了一种基于SERDES技术实现高速传输的解决方法。

通过对串行器/解串器( SERDES)原理进行研究,提出了一种利用Idelay原语实现SERDES延时的自适应动态调整方法,可动态调整延时2.496 ns,解决了SERDES传输时固有的相位漂移问题。

高速SERDES接口芯片的应用浅析

高速SERDES接口芯片的应用浅析摘要:本文主要分析高速SERDES接口芯片仿真验证和实际应用,其次阐述了TLK2711工作原理和工作属性,通过相关分析希望进一步提高高速SERDES接口芯片的应用效果,满足星上数传系统更高的速率要求,解决之前存在的技术难题,仅供参考。

关键词:高速SERDES接口;芯片;应用1、TLK2711工作原理TLK2711属于一种千兆高速收发器件,物理层接口器件的典型代表,可对高速串行数据完成接受工作,后将其转换使其成为需要的低速并行数据。

最后将低速并行数据发送出去,使其成为高速串行数据,无论是发送端还是接受端,都可对单工通信单独使用,也可对双工通信同时应用,在超高速双向传输系统(点对点)中可以有效应用。

对于工作原理,如图一所示。

TKLSB属于一种发送控制信号,为K码发生器提供服务,TKMSB也是如此。

TKLSB在发送数据中表示低8bit,数据或者K码,TKMSB表示的是高8bit,他们的使用一般都会结合起来,TXCLK为参考输入时钟,为发送端外部提供服务,发送过程中,TXCLK当中的上升沿,会将想用的TXD[15:0]提供出来,后借助差分高速通道完成编码的效果,编码为8B/10B,进行串行,便可根据顺序有效输出[1]。

这一过程中,时钟综合器会对时钟(TXCLK)10具有的倍频进行参考,当有Bit时钟产生后,可在串行器中使用,起作用于并行转串行移位寄存器,应用该时钟,Bit会沿着上升/下降沿,对数据进行发送,因此速率(串行数据)是时钟的二十倍。

相同的原理,RKLSB和RKMSB也属于指示信号,可为K码提供服务,低8bit和高8bit(数据或者K码)通过两者接收后,RXTLK变成时钟信号,负责接收以及恢复,串行数据只要经过编码后,便可被接收,内插器和时钟恢复电路会对数据流进行锁定,进而把比特率时钟提取出来。

重新计时数据流便可应用恢复的时钟,之后对齐好需要使用的串行数据,安排在2个10位码字边界的地方,实施8B/10B编码。

一文详解Xilinx高速收发器Serdes

一文详解Xilinx高速收发器Serdes

一、为什幺要用Serdes

传统的源同步传输,时钟和数据分离。

在速率比较低时(《1000M),没有问题。

在速率越来越高时,这样会有问题

由于传输线的时延不一致和抖动存在,接收端不能正确的采样数据,对不准眼图中点。

然后就想到了从数据里面恢复出时钟去采样数据,即CDR

这样就不存在延迟不一致的情况,有轻微的抖动也不会影响采样(恢复的时钟会随着数据一起抖动)。

二、为什幺要用8b10b,64b66b?

1 提供足够的跳变来恢复时钟

这样还有问题,收发两端必须共地,但往往很难实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Kintex7的SERDES的结构图CPRI应用的应用

Kintex7系列的GTX,以其良好的性能和功耗表现,已经成为业界FPGA选型时的明星。

由于其良好的DFE性能,它能提供高达12.5Gbps的过背板能力,能支持在插损高达30dB的信道上可靠传输。

在众多的SERDES应用中,有些应用比较特别,那就是需要在实际运行过程中动态切换GTX的链路速率,如无线中的CRPI接口,需要同时支持9.8G,4.9G,2.4G等众多速率。

那么,如何能做到可靠地进行速率切换呢?本文就此作为主题,希望能充分发挥GTX的优势。

1. 背景知识GTX结构Kintex7的SERDES的结构图如图1。

以发送方向为例,参看图2的发送方向的时钟分布图:

Kintex7在进行链路速率切换时,主要有如下几种办法:

1)切换QPLL/CPLL的参考钟源头;

2)通过DRP接口修改QPLL/CPLL的参数设置

3)切换QPLL/CPLL提供链路时钟;

4)调整PMA的分频系数。

GTX工作模式介绍在GTX内部,有2种工作模式:LPM模式和DFE模式。

LPM(Low Power Mode)模式是低功耗模式,其主要支持低插损信道,链路速率《11.2G,信道插损在12dB以下的情况。

在LPM模式中,CTLE和baseline wander cancellaTIon都是全自动的,不需要手工调整。

LPM模式的结构图如下:

DFE模式则提供更好的信道补偿,其能够支持高达12.5G的链路速率,并在信道插损大于8dB的场景下有良好表现。

DFE和CTLE不同,它不会放大噪声和串扰,能纠正信道不连续引起的反射。

它能自动利用AGC,CTLE,DFE和baseline wander cancellaTIon来完成信道补偿,同时也支持CTLE手动模式。

DFE模式下GTX的结构图如图4。