ATmega128

第2章_ATmega128硬件结构

广州大学 机电学院 庞志

$100CA

$1006:LDI R1,$0A $1008:LDS R2,$FF00 $100A:ADD R2,R1 $100C:STS $$FFFF0000(($$110A)) $FF00,R2

R1=$0A R2=$$11AA0

2020年5月19日星期二

广州大学 机电学院 庞志

广州大学 机电学院 庞志

ATmega128

单 片 机 方 框 图

2020年5月19日星期二

广州大学 机电学院 庞志

ATmega128

单 片 机 指 令 执 行 过 程

2020年5月19日星期二

广州大学 机电学院 庞志

$1006

10+(0xFF00$)1=0>0(60:xLFDFI 0R0)1,$0A

当RAMPZ0=1: ELPM/SPM可以访问程序存储器地址 $8000——$FFFF(高64K字节)

2020年5月19日星期二

广州大学 机电学院 庞志

2.2.3 指令执行时序

AVR CPU由系统时钟clkCPU驱动。

并行取指和执行时序

2020年5月19日星期二

广州大学 机电学院 庞志

单时钟周期ALU 操作

模拟比较器

2020年5月19日星期二

广州大学 机电学院 庞志

2.1.2 主要性能 (续)

特殊的处理器特点

上电复位 可编程的掉电检测 片内RC振荡器 片内/片外中断源 6种睡眠模式: 空闲模式、ADC噪声抑制模式、省电模

式、掉电模式、Standby模式以及扩展的Standby模式 可选的时钟频率 可选ATmega103兼容模式 全局上拉禁止功能

Bit 6 – T: 位拷贝存储 Bit 4 – S: 符号位,S=N⊕V Bit 2 – N: 负数标志 Bit 0 – C: 进位标志

ATMEGA128熔丝位配置详解

ATMEGA128熔丝位配置详解熔丝位配置2009-07-29 11:51在配置熔丝位时应特别注意,部分熔丝位(如OCDEN、JTAGEN和SPIEN等)的配置是不可逆的2009年04月17日星期五 11:28引言AVR系列单片机在仿真调试之前,首先必须对AVR的熔丝位和锁定位进行配置。

如果配置不当,则可能造成单片机不能正常工作,严重时可能导致单片机死锁。

因此,对单片机熔丝位和锁定位的正确配置显得尤为重要。

熔丝位是对单片机具体功能和工作模式的限定,其正确配置与否直接影响到单片机能否正常工作;锁定位是对单片机的程序和数据进行加密,以防止单片机中的程序和数据被读出或写入。

在进行配置时,一般先配置熔丝位,再配置锁定位。

锁定位又分为引导程序区锁定位和程序及数据存储器锁定位两类。

对引导程序区锁定位进行编程可以实现两套保护模式,即应用区保护模式和Boot Loader区保护模式;不同的编程配置可以实现不同的加密级别。

对程序及数据存储器锁定位进行编程可以禁止对并行和SPI/JTAG串行编程模式中Flash和EEPROM进一步编程,从而对程序和存储器中的数据进行保护。

由于引导程序锁定位和程序及数据存储器锁定位的配置具有可逆性,因此可根据不同的需要多次编程,灵活改变。

但是,在配置熔丝位时应特别注意,部分熔丝位(如OCDEN、JTAGEN和SPIEN等)的配置是不可逆的。

在采用单一编程下载情况下(例如只采用JTAG下载或者只采用AVRISP并行下载),一旦配置后将不可改变。

鉴于熔丝位配置的重要性,本文以AVR系列的ATmega128单片机为例,详细介绍熔丝位的配置以及在配置过程中常出现的一些问题,并给出相应的解决办法,成功地解决了因熔丝位配置不当而引起的单片机不能正常工作和死锁等一系列问题。

1 熔丝位的配置ATmega128的熔丝位共有3个字节:熔丝位扩展字节、熔丝位高字节和熔丝位低字节。

表1、表2和表3分别描述了所有熔丝位的功能、默认值以及它们是如何映射到熔丝位字节的。

atmega128芯片资料(英文)

1Features•High-performance, Low-power AVR ® 8-bit Microcontroller •Advanced RISC Architecture–133 Powerful Instructions – Most Single Clock Cycle Execution–32 x 8 General Purpose Working Registers + Peripheral Control Registers –Fully Static Operation–Up to 16 MIPS Throughput at 16 MHz –On-chip 2-cycle Multiplier•Nonvolatile Program and Data Memories–128K Bytes of In-System Reprogrammable FlashEndurance: 1,000 Write/Erase Cycles–Optional Boot Code Section with Independent Lock BitsIn-System Programming by On-chip Boot Program True Read-While-Write Operation –4K Bytes EEPROMEndurance: 100,000 Write/Erase Cycles –4K Bytes Internal SRAM–Up to 64K Bytes Optional External Memory Space –Programming Lock for Software Security –SPI Interface for In-System Programming •JTAG (IEEE std. 1149.1 Compliant) Interface–Boundary-scan Capabilities According to the JTAG Standard –Extensive On-chip Debug Support–Programming of Flash, EEPROM, Fuses and Lock Bits through the JTAG Interface •Peripheral Features–Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes–Two Expanded 16-bit Timer/Counters with Separate Prescaler, Compare Mode and Capture Mode–Real Time Counter with Separate Oscillator –Two 8-bit PWM Channels–6 PWM Channels with Programmable Resolution from 1 to 16 Bits –8-channel, 10-bit ADC8 Single-ended Channels 7 Differential Channels2 Differential Channels with Programmable Gain (1x, 10x, 200x)–Byte-oriented 2-wire Serial Interface –Dual Programmable Serial USARTs –Master/Slave SPI Serial Interface–Programmable Watchdog Timer with On-chip Oscillator –On-chip Analog Comparator •Special Microcontroller Features–Power-on Reset and Programmable Brown-out Detection –Internal Calibrated RC Oscillator–External and Internal Interrupt Sources–Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby–Software Selectable Clock Frequency–ATmega103 Compatibility Mode Selected by a Fuse –Global Pull-up Disable •I/O and Packages–53 Programmable I/O Lines –64-lead TQFP •Operating Voltages–2.7 - 5.5V (ATmega128L)–4.5 - 5.5V (ATmega128)•Speed Grades–0 - 8 MHz (ATmega128L)–0 - 16 MHz (ATmega128)Rev. 2467AS-08/01Microcontroller with 128K Bytes In-SystemProgrammable ATmega128ATmega128L Preliminary SummaryNote: This is a summary document. A complete document is available on our web site at .2ATmega128(L)2467AS –08/01Pin ConfigurationsFigure 1. Pinout ATmega128OverviewThe ATmega128 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle,the ATmega128 achieves throughputs approaching 1 MIPS per MHz allowing the sys-tem designer to optimize power consumption versus processing speed.3ATmega128(L)2467AS –08/01Block DiagramFigure 2. Block Diagram4ATmega128(L)2467AS –08/01The AVR core combines a rich instruction set with 32 general purpose working registers.All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.The ATmega128 provides the following features: 128K bytes of In-System Programma-ble Flash with Read-While-Write capabilities, 4K bytes EEPROM, 4K bytes SRAM, 53general-purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), four flexible timer/counters with compare modes and PWM, 2 USARTs, a byte oriented 2-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain, programmable Watchdog Timer with internal oscillator,an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM,timer/counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the oscillator, disabling all other chip func-tions until the next interrupt or hardware reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction Mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conver-sions. In Standby mode, the crystal/resonator oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption.In Extended Standby mode, both the main oscillator and the asynchronous timer con-tinue to run.The device is manufactured using Atmel ’s high-density nonvolatile memory technology.The on-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an on-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Soft-ware in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega128 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.The ATmega128 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.ATmega103 and ATmega128 CompatibilityThe ATmega128 is a highly complex microcontroller where the number of I/O locations supersedes the 64 I/O location reserved in the AVR instruction set. To ensure backward compatibility with the ATmega103, all I/O locations present in ATmega103 have the same location in ATmega128. Most additional I/O locations are added in an Extended I/O space starting from $60 to $FF, (i.e., in the ATmega103 internal RAM space). These location can be reached by using LD/LDS/LDD and ST/STS/STD instruction only, not by using IN and OUT instruction. The relocation of the internal RAM space may still be a problem for ATmega103 users. Also, the increased number of interrupt vectors might be a problem if the code uses absolute addresses. To solve these problems, an ATmega103 compatibility mode can be selected by programming the fuse M103C. In this mode, none of the functions in the Extended I/O space are in use, so the internal RAM is located as in ATmega103. Also, the extended interrupt vectors are removed.5ATmega128(L)2467AS –08/01The ATmega128 is 100% pin compatible with ATmega103, and can replace the ATmega103 on current Printed Circuit Boards. The application note “Replacing ATmega103 by ATmega128” describes what the user should be aware of replacing the ATmega103 by an ATmega128.ATmega103 Compatibility ModeBy programming the M103C fuse, the ATmega128 will be compatible with the ATmega103 regards to RAM, I/O pins and interrupt vectors as described above. How-ever, some new features in ATmega128 are not available in this compatibility mode,these features are listed below:•One USART instead of two, asynchronous mode only. Only the 8 least significant bits of the Baud Rate Register is available.•One 16 bits Timer/Counter with 2 compare registers instead of two 16-bit Timer/Counters with 3 compare registers.•2-wire serial interface is not supported.•Port G serves alternate functions only (not a general I/O port).•Port F serves as digital input only in addition to analog input to the ADC.•Boot Loader capabilities is not supported.•It is not possible to adjust the frequency of the internal calibrated RC oscillator.•The External Memory Interface can not release any Address pins for general I/O, neither configure different wait-states to different External Memory Address sections.Pin DescriptionsVCC Digital supply voltage.GNDGround.Port A (PA7..PA0)Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port A also serves the functions of various special features of the ATmega128 as listed on page 68.Port B (PB7..PB0)Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port B also serves the functions of various special features of the ATmega128 as listed on page 69.Port C (PC7..PC0)Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.6ATmega128(L)2467AS –08/01Port C also serves the functions of special features of the ATmega128 as listed on page 72. In ATmega103 compatibility mode, Port C is output only, and the port C pins are not tri-stated when a reset condition becomes active.Port D (PD7..PD0)Port D is an 8-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port D also serves the functions of various special features of the ATmega128 as listed on page 73.Port E (PE7..PE0)Port E is an 8-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port E also serves the functions of various special features of the ATmega128 as listed on page 76.Port F (PF7..PF0)Port F serves as the analog inputs to the A/D Converter.Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used.Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability.As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resis-tors on pins PF7(TDI), PF5(TMS) and PF4(TCK) will be activated even if a reset occurs.Port F also serves the functions of the JTAG interface.In ATmega103 compatibility mode, Port F is an input Port only.Port G (PG4..PG0)Port G is a 5-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port G also serves the functions of various special features.The port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.In ATmega103 compatibility mode, these pins only serves as strobes signals to the external memory as well as input to the 32 kHz oscillator, and the pins are initialized to PG0 = 1, PG1 = 1, and PG2 = 0 asynchronously when a reset condition becomes active,even if the clock is not running. PG3 and PG4 are oscillator pins.RESETReset input. A low level on this pin for longer than the minimum pulse length will gener-ate a reset, even if the clock is not running. The minimum pulse length is given in Table 19 on page 46. Shorter pulses are not guaranteed to generate a reset.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.7ATmega128(L)2467AS –08/01XTAL2Output from the inverting oscillator amplifier.AVCCThis is the supply voltage pin for Port F and the A/D Converter. It should be externally connected to VCC, even if the ADC is not used. If the ADC is used, it should be con-nected to VCC through a low-pass filter.AREF This is the analog reference pin for the A/D Converter.PENThis is a programming enable pin for the serial programming mode. By holding this pin low during a power-on reset, the device will enter the serial programming mode. PEN has no function during normal operation.8ATmega128(L)2467AS –08/01Register SummaryAddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page($FF)Reserved --------..Reserved --------($9E)Reserved --------($9D)UCSR1C -UMSEL1UPM11UPM10USBS1UCSZ11UCSZ10UCPOL1185($9C)UDR1USART1 I/O Data Register182($9B)UCSR1A RXC1TXC1UDRE1FE1DOR1UPE1U2X1MPCM1183($9A)UCSR1B RXCIE1TXCIE1UDRIE1RXEN1TXEN1UCSZ12RXB81TXB81184($99)UBRR1L USART1 Baud Rate Register Low186($98)UBRR1H ----USART1 Baud Rate Register High186($97)Reserved --------($96)Reserved --------($95)UCSR0C -UMSEL0UPM01UPM00USBS0UCSZ01UCSZ00UCPOL0185($94)Reserved --------($93)Reserved --------($92)Reserved --------($91)Reserved --------($90)UBRR0H ----USART0 Baud Rate Register High186($8F)Reserved --------($8E)Reserved --------($8D)Reserved --------($8C)TCCR3C FOC3A FOC3B FOC3C -----132($8B)TCCR3A COM3A1COM3A0COM3B1COM3B0COM3C1COM3C0WGM31WGM30127 ($8A)TCCR3B ICNC3ICES3-WGM33WGM32CS32CS31CS30130($89)TCNT3H Timer/Counter3 - Counter Register High Byte 132 ($88)TCNT3L Timer/Counter3 - Counter Register Low Byte132 ($87)OCR3AH Timer/Counter3 - Output Compare Register A High Byte 133($86)OCR3AL Timer/Counter3 - Output Compare Register A Low Byte 133($85)OCR3BH Timer/Counter3 - Output Compare Register B High Byte 133($84)OCR3BL Timer/Counter3 - Output Compare Register B Low Byte 133($83)OCR3CH Timer/Counter3 - Output Compare Register C High Byte 133($82)OCR3CL Timer/Counter3 - Output Compare Register C Low Byte 133($81)ICR3H Timer/Counter3 - Input Capture Register High Byte 134($80)ICR3L Timer/Counter3 - Input Capture Register Low Byte134($7F)Reserved --------($7E)Reserved --------($7D)ETIMSK --TICIE3OCIE3A OCIE3B TOIE3OCIE3C OCIE1C 135 ($7C)ETIFR --ICF3OCF3A OCF3B TOV3OCF3COCF1C136($7B)Reserved --------($7A)TCCR1C FOC1AFOC1BFOC1C-----131($79)OCR1CH Timer/Counter1 - Output Compare Register C High Byte 133($78)OCR1CL Timer/Counter1 - Output Compare Register C Low Byte133($77)Reserved --------($76)Reserved --------($75)Reserved --------($74)TWCR TWINT TWEA TWSTA TWSTO TWWC TWEN -TWIE 198($73)TWDR 2-wire Serial Interface Data Register199($72)TWAR TWA6TWA5TWA4TWA3TWA2TWA1TWA0TWGCE 200($671TWSR TWS7TWS6TWS5TWS4TWS3-TWPS1TWPS0199($70)TWBR 2-wire Serial Interface Bit Rate Register 197($6F)OSCCAL Oscillator Calibration Register38($6E)Reserved --------($6D)XMCRA -SRL2SRL1SRL0SRW01SRW00SRW1129($6C)XMCRB XMBK ----XMM2XMM1XMM031($6B)Reserved --------($6A)EICRA ISC31ISC30ISC21ISC20ISC11ISC10ISC01ISC0084($69)Reserved --------($68)SPMCSR SPMIE RWWSB-RWWSREBLBSETPGWRTPGERSSPMEN270($67)Reserved --------($66)Reserved --------($65)PORTG ---PORTG4PORTG3PORTG2PORTG1PORTG083($64)DDRG ---DDG4DDG3DDG2DDG1DDG083($63)PING ---PING4PING3PING2PING1PING083($62)PORTFPORTF7PORTF6PORTF5PORTF4PORTF3PORTF2PORTF1PORTF0839ATmega128(L)2467AS –08/01($61)DDRF DDF7DDF6DDF5DDF4DDF3DDF2DDF1DDF083($60)Reserved --------$3F ($5F)SREG I T H S V N Z C 9$3E ($5E)SPH SP15SP14SP13SP12SP11SP10SP9SP812$3D ($5D)SPL SP7SP6SP5SP4SP3SP2SP1SP012$3C ($5C)XDIV XDIVENXDIV6XDIV5XDIV4XDIV3XDIV2XDIV1XDIV039$3B ($5B)RAMPZ -------RAMPZ012$3A ($5A)EICRB ISC71ISC70ISC61ISC60ISC51ISC50ISC41ISC4085$39 ($59)EIMSK INT7INT6INT5INT4INT3INT2INT1INT086$38 ($58)EIFR INTF7INTF6INTF5INTF4INTF3INTF INTF1INTF086$37 ($57)TIMSK OCIE2TOIE2TICIE1OCIE1A OCIE1B TOIE1OCIE0TOIE0103, 134, 153$36 ($56)TIFR OCF2TOV2ICF1OCF1A OCF1B TOV1OCF0TOV0103, 136, 154$35 ($55)MCUCR SRE SRW10SE SM1SM0SM2IVSEL IVCE 29, 41, 58 $34 ($54)MCUCSR JTD --JTRF WDRF BORF EXTRF PORF 49, 246$33 ($53)TCCR0FOC0WGM00COM01COM00WGM01CS02CS01CS0098$32 ($52)TCNT0 Timer/Counter0 (8 Bit)100$31 ($51)OCR0 Timer/Counter0 Output Compare Register100$30 ($50)ASSR ----AS0TCN0UB OCR0UB TCR0UB 101$2F ($4F)TCCR1A COM1A1COM1A0COM1B1COM1B0COM1C1COM1C0WGM11WGM10127$2E ($4E)TCCR1B ICNC1ICES1-WGM13WGM12CS12CS11CS10130$2D ($4D)TCNT1H Timer/Counter1 - Counter Register High Byte 132$2C ($4C)TCNT1L Timer/Counter1 - Counter Register Low Byte132$2B ($4B)OCR1AH Timer/Counter1 - Output Compare Register A High Byte 133$2A ($4A)OCR1AL Timer/Counter1 - Output Compare Register A Low Byte 133$29 ($49)OCR1BH Timer/Counter1 - Output Compare Register B High Byte 133$28 ($48)OCR1BL Timer/Counter1 - Output Compare Register B Low Byte 133$27 ($47)ICR1H Timer/Counter1 - Input Capture Register High Byte 134$26 ($46)ICR1L Timer/Counter1 - Input Capture Register Low Byte 134$25 ($45)TCCR2FOC2WGM20COM21COM20WGM21CS22CS21CS20151$24 ($44)TCNT2Timer/Counter2 (8 Bit)153$23 ($43)OCR2Timer/Counter2 Output Compare Register 153$22 ($42)OCDR IDRD/OCDR7OCDR6OCDR5OCDR4OCDR3OCDR2OCDR1OCDR0242$21 ($41)WDTCR ---WDCE WDE WDP2WDP1WDP051$20 ($40)SFIOR TSM --ADHSMACMEPUDPSR0PSR32167, 104, 139, 237$1F ($3F)EEARH ----EEPROM Address Register High19$1E ($3E)EEARL EEPROM Address Register Low Byte 19$1D ($3D)EEDR EEPROM Data Register20$1C ($3C)EECR ----EERIE EEMWE EEWE EERE 20$1B ($3B)PORTA PORTA7PORTA6PORTA5PORTA4PORTA3PORTA2PORTA1PORTA081$1A ($3A)DDRA DDA7DDA6DDA5DDA4DDA3DDA2DDA1DDA081$19 ($39)PINA PINA7PINA6PINA5PINA4PINA3PINA2PINA1PINA081$18 ($38)PORTB PORTB7PORTB6PORTB5PORTB4PORTB3PORTB2PORTB1PORTB081$17 ($37)DDRB DDB7DDB6DDB5DDB4DDB3DDB2DDB1DDB081$16 ($36)PINB PINB7PINB6PINB5PINB4PINB3PINB2PINB1PINB082$15 ($35)PORTC PORTC7PORTC6PORTC5PORTC4PORTC3PORTC2PORTC1PORTC082$14 ($34)DDRC DDC7DDC6DDC5DDC4DDC3DDC2DDC1DDC082$13 ($33)PINC PINC7PINC6PINC5PINC4PINC3PINC2PINC1PINC082$12 ($32)PORTD PORTD7PORTD6PORTD5PORTD4PORTD3PORTD2PORTD1PORTD082$11 ($31)DDRD DDD7DDD6DDD5DDD4DDD3DDD2DDD1DDD082$10 ($30)PIND PIND7PIND6PIND5PIND4PIND3PIND2PIND1PIND082$0F ($2F)SPDR SPI Data Register163$0E ($2E)SPSR SPIF WCOL -----SPI2X 162$0D ($2D)SPCR SPIE SPE DORD MSTR CPOL CPHA SPR1SPR0161$0C ($2C)UDR0 USART0 I/O Data Register182$0B ($2B)UCSR0A RXC0TXC0UDRE0FE0DOR0UPE0U2X0MPCM0183$0A ($2A)UCSR0B RXCIE0TXCIE0UDRIE0RXEN0TXEN0UCSZ02RXB80TXB80184$09 ($29)UBRR0L USART0 Baud Rate Register Low186$08 ($28)ACSR ACD ACBG ACO ACI ACIE ACIC ACIS1ACIS0218$07 ($27)ADMUX REFS1REFS0ADLAR MUX4MUX3MUX2MUX1MUX0233$06 ($26)ADCSRA ADENADSCADRFADIFADIEADPS2ADPS1ADPS0235$05 ($25)ADCH ADC Data Register High Byte 236$04 ($24)ADCL ADC Data Register Low byte 236$03 ($23)PORTE PORTE7PORTE6PORTE5PORTE4PORTE3PORTE2PORTE1PORTE082$02 ($22)DDREDDE7DDE6DDE5DDE4DDE3DDE2DDE1DDE083Register Summary (Continued)AddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page10ATmega128(L)2467AS –08/01Notes:1.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addressesshould never be written.2.Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate onall bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers $00 to $1F only.$01 ($21)PINE PINE7PINE6PINE5PINE4PINE3PINE2PINE1PINE083$00 ($20)PINFPINF7PINF6PINF5PINF4PINF3PINF2PINF1PINF083Register Summary (Continued)AddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page11ATmega128(L)2467AS –08/01Instruction Set SummaryMnemonicsOperandsDescriptionOperationFlags#ClocksARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add two RegistersRd ← Rd + Rr Z,C,N,V,H 1ADC Rd, Rr Add with Carry two Registers Rd ← Rd + Rr + C Z,C,N,V,H 1ADIW Rdl,K Add Immediate to Word Rdh:Rdl ← Rdh:Rdl + K Z,C,N,V,S 2SUB Rd, Rr Subtract two RegistersRd ← Rd - Rr Z,C,N,V,H 1SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H 1SBC Rd, Rr Subtract with Carry two Registers Rd ← Rd - Rr - C Z,C,N,V,H 1SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H 1SBIW Rdl,K Subtract Immediate from Word Rdh:Rdl ← Rdh:Rdl - K Z,C,N,V,S 2AND Rd, Rr Logical AND RegistersRd ← Rd • Rr Z,N,V 1ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V 1OR Rd, Rr Logical OR RegistersRd ← Rd v Rr Z,N,V 1ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V 1EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V 1COM Rd One ’s Complement Rd ← $FF − Rd Z,C,N,V 1NEG Rd Two ’s Complement Rd ← $00 − Rd Z,C,N,V,H 1SBR Rd,K Set Bit(s) in Register Rd ← Rd v K Z,N,V 1CBR Rd,K Clear Bit(s) in Register Rd ← Rd • ($FF - K)Z,N,V 1INC Rd Increment Rd ← Rd + 1Z,N,V 1DEC Rd DecrementRd ← Rd − 1 Z,N,V 1TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V 1CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V 1SER Rd Set Register Rd ← $FF None 1MUL Rd, Rr Multiply Unsigned R1:R0 ← Rd x Rr Z,C 2MULS Rd, Rr Multiply SignedR1:R0 ← Rd x Rr Z,C 2MULSU Rd, Rr Multiply Signed with Unsigned R1:R0 ← Rd x Rr Z,C 2FMUL Rd, Rr Fractional Multiply Unsigned R1:R0 ← (Rd x Rr) << 1Z,C 2FMULS Rd, Rr Fractional Multiply SignedR1:R0 ← (Rd x Rr) << 1Z,C 2FMULSU Rd, Rr Fractional Multiply Signed with Unsigned R1:R0 ← (Rd x Rr) << 1Z,C 2BRANCH INSTRUCTIONSRJMP kRelative Jump PC ← PC + k + 1None 2IJMP Indirect Jump to (Z)PC ← Z None 2JMP k Direct JumpPC ← kNone 3RCALL kRelative Subroutine Call PC ← PC + k + 1None 3ICALL Indirect Call to (Z)PC ← Z None 3CALL k Direct Subroutine Call PC ← k None 4RET Subroutine Return PC ← STACK None 4RETI Interrupt Return PC ← STACKI 4CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None 1 / 2 / 3CP Rd,Rr CompareRd − Rr Z, N,V,C,H 1 CPC Rd,Rr Compare with CarryRd − Rr − C Z, N,V,C,H 1CPI Rd,K Compare Register with Immediate Rd − KZ, N,V,C,H 1SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b)=0) PC ← PC + 2 or 3 None 1 / 2 / 3SBRS Rr, b Skip if Bit in Register is Set if (Rr(b)=1) PC ← PC + 2 or 3None 1 / 2 / 3SBIC P, b Skip if Bit in I/O Register Cleared if (P(b)=0) PC ← PC + 2 or 3 None 1 / 2 / 3SBIS P, b Skip if Bit in I/O Register is Set if (P(b)=1) PC ← PC + 2 or 3None 1 / 2 / 3BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC ←PC+k + 1None 1 / 2BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC ←PC+k + 1None 1 / 2BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None 1 / 2BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None 1 / 2BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None 1 / 2BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None 1 / 2BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None 1 / 2BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None 1 / 2BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None 1 / 2BRPL k Branch if Plusif (N = 0) then PC ← PC + k + 1None 1 / 2BRGE k Branch if Greater or Equal, Signed if (N ⊕ V= 0) then PC ← PC + k + 1None 1 / 2BRLT k Branch if Less Than Zero, Signed if (N ⊕ V= 1) then PC ← PC + k + 1None 1 / 2BRHS k Branch if Half Carry Flag Set if (H = 1) then PC ← PC + k + 1None 1 / 2BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC ← PC + k + 1None 1 / 2BRTS k Branch if T Flag Set if (T = 1) then PC ← PC + k + 1None 1 / 2BRTC k Branch if T Flag Cleared if (T = 0) then PC ← PC + k + 1None 1 / 2BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None 1 / 2BRVCk Branch if Overflow Flag is Clearedif (V = 0) then PC ← PC + k + 1None1 / 212ATmega128(L)2467AS –08/01MnemonicsOperandsDescriptionOperationFlags#ClocksBRIE k Branch if Interrupt Enabled if ( I = 1) then PC ← PC + k + 1None 1 / 2BRID k Branch if Interrupt Disabled if ( I = 0) then PC ← PC + k + 1None 1 / 2DATA TRANSFER INSTRUCTIONSMOV Rd, Rr Move Between Registers Rd ← RrNone 1MOVW Rd, Rr Copy Register Word Rd+1:Rd ← Rr+1:Rr None 1LDI Rd, K Load Immediate Rd ← K None 1LD Rd, X Load IndirectRd ← (X)None 2LD Rd, X+Load Indirect and Post-Inc.Rd ← (X), X ← X + 1None 2LD Rd, - X Load Indirect and Pre-Dec.X ← X - 1, Rd ← (X)None 2LD Rd, Y Load IndirectRd ← (Y)None 2LD Rd, Y+Load Indirect and Post-Inc.Rd ← (Y), Y ← Y + 1None 2LD Rd, - Y Load Indirect and Pre-Dec.Y ← Y - 1, Rd ← (Y)None 2LDD Rd,Y+q Load Indirect with Displacement Rd ← (Y + q)None 2LD Rd, Z Load IndirectRd ← (Z)None 2LD Rd, Z+Load Indirect and Post-Inc.Rd ← (Z), Z ← Z+1None 2LD Rd, -Z Load Indirect and Pre-Dec.Z ← Z - 1, Rd ← (Z)None 2LDD Rd, Z+q Load Indirect with Displacement Rd ← (Z + q)None 2LDS Rd, k Load Direct from SRAM Rd ← (k)None 2ST X, Rr Store Indirect(X) ← RrNone 2ST X+, Rr Store Indirect and Post-Inc.(X) ← Rr, X ← X + 1None 2ST - X, Rr Store Indirect and Pre-Dec.X ← X - 1, (X) ← Rr None 2ST Y, Rr Store Indirect(Y) ← RrNone 2ST Y+, Rr Store Indirect and Post-Inc.(Y) ← Rr, Y ← Y + 1None 2ST - Y, Rr Store Indirect and Pre-Dec.Y ← Y - 1, (Y) ← Rr None 2STD Y+q,Rr Store Indirect with Displacement (Y + q) ← Rr None 2ST Z, Rr Store Indirect(Z) ← RrNone 2ST Z+, Rr Store Indirect and Post-Inc.(Z) ← Rr, Z ← Z + 1None 2ST -Z, Rr Store Indirect and Pre-Dec.Z ← Z - 1, (Z) ← Rr None 2STD Z+q,Rr Store Indirect with Displacement (Z + q) ← Rr None 2STS k, RrStore Direct to SRAM (k) ← Rr None 2LPM Load Program Memory R0 ← (Z)None 3LPM Rd, Z Load Program MemoryRd ← (Z)None 3LPM Rd, Z+Load Program Memory and Post-Inc Rd ← (Z), Z ← Z+1None 3ELPM Extended Load Program Memory R0 ← (RAMPZ:Z)None 3ELPM Rd, Z Extended Load Program MemoryRd ← (RAMPZ:Z)None 3ELPM Rd, Z+Extended Load Program Memory and Post-Inc Rd ← (RAMPZ:Z), RAMPZ:Z ← RAMPZ:Z+1None 3SPM Store Program Memory (Z) ← R1:R0None -IN Rd, P In Port Rd ← P None 1OUT P, Rr Out PortP ← Rr None 1PUSH Rr Push Register on Stack STACK ← Rr None 2POP Rd Pop Register from Stack Rd ← STACK None 2BIT AND BIT-TEST INSTRUCTIONSSBI P,b Set Bit in I/O Register I/O(P,b) ← 1None 2CBI P,b Clear Bit in I/O Register I/O(P,b) ← 0None 2LSL Rd Logical Shift Left Rd(n+1) ← Rd(n), Rd(0) ← 0Z,C,N,V 1LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0Z,C,N,V 1ROL Rd Rotate Left Through Carry Rd(0)←C,Rd(n+1)← Rd(n),C ←Rd(7)Z,C,N,V 1ROR Rd Rotate Right Through Carry Rd(7)←C,Rd(n)← Rd(n+1),C ←Rd(0)Z,C,N,V 1ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n=0..6Z,C,N,V 1SWAP Rd Swap Nibbles Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0)None 1BSET s Flag Set SREG(s) ← 1SREG(s)1BCLR s Flag ClearSREG(s) ← 0 SREG(s)1BST Rr, b Bit Store from Register to T T ← Rr(b)T 1BLD Rd, b Bit load from T to Register Rd(b) ← T None 1SEC Set Carry C ←1C 1CLC Clear Carry C ← 0 C 1SEN Set Negative Flag N ← 1N 1CLN Clear Negative Flag N ← 0 N 1SEZ Set Zero Flag Z ←1Z 1CLZ Clear Zero Flag Z ← 0 Z 1SEI Global Interrupt Enable I ←1I 1CLI Global Interrupt Disable I ← 0 I 1SES Set Signed Test Flag S ←1S 1CLSClear Signed Test FlagS ← 0S1Instruction Set Summary (Continued)。

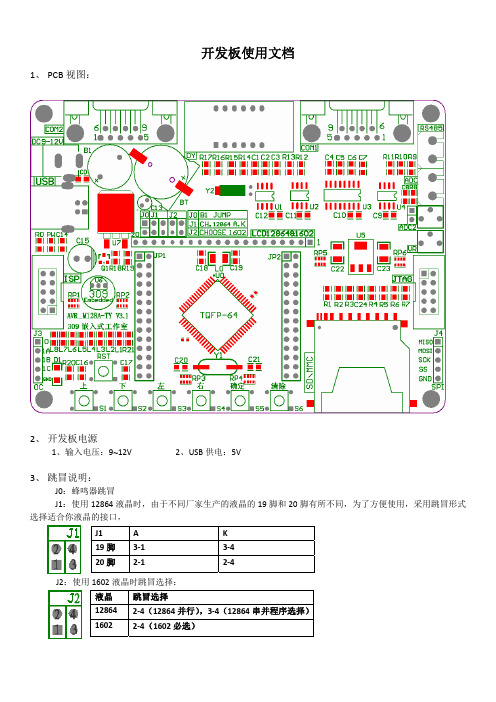

ATmega128开发板功能说明

开发板使用文档1、 PCB 视图:2、 开发板电源1、输入电压:9~12V2、USB 供电:5V3、 跳冒说明:J0:蜂鸣器跳冒J1:使用12864液晶时,由于不同厂家生产的液晶的19脚和20脚有所不同,为了方便使用,采用跳冒形式选择适合你液晶的接口,J2:使用1602液晶时跳冒选择:J1 A K 19脚 3‐1 3‐4 20脚2‐12‐4液晶 跳冒选择12864 2‐4(12864并行),3‐4(12864串并程序选择)16022‐4(1602必选)3、功能说明:1、温度传感器18B202、两通道ADC3、4位数码管显示4、实时时钟DS13025、串口0,串口16、SD卡读写7、IIC_24C02(TWI)8、RS485通讯9、LCD12864接口10、LCD1602接口11、6个按键(有上,下,左,右,确定,取消)12、跑马灯13、SPI14、JTAG接口15、ISP接口16、蜂蜜器17、USB供电18、I/O口扩展4、实验例程:1、跑马灯2、数码管显示3、蜂鸣器4、定时器0输出方波5、定时器2中断6、外部中断7、串口实验 8、RS4859、AT24C02 10、按键实验11、1602液晶显示 12、12864液晶显示13、ADC数码管显示实验 14、ADC在12864液晶显示15、DS18B20数码管显示 16、DS18B20液晶1620显示17、DS18B20液晶LCD12864显示 18、DS1302实时时钟1602显示19、DS1302实时时钟LCD12864显示 20、DS18B20实时时钟液晶显示21、串口多机通讯 22、RS485多机通讯23、SD卡读写 24、SPI通讯25、μCOS-II在ATmega128开发板上的移植。

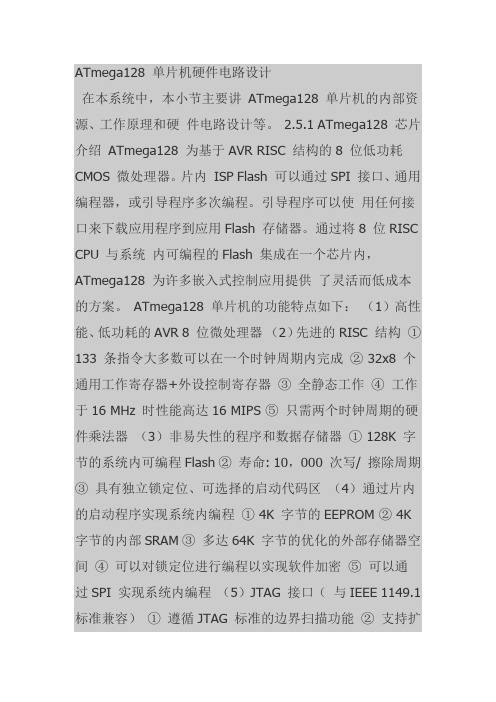

ATmega128 单片机硬件电路设计

ATmega128 单片机硬件电路设计在本系统中,本小节主要讲ATmega128 单片机的内部资源、工作原理和硬件电路设计等。

2.5.1 ATmega128 芯片介绍ATmega128 为基于AVR RISC 结构的8 位低功耗CMOS 微处理器。

片内ISP Flash 可以通过SPI 接口、通用编程器,或引导程序多次编程。

引导程序可以使用任何接口来下载应用程序到应用Flash 存储器。

通过将8 位RISC CPU 与系统内可编程的Flash 集成在一个芯片内,ATmega128 为许多嵌入式控制应用提供了灵活而低成本的方案。

ATmega128 单片机的功能特点如下:(1)高性能、低功耗的AVR 8 位微处理器(2)先进的RISC 结构①133 条指令大多数可以在一个时钟周期内完成② 32x8 个通用工作寄存器+外设控制寄存器③全静态工作④工作于16 MHz 时性能高达16 MIPS ⑤只需两个时钟周期的硬件乘法器(3)非易失性的程序和数据存储器① 128K 字节的系统内可编程Flash ②寿命: 10,000 次写/ 擦除周期③具有独立锁定位、可选择的启动代码区(4)通过片内的启动程序实现系统内编程① 4K 字节的EEPROM ② 4K 字节的内部SRAM ③多达64K 字节的优化的外部存储器空间④可以对锁定位进行编程以实现软件加密⑤可以通过SPI 实现系统内编程(5)JTAG 接口(与IEEE 1149.1 标准兼容)①遵循JTAG 标准的边界扫描功能②支持扩展的片内调试③通过JTAG 接口实现对Flash,EEPROM,熔丝位和锁定位的编程(6)外设特点①两个具有独立的预分频器和比较器功能的8 位定时器/ 计数器②两个具有预分频器、比较功能和捕捉功能的16 位定时器/ 计数器③具有独立预分频器的实时时钟计数器④两路8 位PWM ⑤ 6 路分辨率可编程(2 到16 位)的PWM ⑥输出比较调制器⑦ 8 路10 位ADC ⑧面向字节的两线接口⑨两个可编程的串行USART ⑩可工作于主机/ 从机模式的SPI 串行接口(7)特殊的处理器特点①上电复位以及可编程的掉电检测②片内经过标定的RC 振荡器③片内/ 片外中断源④ 6 种睡眠模式: 空闲模式、ADC 噪声抑制模式、省电模式、掉电模式、Standby 模式以及扩展的Standby 模式⑤可以通过软件进行选择的时钟频率⑥通过熔丝位可以选择ATmega103 兼容模式⑦全局上拉禁止功能ATmega128 芯片有64 个引脚,其中60 个引脚具有I/O 口功能,资源比较丰富,下面对ATmega128 的各个引脚做简单介绍:VCC:数字电路的电源。

ATMEGA128熔丝位配置详解

ATMEGA128熔丝位配置详解熔丝位配置2009-07-29 11:51在配置熔丝位时应特别注意,部分熔丝位(如OCDEN、JTAGEN和SPIEN等)的配置是不可逆的2009年04月17日星期五 11:28引言AVR系列单片机在仿真调试之前,首先必须对AVR的熔丝位和锁定位进行配置。

如果配置不当,则可能造成单片机不能正常工作,严重时可能导致单片机死锁。

因此,对单片机熔丝位和锁定位的正确配置显得尤为重要。

熔丝位是对单片机具体功能和工作模式的限定,其正确配置与否直接影响到单片机能否正常工作;锁定位是对单片机的程序和数据进行加密,以防止单片机中的程序和数据被读出或写入。

在进行配置时,一般先配置熔丝位,再配置锁定位。

锁定位又分为引导程序区锁定位和程序及数据存储器锁定位两类。

对引导程序区锁定位进行编程可以实现两套保护模式,即应用区保护模式和Boot Loader区保护模式;不同的编程配置可以实现不同的加密级别。

对程序及数据存储器锁定位进行编程可以禁止对并行和SPI/JTAG串行编程模式中Flash和EEPROM进一步编程,从而对程序和存储器中的数据进行保护。

由于引导程序锁定位和程序及数据存储器锁定位的配置具有可逆性,因此可根据不同的需要多次编程,灵活改变。

但是,在配置熔丝位时应特别注意,部分熔丝位(如OCDEN、JTAGEN和SPIEN等)的配置是不可逆的。

在采用单一编程下载情况下(例如只采用JTAG下载或者只采用AVRISP并行下载),一旦配置后将不可改变。

鉴于熔丝位配置的重要性,本文以AVR系列的ATmega128单片机为例,详细介绍熔丝位的配置以及在配置过程中常出现的一些问题,并给出相应的解决办法,成功地解决了因熔丝位配置不当而引起的单片机不能正常工作和死锁等一系列问题。

1 熔丝位的配置ATmega128的熔丝位共有3个字节:熔丝位扩展字节、熔丝位高字节和熔丝位低字节。

表1、表2和表3分别描述了所有熔丝位的功能、默认值以及它们是如何映射到熔丝位字节的。

ATmega128简介

◦ ◦ ◦

2.2、产品特点 5)特殊微控制器特性

◦

复位、中断源、省电模式等 53个可编程I/O口线 64引脚TQFP与64引脚MLF封装 2.7~5.5V(ATmega128L) 4.5~5.5V(ATmega128) 0~8MHZ(ATmega128L) 0~16MHZ(ATmega128)

6)I/O和封装

中档(标准) AT90S系列单片机,40脚 ◦ AT90S1200/2313/8515/8535 ◦ AT89C51 高档ATmega系列单片机 64脚 ◦ ATmega8/16/32/64/128 ◦ 存储容量为8/16/32/64/128KB ◦ ATmega8515/8535

2、ATmega128单片机简介

MCUCR寄存器如下所示:

ATmega128单片机结构框图

端口F驱动

端口F 数据寄存器 端口F方向 数据寄存器

端口A驱动

端口A 数据寄存器 端口A方向 数据寄存器

端口C驱动

端口C 数据寄存器 端口C方向 数据寄存器

内部晶振 晶振 JTAG接口 编程计数器 堆栈指针 晶振 时序控制

在线调试

编程Flash

◦ 电路:自动上电复位、看门狗、掉电检测, ◦ 多个复位源等

8)具有多种省电休眠模式、宽电压运行 (2.7~5V),抗干扰能力强,可降低一般8位机 中的软件抗干扰设计的工作量和硬件的使用量。 9)集成多种器件和多种功能,充分体现了单片机 技术向片上系统SOC的发展方向过渡。

1.2 、AVR系列单片机的选型 AVR单片机有3个档次: 低档Tiny系列单片机, 20脚 ◦ Tiny 11/12/13/15/26/28 ◦ AT89C1051,AT89C1052

atmega128实用双串口通讯

}

tx_data[21] =data;

led_2_0();

//----------------数据校验、处理部分

if( (tx_data[0]==0xfe) && (tx_data[21]==0x16) )

{

//--------------------------略 }

} //--------uart 1----RX-----中断方式- 同上---------------------ISR(USART1_RX_vect) {

unsigned char status,data; status=UCSR1A; data=UDR1; unsigned char f; //----status &= ~(FRAMING_ERROR1 | PARITY_ERROR1 | DATA_OVERRUN1); //----f=data;

//---------------------------------------------

#define

led_1_1() (PORTE |= bit(3))//--1

#define #define #define #define #define #define #define #define #define

Atmega128 实用串口通讯程序

1、 双串口异步通讯, USART0——发送使能,接收使能 、2400bps/8 位/偶校验/1 停止位

USART1——发送使能、9600bps/8 位/无校验/1 停止位

2、 外围 5 个 LED 指示 共阳极, PE3~PE7

#include <avr/io.h> #include <util/delay.h> #include <stdio.h> #include <avr/interrupt.h> #include <avr/wdt.h>

ATmega128寄存器概述

ATmega128寄存器概述($FF) 保留––––––––.. 保留––––––––($9E) 保留––––––––($9D) UCSR1C – UMSEL1 UPM11 UPM10 USBS1 UCSZ11 UCSZ10 UCPOL1 174 ($9C) UDR1 USART1 I/O 数据寄存器173 ($9B) UCSR1A RXC1 TXC1 UDRE1 FE1 DOR1 UPE1 U2X1 MPCM1 173 ($9A) UCSR1B RXCIE1 TXCIE1 UDRIE1 RXEN1 TXEN1 UCSZ12 RXB81 TXB81 174 ($99) UBRR1L USART1 波特率寄存器低字节176 ($98) UBRR1H –––– USART1 波特率寄存器高字节176 ($97) 保留––––––––($96) 保留––––––––($95) UCSR0C – UMSEL0 UPM01 UPM00 USBS0 UCSZ01 UCSZ00 UCPOL0 174 ($94) 保留––––––––($93) 保留––––––––($92) 保留––––––––($91) 保留––––––––($90) UBRR0H –––– USART0 波特率寄存器高字节176 ($8F) 保留––––––––($8E) 保留––––––––($8D) 保留––––––––($8C) TCCR3C FOC3A FOC3B FOC3C –––––124 ($8B) TCCR3A COM3A1 COM3A0 COM3B1 COM3B0 COM3C1 COM3C0 WGM31 WGM30 120 ($8A) TCCR3B ICNC3 ICES3 – WGM33 WGM32 CS32 CS31 CS30 123 ($89) TCNT3H T/C3 –计数器寄存器高字节125 ($88) TCNT3L T/C3 –计数器寄存器低字节125 ($87) OCR3AH T/C3 –输出比较寄存器A 高字节125 ($86) OCR3AL T/C3 –输出比较寄存器A 低字节125 ($85) OCR3BH T/C3 –输出比较寄存器B 高字节125 ($84) OCR3BL T/C3 –输出比较寄存器B 低字节125 ($83) OCR3CH T/C3–输出比较寄存器C 高字节126 ($82) OCR3CL T/C3 –输出比较寄存器C 低字节125 ($81) ICR3H T/C3 –输入捕捉寄存器高字节126 ($80) ICR3L T/C3 –输入捕捉寄存器低字节126 ($7F) 保留––––––––($7E) 保留––––––––($7D) ETIMSK –– TICIE3 OCIE3A OCIE3B TOIE3 OCIE3C OCIE1C 127 ($7C) ETIFR –– ICF3 OCF3A OCF3B TOV3 OCF3C OCF1C 128 ($7B) 保留––––––––($7A) TCCR1C FOC1A FOC1B FOC1C –––––124 ($79) OCR1CH T/C1 –输出比较寄存器C 高字节125 ($78) OCR1CL T/C1 –输出比较寄存器C 低字节125($77) 保留––––––––($76) 保留––––––––($75) 保留––––––––($74) TWCR TWINT TWEA TWSTA TWSTO TWWC TWEN – TWIE 188 ($73) TWDR 两线串行接口数据寄存器189 ($72) TW AR TW A6 TW A5 TW A4 TW A3 TW A2 TWA1 TW A0 TWGCE 190 ($71) TWSR TWS7 TWS6 TWS5 TWS4 TWS3 – TWPS1 TWPS0 189 ($70) TWBR 两线串行接口比特率寄存器188 ($6F) OSCCAL 振荡器标定寄存器38 ($6E) 保留––––––––($6D) XMCRA – SRL2 SRL1 SRL0 SRW01 SRW00 SRW11 28 ($6C) XMCRB XMBK –––– XMM2 XMM1 XMM0 29 ($6B) 保留––––––––($6A) EICRA ISC31 ISC30 ISC21 ISC20 ISC11 ISC10 ISC01 ISC00 84 ($69) 保留––––––––($68) SPMCSR SPMIE RWWSB – RWWSRE BLBSET PGWRT PGERS SPMEN 258 ($67) 保留––––––––($66) 保留––––––––($65) PORTG ––– PORTG4 PORTG3 PORTG2 PORTG1 PORTG0 83 ($64) DDRG ––– DDG4 DDG3 DDG2 DDG1 DDG0 83 ($63) PING ––– PING4 PING3 PING2 PING1 PING0 83 ($62) PORTF PORTF7 PORTF6 PORTF5 PORTF4 PORTF3 PORTF2 PORTF1 PORTF082 ($61) DDRF DDF7 DDF6 DDF5 DDF4 DDF3 DDF2 DDF1 DDF0 83 ($60) Reserved ––––––––$3F ($5F) SREG I T H S V N Z C 8$3E ($5E) SPH SP15 SP14 SP13 SP12 SP11 SP10 SP9 SP8 11$3D ($5D) SPL SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0 11$3C ($5C) XDIV XDIVEN XDIV6 XDIV5 XDIV4 XDIV3 XDIV2 XDIV1 XDIV0 40$3B ($5B) RAMPZ ––––––– RAMPZ0 11$3A ($5A) EICRB ISC71 ISC70 ISC61 ISC60 ISC51 ISC50 ISC41 ISC40 84$39 ($59) EIMSK INT7 INT6 INT5 INT4 INT3 INT2 INT1 INT0 85$38 ($58) EIFR INTF7 INTF6 INTF5 INTF4 INTF3 INTF INTF1 INTF0 85$37 ($57) TIMSK OCIE2 TOIE2 TICIE1 OCIE1A OCIE1B TOIE1 OCIE0 TOIE0 98, 126,144 $36 ($56) TIFR OCF2 TOV2 ICF1 OCF1A OCF1B TOV1 OCF0 TOV0 98, 128,144 $35 ($55) MCUCR SRE SRW10 SE SM1 SM0 SM2 IVSEL IVCE 28, 41, 58 $34 ($54) MCUCSR JTD –– JTRF WDRF BORF EXTRF PORF 50, 237 $33 ($53) TCCR0 FOC0 WGM00 COM01 COM00 WGM01 CS02 CS01 CS00 94$32 ($52) TCNT0 T/C0 (8 比特) 96$31 ($51) OCR0 T/C0 输出比较寄存器96$30 ($50) ASSR –––– AS0 TCN0UB OCR0UB TCR0UB 97$2F ($4F) TCCR1A COM1A1 COM1A0 COM1B1 COM1B0 COM1C1 COM1C0 WGM11WGM10 120$2E ($4E) TCCR1B ICNC1 ICES1 – WGM13 WGM12 CS12 CS11 CS10 123$2D ($4D) TCNT1H T/C1 –计数器寄存器高字节125$2C ($4C) TCNT1L T/C1 –计数器寄存器低字节125$2B ($4B) OCR1AH T/C1 –输出比较寄存器A 高字节125$2A ($4A) OCR1AL T/C1 –输出比较寄存器A 低字节125 $29 ($49) OCR1BH T/C1 –输出比较寄存器B 高字节125 $28 ($48) OCR1BL T/C1 –输出比较寄存器B 低字节125 $27 ($47) ICR1H T/C1 –输入捕捉寄存器高字节126 $26 ($46) ICR1L T/C1 –输入捕捉寄存器低字节126 $25 ($45) TCCR2 FOC2 WGM20 COM21 COM20 WGM21 CS22 CS21 CS20 142 $24 ($44) TCNT2 T/C2 (8 比特) 144 $23 ($43) OCR2 T/C2 输出比较寄存器144 $22 ($42) OCDR IDRD/OCDR7 OCDR6 OCDR5 OCDR4 OCDR3 OCDR2 OCDR1 OCDR0234 $21 ($41) WDTCR ––– WDCE WDE WDP2 WDP1 WDP0 52$20 ($40) SFIOR TSM ––– ACME PUD PSR0 PSR 321 68, 99, 131, 210 $1F ($3F) EEARH –––– EEPROM 地址寄存器高字节18$1E ($3E) EEARL EEPROM 地址寄存器低字节18$1D ($3D) EEDR EEPROM 数据寄存器18$1C ($3C) EECR –––– EERIE EEMWE EEWE EERE 19$1B ($3B) PORTA PORTA7 PORTA6 PORTA5 PORTA4 PORTA3 PORTA2 PORTA1 PORTA0 81$1A ($3A) DDRA DDA7 DDA6 DDA5 DDA4 DDA3 DDA2 DDA1 DDA0 81$19 ($39) PINA PINA7 PINA6 PINA5 PINA4 PINA3 PINA2 PINA1 PINA0 81$18 ($38) PORTB PORTB7 PORTB6 PORTB5 PORTB4 PORTB3 PORTB2 PORTB1 PORTB0 81$17 ($37) DDRB DDB7 DDB6 DDB5 DDB4 DDB3 DDB2 DDB1 DDB0 81$16 ($36) PINB PINB7 PINB6 PINB5 PINB4 PINB3 PINB2 PINB1 PINB0 81$15 ($35) PORTC PORTC7 PORTC6 PORTC5 PORTC4 PORTC3 PORTC2 PORTC1 PORTC0 81$14 ($34) DDRC DDC7 DDC6 DDC5 DDC4 DDC3 DDC2 DDC1 DDC0 81$13 ($33) PINC PINC7 PINC6 PINC5 PINC4 PINC3 PINC2 PINC1 PINC0 82$12 ($32) PORTD PORTD7 PORTD6 PORTD5 PORTD4 PORTD3 PORTD2 PORTD1 PORTD0 82$11 ($31) DDRD DDD7 DDD6 DDD5 DDD4 DDD3 DDD2 DDD1 DDD0 82$10 ($30) PIND PIND7 PIND6 PIND5 PIND4 PIND3 PIND2 PIND1 PIND0 82$0F ($2F) SPDR SPI 数据寄存器153$0E ($2E) SPSR SPIF WCOL ––––– SPI2X 153$0D ($2D) SPCR SPIE SPE DORD MSTR CPOL CPHA SPR1 SPR0 151$0C ($2C) UDR0 USART0 I/O 数据寄存器173$0B ($2B) UCSR0A RXC0 TXC0 UDRE0 FE0 DOR0 UPE0 U2X0 MPCM0 173$0A ($2A) UCSR0B RXCIE0 TXCIE0 UDRIE0 RXEN0 TXEN0 UCSZ02 RXB80 TXB80174$09 ($29) UBRR0L USART0 波特率寄存器低字节176 $08 ($28) ACSR ACD ACBG ACO ACI ACIE ACIC ACIS1 ACIS0 210 $07 ($27) ADMUX REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0 225 $06 ($26) ADCSRA ADEN ADSC ADFR ADIF ADIE ADPS2 ADPS1 ADPS0 227 $05 ($25) ADCH ADC 数据寄存器高字节228 $04 ($24) ADCL ADC 数据寄存器低字节228 $03 ($23) PORTE PORTE7 PORTE6 PORTE5 PORTE4 PORTE3 PORTE2 PORTE1 PORTE0 82 $02 ($22) DDRE DDE7 DDE6 DDE5 DDE4 DDE3 DDE2 DDE1 DDE0 82 $01 ($21) PINE PINE7 PINE6 PINE5 PINE4 PINE3 PINE2 PINE1 PINE0 82 $00 ($20) PINF PINF7 PINF6 PINF5 PINF4 PINF3 PINF2 PINF1 PINF0 83 Notes: 1. 为__________了保持与后续器件的兼容性,在访问寄存器时保留的位应写0。

ATmega128单片机概述、系统结构解析

内部晶振 晶振 JTAG接口 编程计数器 堆栈指针 晶振 时序控制

在线调试

编程Flash

边界扫描

指令寄存器

通用 寄存器 中断单元

编程逻辑

指令译码器

控制线

状态寄存器

两线接口

模 拟 比 较 器

端口E 数据寄存器

端口E方向 数据寄存器

端口B 数据寄存器

端口B方向 数据寄存器

ATmega128单片机概述 ATmega128单片机引脚功能

导航、制导与控制

7/78

2.1 ATmega128单片机概述

基于AVR低功耗CMOS 8位微控制器,近1MIPS/MHz。 6种省电模式: 空闲模式Idle:CPU 停止工作,其他子系统继续工作;

ADC 噪声抑制模式:CPU 和所有的I/O 模块停止运行, 而异步定时器和ADC 继续工作;

导航、制导与控制 18/78

二、ATmega128单片机的 系统结构

19

ATmega128单片机的系统结构 主要内容

1、ATmega128的CPU内核

2、ATmega128 存储器 3、系统时钟及其选项 4、系统控制和复位 5、ATmega128 的中断向量 6、I/O端口 7、定时器/ 计数器(T/C) 8、模数转换器 A/D

AVR 中断响应时间最少为4个时钟周期。 若中断发生时MCU 处于睡眠模式,中断响应时间增加 到8个时钟周期。 中断返回亦需4个时钟。

导航、制导与控制 27/78

1.6.2 ATmega128的中断响应时间

内容

1、ATmega128的CPU内核

2、ATmega128 存储器

Atmega128定时计数器

128有两个8位计数器T/C0和T/C2,两个16位计数器T/C1和T/C3.一.定时/计数器的工作的开始与结束是由TCCR0(8位T/C0)中的最后三位0-2工作时钟的选择决定的,工作时钟选定以后则定时器开始工作.同理.16位的是由TCCR1B中的后三位决定的.二.定时/计数器有三种工作方式:1.普通模式.2.CTC模式(比较匹配时清楚定时器).3.快速PWM模式.4.相位修正PWM模式. 其中1,2是经常用到的.在普通模式下没有什么需要特殊考虑的,用户可以随时写入新的计数器值,输出比较单元可以用来产生中断,即在普通模式下,也可对TCNT0和OCR0置数(同CTC模式).但不推荐在普通模式下利用输出比较产生波形,因为会占用太多的CPU时间.三.对于16位计数器中的16位寄存器的读写操作顺序是不同的.在写的时候,是先写高字节,再写低字节.而在读的时候则反过来,先读低字节,再读高字节.四.16位计数器的输入捕获功能.可以用于周期和频率的精确测量.eg:记下某一管脚两次变化的时间.viod init_timer1_icp(viod){TCCR1B|=(1<<CS11)|(1<<CS10);//设置预分频为64,同时启动计数器TIFR |=(1<<ICF1);//清除该标志位(清|除没有执行的中断)TIMSK |=1<<TICIE1;//允许计数器1的输入捕捉中断DDRD &=~(1<<PD6);//设置PD6为需要捕捉的输入}每当捕捉到引脚的变化后,则ICF1置位,产生中断.同时将计数寄存器TCNT1中的数值存放到ICR1中.五.定时器的CTC工作模式可以用来对定时器进行连续定时.例如 T1,CTC模式,8MHz定时时间 T= 0.125uS*N*(1+TOP) 其中N为分频系数,1,8,64,128...分频系数定时步距最长定时时间1(无分频) 0.125uS 8192us 8毫秒8 1uS 65536us 65毫秒64 8uS 524ms 0.5秒256 32uS 2097ms 3秒1024 128uS 8388ms 超8秒了根据要定时的时间比较上表中的最长定时时间选择分频系数,然后根据公示TOP=8*1000000/N-1 可计算出TOP值,即为要设定的OCR值. 注意,定时器与程序是独立的,与该定时器的中断程序也是独立的,中断程序执行时,定时器也一直在工作.所以要设定的OCR的值很小的话,那么中断返回后的 TCNT的值有可能比OCR的值大,这样则丢失一次匹配成功的条件,这样计数器会一直累加到最大值0xFF,然后再次到OCR的值时才产生中断.六. 定时器应用初始化总结最简单的用法:eg 工作在普通模式viod timer0_init(viod){TCCR0=0x00; //关闭计数器TIFR|= 1<<OCF0; //清除该标志位(清|除没有执行的中断)TIMSK |=1<<OCIE0; //允许计数器的比较匹配中断 TCNT0= ;//设置计数初值OCR0= ;//设置比较匹配值TCCR0= ; 设置工作模式,预分频,计数器开始计数}。

ATmega128 ATmega128L 介绍

ATmega128 ATmega128L 介绍

ATmega128 ATmega128L 介绍

ATmega128/128L 带 128K 字节 FLASH 的在线可编程 8 位微控制 器 是 AVR 系列中功能最强的单片机,掌握了 ATmega128 的开发应用, 对其它 AVR 单片机的开发应用等于杀鸡用牛刀,快极了 1 特 点

B 口是一个8 位双向I/O口 每一个引脚都有内部可选上拉电阻 B 口的输出缓冲有对称的驱动特 性 包括吸收和输出电流 当作为输入时 如果外部被拉低 由于上拉电阻的存在引脚将输出电流 在 复位过程中 B 口为三态 即使此时时钟还未起振 B 口还可以用做多种特殊用途 请参阅手册 Port C (PC7..PC0)

通过编程 M103C 熔丝 ATmega128 将在上述RAM I/O引脚和中断向量等方面与ATmega103 兼 容 然而 在这一兼容模式下一些 ATmega128 所拥有的新特性就没有了 • 仅有异步模式的一个 USART 而不是两个 波特率寄存器只有低八位有效 • 一个带两个比较寄存器的16位定时/计数器 而不是两个带三个比较寄存器的16位定时/计数器 • 不支持两线串行接口 • C 口只能作为输出 • G 口只有替换功能(而不是通用 I/O 口) • F 口只能作为数字输入和ADC的模拟输入 • 不支持Boot 装载功能 • 不能调整内部RC振荡器的频率 • 外部存储器接口不能释放任何地址引脚作为通用 I/O 也不能为不同的外部存储器地址区设置不同的 等待状态 另外 还有一些与ATmega103的细小差别 • MCUCSR 中只有 EXTRF 和 PORF • 看门狗超时改变不要求时序 • 外部中断脚 3 - 0 只能作为低电平中断 • USART 没有 FIFO 缓冲 所以数据溢出更早 ATmega103 中未用到的 I/O 位应置 0 以确保在 ATmega128 中的相同操作

AVR单片机ATmega128芯片BootLoader详细介绍

TIFR = TIFR|0x02;

}

}

//每秒向 PC 机发送一个控制字符"C",等待控制字〈soh〉

while(uart_getchar()!=XMODEM_SOH) //receive the start of Xmodem

{

if(TIFR & 0x02)

//timer0 over flow

{

Target: Mega128

Crystal: 16Mhz

Used: T/C0,USART0

*****************************************************/

#include #define SPM_PAGESIZE 256

//M128的一个 Flash 页为256字节(128字)

void quit(void)

{

uart_putchar('O');uart_putchar('K');

uart_putchar(0x0d);uart_putchar(0x0a);

while(!(UCSR0A & 0x20));

//等待结束提示信息回送完成

MCUCR = 0x01;

MCUCR = 0x00;

区本身。引导加载程序还可以对自身进行更新修改,甚至可以将自身删除,使系统的自编程能力消失。引导加载程序区的大小

可以由芯片的熔丝位设置,该段程序区还提供两组锁定位,以便用户选择对该段程序区的不同级别的保护。本节将给出一个实

际的的 Boot Loader 程序,它可以配合 Windows 中的超级终端程序,采用 Xmodem 传输协议,通过 RS232接口下载更新

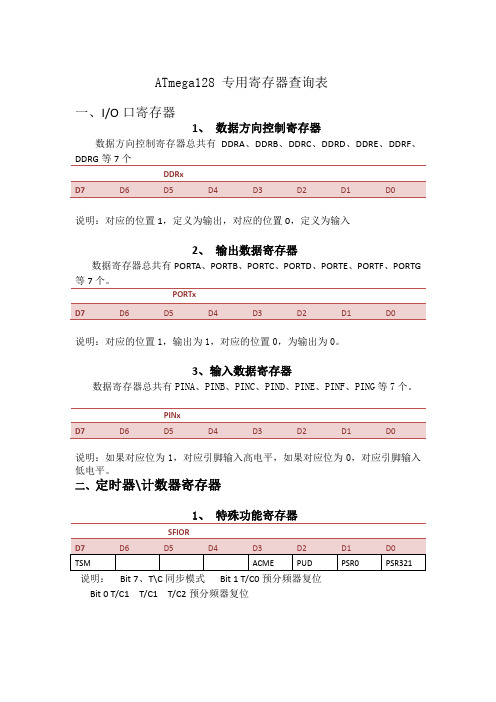

ATmega128 专用寄存器查询表

ATmega128 专用寄存器查询表一、I/O口寄存器1、数据方向控制寄存器数据方向控制寄存器总共有DDRA、DDRB、DDRC、DDRD、DDRE、DDRF、DDRG等7个D DRxD7 D6D5D4D3D2D1D0说明:对应的位置1,定义为输出,对应的位置0,定义为输入2、输出数据寄存器数据寄存器总共有PORTA、PORTB、PORTC、PORTD、PORTE、PORTF、PORTG 等7个。

PORTxD7 D6D5D4D3D2D1D0说明:对应的位置1,输出为1,对应的位置0,为输出为0。

3、输入数据寄存器数据寄存器总共有PINA、PINB、PINC、PIND、PINE、PINF、PING等7个。

PINxD7 D6D5D4D3D2D1D0说明:如果对应位为1,对应引脚输入高电平,如果对应位为0,对应引脚输入低电平。

二、定时器\计数器寄存器1、特殊功能寄存器SFIORD7 D6D5D4D3D2D1D0TSM ACME PUD PSR0 PSR321 说明:Bit 7、T\C同步模式Bit 1 T/C0预分频器复位Bit 0 T/C1 T/C1 T/C2预分频器复位2、T/C0控制寄存器TCCR0D7 D6D5D4D3D2D1D0FOC0 WGM00 COM01 COM00 WGM01 CS02 CS01 CS00说明:Bit 7 FOCO 为强制输出,Bit6、Bit3工作模式T/C0工作模式:模式WGM01 WGM00 工作模式TOP OCR0更新时刻TOV0置位时刻0 0 0 普通0XFF MAX1 0 1 PWM,修正0XFF TOP BOTTOM2 1 0 CTC OCR0 MAX3 1 1 快速PWM 0XFF TOP MAXBit 5, Bit4 比较输出模式非PWM输出模式COM01 COM00 说明0 0 正常端口0 1 比较匹配时取反1 0 比较匹配时清01 1 比较匹配时置位快速PWM模式时COM01 COM00 说明0 0 正常端口0 1 保留1 0 比较匹配时清0,达到TOP时置位1 1 比较匹配时置位,达到TOP时清0相位修正PWM模式时COM01 COM00 说明0 0 正常端口0 1 保留1 0 升序匹配时清0,降序匹配时清01 1 升序匹配时置位,降序匹配时置位Bit 2 、Bit 1 、Bit0 时钟选择CS02 CS01 CS00 说明0 0 0 无时钟,不工作0 0 1 无分频0 1 0 1/8分频0 1 1 1/321 0 0 1/641 0 1 1/1281 1 0 1/2561 1 1 1/1024T/C0的计数寄存器TCNT07 6543210输出比较寄存器OCR07 6543210T/C中断屏蔽寄存器TIMSK7 6543210OCIE0 TOIE0 Bit 1输出比较匹配使能Bit 0 T/C0 溢出使能T/C中断标志寄存器TIFR7 6543210OCF0 TOV0 Bit 1输出比较匹配标志Bit 0 T/C0 溢出标志2、定时/计数器2(大多定时/计数器1大多一样,注意区分)定时/计数器2控制器寄存器TCCR27 6543210FOC2 WGM20 COM21 COM20 WGM21 CS22 CS21 CS020 说明:Bit 7 强制输出比较Bit6、Bit3波形产生模式Bit 5, Bit4 比较输出模式Bit 2 、Bit 1 、Bit0 时钟选择CS22 CS21 CS20 说明0 0 0 无时钟,不工作0 0 1 无分频0 1 0 1/8分频0 1 1 1/641 0 0 1/2561 0 1 1/10241 1 0 从T2引脚外部时钟源。

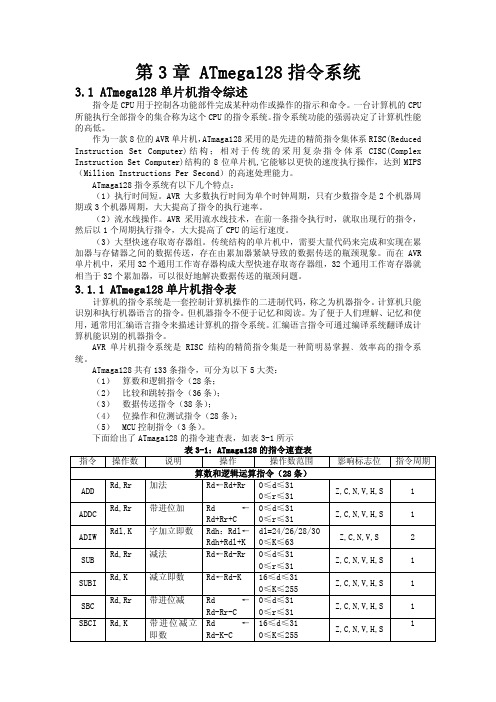

ATmega128指令系统

(1)执行时间短。AVR 大多数执行时间为单个时钟周期,只有少数指令是 2 个机器周

期或 3 个机器周期,大大提高了指令的执行速率。

(2)流水线操作。AVR 采用流水线技术,在前一条指令执行时,就取出现行的指令, 然后以 1 个周期执行指令,大大提高了 CPU 的运行速度。

(3)大型快速存取寄存器组。传统结构的单片机中,需要大量代码来完成和实现在累

SBRS Rr,b

SBIC P,b

SBIS P,b

BRBS s,k BRBC s,k BREQ k BRNE k BRCS k BRCC k BRSH k BRLO k

相对调用子 程序

间接调用子 程序

直接调用子 程序

子程序返回

中断返回

比较相等跳 行

比较

带进位比较

与立即数比 较 寄存器为 0 跳行

寄存器为 1 跳行

识别和执行机器语言的指令。但机器指令不便于记忆和阅读。为了便于人们理解、记忆和使 用,通常用汇编语言指令来描述计算机的指令系统。汇编语言指令可通过编译系统翻译成计

算机能识别的机器指令。

AVR 单片机指令系统是 RISC 结构的精简指令集是一种简明易掌握﹑效率高的指令系

统。

ATmaga128 共有 133 条指令,可分为以下 5 大类: (1) 算数和逻辑指令(28 条;

0≤d≤31 0≤q≤63

2

LD Rd,Z Z 间址取数 Rd←(Z)

0≤d≤31

2

LD Rd,Z+ Z 间 址 取 数 Rd←(Z)

后加 1

Z←Z+1

0≤d≤31

2

LD Rd,-Z Z 减 1 后间址 Z←Z-1

取数

Rd←(Y)

Atmega128定时计数器

Atmega128定时计数器128有两个8位计数器T/C0和T/C2,两个16位计数器T/C1和T/C3.一.定时/计数器的工作的开始与结束是由TCCR0(8位T/C0)中的最后三位0-2工作时钟的选择决定的,工作时钟选定以后则定时器开始工作.同理.16位的是由TCCR1B中的后三位决定的.二.定时/计数器有三种工作方式:1.普通模式.2.CTC模式(比较匹配时清楚定时器).3.快速PWM模式.4.相位修正PWM模式. 其中1,2是经常用到的.在普通模式下没有什么需要特殊考虑的,用户可以随时写入新的计数器值,输出比较单元可以用来产生中断,即在普通模式下,也可对TCNT0和OCR0置数(同CTC模式).但不推荐在普通模式下利用输出比较产生波形,因为会占用太多的CPU时间.三.对于16位计数器中的16位寄存器的读写操作顺序是不同的.在写的时候,是先写高字节,再写低字节.而在读的时候则反过来,先读低字节,再读高字节.四.16位计数器的输入捕获功能.可以用于周期和频率的精确测量.eg:记下某一管脚两次变化的时间.viod init_timer1_icp(viod){TCCR1B|=(1<<cs11)|(1<<="">TIFR |=(1<<="">TIMSK |=1<<="">DDRD &=~(1<<="">}每当捕捉到引脚的变化后,则ICF1置位,产生中断.同时将计数寄存器TCNT1中的数值存放到ICR1中.五.定时器的CTC工作模式可以用来对定时器进行连续定时.例如 T1,CTC模式,8MHz定时时间T= 0.125uS*N*(1+TOP) 其中N为分频系数,1,8,64,128...分频系数定时步距最长定时时间1(无分频) 0.125uS 8192us 8毫秒8 1uS 65536us 65毫秒64 8uS 524ms 0.5秒256 32uS 2097ms 3秒1024 128uS 8388ms 超8秒了根据要定时的时间比较上表中的最长定时时间选择分频系数,然后根据公示TOP=8*1000000/N-1 可计算出TOP值,即为要设定的OCR 值. 注意,定时器与程序是独立的,与该定时器的中断程序也是独立的,中断程序执行时,定时器也一直在工作.所以要设定的OCR的值很小的话,那么中断返回后的 TCNT的值有可能比OCR的值大,这样则丢失一次匹配成功的条件,这样计数器会一直累加到最大值0xFF,然后再次到OCR 的值时才产生中断.六. 定时器应用初始化总结最简单的用法:eg 工作在普通模式viod timer0_init(viod){TCCR0=0x00; //关闭计数器TIFR|= 1<<="">TIMSK |=1<OCR0= ;//设置比较匹配值TCCR0= ; 设置工作模式,预分频,计数器开始计数}</cs11)|(1<。

Atmega128简介

Atmega128简介Atmega128⽬录主要特性如下:1. · ⾼性能、低功耗的 AVR 8 位微处理器2. · 先进的 RISC 结构3. · ⾮易失性的程序和数据存储器4. · JTAG 接⼝( 与IEEE 1149.1 标准兼容)· 外设特点· 特殊的处理器特点· I/O 和封装1. · 速度等级下⾯对ATmega128的型号标识进⾏解析: ATmega128 是ATMEL公司的 8位系列单⽚机的最⾼配置的⼀款单⽚机,应⽤极其⼴泛主要特性如下:· ⾼性能、低功耗的 AVR 8 位微处理器· 先进的 RISC 结构 – 133 条指令 – ⼤多数可以在⼀个时钟周期内完成 – 32 x 8 通⽤⼯作寄存器 + 外设控制寄存器 – 全静态⼯作 – ⼯作于16 MHz 时性能⾼达16 MIPS – 只需两个时钟周期的硬件乘法器· ⾮易失性的程序和数据存储器 – 128K 字节的系统内可编程Flash 寿命: 10,000 次写/ 擦除周期 – 具有独⽴锁定位、可选择的启动代码区 通过⽚内的启动程序实现系统内编程 真正的读- 修改- 写操作 – 4K字节的EEPROM 寿命: 100,000 次写/ 擦除周期 – 4K 字节的内部SRAM – 多达64K 字节的优化的外部存储器空间 – 可以对锁定位进⾏编程以实现软件加密 – 可以通过SPI 实现系统内编程· JTAG 接⼝( 与IEEE 1149.1 标准兼容) – 遵循JTAG 标准的边界扫描功能 – ⽀持扩展的⽚内调试 – 通过JTAG 接⼝实现对Flash, EEPROM, 熔丝位和锁定位的编程· 外设特点 – 两个具有独⽴的预分频器和⽐较器功能的8 位定时器/ 计数器 – 两个具有预分频器、⽐较功能和捕捉功能的16 位定时器/ 计数器 – 具有独⽴预分频器的实时时钟计数器 – 两路8 位PWM – 6路分辨率可编程(2 到16 位)的PWM – 输出⽐较调制器 – 8路10 位ADC 8 个单端通道 7 个差分通道 2 个具有可编程增益(1x, 10x, 或200x)的差分通道 – ⾯向字节的两线接⼝ – 两个可编程的串⾏USART – 可⼯作于主机/ 从机模式的SPI 串⾏接⼝ – 具有独⽴⽚内振荡器的可编程看门狗定时器 – ⽚内模拟⽐较器· 特殊的处理器特点 – 上电复位以及可编程的掉电检测 – ⽚内经过标定的RC 振荡器 – ⽚内/ ⽚外中断源 – 6种睡眠模式: 空闲模式、ADC 噪声抑制模式、省电模式、掉电模式、Standby 模式以及 扩展的Standby 模式 – 可以通过软件进⾏选择的时钟频率 – 通过熔丝位可以选择ATmega103 兼容模式 – 全局上拉禁⽌功能· I/O 和封装 – 53个可编程I/O ⼝线 – 64引脚TQFP 与 64 引脚 MLF 封装 · ⼯作电压 – 2.7 - 5.5V ATmega128L – 4.5 - 5.5V ATmega128· 速度等级 – 0 - 8 MHz ATmega128L – 0 - 16 MHz ATmega128 ATmega128 TQFP封装现主要有这些型号:ATmega128-16AU、ATmega128-16AI。

atmega128单片机pwm学习总结

ATMEGA128 PWM输出系列例程1、定时器0,快速PWM模式快速PWM可以的到比较高频率的PWM输出,但占空比的调节精度稍微差一些。

此时计数器仅工作在单程正向计数方式,计数器的上限值决定PWM的频率,而比较匹配寄存器的值决定了占空比的大小。

PWM 频率的计算公式为:))PWM频率= 系统时钟频率/(分频系数*(1+计数器上限值计数器上限值))快速PWM模式适合要求输出PWM频率较高,但频率固定,占空比调节精度要求不高的应用。

/*定时器0,快速PWM模式,由OC0输出PWM波 *//*PWM频率= 系统时钟频率/(分频系数*(1+计数器上限值))*//*本程序中:频率=8000000/(8*(1+255))=3.91KHZ,频率固定 *//*占空比为:OCR0/0XFF=OCR0/256,占空比可调 *//*TCNT0从BOTTOM计数到MAX,然后回到BOTTOM重新开始;TCNT0计数到与OCR0相等时,OC0清零,在BOTTOM时置位1 */#include <iom128v.h>#include<macros.h>#define uint unsigned int#define uchar unsigned charvolatile uchar num;void pwm0_init(void){DDRB=0X10; //将PB4设置为输出TCCR0=0X00; //关闭num=64; //设置输出比较寄存器的初值TCNT0=0; //计数器初值为0TCCR0=0X6A; //设置为快速pwm模式,采取8分频}/*键盘初始化*/void init_key(){DDRD=0X00;PORTD=0XFF;}/*延时函数 */void delay_ms(uint z){uint x,y;for(x=z;x>0;x--)for(y=1140;y>0;y--);}/*键盘扫描 */void keyscan(void ){if((PIND&0x01)==0){while(!(PIND&0x01)); //松手检测delay_ms(50);num+=5;if(num==255)num=0;}if((PIND&0x02)==0){while(!(PIND&0x02));delay_ms(50);num-=5;if(num==0)num=255;}if((PIND&0x08)==0){while(!(PIND&0x01));delay_ms(50);num=128;}}void main(void){uchar wide;pwm0_init();init_key();while(1){OCR0=num;keyscan();}}相位修正((调整调整))模式2、定时器0,相位修正频率(相位)调整PWM模式的占空比调节精度高,但输出频率比较低,因为此时计数器仅工作在双向计数方式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、流水灯/*硬件环境:atmega128开发板软件环境:CodeVisionAVR-C*/#include <mega128.h>#define uchar unsigned char#define uint unsigned intuchar cnt;void timer1_init(){TCCR1B=0X00; //先停止定时器1TCNT1H=0XF0; //设定定时器初值TCNT1L=0XBE;TCCR1A=0X00; //启动定时器1TCCR1B=0X05; //使用1024分频}interrupt [TIM1_OVF] void timer1_ovf_isr(void){TCNT1H=0XF0; //重载定时器初值TCNT1L=0XBE;DDRE|=1<<2;PORTE|=1<<2;DDRA=0xff;PORTA=cnt; //输出led的值到端口Bcnt++;if(cnt==255)cnt=0;}void main(){//DDRB=0XFF;SREG|=0X80;TIMSK=0X04;timer1_init();while(1){;}}2、AD转换+数码管显示/*********************************************************************** ****//*ADC测试程序*//*目标器件:ATmega128 *//*晶振:RC 8MHZ *//*编译环境:ICCAVR 7.13A *//*E-Mail:number007cool@ *//*时间:2010年11月13日*///Aref接AVCC(+5V),采用Aref作参考电压/*用数码管显示AD转换的结果*//*********************************************************************** ****//*********************************包含头文件********************************/#include <iom128v.h>#include <macros.h>/********************************数码管段码表*******************************/extern const unsigned char tab[]={0x3f,0x06,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F};/*********************************全局变量**********************************/unsigned int adc_rel=0;/*********************************************************************** *****函数功能:ADC初始化函数入口参数:出口参数:************************************************************************ ****/void adc_init(void){DDRF&=0XFE; //PORTF0设置为输入,即作为ADC0口输入模拟电压PORTF&=0XFE; //PORTF0设置为输入低电平ADCSRA=0x00; //关ADCADMUX = 0X00; //采用Aref作为参考电压,ADC0单端输入,右对齐ACSR=(1<<ACD);ADCSRA = (1<<ADEN)|(1<<ADSC)|(1<<ADATE)|(1<<ADIE)|(1<<ADPS2)|(1<<ADPS1); //ADEN,启动ADC;ADSC,ADC开始转换;ADIE,ADC中断使能;ADPSx,设置分频因子64}/*********************************************************************** *****函数功能:ADC中断函数入口参数:出口参数:****************************************************************************/#pragma interrupt_handler adc_isr:iv_ADCvoid adc_isr(void){//int data_h,data_l;//data_l=ADCL;//data_h=ADCH;ADCSRA = 0x00;ADCSRA = (1<<ADEN)|(1<<ADSC)|(1<<ADIE);adc_rel=ADC;/*if(adc_rel>0x1ff){PORTA|=1<<2;}elsePORTA&=~(1<<2);*/}/*********************************************************************** *****函数功能:延时子程序入口参数:出口参数:************************************************************************ ****/void delay(void){int i;for(i=0;i<1800;i++);}/*********************************************************************** *****函数功能:显示子程序入口参数:k出口参数:************************************************************************ ****/void display(unsigned int k)//发光二极管显示初始化{DDRE|=1<<2;PORTE|=1<<2;DDRA=0XFF;PORTA=k;}#define SS 0#define SCK 1#define MOSI 2#define MISO 3#define SS_H() PORTB|=(1<<SS)#define SS_L() PORTB&=~(1<<SS)#define led0_en() {DDRB|=1<<4;PORTB|=(1<<4);} //开第一个数码管的位选#define led0_dis() {DDRB|=1<<4;PORTB&=~(1<<4);} //关第一个数码管的位选#define led1_en() {DDRB|=1<<5;PORTB|=(1<<5);}#define led1_dis() {DDRB|=1<<5;PORTB&=~(1<<5);}#define led2_en() {DDRB|=1<<6;PORTB|=(1<<6);}#define led2_dis() {DDRB|=1<<6;PORTB&=~(1<<6);}#define led3_en() {DDRB|=1<<7;PORTB|=(1<<7);}#define led3_dis() {DDRB|=1<<7;PORTB&=~(1<<7);}#define OE 7#define point 3#define dp 7#include <iom128v.h>#include <macros.h>const unsigned char table[]={0x3F,0x06,0x5B,0x4F,0x66, //0,1,2,3,40x6D,0x7D,0x07,0x7F,0x6F, //5,6,7,8,9 0x77,0x7C,0x39,0x5E,0x79,0x71,0x00}; //a,b,c,d,e,f volatile unsigned char led_buffer[4];void delay_1us(void) //1us延时函数{asm("nop");}void delay_nus(unsigned int n) //N us延时函数{unsigned int i=0;for (i=0;i<n;i++)delay_1us();}void delay_1ms(void) //1ms延时函数{unsigned int i;for (i=0;i<1140;i++);}void delay_nms(unsigned int n) //N ms延时函数{unsigned int i=0;for (i=0;i<n;i++)delay_1ms();}/*完成spi的初始化*/void spi_init(void){DDRB |= (1<<MOSI)|(1<<SCK)|(1<<SS);//设置MOSI,SCK输出SPCR = (1<<SPE)|(1<<MSTR)|(1<<SPR0)|(1<<SPR1);//使能SPI,主机模式}/*spi主机传送数据*/void SPI_MasterTransmit(char Data){/* 启动数据传输*/SPDR = Data;/* 等待传输结束*/while(!(SPSR & (1<<SPIF)));}/*完成对HC595的初始化*/void HC_595_init(void){DDRC |= (1<<OE); //设置PORTC7为输出PORTC &= (1<<OE); //输出高电平,使能595PORTB = 0x0F; //同时打开四个数码管的位选spi_init();led_buffer[0]=16; //初始化数码管段码led_buffer[1]=16;led_buffer[2]=16;led_buffer[3]=16;}/*HC595完成传送数据*/void HC_595_OUT(unsigned char data){SS_L();SPI_MasterTransmit(data);SS_H();}void leddis_update(void){/*最低位数码管,第四个数码管*/if(point==0)HC_595_OUT(table[led_buffer[3]]|(1<<dp));elseHC_595_OUT(table[led_buffer[3]]);led0_en();delay_nus(60);led0_dis();if(point==1)HC_595_OUT(table[led_buffer[2]]|(1<<dp));elseHC_595_OUT(table[led_buffer[2]]);led1_en();delay_nus(60);led1_dis();if(point==2)HC_595_OUT(table[led_buffer[1]]|(1<<dp));elseHC_595_OUT(table[led_buffer[1]]);led2_en();delay_nus(60);led2_dis();/*最高位数码管,第一个数码管*/if(point==3)HC_595_OUT(table[led_buffer[0]]|(1<<dp));elseHC_595_OUT(table[led_buffer[0]]);led3_en();delay_nus(60);led3_dis();}void display_led(unsigned int data){if(data>9999){HC_595_OUT(0xFF);//当计数大于9999时,四个数码管同时输出8PORTB|=((1<<4)|(1<<5)|(1<<6)|(1<<7));}else if(data>999){led_buffer[0]=data/1000;led_buffer[1]=(data%1000)/100;led_buffer[2]=(data%100)/10;led_buffer[3]=data%10;leddis_update();}else if(data>99){led_buffer[0]=data/1000; //关闭最高位的那个数码管led_buffer[1]=(data%1000)/100;led_buffer[2]=(data%100)/10;led_buffer[3]=data%10;leddis_update();}else if(data>9){led_buffer[0]=data/1000;led_buffer[1]=16;led_buffer[2]=(data%100)/10;led_buffer[3]=data%10;leddis_update();}else{led_buffer[0]=data/1000;led_buffer[1]=16;led_buffer[2]=16;led_buffer[3]=data%10;leddis_update();}}volatile unsigned int countnum=0;void timer1_init(void){TCCR1B = 0x00; //stopTCNT1H = 0x8F; //setupTCNT1L = 0x81;OCR1AH = 0x70;OCR1AL = 0x7F;OCR1BH = 0x70;OCR1BL = 0x7F;OCR1CH = 0x70;OCR1CL = 0x7F;ICR1H = 0x70;ICR1L = 0x7F;TCCR1A = 0x00;TCCR1B = 0x04; //start Timer}#pragma interrupt_handler timer1_ovf_isr:15void timer1_ovf_isr(void){TCNT1H = 0x8F; //reload counter high valueTCNT1L = 0x81; //reload counter low valuecountnum++;if(countnum>9999) countnum=0;}void init_devices(void){CLI(); //disable all interruptstimer1_init();TIMSK = 0x04; //timer interrupt sourcesSEI(); //re-enable interrupts}/*********************************************************************** *****函数功能:主程序入口参数:出口参数:************************************************************************ ****/void main(void){init_devices();HC_595_init();adc_init();SEI();//开全局中断变量display(0);while(1)delay();display_led(adc_rel/1024.0*5*1000);}}3、对EEPROM进行读写操作/************************************************文件:main.c用途:注意:内部8M晶振************************************************/#include "config.h"/*向EEPROM里面写入数据输入量:地址,数据*/void EEPROM_write(unsigned int uiAddress,unsigned char ucData) {while(EECR&(1<<EEWE)); //等待上一次写操作结束EEAR = uiAddress; //地址EEDR = ucData; //数据EECR |=(1<<EEMWE); //置位EEMWE,主机写使能EECR |=(1<<EEWE); //置位EEWE,写使能,启动写操作}/*从EEPROM指定的地址里面读出相应的数据*/unsigned char EEPROM_read(unsigned int uiAddress){while(EECR&(1<<EEWE)); //等待上一次写操作结束EEAR = uiAddress; //设置地址寄存器EECR |=(1<<EERE); //读使能return EEDR; //返回读入EEDR里面的数据}void main(void){unsigned char temp=123;unsigned char data;HC_595_init();EEPROM_write(0x01,temp);data=EEPROM_read(0x01);while(1){Seg7_Led_display(data); //调用显示函数将写入的数据又读出来}4、定时器0(轮循方式)/*定时器0和2(均为八位的定时计数器)有四种工作模式,此例是工作在普通模式。