基于FPGA的SATAIPCORE设计

基于FPGA的SATA硬盘加解密控制器设计

基于FPGA的SATA硬盘加解密控制器设计刘文国李广军林水生(电子科技大学通信与信息工程学院成都 610051)【摘要】:随着信息时代的到来,数据存储和保护的需求与日俱增,如何有效实现对硬盘数据的加密保护成为一个重要的课题。

本文首先分析了目前常用的硬盘数据加密方法,并在比较各种加密方案的基础上给出了基于FPGA的SATA硬盘加解密控制器设计方案。

基于SATA2.0接口的广泛应用性,本文接着介绍了SATA的体系结构,并由此给出了系统的总体设计构架和详细设计方案。

本控制器采用Synopsys 公司的SATA VIP辅助验证,Xilinx ML505开发板为测试平台,并采用Xilinx公司的Virtex-5 FPGA作为最终实现,测试表明能够实现正确有效地实现硬盘数据的加解密工作。

本文在SATA加解密控制器设计与实现方面的研究成果,具有通用性、可移植性,有一定的理论及经济价值。

关键词:SATA,加解密控制器,FPGA, Verilog HDLDesign of SATA Hard Disk Encryption/Decryption Controller Based on FPGALiu Wenguo Li Guangjun Lin Shuisheng(University of Electronic Science and Technology of China, School of Communication and InformationEngineering, Chengdu 610051)Abstract: With the advent of the information era, the need for data storage and data protection has been becoming more and more urgent, so how to protect the Hard Disk data become an important task. This paper firstly analyzes several common ways of Hard Disk data protection, and then presents the design scheme of SATA Hard Disk Encryption/Decryption Controller Based on FPGA after comparison. Because of the common use of SATA2.0 interface, this paper then introduces the system structure of SATA2.0 protocol and presents the general architecture and detailed scheme. The controller adopts SATA VIP as assistant verification , Xilinx ML505 as test platform and Virtex-5 FPGA of Xilinx as the final implementation. The test shows that it can efficiently encrypt/decrypt the Hard Disk data. The design method of this paper is of theoretic and economical value and can be applied to many purposes.Key words: SATA, Encryption/Decryption controller, FPGA, Verilog HDL1引言SATA2.0接口是传输速率达到3Gbps的串行接口,由于采用了吉比特以太网结构和8b/10b编码技术,同时还支持NCQ(本地命令队列)、端口复用器、交错启动、热插拔等功能,在硬盘领域被广泛采用。

第9章 基于FPGA的IP核设计技术

Altera能够提供给用户使用的3种IP形式: 基本宏功能(Megafunctions/LPM) Altera IP(MegaCore) Altera IP合作伙伴(AMPP)的IP

PCIMT32

PCI T32 PCI MT64 PCI64 PCI32 Nios target

DDR Memory I/F

Nios &Nios ii

SRAM interface

SDR DRAM interface

Flash interface

Virterbi

Turbo encoder/decoder

IP核默认的格式

IP核结构连接总线总线接口 逻辑逻辑或算法

Altera公司的Avalon总线

凡是用NiosII软核处理器控制的外设 都需要 符合 Avalon总线传输要求。 Altera公司所有的IP核,包括NiosII在内,支持 Avalon总线。 Avalon总线是交换式(Switch)型总线。任意一 个主设备和从设备都有一个数据通路,主设备可 以同时访问多个不同的从设备。而获得更高的数 据传输率。 SOPC Builder8.0 提供的Avalon-MM(普通模式) 和Avalon-ST(高速模式)。

(6)SPIRXBUF:SPI串行接收缓冲寄存器。

(7)SPITXBUF:SPI串行发送缓冲寄存器。

(8)SPIDAT:SPI串行数据寄存器。

(9)SPIPRI:SPI优先级控制。

SPI操作 下图是SPI用于两个控制器(一个主控制器和一个从控制器)通 信的典型连接方式。

基于fpga的多通道sata接口设计与实现

摘要摘要随着信息社会的蓬勃发展,人们对信息存储设备的存储容量、传输稳定性、数据完整性都提出了更高的要求。

固态硬盘凭借其优良的工作性能以及更快的传输速率,逐渐成为主流的高速存储介质,而且随着存储阵列技术的发展,存储系统的容量也变得越来越大。

论文设计了基于FPGA的多通道SATA接口,进而实现了由固态硬盘组成的高速大容量固态存储阵列,安全稳定,应用广泛,存储容量更大,并且具有一定的可扩展性。

论文首先设计了系统的整体结构,包括主控板卡、存储控制板、VPX背板以及固态存储阵列,主控板卡提供了系统的命令接口和数据接口,负责系统工作控制和数据分发;存储控制板基于FPGA的片上嵌入式系统,根据SATA标准协议,设计实现了多通道SATA控制器;VPX背板一方面完成存储控制板与主控板卡的板间数据传输,另一方面构成存储控制板与固态存储阵列间的SATA通路;固态存储阵列由24块480G的固态硬盘构成。

论文的主要工作如下:1、依据VPX标准设计了总线型系统架构,详细分析了系统数据传输带宽需求及VPX高速串行接口的传输能力,基于FPGA内集成的高速串行接口的高效性和稳定性,通过VPX背板实现了多路并行高速数据的板间传输。

2、以Xilinx公司的XC5VFX200T芯片为核心,对单板多通道SATA接口进行了硬件设计,包括四个主要模块,其中SATA控制模块依据SATA标准协议设计实现了多通道的SATA控制器,完成对固态盘的读写控制;数据传输模块完成与背板之间的数据交互、数据位宽转换以及数据缓存过程;时钟管理模块负责管理外部可配置时钟芯片并完成系统内部时钟网络的设计和管理;命令管理模块负责接收并执行主控板卡的命令,控制单板系统的工作流程。

3、为保证系统工作的可靠性和稳定性,结合硬件调试进行了改进性设计,通过推迟外设时钟芯片工作时间及通过应用层控制底层链路重建的措施,解决了硬盘检测的问题;通过改进控制物理链路的OOB状态机,为底层程序增加了自我校验的功能,增加了系统冗余性,结合硬件设计重新修正了主机端高速串行接口参数,进一步完善了通信链路的信号完整性。

基于FPGA的SOC和IPCore验证平台

版图级也称为物理级 是集成电路描述的最低层次 在版图级 以几何图形 描述晶体管 MOS 管 二极管 电阻 连线等元件 硬件的功能隐含于器件的

物理特性关系中 在这一层次 系统的特性不仅和器件的互连方式有关 而且与 器件的加工工艺有关

2

上海交通大学硕士学位论文

版图级以上的层次是电路级 极管和电阻电容等

KEY WORDS

SOC,IPCore,FPGA

Verification,EDA

III

上海交通大学 学位论文原创性声明

本人郑重声明:所呈交的学位论文,是本人在导师的指导下, 独立进行研究工作所取得的成果。除文中已经注明引用的内容外, 本论文不包含任何其他个人或集体已经发表或撰写过的作品成果。 对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式 标明。本人完全意识到本声明的法律结果由本人承担。

With the rapid development of semiconductor, digital integrated circuit( memory, standard logic gates, etc.) and advance computer technology,the various measuring instruments (virtual i nstruments) with the powerfulfunction of PC are produced in different industrial and scientific researchfields. As we all known, the traditional instruments are usually built with discrete components and small scale ICs, the disadvantages are obvious in system design, debugging and maintenance. With the help of newly developed advance Electronics Design Automation (EDA) technology, some roles and tens or hundreds of components of traditional instruments could bereplaced or redesigned by means of large scale programmable logic

基于FPGA的SATA+IP+CORE设计

负责所有的A1-A命令执行,包括对控制命令模块寄存 器的访问;传输层(Transaction)主要负责以帧信息结 构FIS(Frame Information Structure)的形式传输主 机和设备之间的控制命令与数据;链路层(Link)主要 负责信道编解码,包括8B/1 OB编解码与CRC校验: 物理层(Physical)主要负责串/并转换、发送和接收串 行数据流。

FALSE

2’bOl

REFCLKI

R)【PLU巾IVSEL

பைடு நூலகம்

20

RXOUTDIV2SEL

4

RXUSRDIVISOR

1

RXCI,KMODE

6’b0000l】

TXOUTCLKl USE SYNC

FALSE

TXCLRO FORCE

FALSE

P、tACLK

RX cL0cK DIVI DER

2’bOl

RXABPMACLKSEL

品垃 龆垤

,.——L Ahp^d柚

二紫.竺—卅嚣——与删肛勰黼

图3 系统通迅链接建立序列

物理层通迅链接的状态变迁如图3所示,系统由 有限状态机实现,下面详细介绍通迅链接建立时状态 变迁过程:

A:主机复位,发出COMRES盯; B:设备检测到COMRESET后以COMINIT响应, 连续发送6个传输同期。(COMINIT为重新连接开始 信号,设备可以在任意时间发送COMINIT重新建立 连接): C:主机校准,发出COMWAKE: D:设备接收到COMWAKE后,发送COMWAKE, 接着连续发送ALIGN数据流, G:主机锁存数据。检测到ALIGN后以接收的速 度转发,之前一直发送控制字D1 O.2。 H:设备锁存数据,检测到ALIGN后发送同步信 号SYNCp,通讯建立成功,进入到正常操作模式。如 在54.6us(2048个基元传输时间)内未检测到ALl GNp,则进入错误处理,等待重新连接。 2.2链接层 链接层的主要任务是信道编解码。当传输层有数 据需要传送时,链接层计算CRC值,为其加上包头 SOF(start of frame)和包尾EOF(end of frame)。经 过打包的数据通过CRC、加扰和8B/1 OB编码后,传 递给物理层,并在包的传输过程中通过插入各种

基于FPGA的SATAⅢ控制器的实现

i

● … … … …

;

l

… 一

设 备

:

图 1 S T I 枸 体 系框 图 A AH 结

准 ,A Al的传输 速 率为 S T ST I A A I的两倍 , 到 了 30 达 0

收稿 日期 : 1- - ; 2 2 32 修订 E : 1- — 0 0 2 t 2 2 41 期 0 0 9

层 窭 {

;

一 层’ 键{ 路. [ 至

主 机

…

…

:

物 面向 理 层

昂 j 奁 z

弟 j别

雷 达 与 对 抗

RADAR & ECM

Vo . 2 No 3 13 . S p . 01 e t2 2

21 0 2年 9月

基 于 FG P A的 S T 制 器 的实 现 A Am控

牛 戴 楠 , 江涛 , 李 周 仟

( 中国船舶重 工集 团公 司第 七二 四研究所 , 南京 2 00 ) 10 3

N U D i a , Ja gto, H U Q a I a— n H in — n a Z o in

( o 2 e ac ntue fC I , af g2 0 0 ) N .7 4R s rhIs tt o SC N n n 10 3 e i i

Ab ta t h i lme tt n f h F G b sd AT Ⅲ p ooo i ic se i d ti sr c :T e mpe nai o te P A—a e S A o rtc l s su s d n eal d

基于FPGA的SATA控制器20150420

本人在XILINX公司FPGA(Virtex的FX系列XC5VFX70T/XC5VFX100T/XC5VFX200T,Spartan6的LX系列XC6SLX45T, Virtex6的LX系列XC6SLX75T,XC6VLX130T,XC6VLX240T)中开发了一个SATAII host控制器,SATA协议的应用层由嵌入式处理器PPC440来实现,主要完成硬盘的参数配置和读写操作命令。

SATA协议的传输层和链路层是通过硬件描述语言设计在FPGA中生产相应的电路来实现,这两层主要是完成帧的封装,帧的发送、暂停、结束控制,帧的解析和校验。

SATA协议的物理层由千兆位级收发器GTX、OOB控制模块和接口传输率选择模块共同实现。

千兆位级收发器GTX的主要功能包括8B/10B编码/解码,串并/并串转换,逗点检测,时钟修正,预侧重和线性均衡等。

OOB控制模块完成硬盘的上电过程或硬件复位过程,并同SATA控制器建立通信链接。

用户接口由两部分组成:PLB接口和NPI接口(相当于FIFO接口)。

PLB接口实现嵌入式处理器POWERPC和SATA控制器之间控制信息和状态信息的交换,具体的是通过在SATA控制器中的32个32比特的寄存器实现的。

PLB接口用于小量数据的传输。

FIFO接口用于实现内存和SATA控制器之间数据的交换。

NPI接口(NPI接口是与多端口存储器控制器模块连接的接口)来实现片外存储芯片DDR2和SATA控制器之间数据的交换,主要用于大量数据的传输。

基于SATA控制器的典型应用如图1所示,基于FPGA的SATA控制器可以在一片FPGA中实现典型的存储系统,相机数据或AD采样数据等先经过DDR2缓存然后由SATA控制器直接写入固态硬盘中。

SATA控制器采用分层和模块化的设计方法,在FPGA中应用SATA控制器读写硬盘一般情况下需要3个模块:NPI控制器,SATA控制器和MGT_wrapper。

NPI控制器(Npi_ctrl)实现NPI接口的读写控制(NPI接口是xilinx提供的多端口存储器控制器IP的一种接口,端口存储器控制器即Multi-Port Memory Controller,简称MPMC),NPI控制器是SATA 控制器和内存之间的桥梁,该模块负责将内存的数据传给SATA控制器或者将SATA控制器的数据写入内存。

(基于FPGA的现代数字系统设计)第4章基于IPCore的设计

第4章 基于IP Core的设计

3. 软核(Soft Core) 软核是以可综合的寄存器传输级(RTL)描述或通用库元件的 网表形式提供的可重用的IP模块,这意味着软核的使用者要负责 实际的实现和布图软核,它的优势是对工艺技术的适应性很强, 应用新的加工工艺或改变芯片加工厂家的时候很少需要对软核进 行改动,原来设计好的芯片可以方便地移植到新的工艺中。由于 软核设计以高层次表示,因而软IP Core易于重定目标和重配置, 然而预测软IP Core的时序、面积与功率诸方面的性能较困难。 从完成IP Core设计所花费的代价来讲,硬件宏单元代价最高, 从IP Core的使用灵活性来讲,软件宏单元的可重复使用性最高。 一个IP Core的价值不单与模块本身的用途和设计复杂性有关,而 且与其可重复使用性程度和设计完成的程度有关。将IP Core完成 至物理设计,其设计复杂性增加了,但是其可重复使用性却降低 了。

第4章 基于IP Core的设计

通用IP模块由于开发技术相对比较简单,面临的竞争也 比较激烈。通用IP模块的价值依赖于IP Core的技术含量、IP Core的品质和供应商的信誉,基于较新工艺的通用IP Core 或包含有专利内容的通用IP Core将有较好的发展前景。对 技术要求较高的IP Core,如高速接口、高速锁相环等模块, 也将有较强的生命力。 存储器IP Core与其它IP Core稍有不同。通常存储器的 设计严重依赖于芯片的加工工艺,同时存储器是SOC芯片上 最重要的部件,大多数SOC芯片上的存储器会占整个芯片面 积的70%,甚至更多,而且芯片的性能将主要由存储器的存 取时间决定。存储器IP Core通常由芯片加工厂家提供,而 且都以硬IP Core的方式提供,部分厂家还依据特殊工艺提 供DRAM IP Core。

SATA硬盘控制器的FPGA实现

SATA硬盘控制器的FPGA实现贾效玲;张刚;张博【摘要】The paper designs a high-performance SATA controller IP core. It takes SATA 2.5 protocol for reference and is implemented on the basis of FPGA of Virtex-5 family of Xilinx with modular design concept in VHDL language. A platform for IP core performance verification is built. The test results indicate that the controller IP can realize many operations,such as reading,writing, device reset,identification and so on. And it has good stability. Meanwhile,it also finishes the operating system drivers of PetaLinux. It can facilitate the application of embedded systems.%设计一款高性能的SATA硬盘控制器IP核。

基于Xilinx公司的Virtex-5系列FPGA,参考SATA2.5协议,运用VHDL硬件描述语言,采用模块化的设计理念,完成IP核的设计。

搭建了验证平台,对IP核的性能进行了测试,经测试该控制器IP核能正确地完成读、写、设备复位、设备识别等操作,且稳定性良好。

同时编写了PetaLinux操作系统下的驱动程序,便于嵌入式系统的应用。

【期刊名称】《火力与指挥控制》【年(卷),期】2016(041)009【总页数】4页(P182-184,188)【关键词】SATA2.5;控制器;FPGA;VHDL【作者】贾效玲;张刚;张博【作者单位】太原理工大学信息工程学院,太原 030024;太原理工大学信息工程学院,太原 030024;太原理工大学信息工程学院,太原 030024【正文语种】中文【中图分类】TP333.2随着嵌入式技术的发展,嵌入式系统对存储器容量的要求越来越高,特别是图像采集、视屏监控等系统。

基于FPGA的SATA控制器介绍v1

作者邮箱:***************,欢迎交流探讨。

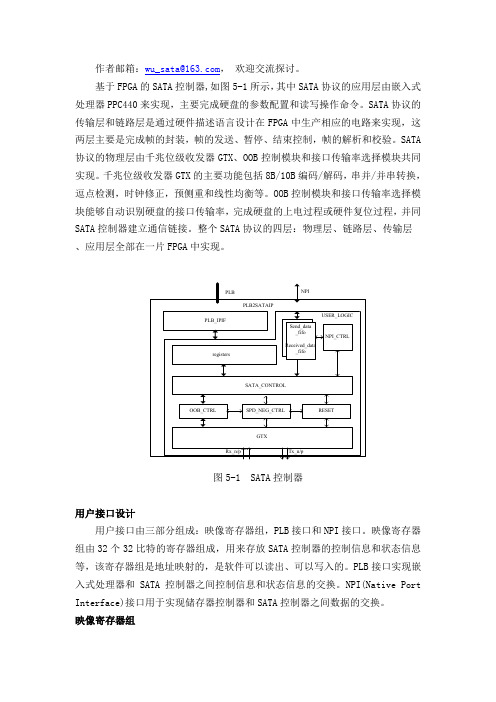

基于FPGA的SATA控制器,如图5-1所示,其中SATA协议的应用层由嵌入式处理器PPC440来实现,主要完成硬盘的参数配置和读写操作命令。

SATA协议的传输层和链路层是通过硬件描述语言设计在FPGA中生产相应的电路来实现,这两层主要是完成帧的封装,帧的发送、暂停、结束控制,帧的解析和校验。

SATA 协议的物理层由千兆位级收发器GTX、OOB控制模块和接口传输率选择模块共同实现。

千兆位级收发器GTX的主要功能包括8B/10B编码/解码,串并/并串转换,逗点检测,时钟修正,预侧重和线性均衡等。

OOB控制模块和接口传输率选择模块能够自动识别硬盘的接口传输率,完成硬盘的上电过程或硬件复位过程,并同SATA控制器建立通信链接。

整个SATA协议的四层:物理层、链路层、传输层、应用层全部在一片FPGA中实现。

图5-1 SATA控制器用户接口设计用户接口由三部分组成:映像寄存器组,PLB接口和NPI接口。

映像寄存器组由32个32比特的寄存器组成,用来存放SATA控制器的控制信息和状态信息等,该寄存器组是地址映射的,是软件可以读出、可以写入的。

PLB接口实现嵌入式处理器和SATA控制器之间控制信息和状态信息的交换。

NPI(Native Port Interface)接口用于实现储存器控制器和SATA控制器之间数据的交换。

映像寄存器组应用层提供一个映像寄存器组,处理器传输各种命令时,向映像寄存器中写入命令或读取状态信息,设备通过发送帧来更新映像寄存器,对主机的命令进行响应。

在SATA协议中定义了有关映像寄存器组中寄存器的类型与用途。

本设计中寄存器组由32个寄存器组成,其中有5个寄存器是用户自定义的,其余的兼容ATA协议指令集,包括Status、Command、Error、Feature,LBA low等。

5个用户自定义的寄存器用于对SATA控制器中某些模块进行复位、观察状态和调试信息以及参数配置等。