AV06XX-XX中文资料

化妆品常用品牌批号

雅顿雅顿的批号第一码为年份,05年就是5开头,06年就是6开头了。

第二码为生产月份(A、B、C、D、F、H、J、K、L、N、P、S,依次代表1 2 3 4 5至12月,木有E、G,跳开了,不知道为啥要跳开),第三码为批次(A、B、C、D、F、H、J、K、L、N、P、S、T、V、X、Z,依次代表第1- 16个生产批次。

A表示第1批生产、B表示第2批生产,依此类推,Z表示第16批生产)例如:8BA就是08年2月第一批次生产的哦~倩碧(Clinique)批号一般是3码:XYZ,Y表月,Z表年,商品的产地会在瓶身或者外包装上标明。

月份表示为:1-9、A、B、C共12个月。

例如A59是2009年5月生产。

雅诗兰黛第一个字母代表批次,第二个数字(或字母)代表月份,1 2 3 4 5 6 7 8 9 A B C分别代表1~12月,第三个数字代表年份。

例如A20是2010年2月兰蔻LANCOME 兰蔻目前市面上最新的批号一般是这样:(例如)“40G101中间一个字母“G”表示2010后面三位数字第一个数字表示月份。

例如1-9代表相应月份,O代表10月份生产的、N代表是11月份生产的、D代表是12月份生产的,所以“40G101”就是2010年1月生产的。

娇韵诗CLARINS批号格式六位,第一位表示年,接着两位表示月份,后面的三位数字则是输入的货柜号。

例如:911214是2009年11月生产的。

CLARINS/娇韵诗保质期:3年。

美体小铺THE BODY SHOP1. 批号识别:一般在瓶底或瓶身会有一个批号,如D008EA,D代表年份是2008年,008是第008天,在英国制造大约是1月初,EA表示厂家编号的生产地点。

年份字母:A代表2005年,B代表2006年C代表2007年D代表2008年以此类推。

但是由于THE BODY SHOP还有部分海外(非英国)生产基地,极少数批号有不一致的现象。

另外就是有些精油类产品没有批号。

AV系列产品型号

A V系列多功能电力仪表产品选型及报价

●固有功能⊙可选功能空白无此功能

AV300系列后缀名命名

●固有功能⊙可选功能空白无此功能AV100系列后缀名命名

●固有功能⊙可选功能空白无此功能

AV160系列直流仪表命名规则

注①:直流电流输入,根据现场实际情况,可以接入分流器信号(0~75mV)、电流型霍尔元件信号(0~20mA或4~20mA)、电压型霍尔元件信号(0~5V)对应的尾缀分别为A1、A2、A3。

注②:如果选择此功能,则对应型号后面加尾缀J,如AV162J。

注③:如果选择此功能,则对应型号后面加尾缀K,如AV161K。

例:AV163KJ-A1:多功能直流电压电流仪表,带4~20mA输出,带IO扩展,电流测量为0~75mV。

KBPC10-10中文资料

KBPC15, IF = 7.5A ............................................. 1.1 ............................................... Volts

KBPC25, IF = 12.5A ............................................. 1.1 ............................................... Volts

Tap and in Double Configurations. Consult with FCI for Your Special Requirements.

Ratings at 25 Deg. C ambient temperature unless otherwise specified. Single Phase Half Wave, 60 HZ Resistive or Inductive Load. For Capacitive Load, Derate Current by 20%.

TA = 25°C ............................................. 5.0 ............................................... µAmps TA = 125°C ............................................. 500 ............................................... µAmps

Amps Amps Amps Amps Amps

............................................. 200 ............................................... ............................................. 300 ............................................... ............................................. 300 ............................................... ............................................. 400 ............................................... ............................................. 400 ...............................................

化妆品批号

AANNA SUI(安娜苏) 英文网站:/日文网站:/AVEDA批号表示法:例A93第一码为生产地,第二码为生产月份(1 2 3 4 5 6 7 8 9 a b c共12个月),第三码为生产年份A93就表示为03年9月生产AVON(雅方) 官方网站:中文网站台湾网站:日本AVON批号表示法:例:E8E第一位代表年分E为03年第二位为月分为8月第三为日期AYjewelry(AY珠宝) 官方网站:中文网站国际网站/饰品界的航空母舰集合了几乎所有的手工饰品Avene(雅漾) 官方网站:/avene.html日文网站:http://www.avene.co.jp中文网站:进口Avene批号表示法:产品外盒下方或上方会有两排英文及数字例如AV105 是指批号2104是指效期到2004年02月为止BBiotherm(碧欧泉)官方网站/中文网站:http://61.152.95.159/biotherm/台湾网站:批号表示法:例XY054第一位代表产地,第二位代表月份(X为02 Y为03 A为04) 后三位数表示那一年的第几天XY就表示03年的第54天生产注:04年开始欧莱雅集团统一年份开始为A开始如果为XA054就表示为04年第54天生产BLOOM 官方网站BOOTS 中文网站:/Bobbibrown 官方网站:Borghese(贝佳斯)官方网站: /生产批号比较法:例:PGPGRV第一位P表示是03年(O由于和0相似所以跳过不用,N为01年)至于日期我叫台湾网友问过专柜,那边也不知道怎么表示所以我也不知道怎么判断了.还有种是表示法如:len03c第一个字母l 代表2000年中间两个数字03 是3月,依此类推..j=1998年k=1999年l=2000年m=2001年贝佳斯的出厂日期还有分为新旧版两种的新版包含四个部份, 依序代表的是年.批.月.日。

如j是1998, k是1999, 4月1日则为401旧版包含四个部份, 依序代表的是年.批.月.日。

国外化妆品生产日期查询

ANNA SUI(安娜苏)英文网站: /日文网站: /AVEDA官方网站: 批号表示法:例A93第一码为生产地,第二码为生产月份(1 2 3 4 5 6 7 8 9 a b c共12个月),第三码为生产年份A93就表示为03年9月生产AVON(雅方)官方网站: 中文网站台湾网站: 日本AVON批号表示法:例:E8E第一位代表年分E为03年第二位为月分为8月第三为日期Avene(雅漾)官方网站/avene.html日文网站: http://www.avene.co.jp中文网站: 进口Avene批号表示法:产品外盒下方或上方会有两排英文及数字例如 AV105 是指批号 2104是指效期到2004年02月为止Biotherm(碧欧泉)官方网站/中文网站: http://61.152.95.159/biotherm/台湾网站: 批号表示法:例XY054第一位代表产地,第二位代表月份(X为02 Y为03 A为04) 后三位数表示那一年的第几天XY就表示03年的第54天生产注:04年开始欧莱雅集团统一年份开始为A开始如果为XA054就表示为04年第54天生产一般3年保质期。

BLOOM官方网站BOOTS中文网站: /Bobbibrown官方网站: THE BODY SHOP(美体小铺)官方网站: /中文网站: 生产批号表示法:例:K305A第一位代表年份(K表示02年L代表03年以此类推)305表示第305天生产A表示第一批生产K305A就表示是02年第305天生产Borghese(贝佳斯)官方网站: //生产批号比较法:例GPGRV第一位P表示是03年(O由于和0相似所以跳过不用,N为01年)至于日期我叫台湾网友问过专柜,那边也不知道怎么表示所以美肤小铺我也不知道怎么判断了.还有种是表示法如:len03c第一个字母 l 代表2000年中间两个数字 03 是3月,依此类推..j=1998年 k=1999年 l=2000年 m=2001年贝佳斯的出厂日期还有分为新旧版两种的新版包含四个部份, 依序代表的是年.批.月.日。

生产日期批号大全

批号大全:化妆品的生产日期AVEDA:批号表示法:例A93第一码为生产地,第二码为生产月份(1 2 3 4 5 6 7 8 9 a b c共12个月),第三码为生产年份A93就表示为03年9月生产AVON(雅方)**AVON批号表示法:例:E8E第一位代表年分E为03年第二位为月分为8月第三为日期Avene(雅漾)进口Avene批号表示法:产品外盒下方或上方会有两排英文及数字例如AV105 是指批号2104是指效期到2004年02月为止Biotherm(碧欧泉)批号表示法:例XY054第一位代表产地,第二位代表年份(X为02 Y为03 A为04) 后三位数表示那一年的第几天XY就表示03年的第54天生产注:04年开始欧莱雅集团统一年份开始为A开始如果为XA054就表示为04年第54天生产THE BODY SHOP(美体小铺)生产批号表示法:例:K305A第一位代表年份(K表示02年L代表03年以此类推)305表示第305天生产A表示第一批生产K305A就表示是02年第305天生产Borghese(贝佳斯)生产批号比较法:例:PGPGRV第一位P表示是03年(O由于和0相似所以跳过不用,N为01年)至于日期我叫台湾网友问过专柜,那边也不知道怎么表示所以美肤小铺我也不知道怎么判断了.还有种是表示法如:len03c第一个字母l 代表2000年中间两个数字03 是3月,依此类推..j=1998年k=1999年l=2000年m=2001年贝佳斯的出厂日期还有分为新旧版两种的新版包含四个部份, 依序代表的是年.批.月.日。

如j是1998, k是1999, 4月1日则为401 旧版包含四个部份, 依序代表的是年.批.月.日。

如8是1998, 9是1999, 4月1日则为401 所以mj730应该是2001年7月30号Burt`s bees例:1430312143代表的是生产日,03代表的是03年12是他们的商品代号所以1430312代表是2003年的第143天制造的.chanel(香奈尔)生产日期表示法:它的批号有四码, 只有前二码与制造日期有关:例如:35xx 表示是03年3月生产31xx-2002 1132xx-2002 1233xx-2003 0134xx-2003 0235xx-2003 0336xx-2003 0437xx-2003 0538xx-2003 06Christian Dior ( 克丽丝汀.迪奥)生产批号表示法:例3K023代表年份为03年,K代表月份表示为10月(A一月B二月C三月D四月E五月F六月G 七月H八月J九月K十月十一月M十二月)(其中英文字母“I“因为和阿拉伯数字的“1“很像..怕会混淆..所以跳过)所以3K02就表示是03年10月生产的Clarins(娇韵诗)生产批号表示法:210122第一位2表示02年然后10是表示月份,后面的122和生产日期无关210122就表示是02年10生产娇韵诗台湾官方说法保养品保质期是五年Clinique(倩碧)生产日期表示法:例A92第一位A代表是产地,第二位9为表示月份(8表示8月.9表示9月,A表示10月,B表示11月,C表示12月)第三位2表示年份A92就表示是02年九月生产Elizabeth Arden(伊莉莎白雅顿)批号表示法:例:B2NA第二位2代表02年生产Estee lauder(雅诗兰黛)生产日期表示法:例A92第一位A代表是产地,第二位9为表示月份(8表示8月.9表示9月,A表示10月,B表示11月,C表示12月)第三位2表示年份A92就表示是02年九月生产Givenchy ( 纪梵希)生产日期表示法:例:3A01第一位代表年份,第二位代表月份(A代表1月,以此类推,因为I和1和象所以跳过不用J代表9月)3A01就表示是03年1月生产GuerLian(娇兰)生产日期表示法:例2J02第一位代表年份,第二位代表月份(A代表1月,以此类推,因为I和1和象所以跳过不用J代表9月)2J01就表示是02年9月生产H20+(水之澳)生产日期表示法:例:2133H73第一位2表示年分就是02年产的之后133就代表该年的第几天所以2133H73就表示是02年第133天生产的Lancome(兰蔻)生产日期表示法:例CY054第一位代表产地,第二位代表月份(X为02 Y为03 A为04) 后三位数表示那一年的第几天CY就表示03年的第54天生产注:04年开始欧莱雅集团统一年份开始为A开始如果为CA054就表示为04年第54天生产L’’occitane生产日期表示法:例30V30代表周数(大概为10月)V代表年份(U-01年, V-02年)所以30V代表02年10月该品牌官方说法保质期为2年L“Oreal(欧莱雅)生产日期表示法请查看碧欧泉LANCOME表示法因为是同集团的产品Kiehl’’s ( 契奥氏)例nX196N代表产地,X代表年份,196代表该年的生产日,NX196就表示是02年第196天生产,因为属于欧莱雅集团,所以表示法和碧欧泉LANCOME等相同Helena Rubinstein(赫莲娜)与碧欧泉LANCOME等相同所以不再另做说明Neutrogena (露得清)生产日期表示法:例040703就表示是03年7月4号Sisley生产日期表示法:例020326就是02年3月26号产这个最简单了SISLEY台湾官方说法保质期4年Vichy(薇姿)属于欧莱雅集团,所以批号和LANCOME等相同YSL (圣罗兰)生产日期表示法:例如标号为EMB 60350 22411 00189则看法为....22411-->第一个字 2 -->2002年第二个2开始241为当年度的第241天制造所以是2002年8月制造...。

AV系列代码说明书

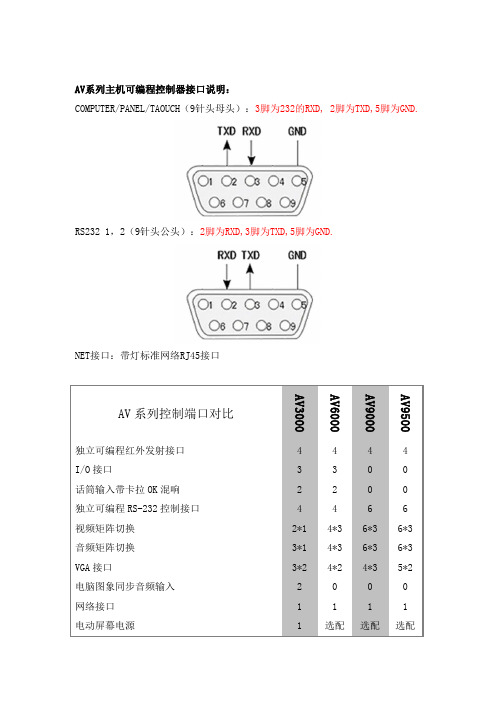

AV系列主机可编程控制器接口说明:COMPUTER/PANEL/TAOUCH(9针头母头):3脚为232的RXD, 2脚为TXD,5脚为GND.RS232 1,2(9针头公头):2脚为RXD,3脚为TXD,5脚为GND.NET接口:带灯标准网络RJ45接口AV系列控制主机通讯控制协议波特率:9600数据:8 BITS奇偶:无停止位: 1 BIT=====================================================================【开系统】3B 00 01 01 00 A0 07 0D【关系统】3B 00 01 00 00 A1 07 0D【强电控制】继电器开关停电动幕B0 B1 B2 3B 00 04 01 00 B0 00 0D3B 00 04 01 00 B1 00 0D3B 00 04 01 00 B2 00 0D投影机电源52 53 3B 00 03 00 00 52 00 0D3B 00 03 00 00 53 00 0D功放电源84 85 3B 00 04 01 00 84 00 0D3B 00 04 01 00 85 00 0D电脑开/关8C 8D 3B 00 04 01 00 8C 00 0D3B 00 04 01 00 8D 00 0D网络接口通3B 00 04 01 00 86 00 0D网络接口断3B 00 04 01 00 87 00 0D【信号切换 (输入,输出通道切换法) 】:VGA3B 00 09 01 XX YY 07 0DAV3B 00 09 02 XX YY 07 0DV(主输出)3B 00 09 03 XX YY 07 0DA(主输出)3B 00 09 04 XX YY 07 0D(XX 输入通道)VGA信号01—VGA INPUT1 02-VGA INPUT2 03-VGA INPUT304-VGA INPUT4 05-VGA INPUT5音视频信号01-INPUT AV1 02-INPUT AV2 03-INPUT AV304-INPUT AV4 05-INPUT AV5 06-INPUT AV6(YY 输出通道)VGA信号01-OUTPUT1 02-OUTPUT2 03-OUTPUT3视频信号01-OUTPUT1 02-OUTPUT2 03-OUTPUT3【音量控制】:3B 00 0B YY XX AA 00 0DYY=1-4 分别为第一输出通道,第二输出通道,第三输出通道第四话筒通道XX=1-3 1加,2减,3预置AA为预置值(0-20)预置值等于0为静音【红外控制】:红外通道切换3B 00 0A 00 XX XX 00 0D (XX=[01-04]4通道)红外键码使用3B 00 03 AA BB CC 00 0DAA BB 为0时,默认当前设备AA 为(01-04设备码时)为指定设备码BB 为0时,为指定设备红外通道,非0可指定通道 1-4 或组和值(1,2,4,8)CC 为键码(1-40)键码编码键码编码红外1 01 红外16 10红外2 02 红外17 11红外3 03 红外18 12红外4 04 红外19 13红外5 05 红外20 14红外6 06 红外21 15红外7 07 红外22 16红外8 08 红外23 17红外9 09 红外24 18红外10 0A 红外25 19红外11 0B 红外26 1A红外12 0C 红外27 1B红外13 0D 红外28 1C红外14 0E 。

ELH0002H中文资料

manufactured in U S A

Applications

Line driver 30 MHz buffer High-speed D A conversion Instrumentation buffer Precision current source

AV AI RIN ROUT HD tr

Voltage Gain

Current Gain Input Impedance

Output Impedance

Harmonic Distortion Rise Time

RS e 10 kX RL e 1 kX VIN e 3 VP-P f e 1 kHz VIN e 1 VRMS f e 1 kHz RS e 200 kX VIN e 1 VRMS RL e 1 kX f e 1 kHz RL e 50X VIN e 1 VRMS RS e 10 kX f e 1 kHz VIN e 5 VRMS f e 1 kHz

Test Level I II

III IV V

Test Procedure 100% production tested and QA sample tested per QA test plan QCX0002 100% production tested at TA e 25 C and QA sample tested at TA e 25 C TMAX and TMIN per QA test plan QCX0002 QA sample tested per QA test plan QCX0002 Parameter is guaranteed (but not tested) by Design and Characterization Data Parameter is typical value at TA e 25 C for information purposes only

化妆品批号

AANNA SUI(安娜苏) 英文网站:/日文网站:/AVEDA批号表示法:例A93第一码为生产地,第二码为生产月份(1 2 3 4 5 6 7 8 9 a b c共12个月),第三码为生产年份A93就表示为03年9月生产AVON(雅方) 官方网站:中文网站台湾网站:日本AVON批号表示法:例:E8E第一位代表年分E为03年第二位为月分为8月第三为日期AYjewelry(AY珠宝) 官方网站:中文网站国际网站/饰品界的航空母舰集合了几乎所有的手工饰品Avene(雅漾) 官方网站:/avene.html日文网站:http://www.avene.co.jp中文网站:进口Avene批号表示法:产品外盒下方或上方会有两排英文及数字例如AV105 是指批号2104是指效期到2004年02月为止BBiotherm(碧欧泉)官方网站/中文网站:http://61.152.95.159/biotherm/台湾网站:批号表示法:例XY054第一位代表产地,第二位代表月份(X为02 Y为03 A为04) 后三位数表示那一年的第几天XY就表示03年的第54天生产注:04年开始欧莱雅集团统一年份开始为A开始如果为XA054就表示为04年第54天生产BLOOM 官方网站BOOTS 中文网站:/Bobbibrown 官方网站:Borghese(贝佳斯)官方网站: /生产批号比较法:例:PGPGRV第一位P表示是03年(O由于和0相似所以跳过不用,N为01年)至于日期我叫台湾网友问过专柜,那边也不知道怎么表示所以我也不知道怎么判断了.还有种是表示法如:len03c第一个字母l 代表2000年中间两个数字03 是3月,依此类推..j=1998年k=1999年l=2000年m=2001年贝佳斯的出厂日期还有分为新旧版两种的新版包含四个部份, 依序代表的是年.批.月.日。

如j是1998, k是1999, 4月1日则为401旧版包含四个部份, 依序代表的是年.批.月.日。

A43L2616AV-6中文资料

Preliminary 1M X 16 Bit X 4 Banks Synchronous DRAMDocument Title1M X 16 Bit X 4 Banks Synchronous DRAMRevision HistoryDate Remark Rev. No. History Issue issue November 30, 2004 Preliminary0.0 InitialA43L2616APreliminary1M X 16 Bit X 4 Banks Synchronous DRAMFeatureJEDEC standard 3.3V power supplyLVTTL compatible with multiplexed address Four banks / Pulse RAS MRS cycle with address key programs - CAS Latency (2,3)- Burst Length (1,2,4,8 & full page) - Burst Type (Sequential & Interleave) All inputs are sampled at the positive going edge of the system clock Clock Frequency: 166MHz @ CL=3 143MHz @ CL=3Burst Read Single-bit Write operationDQM for masking Auto & self refresh 64ms refresh period (4K cycle) Commercial Temperature Operation : 0°C~70°C Industrial Temperature Operation : -40°C~85°C for –U grade 54 Pin TSOP (II) and 54 Balls CSP (8mm x 8mm)General DescriptionThe A43L2616A is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 X 1,048,576 words by 16 bits, fabricated with AMIC’s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock.I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable latencies allows the same device to be useful for a variety of high bandwidth, high performance memory system applications.Pin ConfigurationTSOP (II)V S SD Q 15V S S QD Q 14D Q 13V D D QD Q 12D Q 11V S S QD Q 10D Q 9V D D QD Q 8V S SU D Q MC KC K EN CA 9A 8A 7A 6A 5A 4V S SV D DD Q 0V D D QD Q 1D Q 2V S S QD Q 3D Q 4V D D QD Q 5D Q 6V S S QD Q 7V D DL D Q MW EC A SR A SC SA 10/A PB S 1B S 0A 0A 1A 2A 3V D DA 11N CPin Configuration (continued)54 Balls CSP (8 mm x 8 mm)Top ViewBlock DiagramCLKADDDQiPin DescriptionsAbsolute Maximum Ratings*Voltage on any pin relative to VSS (Vin, Vout ) . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1.0V to +4.6V Voltage on VDD supply relative to VSS (VDD, VDDQ ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-1.0V to +4.6V Storage Temperature (T STG ) . . . . . . . . . . -55°C to +150°C Soldering Temperature X Time (T SLODER ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C X 10sec Power Dissipation (P D ) . . . . . . . . . . . . . . . . . . . . . . . . .1W Short Circuit Current (Ios) . . . . . . . . . . . . . . . . . . . . 50mA *CommentsPermanent device damage may occur if “Absolute Maximum Ratings” are exceeded.Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.Capacitance (T A =25°C, f=1MHz)DC Electrical CharacteristicsRecommend operating conditions (Voltage referenced to VSS = 0V, T A = 0ºC to +70ºC or T A = -40ºC to +85ºC)Parameter Symbol Min Typ Max Unit NoteSupply Voltage VDD,VDDQ 3.0 3.3 3.6 VInput High Voltage V IH 2.0 3.0 VDD+0.3 VInput Low Voltage V IL -0.3 0 0.8 V Note 1 Output High Voltage V OH 2.4 --V I OH = -2mAOutput Low Voltage V OL - - 0.4 V I OL = 2mA Input Leakage Current I IL -5 - 5 µA Note 2 Output Leakage Current I OL -5 - 5 µANote 3Output Loading ConditionSee Figure 1Note: 1. V IL (min) = -1.5V AC (pulse width ≤ 5ns).2. Any input 0V ≤ VIN ≤ VDD + 0.3V, all other pins are not under test = 0V3. Dout is disabled, 0V ≤ Vout ≤ VDDDecoupling Capacitance Guide LineRecommended decoupling capacitance added to power line at board.Parameter Symbol Value UnitDecoupling Capacitance between VDD and VSS C DC1 0.1 + 0.01 µF Decoupling Capacitance between VDDQ and VSSQC DC20.1 + 0.01µFNote: 1. VDD and VDDQ pins are separated each other.All VDD pins are connected in chip. All VDDQ pins are connected in chip. 2. VSS and VSSQ pins are separated each otherAll VSS pins are connected in chip. All VSSQ pins are connected in chip.DC Electrical Characteristics(Recommended operating condition unless otherwise noted, T A = 0°C to 70°C T A = -40ºC to +85ºC) Note: 1. Measured with outputs open. Addresses are changed only one time during t CC (min).2. Refresh period is 64ms. Addresses are changed only one time during t CC (min).3. I CC6 normal version: A43L2616AV-6, A43L2616AV-7.4. I CC6 low self refresh current version: A43L2616AV-6V, A43L2616AV-7V.AC Operating Test Conditions(VDD = 3.3V ±0.3V, T A = 0°C to +70°C or T A = -40ºC to +85ºC)Parameter ValueAC input levelsV IH /V IL = 2.4V/0.4V Input timing measurement reference level 1.4VInput rise and all time (See note3)tr/tf = 1ns/1ns Output timing measurement reference level 1.4V Output load conditionSee Fig.2Output(Fig. 1) DC Output Load Circuit ΩTT =1.4V (Fig. 2) AC Output Load CircuitAC Characteristics(AC operating conditions unless otherwise noted)-6 -7Symbol Parameter CAS Latency Min Max Min MaxUnit Notet CC CLK cycle time 6 1000 7 1000 ns 1t SACCLK to valid Output delay- 5 - 5.4 ns 1,2 t OH Output data hold time 2.5-2.7-ns2t CH CLK high pulse width 32.5 - 2.5 - ns 3 t CL CLK low pulse width 2.5 - 2.5 - ns 3 t SS Input setup time 2 - 2 - ns 3 t SH Input hold time 1 - 1 - ns 3 t SLZ CLK to output in Low-Z 1-1-ns2t SHZCLK to output In Hi-Z3- 5.5 - 6 ns*All AC parameters are measured from half to half.Note : 1. Parameters depend on programmed CAS latency.2. If clock rising time is longer than 1ns, (tr/2-0.5) ns should be added to the parameter.3. Assumed input rise and fall time (tr & tf) = 1ns.If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter.Operating AC Parameter(AC operating conditions unless otherwise noted)Note: 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then rounding off to the next higher integer.2. Minimum delay is required to complete write.Simplified Truth Table(V = Valid, X = Don’t Care, H = Logic High, L = Logic Low) Note : 1. OP Code: Operand CodeA0~A11, BS0, BS1: Program keys. (@MRS)2. MRS can be issued only at both banks precharge state.A new command can be issued after 2 clock cycle of MRS.3. Auto refresh functions as same as CBR refresh of DRAM.The automatical precharge without Row precharge command is meant by “Auto”.Auto/Self refresh can be issued only at both precharge state.4. BS0, BS1 : Bank select address.If both BS1 and BS0 are “Low” at read, write, row active and precharge, bank A is selected.If both BS1 is “Low” and BS0 is “High” at read, write, row active and precharge, bank B is selected.If both BS1 is “High” and BS0 is “Low” at read, write, row active and precharge, bank C is selected.If both BS1 and BS0 are “High” at read, write, row active and precharge, bank D is selected.If A10/AP is “High” at row precharge, BS1 and BS0 is ignored and all banks are selected.5. During burst read or write with auto precharge, new read write command cannot be issued.Another bank read write command can be issued at every burst length.6. DQM sampled at positive going edge of a CLK masks the data-in at the very CLK (Write DQM latency is 0) butmasks the data-out Hi-Z state after 2 CLK cycles. (Read DQM latency is 2)Mode Register Filed Table to Program ModesRegister Programmed with MRS AddressBS0, BS1A11, A10A9A8A7A6A5A4A3A2A1A0FunctionRFURFU W.B.L TM CAS Latency BT Burst Length(Note 1)(Note 2)Test ModeCAS LatencyBurst TypeBurst LengthA8 A7TypeA6 A5 A4Latency A3TypeA2A1 A0 BT=0BT=10 0 Mode Register Set0 0 0Reserved0Sequential 00 0 1 1 0 1 0 0 1- 1Interleave 00 1 2 2 1 0 0 1 0 2 0 1 0 4 4 1 1Vendor Use Only0 1 1 3 0 1 188 Write Burst Length 1 0 0Reserved 10 0 Reserved Reserved A9 Length 1 0 1Reserved10 1 ReservedReserved0 Burst 1 1 0Reserved 1 1 0 Reserved Reserved 1 Single Bit 1 1 1Reserved11 1 256(Full)ReservedPower Up Sequence1. Apply power and start clock, Attempt to maintain CKE = “H”, DQM = “H” and the other pins are NOP condition at inputs.2. Maintain stable power, stable clock and NOP input condition for a minimum of 200µs.3. Issue precharge commands for all banks of the devices.4. Issue 2 or more auto-refresh commands.5. Issue a mode register set command to initialize the mode register. cf.) Sequence of 4 & 5 may be changed.The device is now ready for normal operation.Note : 1. RFU(Reserved for Future Use) should stay “0” during MRS cycle.2. If A9 is high during MRS cycle, “Burst Read Single Bit Write” function will be enabled.Burst Sequence (Burst Length = 4)Initial addressSequential Interleave A1 A00 0 0 1 2 3 0 1 2 30 1 1 2 3 0 1 0 3 21 023 0 1 2 3 0 11 1 3 0 123 2 1 0Burst Sequence (Burst Length = 8)Initial addressSequential Interleave A2 A1 A00 0 0 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 70 0 1 1 2 3 4 5 6 7 0 1 0 3 2 5 4 7 60 1 0 2 3 4 5 6 7 0 1 2 3 0 1 6 7 4 50 1 1 3 4 5 6 7 0 1 2 3 2 1 0 7 6 5 41 0 0 4 5 6 7 0 1234567 0 1 2 31 0 1 5 6 7 0 12345 4 76 1 0 3 21 1 0 6 7 0 1234567 4 5 2 3 0 11 1 1 7 0 1234567 6 5 4 3 2 1 0Device OperationsClock (CLK)The clock input is used as the reference for all SDRAM operations. All operations are synchronized to the positive going edge of the clock. The clock transitions must be monotonic between V IL and V IH. During operation with CKE high all inputs are assumed to be in valid state (low or high) for the duration of set up and hold time around positive edge of the clock for proper functionality and ICC specifications.Clock Enable (CLK)The clock enable (CKE) gates the clock onto SDRAM. If CKE goes low synchronously with clock (set-up and hold time same as other inputs), the internal clock is suspended form the next clock cycle and the state of output and burst address is frozen as long as the CKE remains low. All other inputs are ignored from the next clock cycle after CKE goes low. When both banks are in the idle state and CKE goes low synchronously with clock, the SDRAM enters the power down mode form the next clock cycle. The SDRAM remains in the power down mode ignoring the other inputs as long as CKE remains low. The power down exit is synchronous as the internal clock is suspended. When CKE goes high at least “t SS + 1 CLOCK” before the high going edge of the clock, then the SDRAM becomes active from the same clock edge accepting all the input commands.Bank Select (BS0, BS1)This SDRAM is organized as 4 independent banks of 1,048,576 words X 16 bits memory arrays. The BS0, BS1 inputs is latched at the time of assertion of RAS and CASto select the bank to be used for the operation. The bank select BS0, BS1 is latched at bank activate, read, write mode register set and precharge operations.Address Input (A0 ~ A11)The 20 address bits required to decode the 262,144 word locations are multiplexed into 12 address input pins (A0~A11). The 12 bit row address is latched along with RAS, BS0 and BS1 during bank activate command. The 8 bit column address is latched along with CAS, WE, BS0 and BS1during read or write command.NOP and Device DeselectWhen , CAS and WE are high, the SDRAM performs no operation (NOP). NOP does not initiate any new operation, but is needed to complete operations which require more than single clock like bank activate, burst read, auto refresh, etc. The device deselect is also a NOP and is entered by asserting CS high. CS high disables the command decoder so that RAS, CAS and WE, and all the address inputs are ignored.Power-UpThe following sequence is recommended for POWER UP 1. Power must be applied to either CKE and DQM inputs topull them high and other pins are NOP condition at the inputs before or along with VDD (and VDDQ) supply.The clock signal must also be asserted at the same time.2. After VDD reaches the desired voltage, a minimumpause of 200 microseconds is required with inputs in NOP condition.3. Both banks must be precharged now.4. Perform a minimum of 2 Auto refresh cycles to stabilizethe internal circuitry.5. Perform a MODE REGISTER SET cycle to program theCAS latency, burst length and burst type as the default value of mode register is undefined.At the end of one clock cycle from the mode register set cycle, the device is ready for operation.When the above sequence is used for Power-up, all the out-puts will be in high impedance state. The high impedance of outputs is not guaranteed in any other power-up sequence.cf.) Sequence of 4 & 5 may be changed.Mode Register Set (MRS)The mode register stores the data for controlling the various operation modes of SDRAM. It programs the CAS latency, addressing mode, burst length, test mode and various vendor specific options to make SDRAM useful for variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after power up to operate the SDRAM. The mode register is written by asserting low on CS,RAS, CAS,(The SDRAM should be in active mode with CKE already high prior to writing the mode register). The state of address pins A0~A11, BS0 and BS1 in the same cycle as CS,,CAS,WE going low is the data written in the mode register. One clock cycle is required to complete the write in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as both banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length field uses A0~A2, burst type uses A3, addressing mode uses A4~A6, A7~A8, A11, BS0 and BS1 are used for vendor specific options or test mode. And the write burst length is programmed using A9. A7~A8, A11, BS0 and BS1 must be set to low for normal SDRAM operation.Refer to table for specific codes for various burst length, addressing modes and CAS latencies.Device Operations (continued)Bank ActivateThe bank activate command is used to select a random row in an idle bank. By asserting low on RAS and CS with desired row and bank addresses, a row access is initiated. The read or write operation can occur after a time delay of t RCD(min) from the time of bank activation. t RCD(min) is an internal timing parameter of SDRAM, therefore it is dependent on operating clock frequency. The minimum number of clock cycles required between bank activate and read or write command should be calculated by dividing t RCD(min) with cycle time of the clock and then rounding off the result to the next higher integer. The SDRAM has two internal banks on the same chip and shares part of the internal circuitry to reduce chip area, therefore it restricts the activation of both banks immediately. Also the noise generated during sensing of each bank of SDRAM is high requiring some time for power supplies recover before the other bank can be sensed reliably. t RRD(min) specifies the minimum time required between activating different banks. The number of clock cycles required between different bank activation must be calculated similar to t RCD specification. The minimum time required for the bank to be active to initiate sensing and restoring the complete row of dynamic cells is determined by t RAS(min) specification before a precharge command to that active bank can be asserted. The maximum time any bank can be in the active state is determined by t RAS(max). The number of cycles for both t RAS(min) and t RAS(max) can be calculated similar to t RCD specification.Burst ReadThe burst read command is used to access burst of data on consecutive clock cycles from an active row in an active bank. The burst read command is issued by asserting low on CS and CAS with WE being high on the positive edge of the clock. The bank must be active for at least t RCD(min) before the burst read command is issued. The first output appears CAS latency number of clock cycles after the issue of burst read command. The burst length, burst sequence and latency from the burst read command is determined by the mode register which is already programmed. The burst read can be initiated on any column address of the active row. The address wraps around if the initial address does not start from a boundary such that number of outputs from each I/O are equal to the burst length programmed in the mode register. The output goes into high-impedance at the end of the burst, unless a new burst read was initiated to keep the data output gapless. The burst read can be terminated by issuing another burst read or burst write in the same bank or the other active bank or a precharge command to the same bank. The burst stop command is valid at every page burst length. Burst WriteThe burst write command is similar to burst read command, and is used to write data into the SDRAM consecutive clock cycles in adjacent addresses depending on burst length and burst sequence. By asserting low on CS,CAS and WE with valid column address, a write burst is initiated. The data inputs are provided for the initial address in the same clock cycle as the burst write command. The input buffer is deselected at the end of the burst length, even though the internal writing may not have been completed yet. The writing can not complete to burst length. The burst write can be terminated by issuing a burst read and DQM for blocking data inputs or burst write in the same or the other active bank. The burst stop command is valid only at full page burst length where the writing continues at the end of burst and the burst is wrap around. The write burst can also be terminated by using DQM for blocking data and precharging the bank “t RDL” after the last data input to be written into the active row. See DQM OPERATION also.DQM OperationThe DQM is used to mask input and output operation. It works similar to OE during read operation and inhibits writing during write operation. The read latency is two cycles from DQM and zero cycle for write, which means DQM masking occurs two cycles later in the read cycle and occurs in the same cycle during write cycle. DQM operation is synchronous with the clock, therefore the masking occurs for a complete cycle. The DQM signal is important during burst interrupts of write with read or precharge in the SDRAM. Due to asynchronous nature of the internal write, the DQM operation is critical to avoid unwanted or incomplete writes when the complete burst write is not required.PrechargeThe precharge operation is performed on an active bank by asserting low on CS,RAS,WE and A10/AP with valid BA of the bank to be precharged. The precharge command can be asserted anytime after t RAS(min) is satisfied from the bank activate command in the desired bank. “t RP” is defined as the minimum time required to precharge a bank. The minimum number of clock cycles required to complete row precharge is calculated by dividing “t RP” with clock cycle time and rounding up to the next higher integer. Care should be taken to make sure that burst write is completed or DQM is used to inhibit writing before precharge command is asserted. The maximum time any bank can be active is specified by t RAS(max). Therefore, each bank has to be precharged within t RAS(max) from the bank activate command. At the end of precharge, the bank enters the idle state and is ready to be activated again.Entry to Power Down, Auto refresh, Self refresh and Mode register Set etc, is possible only when both banks are in idle state.Device Operations (continued)Auto PrechargeThe precharge operation can also be performed by usingauto precharge. The SDRAM internally generates thetiming to satisfy t RAS(min) and “t RP” for the programmedburst length and CAS latency. The auto prechargecommand is issued at the same time as burst read or burstwrite by asserting high on A10/AP. If burst read or burstwrite command is issued with low on A10/AP, the bank isleft active until a new command is asserted. Once autoprecharge command is given, no new commands arepossible to that particular bank until the bank achieves idlestate.Four Banks PrechargeBoth banks can be precharged at the same time by using Precharge all command. Asserting low on CS,RAS and WE with high on A10/AP after both banks have satisfied t RAS(min) requirement, performs precharge on both banks.At the end of tRP after performing precharge all, bothbanks are in idle state.Auto RefreshThe storage cells of SDRAM need to be refreshed every64ms to maintain data. An auto refresh cycle accomplishesrefresh of a single row of storage cells. The internalcounter increments automatically on every auto refreshcycle to refresh all the rows. An auto refresh command is issued by asserting low on CS,RAS and CAS with high on CKE and WE. The auto refresh command can only be asserted with both banks being in idle state and the deviceis not in power down mode (CKE is high in the previouscycle). The time required to complete the auto refresh operation is specified by “t RC(min)”. The minimum number of clock cycles required can be calculated by driving “t RC” with clock cycle time and then rounding up to the next higher integer. The auto refresh command must be followed by NOP’s until the auto refresh operation is completed. Both banks will be in the idle state at the end of auto refresh operation. The auto refresh is the preferred refresh mode when the SDRAM is being used for normal data transactions. The auto refresh cycle can be performed once in 15.6us or a burst of 4096 auto refresh cycles once in 64ms.Self RefreshThe self refresh is another refresh mode available in the SDRAM. The self refresh is the preferred refresh mode for data retention and low power operation of SDRAM. In self refresh mode, the SDRAM disables the internal clock and all the input buffers except CKE. The refresh addressing and timing is internally generated to reduce power consumption.The self refresh mode is entered from all banks idle state by asserting low on CS,RAS,CAS and CKE with high on WE. Once the self refresh mode is entered, only CKE state being low matters, all the other inputs including clock are ignored to remain in the self refresh.The self refresh is exited by restarting the external clock and then asserting high on CKE. This must be followed by NOP’s for a minimum time of “t RC” before the SDRAM reaches idle state to begin normal operation. If the system uses burst auto refresh during normal operation, it is recommended to used burst 4096 auto refresh cycles immediately after exiting self refresh.Basic feature And Function Descriptions1. CLOCK SuspendNote: CLK to CLK disable/enable=1 clock2. DQM Operation* Note : 1. DQM makes data out Hi-Z after 2 clocks which should masked by CKE “L”.2. DQM masks both data-in and data-out.3. CAS Interrupt (I)Note : 1. By “Interrupt”, It is possible to stop burst read/write by external command before the end of burst.By “CAS Interrupt”, to stop burst read/write by CAS access; read, write and block write.2. t CCD : CAS to CAS delay. (=1CLK)3. t CDL : Last data in to new column address delay. (= 1CLK).4. CAS Interrupt (II) : Read Interrupted Write & DQM* Note : 1. To prevent bus contention, there should be at least one gap between data in and data out.2. To prevent bus contention, DQM should be issued which makes a least one gap between data in and data out.5. Write Interrupted by Precharge & DQMNote : 1. To inhibit invalid write, DQM should be issued.2. This precharge command and burst write command should be of the same bank, otherwise it is not prechargeinterrupt but only another bank precharge of dual banks operation.6. Precharge7. Auto Precharge* Note : 1. The row active command of the precharge bank can be issued after t RP from this point.The new read/write command of other active bank can be issued from this point.At burst read/write with auto precharge, CAS interrupt of the same/another bank is illegal.8. Burst Stop & Interrupted by Precharge9. MRSNote : 1. t RDL : 1CLK 2. t BDL : 1CLK; Last data in to burst stop delay.Read or write burst stop command is valid at every burst length.3. Number of valid output data after row precharge or burst stop: 1,2 for CAS latency = 2, 3 respectively.4. PRE: All banks precharge if necessary.MRS can be issued only when all banks are in precharged state.10. Clock Suspend Exit & Power Down Exit11. Auto Refresh & Self Refresh* Note : 1. Active power down : one or more bank active state.2. Precharge power down : both bank precharge state.3. The auto refresh is the same as CBR refresh of conventional DRAM.No precharge commands are required after Auto Refresh command.During t RC from auto refresh command, any other command can not be accepted.4. Before executing auto/self refresh command, both banks must be idle state.5. MRS, Bank Active, Auto/Self Refresh, Power Down Mode Entry.6. During self refresh mode, refresh interval and refresh operation are performed internally.After self refresh entry, self refresh mode is kept while CKE is LOW.During self refresh mode, all inputs expect CKE will be don’t cared, and outputs will be in Hi-Z state.During t RC from self refresh exit command, any other command can not be accepted.Before/After self refresh mode, burst auto refresh cycle (4K cycles ) is recommended.12. About Burst Type ControlSequential counting At MRS A3=”0”. See the BURST SEQUENCE TABE.(BL=4,8) BL=1,2,4,8 and full page wrap around.BasicMODEInterleave counting At MRS A3=” 1”. See the BURST SEQUENCE TABE.(BL=4,8) BL=4,8 At BL=1,2 Interleave Counting = Sequential CountingRandom MODE Random column Accesst CCD = 1 CLKEvery cycle Read/Write Command with random column address can realizeRandom Column Access.That is similar to Extended Data Out (EDO) Operation of convention DRAM.13. About Burst Length ControlPower On Sequence & Auto RefreshCKECSRASCASADDRBS0, BS1A10/APWEDQMDQ(A-Bank)Single Bit Read-Write-Read Cycles (Same Page) @CAS Latency=3, Burst Length=1CLOCKCKECSRASCASADDRBS0, BS1A10/APWEDQMDQ* Note : 1. All inputs can be don’t care when CS is high at the CLK high going edge.2. Bank active & read/write are controlled by BS0, BS1.BS1 BS0 Active & Read/WriteA0 0 BankB0 1 BankC1 0 BankD1 1 Bank3. Enable and disable auto precharge function are controlled by A10/AP in read/write command.A10/AP BS1 BS0Operation0 0 Disable auto precharge, leave bank A active at end of burst.0 1 Disable auto precharge, leave bank B active at end of burst.1 0 Disable auto precharge, leave bank C active at end of burst.1 1 Disable auto precharge, leave bank D active at end of burst.0 0 Enable auto precharge, precharge bank A at end of burst.0 1 Enable auto precharge, precharge bank B at end of burst.11 0 Enable auto precharge, precharge bank C at end of burst.1 1 Enable auto precharge, precharge bank D at end of burst.4. A10/AP and BS0, BS1 control bank precharge when precharge command is asserted.A10/AP BS1 BS0 PrechargeA0 0 0 BankB0 0 1 BankC0 1 0 BankD0 1 1 BankBanks1 X X All。

EXBVxxxx中文资料

5.08+0.20 –0.10

2.20 +0.20 –0.10

0.70 ±0.20

0.80 ±0.15

0.80 ±0.15

0.50 ±0.15

0.55 ±0.15

(3) Flat Terminal type

A1 A2 EXB18V G T G W P L B B

Type (inches) EXB18V (0201 4)

±0.10

B

W 0.60 ±0.10 1.00 ±0.10 1.00

±0.10

T 0.35 ±0.10 0.35 ±0.10 0.35

±0.10

A1 0.35 ±0.10 0.40 ±0.10 0.45

±0.10

A2 — — 0.35

±0.10

B 0.15 ±0.10 0.18 ±0.10 0.20

May. 2005

元器件交易网

Chip Resistor Array

■

Item Resistance Range Resistance Tolerance 14V,24V,V4V,34V Specifications 10 to 1 M :E24 series J: ±5 % 4 terminal Item 14V,18V (1) Limiting Element Voltage 2HV Max. Rated Continuous 24V,28V,N8V,38V,34V,V4V,V8V Working Voltage S8V Specifications 12.5 V 25 V 50 V 100 V 25 V 50 V 200 V ±200 10 -6/°C(ppm/°C)

Dimensions (mm) L 1.40 ±0.10 W 0.60 ±0.10 T 0.35 ±0.10 A1 0.20 ±0.10 A2 0.20 ±0.10 B 0.10 ±0.10 P (0.40) G 0.20 ±0.10

化妆品批号大全

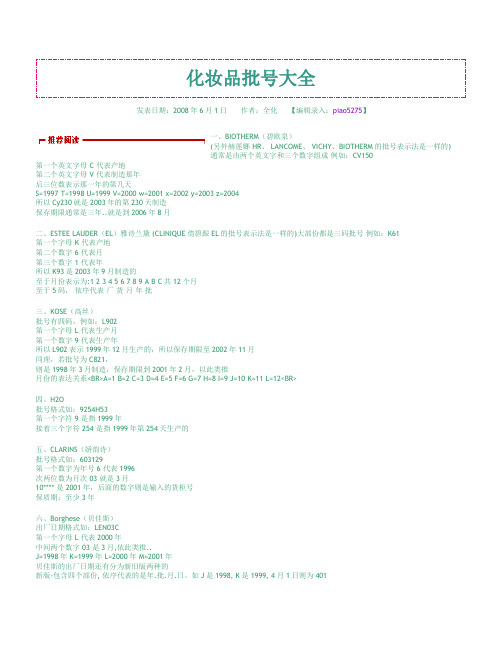

化妆品批号大全发表日期:2008年6月1日 作者:全化 【编辑录入:piao5275】一、BIOTHERM (碧欧泉) (另外赫莲娜 HR 、 LANCOME 、 VICHY 、BIOTHERM 的批号表示法是一样的)通常是由两个英文字和三个数字组成 例如:CV150第一个英文字母 C 代表产地第二个英文字母 V 代表制造那年后三位数表示那一年的第几天S=1997 T=1998 U=1999 V=2000 w=2001 x=2002 y=2003 z=2004所以Cy230就是2003年的第230天制造保存期限通常是三年..就是到2006年8月二、ESTEE LAUDER (EL )雅诗兰黛 (CLINIQUE 倩碧跟EL 的批号表示法是一样的)大部份都是三码批号 例如:K61 第一个字母 K 代表产地第二个数字 6 代表月第三个数字 1 代表年所以K93是2003年9月制造的至于月份表示为:1 2 3 4 5 6 7 8 9 A B C 共12个月至于5码, 依序代表 厂 货 月 年 批三、KOSE (高丝)批号有四码,例如:L902第一个字母 L 代表生产月第一个数字 9 代表生产年所以L902表示1999年12月生产的,所以保存期限至2002年11月同理,若批号为C821,则是1998年3月制造,保存期限到2001年2月,以此类推月份的表达关系<BR>A=1 B=2 C=3 D=4 E=5 F=6 G=7 H=8 I=9 J=10 K=11 L=12<BR>四、H2O批号格式如:9254H53第一个字符 9 是指1999年接着三个字符 254 是指1999年第254天生产的五、CLARINS (娇韵诗)批号格式如:603129第一个数字为年号 6 代表1996次两位数为月次 03 就是3月10**** 是2001年,后面的数字则是输入的货柜号保质期:至少3年六、Borghese (贝佳斯)出厂日期格式如:LEN03C第一个字母 L 代表2000年中间两个数字 03 是3月,依此类推..J=1998年 K=1999年 L=2000年 M=2001年贝佳斯的出厂日期还有分为新旧版两种的新版-包含四个部份, 依序代表的是年.批.月.日。

舞美知识培训教材

调音台是将多路音频电信号进行技术处理后,依所需的电平值加以混合、分配输送给还音系统重放或录音机予以记录的一种电子音频系统设备。 在音频系统中,以调音台为中心,连接各种信号源设备和音频处理、输出设备。它是录音、扩音、播音系统中的重要设备,是音响工作者进行艺术再创造的主要工具,被誉为专业音频系统的“心脏”。

AV设备及及基础知识介绍

单击此处添加副标题

北京恒基国际展览服务中心

目录

CONTENTS

01

单击添加文本具体内容

02

单击添加文本具体内容

目录

CONTENTS

01

CONTENTS

灯光设备

05

音频设备

P37

03

视频设备

特效设备

02

目 录

P59

06

P20

单击添加文本具体内容

04

P04

单击添加文本具体内容

镜头倍数*幕布宽度= 最佳距离

周边设备

分配器/切换器/矩阵 DA/Switcher/Matrix 处理器和转换器 Processor/Convertor 监视器和电视机 Monitor/TV

使用切换器,可将视频,电脑,现场,VCR之间的互相转换。 如果在同一时间要使屏幕或其他显示设备出现不同的图象,需要使用矩阵。 切换到屏幕前必须使用视频监视器(Monitor)进行预览,以避免差错。

压限器又称压缩/限幅器,是用于压缩(或限制)节目信号的动态范围,避免过激失真的音频信号处理设备。 作用: 抑制信号幅度,保护扩声系统 产生特殊的音响效果 使音量变化平稳

麦克风 无线手持: 目前拾音方式都是动圈,特点灵敏度低,使用方便。所以要求使用者近距离使用,甚至于贴着嘴,才会把声音全频段完套的拾取到系统, 讲台麦克: 会议中经常用到的。特点:灵敏度高,指向性强,所以要求安装人员将音箱背对MIC以免产生反馈。如果环境要求MIC必须在音箱前面,会出项三种情况是:1、乱叫 2、没声 3、讲话者听不出来是谁在说话。