AMF2812S-EM中文资料

F2812外部接口XINTF资料

F2812外部接口XINTF什么是外部接口,外部接口有什么作用,怎么去配置和使用这一块。

今天了解了这部分的知识,现将其详细的记录下来。

先看一下什么是外部接口。

外部接口是F2812与外部设备进行通信的重要接口,这些外部接口对应着CPU内部的某个存储空间,CPU通过对存储空间进行的读写操作间接控制外部接口。

书本上抄下来的定义,很是官方啊,不好懂。

再来看一下接的是一些什么,估计是不是会好理解一些呢?一般用于RAM,FLASH等。

哦...估计是内部数据或者是程序存不下了,找一个外面的片子来做存储区扩展用的接口。

外部接口有哪一些线呢?有片选信号线、数据总线、地址总线、读写使能信号线、以及其他信号线。

F2812中外部接口被映射到5个固定的存储空间区域,每个区域都有一个片选信号。

当系统使能片选信号后,数据自动存储到对应的存储空间内。

嘻嘻!就喜欢这一句自动存储。

所有的数字芯片不能少的一条主线就是时钟,这个模块的时钟怎样呢?答:XINTF模块的时序都是参照F2812的内部时钟XTIMCLK。

大小可以人为设定为系统时钟或系统时钟的一半。

F2812中XINTF的使用想使用XINTF先要弄清楚里面有些什么,外面有些什么引脚需要接线。

XINTF一共有5个空间,分别是Zone0、Zone1、Zone2、Zone6、Zone7,每个空间有相应的片选信号线连接到外面。

其中1、2共用一根片选线,6、7共用一根片选线;2、6共用相同的外部地址,外部首地址0x0 0000、尾地址0x7 ffff;1、2占用的外部总线地址不同,0的为0x2000~0x3fff、1的为0x4000~0x5fff;空间7可以作为外部启动的存储空间,由于这个空间的特殊性,所以暂时不打算用,也就不放在这里讨论了。

观察了一下开发板,CPLD的接线为8根数据线,五根地址线,空间0、1共用的片选线,还有R/W读写信号线,WE写使能信号线,RD读使能信号线。

对XINTF空间的操作分为以下三个部分,引导、激活、跟踪。

EVMF2812用户使用手册

Techv- TMS320F2812评估板使用说明书北京精仪达盛科技有限公司2007.02.01*本公司保留对此说明书最终解释权,如有更改恕不另行通知*版权所有,严禁非法复制、传播北京精仪达盛科技有限公司 2007.01 version 2.0目录第一章TMS320F2812EVM评估板介绍 (1)1.1 F2812EVM概述 (2)1.2 F2812EVM主要功能 (2)1.3 F2812EVM功能框图 (4)第二章TMS320LF2407EVM评估板接口说明 (5)2.1 F2812EVM组成 (6)2.2 F2812EVM模块介绍 (6)2.2.1 F2812EVM存储器接口 (9)2.2.2 用户开关和LED (11)2.2.3 晶振选择 (13)2.2.4 复位电路 (13)2.2.5 电源接口 (14)2.2.6 扩展总线........ . (15)2.2.7 JTAG接口 (19)2.2.8 板上串行通信接口 (20)2.2.9 CAN总线接口...... .. (20)2.2.10 AD变换单元 (21)2.2.11 CPLD模块 (22)第三章TMS320F2812EVM评估板测试软件说明 (28)北京精仪达盛科技有限公司 2007.01 version 2.0第一章TMS320F2812 EVM评估板介绍本章主要介绍TMS320F2812 EVM评估板的基本概况、主要特点、评估板功能以及功能框图等内容。

北京精仪达盛科技有限公司 2007.01 version 2.0 11.1 F2812EVM概况F2812EVM是一个独立的嵌入式应用板卡,用户可以通过它直接验证自己的算法,或在此基础上进行最终产品的集成或开发。

板卡上面丰富的资源能够满足大多数应用场合的需求。

高容量的存储器能够满足各种应用代码的调试。

完全的信号扩展式用户更方便进行二次开发。

该产品灵活方便的外部接口,可以作为工业控制特别是电机控制系统集成的配套产品。

第五章 TMS320F2812 片内外设模块

▲ 捕获单元

▲ 正交编码脉冲电路

事件管理器的功能如图P134( P135)所示。

4

事件管理器功能框图 (EVA)

Reset PIE

EV Control Registers / Logic

/

2

TCLKINA / TDIRA ADC Start

GP Timer 1 Compare

GP Timer 1

22

GP 连续增计数模式

(Used for Asymmetric PWM Waveforms)

This example: TxCON.3-2 = 00 (下溢时 TxCMPR重载) TxPR = 3 无延迟计数 TxCMPR = 1 (initially) 计数值= TxPR+1 Prescale = 1

▲ 来自CPU的内部高速外设 时钟 HSPCLK ▲ 外部时钟TCLKINA/B ▲ 方向输入TDIRA/B ▲ 复位信号RESET

输 出

▲ 比较输出TxCMP, 输出pwm 波 ▲ ADC转换启动信号 ▲ 提供上溢、下溢、比较匹 配和周期匹配信号 ▲ 计数方向标识位

第5.1节 事件管理器(EV)

▲ 连续增计数模式 在产生周期匹配的下一个CPU时钟周期后,周期中断被置 位,产生一个中断请求,也可作ADC转换启动信号。定时

器变成0的一个CPU时钟周期之后,定时器的下溢中断标志

被置位,也可发出一个ADC启动信号。 定时器计数到FFFFh后,定时器的上溢中断标志在一 个 CPU时钟周期之后被置位。 定时器初值可以是0000h-FFFFh之间的任何值。

9

●

每个通用定时器包括:

① 一个16位可读/写的定时器计数器TxCNT(x=1, 2, 3, 4)。

TMS320F2812中文手册

TMS320F2812中文手册第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

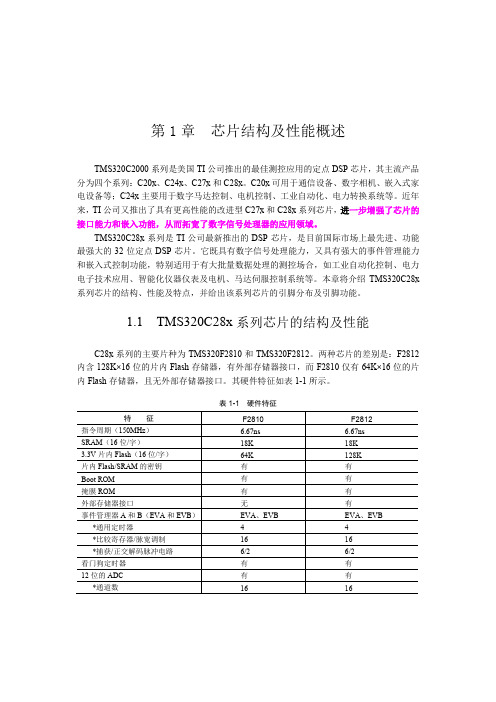

1.1 TMS320C28x 系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征特征 F2810 F2812 指令周期(150MHz) 6.67ns 6.67ns SRAM(16位/字)18K 18K 3.3V片内Flash(16位/字) 64K 128K 片内Flash/SRAM的密钥有有有有 Boot ROM掩膜ROM 有有外部存储器接口无有事件管理器A和B(EVA和EVB)EVA、EVB EVA、EVB*通用定时器 4 4*比较寄存器/脉宽调制 16 16*捕获/正交解码脉冲电路 6/2 6/2 看门狗定时器有有 12位的ADC 有有*通道数 16 16TMS320C28x系列DSP的CPU与外设(上) ?2?续表特征 F2810 F2812 32位的CPU定时器 3 3 串行外围接口有有串行通信接口(SCI)A和B SCIA、SCIB SCIA、SCIB 控制器局域网络有有多通道缓冲串行接口有有数字输入/输出引脚(共享)有有外部中断源 3 3 核心电压1.8V 核心电压1.8V 供电电压 I/O电压3.3V I/O电压3.3V 封装128针PBK 179针GHH,176针PGF 温度选择‡ A:-40? ~ +85? PGF和GHH PBK S:-40? ~ +125? 仅适用于TMS 仅适用于TMS 产品状况‡‡产品预览(PP) AI AI 高级信息(AI)(TMP)‡‡‡ (TMP)‡‡‡ 产品数据(PD)注:‡ “S”是温度选择(-40? ~ +125?)的特征化数据,仅对TMS是适用的。

TMS320F2812芯片介绍

TMS320F2812芯片介绍1 TMS320F2812芯片的特点 (1)2 F2812内核组成 (4)3 F2812外设介绍 (5)①事件管理器 (6)②模数转换模块 (6)③SPI和SCI通信接口 (6)④CAN总线通信模块 (7)⑤看门狗 (7)⑥通用目的数字量I/O (7)⑦PLL时钟模块 (7)⑧多通道缓冲串口 (7)⑨外部中断接口 (8)⑩JTAG (8)1 TMS320F2812芯片的特点TMS320F2812是TI公司推出的低价钱、高性能的32位定点DSP数字信号处置器,是到目前为止用于数字控制领域性能最好的DSP芯片。

它是在TMS320C28x为内核的基础上扩展了相应的存储器并集成了大量的片内外设而成的新一代适用于工业控制的DSP芯片。

图9为F2812控制器方框图。

图9 F2812控制器方框图TMS320F2812 系统组成包括:150MHz、150MIPS的低电压3.3VCPU、片内存储器、中断管理模块、事件管理器模块、片内集成外围设备。

TMS320F2812的体系结构采用4级流水线技术,加速程序的执行。

32位的CPU 内核提供了壮大的数据处置能力, 最高速度可达150MIPS,能够在单个指令周期内完成32*32位的乘累加运算。

TMS320F2812采用增强的哈佛结构,芯片内部具有6 条32位总线, 程序存储器总线和数据存储器总线彼此独立, 支持并行的程序和操作数寻址, 因此CPU的读/写可在同一周期内进行。

这种高速运算能力使各类复杂控制算法得以实现。

芯片本身具有128KB的Flash,外部RAM 能够按照需要进行扩充。

另外,它还具有高性能的12位模/数转换能力,改良的通信接口和1MB的线性地址空间。

外设模块丰硕且功能壮大,其中包括:事件管理器EV A和EVB,包括16个PWM输出,10个16位比较器和4个通用按时器;快速灵活的12位,16通道ADC,12.5MPS数据吞吐率;及其它丰硕的片内集成外设:2通道的SCI模块、SPI模块、eCAN2.0B模块、McBSP模块等。

F2812主要功能简介-事件管理器

tactive (2 TxPR-TxCMPRup -TxCMPRdn )T定标输入时钟周期

TxCMPRup=0,TxCMPRdn≠0

tactive (2 TxPR-TxCMPRdn )T定标输入时钟周期

TxCMPRup=0,TxCMPRdn=0

tactive 2 TxPR T定标输入时钟周期

TxCMPRup﹥TxPR,TxCMPRdn﹥TxPR

tactive 0

35

GP Timer 复位状态

任何RESET事件发生时,都产生下列结果

计数方向位 = 1 其它所有定时器寄存器的位 = 0,定时器被禁止 所有中断标志位 = 0 功率保护中断屏蔽位 = 1,开放 其它所有中断屏蔽位 = 0 定时器比较输出被置高阻

内部/外部时钟输入,可编程分频,方向可引脚控制

4种可屏蔽中断:上溢、下溢、比较、周期

全比较单元 Full-Compare Units

3 x 2 个独立的比较单元,每个有6个比较输出

配合可编程死区发生器,产生PWM波形

可编程死区发生器 Programmable Deadband

Generation

为什么要设计6个PWM输出?

3个4位计数器,1个16位比较寄存器,死区值可编程

PWM波形发生器 PWM Waveform Generation

共可产生8个PWM波形输出

捕获单元 Capture Units

EVA:CAP1/2/3,EVB:CAP4/5/6,上/下边沿触发

3个16位 2-level-deep FIFO堆栈

不变

高 低 低 高 立即高 立即低

31

PWM输出逻辑

3.1 F2812主要功能简介-系统控制和中断

F2812主要功能简介 3 F2812主要功能简介 3-1 1 系统控制和中断 F2812的存储器 F2812的存储器

问题

F2812有哪些片上存储器 有哪些片上存储器? 1 F2812有哪些片上存储器? 2 各有多少?地址如何分布? 各有多少?地址如何分布?

Flash & OTP Flash on-chip (F2812) on128K x 16bit, 0x3D 8000 – 0x3F 7FFF always enabled, program & data space Multiple sectors Code security Low power modes Wait states can be adjusted based on CPU frequency Flash pipeline mode improve performance

Lowest power CPU read or fetch, active or read state

Standby State

CPU read or fetch, active or read state

Active or Read State

Highest power Prefetch mechanism

问题

密码存储在哪里? 1 密码存储在哪里? 2 地址多少? 地址多少?

CSM Functional Description

代码安全密码区 (PWL):

0x3F 7FF8 – 0x3F 7FFF 中有用户烧写, Flash 中有用户烧写,更改需知道旧密码 OTP 中 TI 公司一次性烧写

PWL全为 PWL全为 1: PWL全为 PWL全为 0:

FBANKWAIT, FBANKWAIT, Flash Waitstate Register

F2812中文手册

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x 系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征注:‡“S”是温度选择(-40℃~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

F2812 DEMO 板 说明书

F2812 DEMO板使用说明书F2812 DEMO板是为学习、熟悉TMS320F2812芯片而开发的演示板。

一.F2812 DEMO板上的资源:1. TMS320F2812●静态CMOS、主频可达150MHz、低功耗(核电压1.8V、I/O电压3.3V);●128K×16位片上FLASH、18K×16位片上SRAM、4K×16位片上ROM;●外部存储空间接口:最多可达1M×16位、提供3个独立的片选信号、读/写时序可编程●动态PLL,主频可由软件编程修改、片上看门狗电路●3个外部中断源●外设中断扩展模块,最多支持45个外部中断●具有加密功能,密钥长度128位●3个32位CPU定时器●用于电机控制的外设:2个事件管理器(与C240x器件兼容)●多种标准串口外设:1个SPI同步串口、2个UART异步串口、1个增强型CAN总线接口、1个McBSP同步串口●12位A/D转换器:16通道、双采/保、2×8多路切换器●56个独立可编程、复用型、通用I/O口2.电源采用TPS767D318,将外部提供的+5VDC转换为TMS320F2812所需的+3.3VDC和+1.8VDC。

3.时钟板上提供30MHz晶振,由软件将PLLCR寄存器设置为1010,系统时钟为外部时钟的5倍频,即系统时钟为150MHz。

PLLCR寄存器参看《TMS320F28x Control and Interrupts Peripheral Reference Guide》。

4. JTAG仿真接口SEED-XDS仿真器与JTAG仿真接口相联,即可对TMS320F2812进行仿真、调试。

5. MP/MC方式设置板上J3跳针用于设置MP/MC方式,当跳针开路时为MC方式,短路时为MP方式。

6. TMS320F2812引脚F2812 DEMO板上已将TMS320F2812上的所有引脚引至对应的焊盘,并将引脚名标在相应的焊盘处,以便用户作简单的实验。

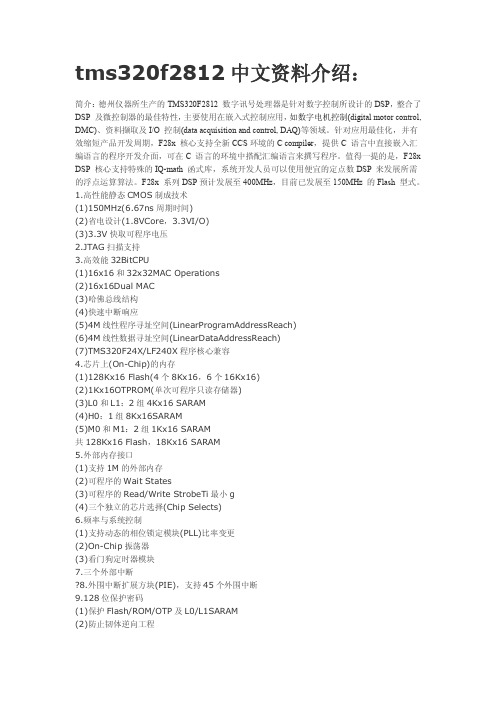

TMS320f2812中文资料

tms320f2812中文资料介绍:简介:德州仪器所生产的TMS320F2812 数字讯号处理器是针对数字控制所设计的DSP,整合了DSP 及微控制器的最佳特性,主要使用在嵌入式控制应用,如数字电机控制(digital motor control, DMC)、资料撷取及I/O 控制(data acquisition and control, DAQ)等领域。

针对应用最佳化,并有效缩短产品开发周期,F28x 核心支持全新CCS环境的C compiler,提供C 语言中直接嵌入汇编语言的程序开发介面,可在C 语言的环境中搭配汇编语言来撰写程序。

值得一提的是,F28x DSP 核心支持特殊的IQ-math 函式库,系统开发人员可以使用便宜的定点数DSP 来发展所需的浮点运算算法。

F28x 系列DSP预计发展至400MHz,目前已发展至150MHz 的Flash 型式。

1.高性能静态CMOS制成技术(1)150MHz(6.67ns周期时间)(2)省电设计(1.8VCore,3.3VI/O)(3)3.3V快取可程序电压2.JTAG扫描支持3.高效能32BitCPU(1)16x16和32x32MAC Operations(2)16x16Dual MAC(3)哈佛总线结构(4)快速中断响应(5)4M线性程序寻址空间(LinearProgramAddressReach)(6)4M线性数据寻址空间(LinearDataAddressReach)(7)TMS320F24X/LF240X程序核心兼容4.芯片上(On-Chip)的内存(1)128Kx16 Flash(4个8Kx16,6个16Kx16)(2)1Kx16OTPROM(单次可程序只读存储器)(3)L0和L1:2组4Kx16 SARAM(4)H0:1组8Kx16SARAM(5)M0和M1:2组1Kx16 SARAM共128Kx16 Flash,18Kx16 SARAM5.外部内存接口(1)支持1M的外部内存(2)可程序的Wait States(3)可程序的Read/Write StrobeTi最小g(4)三个独立的芯片选择(Chip Selects)6.频率与系统控制(1)支持动态的相位锁定模块(PLL)比率变更(2)On-Chip振荡器(3)看门狗定时器模块7.三个外部中断?8.外围中断扩展方块(PIE),支持45个外围中断9.128位保护密码(1)保护Flash/ROM/OTP及L0/L1SARAM(2)防止韧体逆向工程10.三个32位CPU Timer11.电动机控制外围(1)两个事件管理模块(EVA,EVB)(2)与240xADSP相容12. (1)同步串行外围接口SPI模块(2)两个异步串行通讯接口SCI模块,标准UART(3)eCAN(Enhanced Controller Area Network)(4)McBSP With SPI Mode13.16个信道12位模拟-数字转换模块(ADC)(1)2x8通道的输入多任务(2)两个独立的取样-保持(Sample-and-Hold)电路(3)可单一或同步转换(4)快速的转换率:80ns/12.5MSPS图1TMS320F2812功能方块图。

TMS320F2812开发板 说明书

F2812的外部存储器接口XINTF的详细说明和编程操作请参考《TMS320F28X External Interface(XINTF) Reference Guid》 4. 外部扩ቤተ መጻሕፍቲ ባይዱ的控制/状态寄存器

开发板上配置有HOST USB接口,Ethernet接口,LCD接口,输入输出等控制 寄存器和状态寄存器等,它映射在F2812的Zone0 和 Zone1存储空间中,具体的 定义如下:

功能/名称 扩展的输出接口控制寄存器

寄存器 名称 OutRegs

发光二极管控制寄存器

LedRegs

网卡复位、485接收使能等控制寄存器

Led8Reg

键盘输入寄存器

KeyReg

扩展的输入接口控制寄存器

InReg

扩展的外部可屏蔽中断EXINT1—EXINT5状态寄存器 IFReg1

扩展的外部非屏蔽中断EXNMI1—EXNMI2状态寄存器 IFReg2

2.本板卡的平面图如下: 平面图上的标号和板卡的标号一一对应,详细的说明请看后面章节的说明。

第二章 入门

1. 1特点 采用32位定点DSP TMS320F2812(150M),方便电机控制,电力设备控制及工业控 制等。 片上存储器 FLASH 128K X 16位 SRAM 18K X 16位 BOOT ROM 4K X 16 位 OPT ROM 1K X 16位

IFReg2 LcdDat LcdCom AddrPort DataPort BaseAddr

0X0033FF Zone0 0X0039FE Zone0 0X0039FF Zone0 0x0035FE Zone0 0x0035FF Zone0 0x003700 Zone0

2位只读

F2812性能及引脚简介

74164工作时序图

程序设计 主程序主要包括系统初始化、中断向量初始化、设置 GPIO端口、控制数据传输几个步骤。

设置GPIO端口的配置函数 void Gpio_select(void) { EALLOW; GpioMuxRegs.GPBMUX.all=0x0000; GpioMuxRegs.GPBDIR.all=0xFFFF; GpioMuxRegs.GPFMUX.all=0x0000; GpioMuxRegs.GPFDIR.all=0xFFFF ; EDIS; }

• C28X系列主要芯片包括TMS320F2812和 TMS2810。二者差别:F2812内含128K*16位 的Flash存储器,有外部存储器接口,而 F2810仅有64K*16位的片内Flash存储器,且 无外部存储器接口。

C28X系列芯片主要性能

• • • • 主频150MHz(时钟周期6.67ns) CPU内核电压1.8V,I/O口电压3.3V Flash编程电压3.3V 高性能的32位CPU: 16位*16位和32位*32位乘且累加操作 16位*16位的两个乘且累加 哈佛总线结构 • 功能强大的外设

个15位的数字I/O口GPIOF。

• 通过使用GPIO的有关寄存器可以选择和控制这些 共享引脚的操作。例如:通过GPxMUX寄存器可

以把这些引脚作为数字I/O或片内外设I/O口。如果

选择某个引脚作为数字I/O口,则可以通过 GPxDIR寄存器来设置引脚的方向;另外,可以 通过GPxQUAL寄存器来改善输入信号,有效的 消除输入信号的毛刺脉冲的干扰。

看门狗功能的软件配置

// Disable watchdog module SysCtrlRegs.WDCR= 0x0068; • • • • • • • • • • • // This function resets the watchdog timer. // Enable this function for using KickDog in the application /* void KickDog(void) { EALLOW; SysCtrlRegs.WDKEY = 0x0055; SysCtrlRegs.WDKEY = 0x00AA; EDIS; } */

3.4 F2812主要功能简介-串行通信接口

问题

SCI多处理器通信

识别地址字节

空闲线模式:在地址字节前留一段静态空间

没有附加地址位,数据>10个,效率比地址位模式高 一般应用于典型的非多处理器的SCI通信

地址位模式:每个字节增加一个地址附加位

小块数据时更有效,数据块之间不需要等待 高速传送时,程序不可避免地要加入空闲位

问题

你认为静态空间如何设计?

Serial Communications Interface (SCI)

F2812的SCI

两根外部信号线引脚:SCITXD/SCIRXD 异步串行、标准非归零(NRZ)格式 16位波特率64K种可编程通信速率,增强型自动波特率检测硬件逻辑 数据格式灵活

接收数据出错检测 间断、奇偶、超时、帧错 2种多处理器唤醒模式 空闲线模式 地址位模式 半双工、全双工 双缓冲接收和发送 发送、接收独立的中断使能和中断位 增强型发送、接收16级FIFO 13个8位SCI模块控制寄存器 发送、接收可采用中断或状态标志位查询编程方式

SCI优先级控制寄存器,SCIPRI

详细解释参见手册或教材

SCI Registers (FIFO增强)

SCI FIFO发送寄存器,SCIFFTX

SCI FIFO接收寄存器,SCIFFRX

详细解释参见手册或教材

SCI Registers (FIFO增强)

SCI FIFO控制寄存器,SCIFFCT

数据传输:

空闲线路多处理器模式、地址位多处理器模式

提供了与流行外设接口的通用异步接收/发送(UART)模

式,只需两条钱与标准设备接口,如RS-232C格式的终 端和打印机,数据传送的字符包括:

DSP 2812中文手册

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x 系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征TMS320C28x系列DSP的CPU与外设(上)·2·注:‡“S”是温度选择(-40℃~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

1 TMS320F2812简介

1 TMS320F2812简介TMS320F2812是TI公司的一款用于控制的高性能、多功能、高性价比的32位定点DSP芯片。

该芯片兼容TMS320LF2407指令系统最高可在150MHz主频下工作,并带有18k×16位0等待周期片上SRAM和128k×16位片上FLASH(存取时间36ns)。

其片上外设主要包括2×8路12位ADC(最快80ns转换时间)、2路SCI、1路SPI、1路McBSP、1路eCAN等,并带有两个事件管理模块(EVA、EVB),分别包括6路PWM/CMP、2路QEP、3路CAP、2路16位定时器(或TxPWM/TxCMP)。

另外,该器件还有3个独立的32位CPU定时器,以及多达56个独立编程的GPIO引脚,可外扩大于1M×16位程序和数据存储器。

TMS320F2812采用哈佛总线结构,具有密码保护机制,可进行双16×16乘加和32×32乘加操作,因而可兼顾控制和快速运算的双重功能。

通过对TMS320F2812定点DSP芯片合理的系统配置和编程可实现快速运算,本文着重对此加以说明。

2 TMS320F2812基本系统配置2.1TMS320F2812时钟TMS320F2812的片上外设按输入时钟可分为如下4个组:(1)SYSOUTCLK组:包括CPU定时器和eCAN总线,可由PLLCR寄存器动态地修改;(2)OSCCLK组:主要是看门狗电路,由WDCR寄存器设置分频系数;(3)低速组:有SCI、SPI、McBSP,可由LOSPCP寄存器设置分频系数;(4)高速组:包括EVA/B、ADC,可由HISPCP寄存器设置分频系数。

为了使系统具有较快的工作速度,除了定时器和SCI等少数需要低速时钟的地方,其它外设均可以150MHz时钟工作。

图12.2存储空间图1所示是TMS320F2812的内部存储空间映射图。

TMS320F2812为哈佛(Harvard)结构的DSP,即在同一个时钟周期内可同时进行一次取指令、读数据和写数据的操作。

MEMORY存储芯片TMS320F2812ZHHA中文规格书

59TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Configuration Copyright ©2008–2014,Texas Instruments Incorporated 4.3Pullup/Pulldown ResistorsProper board design should ensure that input pins to the device always be at a valid logic level and not floating.This may be achieved via pullup/pulldown resistors.The device features internal pullup (IPU)and internal pulldown (IPD)resistors on most pins to eliminate the need,unless otherwise noted,for external pullup/pulldown resistors.An external pullup/pulldown resistor needs to be used in the following situations:•Boot and Configuration Pins:If the pin is both routed out and 3-stated (not driven),an external pullup/pulldown resistor is strongly recommended,even if the IPU/IPD matches the desired value/state.•Other Input Pins:If the IPU/IPD does not match the desired value/state,use an external pullup/pulldown resistor to pull the signal to the opposite rail.For the boot and configuration pins,if they are both routed out and 3-stated (not driven),it is strongly recommended that an external pullup/pulldown resistor be implemented.Although,internal pullup/pulldown resistors exist on these pins and they may match the desired configuration value,providing external connectivity can help ensure that valid logic levels are latched on these device boot and configuration pins.In addition,applying external pullup/pulldown resistors on the boot and configuration pins adds convenience to the user in debugging and flexibility in switching operating modes.Tips for choosing an external pullup/pulldown resistor:•Consider the total amount of current that may pass through the pullup or pulldown resistor.Make sure to include the leakage currents of all the devices connected to the net,as well as any internal pullup or pulldown resistors.•Decide a target value for the net.For a pulldown resistor,this should be below the lowest V IL level of all inputs connected to the net.For a pullup resistor,this should be above the highest V IH level of all inputs on the net.A reasonable choice would be to target the V OL or V OH levels for the logic family of the limiting device;which,by definition,have margin to the V IL and V IH levels.•Select a pullup/pulldown resistor with the largest possible value;but,which can still ensure that the net will reach the target pulled value when maximum current from all devices on the net is flowing through the resistor.The current to be considered includes leakage current plus,any other internal and external pullup/pulldown resistors on the net.•For bidirectional nets,there is an additional consideration which sets a lower limit on the resistance value of the external resistor.Verify that the resistance is small enough that the weakest output buffer can drive the net to the opposite logic level (including margin).•Remember to include tolerances when selecting the resistor value.•For pullup resistors,also remember to include tolerances on the IO supply rail.•For most systems,a 1-k Ωresistor can be used to oppose the IPU/IPD while meeting the above ers should confirm this resistor value is correct for their specific application.•For most systems,a 20-k Ωresistor can be used to compliment the IPU/IPD on the boot and configuration pins while meeting the above ers should confirm this resistor value is correct for their specific application.•For more detailed information on input current (I I ),and the low-/high-level input voltages (V IL and V IH )for the device,see Section 5.3,Recommended Operating Conditions.•For the internal pullup/pulldown resistors for all device pins,see the peripheral/system-specific terminal functions table.60TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Operating Conditions Copyright ©2008–2014,Texas Instruments Incorporated(1)Stresses beyond those listed under "absolute maximum ratings"may cause permanent damage to the device.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)All voltage values are with respect to VSS,PLL0_VSSA,OSCVSS,RTC_VSS (3)Up to a max of 24hours.5Device Operating Conditions5.1Absolute Maximum Ratings Over Operating Case Temperature Range (Unless Otherwise Noted)(1)Supply voltage ranges Core(CVDD,RVDD,RTC_CVDD,PLL0_VDDA )(2)-0.5V to 1.4V I/O,1.8V(USB0_VDDA18,USB1_VDDA18)(2)-0.5V to 2VI/O,3.3V (DVDD,USB0_VDDA33,USB1_VDDA33)(2)-0.5V to 3.8VInput voltage ranges V I I/O,1.2V (OSCIN,RTC_XI)-0.3V to CVDD +0.3VV I I/O,3.3V (Steady State)-0.3V to DVDD +0.35VV I I/O,3.3V (Transient)DVDD +20%up to 20%of SignalPeriodV I I/O,USB 5V Tolerant Pins:(USB0_DM,USB0_DP,USB0_ID,USB1_DM,USB1_DP) 5.25V (3)V I I/O,USB0VBUS 5.50V (3)Output voltage ranges V O I/O,3.3V (Steady State)-0.5V to DVDD +0.3VV O I/O,3.3V (Transient Overshoot/Undershoot)20%of DVDD for up to20%of the signal periodClamp Current Input or Output Voltages 0.3V above or below their respective powerrails.Limit clamp current that flows through the I/O's internal diodeprotection cells.±20mA Operating Junction Temperature ranges,T J Commercial0°C to 90°C Industrial (D suffix )-40°C to 90°C Extended (A suffix)-40°C to 105°C Automotive (T suffix)-40°C to 125°C (1)Electrostatic discharge (ESD)to measure device sensitivity/immunity to damage caused by electrostatic discharges into the device.(2)Level listed above is the passing level per ANSI/ESDA/JEDEC JS-001-2010.JEDEC document JEP155states that 500V HBM allows safe manufacturing with a standard ESD control process,and manufacturing with less than 500V HBM is possible if necessary precautions are taken.Pins listed as 1000V may actually have higher performance.(3)Level listed above is the passing level per EIA-JEDEC JESD22-C101E.JEDEC document JEP157states that 250V CDM allows safemanufacturing with a standard ESD control process.Pins listed as 250V may actually have higher performance.5.2Handling RatingsUNITStorage temperature range,T stg (default)-55to 150°C ESD Stress Voltage,V ESD (1)Human Body Model (HBM)(2)>2000V Charged Device Model (CDM)(3)>500V。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

07/25/03 1ADVANCED ANALOG RADIATION TOLERANTDC/DC CONVERTERSDescriptionn 12 Watts Output Powern Available in ±5, ±12 and ±15 Volt Outputs n 16 - 40 VDC Input Range (28 VDC Nominal)n Low Input/Output Noisen Total Ionizing Dose > 30KRads (Si)n No SEE to LET > 60 MeV-cm 2/mg n -55°C to +125°C Operating Range n Indefinite Short Circuit Protection n Flexible Mounting n High Power Densityn Fully Isolated - Input to Output and to Case n Complimentary EMI Filter Available n Externally Synchronizablen Electrical Performance Similar to AHF28XXD SeriesFeaturesAMF28V Input, Dual OutputThe AMF28XXD has been designed for high density using chip and wire hybrid technology that complies with the class H requirements of MIL-PRF-38534. Fin-ished product are fabricated in a facility fully qualified to MIL-PRF-38534. The standard processing adopted for the AMF28XXD meets the requirements of MIL-PRF-38534 for class H but with enhanced screening steps and includes element evaluation. Applicable generic lot qualification test data including radiation perfor-mance can be made available on request. Consult Advanced Analog for special requirements.AMF28XXD SERIESThe AMF28XXD series of DC/DC converter modules has been specifically designed for operation in moder-ate radiation environments supplementing the higher radiation performance available in the Advanced Ana-log ART2815T converter series. Environments pre-sented to space vehicles operating in low earth orbits,launch boosters, orbiting space stations and similar applications requiring a low power, high performance converter with moderate radiation hardness perfor-mance will be optimally served by the AMF28XXD se-ries.PD - 94688The physical configuration of the AMF28XXD series permits mounting directly to a heat conduction surface without the necessity of signal leads penetrating the heat sink surface. This package configuration permits greater independence in mounting and more mechani-cal security than traditional packages. Advanced Analog’s rugged ceramic seal pins are used exclusively in the package thereby assuring long term hermeticity.AMF28XXD SeriesSpecificationsFor Notes to Specifications, refer to page 5Static Characteristics -55°C ≤ T CASE ≤ +125°C, V IN =28 V DC ±5%, C L =0, unless otherwise specified.ParameterGroup A SubgroupsTest Conditions Min NomMaxUnitInput Voltage16 28 40 V Output Voltage AMF2805D AMF2812D AMF2815D AMF2805D AMF2812DAMF2815D1 1 1 2, 3 2, 3 2, 3 Vin = 28 Volts, 10% load on both outputs±4.95 ±11.88 ±14.85±4.90 ±11.76 ±14.70 ±5.00 ±12.00 ±15.00±5.05 ±12.12 ±15.15±5.10 ±12.24 ±15.30 V V V V V V Output Current1, 2AMF2805D AMF2812DAMF2815D1, 2, 3 1, 2, 3 1, 2, 3 Vin = 16, 28, 40 Volts each output each output each output240 100 80 2160 900 720 mA mA mA Output Power 1, 2AMF2805D AMF2812DAMF2815D1, 2, 3 1, 2, 3 1, 2, 3 Vin = 28 Volts, 100% load12 12 12 W W W Output Ripple Voltage 1, 3AMF2805D AMF2812D AMF2815D 1, 2, 3 1, 2, 3 1, 2, 3 Vin = 16, 28, 40 Volts, 100% load,BW = 20 Hz to 2 MHz25 25 2560 60 60mV PP mV PP mV PP Output voltage Regulation3 LineAMF2805D AMF2812D AMF2815D LoadAMF2805D AMF2805DAMF2805D1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3V in = 16, 28, 40 VoltsIout = 10, 50%, and 100% load±10 ±10 ±10±10 ±10 ±10±25 ±50 ±50 ±50 ±50 ±50mV mV mVmV mV mVAbsolute Maximum RatingsInput Voltage Range -0.5V to +50VDC Soldering Temperature 300°C for 10 seconds Storage Case Temperature 65°C to +135°CRecommmended Operating ConditionsInput Voltage Range +16V to +40VDC Output Power Less than or equal to 12W Operating Case Temperature -55°C to +125°C3AMF28XXD SeriesStatic Characteristics (Continued) -55°C ≤ T CASE ≤ +125°C, V IN =28 V DC ±5%, C L =0, unless otherwise specified.For Notes to Specifications, refer to page 5ParameterGroup A SubgroupsTest ConditionsMin Nom Max Unit Cross Regulation5AMF2805D AMF2812D AMF2815D 1, 2, 3 1, 2, 3 1, 2, 3 Minimum 1.0 watt on both outputs 10%-90% load10 3 3% % % Input CurrentNo Load AMF2805D AMF2812D AMF2815D Inhibit AMF2805D AMF2812DAMF2815D1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 Vin=28V,Iout=0, Inhibit (pin 1)=openInhibit (pin 1) shorted to input return (pin 7)35 35 35 8 8 8 60 60 60 12 12 12 mA mA mA mA mA mA Input Ripple Current 3AMF2805D AMF2812D AMF2815D 1, 2, 3 1, 2, 3 1, 2, 3Vin = 16, 28, 40 Volts, 100% load, BW = 20 Hz to 2 MHz20 20 2050 50 50 mA PP mA PP mA PP Efficiency 3AMF2805D AMF2812D AMF2815D AMF2805D AMF2812DAMF2815D1, 3 1, 3 1, 3 2 2 2 100% load76 77 78 72 74 74% % % % % %Isolation1 Input to output or any pin to case (except pin 6) at 500Vdc 100 M Ω Capacitive Load 5, 6AMF2805D AMF2812DAMF2815D4No effect on dc performance, total for both outputs500 200 200µF µF µF Short Circuit Power Dissipation 1, 2, 36 watts MTBF MIL-HDBK-217F, SF @ Tc=35°C 750 Khrs Weight36gAMF28XXD SeriesDynamic Characteristics -55°C ≤ T CASE ≤ +125°C, V IN =28 V DC ±5%, C L =0, unless otherwise specified.For Notes to Specifications, refer to page 5ParameterGroup A SubgroupsTest Conditions Min Nom Max Unit Short Circuit Recovery 6AMF2805D AMF2812DAMF2815D4, 5, 6 4, 5, 6 4, 5, 60% load to 100% Load25 25 25 ms ms ms Switching Frequency 34, 5, 6 100% load 500 550 600 KHz Synchronization Input 3Frequency Range Pulse Amplitude, Hi 6 Pulse Amplitude, Lo 6Pulse Rise time 6Pulse Duty Cycle 64, 5, 6500 2.5 -0.5 20700 10 0.8 100 80 KHz V V ns %Output Response To Step TransientLoad Changes 3, 74, 5, 6 4, 5, 6Load step 50%ó100%Load step 10% ó 50% -200 --800+200 +800mV pk mV pk Recovery Time, Step Transient LoadChanges 3, 7, 84, 5, 6 4, 5, 6Load step 50%ó100%Load step 10% ó50% 70 2000µs µs Output Response Transient Step Line Changes 3, 6, 9 AMF2805D AMF2812D AMF2815D 4, 5, 6 4, 5, 6 4, 5, 6 Input step 16ó 40Vdc, 100% Load-450 -750 -750+450 +750 +750 mV pk mV pk mV pk Recovery Time Transient Step Line Changes 3, 6, 94, 5, 6 Input step 16 ó 40Vdc, 100% load1200 µs Turn On Overshoot 3, 10 All AMF2805D AMF2812D AMF2815D 4, 5, 6 4, 5, 6 4, 5, 6 4, 5, 60% load100% load600400 300 300 mV pk mV pk mV pk mV pk Turn On Delay 3, 104, 5, 60% load to 100% load25ms5AMF28XXD SeriesAMF28XXD Block DiagramApplication InformationInhibit FunctionEMI FilterDevice SynchronizationNotes to SpecificationsAn optional EMI filter is available (AFH461) that will reduce the input ripple current to levels below the limits imposed by MIL-STD-461 CE03.When multiple DC/DC converters are utilized in a single system, significant low frequency noise may be generated due to a small difference in the switch-ing frequency of the converters (beat frequency noise). Because of the low frequency nature of this noise (typically less than 10 KHz), it is difficult to filter out and may interfere with proper operation of sensitive systems (communication, radar or telem-etry). Advanced Analog provides synchronization of multiple AMF type converters to match switching frequency of the converter to the frequency of the system clock, thus eliminating this type of noise.outeturnoutConnecting the enable input (Pin 1) to input common (Pin 7) will cause the converter to shut down. It is recommended that the enable pin be driven by an open collector device capable of sinking at least 400µA of current. If the user chooses not to use the inhibit function, it may be left open and the converter will function normally. Because it is internally pulled up,the open circuit voltage of the inhibit input is 10.0+1V DC.1. Applicable to positive and negative outputs.2. Maximum combined output is 12 watts. 10.8 watts (max.) is available from either output (90%).3. Load current split equally between +V OUT and V OUT .4. 1.2 watt load on output under test, 1.2 watt to 10.8 watt load change on other output.5.Capacitive value may be any value from 0 to the maximum limit without compromising DC performance. Acapacitive load in excess of the maximum limit will not disturb loop stability but may interfere with the operation of the load fault detection circuitry, appearing as a short circuit during turn-on.6. Parameter shall be tested as part of design characterization and after design or process changes. Thereafter,parameters shall be guaranteed to the limit specified.7. Load step transition time between 2 and 10 microseconds.8. Recovery time is measured from initiation of the transient to where V out has returned to within ±1% of V out at50% load.9. Input step transient time between 1 and 10 microseconds.10. Turn-on delay time measurement is for either a step application of power at the input or the removal of a groundsignal from the inhibit pin while power is applied to the input.AMF28XXD SeriesStandard Process Screening for AMF28XXD SeriesRadiation SpecificationParameter Condition Min Typ Max UnitTotal Ionizing Dose MIL-STD-883, Method 1019.4Operating bias applied during exposure 30 KRads(Si)Heavy Ion (Single event effects) BNL Dual Van de Graf Generator 60 MeV •cm2/mgRequirement MIL-STD-883 Method CH+ LimitsTemperature Range -55°C to +125°C Element Evaluation MIL-PRF-38534 Internal Visual 2017 Yes Temperature Cycle 1010 Condition C Constant Acceleration 2001 Condition A, (3000g) PIND 2020 Condition ABurn-inInterim Electrical; @160 hrs 1015 320 hrs @ +125°C(2 x 160 hrs)Final Electrical (Group A) Read & Record Data MIL-PRF-38534& Specification-55°C, +25°C, +125°CPDA (25C, interim to final) 2% Radiographic Inspection 2012 YesFine & Gross 1014 Condition A, C External Visual 2009 Yes7AMF28XXD SeriesWORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, Tel: (310) 322 3331ADVANCED ANALOG: 2270 Martin Av., Santa Clara, California 95050, Tel: (408) 727-0500Visit us at for sales contact information .Data and specifications subject to change without notice. 07/03AMF28XXD Case OutlinePart NumberingPin DesignationPin No. Designation 1 Enable 2 Sync Input 3 Positive Output 4 Output Return 5 Negative Output 6 Case Ground 7 Input Return 8Positive InputAMF 28 05 D / EMModel Input Voltage28 = 28VOutputsS = Single D = DualOutput Voltage05 = ±5V,12 = ±12V,15 = ±15VScreeningBlank = Flight Model (CH+)/EM = Engineering Model。