基于SOPC的正弦信号源【课程设计】

单片机课程设计 正弦信号发生器 (嵌入式系统基础)

嵌入式系统基础课程设计题目:正弦信号发生器班级:通信0701姓名学号:同组人:一、设计题目正弦信号发生器二、设计要求1.功能要求(1)设计一个正弦信号发生器,可实现双极性输出,频率可变的正弦信号。

(2)可通过面板键盘控制输出频率。

(3)用LED数码管实时显示波形的相关参数。

2.参数要求(1)产生的正弦信号频率在范围在1Hz—1KHz之间。

(2)用键盘控制频率变化,最小步进为1KHz三、方案论证经查阅相关资料,实现正弦信号发生器的方法有很多,列举以下几种并分析:1.使用专用函数发生电路,如ICL8038 或MAX038,通过D/A转换调整函数发生器控制电压实现频率的控制,这种方案可以使频率连续可调,省却了波形转换电路,但控制电压与频率的变化不是严格的线性关系,如果不加频率负反馈则频率无法稳定准确,加上频率负反馈将使电路大大复杂,稳定度也会下降,而且如果要实现比较大的带宽,就需要不断更换振荡电容,电路复杂程度进一步增加。

调试困难,没有采用这种方案。

2.采用微处理器和数模转换器直接合成的数字式函数信号发生器。

这种信号发生器具有价格低,在低频范围内可靠性好,体积小,功耗低,使用方便等特点,它输出的频率是由微处理器向数模转换输出数据的频率和信号在一个周期内的采样点数(N)来决定的,因此受单片机的时钟频率的限制很大,如果单片机的晶振取12MHz,则单片机的工作频率为1MHz,若在一个周期内输出360个数据,则输出信号的频率理论上最高3.只能达到2777Hz。

实际上单片机完成一次数据访问并输出到D/A电路,至少要5个机器周期,因此实际输出信号的频率只有500Hz左右。

即使增大晶振频率,减小一个周期内输出数据个数,在稍高的频率下输出的波形频率误差也是很大的,而且计算烦琐,软件编程麻烦,控制不方便。

4.利用DSP处理器,根据幅值,频率参数,计算产生高精度的信号所需数据表,经数模转换后输出,形成需要的信号波形。

这种信号发生器可实现程控调幅,调频。

基于dsp的正弦波信号发生器课程设计

目录第1章绪论 (1)1 DSP简介 (1)第2章总体方案的分析和设计 (2)2.1 总体方案设计 (2)2.2正弦波信号发生器 (2)第3章硬件设计 (3)3.1硬件组成 (3)3.2控制器部分 (4)3.4人机接口部分 (5)第4章软件设计 (6)4.1流程图 (6)4.2 正弦信号发生器程序清单 (7)第5章总结 (12)参考文献 (12)第1章绪论1 DSP简介数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。

在过去的二十多年时间里,信号处理已经在通信等领域得到极为广泛的应用。

图一是数字信号处理系统的简化框图。

此系统先将模拟信号转换为数字信号,经数字信号处理后,再转换成模拟信号输出。

其中抗混叠滤波器的作用是将输入信号x (t)中高于折叠频率的分量滤除,以防止信号频谱的混叠。

随后,信号经采样和A/D 转换后,变成数字信号x(n)。

数字信号处理器对x(n)进行处理,得到输出数字信号y (n),经D/A转换器变成模拟信号。

此信号经低通滤波器,滤除不需要的高频分量,最后输出平滑的模拟信号y(t)。

图1.1数字信号处理系统简化框图数字信号处理是以众多学科为理论基础的,它所涉及的范围极其广泛。

例如,在数学领域,微积分、概率统计、随机过程、数值分析等都是数字信号处理的基本工具,与网络理论、信号与系统、控制论、通信理论、故障诊断等也密切相关。

近来新兴的一些学科,如人工智能、模式识别、神经网络等,都与数字信号处理密不可分。

可以说,数字信号处理是把许多经典的理论体系作为自己的理论基础,同时又使自己成为一系列新兴学科的理论基础。

第2章 总体方案的分析和设计2.1 总体方案设计1.基于DSP 的特点,本设计采用TMS320C54X 系列的DSP 作为正弦信号发生器的核心控制芯片。

基于DSP的正弦信号发生器

基于DSP的正弦信号发生器1.正弦信号在各种科学和工程领域中广泛应用,如通信系统、音频处理、医学诊断等。

因此,制作一个能够生成正弦信号的设备是非常必要的。

传统的方法是使用模拟电路,但这种方法需要用到很多电子元器件,难以控制和调整。

同时,传统的模拟电路还容易受到电磁干扰、温度等环境因素的影响,导致输出的信号失真。

因此,数字信号处理(DSP)技术逐渐成为生成正弦波信号的常见方法,能够实现高精度、低失真的输出。

2. 设计概述本文介绍一种基于DSP的正弦信号发生器的设计。

该设计采用TMS320C5505数字信号处理芯片和信号解调电路,通过软件和硬件设计,实现了一个高精度、低失真的正弦信号发生器。

2.1 硬件设计本设计采用了TMS320C5505数字信号处理器集成电路作为主控芯片。

该芯片具有低功耗、高性能、灵活性和易于开发等优点。

除此之外,还需要电源模块、时钟模块、信号解调模块等。

2.2 软件设计本设计采用了C语言进行程序设计。

使用Code Composer Studio作为开发环境,将程序编译后烧录到芯片中。

代码的主要实现过程为:1.生成一个只包含一周期正弦波形的信号2.将该信号送入DA(Digital to Analog)转换器,使其变为模拟信号3.经过信号解调器后输出到外部接口信号的生成采用的是Taylor级数展开,可以实现高精度的波形生成。

信号解调电路主要是由低通滤波器、防干扰电路和放大电路等模块组成。

3. 实验结果经过实验测试,本设计输出的正弦波信号的频率可以在0~10kHz范围内任意设定。

信号的失真率小于0.1%。

同时,本设计还支持正弦波的相位调节和幅度调节等功能。

通过外部的控制,可以实现信号的精准控制和调节。

4.本文介绍了一种基于DSP的正弦信号发生器的设计,通过使用数字信号处理技术,实现了高精度、低失真的正弦波信号的生成。

该设计具有灵活性和可扩展性,可以为各种科学和工程领域提供高精度的正弦信号源。

基于DSP的正弦信号发生器的设计

/(/A)低16位→d_xc

sinx

/调/ 用sinx程序

cosx

/调/ 用cosx程序

#d_sinx,DP /D/P←d_sinx

@d_sinx,16,A /A/=sin(x)

@d_cosx

/B/= sin(x)*cos(x)

B,1,*AR6+

/A/R6→2*sin(x)*cos(x)

*AR1+0

方

ST

A,*AR2 /(/ A)左移16位→AR2

||LD *AR4,B /(/ AR4)左移16位→B

MASR

*AR2+,*AR3+,B,A /从/ 累加器A中减去(AR2)

*(AR3)

MPYA

A

/操/ 作数与累加器A中高位相乘

STH

A,*AR2 /(/ A)高16位→AR2

MASR

*AR2-,*AR3+,B,A /从/ 累加器A中减去(AR2)

.text

定//义文本代码段

SSBX

FRCT

/F/RCT=1以清除冗余符号位

STM

#d_coef_c,AR5 /A/R5指向d_coef_c首地址

RPT

#3

重//复下条指令4次

MVPD

#table_c,*AR5+ /把/ table_c中的数复制到中

AR5

STM

#d_coef_c,AR3 /A/R3指向d_coef_c首地址

d_temp_c .usect "cos_vars",1 //为d_temp_c中cos_vars保存1个存储

单元

d_cosx .usect "cos_vars",1 //为d_cosx中cos_vars保存1个存储单

简易正弦信号发生器设计

简易正弦信号发生器设计

一、实验目的

1.进一步熟悉QuartusII及LPM-RAM宏模块与FPGA硬件资源的使用方法。

二、实验设备

计算机、和软件QuartusII和EDA/SOPC试验箱

三、试验内容

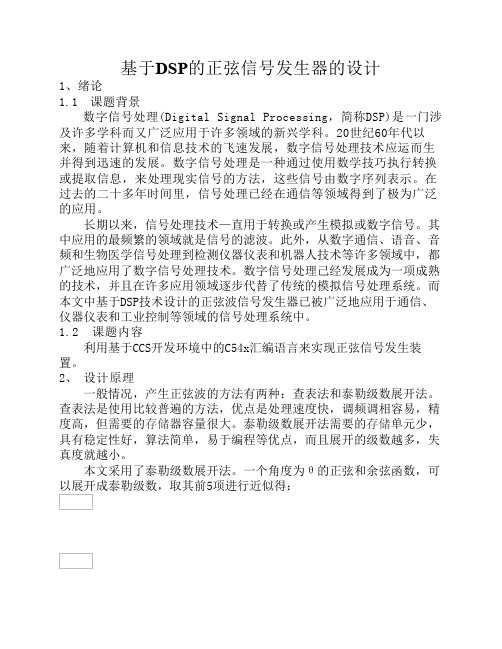

简易正弦信号发生器设计,要求ROM是8位数据线,8位地址线。

四、试验原理

打开QuartusII软件,在连接试验电路之前调入LPM-RAM-DQ宏模块,PLM-COUNER模块和74244芯片,再连接电路图,试验原理设计图如下:

图1-1键入64个正弦信号数据

图1-2简易正弦信号发生器顶层电路设计

五、实验结果

试验结果如下图:

图1-3综合后的RLT图

图1-4仿真波形图3.引脚锁定方案图

图1-5引脚锁定方案图

图1-6编程下载模式图

六、试验小节

一学期匆匆而过,通过大半学期的学习,我们学到了很多处理问题的技巧。

不过我们还要熟记很多单词,大多数的单词我们还不认识,相信通过进一步的学习,我们一定能学好这个软件。

我们也将以浓厚的兴趣和积极的态度去学习。

相信我们一定会有更加长足的进步。

基于PIC单片机的正交正弦信号发生器的设计

第5期(总第150期)2008年10月机械工程与自动化M ECHA N ICAL EN GI NEER IN G & AU T O M A T IO N N o.5O ct.文章编号:1672-6413(2008)05-0018-03基于PIC 单片机的正交正弦信号发生器的设计宋进红1,张晓丽1,2,张芳芳1(1.平顶山工学院计算机科学与工程系,河南 平顶山 467001; 2.南京航空航天大学智能材料与结构重点实验室,江苏 南京 210016)摘要:设计了一个基于PI C16F 877A 单片机和D DS 芯片A D9854的数字信号发生器,该信号发生器可以根据输入方波信号自动输出两路同频率的正交正弦信号;对P IC 16F 877A 和A D 9854的硬件实现方案及单片机的控制软件进行了详细的介绍。

所设计的数字信号发生器具有输出信号正交性好、频率稳定度高、可以自动跟踪输入方波信号的频率等特点。

关键词:P IC 单片机;正交;正弦信号发生器中图分类号:T P 368.1 文献标识码:A收稿日期:2008-04-01;修回日期:2008-04-20作者简介:宋进红(1967-),女,河南平顶山人,工程师,本科。

0 引言数字滤波器是数字信号处理中最广泛的一种线性系统环节,是数字信号处理的重要基础。

自适应滤波器因在设计时只需要很少的或者根本不需要任何关于信号和噪声的先验统计知识,且具有可以自动地调节自身的参数等特性而得到迅速发展[1]。

自适应数字滤波器的一个重要应用就是进行噪声抵消,即若信号中包含一频率为 0的正弦波干扰信号,则由自适应滤波器构成的自适应陷波器可以很好地消除这种干扰[2],而对其它频率成分的信号影响很小。

但是,这种数字滤波器需要两路与干扰信号同频率的正交正弦信号,对于恒定频率的干扰信号(例如50Hz 工频干扰信号),可以采用模拟电路做一个信号发生电路来提供参考源;而在有些特殊场合,干扰信号的频率并不是恒定不变的,这时若继续采用模拟电路做参考信号输入就变得很难实现。

数控正弦函数信号发生器-电子电路课程设计

39

第三章 单元电路设计--------------3.1 时基电路的设计 --------3.2 频率控制电路的设计 3.3 地址计数器的设计 -------------3.4 正弦函数表存储电路的设计-----3.5 数模转换电路的设计 -------------

36

3、设计电路并绘制电路图

(1)按照实验要求,绘制电路草图。 (2)必须绘制在规定的坐标纸上,必须用铅笔绘

制。 (3)集成电路必须采用CAD功能符号形式,不可

用管脚图。 (4)所有元件必须有标号。 (5)独立设计。

37

五、课程设计报告格式:

1、封面填写要求:

设计题目 数控正弦函数信号发生器

课程名称 电子电路课程设计

地址计数器产生256个地址依次从存储器 中取出正弦信号的样值。该样值经D/A(Ⅱ) 变换,输出一正弦波。幅度开关控制衰减电路 使幅度变化。放大电路可满足输出信号的幅度 及输出阻抗的要求。

14

可变256分频

基准电路 锁相环电路

256分频

正弦函数表

输出

D/AII

D/A I

幅度开关

15

2、频率控制电路

16

2.1时基电路的设计

• 首先选择4060振荡及分频芯片加上 3.2768MHz晶体经过8位分频产生 12.8KHz方波信号,再10分频产生 1.28KHz给PLL(锁相环)作为基准时钟。利 用PLL倍频功能产生2.56KHz至320KHz频 率方波。(N=2-255)

FPGA实验一、正弦信号发生器

河北大学 电子与信息工程学院 2010 张庆顺1 / 53SOPC 设计技术课程实验一、正弦信号发生器河北大学 电子信息工程学院教师:张庆顺本实验指导书演示了一个简单的正弦信号发生器在QUARTU S Ⅱ上的实现。

通过这个文档,旨在演示利用QUARTUS Ⅱ开发数字电路的基本流程和QUARTUS Ⅱ软件的相关操作,并借此介绍QUARUTS Ⅱ的软件界面。

我们还针对DE Ⅱ-70的实验板,实现了本文档所示硬件模块的相关配置工作以及下载和实现。

实验条件:Quartus II 9.1目录二、实验步骤: (6)1、工程创建 (6)2、sin信号发生器顶层模块的设计 (13)3、定制ROM存储sin波形数据 (17)3.1 建立.mif文件 (17)3.2 ROM数据的生成 (19)3.3 定制ROM元件 (19)3.3.1 调用Mega Wizard Plug-In Manager (20)3.3.2 设置LPM_ROM模块 (21)4、编译、综合等 (27)5、仿真 (28)5.1 编辑波形文件 (28)5.2进行仿真 (36)6、内部电路观察 (38)7、生成symbol (40)8、管脚分配 (46)9、下载 (49)10.作业 (53)一、设计原理:下图所示为正弦信号发生器的结构,共有4个部分组成:顶层文件singt.v 在FPGA 中实现两个部分:1、6位计数器产生地址信号;2、存储正弦信号(6bits 地址线,8bits 数据线)的ROM ,由LPM_ROM 模块实现,LPM_ROM 模块底层由FPGA 的EAB 、ESB 或M4K 来实现。

地址发生器的时钟频率CLK 假设为f0,这里我们设定的地址发生器为6bit ,则周期为26=64,所以一个正弦周期内可以采样64个点,DAC 后的输出频率f 为:64/0f f =我们可以如下生成sin 数据以用于查找表,双、单极性Sin(x)数据波形可如下:x = round((sin(linspace(0,2*pi,64))+1)*127.5);所要得到的单极性信号波形。

基于DSP的正弦信号发生器的设计

图1 程序流程图

4、 程序设计

4.1 产生正弦波程序清单sin.asm

.title "sin.asm" //为汇编文件取名为“sin.asm”

.mmregs

/定/ 义存储器映像寄存器

.def

_c_int00

.ref

sinx,d_xs,d_sinx,cosx,d_xc,d_cosx //定义标

号

sin_x: .usect "sin_x",360 //为"sin_x"保留360个存储空间

MPYA

*AR2+ /B/=x^2(1-x^2/30(1-x^2/56))

2(1-x^2/30(1-x^2/56))

||LD *AR4,B //B=1

MASR

*AR2-,*AR3+,B,A //A= 1-x^2/12(1-x^2/30(1-x^2/56))

SFTA

A,-1,A

NEG

A

MPYA

*AR2+ //B=1-x^2/2(1-x^2/12(1-x^2/30(1-x^2/56)))

STM

#d_xc,AR2

/A/R2 指向d_xc首地址

STM

#c_l_c,AR4 /A/R4指向c_l_c首地址

ST

#7FFFh,c_l_c /7/FFFh→c_l_c

SQUR

*AR2+,A

/求/ x的平方存放在累加器A中

ST

A,*AR2

/(/ A)左移16位→AR2

||LD *AR4,B

/(/ AR4)左移16位→B

d_temp_c .usect "cos_vars",1 //为d_temp_c中cos_vars保存1个存储

基于dsp的正弦波发生器课程设计概要

第1章 绪论1.1 DSP 简介数字信号处理(Digital Signal Processing ,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。

在过去的二十多年时间里,信号处理已经在通信等领域得到极为广泛的应用。

图一是数字信号处理系统的简化框图。

此系统先将模拟信号转换为数字信号,经数字信号处理后,再转换成模拟信号输出。

其中抗混叠滤波器的作用是将输入信号x (t)中高于折叠频率的分量滤除,以防止信号频谱的混叠。

随后,信号经采样和A/D 转换后,变成数字信号x(n)。

数字信号处理器对x(n)进行处理,得到输出数字信号y (n),经D/A 转换器变成模拟信号。

此信号经低通滤波器,滤除不需要的高频分量,最后输出平滑的模拟信号y(t)。

图1.1 数字信号处理系统简化框图数字信号处理是以众多学科为理论基础的,它所涉及的范围极其广泛。

例如,在数学领域,微积分、概率统计、随机过程、数值分析等都是数字信号处理的基本工具,与网络理论、信号与系统、控制论、通信理论、故障诊断等也密切相关。

近来新兴的一些学科,如人工智能、模式识别、神经网络等,都与数字信号处理密不可分。

可以说,数字信号处理是把许多经典的理论体系作为自己的理论基础,同时又使自己成为抗混叠 滤波器A/D数字信号处理D/A低通滤波器x(n)y(n) x(t)y(t)一系列新兴学科的理论基础。

1.2课题研究的目的意义科技的进步带动了DSP技术的发展,现代控制设备的性能和结构发生了巨大的变化,我们已经进入了高速发展的信息时代,DSP技术也成为当今科技的主流之一,被广泛地应用于生产的各个领域。

对于本次设计,其目的在于:(1) 了解DSP及DSP控制器的发展过程及其特点。

正弦信号电压采集课程设计

正弦信号电压采集课程设计一、课程目标知识目标:1. 学生理解正弦信号电压的基本概念,掌握正弦波的形成原理及其表达式。

2. 学生掌握使用电压采集模块对正弦信号电压进行采集的方法,了解相关的传感器工作原理。

3. 学生能够运用所学的数学知识,对采集到的正弦信号电压数据进行处理和分析。

技能目标:1. 学生能够正确连接电压采集模块,进行正弦信号电压的实时采集。

2. 学生能够运用数据采集软件进行数据记录,并能够对采集到的数据进行初步分析。

3. 学生通过实践操作,提高解决实际问题的能力,培养创新意识和团队合作精神。

情感态度价值观目标:1. 学生通过课程学习,增强对物理现象的观察力和好奇心,激发学习自然科学知识的兴趣。

2. 学生在学习过程中,培养严谨的科学态度和良好的实验习惯,提高安全意识。

3. 学生通过小组合作,培养沟通与协作能力,增强集体荣誉感。

课程性质:本课程为实践性较强的课程,结合理论知识与实际操作,使学生在动手实践的过程中深入理解正弦信号电压的相关知识。

学生特点:考虑到学生所在年级的特点,课程设计以直观、易懂、有趣为原则,注重培养学生的动手能力和实际应用能力。

教学要求:课程要求学生在掌握基本理论知识的基础上,通过实践操作,达到学以致用的目的。

教师需引导学生主动参与,关注个体差异,确保每位学生都能在课程中取得实际的学习成果。

二、教学内容本课程依据课程目标,结合课本相关章节,制定以下教学内容:1. 正弦波基本概念及表达式:讲解正弦波的定义,引导学生学习正弦波的数学表达式,了解其物理意义。

2. 正弦信号电压的产生:介绍正弦信号电压的产生原理,如振荡电路等,并分析其特点。

3. 电压采集模块及传感器:讲解电压采集模块的原理与使用方法,介绍常用的传感器及其工作原理。

4. 数据采集与处理:教授如何使用数据采集软件进行正弦信号电压的实时采集,并对采集到的数据进行处理和分析。

5. 实践操作:安排学生分组进行正弦信号电压的采集实验,培养学生的动手能力和团队协作精神。

正弦发生器课程设计

正弦发生器课程设计一、课程目标知识目标:1. 学生能理解正弦波的基本概念,掌握正弦波的发生原理。

2. 学生能够运用所学的电子元件和电路知识,设计并搭建一个简易的正弦发生器。

3. 学生能够解释正弦波在电子技术中的应用和意义。

技能目标:1. 学生能够运用所学的电路知识,进行电路分析和设计,具备实际操作能力。

2. 学生通过实践操作,提高动手能力,培养问题解决能力和团队合作能力。

情感态度价值观目标:1. 学生通过本课程的学习,培养对电子技术的兴趣和热情,激发创新思维。

2. 学生在学习过程中,树立正确的科学态度,严谨求实,勇于探索。

3. 学生在团队合作中,学会尊重他人,培养良好的沟通能力和团队协作精神。

课程性质分析:本课程属于电子技术领域,以实践操作为主,理论联系实际。

结合学生特点和教学要求,课程目标旨在培养学生的实际操作能力、问题解决能力和团队合作精神。

学生特点分析:学生为初中生,具备一定的电子元件知识和电路原理,但实践经验不足。

学生对新鲜事物充满好奇心,动手能力强,但注意力容易分散。

教学要求:1. 课程内容要紧密结合课本,注重实践操作,提高学生的实际操作能力。

2. 教学过程中,教师要以学生为主体,引导他们积极参与,培养问题解决能力和团队合作精神。

3. 教学评价要关注学生在知识、技能和情感态度价值观方面的具体表现,全面评估学生的学习成果。

二、教学内容根据课程目标,本章节教学内容主要包括以下几部分:1. 正弦波基本概念:- 正弦波的数学表达式- 正弦波的图形特征- 正弦波的应用领域2. 正弦发生器原理:- 正弦发生器的种类- 运算放大器在正弦发生器中的应用- 正弦波振荡电路的组成和原理3. 正弦发生器电路设计与搭建:- 电路元件的选择与应用- 电路图的绘制与分析- 搭建简易正弦发生器的步骤及注意事项4. 正弦波的应用实例:- 正弦波在通信领域的应用- 正弦波在音频设备中的应用- 正弦波在其他电子设备中的应用教学大纲安排如下:第一课时:1. 正弦波基本概念2. 正弦发生器原理第二课时:1. 正弦发生器电路设计与搭建2. 正弦波的应用实例教学内容与教材关联性:本教学内容紧密结合教材中关于正弦波及其发生器的内容,按照科学性和系统性进行组织,旨在帮助学生掌握正弦波基础知识,学会设计和搭建正弦发生器,并了解正弦波在实际应用中的重要性。

一种多功能信号源的SoPC解决方案

论文摘要:探讨了一种运用SoPC技术,将Nios系统、DDS 信号产生电路、等精度频率计电路嵌入到一块FPGA里,实现信号源的方案。

由于FPGA可重配置的特性,信号源可以根据需要随时对主要功能进行修改,不必更换硬件。

该信号源功能多,使用范围宽,精度高。

系统的主要功能都在一块芯片上,抗干扰能力强,功耗低,体积小。

论文关键词:等精度频率计,信号源1.引言信号源是电子系统设计、测试和实验中必备的工具。

数字化的信号源转换速度快,具有较高的频率分辨率,频率转换时间和相位连续,相对传统的模拟信号源有更多的优势。

实际应用系统中情况各不相同,专用信号源使用范围有限,不改变硬件电路但可以改变信号源功能和使用范围的新型信号源就有了需求。

SoPC(SystemOnaProgrammableChip)能够根据需要裁减或扩充功能,加上FPGA (FieldProgrammableGateArray)可重构的特点,可以满足上述要求。

SoPC是采用Nios可配置软核处理器和IP(IntellectualProperty)核在集成电路内搭建的系统,Nios负责系统控制和通讯,利用现有IP或者HDL语言实现其它主要的硬件部分。

该系统在一片FPGA上不仅嵌入了Nios软核MPU,还集成了DDS(DirectDigitalFrequencySynthesis)信号产生电路和等精度频率计,设计方式灵活、可靠性高,功能齐全,功耗比较低,适用于诸多领域。

2.系统总体设计和工作原理多功能信号源组成如图1所示。

SoPC主要由下面几个部分组成,Nios、AvalonBus、BootROM、Timer、外部接口、DDS信号产生电路、等精度频率计、通信、显示和键盘管理。

这里,我们着重对Nios的作用、DDS信号产生电路、等精度频率计进行了说明。

图1Nios系统组成图2.1Nios软核Nios是Altera公司的用户可配置嵌入式32位MPU软核,主要完成系统的管理、控制和人机对话。

SOPC课程设计

齐齐哈尔大学EDA设计题目数字频率计学院通信与电子工程学院专业班级通信071班学生姓名金守礼郭海龙陈金旭指导教师朱恒军成绩2010年7月10日摘要本实验描述了一个数字频率计的设计与实现,包括数字频率计前端信号的放大整形处理,数字频率计的VHDL 设计实现。

本实验以模块化的思想讲解了用VHDL 设计实现数字频率计的整个过程,包括模块的划分和相应模块的VHDL 设计实现。

重点是数字频率计的前端信号处理,数字频率计的VHDL设计与实现。

频率是电子测量中一个最为基本的参量,在信号发生器以及振荡器,各种倍频和分频电路的输出信号中,都要进行频率的测量。

如何能可靠又准确地测量信号频率是衡量频率计性能的一个很重要的指标。

随着可编程逻辑器件的发展与进步,采用可编程逻辑器件来实现频率计,使频率计测量频率的准确度大大提高,同时也是频率计的可靠性大大增加。

关键词:数字频率计 VHDL语言目录摘要 (2)第1章绪论 (4)1.1.VHDL简介 (4)1.1.1 VHDL概况 (4)1.1.2 VHDL语言的特点 (4)第2章数字频率计 (6)2.1 任务及模块 (6)2.1.1 设计任务及要求 (6)2.1.2 计数模块counter (6)2.1.3 门控模块gate-control (9)2.1.4 分频模块fdiv (11)2.1.5 寄存器模块flip-latch (14)2.1.6 多路选择模块data-mux (15)2.1.7 动态位选模块dispselect (16)2.1.8 BCD译码模块 (17)2.1.9 顶层电路TOP (21)2.2 利用软件Quartus2编译和仿真结果 (24)2.2.1 仿真波形 (24)2.2.2 RTl Viewer (rtl 级描述图) (25)2.2.3 程序编译(无错误) (25)结论 (26)参考文献 (27)致谢 (28)第1章绪论1.1.VHDL简介1.1.1 VHDL概况VHDL 的英文全名是 Very-High-Speed Integrated Circuit Hardware Description Language,诞生于 1982 年。

数控正弦函数信号发生器电工电子课程设计

目录第1章技术指标 (1)1.1 系统功能要求 (1)1.2 系统结构要求 (1)1.3 电气指标 (1)1.4 扩展指标 (1)1.5 附加指标 (1)1.6 设计条件 (1)1.6.1 电源条件 (1)1.6.2 可供选择的元器件范围 (1)第2章整体方案设计 (2)2.1 整体方案 (2)2.1.1 方案一 (2)2.1.2 方案二 (2)2.1.3 方案三 (2)2.1.4 方案比较 (3)2.2 整体方框图及原理 (3)2.2.1 整体方框图 (3)2.2.2 原理 (3)第3章单元电路设计 (5)3.1 基准信号电路设计 (5)3.2 频率合成器电路设计 (6)3.2.1 频率合成器的总体电路 (6)3.2.2 锁相电路设计 (6)3.2.3 频率控制电路设计 (7)3.3 地址计数器、存储器电路设计及函数表 (1)3.3.1地址计数器、存储器电路设计 (1)3.3.2正弦波、锯齿波、三角波和方波函数表 (1)3.4 D/A转换电路设计 (1)3.5 数字幅度控制电路设计 (1)3.6 输出阻抗电路设计 (1)3.7 整体电路图 (1)3.8 整体元件清单 (1)第4章测试与调整 (1)4.1 基准信号电路调测 (1)4.2 频率控制电路调测 (1)4.3 锁相电路调测 (1)4.4 地址计数器与存储器电路调测 (1)4.5 D/A转换电路调测 (1)4.6 数字幅度控制电路调测 (1)4.7 整体指标测试 (1)4.8 测试用仪器 (1)第5 章设计小节 (1)5.1 设计任务完成情况 (1)5.2 问题及改进 (1)5.3 心得体会 (1)参考文献 (1)附录一函数表的C语言程序 (1)附录二整体电路图 (1)附录三预习报告电路图 (1)附录四输出阻抗的有关解决方案 (1)附录五调测整体电路的常见问题及解决方法 (1)摘要本次电子电路课程设计所设计的数控正弦函数信号发生器,在面包板上装配完成之后,能产生出正弦波,其输出频率范围为15.625Hz~6KHz,通过开关能控制其输出频率,产生出所需要的正弦波频率,并能通过幅度控制开关控制其输出幅度。

正弦波信号源设计

选频网络 是从很宽的频率信号中选择出单一频率的 信号送到放大器的输入端,而将其他频率的信 号进行衰减。

LOGO

4

正弦波振荡电路

正弦波振荡器的基本原理

反馈信号代替了放大电路的输入信号

自激振荡的条件

Hale Waihona Puke 如何启振?文氏桥选频电路

频率特性曲线

整合后的电路

能自启动的电路

输出频率可调的电路

设计完成的电路

总结 正弦波振荡电路 是由放大电路和正反馈网络两部分组成的。 为了得到单一频率的正弦波,并且使振荡电路 稳定工作,电路中还应该包含选频网络和稳幅 环节。

logo即信号选频网络正弦波信号源设计设计流程正弦波振荡电路1文氏桥电路2整合后的电路及演示3总结4正弦波振荡电路?正弦波振荡器的基本原理反馈信号代替了放大电路的输入信号自激振荡的条件如何启振

LOGO

正弦波信号源设计

即信号选频网络

设计流程

1 2 3

正弦波振荡电路 文氏桥电路 整合后的电路及演示 总结

2019年基于sopc的正弦信号源课程.doc

目录摘要 (2)Abstract (3)1 绪论 (4)2设计任务与要求 (5)3 方案对比和论证确定 (5)4 电路工作原理分析 (6)4.1 MC8051 IP core原理 (6)4.2 DDS电路原理分析 (7)4.3 DA转换与放大电路原理分析 (8)5 软件设计及仿真 (9)5.1 MCU8051软核模块 (9)5.2 MCU8051控制程序设计 (9)5.3 DDS逻辑电路设计 (10)6 实物制作与硬件调试 (11)7总结 (12)参考文献 (13)基于SOPC的正弦信号源摘要本文应用altera的EP2C8TQ208,内建MCU8051 core,加上内建逻辑电路构成了单片信号源。

其中MCU8051完成按键扫描,显示控制和DDS频率数据控制的作用。

DDS信号源输出10位数据经过外部DAC900和运放放大处理输出正弦波。

经实物制作验证,输出的正弦波可达到0-2MHz,并且波形清晰,在0-500KHz内无明显失真。

关键词:正弦波MCU8051 core 信号源AbstractIn this paper, altera a EP2C8TQ208, built-in MCU8051 core, coupled with built-in logic constitutes a single signal source. Which MCU8051 completion of key scanning, display control, and the role of the DDS frequency data control. DDS signal source output 10-bit data on an external op amp to enlarge DAC900 and processing the output sine wave. The physical production of validation, the output sine wave can reach 0-2MHz, and the waveform clear, in the 0-500KHz in no obvious distortion.Key words: Sine MCU8051 core Source1绪论微电子技术的近期发展成果,为SOC的实现提供了多种途径。

正弦信号发生器实验教学教案

3、通过VHDL语言编程实现数字载波的产生 使用一个计数器,计数范围为0~7,每个值对应一个正弦波 的采样值。 建议用CASE语句来写程序。

4、将数字采样值送入D/A转换芯片的对应管脚 程序编译成功后,管脚分配时注意设置参照下表:

表1 DA管脚分配表

DA0

DA1

DA2

DA3

DA4

DA5

DA6

DA7

68

67

65

64

63

62Leabharlann 60595、顶层电路图

考虑一下:此分频器的分频倍数应该 是多少?才能使得最终得到的正弦波

的频率是1KHz

系统时钟: 32.768MHz

D/A数字模拟转换模块采用的是DAC0832芯片,该芯片为双列直 插20脚封装,最高转换速率为1MHz。在实验板中,D/A模块输 入直接与FPGA相连。

正弦信号发生器实验

(3学时)

1、实验目的:

熟悉VHDL语言、熟练使用QuartusII软件 熟悉正弦信号采样过程、采样点的选取 熟悉CASE语句的使用

2、实验设备

微机1台、示波器1台、FPGA实验箱1套。

3、实验内容

采用FPGA器件来设计产生正弦信号,要求正弦信号频率为 1KHz。 具体过程如下: 1、先将一个正弦波等间隔采样8个点。

6、观察实验结果:用示波器观察OUTPUT的输出波形,看

看频率是否达到设计要求。 由于采样的点只有8个所以输出的波形呈阶梯状与正弦波相比有 一定差距。

4、实验注意事项

1、严禁带电插拔下载线; 2、不要用手触摸FPGA器件,避免静电击穿器件; 3、不要触碰散热片,小心烫伤。

5、实验报告要求:

写出实验目的、实验内容、实验程序、顶层电路图、 示波器测试波形(频率和峰峰值)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录摘要 (2)Abstract (3)1 绪论 (4)2设计任务与要求 (5)3 方案对比和论证确定 (5)4 电路工作原理分析 (6)4.1 MC8051 IP core原理 (6)4.2 DDS电路原理分析 (7)4.3 DA转换与放大电路原理分析 (8)5 软件设计及仿真 (9)5.1 MCU8051软核模块 (9)5.2 MCU8051控制程序设计 (9)5.3 DDS逻辑电路设计 (10)6 实物制作与硬件调试 (11)7总结 (12)参考文献 (13)基于SOPC的正弦信号源摘要本文应用altera的EP2C8TQ208,内建MCU8051 core,加上内建逻辑电路构成了单片信号源。

其中MCU8051完成按键扫描,显示控制和DDS频率数据控制的作用。

DDS信号源输出10位数据经过外部DAC900和运放放大处理输出正弦波。

经实物制作验证,输出的正弦波可达到0-2MHz,并且波形清晰,在0-500KHz内无明显失真。

关键词:正弦波MCU8051 core 信号源AbstractIn this paper, altera a EP2C8TQ208, built-in MCU8051 core, coupled with built-in logic constitutes a single signal source. Which MCU8051 completion of key scanning, display control, and the role of the DDS frequency data control. DDS signal source output 10-bit data on an external op amp to enlarge DAC900 and processing the output sine wave. The physical production of validation, the output sine wave can reach 0-2MHz, and the waveform clear, in the 0-500KHz in no obvious distortion.Key words: Sine MCU8051 core Source1绪论微电子技术的近期发展成果,为SOC的实现提供了多种途径。

对于经过验证而又具有批量的系统芯片,可以做成专用集成电路ASIC而大量生产。

而对于一些仅为小批量应用或处于开发阶段的SOC,若马上投入流片生产,需要投入较多的资金,承担较大的试制风险。

最近发展起来的SOPC技术则提供了另一种有效的解决方案,即用大规模可编程器件的FPGA来实现SOC的功能。

可编程逻辑器件产生于20世纪70年代。

其出现的最初目的是为了用较少的PLD品种替代种类繁多的各式中小规模逻辑电路。

在30多年的发展过程中,PLD 的结构、工艺、功耗、逻辑规模和工作速度等都得到了重大的进步。

尤其是在20世纪90年代,出现了大规模集成度的FPGA,单片的集成度由原来的数千门,发展到数十万甚至数百万门。

芯片的I/O口也由数十个发展至上千个端口。

有的制造商还推出了含有硬核嵌入式系统的IP。

因此,完全可能将一个电子系统集成到一片FPGA中,即SOPC,为SOC的实现提供了一种简单易行而又成本低廉的手段,极大地促进了SOC的发展。

SOPC技术是美国Altrea公司于2000年最早提出的,并同时推出了相应的开发软件Quartus II。

SOPC是基于FPGA解决方案的SOC,与ASIC的SOC解决方案相比,SOPC系统及其开发技术具有更多的特色,构成SOPC的方案也有如下多种途径:1.基于FPGA嵌入IP硬核的SOPC系统,即在FPGA中预先植入嵌入式系统处理器。

目前最为常用的嵌入式系统大多采用了含有ARM的32位知识产权处理器核的器件。

尽管由这些器件构成的嵌入式系统有很强的功能,但为了使系统更为灵活完备,功能更为强大,对更多任务的完成具有更好的适应性,通常必须为此处理器配置许多接口器件才能构成一个完整的应用系统;2.基于FPGA嵌入IP软核的SOPC系统,采用软核设计时,设计更加灵活,设计周期短,成本低,目前最有代表性的软核嵌入式系统处理器分别是Altera的Nios和Nios II核,及Xilinx的MicroBlaze核;3.基于HardCopy技术的SOPC系统,通过强化SOPC工具的设计能力,在保持FPGA开发优势的前提下,引入ASIC的开发流程,从而对ASIC市场形成直接竞争。

这就是Altera推出的HardCopy技术。

HardCopy就是利用原有的FPGA开发工具,将成功实现于FPGA器件上的SOPC系统通过特定的技术直接向ASIC转化,从而克服传统ASIC设计中普遍存在的问题;本设计中采用了第二种方法,即在FPGA中嵌入了8051 软核来设计单片正弦波信号源,设计方便灵活,硬件电路简单。

2设计任务与要求1.按集成电路设计以下几个阶段:系统(或逻辑)设计、电路设计、版图设计。

在每个阶段利用相关软件对设计的电路进行计算、分析、设计、模拟和仿真。

2.利用集成电路芯片进行电路设计,需对设计的系统或电路进行结构和原理进行分析,对电路进行分析计算等方面的工作。

3.调试相关硬件电路,验证是是否达到了该功能。

3方案对比和论证确定方案一:采用专用DDS芯片,外加微控制器控制专用DDS芯片来实现信号源,这种方案硬件电路复杂,成本比较高,尤其是专用DDS芯片,价格比较昂贵。

方案二:采用基于FPGA嵌入IP硬核的SOPC系统,MCU硬核控制内建DDS逻辑电路,但存在如下缺点:1. 由于此类硬核多来自第3方公司,FPGA厂商通常无法直接控制其知识产权费用,从而导致FPGA器件价格相对偏高;2. 由于硬核是预先植入的,设计者无法根据实际需要改变处理器的结构,如总线规模、接口方式,乃至指令形式,更不可能将FPGA 逻辑资源构成的硬件模块以指令的形式形成内置嵌入式系统的硬件加速模块(如DSP模块),以适应更多的电路功能要求。

3. 无法裁减处理器硬件资源以降低FPGA成本。

4.只能在特定的FPGA中使用硬核嵌入式系统,如只能使用Excalibur系列FPGA中的ARM核,Virtex-II Pro系列中的PowerPC核。

方案三:采用FPGA内嵌8051单片机软核核DDS逻辑电路,可充分克服方案一和方案二的缺点,同时设计周期短,成本低,灵活性高。

特别值得一提的是,通过Matlab和DSP Builder,或直接使用VHDL等硬件描述语言设计,用户可以为Nios嵌入式处理器设计各类加速器,并以指令的形式加入Nios的指令系统,从而成为Nios系统的一个接口设备,与整个片内嵌入式系统融为一体。

例如,用户可以根据设计项目的具体要求,随心所欲地构建自己的DSP处理器系统,而不必拘泥于其他DSP公司已上市的有限款式的DSP处理器。

综上所述,选择方案三比较合适。

系统的框图如下图1:图1系统框图4电路工作原理分析4.1 MC8051 IP core 原理MC8051 IP Core 顶层结构图如图2所示,图中指示了mc8051_core 的顶层结构以及同三个存储模块的连接关系,同时显示了顶层的输入输出 I/O 口,各I/O 信号的描述如表1所示。

定时器/计数器和串行接口单元对应于图中的 mc8051_tmrctr和 mc8051_siu 模块,数量是可选择的,在图中用虚线表示。

图2 MC8051 IP Core 顶层结构图SOPC FPGA EP2C8Q208DDS 逻辑MCU8051 ROM RAMLCD1602 显示部分DAC 转换放大处理 低通滤波3X4键盘 控制部分输出MC8051 IP Core 的层次结构及对应的VHDL 文件如图3所示。

核心由定时器/计数器、ALU、串行接口和控制单元各模块组成。

ROM 和RAM 模块不包括于核心内,处于设计的顶层,方便于不同的应用设计及仿真。

MC8051 IP Core 的定时器和串口波特率的计算和标准8051 一样,计数时钟也是由系统时钟经 12 分频得到。

外部中断信号是经两级寄存器做同步处理后输入的。

写应用程序时,I/O口如果没有做成双向口,而是输入和输出分开的,那么要特别注意,像P1=~P1、P1^0=P1^0 这样的I/O 取反操作是无效(不起作用)的,因为读回来的值不是I/O 寄存器的值,而是输入引脚的状态。

图3 顶层结构图4.2 DDS电路原理分析直接数字频率合成器(Direct Digital Synthesizer)是从相位概念出发直接合成所需波形的一种频率合成技术。

一个直接数字频率合成器有相位累加器,加法器,波形存储ROM,DA转换器和低通滤波器(LPF)构成。

DDS原理框图如下图4所示:图5 DA转换和放大电路5软件设计及仿真5.1 MCU8051软核模块利用Synplify Pro综合得到8051软核,再加入Quartus设计文件,得到的顶层的CPU及ROM和RAM原理图如下图6所示,其中CPU时钟为50MHz,RST为电平复位。

图6 8051软核及其RAM和ROM5.2 MCU8051控制程序设计MCU8051主要作用是按键值读取以及相应的处理,显示控制和DDS 频率写入控制。

其软件流程图如下图7:图7 8051内置程序流程图 5.3 DDS 逻辑电路设计图8 DDS 数字逻辑部分原理图其利用MATLAB中的DSP Builder仿真结果如下图9,其中频率控制字为00000001H。

图9 DDS仿真电路图6 实物制作与硬件调试硬件的调试要遵循逐级调试的原则。

首先要对整个硬件系统进行逐级焊接调试,硬件部分包括LCD1602,3X4矩阵式键盘,DA转换部分。

其中LCD1602,矩阵式键盘部分焊接调试比较简单,利用单片机调试好相关程序模块就可以了。

DA转换及处理部分是一个比较关键的部分,由于电路的工作速度比较高,电路的布局和处理直接影响到输出信号的质量,因此在这一部分要注意相关的高速电路的布线规则,DAC900的数字电源与模拟电源要注意隔离,尽量单点接地,最好使用印刷电路板,并且要铺地,各个电源处要加去耦电容。

其次是FPGA的内部的逻辑设计,对于FPGA的内部的逻辑设计,首先是要利用Quartus II做好仿真,以确保FPGA内部逻辑的各个模块工作正常。

其次,要注意协调各个模块的工作,确保各个模块之间能够相互协调,有序的工作而不至于相互影响。

利用Keil C51逐个调试好各个模块后再进行整体程序调试。

本设计中,我们以NIOS II 核心板为基础,利用Keil C51 编译好MCU的控制程序,加载设计文件的MCU的ROM中,再利用Quartus II编译下载到FPGA中进行系统整体调试。