STUS518中文资料

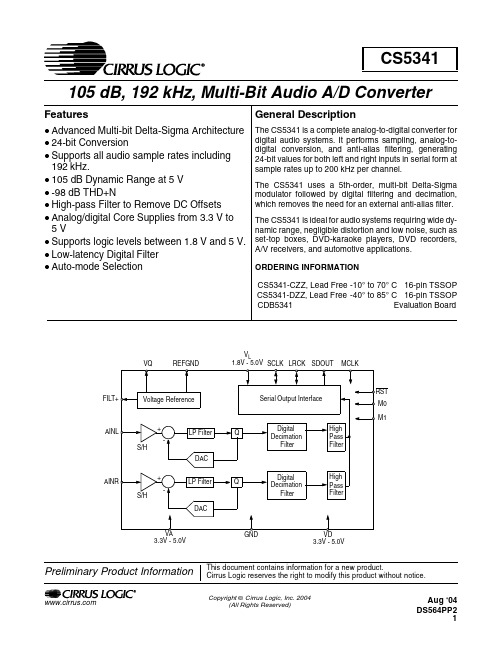

CS5341

FILT+

Voltage Reference

RST Serial Output Interface

M0

M1

AINL

+

S/H

LP Filter

Q

Digital Decimation

Filter

High Pass Filter

DAC

AINR

+

LP Filter

Q

-

S/H

DAC

Digital Decimation

2 PIN DESCRIPTION ................................................................................................................. 15 3 TYPICAL CONNECTION DIAGRAM ....................................................................................... 16 4 APPLICATIONS ....................................................................................................................... 17

ORDERING INFORMATION

CS5341-CZZ, Lead Free -10° to 70° C 16-pin TSSOP

CS5341-DZZ, Lead Free -40° to 85° C 16-pin TSSOP

CDB5341

1955918资料

Extract from the onlinecatalogCCVA 2,5/ 8-G-5,08 P26THROrder No.: 1955918The figure shows a 10-position version of the producthttp://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1955918Headers, pin length: 2.6 mm, 5.08 mm pitch, 8-pos.http://Please note that the data givenhere has been taken from theonline catalog. For comprehensiveinformation and data, please referto the user documentation. TheGeneral Terms and Conditions ofUse apply to Internet downloads. Technical dataDimensions / positionsPitch 5.08 mmDimension a35.56 mmNumber of positions8Pin dimensions 1 x 1 mmPin spacing 5.08 mmHole diameter 1.6 mmTechnical dataInsulating material group IIIaRated surge voltage (III/3) 4 kVRated surge voltage (III/2) 4 kVRated surge voltage (II/2) 4 kVRated voltage (III/2)320 VRated voltage (II/2)400 VConnection in acc. with standard EN-VDENominal current I N12 ANominal voltage U N250 VMaximum load current12 A (per position)Insulating material LCPInflammability class acc. to UL 94V0Certificates / ApprovalsApproval logoCULNominal voltage U N300 VNominal current I N10 AULNominal voltage U N300 VNominal current I N10 ACertification CUL, ULAccessoriesItem Designation DescriptionGeneral1954362CR-MSTB NAT HT HT coding section, is pushed into the recess on the header beforethe reflow process, made of highly temperature-resistant, beigeinsulating materialMarking1051993B-STIFT Marker pen, for manual labeling of unprinted Zack strips, smear-proof and waterproof, line thickness 0.5 mm0804293SK 5,08/3,8:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 12 identicaldecades marked 1-10, 11-20 etc. up to 91-(99)100, sufficient for120 terminal blocks0805085SK 5,08/3,8:SO Marker card, special printing, self-adhesive, labeled acc. tocustomer requirements, 12 identical marker strips per card, max.25-position labeling per strip, color: white0805412SK 5,08/3,8:UNBEDRUCKT Marker cards, unprinted, with pitch divisions, self-adhesive, 10-section marker strips, 12 strips per card, can be labeled with theM-PENPlug/Adapter1734401CR-MSTB Coding section, inserted into the recess in the header or theinverted plug, red insulating materialDrawingsApplication drawingDrilling diagramDimensioned drawingBottom view, free space for solder paste, 0.55mm deepAddressPHOENIX CONTACT GmbH & Co. KGFlachsmarktstr. 832825 Blomberg,GermanyPhone +49 5235 3 00Fax +49 5235 3 41200http://www.phoenixcontact.de© 2008 Phoenix ContactTechnical modifications reserved;。

SN74LS56P中文资料

Copyright © 1988, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instrumentsstandard warranty. Production processing does not necessarily includetesting of all parameters.1POST OFFICE BOX 655303 • DALLAS, TEXAS 752652POST OFFICE BOX 655303 • DALLAS, TEXAS 752653 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityLow Power /lpw Telephony /telephonyWirelessVideo&Imaging /videoWireless /wirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments IncorporatedIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityLow Power /lpw Telephony /telephonyWirelessVideo&Imaging /videoWireless /wirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments IncorporatedIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityLow Power /lpw Telephony /telephonyWirelessVideo&Imaging /videoWireless /wirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments IncorporatedIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityLow Power /lpw Telephony /telephonyWirelessVideo&Imaging /videoWireless /wirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments IncorporatedIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityLow Power /lpw Telephony /telephonyWirelessVideo&Imaging /videoWireless /wirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments IncorporatedIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityLow Power /lpw Telephony /telephonyWirelessVideo&Imaging /videoWireless /wirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments Incorporated。

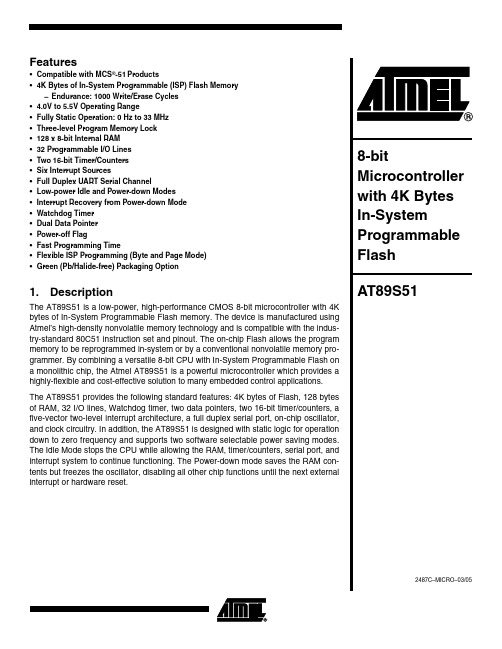

at89s51中文资料_数据手册_参数

XTAL2 10 XTAL1 11

GND 12 PWRGND 13 (A8) P2.0 14 (A9) P2.1 15 (A10) P2.2 16 (A11) P2.3 17 (A12) P2.4 18 (A13) P2.5 19 (A14) P2.6 20 (A15) P2.7 21

The AT89S51 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, two 16-bit timer/counters, a five-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89S51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power-down mode saves the RAM contents but freezes the oscillator, disabling all other chip functions until the next external interrupt or hardware reset.

ABB机器人操作手册(中文版)

3HAC16590-10 米Ι : N

3

© Copyright 2004-2010 ABB. 保留所有权利。

目表

3.3.6 备份和恢复 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69 3.3.7 在生产模式下运行 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70 3.3.8 授予 RobotStudio 访问权限 . . . . . . . . . . . . . . . . . . . . . . . . . 71 3.3.9 升级 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 3.3.10 安装软件选项 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73 3.3.11 关闭 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

1.4 如何处理紧急情况 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 1.4.1 停止系统 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 1.4.2 释放机器人制动闸 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 1.4.3 灭火 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 1.4.4 从紧急停止状态恢复 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 1.4.5 返回到编程路径 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

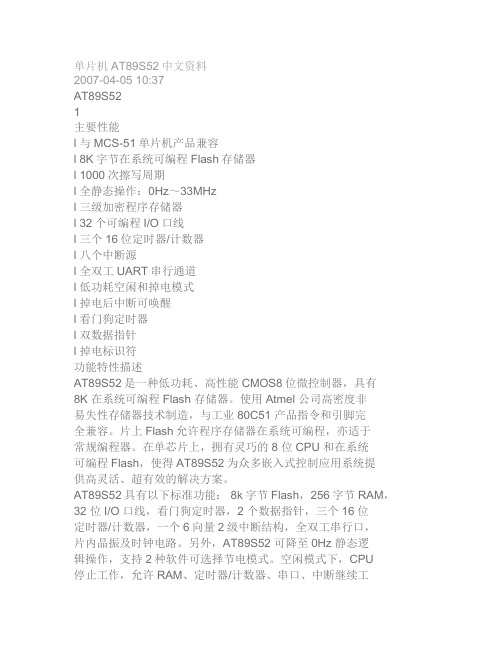

89s52中文资料 通用版

单片机AT89S52中文资料2007-04-05 10:37AT89S521主要性能l 与MCS-51单片机产品兼容l 8K字节在系统可编程Flash存储器l 1000次擦写周期l 全静态操作:0Hz~33MHzl 三级加密程序存储器l 32个可编程I/O口线l 三个16位定时器/计数器l 八个中断源l 全双工UART串行通道l 低功耗空闲和掉电模式l 掉电后中断可唤醒l 看门狗定时器l 双数据指针l 掉电标识符功能特性描述AT89S52是一种低功耗、高性能CMOS8位微控制器,具有8K 在系统可编程Flash 存储器。

使用Atmel 公司高密度非易失性存储器技术制造,与工业80C51 产品指令和引脚完全兼容。

片上Flash允许程序存储器在系统可编程,亦适于常规编程器。

在单芯片上,拥有灵巧的8 位CPU 和在系统可编程Flash,使得AT89S52为众多嵌入式控制应用系统提供高灵活、超有效的解决方案。

AT89S52具有以下标准功能: 8k字节Flash,256字节RAM,32 位I/O 口线,看门狗定时器,2 个数据指针,三个16 位定时器/计数器,一个6向量2级中断结构,全双工串行口,片内晶振及时钟电路。

另外,AT89S52 可降至0Hz 静态逻辑操作,支持2种软件可选择节电模式。

空闲模式下,CPU停止工作,允许RAM、定时器/计数器、串口、中断继续工作。

掉电保护方式下,RAM内容被保存,振荡器被冻结,单片机一切工作停止,直到下一个中断或硬件复位为止。

R8 位微控制器8K 字节在系统可编程FlashAT89S52Rev. 1919-07/01AT89S522引脚结构AT89S523方框图引脚功能描述AT89S524VCC : 电源GND: 地P0 口:P0口是一个8位漏极开路的双向I/O口。

作为输出口,每位能驱动8个TTL逻辑电平。

对P0端口写“1”时,引脚用作高阻抗输入。

当访问外部程序和数据存储器时,P0口也被作为低8位地址/数据复用。

AK5365中文资料

ASAHI KASEI[AK5365]GENERAL DESCRIPTIONAK5365 is a high-performance 24-bit, 96kHz sampling ADC for consumer audio and digital recording applications. Thanks to AKM’s Enhanced Dual-Bit modulator architecture, this analog-to-digital converter has an impressive dynamic range of 103dB with a high level of integration. The AK5365 has a 5-channel stereo input selector, an input Programmable Gain Amplifier with an ALC function. All this integration with high-performance makes the AK5365 well suited for CD and DVD recording systems.FEATURES1. 24bit Stereo ADC• 5ch Stereo Inputs Selector• Input PGA from +12dB to 0dB, 0.5dB Step• Auto Level Control (ALC) Circuit• Digital HPF for offset cancellation (fc=1.0Hz@fs=48kHz)• Digital Attenuator• Soft Mute• Single-end Inputs• S/(N+D) : 94dB• DR, S/N : 103dB• Audio I/F Format : 24bit MSB justified, I2S2. 3-wire Serial µP Interface / I2C-Bus3. Master / Slave Mode4. Master Clock : 256fs/384fs/512fs5. Sampling Rate : 32kHz to 96kHz6. Power Supply• AVDD: 4.75 ∼ 5.25V (typ. 5.0V)• DVDD: 3.0 ∼ 5.25V (typ. 3.3V)7. Power Supply Current : 27mA8. Ta = -40 ∼85°C9. Package : 44pin LQFPOrdering GuideAK5365VQ −40 ∼ +85°C 44pin LQFP (0.8mm pitch)AKD5365Evaluation Board for AK5365Pin LayoutLIN5R I N 54443142414039383736353433323130292827262524232221201918171615141312234567891011AK5365VQTop ViewTEST1LIN4TEST2LIN3TEST3LIN2TEST4LIN1LOPIN LOUTI P G A LI P G A RR O U TR O P I NA V D DA V S SV C O MD V S SD V D DS D T OB IC K LRCKMCLK PDN ALC SMUTE SEL0SEL1SEL2CDTI/SDA CCLK/SCL CSN/CAD1T E S T 8R I N 4T E S T 7R I N 3T E S T 6R I N 2T E S T 5R I N 1M /SC T R LPIN/FUNCTIONNo.Pin Name I/O Function 1LIN5I Lch Analog Input 5 Pin2TEST1I Test 1 Pin (Connected to AVSS)3LIN4I Lch Analog Input 4 Pin4TEST2I Test 2 Pin (Connected to AVSS)5LIN3I Lch Analog Input 3 Pin6TEST3I Test 3 Pin (Connected to AVSS)7LIN2I Lch Analog Input 2 Pin8TEST4I Test 4 Pin (Connected to AVSS)9LIN1I Lch Analog Input 1 Pin10LOPIN I Lch Feed Back Resistor Input Pin11LOUT O Lch Feed Back Resistor Output Pin12IPGAL I Lch IPGA Input Pin13IPGAR I Rch IPGA Input Pin14ROUT O Rch Feed Back Resistor Output Pin15ROPIN I Rch Feed Back Resistor Input Pin16AVDD-Analog Power Supply Pin, 4.75 ∼ 5.25V17AVSS-Analog Ground Pin18VCOM O Common Voltage Output Pin, AVDD/2 Bias voltage of ADC input.19DVSS-Digital Ground Pin20DVDD-Digital Power Supply Pin, 3.0 ∼ 5.25V21SDTO O Audio Serial Data Output Pin22BICK I/O Audio Serial Data Clock PinNote: All digital input pins except pull-down pins should not be left floating. Note: TEST1, TEST2, TEST3 and TEST4 pins should be connected to AVSS.No.Pin Name I/O Function 23LRCK I/O Output Channel Clock Pin24MCLK I Master Clock Input Pin25PDN I Power-Down Mode Pin“H”: Power up, “L”: Power down reset and initializes the control register.26ALC I ALC Enable Pin (Internal Pull-down Pin, typ. 100kΩ) “H” : ALC Enable, “L” : ALC Disable27SMUTE I Soft Mute Pin (Internal Pull-down Pin, typ. 100kΩ) “H” : Soft Mute, “L” : Normal Operation28SEL0I Input Selector 0 Pin29SEL1I Input Selector 1 Pin30SEL2I Input Selector 2 PinCDTI I Control Data Input Pin in 3-wire Control (CTRL pin = “L”) 31SDA I/O Control Data Input / Output Pin in I2C Control (CTRL pin = “H”)CCLK I Control Data Clock Pin in 3-wire Control (CTRL pin = “L”) 32SCL I Control Data Clock Pin in I2C Control (CTRL pin = “H”)CSN I Chip Select Pin in 3-wire Control (CTRL pin = “L”) 33CAD1I Chip Address 1 Select Pin in I2C Control (CTRL pin = “H”)34CTRL I Control Mode Pin“H” : I2C Control & I2S Compatible, “L” : 3-wire Control35M/S I Master / Slave Mode Pin“H” : Master Mode, “L” : Slave Mode36RIN1I Rch Analog Input 1 Pin37TEST5I Test 5 Pin (Connected to AVSS)38RIN2I Rch Analog Input 2 Pin39TEST6I Test 6 Pin (Connected to AVSS)40RIN3I Rch Analog Input 3 Pin41TEST7I Test 7 Pin (Connected to AVSS)42RIN4I Rch Analog Input 4 Pin43TEST8I Test 8 Pin (Connected to AVSS)44RIN5I Rch Analog Input 5 PinNote: All digital input pins except pull-down pins should not be left floating. Note: TEST5, TEST6, TEST7 and TEST8 pins should be connected to AVSS.ABSOLUTE MAXIMUM RATINGS(AVSS, DVSS=0V; Note 1)Parameter Symbol min max UnitsPower Supplies:AnalogDigital|AVSS – DVSS| (Note 2)AVDDDVDD∆GND−0.3−0.3-6.06.00.3VVVInput Current, Any Pin Except Supplies IIN-±10mA Analog Input Voltage(VREF, LIN1-5, RIN1-5, LOPIN, ROPIN, IPGAL, IPGAR pins)VINA−0.3AVDD+0.3V Digital Input Voltage (All digital input pins)VIND−0.3DVDD+0.3V Ambient Temperature (powered applied)Ta−4085°C Storage Temperature Tstg−65150°C Note 1. All voltages with respect to ground.Note 2. AVSS and DVSS must be connected to the same analog ground plane.WARNING: Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.RECOMMENDED OPERATING CONDITIONS(AVSS, DVSS=0V; Note 1)Parameter Symbol min typ max UnitsPower Supplies (Note 3)AnalogDigitalAVDDDVDD4.753.05.03.35.25AVDDVVNote 1. All voltages with respect to ground.Note 3. The power up sequence between AVDD and DVDD is not critical.WARNING: AKM assumes no responsibility for the usage beyond the conditions in this datasheet.ANALOG CHARACTERISTICS(Ta=25°C; AVDD=5.0V, DVDD=3.3V; AVSS=DVSS=0V; fs=48kHz, 96kHz; BICK=64fs; Signal Frequency=1kHz; 24bit Data; Measurement frequency=20Hz ∼ 20kHz at fs=48kHz, 40Hz ∼ 40kHz at fs=96kHz; unless otherwise specified) Parameter min typ max Units Pre-Amp Characteristics:Feedback Resistance1050kΩS/(N+D) (Note 4)-100dBS/N (A-weighted)-108dB Load Resistance (Note 5) 6.3kΩLoad Capacitance20pF Input PGA Characteristics:Input Voltage (Note 6)0.91 1.1Vrms Input Resistance (Note 7) 6.31015kΩStep Size0.20.50.8dBGain Control Range ALC = OFFALC = ON−9.5+12+12dBdBADC Analog Input Characteristics: IPGA=0dB, ALC = OFF (Note 8)Resolution24BitsS/(N+D) (−0.5dBFS)fs=48kHzfs=96kHz 84829492dBdBDR (−60dBFS)fs=48kHz, A-weightedfs=96kHz 968910399dBdBS/N fs=48kHz, A-weightedfs=96kHz 968910399dBdBInterchannel Isolation (Note 9)90110dB Interchannel Gain Mismatch0.20.5dB Gain Drift100-ppm/°C Power Supply Rejection (Note 10)50-dB Power SuppliesPower Supply CurrentNormal Operation (PDN pin = “H”)AVDDDVDD (fs=48kHz)(fs=96kHz)Power-down mode (PDN pin = “L”) (Note 11) AVDDDVDD 2348101035816100100mAmAmAµAµANote 4. This value is measured at LOUT and ROUT pins using the circuit as shown in Figure 24.The input signal voltage is 2Vrms.Note 5. This value is the input impedance of an external device that the LOUT and ROUT pins can drive, when a device is connected with LOUT and ROUT pin externally. The feedback resistor (min. 10kΩ) that it is usually connected with the LOUT/ROUT pins, and the value of input impedance (min. 6.3kΩ) of the IPGAL/R pins are not included. Note 6. Full scale (0dB) of the input voltage at ALC=OFF and IPGA=0dB.Input voltage to IPGAL and IPGAR pins is proportional to AVDD voltage. Vin = 0.2 x AVDD (Vrms).Note 7. This value is input impedance of the IPGAL and IPGAR pins.Note 8. This value is measured via the following path. Pre-Amp → IPGA (Gain : 0dB) → ADC.The measurement circuit is Figure 24.Note 9. This value is the interchannel isolation between all the channels of the LIN1-5 and RIN1-5 when the applied input signal causes the Pre-Amp output to equal IPGA input.Note 10. PSR is applied to AVDD and DVDD with 1kHz, 50mVpp.Note 11. All digital input pins are held DVDD or DVSS.FILTER CHARACTERISTICS (fs=48kHz)(Ta=−40 ∼ 85°C; AVDD=4.75 ∼ 5.25V; DVDD=3.0 ∼ 5.25V; fs=48kHz)Parameter Symbol min typ max Units ADC Digital Filter (Decimation LPF):Passband (Note 12)−0.005dB−0.02dB−0.06dB−6.0dB PB0---21.76822.024.021.5---kHzkHzkHzkHzStopband SB26.5kHz Passband Ripple PR±0.005dB Stopband Attenuation SA80dB Group Delay (Note 13)GD29.61/fs Group Delay Distortion∆GD0µs ADC Digital Filter (HPF):Frequency Response (Note 12)−3dB−0.5dB−0.1dB FR 1.02.96.5HzHzHzNote 12. The passband and stopband frequencies scale with fs. For example, 21.768kHz at −0.02dB is 0.454 x fs. Note 13. The calculated delay time induced by digital filtering. This time is from the input of an analog signalto the setting of 24bit data both channels to the ADC output register for ADC.FILTER CHARACTERISTICS (fs=96kHz)(Ta=−40 ∼ 85°C; AVDD=4.75 ∼ 5.25V; DVDD=3.0 ∼ 5.25V; fs=96kHz)Parameter Symbol min typ max Units ADC Digital Filter (Decimation LPF):Passband (Note 14)−0.005dB−0.02dB−0.06dB−6.0dB PB0---43.53644.048.043.0---kHzkHzkHzkHzStopband SB53.0kHz Passband Ripple PR±0.005dB Stopband Attenuation SA80dB Group Delay (Note 15)GD29.61/fs Group Delay Distortion∆GD0µs ADC Digital Filter (HPF):Frequency Response (Note 14)−3dB−0.5dB−0.1dB FR25.813HzHzHzNote 14. The passband and stopband frequencies scale with fs. For example, 43.536kHz at −0.02dB is 0.454 x fs. Note 15. The calculated delay time induced by digital filtering. This time is from the input of an analog signalto the setting of 24bit data both channels to the ADC output register for ADC.DC CHARACTERISTICS(Ta=−40 ∼ 85°C; AVDD=4.75 ∼ 5.25V; DVDD=3.0 ∼ 5.25V)Parameter Symbol min typ Max UnitsHigh-Level Input Voltage Low-Level Input Voltage VIHVIL70%DVDD----30%DVDDVVHigh-Level Output Voltage (Iout=−400µA) Low-Level Output Voltage(Except SDA pin : Iout=400µA) (SDA pin : Iout=3mA)VOHVOLVOLDVDD-0.5------0.50.4VVVInput Leakage Current Iin--±10µASWITCHING CHARACTERISTICS(Ta=−40 ∼ 85°C; AVDD=4.75 ∼ 5.25V; DVDD=3.0 ∼ 5.25V; C L=20pF)Parameter Symbol min typ max Units Master Clock TimingFrequencyPulse Width Low Pulse Width HighfCLKtCLKLtCLKH8.1920.4/fCLK0.4/fCLK24.576MHznsnsLRCK FrequencyNormal Speed Mode Double Speed Mode fsnfsd32484896kHzkHzDuty Cycle Slave modeMaster mode 455055%%Audio Interface Timing Slave modeBICK PeriodBICK Pulse Width LowPulse Width HighLRCK Edge to BICK “↑” (Note 16) BICK “↑” to LRCK Edge (Note 16) LRCK to SDTO (MSB) (Except I2S mode) BICK “↓” to SDTOtBCKtBCKLtBCKHtLRBtBLRtLRStBSD160656530303535nsnsnsnsnsnsnsMaster modeBICK Frequency BICK DutyBICK “↓” to LRCK BICK “↓” to SDTOfBCKdBCKtMBLRtBSD−20−2064fs502035Hz%nsnsNote 17. BICK rising edge must not occur at the same time as LRCK edge.Parameter Symbol min typ max Units Control Interface Timing (3-wire Serial mode):CCLK PeriodCCLK Pulse Width Low Pulse Width High CDTI Setup TimeCDTI Hold TimeCSN “H” TimeCSN “↓” to CCLK “↑” CCLK “↑” to CSN “↑”tCCKtCCKLtCCKHtCDStCDHtCSWtCSStCSH200808040401505050nsnsnsnsnsnsnsnsControl Interface Timing (I2C Bus mode):SCL Clock FrequencyBus Free Time Between TransmissionsStart Condition Hold Time (prior to first clock pulse) Clock Low TimeClock High TimeSetup Time for Repeated Start ConditionSDA Hold Time from SCL Falling (Note 17) SDA Setup Time from SCL RisingRise Time of Both SDA and SCL LinesFall Time of Both SDA and SCL LinesSetup Time for Stop ConditionPulse Width of Spike Noise Suppressed by Input FilterfSCLtBUFtHD:STAtLOWtHIGHtSU:STAtHD:DATtSU:DATtRtFtSU:STOtSP-4.74.04.74.04.70.25--4.0100-------1.00.3-50kHzµsµsµsµsµsµsµsµsµsµsnsReset TimingPDN Pulse Width (Note 18) PDN “↑” to SDTO valid (Note 19) PWN “↑” to SDTO valid (Note 20)tPDtPDVtPDV150516516ns1/fs1/fsNote 17. Data must be held long enough to bridge the 300ns-transition time of SCL.Note 18. The AK5365 can be reset by bringing the PDN pin = “L”.Note 19. This cycle is the number of LRCK rising edges from the PDN pin = “H”.Note 20. This cycle is the number of LRCK rising edges from the PWN bit = “1”.Purchase of Asahi Kasei Microsystems Co., Ltd I2C components conveys a license under the Philips I2C patent to use the components in the I2C system, provided the system conform to the I2C specifications defined by Philips.Timing DiagramMCLKLRCKBICKClock TimingLRCK VIH VILBICK VIH VILSDTO50%DVDDAudio Interface Timing (Slave mode)LRCK BICK50%DVDDSDTO 50%DVDD50%DVDDAudio Interface Timing (Master mode)CSNVIH VILCCLKVIH VILCDTIVIH VILWRITE Command Input TimingCSNVIH VILCCLKVIH VIL CDTI VIH VILWRITE Data Input TimingSDASCLVILVIL I C Bus Mode TimingPDNVILCSNVIH VILSDTO50%DVDDPDNVIH VILSDTO50%DVDDPower Down & Reset TimingOPERATION OVERVIEWSystem ClockMCLK (256fs/384fs/512fs), BICK (48fs∼) and LRCK (fs) clocks are required in slave mode. The LRCK clock input must be synchronized with MCLK, however the phase is not critical. MCLK frequency is automatically detected in slave mode. Table 1 shows the relationship of typical sampling frequency and the system clock frequency.MCLK (256fs/384fs/512fs) is required in master mode. MCLK frequency is selected by CKS1-0 bits as shown in Table 2. In master mode, after setting CKS1-0 bits, there is a possibility the frequency and duty of LRCK and BICK outputs become an abnormal state.All external clocks (MCLK, BICK and LRCK) must be present unless PDN pin = “L” and PWN bit = “1”. If these clocks are not provided, the AK5365 may draw excess current due to its use of internal dynamically refreshed logic. If the external clocks are not present, place the AK5365 in power-down mode (PDN pin = “L” or PWN bit = “0”). In master mode, the master clock (MCLK) must be provided unless PDN pin = “L”.MCLKfs256fs384fs512fs32kHz8.192MHz12.288MHz16.384MHz44.1kHz11.2896MHz16.9344MHz22.5792MHz48kHz12.288MHz18.432MHz24.576MHz96kHz24.576MHz N/A N/ATable 1. System clock example (Slave mode)MCLKCKS1CKS032kHz ≤ fs ≤ 48kHz48kHz < fs ≤ 96kHz00256fs256fs Default01512fs N/A10384fs N/A11N/A N/ATable 2. Master clock frequency select (Master mode)Audio Interface FormatTwo kinds of data formats can be chosen with the DIF bit (Table 3) and the CTRL pin (Table 4). The DIF bit and CTRL pin are ORed between pin and register. In both modes, the serial data is in MSB first, 2’s compliment format. The SDTO is clocked out on the falling edge of BICK. The audio interface supports both master and slave modes. In master mode, BICK and LRCK are output with the BICK frequency fixed to 64fs and the LRCK frequency fixed to 1fs.Mode DIF bit SDTO LRCK BICK FigureDefault0024bit, MSB justified H/L≥ 48fs Figure 11124bit, I2S Compatible L/H≥ 48fs Figure 2Table 3. Audio Interface Format (CTRL pin = “L”)Mode CTRL pin SDTO LRCK BICK Figure0L24bit, MSB justified H/L≥ 48fs Figure 11H24bit, I2S Compatible L/H≥ 48fs Figure 2Table 4. Audio Interface Format (DIF bit = “0”)LRCKBICK(64fs)SDTO(o)Figure 1. Mode 0 TimingLRCKBICK(64fs)SDTO(o)Figure 2. Mode 1 TimingMaster Mode and Slave ModeThe M/S pin selects either master or slave mode. M/S pin = “H” selects master mode and “L” selects slave mode. The AK5365 outputs BICK and LRCK in master mode. In slave mode, MCLK, BICK and LRCK are input externally.BICK, LRCKSlave Mode BICK = Input LRCK = InputMaster Mode BICK = Output LRCK = OutputTable 5. Master mode/Slave modeDigital High Pass FilterThe ADC has a digital high pass filter for DC offset cancellation. The cut-off frequency of the HPF is 1.0Hz (@fs=48kHz) and scales with sampling rate (fs).Power-up/downThe AK5365 is placed in the power-down mode by bringing PDN pin = “L” and the digital filter is also reset at the same time. This reset should always be done after power-up. An analog initialization cycle starts after exiting the power-down mode. Therefore, the output data SDTO becomes available after 516 cycles of LRCK.(1) Power-up Sequence 1Power SupplyPDN pinADC Internal StateIPGASDTOExternal clocksin slave modeExternal clocksin master modeBICK, LRCKin master mode- INITA :Initializing period of ADC analog section (516/fs).- FI :Fade in. After exiting power down, IPGA value fades in.- PDN :Power down state.- The period of (1) should be min. 150ns in Figure 3.Figure 3. Power-up Sequence 1(2) Power-up Sequence 2Power SupplyPDN pinADC Internal StateIPGASDTOExternal clocksin slave modeExternal clocksin master modeBICK, LRCKin master mode- INITA :Initializing period of ADC analog section (516/fs).- FI :Fade in. After exiting power down, IPGA value fades in.- PDN :Power down state.- The period of (1) should be min. 150ns in Figure 4.Figure 4. Power-up Sequence 2Input SelectorThe AK5365 includes 5ch stereo input selectors (Figure 5). The input selector is 5 to 1 selector. The input channel is set by the SEL2-0 bits (Table 6) and the SEL2-0 pins (Table 7). The SEL2-0 pins should be fixed to “LLL” if the AK5365 is controlled by the SEL 2-0 bits, because the setting of the SEL2-0 pins are prior to the SEL2-0 bits setting.SEL2 bit SEL1 bit SEL0 bit Input Channel000LIN1 / RIN1Default001LIN2 / RIN2010LIN3 / RIN3011LIN4 / RIN4100LIN5 / RIN5Table 6. Input Selector (SEL2-0 pin = “LLL”)SEL2 pin SEL1 pin SEL0 pin Input ChannelL L L LIN1 / RIN1L L H LIN2 / RIN2L H L LIN3 / RIN3L H H LIN4 / RIN4H L L LIN5 / RIN5Table 7. Input Selector (SEL2-0 bit = “000”)Figure 5. Input Selector[Input selector switching sequence]The input selector should be changed after soft mute to avoid the switching noise of the input selector (Figure 6).1.Enable the soft mute before changing channel.2.Change channel.3.Disable the soft mute.SMUTEAttenuation Channel DATT Level-∞Figure 6. Input channel switching sequence exampleThe period of (1) varies in the setting value of DATT. It takes 1024/fs to mute when DATT value is 0dB.When changing channels, the input channel should be changed during (2). The period of (2) should be around 200ms because there is some DC difference between the channels.Function of CTRL PinThe CTRL pin sets the audio interface format and the type of serial control interface. When the CTRL pin is “L”, the audio interface format is selected by the DIF bit and the serial control interface is 3-wire control mode. When the CTRL pin is “H”, the audio interface format is fixed to 24bit I2S compatible and the serial control interface is I2C-bus control mode.CTRL pin Audio Interface Format Serial Control InterfaceL Note3-wire ControlH24bit, I2S Compatible I2C-Bus ControlTable 8. CTRL pin FunctionNote: The audio interface format is ORed between the CTRL pin and DIF bit. When the CTRL pin is “L”, the audio interface format can be selected between 24bit MSB justified and 24bit I2S compatible by DIF bit. When the CTRL pin is “H”, the audio interface format is fixed to 24bit I2S compatible.Input AttenuatorThe input ATTs are constructed by adding the input resistor (Ri) for LIN1-5/RIN1-5 pins and the feedback resistor (Rf) between LOPIN (ROPIN) pin and LOUT (ROUT) pin (Figure 7). The input voltage range of the IPGAL/IPGAR pin is typically 0.2 x AVDD (Vrms). If the input voltage of the input selector exceeds 0.2 x AVDD, the input voltage of the IPGAL/IPGAR pins must be attenuated to 0.2 x AVDD by the input ATTs. Table 9 shows the example of Ri and Rf.Figure 7. Input ATT• Example for input rangeInput Range Ri [kΩ]Rf [kΩ]ATT Gain [dB]IPGAL/R pin4Vrms4712−11.86 1.02Vrms2Vrms4724−5.84 1.02Vrms1Vrms474701VrmsTable 9. Input ATT exampleInput VolumeThe AK5365 includes two independent channel analog volumes (IPGA) with 25 levels at 0.5dB steps located in front of the ADC. The digital volume controls (DATT) have 128 levels (including MUTE) and is located after the ADC. Both the analog and digital volumes are controlled through the same register address. When the MSB of the register is “1”, the IPGA changes and when the MSB = “0”, the DATT changes.The IPGA is a true analog volume control that improves the S/N ratio as seen in Table 10. Independent zero-crossing detection is used to ensure level changes only occur during zero-crossings. If there are no zero-crossings, the level will then change after a time-out period (Table 11); the time-out period scales with fs. If a new value is written to the IPGA register before the IPGA changes at the zero crossing or time-out, the previous value becomes invalid. The timer (channel independent) for time-out is reset and the timer restarts for new IPGA value.The DATT is a pseudo-log volume that is linear-interpolated internally. When changing the level, the transition between ATT values has 8031 levels and is done by soft changes, eliminating any switching noise.Input Gain Setting0dB+6dB+12dBfs=48kHz, A-weight103dB100dB96dBTable 10. PGA+ADC S/NZTM1ZTM0Zero crossing timeout period@fs=48kHz00288/fs6ms011152/fs24ms102304/fs48ms Default114608/fs96msTable 11. Zero crossing timeout period[Writing operation at ALC Enable]Writing to the area over 80H (Table 17) of IPGL/R registers is ignored during ALC operation. After ALC is disabled, the IPGA changes to the last written data by zero-crossing or time-out. In case of writing to the DATT area under 7FH (Table 17) of IPGL/R registers, the DATT changes even if ALC is enabled.ALC Operation[1]ALC Limiter OperationWhen the ALC limiter is enabled, and either Lch or Rch exceed the ALC limiter detection level (LMTH bit), the IPGA value is attenuated by the amount defined in the ALC limiter ATT step (LMAT bit) automatically. Then the IPGA value is changed commonly for L/R channels.When the ZELMN bit = “1”, the timeout period is set by the LTM1-0 bits. The operation for attenuation is done continuously until the input signal level becomes the ALC limiter detection level (LMTH bit) or less. If the ALC bit does not change into “0” or the ALC pin does not change into “L” after completing the attenuation, the attenuation operation repeats until the input signal level equals or exceeds the ALC limiter detection level (LMTH bit).When the ZELMN bit = “0”, the timeout period is set by the ZTM1-0 bits. This enables the zero-crossing attenuation function so that the IPGA value is attenuated at the zero-detect points of the waveform.When FR bit = “1”, the ALC operation corresponds to the impulse noise in additional to the normal ALC operation. Then if the impulse noise is supplied at ZELMN bit = “0”, the ALC operation becomes the faster period than a set of ZTM1-0 bits. In case of ZELMN bit = “1”, it becomes the same period as LTM1-0 bits. When FR bit = “0”, the ALC operation is the normal ALC operation.[2]ALC Recovery OperationThe ALC recovery refers to the amount of time that the AK5365 will allow a signal to exceed a predetermined limiting value prior to enabling the limiting function. The ALC recovery operation uses the WTM1-0 bits to define the wait period used after completing an ALC limiter operation. If the input signal does not exceed the “ALC Recovery Waiting Counter Reset Level”, the ALC recovery operation starts. The IPGA value increases automatically during this operation up to the reference level (REF7-0 bits). The ALC recovery operation is done at a period set by the WTM1-0 bits. Zero crossing is detected during WTM1-0, the ALC recovery operation waits WTM1-0 period and the next recovery operation starts. During the ALC recovery operation, when input signal level exceeds the ALC limiter detection level (LMTH bit), the ALC recovery operation changes immediately into an ALC limiter operation.In the case of “(Recovery waiting counter reset level) ≤ Input Signal < Limiter detection level” during the ALC recovery operation, the wait timer for the ALC recovery operation is reset. Therefore, in the case of “(Recovery waiting counter reset level) > Input Signal”, the wait timer for the ALC recovery operation starts.When the impulse noise is input at FR bit = “1”, the ALC recovery operation becomes faster than a normal recovery operation. When the FR bit = “0”, the ALC recovery operation is done by normal period.[3] ALC Level Diagram (1) ALC=OFFFigure 8 and 9 show the level diagram example at ALC=OFF. In Figure 8, Input ATT is −12dB.4Vrms2Vrms0dBFS-12dB-12dB-12dB1Vrms-12dB+6dB+12dBFigure 8. ALC Level diagram example (ALC=OFF)In Figure 9, Input ATT is −6dB.0dBFSFigure 9. ALC Level diagram example (ALC=OFF)(2) ALC=ONFigure 10 and 11 show the level diagram example at ALC=ON. In Figure 10, Input ATT is −12dB and REF7-0 bits are “8CH”.4Vrms2Vrms-12dB-12dB-12dB1Vrms-12dB0.5Vrms-0.5dB-0.5dBFS-6dBFS -12dBFS 0dBFS +5.5dB+6dB0.25VrmsFigure 10. ALC Level diagram example (ALC=ON)In Figure 11, Input ATT is −6dB and REF7-0 bits are “8CH”.2Vrms1Vrms-6dB-6dB0.5Vrms-6dB0.25Vrms-6dB-0.5dB-0.5dBFS-6dBFS 0dBFS +5.5dB+6dB-12dBFSFigure 11. ALC Level diagram example (ALC=ON)[4]Example of ALC OperationThe following registers should not be changed during the ALC operation.•LTM1-0, LMTH, LMAT, WTM1-0, ZTM1-0, RATT, REF7-0, ZELMN bits• The IPGA value of Lch becomes the start value if the IPGA value is different with Lch and Rch when the ALC starts.• Writing to the area over 80H (Table 17) of IPGL/R registers is ignored during ALC operation. After ALC is disabled, the IPGA changes to the last written data by zero-crossing or time-out. In case of writing to the DATT area under 7FH (Table 17) of IPGL/R registers, the DATT changes even if ALC is enabled.Figure 12. Registers set-up sequence at ALC operation(1): Enable soft mute (2): Disable soft muteNote : ALC operation is enabled by the ALC pin.Note : All the bits about ALC operation operate by the default value when an ALC operation is started with the ALC pin without setting up a bit about ALC operation with the register. A bit about ALC operation operate by the setting value when a bit about ALC operation is set up with the register and an ALC operation is started with the ALC pin. Note : After ALC operation is disabled, the IPGA changes to the last written data during or before ALC operation.。

SY58018UMGTR中文资料

Part Number

16 15 14 13 12 11 10 9 5 6 7 8

Package Type MLF-16 MLF-16 MLF-16 MLF-16

Operating Range Industrial Industrial Industrial Industrial

SY58018UMI

Q GND GND /Q

IN0 /IN0 IN1 /IN1

1 2 3 4

SY58018UMITR(2) SY58018UMG(3) SY58018UMGTR(2, 3)

16-Pin MLF®

Notes: 1. Contact factory for die availability. Dice are guaranteed at TA = 25°C, DC electricals only. 2. Tape and Reel. 3. Pb-Free package recommended for new designs.

Precision Edge®

DESCRIPTION

The SY58018U is a 2.5V/3.3V precision, high-speed, 2:1 differential MUX capable of handling clocks up to 4GHz and data up to 5Gbps. The differential input includes Micrel’s unique, 3-pin input termination architecture that allows customers to interface to any differential signal (AC- or DC-coupled) as small as 100mV without any level shifting or termination resistor networks in the signal path. The outputs are 800mV, 100k compatible, LVPECL, with extremely fast rise/fall times guaranteed to be less than 110ps. The SY58018U operates from a 2.5V ±5% supply or a 3.3V ±10% supply and is guaranteed over the full industrial temperature range of –40°C to +85°C. For applications that require CML outputs, consider the SY58017U or for 400mV LVPECL outputs the SY58019U. The SY58018U is part of Micrel’s high-speed, Precision Edge® product line. All support documentation can be found on Micrel’s web site at .

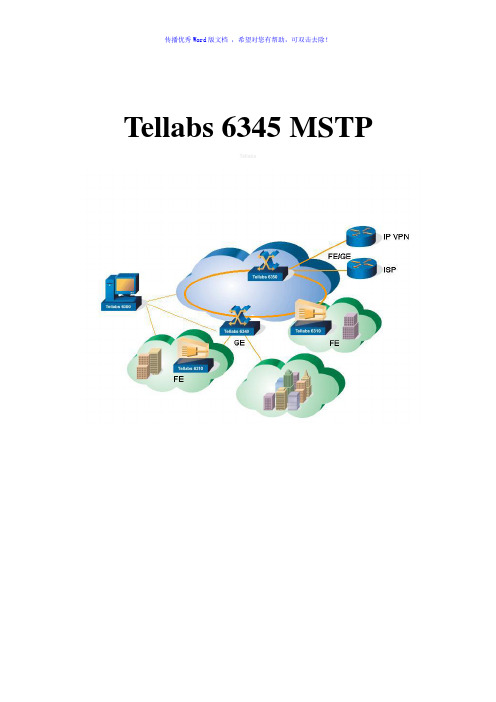

Tellabs6345中文Word版

Tellabs 6345 MSTPTellabs目录1 设备简介.......................................................................42 典型应用.......................................................................62.1 STM-64和STM-16 MSTP、链形网/环网/网状网................................62.2 环网互连................................................................62.3 SDXC 4/4 ...............................................................72.4 SDXC 4/1 ...............................................................72.5 以太网传送...............................................................82.5.1 以太网封装进SDH......................................................82.5.2 无缝带宽调整..........................................................82.5.3 以太网交换和承诺服务质量等级..........................................82.5.4 统计复用..............................................................92.5.5 IP解决方案............................................................92.6 基于Tellabs产品组合的解决方案............................................102.6.1 Tellabs 6345 MSTP与Tellabs 6320 MSTP和Tellabs 6340 MSTP组合.............102.6.2 Tellabs 6345 MSTP与Tellabs 6370 DWDM组合.............................112.7 容量升级................................................................112.7.1 从单STM-16环升级为多STM-16环.......................................112.7.2 从STM-16环升级为STM-64环...........................................112.7.3 从单STM-64环升级为多STM-64环.......................................123 系统描述.......................................................................133.1 接口类型................................................................133.2 模块化..................................................................133.3 同步结构................................................................133.4 管理系统................................................................143.5 子架....................................................................143.6 交叉连接...............................................................153.7 保护...................................................................154 配置范例.......................................................................175 平台概况.......................................................................191 设备简介Tellabs 6345 MSTP是Tellabs产品系列的一个重要组成部分,它是基于10Gb/s速率的多业务传送平台,专门用于电信传输网络,基于ETSI和ITU-T关于SDH和OTN的有关标准和建议。

F18 大黄蜂 战斗机 中文手册 GPS制导

AGM-84H SLAM-ER/AGM-154 JSOW/GBU-29/30/31 JDAM GPS 制导武器这三个系列的武器都使用最新的全球定位系统制导系统,同时也具有非常类似的HUD/SMS显示和控制。

AGM-84H SLAM-ER 是最初基于捕鲸叉反舰导弹的防区外攻击导弹的升级版本。

“ER”代表扩大的反应,这就意味着它比最初的SLAM型号具有更大的射程和准确性。

AGM-154 联合防区外武器(JSOW)被定于代替美国空军的GBU-15 和AGM-130 页就是美国海军的Walleye。

它是一种固定使用1000磅GP战斗部或集束子弹头的滑翔类武器。

GBU29/30/31联合直接攻击弹(JDAM)一个可使用1000和2000磅GP战斗部或2000磅渗透战斗部的武器家族。

JDAM被用于铺路石系列激光制导炸弹系列的补充武器,并总有一天将完全取代这个系列的武器。

GPS 制导武器HUD 符号这些武器的各个类型都使用相同基础的HUD符号:×上升操作线(仅在SLAM-ER):上升操作线提供到达选择的发射投放高度的提示。

×方位操作提示:方位操作提示提供一个相对于指定目标的最佳发射点的操作。

×在域提示:指出选择的武器发射符合的所有条件,和下面在GPS制导武器SMS MDI页面中描述的相同。

×武器选择/状态指示:在这个位置显示选择的武器类型。

×到达发射点的时间(TTLP):TTLP指出到达选择的武器的理想发射点的时间。

如果计算的TTLP 超过99 秒,那么显示将限制在99 秒直到TTLP 变得小于99 秒。

×到发射点距离(LP):以海浪表示的到达理想发射点的距离。

GPS 制导武器SMS(挂载)MDI 页面符号这些武器的各个挂载页面选项基于捕鲸叉挂载页面格式,彼此之间非常类似。

60×程序选择(PROG):这个选项按次序在各个可用的程序之间轮流。

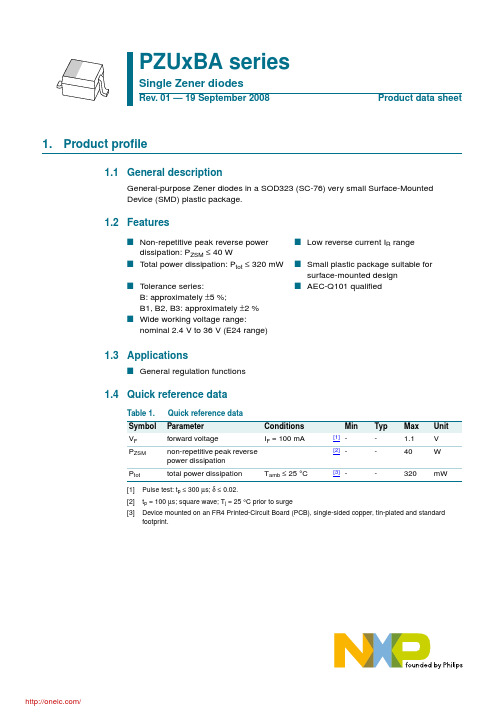

PZU5.1BA,115;PZU24BA,115;PZU6.2B2A,115;PZU7.5B3A,115;PZU3.9B1A,115;中文规格书,Datasheet资料

1.Product profile1.1General descriptionGeneral-purpose Zener diodes in a SOD323(SC-76) very small Surface-Mounted Device (SMD) plastic package.1.2Features1.3ApplicationsI General regulation functions1.4Quick reference data[1]Pulse test: t p ≤300µs;δ≤0.02.[2]t p =100µs; square wave; T j =25°C prior to surge[3]Device mounted on an FR4Printed-Circuit Board (PCB), single-sided copper, tin-plated and standard footprint.PZUxBA seriesSingle Zener diodesRev. 01 — 19 September 2008Product data sheetI Non-repetitive peak reverse power dissipation: P ZSM ≤40WI Low reverse current I R range I Total power dissipation: P tot ≤320mW I Small plastic package suitable for surface-mounted design I T olerance series:B:approximately ±5%;B1,B2,B3:approximately ±2%I AEC-Q101 qualifiedI Wide working voltage range:nominal 2.4V to 36V (E24range)Table 1.Quick reference data Symbol Parameter Conditions Min Typ Max Unit V F forward voltageI F =100mA[1]-- 1.1V P ZSM non-repetitive peak reverse power dissipation [2]--40W P tottotal power dissipationT amb ≤25°C [3]--320mW2.Pinning information[1]The marking bar indicates the cathode.3.Ordering information[1]The series consists of 97types with nominal working voltages from 2.4V to 36V .[2]/DG: halogen-freeTable 2.PinningPin Description Simplified outlineGraphic symbol1cathode [1]2anode21006aaa15221Table 3.Ordering informationType numberPackage NameDescriptionVersion PZU2.4BA to PZU36BA [1]SC-76plastic surface-mounted package; 2leadsSOD323PZU2.4BA/DG to PZU36BA/DG [1][2]4.MarkingTable 4.Marking codesType number[1]Marking code Type number[1]Marking codeB B1B2B3B B1B2B3PZU2.4*A X8---PZU2.4*A/DG Y8---PZU2.7*A X9XA XB-PZU2.7*A/DG Y9YA YB-PZU3.0*A XT XU XV-PZU3.0*A/DG YT YU YV-PZU3.3*A XW XX XY-PZU3.3*A/DG YW YX YY-PZU3.6*A XZ MC MD-PZU3.6*A/DG YZ NC ND-PZU3.9*A ME MF MG-PZU3.9*A/DG NE NF NG-PZU4.3*A MM MN MP MR PZU4.3*A/DG NM NN NP NRPZU4.7*A MS MT MU MV PZU4.7*A/DG NS NT NU NVPZU5.1*A MW MX MY MZ PZU5.1*A/DG NW NX NY NZPZU5.6*A LF LG LH LK PZU5.6*A/DG RF RG RH RKPZU6.2*A LL LM LN LP PZU6.2*A/DG RL RM RN RPPZU6.8*A LR LS LT LU PZU6.8*A/DG RR RS RT RUPZU7.5*A LV LW LX L Y PZU7.5*A/DG RV RW RX RYPZU8.2*A LZ CR CS CT PZU8.2*A/DG RZ ER ES ETPZU9.1*A CU CV CW CX PZU9.1*A/DG EU EV EW EXPZU10*A VA VB VC VD PZU10*A/DG WA WB WC WDPZU11*A VE VF VG VH PZU11*A/DG WE WF WG WHPZU12*A VK VL VM VN PZU12*A/DG WK WL WM WNPZU13*A VP VR VS VT PZU13*A/DG WP WR WS WTPZU14*A--VU-PZU14*A/DG--WU-PZU15*A VV VW VX VY PZU15*A/DG WV WW WX WYPZU16*A VZ X1X2X3PZU16*A/DG WZ Y1Y2Y3PZU18*A X4X5X6X7PZU18*A/DG Y4Y5Y6Y7PZU20*A XC XD XE XF PZU20*A/DG YC YD YE YFPZU22*A XG XH XK XL PZU22*A/DG YG YH YK YLPZU24*A XM XN XP XR PZU24*A/DG YM YN YP YRPZU27*A XS---PZU27*A/DG YS---PZU30*A MH---PZU30*A/DG NH---PZU33*A MK---PZU33*A/DG NK---PZU36*A ML---PZU36*A/DG NL---[1]* = B: tolerance series B, approximately±5%* = B1, B2, B3: tolerance series B1, B2, B3: approximately±2%5.Limiting values[1]t p =100µs; square wave; T j =25°C prior to surge[2]Device mounted on an FR4PCB, single-sided copper, tin-plated and standard footprint.[3]Device mounted on an FR4PCB, single-sided copper, tin-plated, mounting pad for cathode 1cm 2.6.Thermal characteristics[1]Device mounted on an FR4PCB, single-sided copper, tin-plated and standard footprint.[2]Device mounted on an FR4PCB, single-sided copper, tin-plated, mounting pad for cathode 1cm 2.[3]Soldering point of cathode tab.7.Characteristics[1]Pulse test: t p ≤300µs;δ≤0.02.Table 5.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol Parameter Conditions Min Max Unit I F forward current-200mAI ZSMnon-repetitive peak reverse current[1]-see Table 8and 9P ZSM non-repetitive peak reverse power dissipation [1]-40W P tot total power dissipation T amb ≤25°C[2]-320mW [3]-490mW T j junction temperature -150°C T amb ambient temperature −55+150°C T stgstorage temperature−65+150°CTable 6.Thermal characteristics Symbol ParameterConditions Min Typ Max Unit R th(j-a)thermal resistance from junction to ambient in free air[1]--390K/W [2]--255K/W R th(j-sp)thermal resistance from junction to solder point[3]--55K/WTable 7.CharacteristicsT j =25°C unless otherwise specified.Symbol Parameter ConditionsMin Typ Max Unit V Fforward voltage[1]I F =10mA --0.9V I F =100mA--1.1V[1]f =1MHz; V R =0V[2]t p =100µs; square wave; T j =25°C prior to surgeTable 8.Characteristics per type; PZU2.4BA to PZU5.6B3A and PZU2.4BA/DG to PZU5.6B3A/DG T j =25°C unless otherwise specified.PZUxBASelWorking voltage V Z (V)Differential resistance r dif (Ω)Reverse currentI R (µA)Temperature coefficient S Z (mV/K)Diode capacitance C d (pF)[1]Non-repetitivepeak reverse current I ZSM (A)[2]I Z =5mA I Z =0.5mA I Z =5mA I Z =5mA MinMax Max Max Max V R (V)Typ Max Max 2.4B 2.3 2.61000100501−1.645082.7B 2.5 2.91000100201−2.04408B1 2.5 2.75B22.65 2.93.0B 2.8 3.2100095101−2.14258B1 2.8 3.05B22.953.23.3B 3.1 3.510009551−2.44108B1 3.1 3.35B23.25 3.53.6B 3.4 3.810009051−2.43908B1 3.4 3.65B23.55 3.83.9B 3.7 4.110009031−2.53708B1 3.7 3.97B23.874.104.3B 4.01 4.4810009031−2.53508B1 4.01 4.21B2 4.15 4.34B34.28 4.484.7B 4.42 4.98008021−1.43258B1 4.42 4.61B2 4.55 4.75B34.69 4.95.1B 4.84 5.37250602 1.50.3300 5.5B1 4.84 5.04B2 4.98 5.2B35.14 5.375.6B 5.31 5.92100401 2.5 1.9275 5.5B1 5.31 5.55B2 5.49 5.73B35.675.92Table 9.Characteristics per type; PZU6.2BA to PZU36BA and PZU6.2BA/DG to PZU36BA/DG T j=25°C unless otherwise specified.PZUxBA Sel WorkingvoltageV Z(V)Differential resistancer dif(Ω)ReversecurrentI R(nA)TemperaturecoefficientS Z(mV/K)DiodecapacitanceC d(pF)[1]Non-repetitivepeak reversecurrentI ZSM(A)[2]I Z=5mA I Z=0.5mA I Z=5mA I Z=5mAMin Max Max Max Max V R(V)Typ Max Max 6.2B 5.86 6.5380305003 2.7250 5.5B1 5.86 6.12B2 6.06 6.33B3 6.26 6.536.8B 6.477.146020500 3.5 3.4215 5.5B1 6.47 6.73B2 6.65 6.93B3 6.867.147.5B7.067.8460105004 4.0170 3.5B17.067.36B27.287.60B37.527.848.2B7.768.6460105005 4.6150 3.5B17.768.1B28.028.36B38.288.649.1B8.569.5560105006 5.5120 3.5B18.568.93B28.859.23B39.159.5510B9.4510.5560101007 6.4110 3.5 B19.459.87B29.7710.21B310.1110.5511B10.4411.56601010087.41083 B110.4410.88B210.7611.22B311.111.5612B11.4212.6801010098.41053 B111.4211.9B211.7412.24B312.0812.613B12.4713.968010100109.4103 2.5 B112.4713.03B212.9113.49B313.3713.96[1]f =1MHz; V R =0V[2]t p =100µs; square wave; T j =25°C prior to surge14B213.7014.3080101001110.4101215B 13.8415.528015501111.4992B113.8414.46B214.3414.98B314.8515.5216B 15.3717.098020501212.497 1.5B115.3716.01B215.8516.51B316.3517.0918B 16.9419.038020501314.493 1.5B116.9417.7B217.5618.35B318.2119.0320B 18.8621.0810020501516.488 1.5B118.8619.7B219.5220.39B320.2121.0822B 20.8823.1710025501718.484 1.3B120.8821.77B221.5422.47B322.2323.1724B 22.9325.5712030501920.480 1.3B122.9323.96B223.7224.78B324.5425.5727B 25.128.915040502123.473130B 283220040502326.666133B 313525*********.7600.936B343830060502733.0590.8Table 9.Characteristics per type; PZU6.2BA to PZU36BA and PZU6.2BA/DG to PZU36BA/DG …continued T j =25°C unless otherwise specified.PZUxBASelWorking voltage V Z (V)Differential resistance r dif (Ω)Reverse currentI R (nA)Temperature coefficient S Z (mV/K)Diode capacitance C d (pF)[1]Non-repetitivepeak reverse current I ZSM (A)[2]I Z =5mA I Z =0.5mA I Z =5mA I Z =5mA MinMaxMaxMax Max V R (V)Typ Max MaxT j =25°C (prior to surge)T j =25°CFig 1.Non-repetitive peak reverse power dissipation as a function of pulse duration; maximum valuesFig 2.Forward current as a function of forward voltage; typical valuesT j =25°C to 150°C V Z =2.4V to 4.3VT j =25°C to 150°C V Z =4.7V to 12VFig 3.Temperature coefficient as a function of working current; typical valuesFig 4.Temperature coefficient as a function of working current; typical values006aab21510210103P ZSM (W)1t p (s)10−410−210−3V F (V)0.610.8mbg781100200300I F (mA)00600−2−3−1mgl2732040I Z (mA)S Z (mV/K)4.33.93.63.33.02.42.702016100−55mgl2744812I Z (mA)S Z (mV/K)4.71211109.18.27.56.86.25.65.1T j =25°C V Z =2.4V to 4.3VT j =25°C V Z =4.7V to 12VFig 5.Working current as a function of working voltage; typical valuesFig 6.Working current as a function of working voltage; typical valuesT j =25°C V Z =13V to 36VFig 7.Working current as a function of working voltage; typical values006aab24610−110−2101102I Z (mA)10−3V Z (V)054231V Z(nom) (V) = 2.42.73.03.33.63.94.3006aab24710−110−2101102I Z (mA)10−3V Z (V)01410128624V Z(nom) (V) = 4.75.15.66.26.87.58.29.1101112006aab24810−110−2101102I Z (mA)10−3V Z (V)10403020V Z(nom) (V) = 1318202224273033361415168.Test information8.1Quality informationThis product has been qualified in accordance with the Automotive Electronics Council (AEC) standard Q101 - Stress test qualification for discrete semiconductors , and is suitable for use in automotive applications.9.Package outline10.Packing information[1]For further information and the availability of packing methods, see Section 13.Fig 8.Package outline SOD323(SC-76)03-12-17Dimensions in mm0.250.100.450.152.72.3 1.81.60.400.251.10.81.351.1512Table 10.Packing methodsThe indicated -xxx are the last three digits of the 12NC ordering code.[1]Type number Package DescriptionPacking quantity 300010000PZU2.4BA to PZU36BA SOD3234mm pitch, 8mm tape and reel-115-135PZU2.4BA/DG to PZU36BA/DG分销商库存信息:NXPPZU5.1BA,115PZU24BA,115PZU6.2B2A,115 PZU7.5B3A,115PZU3.9B1A,115PZU20B1A,115 PZU10BA,115PZU11BA,115PZU12BA,115 PZU13BA,115PZU15BA,115PZU16BA,115 PZU18BA,115PZU2.4BA,115PZU2.7BA,115 PZU20BA,115PZU22BA,115PZU27BA,115 PZU3.0BA,115PZU3.3BA,115PZU3.6BA,115 PZU3.9BA,115PZU30BA,115PZU33BA,115 PZU36BA,115PZU4.3BA,115PZU4.7BA,115 PZU5.6BA,115PZU6.2BA,115PZU6.8BA,115 PZU5.1B1A,115PZU10B1A,115PZU10B2A,115 PZU10B3A,115PZU11B1A,115PZU11B2A,115 PZU11B3A,115PZU12B1A,115PZU12B2A,115 PZU12B3A,115PZU13B1A,115PZU13B2A,115 PZU13B3A,115PZU14B2A,115PZU15B1A,115 PZU15B2A,115PZU15B3A,115PZU16B1A,115 PZU16B2A,115PZU16B3A,115PZU18B1A,115 PZU18B2A,115PZU18B3A,115PZU2.7B1A,115 PZU2.7B2A,115PZU20B2A,115PZU20B3A,115 PZU22B1A,115PZU22B2A,115PZU22B3A,115 PZU24B1A,115PZU24B2A,115PZU24B3A,115 PZU3.0B1A,115PZU3.0B2A,115PZU3.3B1A,115 PZU3.3B2A,115PZU3.6B1A,115PZU3.6B2A,115 PZU4.3B1A,115PZU8.2B1A,115PZU8.2B2A,115。

5833中文资料