实验六 触发器

基本门电路逻辑功能的测试

河 北 科 技 大 学实 验 报 告级 专业 班 学号 年 月 日姓 名 同组人 指导教师 王计花 任课教师 实验名称 实验二 基本门电路逻辑功能的测试 成 绩 实验类型 验证型 批阅教师一、实验目的(1)掌握常用门电路的逻辑功能,熟悉其外形及引脚排列图。

(2)熟悉三态门的逻辑功能及用途。

(3)掌握TTL 、CMOS 电路逻辑功能的测试方法。

二、实验仪器与元器件(1)直流稳压电源 1台 (2)集成电路74LS00 四2输入与非门 1片 74LS86 四2输入异或门 1片 74S64 4-2-3-2输入与或非门 1片 74LS125 四总线缓冲门(TS ) 1片 CD4011 四2输入与非门1片三、实验内容及步骤1.常用集成门电路逻辑功能的测试在数字实验板上找到双列直插式集成芯片74LS00和74LS86。

按图进行连线。

测试各电路的逻辑功能,并将输出结果记入表中。

门电路测试结果2.测试与或非门74S64的逻辑功能在实验板上找到芯片74S64,实现Y AB CD =+的逻辑功能。

真值表A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 YA B Y (00) Y (86)0 0 0 1 1 0 1 1Y Y &3.用与非门组成其他逻辑门电路 (1)用与非门组成与门电路按图接线,按表测试电路的逻辑功能。

根据测得的真值表,写出输出Y的逻辑表达式。

真值表逻辑表达式:(2)用与非门组成异或门电路按图接线,将测量结果记入表中,并写出输出Y 的逻辑表达式。

真值表逻辑表达式:真值表4.三态门测试(1)三态门逻辑功能测试三态门选用 74LS125将测试结果记入表中。

(2)按图接线。

将测试结果记录表中。

计算机信息管理专业课程实验

计算机信息管理专业课程实验课程编码课程名称课程实验内容实验性质学时计算机应用基础统必 45 1(实验一:WindowsXP基本操作和汉字输入练习2(实验二: 文字编辑和排版3(实验三:表格编辑4(实验四:演示文稿制作5(实验五: 因特网接入、浏览网页和电子邮件的收发网络实用技术基础统必 24 实验一局域网安装与使用实验二 Internet接入与应用实验三 Windows 2000 安装与配置实验四局域网交换机设置实验五路由器的基本设置实验六网络安全54 统必 Dreamweaver网页设计实训1:基本网页设计实训2利用表格进行网页排版实训3使用页面布局模式实训4对网页进行排版应用CSS样式表实训5在网页中应用模板实训6在网页中应用库实训7在网页中插入导航条和翻转按钮实训8插入Flash及多媒体内容实训9使用层进行网页的排版和布局选做实训题实训1:插入Flash及多媒体内容实训2:自行设计和制作个人网站实训3:自行设计和制作商业网站数据库基础与应用统必 42 本课程必做实验共42学时,具体题目如下:(1) ACCESS实验内容12学时实验一表的操作实验二查询操作实验三窗体的操作实验四报表的操作实验五宏与数据访问页的使用实验六数据导入与导出(2) SQL Server实验内容30学时实验一安装与配置SQL Server实验二创建“进销存”数据库实验三创建表和索引实验四备份与恢复数据库实验五 Transact-SQL综合查询应用实验六触发器设计实验七存储过程设计(选做)实验八数据库安全性管理(选做) 实验九 ODBC及SQL Server应用程序设计(选做)36 限选 Visual Basic程序设计实验一:Visual Basic开发环境实验二:简单程序设计实验三:菜单设计实验四:鼠标、键盘、API函数调用实验五:文件管理程序设计实验六:绘图和多媒体应用实验七:数据库应用程序设计实验八:网络应用程序设计实验九:简单程序调试及错误处理实验十:ActiveX的简单应用。

实验六 触发器

实验六触发器一、实验目的1. 学习触发器逻辑功能的测试方法。

2. 熟悉基本RS触发器的组成、工作原理和性能。

3. 熟悉集成JK触发器和D触发器的逻辑功能及触发方式。

二、实验原理触发器具有两个稳定状态,用以表示逻辑状态“1”和逻辑状态“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存储器件,是构成各种时序电路的最基本的逻辑单元。

1.基本RS触发器基本RS触发器是一种无时钟控制的低电平直接触发的触发器。

它具有置“0”、置“1”和“保持”三种功能。

通常S端为置“1”端,因为S=0时触发器被置“1”;R为置“0”端,因为R=0时触发器被置“0”;当S=R=1时,状态保持。

基本RS触发器可以用两个“与非门”(如图6-1)或两个“或非门”组成。

2.JK触发器在输入信号为双端输入的情况下,JK触发器是功能完善、使用灵活和通用性较强的一Q+K Q n,J和K是数据输入端,是触发器状态更新的种触发器。

其状态方程为:Q n+1=J n依据,若J、K有两个或两个以上输入端时,组成“与”的关系。

Q与Q为两个互补输出端,通常把Q=0、Q=1的状态规定为触发器的“0”状态;而把Q=1、Q=0规定为“1”状态。

JK触发器输出状态的更新发生在CP脉冲的下降沿。

JK触发器通常被用作缓冲存储器、移位寄存器和计数器等。

3.D触发器在输入信号为单端输入的情况下,D触发器用起来比较方便。

它的状态方程为:Q n+1=D n,其输出状态的更新发生在CP脉冲的上升沿,所以又称为上升沿触发的边沿触发器。

触发器的状态只取决于时钟到来前D端的状态,D触发器可用作数字信号的寄存、移位寄存、分频和波形发生等。

4.触发器间的转换在集成触发器中,每一种触发器都有自己固定的逻辑功能。

我们可以利用转换的方法获得具有其它功能的触发器。

例如将JK触发器转换成T和Tˊ触发器,也可将JK触发器转换成D触发器。

三、实验仪器及器件1. DS1052E型示波器2. EL-ELL-Ⅳ型数字电路实验系统3. 器件:集成电路芯片74LS00 74LS112 74LS74四、实验内容及步骤1.基本RS 触发器的逻辑功能测试在实验仪上选用74LS00,按图6-1连接实验电路,即为基本RS 触发器。

实验六 触发器实验报告

实验六触发器实验报告一、实验目的本次实验的主要目的是深入理解触发器的工作原理和应用,通过实际操作和观察,掌握触发器在数字电路中的功能和特性。

二、实验原理触发器是一种具有记忆功能的基本逻辑单元,能够存储一位二进制信息。

常见的触发器类型有 SR 触发器、JK 触发器、D 触发器和 T 触发器等。

以 D 触发器为例,其工作原理是在时钟脉冲的上升沿或下降沿,将输入数据D 传递到输出端Q。

在没有时钟脉冲时,输出状态保持不变。

三、实验设备与材料1、数字电路实验箱2、 74LS74 双 D 触发器芯片3、示波器4、导线若干四、实验内容与步骤1、用 74LS74 芯片搭建 D 触发器电路将芯片插入实验箱的插座中,按照芯片引脚功能连接电源、地和输入输出引脚。

使用导线将 D 输入端连接到逻辑电平开关,将时钟输入端连接到脉冲信号源,将 Q 和 Q'输出端连接到发光二极管或逻辑电平指示器。

2、测试 D 触发器的功能置 D 输入端为高电平(1),观察在时钟脉冲作用下 Q 输出端的变化。

置 D 输入端为低电平(0),再次观察时钟脉冲作用下 Q 输出端的变化。

3、观察 D 触发器的异步置位和复位功能将异步置位端(PRE)和异步复位端(CLR)分别连接到逻辑电平开关,测试在置位和复位信号作用下触发器的状态。

4、用示波器观察时钟脉冲和 Q 输出端的波形将示波器的探头分别连接到时钟脉冲输入端和 Q 输出端,调整示波器的设置,观察并记录波形。

五、实验结果与分析1、在 D 输入端为高电平时,每当时钟脉冲的上升沿到来,Q 输出端变为高电平;在D 输入端为低电平时,每当时钟脉冲的上升沿到来,Q 输出端变为低电平,验证了 D 触发器的正常功能。

2、当异步置位端(PRE)为低电平时,无论其他输入如何,Q 输出端立即变为高电平;当异步复位端(CLR)为低电平时,Q 输出端立即变为低电平,表明异步置位和复位功能有效。

3、从示波器观察到的波形可以清晰地看到时钟脉冲与 Q 输出端的关系,进一步验证了触发器的工作特性。

数字电路 实验 计数器及其应用 实验报告

实验六计数器及其应用一、实验目的1.学习用集成触发器构成计数器的方法2.掌握同步计数的逻辑功能、测试方法及功能扩展方法3.掌握构成任意进制计数器的方法二、实验设备和器件1.+5V直流电源2.双踪示波器3.连续脉冲源4.单次脉冲源5.逻辑电平开关6.逻辑电平显示器7.译码显示器8.CC4013×2(74LS74)CC40192×3(74LS192)CC4011(74LS00)CC4012(74LS20)三、实验原理计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

计数器计数时所经历的独立状态总数为计数器的模(M)。

计数器按模可分为二进计数器(M=2n)、十进计数器(M=10n)和任意进制计数器(M≠2n、M≠10n)。

按计数脉冲输入方式不同,可分为同步计数和异步计数。

按计数值增减趋势分为:加法计数器、减法计数器和可逆(加/减)计数器。

1.用D触发器构成异步二进制加/减计数器图6-1是用四只D触发器构成的四位二进制异步加法计数器,它的连接特点是将每只D触发器接成T 触发器,再由低位触发器的Q端和高一位的CP端相连接。

若将图6-1稍加改动,即将低位触发器的Q端与高一位的CP端相连接,即构成了一个4位二进制减法计数器。

2.中规模十进制计数器、十六进制计数器(1)CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能。

当清除端CR为高电平“1”时,计数器直接清零;CR置低电平则执行其它功能。

当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3置入计数器。

当CR为低电平,LD为高电平时,执行计数功能。

执行加计数时,减计数端CP D接高电平,计数脉冲由CP U输入;在计数脉冲上升沿进行8421码十进制加法计数。

执行减计数时,加计数端CP U接高电平,计数脉冲由减计数端CP D 输入,表6-2为8421码十进制加、减计数器的状态转换表。

实验_六计数、译码和显示电路(Y)

十进制计数器 CT74LS160(162)与二进制计数器 74LS161(163) 比较

Q0

Q1

Q2

Q3

Q0

Q1

Q2

Q3

CP

CTT CTT CTP CT74LS161 CO CTP CT74LS160 CO CT74LS163 CT74LS162 (162)与 CR LD D0 D1 D2 D3 D3 CP CR LD D0 D1 D2CT74LS160 CT74LS161(163)有何不同? CR LD

0 1 2 3 4 5 6 7 8 9 10

也可取 D3 D2 D1 D0 = 0011 LD = CO CO = Q3 Q0

方案 2:用 “160” 的后七个状态 0011 ~ 1001实现七进制计数。

取 D3 D2 D1 D0 = 0011 ,LD = CO

1 CP

CTT Q0 Q1 Q2 Q3 CTP CT74LS160 CO

00 0 0

01 0

Z

11 0 0

10 1

Q3 Q2 Q1

n +1 n +1 n +1

= Q 2n

= Q 1n = Q 3n

即:

Q3n+1(010)=1, Q3n+1(101)=0

Q2n+1(010)=0 , Q2n+1(101)=1 Q1n+1(010)=1 , Q1n+1(101)=0

010 101

Z = Q 3n Q 2n 自启动失败, 改变 Q1:

Q1

n +1

n n = Q3n + Q2 Q1

010

101

这样:Q1n+1(010)=1, Q1n+1(101)=1 明显的, 能够自启动

触发器功能测试实验报告

触发器功能测试实验报告触发器功能测试实验报告一、引言触发器是数字电路中常见的重要元件之一,其具有存储和放大信号的功能。

触发器的功能测试是电子工程师在设计和制造数字电路时必不可少的一项工作。

本实验旨在通过对不同类型的触发器进行功能测试,验证其在不同工作模式下的正确性和稳定性。

二、实验目的1. 了解触发器的基本原理和工作模式;2. 掌握触发器的功能测试方法;3. 验证不同类型触发器的工作特性。

三、实验器材和材料1. 实验板;2. 电源供应器;3. 逻辑分析仪;4. 电压表;5. 连接线。

四、实验步骤1. 准备工作:将实验板连接好电源供应器和逻辑分析仪,并确保连接正确;2. 功能测试:依次测试RS触发器、D触发器、JK触发器和T触发器的工作特性。

五、实验结果与分析1. RS触发器测试:a. 将RS触发器的S端和R端分别接入逻辑分析仪的输入端,CLK端接入逻辑分析仪的时钟信号输出端;b. 通过逻辑分析仪观察输入信号和输出信号的波形,并记录下来;c. 分析波形,验证RS触发器在不同输入情况下的工作特性。

2. D触发器测试:a. 将D触发器的D端接入逻辑分析仪的输入端,CLK端接入逻辑分析仪的时钟信号输出端;b. 通过逻辑分析仪观察输入信号和输出信号的波形,并记录下来;c. 分析波形,验证D触发器在不同输入情况下的工作特性。

3. JK触发器测试:a. 将JK触发器的J端和K端分别接入逻辑分析仪的输入端,CLK端接入逻辑分析仪的时钟信号输出端;b. 通过逻辑分析仪观察输入信号和输出信号的波形,并记录下来;c. 分析波形,验证JK触发器在不同输入情况下的工作特性。

4. T触发器测试:a. 将T触发器的T端接入逻辑分析仪的输入端,CLK端接入逻辑分析仪的时钟信号输出端;b. 通过逻辑分析仪观察输入信号和输出信号的波形,并记录下来;c. 分析波形,验证T触发器在不同输入情况下的工作特性。

六、实验结论通过对RS触发器、D触发器、JK触发器和T触发器的功能测试,我们可以得出以下结论:1. RS触发器具有存储和放大信号的功能,可以用于实现简单的存储器和时序电路;2. D触发器可以将输入信号在时钟脉冲到来时存储,并在下一个时钟脉冲到来时输出;3. JK触发器是一种带有异步清零和置位功能的触发器,可以用于实现频率分割和计数器等电路;4. T触发器是一种特殊的JK触发器,其输入端和输出端相连,可以实现频率分割和频率加倍等功能。

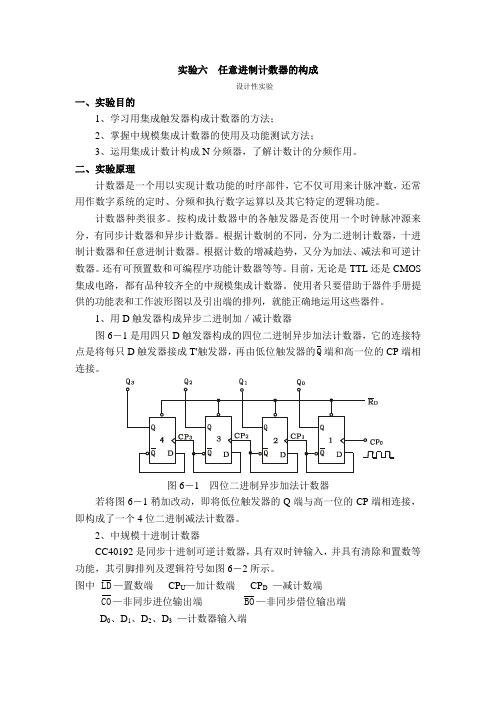

实验六 任意进制计数器的构成

实验六任意进制计数器的构成设计性实验一、实验目的1、学习用集成触发器构成计数器的方法;2、掌握中规模集成计数器的使用及功能测试方法;3、运用集成计数计构成N分频器,了解计数计的分频作用。

二、实验原理计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。

根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。

根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等等。

目前,无论是TTL还是CMOS 集成电路,都有品种较齐全的中规模集成计数器。

使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。

1、用D触发器构成异步二进制加/减计数器图6-1是用四只D触发器构成的四位二进制异步加法计数器,它的连接特点是将每只D触发器接成T'触发器,再由低位触发器的Q端和高一位的CP端相连接。

图6-1 四位二进制异步加法计数器若将图6-1稍加改动,即将低位触发器的Q端与高一位的CP端相连接,即构成了一个4位二进制减法计数器。

2、中规模十进制计数器CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如图6-2所示。

图中LD—置数端CP U—加计数端CP D—减计数端CO—非同步进位输出端BO—非同步借位输出端D0、D1、D2、D3—计数器输入端Q 0、Q 1、Q 2、Q 3 —数据输出端 CR图6-2 CC40192引脚排列及逻辑符号CC40192(同74LS192,二者可互换使用)的功能如表6-1,说明如下:当清除端CR 为高电平“1”时,计数器直接清零;CR 置低电平则执行其它功能。

当CR 为低电平,置数端LD 也为低电平时,数据直接从置数端D 0、D 1、D 2、D 3 置入计数器。

EDA实验报告xianxi

数字电路EDA可编程逻辑实验报告学院:电子工程学院班级:学号:姓名:西安邮电大学电子工程学院电工电子实验教学部实验二:用原理图输入法设计门电路实验目的:1.进一步掌握PLD芯片的基本使用方法,熟悉EDA软件MAX+plus的操作。

2.学会利用软件仿真和实现用硬件对数字电路的逻辑功能进行验证和分析。

3.学习初步的VHDL程序设计方法。

器材:PC实验内容:实现1、F=a∙b2、F=a b3、F=A⊕B4、F=abc d实验结果:1、F=a∙b源程序:library ieee;use ieee.std_logic_1164.all;entity and2 isport(a,b:in std_logic;y:out std_logic);end;architecture rel_1 of and2 isbeginy<=a and b;end;仿真结果:2、F=a b源程序:library ieee;use ieee.std_logic_1164.all; entity nand2 isport(a,b:in std_logic;y:out std_logic); end;architecture rel_1 of nand2 is beginy<=a nand b;end;仿真结果:3、F=A⊕B源程序:library ieee;use ieee.std_logic_1164.all; entity xor2 isport(a,b:in std_logic;y:out std_logic); end;architecture rel_1 of xor2 is beginy<=a xor b;end;仿真结果:4、F=abc d源程序:library ieee;use ieee.std_logic_1164.all; entity yhf isport(a,b,c,d:in std_logic;F:out std_logic); end;architecture rel_1 of yhf is signal g,h,y:std_logic; beging<=not a and b and c;h<=not d;y<=g or h;F<=y;end;仿真结果:实验小结:本实验为第一次EDA实验,不免有些兴奋和好奇,加之老师讲的比较好,所以基本上没有遇到什么问题。

实验六实验报告

实验六实验报告云南大学软件学院实验报告课程:数据库原理与实用技术实验任课教师:包崇明姓名:匿名学号:2013…….专业:软件工程成绩:实验6 数据库完整性实验6-1 完整性约束1、在学生表上面创建下列CHECK约束【注】:因为学生表已经存在,所以这里使用添加check约束的方法实现:(1)创建入学日期约束“Enter_University_date_rule”,假定该学校于1923年4月30日创建。

要求:入学日期必须大于等于学校创建日期,并且小于等于当前日期测试语句:结果(添加的check约束起作用了),如图:(2)创建学生年龄约束“Age_rule”。

要求:学生年龄必须在15~30岁之间测试语句结果(添加”Age_rule”成功,并且年龄为’2015/4/27’没有违反”Enter_University_date_rule”约束,进一步说明了(1)中的check约束添加成功,如图:【注】:考虑到时间关系,下面的部分解答中将会省略测试约束的步骤。

(3)创建学生性别约束“Sex_rule”。

要求:性别只能为“男”或“女”(4)创建学生成绩约束“Score_rule”。

要求:学生成绩只能在0~100之间(5)用图形方法查看学生成绩约束“Score_rule”,截图为:2、删除约束Enter_University_date_rule测试语句:结果:(更新成功)3、创建声明式默认约束:在创建表的过程中创建默认约束(1)创建表“default_example”,表中包含字段pid、name、sex、age。

要求设定sex的默认值为“男”、age的默认值为18。

创建default_example表语句:采用SQL语句进行插入元祖:执行结果为:(默认值起作用了!!)(2)插入一条编号为100 的记录,执行结果为:(3)修改默认值一般先删除老的默认约束,再新建一个默认约束方法如下:删除约束:alter TABLE default_example drop 约束名新建默认约束:alter TABLE default_example add constraint df_age default(20) for age①删除老的默认约束:②新建默认约束:请将年龄默认值更改为19,执行结果为:测试语句:结果(默认年龄被修改为19),如图:3、在“学生管理数据库”各个数据表中建立相应的主键、外键、惟一值、以及check约束,要求:学生的年龄必须是两位数,其中第一位是1或2:(1)学生表【添加主键和年龄约束】:(2)授课表【添加主键和外键】:(3)课程表【添加主键】:(4)成绩表【添加主键和外键】:第一次添加外键失败,因为两个表中的学号长度不等,所以我需要修改使其相等再添加。

实验六 三相桥式全控整流及有源逆变电路实验

实验六三相桥式全控整流及有源逆变电路实验实验六三相桥式全控整流及有源逆变电路实验实验六三相桥式全控整流与有源逆变电路实验一、实验目的(1)加深对三相桥式全控整流和有源逆变电路工作原理的理解。

(2)了解KC系列集成触发器的调整方法及各点的波形。

2、实验所需的挂件和附件序列号为12345678型djk01电源控制面板djk02晶闸管主电路djk02-1三相晶闸管触发电路djk06设定和实验装置djk10变压器实验d42三相可调电阻双道示波器万用表。

挂件包括“触发电路”、“正负桥功率放大器”等模块。

挂件包含几个模块,如“二极管”。

挂件包括“逆变变压器”和“三相非受控整流器”。

自备备注控制面板包括“三相电源输出”等几个模块。

3、实验电路和原理如图3-6和3-7所示。

主电源电路由三相全控整流电路和三相不控整流电路组成,作为逆变直流电源。

触发电路是djko2-1中的集成触发电路,由kco4、kc4l、kc42等集成芯片组成,经高频调制后可输出双窄脉冲链。

三相桥式整流器和逆变电路的工作原理见电力电子技术教材的相关内容。

芯式变压力装置图3-6三相桥式全控整流电路实验原理图在三相桥式有源逆变电路中,电阻和电感与整流器一致,而三相非受控整流器和铁芯变压器位于djk10悬挂式支架上。

铁芯变压器用作升压变压器,逆变器输出的电压连接到铁芯变压器的中压端子am、BM和cm,返回电网的电压从高压端子a、B和C输出,变压器连接成Y/Y连接。

图中的r均使用d42三相可调电阻,将两个900ω接成并联形式;电感ld在djk02面板上,选用700mh,直流电压、电流表由djk02获得。

图3-7三相桥式有源逆变电路实验原理图四、实验内容(1)三相桥式全控整流电路。

(2)三相桥式有源逆变电路。

(3)在整流或有源逆变状态下,当触发电路出现故障(人为模拟)时观测主电路的各电压波形。

五、预览需求(1)阅读电力电子技术教材中有关三相桥式全控整流电路的有关内容。

实验六-JK触发器的VHDL设计复习过程

实验六-J K触发器的V H D L设计实验六 JK触发器的VHDL设计设计JK触发器,其中prn(置1端)、clrn(清零端)均为高电平有效,当prn(置1端)、clrn(清零端)均为低电平时,cp上升沿来临输出q、q_not根据J、K的值有不同的输出。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity chufa_JK isport(cp,j,k,prn,clrn:in std_logic;q,q_not: out std_logic);end chufa_JK;architecture arch of chufa_JK issignal qn:std_logic;beginprocess(cp,prn,clrn)beginif clrn='1'and prn='0' then ----------异步(强制)置0qn<='0';elsif prn='1'and clrn='0'then ---------异步(强制)置1qn<='1';elsif cp'event and cp='1' then ---------cp上升沿qn<=(j and not qn) or(not k and qn);end if;end process;q<=qn;q_not<=not qn;end arch; 1、波形仿真分析prn(置1端)clrn(清零端)cp J K Q Q_not0 1 x x x 0 11 0 x x x 1 00 0 上升沿0 0 保持保持0 0 上升沿0 1 0 10 0 上升沿 1 0 1 00 0 上升沿 1 1 翻转翻转注意:此JK触发器设计中prn(置1端)、clrn(清零端)均为高电平有效,当prn(置1端)、clrn(清零端)均为低电平时,cp上升沿来临输出q、q_not 根据J、K的值有不同的输出。

SQL数据库实验报告实验六

第1部分实验8 存储过程和触发器1.实验目的(1)掌握通过SQL Server 管理平台和Transact-SQL 语句CREA TE PROCEDURE 创建存储过程的方法和步骤。

(2)掌握使用Transact-SQL 语句EXECUTE 执行存储过程的方法。

(3)掌握通过SQL Server 管理平台和Transact-SQL 语句ALTER PROCEDURE 修改存储过程的方法。

(4)掌握通过SQL Server 管理平台和Transact-SQL 语句DROP PROCEDURE 删除存储过程的方法。

(5)掌握通过SQL Server 管理平台和Transact-SQL 语句CREA TE TRIGGER 创建触发器的方法和步骤。

(6)掌握引发触发器的方法。

(7)掌握使用SQL Server 管理平台或Transact-SQL 语句修改和删除触发器。

2.实验内容及步骤(1)在查询设计器中输入以下代码,创建一个利用流控制语句的存储过程letters_print ,该存储过程能够显示26个小写字母。

CREATE PROCEDURE letters_print ASDECLARE @count int SET @count=0 WHILE @count<26 BEGINPRINT CHAR(ASCII('a')+ @count) SET @count=@count +1 END单击查询分析器的“执行查询”按钮,查看studentsdb 数据库的存储过程是否有letters_print 。

使用EXECUTE 命令执行letters_print 存储过程。

(2)输入以下代码,创建存储过程stu_info,执行时通过输入姓名,可以查询该姓名对应的学生的各科成绩。

CREATE PROCEDURE stu_info @name varchar(40)ASSELECT a.学号,姓名,课程编号,分数FROM student_info a INNER JOIN grade taON a.学号= ta.学号WHERE 姓名= @name使用EXECUTE命令执行存储过程stu_info,其参数值为“马东”。

数电实验——精选推荐

实验一 TTL集成逻辑门的参数测试一、实验目的1、了解TTL与非门各参数的意义。

2、掌握TTL集成门电路的逻辑功能和参数测试方法。

二、实验原理、方法和手段TTL集成与非门是数字电路中广泛使用的一种逻辑门,使用时,必须对它的逻辑功能、主要参数和特性曲线进行测试,以确定其性能好坏。

本实验主要是对TTL集成与非门74LS20进行测试,该芯片外形为DIP双列直插式结构。

原理电路、逻辑符号和管脚排列如图1-1(a)、(b)、(c)所示。

图1-1 74LS20芯片原理电路、逻辑符号和封装引脚图1. 与非门的逻辑功能与非门的逻辑功能是:当输入端有一个或一个以上的低电平时,输出端为高电平;只有输入端全部为高电平时,输出端才是低电平。

(即有“0”得“1”,全“1”得“0”。

)对与非门进行测试时,门的输入端接逻辑开关,开关向上为逻辑“1”,向下为逻辑“0”。

门的输出端接电平指示器,发光管亮为逻辑“1”,不亮为逻辑“0”。

与非门的逻辑表达式为:Q ABCD2. TTL与非门的主要参数(1)低电平输出电源电流I CCL与高电平输出电源电流I CCH与非门在不同的工作状态,电源提供的电流是不同的。

I CCL 是指输出端空载,所有输入端全部悬空,(与非门处于导通状态),电源提供器件的电流。

I CCH 是指输出端空载,每个门各有一个以上的输入端接地,其余输入端悬空,(与非门处于截止状态),电源提供器件的电流。

测试电路如图1-2(a)、(b)所示。

通常I CCL >I CCH ,它们的大小标志着与非门在静态情况下的功耗大小。

导通功耗:P CCL =I CCL ×U CC 截止功耗:P CCH =I CCH ×U CC由于I CCL 较大,一般手册中给出的功耗是指P CCL 。

注意:TTL 电路对电源电压要求较严,电源电压V CC 允许在+5±10%的电压范围内工作,超过5.5V 将损坏器件;低于4.5V 器件的逻辑功能将不正常。

触发器实验报告

触发器实验报告一、实验目的本次实验的主要目的是深入了解和掌握触发器的工作原理、功能特点以及其在数字电路中的应用。

通过实际操作和观察,提高对触发器逻辑功能的理解和运用能力,为进一步学习数字电路的相关知识打下坚实的基础。

二、实验设备与器材1、数字电路实验箱2、双踪示波器3、集成电路芯片:74LS74(D 触发器)、74LS112(JK 触发器)4、若干导线三、实验原理(一)D 触发器D 触发器是一种在时钟脉冲上升沿或下降沿触发的触发器,其逻辑功能为:当 D 端输入为 1 时,在时钟脉冲的作用下,输出 Q 变为 1;当 D 端输入为 0 时,在时钟脉冲的作用下,输出 Q 变为 0。

其逻辑表达式为:Q(n+1) = D。

(二)JK 触发器JK 触发器也是一种在时钟脉冲上升沿或下降沿触发的触发器,具有置 0、置 1、保持和翻转四种功能。

当 J=1、K=0 时,在时钟脉冲作用下,输出 Q 置 1;当 J=0、K=1 时,在时钟脉冲作用下,输出 Q 置 0;当 J=K=0 时,输出保持不变;当 J=K=1 时,输出翻转。

其逻辑表达式为:Q(n+1) = JQ' + K'Q。

四、实验内容与步骤(一)D 触发器实验1、按照实验电路图,在数字电路实验箱上正确连接 74LS74 芯片和其他相关元件。

2、将 D 端分别接高电平(1)和低电平(0),用示波器观察时钟脉冲和输出 Q 的波形,记录实验结果。

3、改变时钟脉冲的频率,观察输出 Q 的变化,分析时钟频率对触发器工作的影响。

(二)JK 触发器实验1、依照实验电路图,在实验箱上连接 74LS112 芯片及相关元件。

2、分别设置 J、K 的不同输入组合,如 J=0、K=0;J=1、K=0;J=0、K=1;J=1、K=1,用示波器观察时钟脉冲和输出 Q 的波形,并做好记录。

3、调整时钟脉冲的占空比,观察输出 Q 的变化,探讨占空比对触发器工作的影响。

五、实验数据与结果分析(一)D 触发器1、当 D 端接高电平时,在时钟脉冲上升沿,输出 Q 变为高电平;当 D 端接低电平时,在时钟脉冲上升沿,输出 Q 变为低电平。

(6)脉冲信号产生电路 - 副本

(6)脉冲信号产生电路题目都看出来了实验六脉冲信号产生电路一、实验目的1.掌握555时基电路的结构和工作原理, 学会对此芯片的正确使用.2.学会分析和测试用555时基电路构成的多谐振荡器, 单稳态触发器, 旋密特触发器等三种典型电路.二、实验仪器及材料1.实验仪器设备:双踪示波器、数字万用表、数字电路实验箱2.器件NE556, (或NE555二片)双时基电路1片二极管1N41482只电位器22K, 1K2只电阻、电容若干扬声器一支三、实验原理本实验所用的时基电路芯片为NE556, 同一芯片上集成了二个各自独立的555时基电路, 图中各管脚的功能简述如下:TH-高电平触发端:当TH端电平大于2/3Vcc, 输出端OUT呈低电平, DIS端导通.TR-低电平触发端:当TR端电平小于1/3Vcc时, OUT端呈现高电平, DIS端关断.R-复位端:R=0, OUT端输出低电平, DIS端导通.题目都看出来了VC-控制电压端:VC接不同的电压值可以改变TH, TR的触发电平值. DIS-放电端:其导通或关断为RC回路提供了放电或充电的通路. OUT-输出端. VCC-接正电源端. GND-接地端.表6.1功能测试步骤如下:(1)按图6.3接线, 可调电压取自电位器分压器.(2)按表6.1逐项测试其功能并记录.四、实验内容及步骤1.555时基电路构成的多谐振荡器电路图6.1题目都看出来了图6.2时基电路内部结构图图6.3测试接线图图6.4555定时器构成的多谐振荡器(1)按图6.4接线. 图中元件参数如下:R115K,R25K,C10.033F,C20.1F(2)用示波器观察并测量OUT端波形的频率和理论估算值比较, 算出频率的相对误差值.(3)若将电阻值改为R115K, R210K, 电容C不变, 上述的数据有何变化?(4)根据上述电路的原理, 充电回路的支路是R1R2C1,放电回路的支路题目都看出来了是R2C1, 将电路略作修改, 增加一个电位器RW, 和两个引导二极管, 构成图6.5所示的占空比可调的多谐振荡器.其占空比q为qR1R1R2调节RW的阻值, 可改变q值.合理选择元件参数(电位器选用22K),使电路的占空比q=0.2, 且正脉冲宽度为0.2ms.调试电路, 测出所用元件的数值, 估算电路的误差.2.555构成的单稳态触发器图6.5占空比可调多谐振荡器电路(1)按图6.6接线, 图中R210K, C10.01F输入频率约为10kHz 左右的方波时, 用在器示波器观察OUT端相对于V1的波形, 并测出输出脉冲的宽度TW(2)调节V1频率, 分析并记录观察到的OUT端波形的变化.(3)若输出脉冲TW=20us, 怎样调整电路参数, 记录各有关参数值.图6.6单稳态触发器题目都看出来了3.应用电路图6.8所用555的两个时基电路构成低频对高频调制的救护车警铃电路.(1)参考实验内容2确定图6.8中未定元件参数.(2)按图接线, 注意扬声器先不接.(3)用示波器观察输出波形并记录.(4)接上扬声器, 调整参数声响效果满意.(5)本实验所使用的电器电压V0=+5V图6.8救护车警铃电路五、实验报告1、按实验内容的要求整理实验数据.2、按实验内容的要求计算出相关电路的元器件参数.3、画出实验内容2、3中的相应波形.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、实验目的

1)理解触发器的用途、类型和工作原理

2)掌握利用T-SQL语句创建和维护触发器的方法

3)掌握利用企业管理器创建、维护触发器的方法

二、实验内容

说明:在所有触发器取名时,请各位同学在所给定的名称后加上下划线及学号后四位数字构成自己的实验触发器名。

如:deltr_20051101.各触发器中的所用到的参数变量名自取。

1、利用企业管理器创建与维护触发器

(1)创建简单触发器

创建一个触发器stu_modify在修改student表后,显示一个提示信息,告诉用户有多少行数据被修改了。

创建步骤:

create trigger stu_modify on student

after insert,delete,update

as

print'(所影响的行数为:'+cast(@@rowcount as varchar(10))+'行';

触发器的触发执行测试语句(T-SQL):

update Student_20083386

set sex='男'

where sno='20050001'

执行结果:

(2)修改触发器

修改stu_modify触发器,使其为一个加密触发器。

(提示:加with encpytion关键子句)修改步骤:

USE[XSGL_20083386]

GO

/****** Object: Trigger [dbo].[stu_modify] Script Date: 05/17/2010 19:59:55 ******/

SET ANSI_NULLS ON

GO

SET QUOTED_IDENTIFIER ON

GO

ALTER trigger[dbo].[stu_modify]

on[dbo].[Student_20083386]

with Encryption

after insert,delete,update

as

print'(所影响的行数为:'+cast(@@rowcount as varchar(10))+'行)'

(3)删除触发器

删除stu_modify触发器。

删除步骤:

2、利用T-SQL语句创建与维护触发器

(1)创建after触发器

1)创建一个在插入时触发的触发器sc_insert,当向sc表插入数据时,须确保插入的学号已在student表中存在,并且还须确保保插入的课程号在course表中存在;若不存在,则给出相应的提示信息,并取消插入操作,提示信息要求指明插入信息是学号不满足条件还是课程号不满足条件。

(注:student表与sc表的外键约束要先取消)。

T-SQL语句:

create trigger sc_insert on SC_20083386

for insert

as

begin

if exists(select Sno from inserted where Sno not in(select Sno from

Student_20083386))

print'not Sno'

delete from SC_20083386

where Sno not in(select Sno from Student_20083386);

if exists(select Cno from inserted where Cno not in(select Cno from Course_20083386))

print'not cno'

delete from SC_20083386

where Cno not in(select Cno from Course_20083386);

end;

触发器的触发执行测试语句(T-SQL):

insert

into SC_20083386

values('20050002','001','20');

执行结果:

2)为course表创建一个触发器course_del,当删除了course表中的一条课程信息时,同时将表sc表中相应的学生选课记录删除掉。

T-SQL语句:

create trigger course_del on Course_20083386

for delete

as

begin

delete from SC_20083386

where SC_o in(select Cno from deleted)

end;

触发器的触发执行测试语句(T-SQL):

delete

from Course_20083386

where Cno='002';

执行结果:

3)在course表中添加一个平均成绩avg_grade字段(记录每门课程的平均成绩),创建一个触发器grade_modify,当SC表中的某学生的成绩发生变化时,则course表中的平均成绩也能及时相应的发生改变。

T-SQL语句:

create trigger avg_grade on Course_20083386

for update,insert,delete

as

begin transaction

begin

update Course_20083386

set avg_grade=(select avg(Grade)

from SC_20083386

where SC_o=Course_o)

End

触发器的触发执行测试语句(T-SQL):

update SC_20083386

set grade=77

where Sno='20050001'

执行结果:

3、删除触发器

将触发器sc_insert删除。

T-SQL语句:

drop trigger sc_insert

三.实验总结

本次实验中出现错误:DELETE语句与REFERENCE约束“FK_SC_20083386_Course_20083386"发生冲突,网上查后知道是Cno外键的问题,然后删除外键成功运行。

最终我理解触发器的用途、类型和工作原理掌握了利用T-SQL语句创建和维护触发器的方法,掌握了利用企业管理器创建、维护触发器的方法。