基于DSP的I 2S数字音频接口设计

DSP28335 I2C接口应用

D S P I2C应用说明1.示例程序中几种状态第一次看i2c_eeprom示例程序,对程序中的MsgStatus信息状态切换非常懵懂,为什么要有这几个状态?状态切换顺序如何安排?一大堆的状态,让人有些摸不着头脑。

先把程序中的头文件涉及的7种状态分析一下。

//I2CMessageCommandsforI2CMSGstruct#defineI2C_MSGSTAT_INACTIVE0x0000//未激活状态:一般成功发送数据或者//接受数据后可以设置信息状态为此状态,告诉用户可进行下一次的写数据或读数据。

#defineI2C_MSGSTAT_SEND_WITHSTOP0x0010//发送带停止位数据:这是为写数据而设///的状态,写入地址和数据之后发个停止位告诉存储器数据写入完毕。

#defineI2C_MSGSTAT_WRITE_BUSY0x0011//写数据忙状态:在将待写的数据放入//缓存后,就可以使能IIC传输数据了,然后把信息状态设为该状态,意在告诉用户:数据//已经在传送过程中。

当然是否传送完毕,还需要通过查询SCD位来判断。

#defineI2C_MSGSTAT_SEND_NOSTOP0x0020//发送无停止位数据:这个状态是为了读//取数据而设的,有查阅过AT24C1024EEPROM存储器使用手册的读者知道,在读数据之前//要发送数据的地址,发完地址不能产生停止位,这是存储器硬件设计决定的。

设为这个状//态意在告诉读者,可以发送要读取的数据的地址了。

#defineI2C_MSGSTAT_SEND_NOSTOP_BUSY0x0021//发送无停止位数据忙状态:这个状态是//为了读取数据而设的,似于I2C_MSGSTAT_WRITE_BUSY,说明地址数据已经在传送过程中。

//传送是否成功,还要看ARDY的状态。

#defineI2C_MSGSTAT_RESTART0x0022//重发开始位状态:这个状态也是为读取////数据而设。

I2S和PCM 接口精编版

I²S和PCMI²S总线规范I²S(Inter-IC Sound Bus)是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。

在飞利浦公司的I2S标准中,既规定了硬件接口规范,也规定了数字音频数据的格式。

I2S有3个主要信号:1、串行时钟SCLK,也叫位时钟BCLK,即对应数字音频的每一位数据,SCLK 有1个脉冲。

SCLK的频率=2×采样频率×采样位数。

2、帧时钟LRCK,用于切换左右声道的数据。

LRCK为“0”表示正在传输的是左声道的数据,为“1”则表示正在传输的是右声道的数据。

LRCK的频率等于采样频率。

3、串行数据SDATA,就是用二进制补码表示的音频数据。

有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍。

I²S格式的信号无论有多少位有效数据,数据的最高位总是出现在LRCK变化(也就是一帧开始)后的第2个SCLK脉冲处,见下面I²S格式图。

这就使得接收端与发送端的有效位数可以不同。

如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。

这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

随着技术的发展,在统一的I²S接口下,出现了多种不同的数据格式。

根据SDATA数据相对于LRCK和SCLK的位置不同,分为左对齐(较少使用)、I²S 格式(即飞利浦规定的格式)和右对齐(也叫日本格式、普通格式)。

非I²S格式如图:I²S格式如图:对非I²S格式而言,为了保证数字音频信号的正确传输,发送端和接收端应该采用相同的数据格式和长度。

对I²S格式来说数据长度可以不同。

而且帧时钟LRCK 高低电平对应左右声道的意义也不同?注意I²S总线和I²S格式的区别,I²S总线是一种总线标准,I²S格式是飞利浦制定的数据格式。

基于DSP的I2S数字音频接口设计

基于DSP的I2S数字音频接口设计

张秀丽

【期刊名称】《电声技术》

【年(卷),期】2007(31)4

【摘要】从软件和硬件两方面设计了一种简单、实用的24bit音频编解码器

TLC320AD77与DSP之间的I2S数字音频接口电路.该方法中TLC320AD77与DSP串行口直接相连,不需要占用并行数据总线,避免总线冲突.此方法对于开发、研制基于通用DSP芯片的音效处理器具有重要意义.

【总页数】3页(P38-40)

【作者】张秀丽

【作者单位】浙江万里学院,电子信息学院,浙江,宁波,315100

【正文语种】中文

【中图分类】TN912

【相关文献】

1.基于FPGA和AD1836的I2S接口设计 [J], 周伟;王慧梅

2.基于McBSP实现DSPs与串行AD/DA的接口设计 [J], 杨雪;牟燕妮

3.基于ADSP的I2S总线应用 [J], 王玥婷;毛敏

4.基于DSPs的16位并行输出/串行输出高速ADC芯片AD77223的接口设计[J], 潘志铂; 杨力波

5.基于DSPs的16位并行输出/串行输出高速 ADC 芯片 AD7723 的接口设计 [J], 潘志铂; 杨力波

因版权原因,仅展示原文概要,查看原文内容请购买。

基于dsp芯片的音频信号的分析器的设计

基于dsp芯片的音频信号的分析器的设计摘要DSP 技术在音频处理领域的应用越来越广。

目前,在专门多语音处理系统中都用到了语音分析模块,采集现场的声音并进行频谱分析。

语音处理系统的实时性、功耗、体积、以及对语音信号的保真度差不多上专门阻碍系统性能的关键因素。

因此,音频信号的分析器的设计是专门必要的。

本设计采纳的高速TMS320C5416DSP芯片,最高频率能达到160MIPS,能够专门好的解决系统的实时性;采纳的数字编解码芯片TLV320AIC23(以下简称AIC23)具有16~32位采样精度,采样频率范畴从8kHz~96kHz。

因此,该音频编解码芯片与TMS320C5416DSP的结合是可移动数字音频录放系统、现场语音分析系统的理想解决方案。

本文第一介绍了基于TMS320C5416DSP芯片的语音分析系统的工作原理,给出了整体设计方案和工作框图,然后给出了系统的硬件设计方案;接着介绍了基于TMS320C5416DSP芯片的语音录放系统的软件设计。

在整个设计过程中,我们采纳了TLV320AIC23DSP芯片为核心音频录放接口器件,结合TMS320C5416DSP芯片,语音数据储备FLASH储备器等进行了硬件设计。

软件部分则采纳模块化的设计方法,用C语言来实现。

该语音录放器的设计能够完成语音采集,储备,滤波,频谱分析,差不多实现了语音分析功能。

关键词:TMS320C5416,TLV320AIC23,DSP,语音分析THE DESIGN OF SPEECH ANALYSOR BASED ONTMS320C5416 DSP CHIPABSTRACTThe use of DSP technology in the field of audio processing is increasingly wider. At present, many speech processing systems are used in speech-analysis module, acquisition scene speech and stored for speech-process. Speech-processing System with real-time, power consumption, size, and the speech signal fidelity is a key factor which is affecting system performance. Therefore, speech recording and playing design is very necessary.The design of high-speed chip used TMS320C5416 DSP, the maximum frequency can reach 160 MIPS , which is a good solution to the real-time system; the figures used in the codec chip TLV320AIC23 (hereinafter referred AIC23) is 16 ~ 32 Sampling precision, sampling frequency’s range from 8kHz~96kHz. Therefore, The Audio Decoder Chip and the combination TMS320C5416 DSP Mobile Digital Speech-analysis System Speech Acquisition scene, is the ideal solution.This paper firstly introduces the Speech-analysis of principle based on TMS320C5416 DSP chip, given the overall design of the plan and diagram, and then gives the system hardware design program; Secondly Speech-analysis System software design based on TMS320C5416 DSP chip .Throughout the design process, we used TLV320AIC23 DSP core chips for audio-recording device interface, TMS320C5416 DSP combination of chips, Speech Data Storage Flash memory, and so on the hardware design. Software is a modular design method, the C language to achieve.The speech recording of the design is to complete speech acquisition, storage, filtering, spectrum-analysis. The basic realization of the Speech-analysis functionKEY WORDS:TMS320C5416,TLV320AIC23,DSP,Speech-analysis名目前言.1 第1章语音分析的技术方案及硬件电路设计.21.1语音分析器的性能指标和硬件方案 .2 1.1.1 语音分析器的性能指标.2 1.1.2 硬件设计方案.3 1.2语音分析系统的硬件电路设计.41.2.1 TMS320C5416DSP数字信号处理接口电路模块.51.2.2 TLV320AIC23语音采集、回放接口电路模块.9 1.2.3语音数据储备接口电路模块 .121.2.4 音频接口电路模块 .131.2.5 电源接口电路模块.15第2章语音分析器的应用软件设计.17 2.1 语音分析器应用软件系统的设计方案.17 2.2 主程序模块.17 2.3 语音分析模块的程序设计.20 2.3.1 MCBSP的初始化.20 2.3.2 AIC23 的初始化 .22 结论.27 参考文献.27致谢.31 附录33前言DSP处理速度快,功耗低,性能好,基于TMS320C5416DSP芯片的语音储备容量大,具有专门好的通信音质等特点,因此被广泛应用于专门多领域中。

基于I2S音频接口模块的FPGA设计与应用

EPM240TCl00—3

~ 螂 o

∽ 三要 =芒

i蚕i

。㈣ 随 洲m

色加

。咖

缘 ㈣m

oⅢ

。㈣

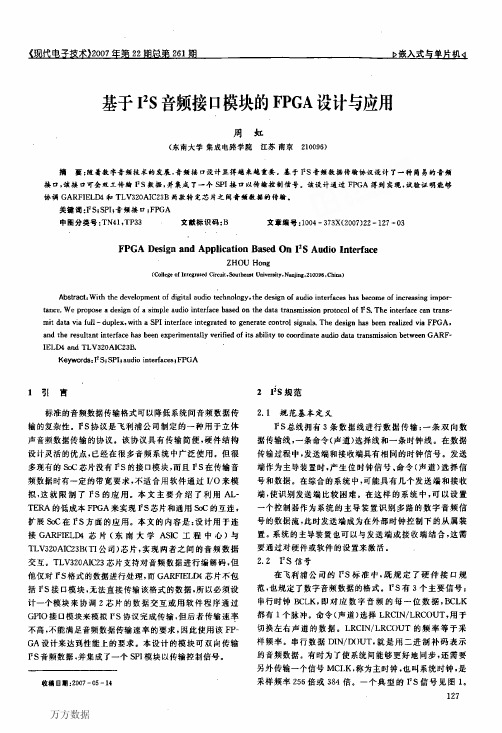

田5 rS黠袖 接口模块主要功能:将GARFIELD4提供的读写、地 址以及使能片选信号传输给SP]和rS模块。他只是实现 基本的传输功能,在这里就不详细说明了。

6实验环节

以下是试验的结果。表格1是FPGA布局布线工具 QuartusⅡ的结果,其中包括了I/o管脚数目、占用的面积 和调用逻辑资源的比例,经过分析发现基本满足设汁要 求。表格2是静态时序分析的结果,基本满足时序要求。 图6是仿真工具VCS产生的波形,是分别对SPI时序和 rs时序仿真所得。

§现益虫壬撞苤22业Z至差!£舶是差!!!期 本rs接口模块采用从属模式,设计如图s所示,主要

是由四组寄存器实现,其中C2G—TMPl,C2G—TMP2, G2C—TMPl和G2C—TMP2是按地址寻址寄存器,当选 中寄存器地址后,GARFIELD4对其进行读写。当读写完 成后,数据在下一时钟节拍并行导出/人移位寄存器。

】27

对于系统而言,产生BCLK和LRCIN/LRCOUT的信号 端就是主导装置。

u。L。R。—几nCnInN几I]几厂n]—几— 几— r]几—n]几U

黜::::皿:口丑:::血:口丑:::: IBCLK—一 ;卜.!盟!唑型

-:·

些型!!竺型

':

田1 rS的时序关系

3应用对象介绍

GARFIELD4芯片是东南大学国家专用集成电路系 统工程技术研究中心自主设计的一款面向基于网络和消 费类电子控制应用的SaC芯片。该芯片采用了ARM7处 理器内核+AMBA总线+应用模块的体系结构。整个芯 片可以运行在100 MHz的频率上,并支持多种外存类型: SRAM,NOR FLASH,SDRAM。

基于CPLD的I2S语音总线接口

基于CPLD的I2S语音总线接口摘要:本文介绍了利用Xilinx公司的XC9500系列CPLD器件,以I2S接口方式对四路输入语音信号进行处理与传输,并用VHDL进行建模,通过ISE软件仿真得出了比较理想的结果,并在工程应用中使用良好。

关键词:CPLD;XC9500;数据传输;多路复用1 引言CPLD器件被广泛地应用在通信系统、网络、计算机系统及控制系统等电子系统中。

XC9500系列CPLD 器件tPD最快达3.5ns,系统时钟可达200MHz。

XC9500系列器件采用第二代“支持ISP”的引脚锁定结构,它拥有一个54比特输入函数块,是用户可以在进行多种改变的同时保持输出引脚固定。

这个特点使设计更具有灵活性,如时钟完全受控,用户既可以对每个宏单元作输出使能反转,也可以对个别的乘积项时钟作使能反转。

在视频监控光端机设备设计中,采用XC95144XL芯片实现了视频采集和处理,语音采集和处理,RS485、RS232通信、与光通信模块一起实现了远程监控系统,本文仅就语音采集和处理、传输的编程、仿真、实现作详细地阐述。

该系统在实际工程中性能稳定可靠,具有一定的参考价值。

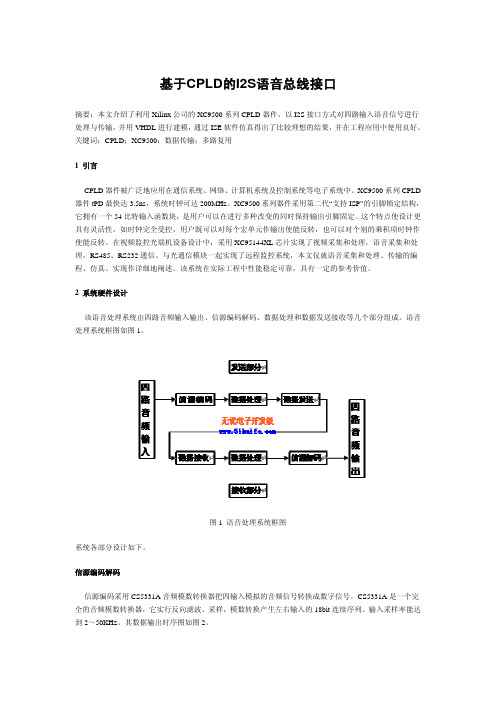

2 系统硬件设计该语音处理系统由四路音频输入输出、信源编码解码、数据处理和数据发送接收等几个部分组成。

语音处理系统框图如图1。

图1 语音处理系统框图系统各部分设计如下。

信源编码解码信源编码采用CS5331A音频模数转换器把四输入模拟的音频信号转换成数字信号。

CS5331A是一个完全的音频模数转换器,它实行反向滤波、采样,模数转换产生左右输入的18bit连续序列。

输入采样率能达到2~50KHz。

其数据输出时序图如图2。

图2 数据输出时序图信源解码采用CS4334芯片音频数模转换器把四输入数字信号转换成模拟信号的音频信号。

CS4334的特性主要有:完善的立体声D/A转换系统,插入补偿,D/A转换,输出模拟滤波,24位转换,96dB动态范围。

其时序如图3。

I2S总线原理及应用实例

I2S总线原理及应用实例I2S(Inter-IC Sound)是一种音频数字接口标准,主要用于在集成电路之间传输音频数据。

I2S总线由三根线组成,即数据线(Data Line)、时钟线(Clock Line)和帧同步线(Frame Sync Line)。

其中,数据线用于传输音频数据,时钟线用于同步数据传输,帧同步线用于标识数据的起始和结束。

I2S总线通过时钟线和帧同步线实现数据的同步传输。

时钟线的频率可以灵活选择,在典型的应用中一般选择44.1kHz或48kHz。

帧同步线在时钟的基础上确定了数据的起始和结束时刻,每个数据帧由一个或多个字节组成。

数据线可以是单声道或双声道,每个声道可以是16位或者24位。

I2S总线主要用于音频数字信号处理器(DSP)、音频编解码器、数字信号处理器(DSP)和音频AD/DA转换器等集成电路之间的连接。

它是一种传输高保真音频数据的有效方式,被广泛用于消费电子产品、汽车音响和专业音频设备等领域。

下面将介绍几个常见的I2S应用实例。

1.音频编解码器音频编解码器常常使用I2S总线进行音频数据的传输。

例如,MP3播放器可以使用I2S接口将音频数据从存储器传送到音频解码器,然后再输出到扬声器。

这种方式可以确保音频数据的高保真传输,使用户能够享受高质量的音乐。

2.语音识别系统语音识别系统通常需要将音频流传输到语音处理芯片进行处理。

I2S总线可以提供高品质的音频数据传输,满足语音识别系统对音频数据的高保真需求。

例如,智能音箱中的麦克风阵列可以通过I2S接口将音频数据传输到语音处理芯片,实现语音识别功能。

3.汽车音响系统汽车音响系统需要将音频信号从车载媒体设备传输到音响放大器和扬声器。

I2S总线可以提供高质量、低延迟的音频数据传输,使车内乘客能够获得清晰、逼真的音乐体验。

在汽车音响系统中,I2S总线通常将音频信号传输到DSP芯片,再经过放大器芯片放大,最终通过扬声器播放。

4.专业音频设备专业音频设备,如音频录音设备和混音台,通常需要实现多个音频通道的数据传输和处理。

基于DSP的数字音频信号处理

基于DSP的数字音频信号处理一、本文概述随着数字信号处理技术的飞速发展,数字音频信号处理已经成为了音频领域的重要分支。

本文旨在探讨基于DSP(数字信号处理器)的数字音频信号处理技术,包括其基本原理、应用领域以及发展趋势。

我们将首先介绍数字音频信号处理的基本概念,然后详细阐述DSP在音频信号处理中的关键作用,包括音频信号的采样、量化、编码、解码、滤波、增强、分析和合成等。

我们还将讨论数字音频信号处理技术在音频通信、音频编解码、音频识别、音频增强和音频合成等领域的应用,以及DSP技术的发展趋势和前景。

本文的目标是为读者提供一个全面的数字音频信号处理知识框架,以期能够推动该领域的研究和应用。

二、数字音频信号处理基础数字音频信号处理是一种使用数字信号处理技术来分析和修改音频信号的方法。

其基础在于理解音频信号的本质和数字信号处理的原理。

音频信号是一种随时间变化的压力波,其变化可以被人类的耳朵感知为声音。

在数字音频处理中,音频信号首先被采样和量化,转换为数字信号。

采样是指将连续的模拟信号在时间上离散化,而量化则是将采样得到的信号在幅度上进行离散化。

这两个步骤是数字音频处理的基础。

数字信号处理是指使用数字计算机或专门的数字信号处理器(DSP)对数字信号进行各种变换和处理的过程。

在数字音频处理中,常用的数字信号处理技术包括傅里叶变换、滤波器设计、频谱分析等。

这些技术可以帮助我们理解音频信号的特性,如频率分布、噪声成分等,从而对其进行有效的修改和优化。

DSP以其强大的计算能力和灵活性,在数字音频处理中发挥着重要作用。

DSP可以实现各种复杂的音频处理算法,如音频编码、解码、噪声消除、回声消除等。

DSP还可以对音频信号进行实时处理,实现音频效果的实时调整和改变。

数字音频信号处理是一门涉及信号处理、数字计算机技术、音频工程等多个领域的交叉学科。

理解和掌握其基础原理和技术,对于音频工程师、音乐制作人、声音设计师等职业人员来说,都是至关重要的。

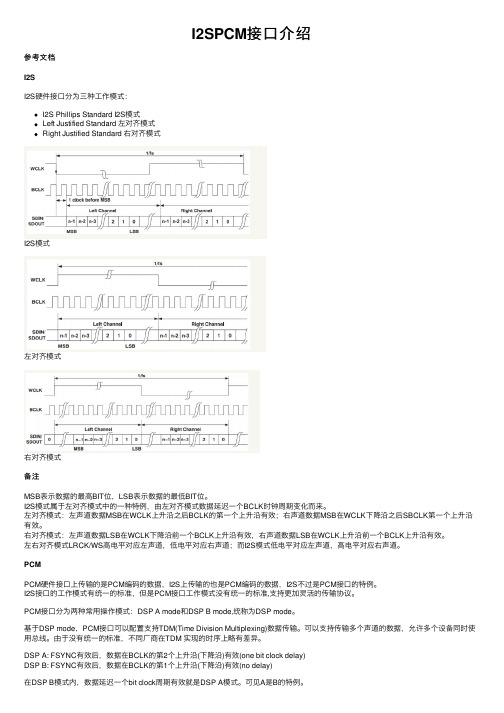

I2SPCM接口介绍

I2SPCM接⼝介绍参考⽂档I2SI2S硬件接⼝分为三种⼯作模式:I2S Phillips Standard I2S模式Left Justified Standard 左对齐模式Right Justified Standard 右对齐模式I2S模式左对齐模式右对齐模式备注MSB表⽰数据的最⾼BIT位,LSB表⽰数据的最低BIT位。

I2S模式属于左对齐模式中的⼀种特例,由左对齐模式数据延迟⼀个BCLK时钟周期变化⽽来。

左对齐模式:左声道数据MSB在WCLK上升沿之后BCLK的第⼀个上升沿有效;右声道数据MSB在WCLK下降沿之后SBCLK第⼀个上升沿有效。

右对齐模式:左声道数据LSB在WCLK下降沿前⼀个BCLK上升沿有效,右声道数据LSB在WCLK上升沿前⼀个BCLK上升沿有效。

左右对齐模式LRCK/WS⾼电平对应左声道,低电平对应右声道;⽽I2S模式低电平对应左声道,⾼电平对应右声道。

PCMPCM硬件接⼝上传输的是PCM编码的数据,I2S上传输的也是PCM编码的数据,I2S不过是PCM接⼝的特例。

I2S接⼝的⼯作模式有统⼀的标准,但是PCM接⼝⼯作模式没有统⼀的标准,⽀持更加灵活的传输协议。

PCM接⼝分为两种常⽤操作模式:DSP A mode和DSP B mode,统称为DSP mode。

基于DSP mode,PCM接⼝可以配置⽀持TDM(Time Division Multiplexing)数据传输。

可以⽀持传输多个声道的数据,允许多个设备同时使⽤总线。

由于没有统⼀的标准,不同⼚商在TDM 实现的时序上略有差异。

DSP A: FSYNC有效后,数据在BCLK的第2个上升沿(下降沿)有效(one bit clock delay)DSP B: FSYNC有效后,数据在BCLK的第1个上升沿(下降沿)有效(no delay)在DSP B模式内,数据延迟⼀个bit clock周期有效就是DSP A模式。

I2S接口规范

S3C44B0X

2S I

接口工作模式

单独发送或接收模式

a、正常传输模式 FIFO队列的就绪标志位决定了CPU读或写队列的时间。发送 队列非空,队列发送数据准备就绪,标志位置1;发送队列为 空,标志位置0。接收队列未满,标志位置1,指示队列可接收数 据;接收队列满,标志位置0。当CPU访问发送或接收队列 (FIFOs)时,串行数据能够被发送或接收。 b、DMA传输模式 发送或接收队列的访问由DMA控制器来完成。在发送或接收 模式中,DMA服务请求由队列的就绪标志位自动给出。

延 迟 特 性

在I2s总线中,任何设备都可以通过提供必需的时 钟信号成为系统的主导装置,而从属装置通过外部时 钟信号来得到它的内部时钟信号,这就意味着必须重 视主导装置和数据以及命令选择信号之间的传播延 迟,总的延迟主要由两部分组成: 外部时钟和从属装置的内部时钟之间的延迟 内部时钟和数据信号以及命令选择信号之间的延 迟 对于数据和命令信号的输入,外部时钟和内部时 的延迟不占据主导的地位,它只是延长了有效的建立 时间(set—up time)。延迟的主要部分是发送端的传输 延迟和设置接收端所需的时间。见图3和图4:

S3C44B0X I2S总线特性

IIS、MSB-Justified格式兼容; 每通道 8/16 位数据格式; 每通道有16 f s、32 f s、48 f s (fs为采样频率)的串行时钟; 具有256 f s和384 f s的主时钟; 具有为主时钟和编码解码时钟分频的可编程分频器; 支持32(2×16)字节发送和接收(FIFO); 具有正常和DMA两种传输模式。

2S I

总线规范

信 号 线 ( 续 )

发送端产生SCK和WS

接收端产生SCK和WS

图1、简单系统配置

基于dsp的i2s音频

电声技术 AUDIO ENGINEERING 2007,31(4) 0次

参考文献(4条)

NOP

NOP

3.3程序设计中应注意的问题 (1)McBSP串行口初始化时,不能直接向控制寄

存器写控制字。VC5402采用了子地址寻址技术,即 McBSP通过复接器将一组子地址寄存器复接到存储 器映射寄存器的同一个位置上。复接器由子块地址寄 存器SPsA控制。子块数据寄存器SPSD用于指定对应 子地址寄存器中数据的读写。其内部连接方式如图4 所示。故访问某个指定的子地址寄存器时,首先要将相 应的子地址写入SPSA,再由SPSA驱动复接器,使其与 SPSD相联,接人相应子地址寄存器所在的实际物理存 储位置,通过SPSD与实际的控制寄存器交换数据。

(2)DSP的串行口没有12S数据格式,采用双相帧 格式来匹配I玛数据格式。

4 结论

笔者设计的基于DSP的12S数字音频接口已通过

软硬件测试,能够正确地实现音频数据流的输入输出。

编写能模拟音乐厅、剧场、电影院等的音质效果的程 序,存入DSP内部ROM或外部ROM中,就可以实现

基于通用DSP的音频效果处理器。

国垒查蕉童万婴生方羞数墅据整差§塑

AINLM AINIP ,2

一种I^2S音频数据处理电路的FPGA设计

据 接 收进来 或发 送 出去 , 太早 或太 晚均会 对音 频 的还 原 产生 较 大 的 影 响 。而 采 用 C P U 自行 计 时控 制 并 按 要求 的格 式传 输 数据 将 会 占用 过 多 的 C P U 时间 ,

明, 电路 设 计 合 理 , 可实现对音频数 据的接收和发送功能。

关键词 : 1 S; F P GA; Z YNQ; 独 立 时钟

中图分类号 : TN4 9 2

文 献 标 志码 : A

文 章 编 号 :1 6 7 3 — 8 0 8 X( 2 0 1 6 ) 0 6 — 0 4 6 1 — 0 5

路 。以 I S协 议 为 基 础 , 采用 Z Y NQ - 7 0 0 0开 发 平 台 , 为 音 频 解 码 芯 片 AUD U1 7 6 1与 C P U完成 音频数据通 信 , 实 现 了 音 频

输 入 和 输 出功 能 。为 音 频 解 码 设 计 独立 时 钟 , 解 决 了传 统 设 计 中 占用 C P U 过多 的问题 , 同 时 可 以 降 低 失 真 。仿 真 结 果 表

c o mp l e t e d gr e a t l y .

Ke y wo r d s : I S;F P GA ;Z YNQ ;c l o c k

对 于现 代 汽 车 电子 系统 , 音 乐播 放 、 F M 广 播 等 都是 必备 功能 , 因此 , 音 频 数 据 的解 码 芯 片就 必 不 可 少 。此外 , 现 在相 当多 的智 能车 载 系统都 有语 音控 制

De s i g n o f 1 2 S d a t a pr o c e s s i n g c i r c u i t b a s e d o n FPGA

嵌入式系统中I2S总线数据通信的软件模拟

嵌入式系统中I2S总线数据通信的软件模拟

引言

I2S(InterIC Sound Bus)是飞利浦公司针对数字音频设备之间的音频数据传输而制定的一种总线标准,采用沿独立的导线传输时钟与数据信号的设计,通过分离数据和时钟信号,避免了时差诱发的失真。

I2S 总线简单有效,可以

有效提升输出数据的质量,在各种嵌入式音频系统中有广泛应用。

但是在嵌入

式音频系统设计中,并不是所有的MCU 都支持I2S 总线格式,再加上I2S 还

没有统一的接口标准,不同的厂家生产的设备接口也是五花八门,采用软件模

拟实现I2S 总线可有效解决在不支持其的MCU 和设备之间通过I2S 总线实现

数据传输时出现的问题。

本文通过在以太网数字语音广播系统中软件模拟I2S 总线实现语音数据

传输,给出了软件模拟实现I2S 总线的方法。

1 I2S 总线规范

I2S 为三线总线,3 个信号分别为:

①串行时钟SCK,也叫位时钟(BCK)。

即每发送1 位数字音频数据,SCK 上都有1 个脉冲。

SCK 的频率=2 乘以采样频率乘以采样位数。

在数据传输过程中,I2S 总线的发送器和接收器都可以作为系统的主机来提供系统的时

钟频率。

②帧时钟WS,即命令(声道)选择,用于切换左右声道的数据。

WS 的频率等于采样频率,由系统主机提供。

WS 为0 表示传输的是左声道的数据,WS 为1 表示传输的是右声道的数据。

③串行数据信号SD,用于传输二进制补码表示的音频数据。

I2S 格式的信号无论有多少位有效数据,数据位的最高位(MSB)总是。

车载数字音频接口的设计

车载数字音频接口的设计

黄爱蓉;江学焕

【期刊名称】《汽车科技》

【年(卷),期】2010(000)004

【摘要】从车载音频设备对存储器的兼容性出发,设计了一个有多种数字接口的车载数字音频接口系统.介绍了车载数字音频接口系统的系统组成,以使用USB-HOST 技术读取并解码U盘上的MP3文件为例说明整个系统的软硬件设计和实现过程.【总页数】4页(P31-34)

【作者】黄爱蓉;江学焕

【作者单位】湖北汽车工业学院电气与信息工程学院,十堰,442002;湖北汽车工业学院电气与信息工程学院,十堰,442002

【正文语种】中文

【中图分类】TP334

【相关文献】

1.基于DSP的I2S数字音频接口设计 [J], 张秀丽

2.基于AMBA总线的双协议数字音频接口IP核设计 [J], 龙国强;阳晔

3.基于LPC2138的AES3数字音频接口设计 [J], 李俊锋;周南

4.数字调频调制器AES/EBU音频接口设计探析 [J], 汪阳;胡军

5.基于STM32F4和CPLD的高品质立体声USB数字音频接口设计 [J], 刘汉阳;杨雷;杜启行;王奎;孔繁海;邓林涓

因版权原因,仅展示原文概要,查看原文内容请购买。

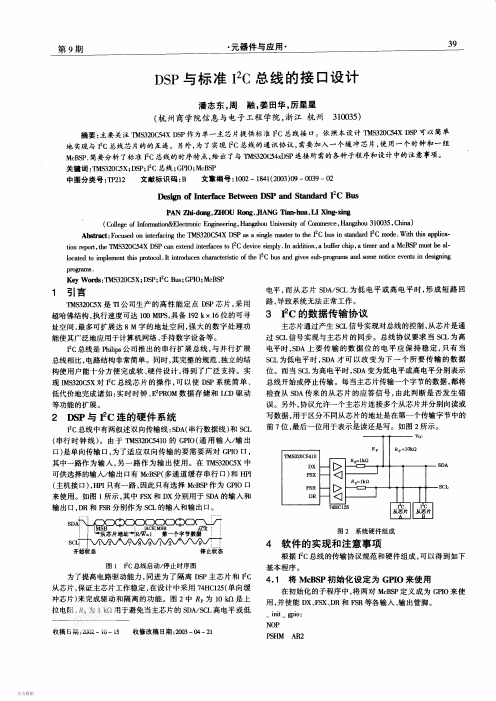

DSP与标准I2C总线的接口设计

LD *A RI,I,A

NOP

RETE

4.5 注意事项

在 PC 总 线的协议中,对 SCL和 SDA的高、低电平和上升、 下降沿的时间有较严格的要求,这对于保证最适宜数据取样时 机非常重要,否则有可能造成错误的数据传输。为此,在程序

中设定了一个5p s的时间中断,这一点已经在总线通讯开始 和停止子程序中有了体现。另外,还一个 Ip s的中断用于检

2 DSP与 rC连的硬件系统

PC 总 线 中有两叙述双向传输线:SDA(串行数据线)和 SCL (串行时钟线)。由于 TMS32OC5410的 GPIO(通用输人/输出 口)是单向传输口,为了适应双向传输的要需要两对 GPIO口, 其中一路作为输人,另一路作为输出使用。在 TMS320C5X中 可供选择的输人/输出口有 McBSP(多通道缓存串行口)和 HPI (主机接口),HPI只有一路,因此只有选择 McBSP作为 GPIO口 来使用。如图 1所示,其中FSX和 DX分别用于SDA的输人和 输出口,DR和 FSR分别作为 SCL的输人和输出口。

基于DSP双路音频信号实时处理系统设计

基于DSP双路音频信号实时处理系统设计袁茹轩;尉乐;何天璐;高中山【摘要】This design scheme adopts TMS320C5509A as the core processor,giving a realization method for composing the speech signal acquisition system with DMA and McBSP,distributing data buffers reasonably and realizing real-time data updated reliably and steadily.%采用TMS320C5509A作为核心处理器,给出了一种利用DMA结合多通道缓冲串口McBSP组成的语音信号采集系统的实现方法。

合理分配了数据缓冲空间,可靠稳定地实现数据的实时更新,完成双路立体声信号的实时采集、处理和发送。

阐述了AIC芯片与DSP连接的配置和数据接口的设计方法,给出CODEC与DSP之间数据传输的程序示例。

试验证明,该系统能够高精度、高稳定地完成音频信号的采集处理和发送任务,适用于个人便携式音频通信设备的驱动开发。

【期刊名称】《电子科技》【年(卷),期】2011(024)007【总页数】3页(P24-26)【关键词】DSP;DMA;TLV320AIC23B;实时采集处理;缓冲更新【作者】袁茹轩;尉乐;何天璐;高中山【作者单位】西安电子科技大学本科生创新实践基地,陕西西安710126;西安电子科技大学本科生创新实践基地,陕西西安710126;西安电子科技大学本科生创新实践基地,陕西西安710126;西安电子科技大学本科生创新实践基地,陕西西安710126【正文语种】中文【中图分类】TN911.72现代音频信号处理领域,通常需要采集大量的数据进行实时分析,并且逐步从处理单路信号发展为处理多路信号。

对语音信号而言,采用元音强度与元音间隔作为听者识别信号的基础参数。

I2S总线接口结构的配置

S3C44B0X I2S总线结构

图7 IIS总线框图 各部分功能如下:

S3C44B0X I2S总线结构

✓总线接口、寄存器组、和状态机(BRFC):总线接口逻辑和FIFO的 访问由状态机控制;

✓ 两个三位的预分频器(IPSR):一个被用作IIS总线接口的主时钟发 生器,另一个被用作外部编码解码的时钟发生器;

信号线(续)

I2S总线规范

➢ 串行数据(SD)

I2S格式的信号无论有多少位有效数据,数据的最 高位总是被最先传输(在WS变化(也就是一帧开始)后的 第2个SCK脉冲处),因此最高位拥有固定的位置,而 最低位的位置则是依赖于数据的有效位数。也就使得 接收端与发送端的有效位数可以不同。如果接收端能 处理的有效位数少于发送端,可以放弃数据帧中多余 的低位数据;如果接收端能处理的有效位数多于发送 端,可以自行补足剩余的位(常补足为零)。这种同步机 制使得数字音频设备的互连更加方便,而且不会造成 数据错位。为了保证数字音频信号的正确传输,发送 端和接收端应该采用相同的数据格式和长度。当然, 对I2S格式来说数据长度可以不同。

✓ 16位移位寄存器(SFTR):在发送数据模式中,并行数据被移成串 行数据输出,在接收数据模式中,串行数据被移成并行数据输入;

S3C44B0X I2S接口工作模式

✓ 单独发送或接收模式

a、正常传输模式 FIFO队列的就绪标志位决定了CPU读或写队列的时间。发送

队列非空,队列发送数据准备就绪,标志位置1;发送队列为 空,标志位置0。接收队列未满,标志位置1,指示队列可接收数 据;接收队列满,标志位置0。当CPU访问发送或接收队列 (FIFOs)时,串行数据能够被发送或接收。 b、DMA传输模式

I2S总线概述

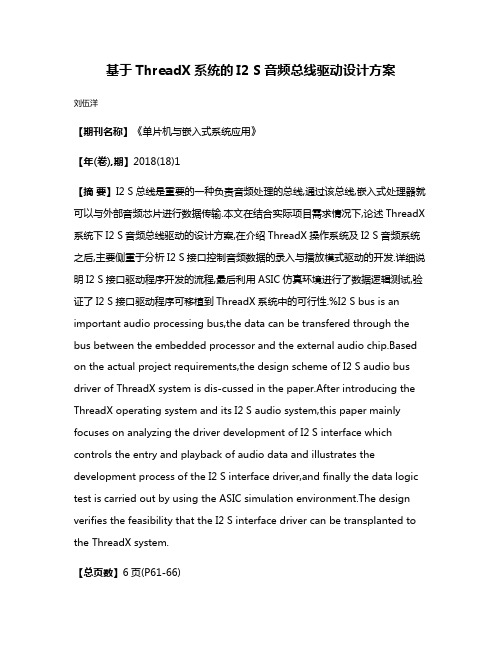

基于ThreadX系统的I2 S音频总线驱动设计方案

基于ThreadX系统的I2 S音频总线驱动设计方案刘伍洋【期刊名称】《单片机与嵌入式系统应用》【年(卷),期】2018(18)1【摘要】I2 S总线是重要的一种负责音频处理的总线,通过该总线,嵌入式处理器就可以与外部音频芯片进行数据传输.本文在结合实际项目需求情况下,论述ThreadX 系统下I2 S音频总线驱动的设计方案,在介绍ThreadX操作系统及I2 S音频系统之后,主要侧重于分析I2 S接口控制音频数据的录入与播放模式驱动的开发.详细说明I2 S接口驱动程序开发的流程,最后利用ASIC仿真环境进行了数据逻辑测试,验证了I2 S接口驱动程序可移植到ThreadX系统中的可行性.%I2 S bus is an important audio processing bus,the data can be transfered through the bus between the embedded processor and the external audio chip.Based on the actual project requirements,the design scheme of I2 S audio bus driver of ThreadX system is dis-cussed in the paper.After introducing the ThreadX operating system and its I2 S audio system,this paper mainly focuses on analyzing the driver development of I2 S interface which controls the entry and playback of audio data and illustrates the development process of the I2 S interface driver,and finally the data logic test is carried out by using the ASIC simulation environment.The design verifies the feasibility that the I2 S interface driver can be transplanted to the ThreadX system.【总页数】6页(P61-66)【作者】刘伍洋【作者单位】重庆邮电大学通信与信息工程学院,重庆 400065【正文语种】中文【中图分类】TP311.1【相关文献】1.基于S3C2410的IIS音频总线研究及其驱动实现 [J], 庄海军2.基于USB和I2S总线的高速数据采集系统设计 [J], 李龙雨;冯志华;刘志刚;张长会3.一种基于DAB的实时音频系统设计方案 [J], 王国裕;曹瑞;陆明莹4.基于ThreadX实时操作系统的USB设备驱动开发 [J], 潘应进;朱子元5.基于FPGA的I2S转AES/EBU音频转换系统的设计 [J], 钱坤;杨秀芝;郑明魁;杜伟庆因版权原因,仅展示原文概要,查看原文内容请购买。

I2S接口设计

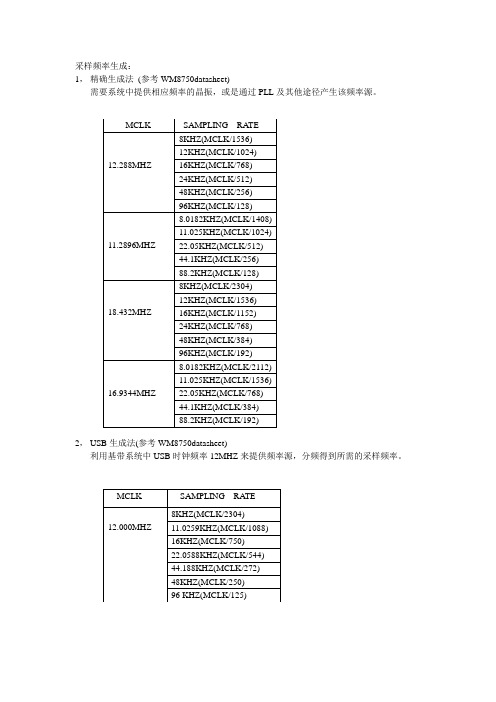

采样频率生成:

1,精确生成法(参考WM8750datasheet)

需要系统中提供相应频率的晶振,或是通过PLL及其他途径产生该频率源。

2,USB生成法(参考WM8750datasheet)

利用基带系统中USB时钟频率12MHZ来提供频率源,分频得到所需的采样频率。

3, PLL 合成法(参考STW5094A & MAX9851 datasheet )

PLL 合成是比较常用的频率合成方法,精度比较高,动态范围大,获得频率源比较容易。

设AMCK f 为基带频率(手机基带频率为13MHZ 或26MHZ ),L

R C K f 为目标采样频率,

Round 为求余运算,N 为倍频数。

则这四者存在如下关系: ))/(2

(23

AMCK LRCK f f Round N *=

PLL 合成法示意图

例如:设基带频率为13MHZ ,要产生44.1KHZ 的采样频率,则运用上式可求得LRCK f

28456))13000000/44100(2

(23

=*=Round N

Hz f LRCK 9.440982

/)1300000028456(23

=*=

4, 分频法(参考台湾某公司I2S 设计讲义)

最简单的采样频率生成法,为分别得到48KHZ 和44.1KHZ 的采样率,要找到它们的公约数,但公约数太大不符合实际,在工程上采用近似的办法。

如典型的MCLK 为

*

所以在MCLK 输入前,要预分频为SYSCLK 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

I 2 准 中 , 规 定 了硬 件接 口规 范 , 规定 了数 字 音 频 s标 既 也 数据 的格式 1 下 面 以 2 i音频 编 解码 器 T C 2 A 7 3 1 。 4 t b L 30 D 7 与 r 公 司 T 30 C 4 2 D P为 例 , 绍 I r I MS2 V 5 o S 介 2 字 音 s数 频接 口电路 设 计 方 法 。

2 芯 片介 绍

21 TLC3 0 . 2 AD7 7音频 编 解 码 器 特 点

T C 2A 7 L 3 0 D 7是 使用 多 比特 ∑一 △技术 的 高性能 2 i全 双工立 体声 数模 和模 数转换 器 , 4b t 动态 范 围达

10d , 波 失 真 和 噪 声 为 10d 。 芯 片 采 用 差 动 输 0 B 谐 0 B

张 秀 丽

・

产 品设计 ・

( 江 万 里 学 院 电 子信 息 学 院 ,浙 江 宁 波 3 5 0 ) 浙 1 1o

【 摘 要 】 从软 件 和 硬 件 两 方 面设 计 了一 种 简 单 、 实用 的 2 i音 频 编 解 码 器 T C 2 A 7 4bt L 3 0 D 7与 D P之 间 的 I S 2 字 S数

音 频 接 口 电路 。该 方法 中 T C 2A 7 L 3 0 D 7与 D P 串行 口直 接相 连 , 需 要 占用 并 行 数 据 总 线 , 免 总 线 冲 突 。此 方 法 S 不 避 对 于 开 发 、 制 基 于 通 用 D P芯 片 的 音 效处 理 器 具 有 重要 意义 。 研 S

Z HANG u l Xi — i

( l t nc a d If ma o n ie r g e at n o h j n n nv r t,N n b h in 0 hn ) E e r i n n r t n E gn e n ,D p r c o o i i me t fZ e a g Wa l U i s y ig o Z o a g 3 5hsp prds n a s pe ad pata I u i dga i e ae bten 2 i A do C d cT C A s c】T i ae ei i l n rc cl 2 ado ii l n r c e e 4b ui oe L - r g m i S t t f w t

维普资讯

r 器 件 与 电 路 = 、 囿 , 囿响 @6 @ { 0 凹6 ,

文章 编 号 : 0 2 8 8 ( 0 7 0 - 0 8 0 1 0 — 6 4 2 0 )4 0 3 - 3

基于 DS P的 I 2 字音频接 口设 计 术 S数

【 e r s u i cdc : a dodga ne ae S K y wod 】a do oe ;I u i ii l tr c ;D P S t i f

1 引 言

音响数据的采集 、处理 和传输 是多媒体技术的重 要组成部分 。 多的数 字音频 系统 已经进入 消费市场 , 众 例如数字音频录音 带 、 数字音 效处理器 。 特别是数字音 效处理器在电台 、 电视 台以及歌舞厅 等应用 十分广泛 , 它在美化音乐 、 声 、 歌 语音 的音色 、 进行 艺术的再创作 、

30 2 AD7 n D P I h s d sg 7 a d S . n ti e in, t e T C 2 AD7 s d r cl o n ce o s r l p r o S w i h i n t h L 3 0 7 i i t c n e td t e a o f D P, e y i t h c s o c n e td t P S p r l l d t u n i v i r m u n ef r n e h e h oo y d r e n t i p p r h s o n ce o DS aal a a b s a d w l a od f e l o b s i t r e c .T e t c n lg e v d i hs a e a e i g e t s i c n e i e eo i g a d su yn u i f c a d b s d o e e a P r a i f a c n d v lp n n t d i g a d o e e t c r a e n g n r l DS . n g i

入 和单端输 出,片上 自带抗混叠滤波器和输 出平滑滤 波器以及数字去加重滤波电路 , 支持从工作方式 。 L TC

【 键 词 】 音 频 编 解 码 器 ;F 关 S数 字 音 频 接 口; 数 字信 号处 理 【 图 分 类 号 】T 9 2 中 N 1 【 献 标 识 码 】B 文

D s Ⅱ O h ej g n te Dgtl do Itrae B sd O P ji a Au i nefc ae n DS

着数字信号处 理技术发展 ,数 字信号处理芯 片 ( S ) D P

性 能 不 断提 高 , 价格 也 越 来 越 被 大 众 所 接 受 。 因此 , 基

于通用 D P芯片 的效果 处理器 , S 必将 在追求高性 价比

的数 字 音 频 应 用 中发 挥 越 来 越 大 的 作 用 。 基 于 D P的 音 频 效 果 处 理 器 基 本 原 理 『] 拟 音 S 1: -模 2