Why systemverilog and UVM

SystemVerilog硬件设计及建模

SystemVerilog硬件设计及建模引言在硬件设计领域,SystemVerilog是一种广泛使用的硬件描述语言。

它结合了Verilog HDL和一些现代编程语言的特性,使得硬件设计和建模更加高效和灵活。

本文将介绍SystemVerilog的基本概念和语法,以及如何利用它进行硬件设计和建模。

SystemVerilog基础模块和端口在SystemVerilog中,设计被组织成一个个模块。

每个模块由一个或多个端口组成,其中包含输入端口、输出端口和双向端口。

端口是模块与外部世界之间通信的接口。

以下是一个简单的SystemVerilog模块的示例:module MyModule(input wire clk, input wire rst, input wire A, input wire B, output wire C);// 模块逻辑always @(posedge clk or posedge rst)if (rst)C <= 0;elseC <= A & B;endmodule数据类型SystemVerilog支持多种数据类型,包括基本数据类型(如整数和实数)和复杂数据类型(如数组和结构体)。

它还支持用户自定义数据类型。

以下是一些常用的数据类型示例:•整数类型:int, bit, logic•实数类型:real, time•数组类型:int my_array[8]•结构体类型:typedef struct packed {int x;int y;} my_struct;时序和复位在SystemVerilog中,时序和复位是设计中非常重要的概念。

时序表示硬件的时间顺序行为,比如时钟上升沿触发的操作。

复位用于将设计状态恢复到初始状态。

以下是一个简单的时序和复位示例:always @(posedge clk or posedge rst)if (rst)// 复位逻辑else// 时序逻辑仿真和验证SystemVerilog提供了丰富的仿真和验证功能,以验证设计的正确性。

system verilog 标准

系统Verilog是一种硬件描述语言(HDL),用于描述数字电路。

它包含了Verilog的所有特性,并添加了一些新的特性。

这些新的特性包括在设计中引入了数据类型的定义,更好地支持设计的抽象,以及更自然地支持设计的层次式描述。

在本文中,我们将深入了解System Verilog标准。

1. 介绍System Verilog标准System Verilog是IEEE标准1800,最初是由Accellera组织进行开发的。

它于2005年发行,是Verilog HDL的扩展,它添加了许多新的特性,使得它更适合于硬件验证和设计。

2. System Verilog的特性System Verilog添加了许多新的特性,以提高Verilog HDL的功能。

其中一些主要特性包括:a. 对象导向编程:System Verilog引入了面向对象的编程范式,使得设计和验证更加抽象和灵活。

b. 增强了数据类型和操作:System Verilog引入了更多的数据类型和操作,更好地支持设计和验证的需求。

c. 增加了随机性:System Verilog引入了随机性,使得验证更加全面和高效。

3. System Verilog在硬件验证中的应用System Verilog的特性使得它在硬件验证中应用广泛。

它提供了丰富的验证方法和工具,包括:a. 事务级建模(TLM):System Verilog提供了TLM的支持,使得验证更加抽象和高效。

b. Constrained随机验证:System Verilog引入了constrained random的验证方法,使得验证更加全面和高效。

c. Coverage驱动验证:System Verilog提供了coverage驱动的验证方法,使得验证更加全面和高效。

4. System Verilog在硬件设计中的应用除了在硬件验证中应用广泛外,System Verilog在硬件设计中也有着广泛的应用。

systemverilog类的方法

systemverilog类的方法(原创版3篇)目录(篇1)一、SystemVerilog 类的方法概述二、SystemVerilog 类的方法分类1.构造函数和析构函数2.普通方法3.静态方法4.类方法三、SystemVerilog 类的方法的应用示例四、SystemVerilog 类的方法的注意事项正文(篇1)SystemVerilog 类的方法是指在 SystemVerilog 语言中,类所具有的操作和功能。

这些方法和其他编程语言中的类方法类似,可以用来描述类的状态、行为和属性。

在 SystemVerilog 中,类的方法可以分为以下几类:一、构造函数和析构函数构造函数是在创建类的实例时被自动调用的方法,用于初始化类的属性。

析构函数则是在类的实例被销毁时被自动调用的方法,用于清理类的资源。

二、普通方法普通方法是类的实例可以直接调用的方法,可以访问类的公共属性和保护属性,但不能访问私有属性。

普通方法可以用于实现类的业务逻辑。

三、静态方法静态方法是属于类的,而不是属于类的实例。

静态方法不依赖于类的实例,可以直接通过类名调用。

静态方法不能访问类的非静态属性和方法。

四、类方法类方法是属于类的,但不依赖于类的实例。

类方法可以通过类的实例或者类名调用。

类方法主要用于操作类的属性和方法。

在实际应用中,SystemVerilog 类的方法可以用于实现各种功能,如数据处理、信号生成和验证等。

在使用过程中,需要注意以下几点:1.方法的命名应简洁明了,符合编程规范。

2.方法的参数应合理设置,便于调用和理解。

3.方法的返回值应正确处理,避免出现错误。

4.注意方法的封装和访问控制,保证程序的稳定性和安全性。

总之,SystemVerilog 类的方法为类的实例提供了丰富的操作和功能,有助于实现各种复杂的设计和验证需求。

目录(篇2)1.SystemVerilog 类的概念2.SystemVerilog 类的方法3.SystemVerilog 类的方法的应用4.SystemVerilog 类的方法的优点正文(篇2)SystemVerilog 类的概念SystemVerilog 是一种硬件描述语言,它是 Verilog 的扩展,用于设计和验证数字电路系统。

UVM相关要点范文

UVM相关要点范文UVM(Universal Verification Methodology)是一种验证方法学,用于验证集成电路设计的正确性。

UVM的目标是提供一种可重用的、可扩展的、可配置的验证框架,可以适用于不同规模和复杂度的设计。

以下是UVM相关的要点。

1.UVM基本概念:UVM基于SystemVerilog语言,结构化验证环境,采用面向对象的设计方法。

它提供了一套验证组件,包括验证环境(env),顶层测试(test),驱动(driver),监视器(monitor),事务(transaction)等。

通过配置和连接这些组件,可以创建一个完整的验证环境。

2.UVM构建模块:3.UVM构建方法:UVM采用构建块方法构建验证环境。

首先,创建UVC,对外部接口进行建模,并实现相应的驱动和监视器。

然后,创建UVM Testbench,配置和连接UVC,并实现顶层测试。

最后,创建UVM Testcase,定义测试数据和验证规则。

4.UVM验证过程:UVM的验证过程包括四个阶段:创建、配置、运行和收尾。

在创建阶段,实例化UVM Testbench和UVM Testcase,并配置UVC。

在配置阶段,连接组件,设置参数和启动模拟器。

在运行阶段,执行测试,并生成日志和报告。

在收尾阶段,清理资源,关闭模拟器。

5.UVM核心概念:UVM的核心概念包括交易、序列、驱动、监视器和函数。

交易是验证过程中传递的数据包,包含信号、地址、数据和控制信息。

序列是交易的序列化表示,可以定义多个交易之间的顺序关系。

驱动是产生和驱动交易的组件,负责发送交易到被测对象。

监视器是接收和监视交易的组件,负责检查交易的正确性。

函数是UVM中的工具函数,用于处理和操作交易和序列。

6.UVM高级特性:UVM提供了一些高级特性,如配置管理、消息传递、注解和覆盖率。

配置管理是通过配置文件和命令行参数来配置UVM测试,方便测试的重用和管理。

消息传递是UVM中不同组件之间传递和处理消息的机制,可以实现进程间通信和事件驱动。

利用Systemverilog+UVM搭建SOC及ASIC的RTL验证环境

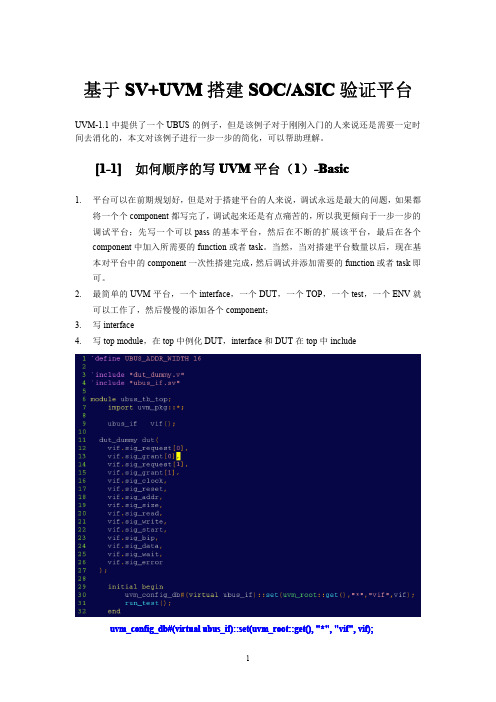

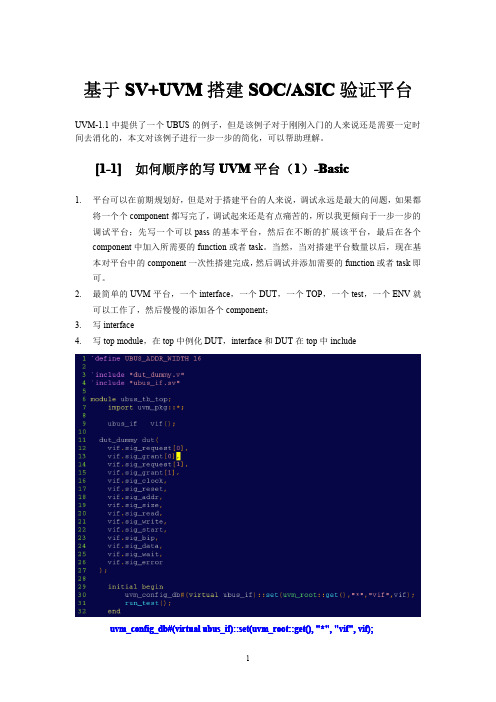

基于SV+UVM搭建SOC/ASIC验证平台UVM-1.1中提供了一个UBUS的例子,但是该例子对于刚刚入门的人来说还是需要一定时间去消化的,本文对该例子进行一步一步的简化,可以帮助理解。

[1-11]如何顺序的写UVM平台(1)-Basic[1-1.平台可以在前期规划好,但是对于搭建平台的人来说,调试永远是最大的问题,如果都将一个个component都写完了,调试起来还是有点痛苦的,所以我更倾向于一步一步的调试平台;先写一个可以pass的基本平台,然后在不断的扩展该平台,最后在各个component中加入所需要的function或者task。

当然,当对搭建平台数量以后,现在基本对平台中的component一次性搭建完成,然后调试并添加需要的function或者task即可。

2.最简单的UVM平台,一个interface,一个DUT,一个TOP,一个test,一个ENV就可以工作了,然后慢慢的添加各个component;3.写interface4.写top module,在top中例化DUT,interface和DUT在top中includeuvm_config_db#(virtual ubus_if)::set(uvm_root::get(),"*","vif",vif);run_test();5.写Makefile,此时编译可以通过6.写自定义的package,然后在top中include该packagetypedef uvm_config_db#(virtual ubus_if)ubus_vif_config;typedef virtual ubus_if ubus_vif;后来证明,这两句话在ubus的env中根本没有用上;7.定义Environment,并将该文件加入到自定义的package中,这个时候编译不能通过此处的get和top中的set是一对,如果top中没有set则会报告·uvm_fatal中的错误if(!uvm_config_db#(virtual ubus_if)::get(this,"","vif",vif))`uvm_fatal("NOVIF",{"virtual interface must be set for: ",get_full_name(),".vif"});8.定义base_test,需要在top中include该test文件,并在makefile中加入编译该test的命令;此时可以再次编译通过,并运行最basic的testcase编译第一次通过总结一:在一个芯片的验证平台中,总会给一个最basic 的base_test ,但是可能每个人负责验证的部分是不一样的,比如说我要验证USB ,那我一定会从base_test 中派生一个usb_base_test 来给自己用,这样我可以在usb_base_test 加入任何我想要的函数,而不会影响到其他人。

uvm验证方法学框架 -回复

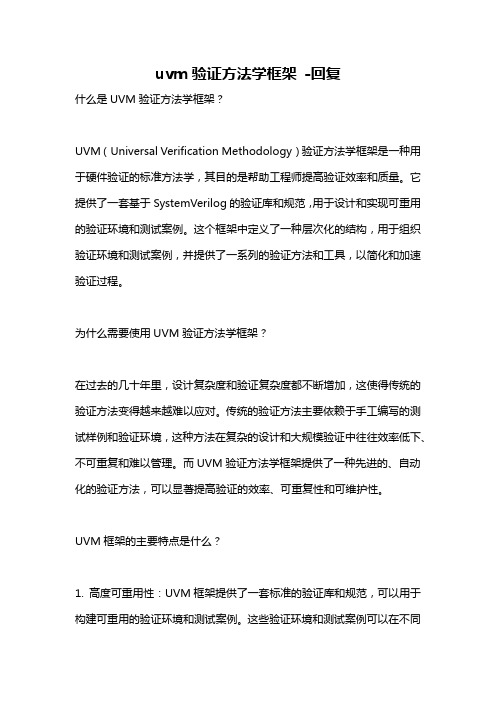

uvm验证方法学框架-回复什么是UVM验证方法学框架?UVM(Universal Verification Methodology)验证方法学框架是一种用于硬件验证的标准方法学,其目的是帮助工程师提高验证效率和质量。

它提供了一套基于SystemVerilog的验证库和规范,用于设计和实现可重用的验证环境和测试案例。

这个框架中定义了一种层次化的结构,用于组织验证环境和测试案例,并提供了一系列的验证方法和工具,以简化和加速验证过程。

为什么需要使用UVM验证方法学框架?在过去的几十年里,设计复杂度和验证复杂度都不断增加,这使得传统的验证方法变得越来越难以应对。

传统的验证方法主要依赖于手工编写的测试样例和验证环境,这种方法在复杂的设计和大规模验证中往往效率低下、不可重复和难以管理。

而UVM验证方法学框架提供了一种先进的、自动化的验证方法,可以显著提高验证的效率、可重复性和可维护性。

UVM框架的主要特点是什么?1. 高度可重用性:UVM框架提供了一套标准的验证库和规范,可以用于构建可重用的验证环境和测试案例。

这些验证环境和测试案例可以在不同的项目中重复使用,提高了效率并减少了验证开发的时间和工作量。

2. 可扩展性:UVM框架支持验证环境和测试案例的层次化组织,可以方便地扩展和修改。

它提供了一种通过继承和重写的方式来实现个性化的功能,使用户可以快速定制自己的验证环境和测试案例。

3. 自动化:UVM框架提供了一系列的验证方法和工具,可以自动化验证过程。

它支持事务级建模(TLM)和通信机制,可以方便地模拟和交互,减少了手工编写测试样例的工作量。

4. 可重复性:UVM框架提供了一套规范,定义了验证环境和测试案例的接口和行为。

这使得不同的团队可以使用相同的方法和规范进行验证,从而提高了验证的可重复性和一致性。

UVM框架的主要组成部分是什么?UVM框架主要包含以下几个组成部分:1. UVC(Universal Verification Component):UVC是UVM框架的基本单元,用于构建可重用的验证环境。

uvm system verilog总结

uvm system verilog总结### UVM System Verilog 总结#### 导语UVM(Universal Verification Methodology)与System Verilog的结合,为芯片设计验证领域带来了革新。

这种方法论不仅提高了验证效率,还增强了验证的可重用性和覆盖率。

本文将全面总结UVM与System Verilog的相关概念、特点以及应用。

---#### 一、UVM与System Verilog概述**1.1 UVM简介**UVM是建立在System Verilog基础上的一个标准化验证方法论,旨在提供一种通用的、模块化的验证平台。

它通过将验证环境分层,实现了环境的可重用性和易于维护性。

**1.2 System Verilog简介**System Verilog是一种硬件描述和验证语言,结合了Verilog和VHDL的优点,并增加了面向对象编程的特性。

它在芯片设计和验证中广泛应用。

---#### 二、UVM的核心特点**2.1 面向对象**UVM采用面向对象的设计思想,将验证环境分为不同的类和层次,便于管理和重用。

**2.2 模块化**UVM的模块化设计使得验证环境可以根据不同的测试需求灵活组合和配置。

**2.3 自动化**UVM支持自动化测试,包括自动生成测试序列、自动检查和报告错误等。

---#### 三、System Verilog在UVM中的应用**3.1 非阻塞赋值**System Verilog的非阻塞赋值在UVM中用于描述硬件行为。

**3.2 面向对象编程**System Verilog的面向对象编程特性使得UVM可以定义基类和派生类,实现代码的复用。

**3.3 功能覆盖**利用System Verilog的功能覆盖(Functional Coverage)特性,UVM 可以全面检查设计功能的覆盖率。

---#### 四、UVM与System Verilog的结合优势**4.1 提高验证效率**UVM与System Verilog的结合使得验证人员可以快速搭建验证环境,提高验证效率。

uvm验证方案介绍

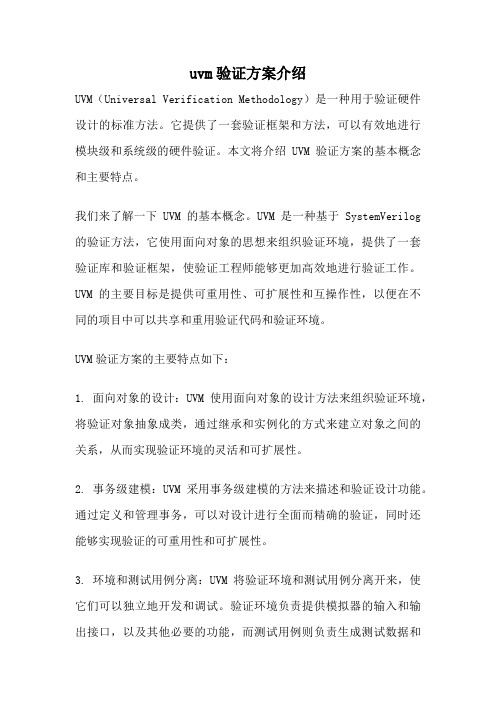

uvm验证方案介绍UVM(Universal Verification Methodology)是一种用于验证硬件设计的标准方法。

它提供了一套验证框架和方法,可以有效地进行模块级和系统级的硬件验证。

本文将介绍UVM验证方案的基本概念和主要特点。

我们来了解一下UVM的基本概念。

UVM是一种基于SystemVerilog 的验证方法,它使用面向对象的思想来组织验证环境,提供了一套验证库和验证框架,使验证工程师能够更加高效地进行验证工作。

UVM的主要目标是提供可重用性、可扩展性和互操作性,以便在不同的项目中可以共享和重用验证代码和验证环境。

UVM验证方案的主要特点如下:1. 面向对象的设计:UVM使用面向对象的设计方法来组织验证环境,将验证对象抽象成类,通过继承和实例化的方式来建立对象之间的关系,从而实现验证环境的灵活和可扩展性。

2. 事务级建模:UVM采用事务级建模的方法来描述和验证设计功能。

通过定义和管理事务,可以对设计进行全面而精确的验证,同时还能够实现验证的可重用性和可扩展性。

3. 环境和测试用例分离:UVM将验证环境和测试用例分离开来,使它们可以独立地开发和调试。

验证环境负责提供模拟器的输入和输出接口,以及其他必要的功能,而测试用例则负责生成测试数据和检查模拟器的输出结果。

4. 交互式验证:UVM提供了一套交互式的验证方法,使验证工程师能够与模拟器进行实时交互,观察和调试模拟器的行为。

这种交互式的验证方法可以极大地提高验证效率,同时也方便了验证工程师的调试工作。

5. 自动化验证:UVM提供了一系列自动化的验证功能,如自动产生验证配置、自动产生验证报告等。

这些自动化的功能可以极大地简化验证工程师的工作,提高验证效率。

通过以上的介绍,我们可以看出,UVM验证方案是一种基于面向对象和事务级建模的验证方法,它具有可重用性、可扩展性和互操作性的特点。

UVM的出现极大地提高了硬件验证的效率和可靠性,使验证工程师能够更加高效地进行验证工作。

uvm验证方法论

uvm验证方法论UVM(Universal Verification Methodology)是一种常用的硬件验证方法论,广泛应用于数字芯片验证领域。

UVM提供了一种结构化的框架和一些验证库,帮助验证工程师和设计工程师共同进行验证工作。

下面将从UVM的背景和原理、UVM的优势、UVM的基本组成以及UVM的应用实例等方面进行介绍和分析。

一、UVM的背景和原理验证是芯片设计过程中至关重要的一环,旨在确保设计的正确性和稳定性。

在过去的几十年中,随着芯片设计复杂度的不断增加,传统的验证方式逐渐无法满足验证需求。

为了解决这个问题,UVM应运而生。

UVM的核心原理是基于面向对象的可复用验证构建。

它基于SystemVerilog语言,通过使用类和对象,创建了一个高层次的验证环境,从而提高了可重用性和可扩展性。

UVM的设计目标是使验证工程师能够更加高效地开发和维护验证环境,提高芯片的验证效率和质量。

二、UVM的优势1.提高可重用性:UVM提供了一些验证库,包括事务级建模(TLM)、验证组件库(UVC)等,可以用于创建可复用的验证环境和测试用例。

这些库是经过验证和验证完整的,可以在不同的项目中直接应用,以提高验证的效率和准确性。

2.提高可扩展性:UVM采用面向对象的方法,将验证环境和测试用例以及其他验证组件进行模块化设计。

这种结构化的设计使得验证工程师能够更方便地进行功能和性能增强,以满足不同项目的验证需求。

3.支持重要的验证特性:UVM提供了一些重要的验证特性,如约束随机测试、反向传播(back-annotation)等,可以帮助验证工程师更好地捕获设计中的错误和漏洞。

4.提供完善的调试功能:UVM提供了一些调试功能,如波形可视化、消息记录等。

这些功能可以帮助验证工程师更方便地对验证结果进行调试和分析,快速定位和修复问题。

三、UVM的基本组成UVM的基本组成主要包括以下几个方面:1. Verification Components(VCs):验证组件是UVM的基本单元,用于建模和描述被验证对象(DUT)的行为和功能。

systemverilog函数

systemverilog函数SystemVerilog是一种硬件描述语言,用于描述硬件设计和验证。

它包含了一系列的语法和语义,使得开发人员能够对电子系统进行描述、模拟和验证。

在SystemVerilog中,我们可以使用函数来创建可重用的代码块,以便在设计和验证过程中使用。

本文将介绍SystemVerilog函数的概念和使用方法。

一、SystemVerilog函数的概述SystemVerilog函数是一段可执行的代码,可以接受输入参数并返回一个值。

它在设计和验证过程中起到了模块化和重用代码的作用。

函数可以用于实现常用的算法、逻辑函数、数据转换等。

与任务不同,函数是同步的,会阻塞进程直到返回结果。

函数可以在模块内部定义,也可以在模块之外定义。

二、SystemVerilog函数的语法函数的语法在SystemVerilog中如下所示:function 函数返回值类型函数名(输入参数列表);函数体;endfunction其中,函数返回值类型指定了函数的返回值类型,函数名指定了函数的名称,输入参数列表指定了函数的输入参数,函数体是实现函数功能的代码。

下面是一个例子:function int add(int a, int b);return a + b;endfunction本例中,函数add接受两个整型参数a和b,并返回它们的和。

三、SystemVerilog函数的特性1.函数可以是递归的,即一个函数可以调用自身。

这在实现一些递归算法时非常有用。

2.函数可以有输入参数,也可以没有输入参数。

输入参数可以通过值传递或引用传递。

3.函数可以有返回值,也可以没有返回值。

如果没有返回值,则函数被称为过程。

4.函数可以有本地变量和输入参数,但不能有任何输出参数。

输出结果通过函数的返回值传递。

5.函数可以在模块之外定义,以便在多个模块中共享和重用。

四、SystemVerilog函数的使用示例下面是一个使用函数的示例,实现了一个二进制加法器:module binary_adder(input [3:0] a, input [3:0] b, output logic [3:0] sum);//二进制加法函数function logic [3:0] binary_add(input [3:0] a, input [3:0] b);logic [3:0] carry = 0;logic [3:0] sum = 0;for(int i=0; i<4; i++) beginsum[i] = a[i] ^ b[i] ^ carry;carry = (a[i] & b[i]) , (a[i] & carry) , (b[i] & carry);endbinary_add = sum;endfunction//使用函数计算二进制加法assign sum = binary_add(a, b);endmodule本例中,我们定义了一个模块binary_adder,包含了一个输入端口a和b,一个输出端口sum。

systemverilog 介绍

SystemVerilog是一个硬件描述语言,用于设计和验证数字系统。

它扩展了Verilog语言,提供了更多的建模能力和验证功能。

在本文中,我将全面介绍SystemVerilog,包括其语言特性、应用领域、优势和未来发展方向。

1. SystemVerilog的语言特性SystemVerilog是一种功能强大的硬件描述语言,它具有以下主要特性:a. 增强的数据类型:SystemVerilog引入了新的数据类型,如bit、logic、byte、int等,使得建模更加灵活和精确。

b. 增强的建模能力:SystemVerilog支持面向对象的建模,包括类、继承、多态等特性,使得设计描述更加直观和模块化。

c. 验证功能:SystemVerilog集成了Assertion语法和Coverage语法,支持设计验证和仿真覆盖率分析,能够更好地检测设计中的错误和缺陷。

d. 接口和连接:SystemVerilog引入了接口和连接功能,方便多模块之间的通信和连接,提高了设计的灵活性和可扩展性。

2. SystemVerilog的应用领域SystemVerilog被广泛应用于数字系统的设计和验证领域,包括但不限于:a. ASIC设计:SystemVerilog可以用于ASIC设计的RTL建模和验证,帮助设计人员快速构建和验证复杂的数字电路。

b. FPGA设计:SystemVerilog支持FPGA设计流程,可以用于FPGA逻辑综合和验证,满足不同规模和复杂度的FPGA设计需求。

c. 验证环境:SystemVerilog的验证功能使其成为验证工程师的首选语言,用于构建全面的验证环境和测试套件。

3. SystemVerilog的优势相比于传统的Verilog语言,SystemVerilog具有如下优势:a. 模块化和面向对象:SystemVerilog的面向对象建模使得设计更加模块化和可重用,提高了设计的灵活性和效率。

b. 验证功能:SystemVerilog集成了验证功能,提供了更多的验证手段和工具,有助于提高设计的质量和稳定性。

uvm验证方法学

uvm验证方法学在现代芯片设计和验证过程中,UVM(Universal Verification Methodology)已经成为了一种非常流行的验证方法学。

它提供了一种标准化的验证方法,可以帮助工程师更高效地进行验证工作。

本文将介绍UVM验证方法学的基本原理和应用,希望能够帮助大家更好地理解和应用这一方法学。

首先,让我们来了解一下UVM的基本原理。

UVM是一种基于SystemVerilog的验证方法学,它提供了一种面向对象的验证框架,可以帮助工程师更好地组织和管理验证环境。

通过使用UVM,工程师可以将验证环境分为不同的层次,从而更好地进行功能验证、时序验证和性能验证等工作。

此外,UVM还提供了一套丰富的验证库,包括各种验证组件和功能,可以帮助工程师更快地搭建验证环境,提高验证效率。

在实际应用中,UVM可以帮助工程师更好地完成以下几个方面的工作。

首先,UVM可以帮助工程师更好地进行功能验证。

通过使用UVM提供的各种验证组件和功能,工程师可以更好地搭建验证环境,完成对芯片功能的全面验证。

其次,UVM还可以帮助工程师进行时序验证。

在现代芯片设计中,时序验证非常重要,通过使用UVM,工程师可以更好地完成对时序要求的验证工作。

最后,UVM还可以帮助工程师进行性能验证。

在芯片设计中,性能验证也是非常重要的一环,通过使用UVM,工程师可以更好地完成对性能指标的验证工作。

除此之外,UVM还有一些其他的优点。

首先,UVM是一种开放的验证方法学,可以帮助工程师更好地进行验证环境的重用。

通过使用UVM,工程师可以将验证环境进行模块化设计,从而更好地进行验证环境的重用。

其次,UVM还可以帮助工程师更好地进行自动化验证。

通过使用UVM提供的各种验证功能,工程师可以更好地进行自动化验证,提高验证效率。

最后,UVM还可以帮助工程师更好地进行仿真管理。

通过使用UVM提供的仿真管理功能,工程师可以更好地进行仿真计划和仿真管理,提高仿真效率。

system verilog 实例化参数模块 -回复

system verilog 实例化参数模块-回复SystemVerilog是一种硬件描述语言,可用于设计和验证各种硬件系统。

其中一个重要的特性是模块化设计,通过实例化参数化模块,可以简化设计和自动化生成代码的过程。

本文将详细介绍SystemVerilog实例化参数模块的概念、语法和应用。

一、什么是实例化参数模块?实例化参数模块是SystemVerilog中一个非常有用的特性,它允许我们在模块定义时通过参数来指定一些特定的行为和属性。

通过使用实例化参数,我们可以重复使用模块,并且根据不同的参数值生成不同的模块实例。

在SystemVerilog中,我们可以在模块的定义中使用参数关键字来声明一个或多个参数。

参数可以是任何数据类型,例如整数,枚举,字符串等。

通过使用参数,我们可以定制化模块,并且在实例化时可以根据实际需求来进行配置。

二、实例化参数模块的语法使用实例化参数模块需要以下几个步骤:1. 声明模块时使用参数关键字来定义参数。

例如:module my_module #(parameter int WIDTH = 8, parameter string NAME = "default");2. 在模块内部,可以使用参数来定义信号,变量和行为。

例如:input [WIDTH-1:0] data;reg [WIDTH-1:0] buffer [NAME];initial display("Hello, s", NAME);3. 在实例化模块时,可以指定参数的具体值。

例如:my_module #(32, "custom_name") inst();在上面的例子中,我们定义了一个名为my_module的模块,并且有两个参数WIDTH和NAME。

在模块内部,我们可以使用这些参数来定义信号,变量和行为。

在实例化模块时,我们可以通过指定参数的具体值来生成不同的模块实例。

system verilog 时序电路和组合电路udp

system verilog 时序电路和组合电路udp SystemVerilog是一种硬件描述语言,它广泛应用于设计和验证复杂的数字电路。

在SystemVerilog中,我们可以使用时序电路和组合电路来描述数字电路的行为和功能。

本文将逐步解释SystemVerilog中时序电路和组合电路的概念和用法。

1. SystemVerilog简介SystemVerilog是一种硬件描述语言,它扩展了Verilog HDL,并添加了一些新的功能。

它既可以用于描述数字电路的结构和行为,也可以用于验证设计的正确性。

SystemVerilog通过组合电路和时序电路的描述,能够模拟和分析电路的行为,进行功能验证和时序验证。

2. 组合电路组合电路是一种无记忆的电路,其输出只依赖于输入的当前值。

在SystemVerilog中,我们使用逻辑门和赋值语句来描述组合电路的行为。

例如,下面是一个使用逻辑门描述的2输入AND门:systemverilogmodule and_gate(input logic a, b, output logic y);assign y = a & b;endmodule在上面的例子中,我们定义了一个具有两个输入和一个输出的模块。

通过使用AND运算符,我们将输入a和b进行逻辑与操作,并将结果赋值给输出y。

这样,无论输入值如何变化,输出y始终是输入a和b的逻辑与结果。

3. 时序电路时序电路是一种有记忆能力的电路,其输出不仅依赖于输入的当前值,还依赖于过去的输入值。

在SystemVerilog中,我们使用时钟、寄存器和时序块来描述时序电路的行为。

下面是一个简单的时序电路的例子:systemverilogmodule counter(input logic clk, input logic reset, output logic [3:0] out); always_ff @(posedge clk or posedge reset)if(reset)out <= 4'b0000;elseout <= out + 1;endmodule在上面的例子中,我们定义了一个计数器模块,它有一个时钟输入clk、一个复位输入reset和一个4位输出out。

uvm 基础知识

uvm 基础知识UVM是一种基于SystemVerilog语言的硬件验证方法学,它为验证工程师提供了一套验证环境和方法,帮助他们设计和开发复杂的硬件验证测试台。

以下为UVM的基础知识:1. UVM环境:UVM环境由各种组件组成,包括顶层测试环境,验证IP,驱动(driver),监控(monitor),事务(transaction),序列(sequence)和配置参数等。

2. UVM顶层测试环境:UVM顶层测试环境是UVM环境的主体,它实例化和连接各种验证组件,管理验证过程和数据路径。

3. 驱动(Driver):驱动是UVM环境的一个组件,负责将测试向硬件发送数据。

它接收事务(transaction)并将其转换为物理信号发送到被测设备。

4. 监控(Monitor):监控是UVM环境的一个组件,用于监听硬件信号并将其转换为事务(transaction)。

它将被测设备的输出信号捕获并生成与之对应的事务。

5. 事务(Transaction):事务是UVM环境中的一种数据结构,它封装了验证过程中的数据和控制信息。

事务用于在驱动和监控之间传递数据。

6. 序列(Sequence):序列是UVM环境中的一个组件,用于生成一系列的事务。

序列定义了事务的数据和控制信息,以及生成和管理事务序列的逻辑。

7. UVM Testbench:UVM Testbench是UVM环境的一部分,它是整个验证环境的顶层组织结构。

UVM Testbench包含了顶层测试环境、监控、驱动、序列等组件。

8. 配置参数:UVM使用一种叫作配置参数(configuration parameter)的机制,用于动态地配置和管理各种验证组件的行为和功能。

9. UVM测试用例:UVM测试用例是UVM环境中的一个组件,它描述了验证目标的特定功能和行为。

测试用例通常由一个或多个序列组成,用来生成一系列的事务。

以上是UVM的基础知识,了解这些概念可以帮助你更好地理解和应用UVM验证方法学。

利用Systemverilog+UVM搭建SOC及ASIC的RTL验证环境

基于SV+UVM搭建SOC/ASIC验证平台UVM-1.1中提供了一个UBUS的例子,但是该例子对于刚刚入门的人来说还是需要一定时间去消化的,本文对该例子进行一步一步的简化,可以帮助理解。

[1-11]如何顺序的写UVM平台(1)-Basic[1-1.平台可以在前期规划好,但是对于搭建平台的人来说,调试永远是最大的问题,如果都将一个个component都写完了,调试起来还是有点痛苦的,所以我更倾向于一步一步的调试平台;先写一个可以pass的基本平台,然后在不断的扩展该平台,最后在各个component中加入所需要的function或者task。

当然,当对搭建平台数量以后,现在基本对平台中的component一次性搭建完成,然后调试并添加需要的function或者task即可。

2.最简单的UVM平台,一个interface,一个DUT,一个TOP,一个test,一个ENV就可以工作了,然后慢慢的添加各个component;3.写interface4.写top module,在top中例化DUT,interface和DUT在top中includeuvm_config_db#(virtual ubus_if)::set(uvm_root::get(),"*","vif",vif);run_test();5.写Makefile,此时编译可以通过6.写自定义的package,然后在top中include该packagetypedef uvm_config_db#(virtual ubus_if)ubus_vif_config;typedef virtual ubus_if ubus_vif;后来证明,这两句话在ubus的env中根本没有用上;7.定义Environment,并将该文件加入到自定义的package中,这个时候编译不能通过此处的get和top中的set是一对,如果top中没有set则会报告·uvm_fatal中的错误if(!uvm_config_db#(virtual ubus_if)::get(this,"","vif",vif))`uvm_fatal("NOVIF",{"virtual interface must be set for: ",get_full_name(),".vif"});8.定义base_test,需要在top中include该test文件,并在makefile中加入编译该test的命令;此时可以再次编译通过,并运行最basic的testcase编译第一次通过总结一:在一个芯片的验证平台中,总会给一个最basic 的base_test ,但是可能每个人负责验证的部分是不一样的,比如说我要验证USB ,那我一定会从base_test 中派生一个usb_base_test 来给自己用,这样我可以在usb_base_test 加入任何我想要的函数,而不会影响到其他人。

SystemVerilog的概念以及与verilog的对比

SystemVerilog的概念以及与verilog的对⽐SystemVerilog语⾔简介SystemVerilog是⼀种硬件描述和验证语⾔(HDVL),它基于IEEE1364-2001 Verilog硬件描述语⾔(HDL),并对其进⾏了扩展,包括扩充了数据类型、结构、压缩和⾮压缩数组、接⼝、断⾔等等,这些都使得SystemVerilog在⼀个更⾼的抽象层次上提⾼了设计建模的能⼒。

SystemVerilog由Accellera开发,它主要定位在芯⽚的实现和验证流程上,并为系统级的设计流程提供了强⼤的连接能⼒。

下⾯我们从⼏个⽅⾯对SystemVerilog所作的增强进⾏简要的介绍,期望能够通过这个介绍使⼤家对SystemVerilog有⼀个概括性的了解。

1. 接⼝(Interface)Verilog模块之间的连接是通过模块端⼝进⾏的。

为了给组成设计的各个模块定义端⼝,我们必须对期望的硬件设计有⼀个详细的认识。

不幸的是,在设计的早期,我们很难把握设计的细节。

⽽且,⼀旦模块的端⼝定义完成后,我们也很难改变端⼝的配置。

另外,⼀个设计中的许多模块往往具有相同的端⼝定义,在Verilog中,我们必须在每个模块中进⾏相同的定义,这为我们增加了⽆谓的⼯作量。

SystemVerilog提供了⼀个新的、⾼层抽象的模块连接,这个连接被称为接⼝(Interface)。

接⼝在关键字interface和endinterface之间定义,它独⽴于模块。

接⼝在模块中就像⼀个单⼀的端⼝⼀样使⽤。

在最简单的形式下,⼀个接⼝可以认为是⼀组线⽹。

例如,可以将PCI总线的所有信号绑定在⼀起组成⼀个接⼝。

通过使⽤接⼝,我们在进⾏⼀个设计的时候可以不需要⾸先建⽴各个模块间的互连。

随着设计的深⼊,各个设计细节也会变得越来越清晰,⽽接⼝内的信号也会很容易地表⽰出来。

当接⼝发⽣变化时,这些变化也会在使⽤该接⼝的所有模块中反映出来,⽽⽆需更改每⼀个模块。

system verilog 语法

system verilog 语法

使用System Verilog进行硬件设计是一项复杂而充满挑战的任务。

在这个语言中,我们可以描述数字逻辑电路的行为和结构,并对其进行仿真和验证。

System Verilog提供了丰富的语法和特性,使我们能够轻松地设计复杂的电路,并确保其正确性。

在System Verilog中,我们可以使用模块来组织我们的设计。

一个模块代表一个独立的功能单元,可以由多个输入和输出端口组成。

通过连接不同的模块,我们可以构建出整个系统。

每个模块可以包含多个时钟域,以及各种组合逻辑和时序逻辑。

我们可以使用always块来描述时序逻辑,使用if-else语句来描述组合逻辑。

System Verilog还提供了一些方便的特性,如任务和函数。

任务可以在仿真过程中执行一些特定的操作,而函数可以返回一个值。

这些特性可以让我们的设计更加模块化和可重用。

除了描述电路结构和行为外,System Verilog还具有强大的验证功能。

我们可以使用断言来验证设计的正确性,并使用cover语句来检测设计中的覆盖率。

这些功能可以帮助我们发现和解决潜在的问题,确保设计的可靠性。

总的来说,System Verilog是一种强大而灵活的硬件设计语言。

它提供了丰富的语法和特性,使我们能够轻松地描述和验证复杂的数字逻辑电路。

通过合理运用这些特性,我们可以设计出高效、可靠

的硬件系统。

虽然学习和掌握System Verilog可能需要一些时间和经验,但它无疑是现代硬件设计中不可或缺的工具之一。

uvm方法学

uvm方法学UVM方法学是一种基于SystemVerilog的硬件验证方法学,被广泛应用于半导体行业中的验证工作。

本文将从UVM方法学的背景、基本原理、主要特点以及应用场景等方面进行介绍,以帮助读者更好地了解和应用UVM方法学。

一、背景随着半导体技术的不断发展,芯片设计的复杂性和验证难度也在不断增加。

传统的验证方法已经无法满足日益增长的验证需求,因此需要一种更加高效、灵活和可重用的验证方法学。

UVM方法学应运而生,它基于SystemVerilog语言,通过提供一套标准的验证组件和方法,帮助验证工程师更好地进行验证工作。

二、基本原理UVM方法学的基本原理是将验证环境和验证测试分离开来,通过验证环境提供的各种功能和工具,来实现对被验证设计的测试和验证。

验证环境由一系列的验证组件组成,包括顶层测试组件、驱动组件、监控组件、代理组件等。

验证测试则由测试用例和测试程序组成,通过对验证组件的配置和控制,来执行测试并收集验证结果。

三、主要特点1. 重用性:UVM方法学提供了一套标准的验证组件和方法,可以在不同的项目和设计中进行重复使用,提高了验证工作的效率和可靠性。

2. 可扩展性:UVM方法学采用了面向对象的设计思想,可以通过继承和扩展的方式,方便地创建新的验证组件和功能,以满足不同设计的验证需求。

3. 可配置性:UVM方法学提供了丰富的配置机制,可以通过配置文件或命令行参数来灵活地配置验证环境和测试,以适应不同的验证场景。

4. 仿真效率:UVM方法学通过使用事务级建模(TLM)和基于事件驱动的机制,可以有效地减少仿真时间和资源消耗,提高仿真效率。

5. 报告和分析:UVM方法学提供了丰富的报告和分析机制,可以方便地生成验证结果报告、覆盖率报告等,帮助验证工程师进行验证结果的分析和优化。

四、应用场景UVM方法学广泛应用于各种半导体芯片的验证工作中,特别适用于复杂和高性能的芯片设计。

以下是一些常见的应用场景:1. 处理器验证:UVM方法学可以用于验证各种类型的处理器,包括单核和多核处理器,通过创建适当的验证环境和测试用例,可以对处理器的功能和性能进行全面的验证。

uvm标准

UVM标准引言UVM(Universal Verification Methodology,通用验证方法学)是一种广泛应用于电子设计验证领域的开放式验证方法学。

本文将深入探讨UVM标准的基本原理、应用场景、优势和挑战。

UVM标准的基本原理UVM标准是建立在SystemVerilog Verification语言基础之上的,并且采用了面向对象编程(OOP)的思想。

它提供了一种方法来组织、管理和执行验证任务,通过将测试环境、测试用例和共享的功能组件模块化,提高了验证工作的效率和可重用性。

UVM标准的应用场景UVM标准广泛应用于各种规模的电子设计验证项目中。

它适用于各种验证级别,包括模块级、芯片级和系统级验证。

UVM标准提供了丰富的功能和库,包括配置管理、消息传递、事务级建模等,可应用于各种验证任务,如功能验证、性能验证和功耗验证等。

1. 功能验证功能验证是验证设计是否符合规范要求的过程。

UVM标准提供了一种验证环境框架,可以快速构建可重用的验证环境,包括生成和注入各种测试用例,以覆盖设计的各种功能和边界条件。

通过使用UVM标准,可以提高功能验证的效率和准确性。

2. 性能验证性能验证是验证设计在各种工作负载和输入条件下的性能表现的过程。

UVM标准提供了交易级建模(TLM)的支持,可以使用事务模型来描述设计和验证环境之间的交互过程。

这种方式可以更好地捕捉和分析系统中的延迟、吞吐量和资源利用等关键性能指标。

3. 功耗验证功耗验证是验证设计在不同功耗模式下的电源消耗的过程。

UVM标准提供了功耗建模和分析的支持,可以模拟和测量设计在不同功耗模式下的电流和电压波形,并分析功耗优化的潜力。

使用UVM标准进行功耗验证可以帮助设计团队在系统级别上做出权衡和决策,以达到设计功耗目标。

UVM标准的优势UVM标准的应用带来了诸多优势,下面将介绍几个主要方面。

1. 可重用性UVM标准通过提供一种标准化的验证方法学,鼓励验证环境的模块化和重用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

– Verilog 2001

• Major function upgrade

– Verilog 2005

• Corrections

– Systemverilog

• OOP

• Latest standard version

– IEEE Std 1800-2009

Marvell Confidential

– A component which handles transaction object

• Channel

– Allow for the communication of transactions among transactors

Marvell Confidential

Configure a register

Marvell Confidential

Configure a register (cont.)

Marvell Confidential

About UVM

• Implement a fundamental infrastructure by using system verilog

– – – – – Implicit phasing Communication Factory overriding Configuration Messaging

Marvell Confidential

• Port

– blocking_(put/peek/get/get_peek)_port – nonblocking_(put/peek/get/get_peek)_port

• Export

– blocking_(put/peek/get/get_peek)_export – nonblocking_(put/peek/get/get_peek)_export

How to describe a circuit

Marvell Confidential

Adopt OOP into traditional verilog

• Verilog

– Everything must be static

• reg, wire…

– Description of a procedure or process

Marvell Confidential

Implicit phasing

• Synchronize the behavior among transactors (components)

– Circuit in nature is parallel executed

Marvell Confidential

– Suitable to describe behavior

Marvell Confidential

Using system verilog in verification

• Verification is kind of behavior

– Stimulus, configuration, result, analysis and etc

Messaging

• Unified messaging scheme

– Verbosity

• none, low, medium, high, full, debug

– Severity

• info, warning, error, fatal

Verbosity UVM_NONE UVM_LOW UVM_MEDIUM UVM_HIGH UVM_FULL UVM_DEBUG UVM_INFO UVM_WARNING UVM_ERROR UVM_FATAL Severity UVM_NO_ACTION UVM_DISPLAY UVM_LOG UVM_COUNT UVM_EXIT UVM_CALL_HOOK Action

Implicit phasing (cont.)

• Common phase • UVM phase

Note: build_phase are executed topdown through hierarchy, others are bottom-up

Marvell Confidential

Hale Waihona Puke Communication• Counter, Finite State Machine…

– Suitable to describe circuit

• Systemverilog

– Some constructs can be dynamic

• class, pointer

– Description of object

• Properties, Methods

• Provide some utilities to ease verification work

– DPI, mailbox, socket

• Using systemverilog to describe a kind of behavior

– Hidden the detailed information from behavior planning (especially timing information, clock cycles) – Systemverilog’s OOP feature provides flexibility for behavior planning

Marvell Confidential

Why systemverilog & UVM

Wenzong Pan 04/23/2015

Marvell Confidential

What is of the importance!!!

•

When talking about a programming language, what we should understand first?

• FIFO

– uvm_tlf_fifo

Marvell Confidential

Factory overriding

• More flexible for replacing certain transactor (component) before it is really built

– set_int_override<_by_name/type> – set_type_override<_by_name/type>

Marvell Confidential

A layered verification environment

Marvell Confidential

Three concepts

• Transaction

– An object which carries information

• Transactor

– By Prabhu Goel & Phil Moorby in 1983/1984 in Gateway Design Automation (purchased by Cadence in 1985)

• Evolution history

– Verilog 95

• Become an open standard

Marvell Confidential

Configuration

• A common configuration scheme

– uvm_config_db, uvm_resource_db – Globally accessed, used by caution

Marvell Confidential

– – – – Syntax??? Application??? Benchmark??? Author???

WHY TO INVENT THIS LANGUAGE!!!

Marvell Confidential

About verilog

• First invented hardware description language