M29F002BB90K1中文资料

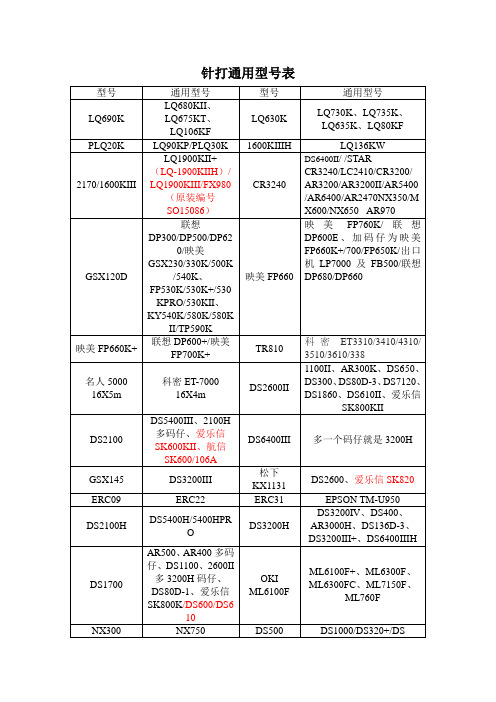

针打类新通用表

映美FP630KII(JMR125)

FP680K/FP680KPRO

映美FP630K(JMR126)

TP632K

映美FP5400K/5800K加上FP660K+导带扣

映美FP5900KII/FP5900KIII/FP8400KIII/映美TP540K/联想DP8400Βιβλιοθήκη NX400/410NX200

DPK800

DPK880/810/8580

DPK900

DPK500/510/910/8680

EPSON LQ100

映美FP200K/龙润310B/凯丰310B色带票据打印机?

EPSON

LQ300/LQ800

映美LQ300K、EPSON LX300K+II(8750#)/LQ300K+II(#7753)/LQ300K+/305KT/305KTII/580K+

更新日期:2012-06-01

GW5370

联想DP8000

DS6400III

DS6400TX/DS3100/DS3100II/DS3100X/DS810/DS800/DS800H/DS7310/AR700

LQ590

原装编号SO15337

映美LQ200KII

无通用

RS11

ND98/DPK7000/DPK7010?

映美FP5400/FP 8400KIII

LQ1900KIII/FX980(原装编号SO15086)

CR3240

DS6400II//STAR CR3240/LC2410/CR3200/AR3200/AR3200II/AR5400/AR6400/AR2470NX350/MX600/NX650 AR970

各厂家中九接收机芯片IC资料大全(目前最完整的)部分附针脚定义

各厂家中九接收机芯片IC资料大全(目前最完整的)部分附针脚定义最新刷机资料点下面的链接最新刷机资料1最新刷机资料24月3日BIN教程工具集中帖刷机教程大全刷机工具大全2.10-3.2刷机bin大全3月3日后刷机bin大全各厂家中九接收机顶盒芯片IC资料大全(目前最完整的),部分附针脚定义。

方便大家速查。

可使用CTRL+F,然后输入相关数据进行速查,或者也可以下载附件。

品牌产品型号芯片配置海尔2晶10芯IC:HI2023E+1108+5812海尔高清OST-666 2晶6芯IC:M88VS2000+241674K.1+M88TS2020海尔高清OST-666 3晶12芯IC:High032E+His121+M88TS2020海尔3晶10芯(9针接口)IC:HI2023E+1108+5812+ESMTM12L64164A-GNR1T80AB 海尔高清OST-666 2晶6芯IC:Hi2023E+3160+TS2020欧视达ABS-209B 3晶10芯IC:GX3001+GX1121+LW37 欧视达ABS-209B 3晶11芯IC:GX3001+5037+8211欧视达ABS-309B 3晶11芯IC:GX3001+GX1121+MGCE5037欧视达AS-900S 1晶11芯IC:GX6121+25L80+LW37城市之宝BEX868 Y32S-93AT 2晶10芯IC:HTV903F+A VL1108+TS2020通达Y35S-8BAT/Y35S-8CAT 2晶10芯IC:HTV903+A VL1108+5812通达Y30S-01BT 2晶12芯IC:HTV903+A VL1108+2020 皇朝HSR-268 10芯IC:Hi2023+A VL1108+5812小霸王TDX-668E ABS-S1 1晶6芯IC:Hi2023+Hi3102+FT8211+HT1117天地星小霸王TDX-328B 1晶10芯IC:ALi M3328F+5810天地星小霸王TDX-668A (9针接口)IC:HI2023+1108+夏普头天地星小霸王TDX-668B 2晶振IC:HTV903+A VL1108EGA+RDA5812+25L8005天地星小霸王(三星数码王)TDX-668B 单晶6芯.针脚定义①-TXD ②-RXD ③VCC ④-GND ⑤-BL IC:Hi2023E+RDA5812+A VL1108E+MXT8211a+25L8005天地星(原大盒中星九号)3晶IC:Hi2023+1108+5037天地星TDX-668B 2晶10芯IC:Hi2023+A VL1108+5812天地星小霸王TDX-668C 2晶6芯IC:HTV903+A VL1108EGA+RDK5812+25F80小霸王TDX-328B 1晶10芯IC:ALi M3328F+5810小霸王TDX-668B 6芯IC:Hi2023+RDA5812+A VL1108E 小霸王TDX-668B 2晶6芯IC:HTV903+1108+5812小霸王TDX-668E 1晶6芯IC:Hi2023EC+Hi3121+5812 小霸王TDX-668E 2晶6芯IC:HTV903+1108+5812小霰王XC-B298 1晶12芯IC:HTV903-RDA5812-A VL1108 小霸王ABS-1388 2晶10芯针脚定义①-GND ②-RXD ③-TXD ④VCC小霸王ABS-1688 2晶10芯针脚定义①-GND ②-RXD ③-TXD ④VCC IC:Hi2023EC+Hi3122E+5812小霸王GF902 IC:A VL1118a+A V2020+EN25F80索尼高清ABS-S 258 2晶10芯针脚定义①-GND ②-RXD ③-TXD ④VCC IC:Hi2023EC+Hi3122E+5812索尼高清ABS-S 258 2晶10芯针脚定义①-GND ②-RXD ③-TXD ④VCC IC:Hi3102E+Hi2023EC+A V2020太阳红TYH-279ABS/289ABS/299ABS 2晶10芯针脚定义①-GND ②-RXD ③-TXD ④VCC松下科技星TDX-668B1/松下科技星-668EIC:Hi3102E+Hi2023EC+5812松下科技星TDX-668B 2晶6芯IC:HTV903FH42+A VL1108EGA+RGK5812松下科技星668B 2晶6芯Hi2023(E0908)+EVl1108EG2+5812松下科技星-668C 2晶6芯针脚定义①-RX .②-TX .③-GND .④VCC. ⑤-BLIC:A VL1108EG+HTV903F+5812松下科技星668E 2晶6芯IC:HV903+A VL1108E+5812松下科技星/海尔数码/海信数码单双晶6芯IC:Hi2023E+Hi3102(Hi3121)+5812松下科技星TDX-668B 2晶6芯针脚定义①-RXD .②-TXD .③-GND .④VCC. ⑤-BLIC:Hi2023+A VL1108+5812+25L8005松下高清SX168 3晶6芯IC:HTV903F+A VL1108+A V2020 松下数码王P-269A 2晶6芯IC:Hi2023E+Hi3122+A V2020 松下高清OST168 2晶10芯IC:Hi2023E+Hi3121+A V2020 松下科技PS-228 11芯IC:Hi2023+Hi3122+5812松下科技PS-228 2晶6芯IC:M88VS2000+M88TS2020+ES261474K松下科技PS-228 1晶12芯N88VS2000+ES261344K+M88TS2020高频头+T25P80+S163816STS松下科技PS-228 2晶IC:HTV903+1108+2020松下科技PS-228 2晶10芯IC:GX3001+GX1211+5812松下数码王OST-266 10芯(4针)针脚定义①-GND ②-RXD ③-TXD ④VCCIC:Hi2023E+Hi3106+2020松下数码王OST-266 2晶6芯IC:M88VS2000+M88TS2020+261414k+25F80松下数码王OST-266 2晶6芯IC:Hi2023E+Hi3102E+M88TS2020+MXT8211松下高清OST-466 2晶10芯IC:Hi2023e+Hi3121+MBBTS2020+MBDA80CG松下科技星3晶6芯IC:Hi2023+A VL1108+WGCE5037松下科技星.海尔数码.海信数码单双晶+6芯IC:Hi2023E+Hi3102(3121)+5812中星科技单晶14芯IC:Hi2023E+1108+5812+25L8单晶14芯中星科技ZG-N02 12芯IC:GX3001+A V2020中星科技2晶10芯针脚定义①-GND ②-RXD ③-TXD ④VCCIC:Hi2023EC+Hi3102E+5812+M12L64164A中兴科技ABS-S323 2晶10芯IC:Hi2023EC+HI3102E+5812+M12L64164A村村通ABS-S323- 2晶10芯针脚定义①-GND ②-RXD ③-TXD ④VCCIC:Hi2023EC+Hi3122E+5812村村通2晶6芯IC:HN4+0001+5812村村通ZL5188 1晶13芯IC:HTV903+1108+SHARP高频头村村通ZL-5188A 2晶11芯IC:HTV903+A VL1108+RDK5812村村通ZL-5188B 2晶13芯IC:HTV903+A VL1108+RDK5812 村村通ZL-5188B 2晶10芯IC:HTV903+A VL1108EGA+5812村村通ZL5188B 1晶13芯IC:HTV903+A V1108+SHARP6306村村通ZJ-11 IC:HTV903+1108+夏普头S7ZH6306村村通wx-666 3晶10芯IC:GX3001+GX1121+RDK5812村村通ZL-6188 2晶10芯IC:HTV903+A VL1108EGA+5812村村通ZL-6188C 10芯IC:GX3001+GX1121+RDK5812村村通DTH(铁壳) 3晶12芯IC:A VL1108EG+HTV903F+A V2020村村通001 3晶10芯IC:GX3001+GX1121+RDK5812村村通ABS-S GD-1008 3晶10芯IC:Hi2023E+A VL1108E+ZL10037+F16-100HIP村村通ABS-S888AIC:Hi2023EC+Hi3121+ET8211+RDA5812+25X80视美人ABS-S PS-1288 2晶10芯IC:Hi3102E+Hi2023EC+A V2020视美人PS-1288 ICM88VS2000+ES256454K+M88TS2020 视美人2晶10芯IC:Hi2023+3106+A V2020太平鸟HJ321 3晶10芯针脚定义①-GND .②-RXD .③-TXD .④VCCIC:GX3001+GX1121+TS2020太平鸟HJ321 3晶11芯IC:GX3001+GX1121+5812焦点yj5888 2晶10芯IC:HTV903+A VL1108+RDA5812幸运之星YJ5988 2晶10芯IC:HTV903F+A VL1108EGa+A V2020克莱尔HT701 1晶10芯IC:A VL1108EG+HTV903F+M88TS2000中电电子J-6288 ABS-S 3晶12芯IC:GX3001+GX1121+5812小福星3晶11芯针脚定义①-GND .②-(空) .③-RXD .④-TXD ()IC:GX3001+GX1121+5812东仕DIS-2000K 单晶10芯IC:HTV903F+A VL1108E+A V2020Souy Ericsson英文机2晶10芯IC:GX3001+GX1121+A V2020高斯贝尔/歌德威尔ABS-208F 3晶14芯针脚定义①-GND .②-TXD .③-RXD .④VCC .⑤-BL IC:A VL1108EG+Hi2023+5812高斯贝尔ABS-208 1晶14芯(5针).针脚定义①-GND .②-TXD .③-RXD .④VCC .⑤-BL IC:A VL1108EG+Hi2023+5812歌德威尔ABS-208H/高斯贝尔208P 3晶14芯针脚定义①-GND .②-TXD .③-RXD .④VCCIC:M3330E+A VL1108EG+A V2020+M12L64164高斯贝尔ABS-208P/歌德威尔208H 1晶14芯针脚定义①-GND .②-TXD .③-RXD .④VCC .⑤-BL IC:A VL1108EGi+Hi2023+5812高斯贝尔ABS-208P/歌德威尔208H 1晶14芯针脚定义①-GND .②-TXD .③-RXD .④VCCIC:M3330E+A VL1108EG+A V2020+M12L64164A高斯贝尔ABS—208F IC:Hi2023+A VL1108EGA+M88TS2020高斯贝尔ABS—208 2晶14芯IC:HTV903+1108+5812吉祥ABS-208C IC:Hi2023+A VL1108EGa+GST GAIM-18R ABS-STUNER吉祥ABS-2009B 3晶14芯IC:GX3001+GX1121+RDK5812吉祥ABS-2009大铁壳2晶IC:GX3001+GX1121+夏普高频头ABS-2009 2晶12芯IC:HTV903+1108+GAIM-18R歌德威尔ABS-208 3晶6芯IC:D61216GJ+1108+5812歌德威尔ABS-208 3晶14芯(9针接口)IC:M3330+1108+5812高斯贝尔ABS-208 3晶(9针母串口)IC:A VL1108+Hi2023+GAIM-18RIC:D61216GJ100+A VL1108EG+S29AL016D70TF102+ISSI高斯贝尔ABS-208N 铁壳(9针母串口) IC42s16400F高斯贝尔ABS-208 IC:D61216GJ+A V1108+29AL016D+5812高斯贝尔ABS-208S 1晶IC:NECD61216GJ+A VL1108EGa+高频头高斯贝尔ABS-208Q 1晶14芯IC:A VL1108EGA+M3330E+M12L64164A+A V2020ABS-S LX-3688A 1晶12芯IC:GX3001+GX1121+5812现代V4、V5 3晶9芯IC:GX3001+GX1121+5812+EN25D80+HY57V641620ETP-6 集信科技V6铁壳(海尔机芯) 3晶9芯针脚定义①VCC .②-TXD .③-RXD .④-GNDIC:1108EG(Hi3121)+Hi2023+5812.集信科技V4.V6(铁壳) 2晶9芯( B型)针脚定义①VCC .②-RXD .③-TXD .④-GNDIC:0001(GX3001)+HN4F74+5812集信科技V4 .V6(铁壳) 2晶10芯针脚定义①VCC. ②-RXD .③-TXD .④-GNDIC:00001(GX3001)+HN4LSW+S6416AHTA+5812集信科技V4.V6(铁壳)IC:HN4LSW+S6416AHTA-6BZH+EN25F80-1000CP+5812集信科技V4.V6(铁壳)IC:0002P1M43700ta06+5812+EN25F80+TM8211+POL4558 集信科技V4.V5 1晶10芯(A型)针脚定义①VCC .②-RXD .③-TXD .④-GNDIC:0002(GX6121)+5812+M12L64164A艾雷特2晶10芯IC:M88VS2000+ES256454K+M88TS2020艾雷特V5IC:HN4F910931M2EE+0001G1K729-1TA060932+5812艾雷特ALT5812 IC:GX3001+GX1121+5812艾雷特ALT600A 2晶11芯IC:M3330E+A VL108的+夏普高频头艾雷特ALT600A/吉祥ABS-2009 2晶IC:GX3001+GX1121-ES29L160FB+SHARP高频头艾雷特ALT600GIC:HTV903+A VL1108+25L160+ST2020(Y32S-8BAT 081113)艾雷特ALT6812 1晶10芯IC:GX6121+RDA5812+ZB-1A艾雷特ALT6815 1晶10芯IC:GX6121-RDA5812-2B-1A艾雷特ALT7815 3晶10芯IC:GX3001+1121+TS2020艾雷特1000 黑珍珠V4.V5 1晶10芯IC:0002(GX6121)+EEPLDA+5812+M12L64164A艾雷特alt 7812 3晶10芯IC:GX3001+GX1121+5812艾雷特ALT7812 3晶11芯针脚定义①VCC .②-RXD .③-TXD .④-GNDIC:GX3001+GX1121+5812艾雷特ALT600c 2晶10芯IC:GX3001+GX1121+5812艾雷特ALT600c 2晶11芯IC:GX3001+GX1121+5812艾雷特ALT600c 1晶11芯IC:CH216H+A VL1108+C6XS-8CA深圳亿通DVB-V5 10芯IC:HN4N46+EN25F80+G1N540-1TA06+IS42S16400-7T+581亿通电子WS-3688ZL 1晶10芯IC:Hi2023EC+Hi3102E+A V2020中大WS-3688ZJ (铁壳) 1晶10芯针脚定义①-GND .②-RXD .③-TXD .④VCCIC:Hi2023EC+Hi3102E+A V2020中大WS-3688ZJ (铁壳) 2晶10芯IC:Hi2023+A VL1108EG+夏普高频头皇视HSR-208A 2晶10芯IC:Hi2023E+A VL1108EG+A V2020皇视HSR-208B 2晶10芯IC:Hi2023+1108+2020皇视HSR-208B 单晶10芯IC:3330+1108+2020皇视HSR-208B 单晶10芯针脚定义①-GND ②-TXD ③-RXD ④-VCCIC:Hi2023EC+Hi3102+A V2020皇视HSR-2090 2晶11芯IC:Hi2023+1108EGa+夏普头++EN29LV160皇视HSR-210A 单晶6芯IC:Hi2023ec+Hi3122e+A V2020 皇视HSR-260A 铁盒2晶10芯IC:Hi+1108+SHARP夏普头皇视HRS-268 3晶10芯IC:Hi2023EC+Hi3102E+A V2020 皇视HRS-268 2晶10芯IC:Hi2023EC+Hi3121+5812皇视HSR-268 单晶10线IC:HTV903+A VL1108+5812皇视HSR-268 单晶10线IC:Hi2023+Hi3121+A V2020皇视HRS-268 3晶10芯IC:Hi2023EC+A VL1108+5812皇视HSR-260B 3晶10芯IC:Hi2023+1108+2020皇视HSR-260B/索尼高清258 1晶10芯IC:2023E+3121+A V2020皇视HSR-260B 3晶10芯IC:HI2023+1108+5812皇朝HSR-268 10芯IC:Hi2023+A VL1108+5812凯恩斯KES-2066S 6芯针脚定义①-TXD .②-RXD .③VCC .④-GND .⑤-BL IC:Hi3122E+Hi2023ECE+N25F80凯恩斯KES-2077Z 1晶6芯针脚定义①-TXD .②-RXD .③VCC .④-GND .⑤-BL IC:Hi2023EC+3122E+5812凯恩斯2077ABS 2晶10芯IC:M3330+A VL1108+5812凯恩斯2077ABS 2晶10芯IC:Hi2023+1108E+5812+25L800凯恩斯KES-2088S 2晶6芯IC:Hi2023EC+HI3102E+RDA5812凯恩斯KES-2088S 2晶10芯IC:Hi2023EC+HI3102E+RDA5812凯恩斯KES-2088S 2晶6芯针脚定义①-TXD .②-RXD .③VCC .④-GND .⑤-BL IC:Hi2023EC+HI3122E+RDA5812凯恩斯KES-2088Z (5针).针脚定义①-TXD .②-RXD .③VCC .④-GND .⑤-BL IC:Hi2023EC+HI3102E+RDA5812凯恩斯KES-2099S 2晶6芯IC:Hi2023EC+Hi3102E+5812+25L80凯恩斯KES-2188T 3晶10芯IC:Hi2023+1108+5812凯恩斯KES-2188T 3晶12芯IC:Hi2023+1108E+5037凯恩斯KES-2288S 3晶10芯IC:M3330E+A VL1108+RDA5812+M12L64164A凯恩斯KES-2688b 2晶10芯IC:Hi2023e+1108e+5812 凯恩斯KES-2688S 2晶10芯IC:Hi2023e+1108e+5812凯恩斯KES-2788S 3晶10芯IC:Hi2023E+A VL1108EGa+5812凯恩斯KES-2788S 2晶6芯IC:Hi2023EC+Hi3122E+5812凯恩斯KES-5188 11芯IC:HTV903+A VL1108EGA+A V2020凯恩斯KES-5188A铁盒2晶10芯IC:HTV903F+A VL1108+RDK5812+F80+PT8211凯恩斯KES-5188B 2晶13芯IC:HTV903+RDA5812+A VL1108+8211+F80美路3晶13芯IC:Hi2023E+1108+2119美路2晶12芯IC:GX3003+GX1121+5812美路MR-1809 IC:Hi2023E+A VL1108E+高频头MAX2119C 美路MR-5598铁壳3晶12芯IC:GX3003+GX1121+5812 美路MR-5598 3晶12芯针脚定义①VCC. ②-RXD .③-TXD .④-GNDIC:Hi2023E+1108+2119C美路-5798 IC:Hi2023E+1108+2119C美路-5598 IC:Hi2023+1108+GAIM-18R+29lv160ZY 5518A 2晶10芯IC:Hi2023E+3102E+5812万利达ZY-5518A 1晶6芯((5针))IC:Hi2023E+Hi3102E+5812万利达ZY-5518A 2晶10芯IC:CX3001+GX1121+5812万利达ZY-5518A 3晶10芯(9针接口)IC:Hi2023+1108+5812长虹新一代3晶10芯IC:HI2023E+1108E+FL016ALF长虹新一代,海尔数码、海信数码单双晶体6芯IC:HI2023E+3102(3121)+5812长虹数码CH930 3晶12芯IC:HTV903F+1108+A V2020+M80长虹精品TC-6688ABS 2晶10芯IC:HTV903+A VL1108EG+5812长虹精工YJ5978 1晶10芯IC:HTV903F+1108EGa+2000+F80-100+8211长虹KES-2099S 2晶5芯IC:Hi2023+Hi3102E+5812长虹KES 2晶6芯IC:Hi2023+Hi3102+5812长虹CH920 3晶6芯IC:HTV903F+1108EGa+A V2020+25L80航天天信WTD198J 2晶12芯(9针接口)IC:GX3001+GX1121+5812+ES29LV160FB-70TG航天珠江WTD-198J 2晶12芯IC:GX3001+GX1121+5812 航天珠江ABS-209B IC:GX3001+GX1121++WGSE5037航天数码ABS-3809 2晶12芯IC:GX3001+GX1121+5812航天直播HT-168 3晶12芯IC:Hi2023+1108+夏普头航天高清王-HS-166 2晶12芯IC:Hi2023EC+Hi3102E+RDA5812航天高清王HS-169 2晶12芯针脚定义①-GND .②-TX .③-RX .④-VCCIC:Hi2023EC+3122+5812天诚TCD-219ABS 2晶10芯IC:M3330E+A VL1108EGA+5812天诚TCD-299Z 2晶10芯IC:Hi2023+3206+5812天诚TD-299Z 2晶5芯IC:Hi2023+3206+5812天诚TD-2992 2晶6芯IC:Hi3122E+Hi2023E+5812+F80+MXT8211天诚539 2晶10芯IC:HTV903+A V1108+5812天诚519型2晶10芯IC:HTV903+1108E+5812天诚TCD-239ABS 3晶10芯IC:M3330+1108+5812 天诚TCD-239ABS 2晶10芯IC:Hi2023+1108E+5812 天诚TCD-239 2晶10芯IC:M3330E+1108E+5812天诚TCD-299ABS 2晶10芯IC:Hi2023EC+Hi3121+5812天诚TCD-319ABS 3晶10芯IC:Hi2023E0914+A VL1108EGa+RDA5812天诚TCD-319ABS 3晶12芯IC:Hi2302+A VL1108+5037 天诚TCD-369ABS 3晶10芯IC:Hi2023+1108+5812天诚TCD-369ABS 3晶10芯IC:M3330E+1108+5812天诚TCD-369ABS 3晶5芯IC:Hi2023+1108+WCGE5037天诚TCD-509ABS 3晶10芯IC:M3330E-A VL1108EGa-5812天诚TCD-509ABS 10芯(5针)IC:Hi2023+A VL1108+5812+M12L6416A天诚TCD-539ABS 2晶10芯(5针)针脚定义①-RX .②-TX .③VCC .④-GND .⑤-BLIC:M3330E+A VL1108+25L80+5812天诚TCD-579ABS 2晶10芯IC:Hi2023+Hi1108+5812天诚TCD-579ABS 3晶10芯IC:HiM3330+A VL1108EGa+RDA5812天诚TCD-589ABS 3晶10芯IC:Hi2023+1108+5812天诚TCD-689ABS铁壳机2晶12芯(9针接口)IC:Hi2023+A VL1108+夏普头天诚TC-ABS1108A 11芯IC:Hi2023EC+A VL1108+5812 TCD--239ABS 2晶10芯IC:M3330E+A VL1108E+5812 TCD-339ABS 3晶10芯(9针接口) IC:Hi2023+1108+5812TCD-509ABS 3晶10芯IC:Hi2023E0915+A VL1108EGa+RDA5812TCD-509ABS 2晶10芯(5针) IC:Hi2023EC+HI3121+5812TCD-519ABS 2晶10芯IC:Hi2023+A VL1108+5812TCD-599 2晶10芯IC:M3330+A VL1008+5812TCD-219ABS 2晶振10芯针脚定义①-TXD .②-RXD .③-VCC .④-GND .⑤-BLIC:Hi2023EC+Hi3121+5812爱普思DVB-2568 3晶10芯IC:HTV903+1121+2020卓异5518A 3晶10芯IC:Hi2023E+1108+5812卓异5518A(铁壳)3晶11芯IC:Hi2023E+1108+5812卓异5518A(铁壳)2晶11芯(9针接口) IC:Hi2023+1108+夏普独立高频头卓异5518A G 1晶10芯爱百信针脚定义①-GND .②-TXD .③-RXD .④VCCIC:HTV903+A VL1108+5812卓异ZY-5518A G 驰骋天下针脚定义①-GND .②-RXD .③-TXD .④VCCIC:HTV903+A VL1108+5812+F80卓异5518AG 2晶11芯针脚定义①-GND .②-RXD .③-TXD .④VCC ⑤-BL IC:Hi2023E+1108+5812卓异ZY-5518A H 春1晶6芯针脚定义①-GND .②-TXD .③-RXD .④VCCIC:GX3001+5812+25L8005卓异ZY-5518A H 春2晶10芯针脚定义①-GND .②-TXD .③-RXD .④VCC .⑤-BLIC:Hi2023E+HI3121+5812+F25L008A卓异ZY-5518A H 秋针脚定义①-GND .②-RXD .③-TXD .④VCC 升级接口在内部PCB上IC:GX6121+5812+F80卓异ZY-5518A H 秋1晶10芯针脚定义①-GND .②-RXD .③-TXD .④VCC ⑤-BLIC:Hi2023EC+Hi3102E+5812+F80-100卓异ZY-5518A H至尊王牌2晶10芯针脚定义①-GND .②-TXD .③-RXD .④VCCIC:GX3001+GX1121+5812+25L8005卓异ZY-5518A H 财富2晶6 芯针脚定义①-GND .②-TXD .③-RXD .④VCC .⑤-BLIC:芯片掩磨+5812+80L100绿达PS-1288 3晶12芯IC:Hi2023E+ABS090520+M88TS2020绿达PS-1288 2晶12芯IC:Hi2023+Hi3021+A V2020绿达视美人\卓异1晶10芯IC:Hi2023EC+Hi3121+2020 绿达金统帅3晶10芯IC:M3330+1108+5812三星DQ88/DQ66 IC:HTV903F+A VL1108+A V2020三星高清王2晶12芯IC:GX3001+GX1121+5812三星高清DQ88 3晶12芯IC:HTV903F+A VL1108+A V2020 三星数码王TDX668B 2晶6芯针脚定义①-RXD .②-TXD .③-GND .④VCC. ⑤-BLIC:Hi2023+1108+5812三星数码王TDX668B 2晶6芯IC:HTV903F+A VL1108E+5812三星数码王668C 2晶6芯IC:HTV903F+A VL1108E+5812三星数码王TDX668E 1晶6芯IC:Hi2023EC+3102C+5812三星HSR-208C 1晶10芯IC:Hi2023E+Hi3102+MXT8211+A V2020+F25L08pA三星小霸王ABS-S 2009 2晶10芯IC:CX3001+CX1121+5812三星小霸王2900 (9针接口)IC:Hi2023E+A VL1108+MAX2119三星王国-KL6350 1晶11芯IC:HTV903+A VL1108EGa+EDA5812开门红KSP638 2晶10芯IC:HTV903F+A VL1108E+A V2020开门红KSP638 1晶10芯IC:CT216H+A VL1108EGa+A V2020日立创新TDX-668B 2晶6芯针脚定义①-RXD .②-TXD .③-GND .④VCC. ⑤-BLIC:Hi2023+A VL1108+5812志高之星HS166 2晶12芯IC:Hi3102+Hi2023+5812志高之星HS169 2晶12芯IC:Hi2023EC+Hi3012E+RDA5812A+EM638165TS-6G金牛ABS-1108 3晶10芯IC:Hi2023+1108+5812小灵通2晶6线IC:Hi2023+1108+5812福临门ABS-S 3晶9线IC:GX1121+GX3001+5812C60S-93AT 单晶10芯IC:CT216H+A VL1108EGa+A V2020 ABS-2301 单晶10芯针脚定义①-GND.②-TXD.③-RX .④VCCIC:Hi2023EC+Hi3211E+5812+25L8005其乐达CT216 2晶10芯IC:CT216+1108+A V2020科海6228 1晶11芯IC:HTV903+A VL1108EGa+RDa5812+25X16A VSIG科海6228-CT216H 1晶11芯IC:CT216H+1108EGa+M88TS2020科海C623S-91AT 单晶10芯IC:CT210H+A VL1108+2020 科海炫彩6888 IC:HTV903+A VL1108EGa+RDa5812科海2888(小天使)2晶10芯IC:HTV903+A VL1108EGa+RDa5812大旗920 3晶12芯IC:HTV903+A VL1108+A V2020大旗DQ920 3晶12芯IC:GX3001+GX1121+5812+25X16 大旗930 3晶12芯IC:HTV903+A VL1108+A V2020众昌电子ABS--2088 2晶10芯IC:Hi2023+A VL1108+5812众昌电子ABS-2087 2晶10芯IC:M3330+A VL1108+5812 创维S600 3晶IC:M3330E+A VL1108E+5812创维新一代3晶10芯IC:Hi2023E+1108+5037+FL016A 中广通XC-B188 3晶12芯IC:GX3001+GX1121+5812深圳知音ABSTAR KT-2309 3晶10芯IC:Hi2023+A VL1108E+5812知音科技ABSTAR KT1028H 2晶振10芯IC:Hi2023+A VL1108+GST GAIM-18R铁壳ABS-2009 2晶11芯IC:Hi2023+1108+夏普头王牌数码OST-366 2晶6芯针脚定义①-GND ②-RXD .③-TXD .④VCCIC:Hi3102+Hi2023EC+A V2020王牌数码王GM-ABS1108A 2晶10芯针脚定义①-GND .②-TXD .③-RXD .④VCCIC:GX3001+GX1121+5812+25L8005王牌数码王GM-ABS1108A 10芯IC:Hi2023+A VL1108+5812JIXIANG ABS-208 2晶14芯(9针接口)IC:Hi2023+1108+GST GAIM-18R ABS TUNER 夏普头JIXIANG-ABS208 2晶IC:D6121+1108+GST高频头East Star 2晶10芯IC:M3330-1108-GST GAIM-18R高频头小福星abs 2008 3晶12芯IC:GX3001+GX1211+5812通达C60S-93AT/C62S-91AT 1晶10芯IC:CT216H+A VL1108E+2020威特斯ZL-5188A 2晶13芯IC:HTV903+A VL1108+RDK5812威特斯ZL-5188B 2晶11芯IC:GX3001+GX1121+5812迷你星3晶13芯IC:GX3001+GX1121+5812+F16-100HIP高星HS-312 3晶12芯IC:GX3001+GX1121+5812北大高科3晶9芯IC:GX3001+GX1211+5812思达科ABS-S 801型2晶10芯IC:GX3001+GX1121+5810思达科ABS-S 802G 2晶10芯IC:GX3001+GX1211+5812思达科ABS-S 803A 1晶10芯IC:A VL1118+A V2020+25D80V思达科ABS-S 803G IC:GX3001+GX1211+5812思达科ABS-S 806H IC:GX3001+GX1211+5812思达科ABS-S 806H IC:A VL1118+A V2020+DSD4M16G思达科ABS-S 806H IC:HN4J7G+G2A954+5812+25X80思达科ABS-S807 1晶5芯IC:A VL1118a+A V2020+806H金霸王JBW-6688 2晶11芯IC:HTV903F+A VL1108EGa+A V2020+8211金霸王JBW-6688 IC:GX3001+GX1211+5812阿德尔ADE-168 IC:HY903+A VL1108EG+A V2020阿德尔ADE131金刚IC:HTV903F+A VL1108E+M88TS2020 海西小霸王TD299Z 2晶6芯IC:Hi2023E+Hi3122+5812 同洲CY-668S 1晶12芯IC:HM1512+1108+5812喜旺ABS5398 IC:Hi2023+1108E+MAX2119C喜旺ABS-5798 12芯IC:GX3001+GX1211+5812喜旺ABS-3809 2晶12芯IC:GX3001+GX1121+RDA5812希旺598 2晶12芯(9针接口) IC:Hi2023+1108+SHRP 高频头彩虹视霸CY84 1晶10芯IC:HTV903F+A VL1108+M88TS2020彩虹视霸A10S-9AAT 1晶10芯IC:A VL1118+SM42S16400B1-7+F80九洲村村通DVS-398F IC:CT216H+ALV1108+SHRP高频头金星ABS-208 1晶14芯IC:Hi2023+A VL1108+铁壳高频头威克2晶6芯(5针) IC:HTV903+1108+5812华尔HR731A1 3晶12芯IC:CX3001+CX1121+SHARP高频头爱普斯3晶9芯IC:HTV903+A V2020+A VL1108EG爱普斯2568 3晶10芯IC:HTV903+A V2020+A VL1108EG 爱普斯IC:GX3001+GX1211+A V2020+2J10X未来视佳ADEI88 3晶9芯IC:HTV903F+A V2020+A VL1108EG黑金刚TRT006 1晶10芯IC:A VL1118+A V2020+4558+F80-100DX-668 2晶10芯针脚定义①-RXD .②-TXD .③VCC .④-GND .⑤-BLIC:Hi2023EC_Hi3102E+5812+F80-100傲天海-吉祥2晶12芯针脚定义①-GND ②-RXD ③-TXD ④VCCIC:GX3001+GX1121+RDA5812高频头+P8075火星漫步LJ6008 1晶10芯IC:HTV903F+A VL1108+M88TS2020+F80-100王牌新一代TD-299Z针脚定义①- . ②-TXD .③-RXD .④-GND ⑤-IC:Hi2023E+Hi3122+5812王牌HJ360 3晶10芯IC:GX1120+GX3001+TS2020TVWALKER ABS-2008 1晶6芯IC:D61216GJ+1108E+SHARP头吉祥988 (ZJ-111) 1晶11芯IC:HTV903 +1108+高频头北京北电科林3晶12芯IC:Hi2023+A VL1108EGa+SHARP高频头家家福BEX811 1晶10芯IC:24645K2+M88VS2000+M88TS2020家家福ADE158 IC:HTV903+A VL1108+M88TS2020华星科技2晶IC:Hi2023+A VL1108+5812亚视达ABR-S(H11) 2晶10芯IC:HTV903+1108E+A V2020HSTAR 3晶10芯IC:Hi2023+A VL1108EGa+M88IS2020长江电讯ABS-2008型铁壳(9针接口)IC:D61216GJ+A VL1108EG+夏普头全家福3晶IC:Hi2023E+A VL1108EG+M88TS2020 畅想BEX818 1晶10芯IC:HTV903+A VL1108+A V2020 必佳GF-901 2晶10芯针脚定义①-GND .②-RXD .③-TXD .④VCCIC:HTV903+1108+A V2020KSP600G 飓风(华亚) 2晶10芯针脚定义①-GND ②-TXD ③-RXD ④VCCIC:HTV903+1108+M88TS2020+25D80万家乐TB002 (5针)IC:Hi2023EC+Hi3102E+M88TS2020+25X80A V万家乐2晶6芯IC:M3330+ALi1108+5812+F80-75奥伟科技ABS-800 3晶(9针接口)IC:GX3001+GX1121+5812奥伟科技ABS-900E 2晶12芯IC:CT216+A VL1108+独立高频头GAIR-08R天眼HSTER3晶10芯IC:Hi2023E+A VL1108+5812飞翔ADE351 2晶10芯IC:HTV903F+A VL1108EG+M88TS2000星视通XC-B268 1晶10芯IC:HTV903+A VL1108+5812星视通XC-C268 1晶11芯IC:HTV903 A VL1108 5812奥维科技ABS-600 3晶12芯IC:GX3001+GX1121+A V2020 超的个人论坛转载分享本资源。

P28F010-90资料

元器件交易网

28F010/28F020

E

CONTENTS

PAGE PAGE 4.5 DC Characteristics—28F020—TTL/NMOS Compatible—Commercial Products .......... 22 4.6 DC Characteristics—28F010—CMOS Compatible—Commercial Products .......... 24 4.7 DC Characteristics—28F020—CMOS Compatible—Commercial Products .......... 25 4.8 DC Characteristics—28F010—TTL/NMO Compatible—Extended Temperature Products ................................................... 27 4.9 DC Characteristics—28F020—TTL/NMO Compatible—Extended Temperature Products ................................................... 29 4.10 DC Characteristics—28F010—CMOS Compatible—Extended Temperature Products ................................................... 31 4.11 DC Characteristics—28F020—CMOS Compatible—Extended Temperature Products ................................................... 32 4.12 AC Characteristics—28F010—Read-Only Operation—Commercial and Extended Temperature Products .............................. 35 4.13 AC Characteristics—28F020—Read Only Operations—Commercial and Extended Temperature Products .............................. 36 4.14 AC Characteristics—28F010— Write/Erase/Program Only Operation— Commercial and Extended Temperature Products ................................................... 38 4.15 AC Characteristics—28F020— Write/Erase/Program Only Operation— Commercial and Extended Temperature Products ................................................... 39 4.16 AC Characteristics—28F010—Alternative CE#-Controlled Write—Commercial and Extended Temperature ............................. 44 4.17 AC Characteristics—28F020—Alternate CE# Controlled Writes—Commercial and Extended Temperature Products .............. 45 4.18 Erase and Programming Performance ..... 46 5.0 ORDERING INFORMATION ......................... 47 6.0 ADDITIONAL INFORMATION....................... 47

CMX589A_datasheet(v4)

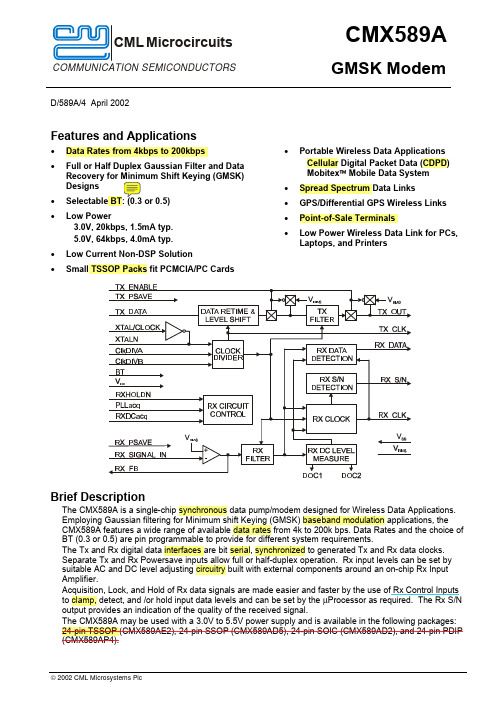

CML MicrocircuitsCOMMUNICATION SEMICONDUCTORSCMX589AGMSK ModemD/589A/4 April 2002Features and Applications• Data Rates from 4kbps to 200kbps•Full or Half Duplex Gaussian Filter and Data Recovery for Minimum Shift Keying (GMSK) Designs• Selectable BT: (0.3 or 0.5) •Low Power3.0V, 20kbps, 1.5mA typ. 5.0V, 64kbps,4.0mA typ. • Low Current Non-DSP Solution•Small TSSOP Packs fit PCMCIA/PC Cards•Portable Wireless Data Applications Cellular Digital Packet Data (CDPD) Mobitex ™ Mobile Data System • Spread Spectrum Data Links • GPS/Differential GPS Wireless Links • Point-of-Sale Terminals•Low Power Wireless Data Link for PCs,Laptops, and PrintersContentsSection Page Features and Applications (1)Brief Description (1)Block Diagram (3)2 Signal List (4)3 External Components (6)4 General Description (8)4.1 Clock Oscillator Divider (8)4.2 Receive (8)4.2.1 Rx Signal Path Description (8)4.2.2 Rx Circuit Control Modes (9)4.2.3 Rx Clock Extraction (10)4.2.4 Rx Data Extraction (10)4.2.6 Rx Signal Quality (12)4.3 Transmit (12)4.3.1 Tx Signal Path Description (12)4.4 Data Formats (14)4.5 Acquisition and Hold Modes (14)5 Application (15)5.1 Radio Channel Requirements (15)5.1.1 Bit Rate, BT, and Bandwidth (15)5.1.2 FM Modulator, Demodulator and IF (15)5.1.3 Two-Point Modulation (16)5.2 AC Coupling of Tx and Rx Signals (17)6 Performance Specifications (18)6.1 Electrical Specifications (18)6.1.1 Absolute Maximum Limits (18)6.1.2 Operating Limits (19)6.1.3 Operating Characteristics (20)6.2 Packages (22)Block DiagramFigure 1: Block Diagram2 Signal ListTable 1: Signal List3 External ComponentsFigure 3: Recommended External ComponentsComponent Notes Value Tolerance Component Notes Value Tolerance R1 1 ±5% C4 0.1µF ±20%R2 1.0MΩ±10% C5 1.0µF ±20%R3 2 ±10% C6 5 ±20%R4 3 ±10% C7 6C1 1 ±10% C8 6C2 4 C9 7C3 4 X1 8Table 2: Recommended External ComponentsRecommended External Component Notes:1. The RC network formed by R1 and C1 is required between the Tx Out pin and the input to the modulator.This network, which can form part of any DC level shifting and gain adjustment circuitry, forms animportant part of the transmit signal filtering. The ground connection to the capacitor C1 should bepositioned to give maximum attenuation of high-frequency noise into the modulator.The component values should be chosen so that the product of the resistance and the capacitance is:For a BT of 0.3 R1.C1 = 0.34/bit rate (bps)For a BT of 0.5 R1.C1 = 0.22/bit rate (bps)Data Rates (kbps)BT = 0.3 BT = 0.5 R1 C1 R1 C1 4 120k Ω 680pF 120k Ω 470pF 4.8 100k Ω 680pF 100k Ω 470pF 8 91k Ω 470pF 120k Ω 220pF 9.6 91k Ω 390pF 47k Ω 470pF 16 47k Ω 470pF 91k Ω 150pF 19.2 100k Ω 180pF 91k Ω 120pF 32 47k Ω 220pF 47k Ω 150pF 38.4 * 47k Ω 180pF 47k Ω 120pF 64 * 56k Ω 100pF 51k Ω 68pF 80 * 39k Ω 68pF 128 * 82k Ω 22pF 144 * 68k Ω 22pF 160 * 62k Ω 22pF 176 * 56k Ω 22pF 192 *51k Ω22pF* V DD ≥ 4.5V, external clockTable 3: Data Rate vs. BT and Selected External Component Values2. R3, R4 and C6 form the gain components for the Rx Input signal. R3 should be chosen as required by thesignal input level. 3. For bit rate ≤ 64kbps, R4 = 100k Ω. For bit rate > 64kbps, R4 = 10k Ω.4. The values chosen for C2 and C3 (including stray capacitance), should be suitable for the applied V DDand the frequency of X1.As a guide: C2 = C3 = 33pF at 1.0MHz falling to 18pF at the maximum frequency.At 3.0V, C2 = C3 = 33pF falling to 18pF at 5.0MHz the equivalent series resistance of X1 should be less than 2.0K Ω falling to 150Ω at the maximum frequency. Stray capacitance on the Xtal/Clock circuit pins must be minimized. 5. For bit rate ≤ 64kbps, C6 = 22pF. For bit rate > 64kbps, C6 =Ω×π××10k 2 rate bit 31e.g. for 128kbps, C6 = 41.1pF.6. C7 and C8 should both be .015µF for a data rate of 8kbps, and inversely proportional to the data rate forother data rates, e.g. 0.030µF at 4kbps, 1800pF at 64kbps, 680pF at 192kbps. 7. The tolerance of C9 is not very critical because it primarily serves as a dc blocking capacitor.8. The CMX589A can operate correctly with the Xtal frequencies between 1.0MHz and 16.0MHz(V DD = 5.0V) and 1.0MHz to 5.0MHz (V DD = 3.0V). External clock frequencies up to 25.6MHz(V DD ≥ 4.5V) are also supported (See Table 4 for examples.) For best results, a crystal oscillator design should drive the clock inverter input with signal levels of at least 40% of V DD , peak to peak. Tuning fork crystals generally cannot meet this requirement. To obtain crystal oscillator design assistance, consult your crystal manufacturer. Operation of this device without a Xtal or Clock input may cause device damage.4 General Description4.1 Clock Oscillator DividerThe Tx and (nominal) Rx data rates are determined by division of the frequency present at the XTALN pin as generated by the on-chip Xtal oscillator, with external components, or supplied from an external source. The division ratio is controlled by the logic level inputs on ClkDivA and ClkDivB pins as shown in Table 4, together with an indication of how various standard data rates may be derived from common µP Xtal frequencies.A/B)(ClkDiv Ratio Division FrequencyXtal/ClkRate Data =* V DD ≥ 4.5V, external clockTable 4: Example Clock/Data RatesNote : The device operation is not guaranteed above 200kbps or below 4kbps at the relevant supply voltage.Figure 4: Minimum µController System Connections4.2 Receive4.2.1Rx Signal Path DescriptionThe function of the Rx circuitry is to: 1. Set the incoming signal to a usable level. 2. Clean the signal by filtering.3. Provide dc level thresholds for clock and data extraction.4. Provide clock timing information for data extraction and external circuits.5. Provide Rx data in a binary form.6. Assess signal quality and provide Signal-to-Noise information.The output of the radio receiver's Frequency Discriminator should be fed to the CMX589A's Rx Filter by a suitable gain and DC level adjusting circuit. This circuit can be built with external components around the on-chip Rx Input Amplifier. The gain should be set so that the signal level at the Rx Feedback pin is nominally 1V peak to peak (for V DD =5.0V) centered around V BIAS when receiving a continuous 1111000011110000.. data pattern.Positive going signal excursions at Rx Feedback pin will produce a logic ‘0’ at the Rx Data Output. Negative going excursions will produce a logic ‘1’.The received signal is fed through the lowpass Rx Filter, which has a -3dB corner frequency of 0.56 times the data bit-rate, before being applied to the Level Measure and Clock and Data extraction blocks.The Level Measuring block consists of two voltage detectors, one of which measures the amplitude of the positive parts of the received signal. The other measures the amplitude of the negative portions. (Positive levels are then used to establish the optimum DC level decision-thresholds for the Clock and Data extraction, depending upon the Rx signal amplitude and any DC offset. 4.2.2Rx Circuit Control ModesThe operating characteristics of the Rx Level Measurement and Clock Extraction circuits are controlled, as shown in Table 6, by logic level inputs applied to the PLLacq, Rx HOLDN and RxDCacq pins to suit a particular application, or to cope with changing reception conditions, reference Figure 5.In general, a data transmission will begin with a preamble, for example, 1100110011001100, to allow the receive modem to establish timing and level-lock as quickly as possible. After the Rx carrier has been detected, and during the time that the preamble is expected, the RxDCacq and PLLacq Inputs should be switched from a logic ‘0’ to a logic ‘1’ so that the Level Measuring and Clock Extraction modes are operated and sequenced as shown.The Rx HOLDN input should normally be held at a logic ‘1’ while data is being received, but may be driven to a logic ‘0’ to freeze the Level Measuring Clock Extraction circuits during a fade. If a fade lasts for less than 200 bit periods, normal operation can be resumed by returning the Rx HOLDN input to a logic ‘1’ at the end of the fade. For longer fades, it may be better to reset the Level Measuring circuits by placing the RxDCacq to a logic ‘1’ for 10 to 20 bit periods.Rx HOLDN has no effect on the Level Measuring circuits while RxDCacq is at a logic ‘1’, and has no effect on the PLL while PLLacq is at a logic ‘1’.A logic ‘0’ on Rx HOLDN does not disable the Rx Clock output, and the Rx Data Extraction and S/N Detector circuits will continue to operate.Figure 5: Rx Mode Control DiagramPLLacq RxHOLDNPLL Action1 1 Acquire Sets the PLL bandwidth wide enough to allow a lock to thereceived signal in less than 8 zero crossings. This mode willoperate as long as PLLacq is a logic “1”.1 to 0 1 MediumBandwidth The correction applied to the extracted clock is limited to a maximum of ±1/16th bit-period for every two received zero-crossings. The PLL operates in this mode for a period of about 30 bits immediately following a 1 to 0 transition of the PLLacq input, provided that the Rx HOLDN input is a logic ‘1’.0 1 NarrowBandwidth The correction applied to the extracted clock is limited to a maximum of ±1/64th bit-period for every two received zero-crossings. The PLL operates in this mode whenever the Rx HOLDN Input is a logic ‘1’ and PLLacq has been a logic ‘0’ for at least 30 bit periods (after Medium Bandwidth operation for instance).0 0 Hold The PLL feedback loop is broken, allowing the Rx Clock tofreewheel during signal fade periods.Table 5: PLL Action Measurement Operational ModesRxDCacq RxHOLDNRx Level Measure Action0 to 1 X Clamp Operates for one bit-time after a 0 to 1 transition of theRXDCacq input. The external capacitors are rapidly chargedtowards a voltage mid-way between the received signal inputlevel and V BIAS, with the charge time-constant being of theorder of 0.5 bit-time.1 X Fast Peak Detect The voltage detectors act as peak-detectors, one capacitor isused to capture the positive-going signal peaks of the RxFilter output signal and the other capturing the negative-going peaks. The detectors operate in this mode wheneverthe RXDCacq input is at a logic ‘1’, except for the initial 1-bitClamp-mode time.0 1 Averaging PeakDetect Provides a slower but more accurate measurement of the signal peak amplitudes.0 0 Hold The capacitor charging circuits are disabled so that theoutputs of the voltage detectors remain substantially at thelast readings (discharging very slowly [time-constant approx.2,000 bits] towards V BIAS).X = Do not careTable 6: Rx Level Measurement Operational Modes4.2.3 Rx Clock ExtractionSynchronized by a PLL circuit to zero-crossings of the incoming data, the Rx Clock Extraction circuitry controls the Rx Clock output. The Rx Clock is also used internally by the Data Extraction circuitry. The PLL parameters can be varied by the Rx Circuit Control inputs PLLacq and Rx HOLDN to operate in one of four PLL modes as described in Table 5 and Table 6.4.2.4 Rx Data ExtractionThe Rx Data Extraction circuit decides whether each received bit is a 1 or 0 by sampling the received signal, after filtering, and comparing the sample values to an adaptive threshold derived from the Level Measuring circuit. This threshold is adapted from bit to bit to compensate for intersymbol interference caused by the and limiting of the overall transmission path and the Gaussian premodulation filter. Extracted data is output from the Rx Data pin, and should be sampled externally on the rising edge of the Rx CLK.4.2.5 Rx S/N DetectionThe Rx S/N Detector system classifies the incoming zero-crossings as GOOD or BAD depending upon the time when each crossing actually occurs with respect to its expected time as determined by the Clock Extraction PLL. This information is then processed to provide a logic level output at the Rx S/N pin. A high level indicates a series of GOOD crossings; a low level indicates a BAD crossing.By averaging this output, it is possible to derive a measure of the Signal-to-Noise-Ratio and hence theBit-Error-Rate of the received signal.Figure 6: Typical Bit-Error-Rate Performance at V DD = 5.0VNote: Figure 6 indicates typical performance, independent of bit rate (although the applied noise bandwidth is considered to match the bit rate used), radio performance (e.g. IF filter distortion), supply voltage (higher bit rates require V DD≥ 4.5V), and other ‘real world’ factors.4.2.6 Rx Signal QualityThe effect of input Rx Signal quality on the Rx S/N output is shown in Figure 7.When power is subsequently restored to the Tx filter, its output will take several bit-times to settle. The Tx Enable input can be used to prevent these abnormal voltages from appearing at the Tx Out pin.Figure 9: Tx Filter ResponseFigure 11: Tx Output Spectrum (Random Data)4.4 Data FormatsThe receive section of the CMX589A works best with data which has a reasonably random structure --the data should contain approximately the same number of ‘ones’ as ‘zeroes’ with no long sequences (>100 bits) of consecutive ones or zeroes. Also, long sequences (>100 bits) of 10101010 ... patterns should be avoided. For this reason, it is recommended that data be made random in some manner before transmission, forexample by exclusive-ORing it with the output of a binary pseudo-random pattern generator.Where data is transmitted in bursts, each burst should be preceded by a preamble designed to allow the receive modem to establish timing and level lock as quickly as possible. This preamble for BT=0.3 should be at least 16 bits long, and should preferably consist of alternating pairs of ones and zeros i.e. 110011001100....; the eye of pattern 10101010 .... has the most gradual slope and will yield poor peak levels for the Rx circuits. For BT=0.5 the eye pattern of 10101010... has reduced intersymbol interference and may be used as the preamble (DC Acq pin should be held high during preamble). See Figure 5.4.5 Acquisition and Hold ModesThe RXDCacq and PLLacq inputs must be pulsed High for about 16 bits at the start of reception to ensure that the DC measurement and timing extraction circuits lock-on to the received signal correctly. Once lock has been achieved, the above inputs should be taken Low again.In most applications, there will be a DC step in the output voltage from the receiver FM discriminator due to carrier frequency offsets as channels are changed or when the remote transmitter is turned on.The CMX589A can tolerate DC offsets in the received signal of at least ±10% of V DD with respect to V BIAS, (measured at the Rx Feedback pin). However, to ensure that the DC offset compensation circuit operates correctly and with minimum delay, the Low to High transition of the RXDCacq and PLLacq inputs should occur after the mean input voltage to the CMX589A has settled to within about 0.1V of its final value.Note: This can place restrictions on the value of any series signal coupling capacitor.As well as using the Rx Hold input to freeze the Level Measuring and Clock Extraction circuits during a signal fade, it may also be used in systems which use a continuously transmitting control channel to freeze the Rx circuitry during transmission of a data packet, allowing reception to resume afterwards without losing bit synchronization. To achieve this, the CMX589A Xtal clock needs to be accurate enough that the derived RxClock output does not drift by more than about 0.1 bit time from the actual received data-rate during the time that the RxHold input is ‘Low’.However; the RXDCacq input may need to be pulsed High for 2 bit durations to re-establish the level measurements if the RxHold input is Low for more that a few hundred bit-times (exact number depends on system crystal tolerances).The voltages on the Doc1 and Doc2 pins reflect the average peak positive and negative excursions of the (filtered) receive signal, and could therefore be used to derive a measure of the data signal amplitude. Note: These pins are driven from very high-impedance circuits, so that the DC load presented by any external circuitry should exceed 10MΩ to V BIAS.5 Application5.1 Radio Channel RequirementsTo achieve legal adjacent channel performance at high bit-rates, a radio with an accurate carrier frequency and an accurate modulation index is required. For optimum channel utilization, (e.g. low BER and high data-rates) attention must be paid to the phase and frequency response of both the IF and baseband circuitry.5.1.1 Bit Rate, BT, and BandwidthThe maximum data rate that can be transmitted over a radio channel depends on the following: Channel spacingAllowable adjacent channel interferenceTx filter bandwidthPeak carrier deviation (Modulation Index)Tx and Rx carrier frequency accuraciesModulator and Demodulator linearityRx IF filter frequency and phase characteristicsUse of error correction techniquesAcceptable error-rateAs a guide to MOBITEX operation, a raw data-rate of 8kbps at 12.5kHz channel spacing may be achievable -depending on local regulatory requirements- using a ±2kHz maximum deviation, a BT of 0.3, and no more than 1.5kHz discrepancy between Tx and Rx carrier frequencies. Forward error correction (FEC) could then be used with interleaving to reduce the effect of burst errors.Reducing the data-rate to 4.8kbps would allow the BT to be increased to 0.5, improving the error-rate performance.5.1.2 FM Modulator, Demodulator and IFFor optimum performance, the eye pattern of the received signal (when receiving random data) applied to the CMX589A should be as close as possible to the Transmit eye pattern examples shown in Figure 10.Of particular importance are general symmetry, cleanliness of the zero-crossings, and for a BT of 0.3, the relative amplitude of the inner eye opening.To achieve this, attention must be paid to:Linearity and frequency/phase response of the Tx frequency modulator. Unless the transmit data is especially encoded to remove low frequency components, the modulator frequency response should extend down to a few hertz. This is because two-point modulation is necessary for synthesizedradios.Bandwidth and phase response of the Rx IF filters.Accuracy of the Tx and Rx carrier frequencies -any difference will shift the received signal towardsone of the skirts of the IF filter response.Ideally, the Rx demodulator should be DC coupled to the CMX589A Rx Signal In pin (with a DC bias added to center the signal at the Rx Feedback pin at V DD/2 [V BIAS]). However, AC coupling can be used provided that:The 3dB cut-off frequency is 20Hz or below (i.e. a 0.1µF capacitor in series with 100kΩ).The data does not contain long sequences of consecutive ones or zeroes.Sufficient time is allowed after a step change at the discriminator output (resulting from channelchanging or the appearance of a RF carrier) for the voltage into the CMX589A to settle before theRXDCacq line is strobed.5.1.3 Two-Point ModulationWhen designing the CMX589A into a radio that uses a frequency synthesizer, a two-point modulation technique is recommended. This is both to prevent the radio's PLL circuitry from counteracting the modulation process, and to provide a clean flat modulation response down to DC.Figure 12 shows a suggested basic configuration to provide a two-point modulation drive from the CMX589A Tx Output using the FX019 or MX019 Digitally Controlled Quad Amplifier Array. The FX019/MX019 elements provide individual set-up, calibration and dynamic control of modulation levels. Level setting control of the amplifiers/attenuators of the FX019/MX019 is via an 8-bit data word. Note that the FX019/MX019 frequency response only supports data rates as high as 8kbps.With reference to Figure 12:The buffer amplifier is required to prevent loading of the CMX589A external RC circuit.Stage B, with R1/R2, provides suitable signal and DC levels for the VCO varactor; C1 is RFdecoupling. The drive level should be adjusted (digitally) to provide the desired deviation.Stage C, with R3/R4, provides the Reference Oscillator drive (application dependent). Thisparameter is set by adjusting for minimum AC signal on the PLL control voltage with a low-frequency modulating signal (inside the PLL bandwidth) applied.Stage D could be used with the components shown if a negative reference drive is required.Stage A provides buffering and overall level control.Figure 12: An Example of Two-Point Modulation Drive with Individual Adjustment Using theFX019/MX0195.2 AC Coupling of Tx and Rx SignalsIn practical applications, it is possible to arrange AC coupling between the CMX589A Tx Output and the frequency modulator to cut-off at a very low frequency, such as 5.0Hz. AC coupling between the receive discriminator and the input of the CMX589A may need a shorter time-constant to avoid problems from voltage steps at the output of the discriminator when changing channels or when the distant transmitter turns on.For these reasons, as well as to maintain reasonable BER, the optimum –3dB cut-off frequencies are around 5.0Hz in the Tx path and 20.0Hz in the Rx path.Figure 13 shows the typical static Bit-Error-Rate performance of the CMX589A operating under nominal conditions for various degrees of AC coupling at the Rx input and the Tx output.Data Rate = 8kbps V DD = 5.0V T AMB = 25°C Tx BT = 0.36 Performance Specifications6.1 Electrical Specifications6.1.1 Absolute Maximum LimitsExceeding these maximum ratings can result in damage to the device.General Notes Min. Typ. Max. Units Supply (V DD-V SS) -0.3 7.0 VVoltage on any pin to V SS-0.3 V DD + 0.3 VCurrentV DD-30 30 mAV SS-30 30 mAAny other pin -20 20 mA D2 / P4 PackagesTotal allowable Power dissipation800 mW at T AMB = 25°CDerating above 25°C 13 mW/°C Operating Temperature -40 85 °C Storage Temperature -55 125 °C D5 Package550 mW Total allowable Power dissipationat T AMB = 25°CDerating above 25°C 9 mW/°C Operating Temperature -40 85 °C Storage Temperature -55 125 °C E2 PackageTotal allowable Power dissipationat T AMB = 25°C 320 mWDerating above 25°C 5.3 mW/°C Operating Temperature -40 85 °C Storage Temperature -55 125 °CTable 7: Absolute Maximum Ratings6.1.2 Operating LimitsCorrect Operation of the device outside these limits is not implied.Notes Min. Typ. Max. Units Supply (V DD-V SS) 3.0 3.3/5.0 5.5 VOperating Temperature -40 85 °CRx and Tx Data RateV DD≥ 3.0V 4 32 kbpsV DD≥ 4.5V 4 200 kbpsXtal FrequencyV DD≥ 3.0V 1.0 5.0 MHzV DD≥ 4.5V 1.0 16.0 MHzExternal Clock FrequencyV DD≥ 3.0V 1 1.0 5.0 MHzV DD≥ 4.5V 1 1.0 25.6 MHzHigh Pulse Width 1 15 nsLow Pulse Width 1 15 nsTable 8: Operating LimitsOperating Limits Notes1. Timing for an external clock input to the Xtal/Clock pin.6.1.3 Operating CharacteristicsFor the following conditions unless otherwise specified.V DD = 5.0V @ T AMB = 25°CXtal/Clock Frequency = 4.096MHz, Data Rate = 8kbps, Noise Bandwidth = Bit RateStatic Values Notes Min. Typ. Max. Units Supply Current Tx PS Rx PS 1I DD (V DD = 3.0V)1 1 - 0.5 - mA0 1 - 1.0 - mA1 0 - 1.0 - mA0 0 - 1.5 - mAI DD (V DD = 5.0V)1 1 - 1.0 - mA0 1 - 2.0 - mA1 0 - 3.0 - mA0 0 - 4.0 - mAInput Logic LevelLogic 1 Input Level 3.5 - - VLogic 0 Input Level - - 1.5 VLogic Input Current 2 -5.0 - 5.0 µA Output Logic LevelLogic 1 Output Level (I OH = 120µA) 4.6 - - VLogic 0 Output Level (I OL = -120µA) - - 0.4 V Transmit Parameters -Tx OUT pin DC bias shift caused by change from-85.0 - 85.0 mV Tx Enable = 0 to Tx Enable = 1 whileTx PSAVE = 0 at 25°CTx OUT, Output Impedance 3 - 1.0 - kΩTx Out, Level 4, 10 0.8 1.0 1.2 V P-P Output DC Offset 12 -0.125 - 0.125 V Tx Data DelayBT = 0.3 5 - 2.0 2.5 bit-periods BT = 0.5 5 - 1.5 2.0 bit-periods Tx PS to Output-Stable time 6 - 4.0 - bit-periods Receive ParametersRx AmplifierInput Impedance 1.0 - - MΩOutput Impedance 7 - 10.0 - KΩVoltage Gain - 50.0 - dB Rx Filter Signal Input Level 8, 10 0.7 1.0 1.3 V P-P Rx Time Delay 9 - - 3.0 bit-periodsStatic Values Notes Min. Typ. Max. Units On-Chip Xtal OscillatorR IN10.0 - - MΩR OUT11 - 50.0 - kΩVoltage Gain 11 - 25.0 - dBTable 9: Operating CharacteristicsOperating Characteristics Notes:1. Not including current drawn from the CMX589A pins by external circuitry. See Absolute MaximumRatings.2. For V IN in the range V SS to V DD.3. For a load of 10KΩ or greater. Tx PS input at logic ‘0’; Tx Enable = ‘1’.4. Data pattern of 1111000011110000…5. Measured between the rising edge of Tx Clock and the centre of the corresponding bit at Tx Out.6. Time between the falling edge of the TXPSAVE and the Tx Out voltage stabilizing to normal outputlevels.7. For a load of 10kΩ or greater. RXPSAVE input at logic ‘0’.8. For optimum performance, Measured at the Rx Feedback pin for an 1111000011110000… pattern.9. Measured between the center of bit at Rx Signal In and corresponding rising edge of the Rx Clock.10. Levels are proportional to applied V DD11. Small signal measurement at 1.0kHz with no load on Xtal output.12. (Tx OUT enabled DC level) – (Tx Out disabled DC level) when transmitting a repeating 11110000 bitpattern.6.2 PackagesFigure 16: 24-pin SSOP Mechanical Outline: Order as part no. CMX589AD5Handling precautions: This product includes input protection, however, precautions should be taken to prevent device damage from electro-static discharge. CML does not assume any responsibility for the use of any circuitry described. No IPR or circuit patent licences are implied. CML reserves the right at any time without notice to change the said circuitry and this product specification. CML has a policy of testing every product shipped using calibrated test equipment to ensure compliance with this product specification. Specific testing of all circuit parameters is not necessarily performed.CML Microcircuits (UK )Ltd4800 Bethania Station Road -Winston-Salem - NC 27105 - USA. Tel: +1 336 744 5050, 800 638 5577 Fax: +1 336 744 5054Sales: us.sales@ Technical Support:us.techsupport@CML Microcircuits (Singapore)P teLtd。

YASKAWA MP900 2000系列 说明书

图标的说明为使读者了解说明内容的区分本书中设计了如下图标并在必要的地方使用这些图标以助读者理解表示需要熟记的重要事项同时也表示发生警报但还不至于造成装置损坏的注意事项表示具体程序举例操作实例表示补充事项或记住后会便于使用的功能表示对难于理解的用语进行解释以及对事先没有说明而后出现的用语进行说明Copyright 2004株式会社 安川电机未经本公司的书面许可禁止转载或复制本书的一部分或全部内容目录图标的说明- - - - - - - - - - - - - - - - - - - - - - - - - -iii本手册的简介- - - - - - - - - - - - - - - - - - - - - - - - viii本手册的资料构成- - - - - - - - - - - - - - - - - - - - - - viii相关手册- - - - - - - - - - - - - - - - - - - - - - - - - - - ix本手册的使用方法- - - - - - - - - - - - - - - - - - - - - - - xi关于软件- - - - - - - - - - - - - - - - - - - - - - - - - - - xi 1章 梯形图指令1.1 继电器电路指令 - - - - - - - - - - - - - - - - - - -1-41.1.1 A触点指令(NOC) - - - - - - - - - - - - - - - - - - - - - -1-41.1.2 B触点指令(NCC) - - - - - - - - - - - - - - - - - - - - - -1-51.1.3 接通延时定时器指令(TON[10ms]) - - - - - - - - - - - - - - -1-51.1.4 断开延时定时器指令(TOFF[10ms])- - - - - - - - - - - - - - -1-71.1.5 接通延时定时器指令(TON[1s]) - - - - - - - - - - - - - - - -1-81.1.6 断开延时定时器指令(TOFF[1s])- - - - - - - - - - - - - - - -1-91.1.7 上升脉冲指令(ON-PLS)- - - - - - - - - - - - - - - - - - - 1-101.1.8 下降脉冲指令(OFF-PLS) - - - - - - - - - - - - - - - - - - 1-121.1.9 线圈指令(COIL)- - - - - - - - - - - - - - - - - - - - - - 1-131.1.10 置位线圈指令(S-COIL)- - - - - - - - - - - - - - - - - - - 1-141.1.11 复位线圈指令(R-COIL)- - - - - - - - - - - - - - - - - - - 1-151.2 数值运算指令 - - - - - - - - - - - - - - - - - - - 1-161.2.1 存储指令(STORE) - - - - - - - - - - - - - - - - - - - - - 1-161.2.2 加法指令(ADD) - - - - - - - - - - - - - - - - - - - - - - 1-181.2.3 加法扩展指令(ADDX)- - - - - - - - - - - - - - - - - - - - 1-201.2.4 减法指令(SUB) - - - - - - - - - - - - - - - - - - - - - - 1-211.2.5 减法扩展指令(SUBX)- - - - - - - - - - - - - - - - - - - - 1-231.2.6 乘法指令(MUL) - - - - - - - - - - - - - - - - - - - - - - 1-241.2.7 除法指令(DIV) - - - - - - - - - - - - - - - - - - - - - - 1-271.2.8 整型余数指令(MOD) - - - - - - - - - - - - - - - - - - - - 1-291.2.9 实型余数指令(REM) - - - - - - - - - - - - - - - - - - - - 1-301.2.10 增量指令(INC) - - - - - - - - - - - - - - - - - - - - - - 1-311.2.11 减量指令(DEC) - - - - - - - - - - - - - - - - - - - - - - 1-321.2.12 时间加法指令(TMADD) - - - - - - - - - - - - - - - - - - - 1-331.2.13 时间减法指令(TMSUB) - - - - - - - - - - - - - - - - - - - 1-351.2.14 时间经过指令(SPEND) - - - - - - - - - - - - - - - - - - - 1-371.2.15 符号取反指令(INV) - - - - - - - - - - - - - - - - - - - - 1-391.2.16 1的补码指令(COM) - - - - - - - - - - - - - - - - - - - - 1-411.2.17 绝对值转换指令(ABS) - - - - - - - - - - - - - - - - - - - 1-421.2.18 2进制转换指令(BIN) - - - - - - - - - - - - - - - - - - - 1-441.2.19 BCD转换指令(BCD) - - - - - - - - - - - - - - - - - - - - 1-451.2.20 校验转换指令(PARITY)- - - - - - - - - - - - - - - - - - - 1-461.2.21 ASCII码转换1指令(ASCII) - - - - - - - - - - - - - - - - 1-471.2.22 ASCII码转换2指令(BINASC)- - - - - - - - - - - - - - - - 1-491.2.23 ASCII码转换3指令(ASCBIN)- - - - - - - - - - - - - - - - 1-501.3 逻辑运算/比较指令 - - - - - - - - - - - - - - - -1-511.3.1 逻辑与指令(AND)- - - - - - - - - - - - - - - - - - - - - -1-511.3.2 逻辑或指令(OR) - - - - - - - - - - - - - - - - - - - - - -1-521.3.3 逻辑异或指令(XOR)- - - - - - - - - - - - - - - - - - - - -1-531.3.4 比较指令()- - - - - - - - - - - - - - - - - - - - - - -1-541.3.5 比较指令(≦)- - - - - - - - - - - - - - - - - - - - - - -1-551.3.6 比较指令()- - - - - - - - - - - - - - - - - - - - - - -1-561.3.7 比较指令()- - - - - - - - - - - - - - - - - - - - - - -1-571.3.8 比较指令(≧)- - - - - - - - - - - - - - - - - - - - - - -1-581.3.9 比较指令()- - - - - - - - - - - - - - - - - - - - - - -1-591.3.10 范围检查指令(RCHK) - - - - - - - - - - - - - - - - - - - -1-60 1.4 程序控制指令 - - - - - - - - - - - - - - - - - - -1-631.4.1 图调用指令(SEE)- - - - - - - - - - - - - - - - - - - - - -1-631.4.2 运动程序调用指令(MSEE) - - - - - - - - - - - - - - - - - -1-641.4.3 函数调用指令(FUNC) - - - - - - - - - - - - - - - - - - - -1-651.4.4 连续执行型直接输入指令(INS)- - - - - - - - - - - - - - - -1-661.4.5 连续执行型直接输出指令(OUTS) - - - - - - - - - - - - - - -1-691.4.6 扩展程序执行指令(XCALL)- - - - - - - - - - - - - - - - - -1-711.4.7 WHILE指令(WHILE END_WHILE)- - - - - - - - - - - - - - - -1-721.4.8 IF指令(IF END_IF) - - - - - - - - - - - - - - - - - - - -1-741.4.9 IF指令(IF ELSE END_IF) - - - - - - - - - - - - - - - - -1-761.4.10 FOR指令(FOR END_FOR)- - - - - - - - - - - - - - - - - - -1-781.4.11 EXPRESSION指令(EXPRESSION) - - - - - - - - - - - - - - - -1-80 1.5 基本函数指令 - - - - - - - - - - - - - - - - - - -1-811.5.1 平方根指令(SQRT) - - - - - - - - - - - - - - - - - - - - -1-811.5.2 正弦指令(SIN)- - - - - - - - - - - - - - - - - - - - - - -1-831.5.3 余弦指令(COS)- - - - - - - - - - - - - - - - - - - - - - -1-851.5.4 正切指令(TAN)- - - - - - - - - - - - - - - - - - - - - - -1-871.5.5 反正弦指令(ASIN) - - - - - - - - - - - - - - - - - - - - -1-881.5.6 反余弦指令(ACOS) - - - - - - - - - - - - - - - - - - - - -1-891.5.7 反正切指令(ATAN) - - - - - - - - - - - - - - - - - - - - -1-901.5.8 指数指令(EXP)- - - - - - - - - - - - - - - - - - - - - - -1-921.5.9 自然对数指令(LN) - - - - - - - - - - - - - - - - - - - - -1-931.5.10 常用对数指令(LOG)- - - - - - - - - - - - - - - - - - - - -1-94 1.6 数据操作指令 - - - - - - - - - - - - - - - - - - -1-951.6.1 位循环左移指令(ROTL) - - - - - - - - - - - - - - - - - - -1-951.6.2 位循环右移指令(ROTR) - - - - - - - - - - - - - - - - - - -1-971.6.3 位传送指令(MOVB) - - - - - - - - - - - - - - - - - - - - -1-991.6.4 字传送指令(MOVW) - - - - - - - - - - - - - - - - - - - - 1-1011.6.5 替换传送指令(XCHG) - - - - - - - - - - - - - - - - - - - 1-1031.6.6 表初始化指令(SETW) - - - - - - - - - - - - - - - - - - - 1-1051.6.7 字节字展开指令(BEXTD)- - - - - - - - - - - - - - - - - 1-1071.6.8 字字节压缩指令(BPRESS) - - - - - - - - - - - - - - - - 1-1091.6.9 数据检索指令(BSRCH)- - - - - - - - - - - - - - - - - - - 1-1111.6.10 分类指令(SORT) - - - - - - - - - - - - - - - - - - - - - 1-1131.6.11 位左移指令(SHFTL)- - - - - - - - - - - - - - - - - - - - 1-1141.6.12 位右移指令(SHFTR)- - - - - - - - - - - - - - - - - - - - 1-1161.6.13 字复制指令(COPYW)- - - - - - - - - - - - - - - - - - - - 1-1171.6.14 字节交换指令(BSWAP)- - - - - - - - - - - - - - - - - - - 1-1191.7 DDC指令- - - - - - - - - - - - - - - - - - - - - -1-1211.7.1 死区A指令(DZA) - - - - - - - - - - - - - - - - - - - - -1-1211.7.2 死区B指令(DZB) - - - - - - - - - - - - - - - - - - - - -1-1231.7.3 上下限值指令(LIMIT) - - - - - - - - - - - - - - - - - - -1-1251.7.4 PI控制指令(PI) - - - - - - - - - - - - - - - - - - - - -1-1281.7.5 PD控制指令(PD) - - - - - - - - - - - - - - - - - - - - -1-1311.7.6 PID控制指令(PID) - - - - - - - - - - - - - - - - - - - -1-1341.7.7 一阶延迟指令(LAG) - - - - - - - - - - - - - - - - - - - -1-1381.7.8 相位超前滞后指令(LLAG)- - - - - - - - - - - - - - - - - -1-1411.7.9 函数发生器指令(FGN) - - - - - - - - - - - - - - - - - - -1-1441.7.10 反函数发生器指令(IFGN)- - - - - - - - - - - - - - - - - -1-1481.7.11 直线加减速器1指令(LAU) - - - - - - - - - - - - - - - - -1-1521.7.12 直线加减速器2指令(SLAU)- - - - - - - - - - - - - - - - -1-1561.7.13 脉宽调制指令(PWM) - - - - - - - - - - - - - - - - - - - -1-1631.8 表数据操作指令 - - - - - - - - - - - - - - - - - -1-1651.8.1 块调出指令(TBLBR) - - - - - - - - - - - - - - - - - - - -1-1651.8.2 块写入指令(TBLBW) - - - - - - - - - - - - - - - - - - - -1-1671.8.3 行检索指令纵向(TBLSRL)- - - - - - - - - - - - - - - - -1-1691.8.4 列检索指令横向(TBLSRC)- - - - - - - - - - - - - - - - -1-1711.8.5 块清除指令(TBLCL) - - - - - - - - - - - - - - - - - - - -1-1731.8.6 表间块传送指令(TBLMV) - - - - - - - - - - - - - - - - - -1-1751.8.7 Q表调出指令(QTBLR QTBLRI) - - - - - - - - - - - - - - -1-1771.8.8 Q表写入指令(QTBLW QTBLWI) - - - - - - - - - - - - - - -1-1791.8.9 Q指针清除指令(QTBLCL)- - - - - - - - - - - - - - - - - -1-181 2章 系统标准函数指令2.1 信息函数 - - - - - - - - - - - - - - - - - - - - - -2-22.1.1 信息发送函数(MSG-SND) - - - - - - - - - - - - - - - - - - -2-22.1.2 信息接收函数(MSG-RCV) - - - - - - - - - - - - - - - - - - 2-152.2 示踪函数 - - - - - - - - - - - - - - - - - - - - - 2-242.2.1 示踪函数(TRACE) - - - - - - - - - - - - - - - - - - - - - 2-242.2.2 数据示踪调出函数(DTRC-RD) - - - - - - - - - - - - - - - - 2-252.2.3 故障示踪调出函数(FTRC-RD) - - - - - - - - - - - - - - - - 2-282.2.4 变频器示踪调出函数(ITRC-RD) - - - - - - - - - - - - - - - 2-322.3 变频器函数 - - - - - - - - - - - - - - - - - - - - 2-352.3.1 变频器常数写入函数(ICNS-WR) - - - - - - - - - - - - - - - 2-352.3.2 变频器常数调出函数(ICNS-RD) - - - - - - - - - - - - - - - 2-402.4 其他的函数 - - - - - - - - - - - - - - - - - - - - 2-432.4.1 计数函数(COUNTER) - - - - - - - - - - - - - - - - - - - - 2-432.4.2 先进先出函数(FINFOUT) - - - - - - - - - - - - - - - - - - 2-45附录A EXPRESSIONA.1 数式 - - - - - - - - - - - - - - - - - - - - - - - A-2A.1.1 运算符- - - - - - - - - - - - - - - - - - - - - - - - - - - A-2A.1.2 运算对象- - - - - - - - - - - - - - - - - - - - - - - - - - A-4A.1.3 函数- - - - - - - - - - - - - - - - - - - - - - - - - - - - A-4A.2 可识别的表达式种类 - - - - - - - - - - - - - - - - A-5A.2.1 算术运算符- - - - - - - - - - - - - - - - - - - - - - - - - A-5A.2.2 比较运算符- - - - - - - - - - - - - - - - - - - - - - - - - A-5A.2.3 逻辑运算符- - - - - - - - - - - - - - - - - - - - - - - - - A-5A.2.4 赋值运算符- - - - - - - - - - - - - - - - - - - - - - - - - A-6A.2.5 函数- - - - - - - - - - - - - - - - - - - - - - - - - - - - A-6A.2.6 其他- - - - - - - - - - - - - - - - - - - - - - - - - - - - A-6A.3 在梯形图程序中的应用 - - - - - - - - - - - - - - - A-7A.3.1 IF指令句的条件表达式 - - - - - - - - - - - - - - - - - - - A-7A.3.2 WHILE指令句的条件表达式- - - - - - - - - - - - - - - - - - A-7A.3.3 EXPRESSION指令句的运算表达式 - - - - - - - - - - - - - - - A-7本手册的简介本手册详细地说明了支持MP900/MP2000系列(以下称MP系列)的设计与维护的新梯形图编辑器软件的操作方法本手册以充分理解Microsoft Windows 95/98/2000/NT的操作方法的人员为对象关于Windows的打开关闭及鼠标操作Windows应用程序的一般操作等请参阅计算机所附的说明书为了能正确使用新梯形图编辑器请仔细阅读本手册请妥善保管本手册以便需要时参阅本手册的资料构成MP900系列有MP910MP920MP930MP940四种MP2000系列有MP2100和MP2300两种资料构成根据上述产品构成修订相关手册在下一页有介绍敬请参阅相关手册机器控制器MP900/MP2000系列的相关手册包括下表所示的内容请根据需要进行阅读用户手册名资料编号适用机型MP910MP920MP930MP940MP2100MP2300机器控制器MP930用户手册设计与维护篇SI-C887-1.1{机器控制器MP900/MP2000系列用户手册梯形图程序篇SI-C887-1.2{{{{{{机器控制器MP900/MP2000系列用户手册运动程序篇SIZ-C887-1.3{{{{{{机器控制器MP900系列用户手册示教操作器篇SI-C887-1.6{{机器控制器MP920用户手册设计与维护篇SIZ-C887-2.1{机器控制器MP900系列编程装置用软件MPE720用户手册操作说明简易版SIZ-C887-2.3{{{{机器控制器MP920用户手册运动模块篇SIZ-C887-2.5{机器控制器MP920用户手册通讯模块篇SIZ-C887-2.6{机器控制器MP920设置手册EMC 指令用SIBZ-C887-2.50{机器控制器MP910用户手册设计与维护篇SIZ-C887-3.1{机器控制器MP940用户手册设计与维护篇SIZ-C887-4.1{机器控制器MP940设置手册EMC 指令用SIBZ-C887-4.50{机器控制器MP900系列用户手册MECHATROLINK 篇SIZ-C887-5.1{{{{机器控制器MP900系列用户手册260I/F DeviceNet 篇SIZ-C887-5.2{{机器控制器MP900系列MPPanel用户手册SIZ-C887-10.1{{{机器控制器MP900系列MPLogger用户手册SIZ-C887-11.1{{{机器控制器MP900系列MPLoader (Server)用户手册SIZ-C887-12.1{{{机器控制器MP900系列MPLoader (Client)用户手册SIZ-C887-12.2{{{机器控制器MP900/MP2000系列用户手册新梯形图编辑器程序指令篇SIZ-C887-13.1{{{{{{机器控制器MP900/MP2000系列用户手册新梯形图编辑器操作篇SIZ-C887-13.2{{{{{{机器控制器MP2300用户手册基本模块篇SIJPC88070003A{机器控制器MP2300用户手册通讯模块篇SIJPC88070004A{机器控制器MP900/MP2000系列编程装置用用户手册标准版SIJPC88070005A{{{{{{机器控制器MP2100用户手册设计与维护篇SIJPC88070001A{用户手册名资料编号适用机型MP910MP920MP930MP940MP2100MP2300xi本手册的使用方法本手册的使用对象本手册以下列人员为对象进行MP900/MP2000系列系统设计的人员进行MP900/MP2000系列运动程序编程的人员进行MP900/MP2000系列梯形图程序编程的人员缩略语及缩写符号本手册使用如下所示的缩略语及缩写符号PLC机器控制器的总称MPE720编程装置用软件的总称关于软件使用注意事项本软件请在1台特定的电脑上使用需要在其他电脑上使用时请另行购买严禁复制本软件并将其用于编程装置用之外的用途请妥善保管本软件的软盘严禁对本软件进行反编译反汇编未经本公司许可严禁将本软件的一部分或全部转让交换转借给第三者使用注册商标Windows Windows95/98/2000/NT 是美国Microsoft公司的注册商标Pentium 是美国Intel公司的注册商标以太网(Ethernet)是美国Xerox公司的注册商标1-111章梯形图指令本章对继电器电路指令数值运算指令逻辑运算/比较指令程序控制指令基本函数指令数据操作指令DDC 指令以及表数据操作指令进行了说明1章 梯形图指令1.1 继电器电路指令- - - - - - - - - - - - - - - - - - - 1-41.1.1 A 触点指令(NOC) - - - - - - - - - - - - - - - - - - - - - -1-41.1.2 B 触点指令(NCC) - - - - - - - - - - - - - - - - - - - - - -1-51.1.3 接通延时定时器指令(TON[10ms]) - - - - - - - - - - - - - - -1-51.1.4 断开延时定时器指令(TOFF[10ms])- - - - - - - - - - - - - - -1-71.1.5 接通延时定时器指令(TON[1s]) - - - - - - - - - - - - - - - -1-81.1.6 断开延时定时器指令(TOFF[1s])- - - - - - - - - - - - - - - -1-91.1.7 上升脉冲指令(ON-PLS)- - - - - - - - - - - - - - - - - - - 1-101.1.8 下降脉冲指令(OFF-PLS) - - - - - - - - - - - - - - - - - - 1-121.1.9 线圈指令(COIL)- - - - - - - - - - - - - - - - - - - - - - 1-131.1.10 置位线圈指令(S-COIL)- - - - - - - - - - - - - - - - - - - 1-141.1.11 复位线圈指令(R-COIL)- - - - - - - - - - - - - - - - - - - 1-151.2 数值运算指令- - - - - - - - - - - - - - - - - - - -1-161.2.1 存储指令(STORE) - - - - - - - - - - - - - - - - - - - - - 1-161.2.2 加法指令(ADD) - - - - - - - - - - - - - - - - - - - - - - 1-181.2.3 加法扩展指令(ADDX)- - - - - - - - - - - - - - - - - - - - 1-201.2.4 减法指令(SUB) - - - - - - - - - - - - - - - - - - - - - - 1-211.2.5 减法扩展指令(SUBX)- - - - - - - - - - - - - - - - - - - - 1-231.2.6 乘法指令(MUL) - - - - - - - - - - - - - - - - - - - - - - 1-241.2.7 除法指令(DIV) - - - - - - - - - - - - - - - - - - - - - - 1-271.2.8 整型余数指令(MOD) - - - - - - - - - - - - - - - - - - - - 1-291.2.9 实型余数指令(REM) - - - - - - - - - - - - - - - - - - - - 1-301.2.10 增量指令(INC) - - - - - - - - - - - - - - - - - - - - - - 1-311.2.11 减量指令(DEC) - - - - - - - - - - - - - - - - - - - - - - 1-321.2.12 时间加法指令(TMADD) - - - - - - - - - - - - - - - - - - - 1-331.2.13 时间减法指令(TMSUB) - - - - - - - - - - - - - - - - - - - 1-351.2.14 时间经过指令(SPEND) - - - - - - - - - - - - - - - - - - - 1-371.2.15 符号取反指令(INV) - - - - - - - - - - - - - - - - - - - - 1-391章 梯形图指令1-21.2.16 1的补码指令(COM) - - - - - - - - - - - - - - - - - - - - 1-411.2.17 绝对值转换指令(ABS) - - - - - - - - - - - - - - - - - - - 1-421.2.18 2进制转换指令(BIN) - - - - - - - - - - - - - - - - - - - 1-441.2.19 BCD 转换指令(BCD) - - - - - - - - - - - - - - - - - - - - 1-451.2.20 校验转换指令(PARITY)- - - - - - - - - - - - - - - - - - - 1-461.2.21 ASCII 码转换1指令(ASCII) - - - - - - - - - - - - - - - - 1-471.2.22 ASCII 码转换2指令(BINASC)- - - - - - - - - - - - - - - - 1-491.2.23 ASCII 码转换3指令(ASCBIN)- - - - - - - - - - - - - - - - 1-501.3 逻辑运算/比较指令 - - - - - - - - - - - - - - - - 1-511.3.1 逻辑与指令(AND) - - - - - - - - - - - - - - - - - - - - - 1-511.3.2 逻辑或指令(OR)- - - - - - - - - - - - - - - - - - - - - - 1-521.3.3 逻辑异或指令(XOR) - - - - - - - - - - - - - - - - - - - - 1-531.3.4 比较指令() - - - - - - - - - - - - - - - - - - - - - - 1-541.3.5 比较指令(≦) - - - - - - - - - - - - - - - - - - - - - - 1-551.3.6 比较指令() - - - - - - - - - - - - - - - - - - - - - - 1-561.3.7 比较指令() - - - - - - - - - - - - - - - - - - - - - - 1-571.3.8 比较指令(≧) - - - - - - - - - - - - - - - - - - - - - - 1-581.3.9 比较指令() - - - - - - - - - - - - - - - - - - - - - - 1-591.3.10 范围检查指令(RCHK)- - - - - - - - - - - - - - - - - - - - 1-601.4 程序控制指令 - - - - - - - - - - - - - - - - - - - 1-631.4.1 图调用指令(SEE) - - - - - - - - - - - - - - - - - - - - - 1-631.4.2 运动程序调用指令(MSEE)- - - - - - - - - - - - - - - - - - 1-641.4.3 函数调用指令(FUNC)- - - - - - - - - - - - - - - - - - - - 1-651.4.4 连续执行型直接输入指令(INS) - - - - - - - - - - - - - - - 1-661.4.5 连续执行型直接输出指令(OUTS)- - - - - - - - - - - - - - - 1-691.4.6 扩展程序执行指令(XCALL) - - - - - - - - - - - - - - - - - 1-711.4.7 WHILE 指令(WHILE END_WHILE)- - - - - - - - - - - - - - - 1-721.4.8 IF 指令(IFEND_IF) - - - - - - - - - - - - - - - - - - - 1-741.4.9 IF 指令(IF ELSE END_IF) - - - - - - - - - - - - - - - - 1-761.4.10 FOR 指令(FOR END_FOR)- - - - - - - - - - - - - - - - - - 1-781.4.11 EXPRESSION 指令(EXPRESSION) - - - - - - - - - - - - - - - 1-801.5 基本函数指令 - - - - - - - - - - - - - - - - - - - 1-811.5.1 平方根指令(SQRT)- - - - - - - - - - - - - - - - - - - - - 1-811.5.2 正弦指令(SIN) - - - - - - - - - - - - - - - - - - - - - - 1-831.5.3 余弦指令(COS) - - - - - - - - - - - - - - - - - - - - - - 1-851.5.4 正切指令(TAN) - - - - - - - - - - - - - - - - - - - - - - 1-871.5.5 反正弦指令(ASIN)- - - - - - - - - - - - - - - - - - - - - 1-881.5.6 反余弦指令(ACOS)- - - - - - - - - - - - - - - - - - - - - 1-891.5.7 反正切指令(ATAN)- - - - - - - - - - - - - - - - - - - - - 1-901.5.8 指数指令(EXP) - - - - - - - - - - - - - - - - - - - - - - 1-921.5.9 自然对数指令(LN)- - - - - - - - - - - - - - - - - - - - - 1-931.5.10 常用对数指令(LOG) - - - - - - - - - - - - - - - - - - - - 1-941.6 数据操作指令 - - - - - - - - - - - - - - - - - - - 1-951.6.1 位循环左移指令(ROTL)- - - - - - - - - - - - - - - - - - - 1-951.6.2 位循环右移指令(ROTR)- - - - - - - - - - - - - - - - - - - 1-971.6.3 位传送指令(MOVB)- - - - - - - - - - - - - - - - - - - - - 1-991.6.4 字传送指令(MOVW)- - - - - - - - - - - - - - - - - - - - -1-1011.6.5 替换传送指令(XCHG)- - - - - - - - - - - - - - - - - - - -1-1031.6.6 表初始化指令(SETW)- - - - - - - - - - - - - - - - - - - -1-1051-31 1.6.7 字节字展开指令(BEXTD)- - - - - - - - - - - - - - - - - 1-107 1.6.8 字字节压缩指令(BPRESS) - - - - - - - - - - - - - - - - 1-1091.6.9 数据检索指令(BSRCH)- - - - - - - - - - - - - - - - - - - 1-1111.6.10 分类指令(SORT) - - - - - - - - - - - - - - - - - - - - - 1-1131.6.11 位左移指令(SHFTL)- - - - - - - - - - - - - - - - - - - - 1-1141.6.12 位右移指令(SHFTR)- - - - - - - - - - - - - - - - - - - - 1-1161.6.13 字复制指令(COPYW)- - - - - - - - - - - - - - - - - - - - 1-1171.6.14 字节交换指令(BSWAP)- - - - - - - - - - - - - - - - - - - 1-1191.7 DDC 指令- - - - - - - - - - - - - - - - - - - - - 1-1211.7.1 死区A 指令(DZA)- - - - - - - - - - - - - - - - - - - - - 1-1211.7.2 死区B 指令(DZB)- - - - - - - - - - - - - - - - - - - - - 1-1231.7.3 上下限值指令(LIMIT)- - - - - - - - - - - - - - - - - - - 1-1251.7.4 PI 控制指令(PI) - - - - - - - - - - - - - - - - - - - - - 1-1281.7.5 PD 控制指令(PD) - - - - - - - - - - - - - - - - - - - - - 1-1311.7.6 PID 控制指令(PID) - - - - - - - - - - - - - - - - - - - - 1-1341.7.7 一阶延迟指令(LAG)- - - - - - - - - - - - - - - - - - - - 1-1381.7.8 相位超前滞后指令(LLAG) - - - - - - - - - - - - - - - - - 1-1411.7.9 函数发生器指令(FGN)- - - - - - - - - - - - - - - - - - - 1-1441.7.10 反函数发生器指令(IFGN) - - - - - - - - - - - - - - - - - 1-1481.7.11 直线加减速器1指令(LAU)- - - - - - - - - - - - - - - - - 1-1521.7.12 直线加减速器2指令(SLAU) - - - - - - - - - - - - - - - - 1-1561.7.13 脉宽调制指令(PWM)- - - - - - - - - - - - - - - - - - - - 1-1631.8 表数据操作指令 - - - - - - - - - - - - - - - - - 1-1651.8.1 块调出指令(TBLBR)- - - - - - - - - - - - - - - - - - - - 1-1651.8.2 块写入指令(TBLBW)- - - - - - - - - - - - - - - - - - - - 1-167 1.8.3 行检索指令纵向(TBLSRL) - - - - - - - - - - - - - - - - 1-169 1.8.4 列检索指令横向(TBLSRC) - - - - - - - - - - - - - - - - 1-1711.8.5 块清除指令(TBLCL)- - - - - - - - - - - - - - - - - - - - 1-1731.8.6 表间块传送指令(TBLMV)- - - - - - - - - - - - - - - - - - 1-1751.8.7 Q 表调出指令(QTBLR QTBLRI) - - - - - - - - - - - - - - - 1-1771.8.8 Q 表写入指令(QTBLW QTBLWI) - - - - - - - - - - - - - - - 1-1791.8.9 Q 指针清除指令(QTBLCL)- - - - - - - - - - - - - - - - - - 1-1811章 梯形图指令1.1.1 A 触点指令(NOC)1-41.1继电器电路指令1.1.1A 触点指令(NOC)概要映像寄存器的值为1(ON)时将位输出置为ON 反之映像寄存器的值为0(OFF)时将位输出置为OFF格式参数程序举例当MB000100 ON 时MB000101为ON 标记NOC 全称NO Contact 类别RELAY 图标参数名称设定继电器编号所有比特型寄存器同上带下标字母1.1 继电器电路指令1-511.1.2B 触点指令(NCC)概要映像寄存器的值为1(ON)时将位输出置为OFF反之映像寄存器的值为0(OFF)时将位输出置为ON格式参数程序举例当MB000100 ON时MB000101为OFF1.1.3接通延时定时器指令(TON[10ms])概要位输入为ON时进行计时当计数值设定值时位输出为ON计数中位输入为OFF时停止计时位输入再次为ON时从(0)开始计数同时计数用的寄存器中存储实际计数时间(以10ms 为单位)的值标记NCC 全称NC Contact 类别RELAY 图标参数名称设定继电器编号所有比特型寄存器同上带下标字母1章 梯形图指令1.1.3 接通延时定时器指令(TON[10ms])1-6格式参数程序举例MW00011作为计时器的计数用寄存器而工作为避免重复请务必设定未使用的寄存器标记TON[10ms]全称On-Delay Timer[10ms]类别RELAY 图标参数名称设定Set(设定值)所有整型寄存器同上带下标字母(065535(655.35s)10ms 刻度)常数Count(计数值)整型寄存器(#C 寄存器除外)同上带下标字母1.1 继电器电路指令1-711.1.4断开延时定时器指令(TOFF[10ms])概要位输入为OFF 时进行计时当计数值设定值时位输出为OFF计数中最近的位输入为ON 时停止计时位输入再次为OFF时从(0)开始计数同时计数用的寄存器中存储实际计数时间(以10ms 为单位)的值格式参数程序举例标记TOFF[10ms]全称Off-Delay Timer[10ms]类别RELAY 图标参数名称设定Set(设定值)所有整型寄存器同上带下标字母(065535(655.35s)10ms 刻度)常数Count(计数值)整型寄存器(#C 寄存器除外)同上带下标字母1章 梯形图指令1.1.5 接通延时定时器指令(TON[1s])1-8MW00011作为计时器的计数用寄存器而工作为避免重复请务必设定未使用的寄存器1.1.5接通延时定时器指令(TON[1s])概要位输入为ON 时进行计时当计数值设定值时,位输出为ON 计数中最近的位输入为OFF时停止计时位输入再次为ON时从(0)开始计数同时计数用的寄存器中存储实际计数时间(以1s 为单位)的值格式参数程序举例标记TON[1s]全称On-Delay Timer[1s]类别RELAY 图标参数名称设定Set(设定值)所有整型寄存器同上带下标字母(065535s 1s 刻度)常数Count(计数值)整型寄存器(#C 寄存器除外)同上带下标字母1.1 继电器电路指令1MW00011作为计时器的计数用寄存器而工作为避免重复请务必设定未使用的寄存器1.1.6断开延时定时器指令(TOFF[1s])概要位输入为OFF 时进行计时当计数值设定值时位输出为OFF 计数中位输入为OFF时停止计时位输入再次为ON时从(0)开始计数同时计数用的寄存器中存储实际计数时间(以1s 为单位)的值格式参数标记TOFF[1s]全称Off-Delay Timer[1s]类别RELAY图标参数名称设定Set(设定值)所有整型寄存器同上带下标字母(065535s1s 刻度)常数Count(计数值)整型寄存器(#C 寄存器除外)同上带下标字母1章 梯形图指令1.1.7 上升脉冲指令(ON-PLS)程序举例MW00011作为计时器的计数用寄存器而工作为避免重复请务必设定未使用的寄存器1.1.7上升脉冲指令(ON-PLS)概要位输入状态从OFF 变为ON时位输出在一个扫描周期内为ON指定的寄存器用于保存位输出上次的值格式参数标记ON-PLS 全称Rise Pulse 类别RELAY图标参数名称设定用于保存位输入上次值的寄存器编号比特型寄存器(#C 寄存器除外)同上带下标字母1.1 继电器电路指令1程序举例当IB00001从OFF 变为ON 时MB000101在一个扫描周期内为ON MB000100用于保存IB00001上次的值表1.1表示上升脉冲指令的寄存器状态(注)在该程序举例中检测出的并非MB000100的上升而是IB00001的上升MB000100仅用于保存IB00001上次的值表1.1 上升脉冲指令的寄存器状态输入结果IB00001MB000100(IB00001上次的值)MB000100(IB00001的保存)MB000100OFF OFF OFF OFF OFF ON OFF OFF ON OFF ON ON ONONONOFF1章 梯形图指令1.1.8 下降脉冲指令(OFF-PLS)1.1.8下降脉冲指令(OFF-PLS)概要位输入从ON 变为OFF时位输出在一个扫描周期内为ON指定的寄存器用于保存位输出上次的值格式参数程序举例当IB00001从ON 变为OFF 时MB000101在一个扫描周期内为ON MB000100用于保存IB00001上次的值标记OFF-PLS 全称Fall Pulse 类别RELAY图标参数名称设定用于保存位输入上次值的寄存器编号比特型寄存器(#C 寄存器除外)同上带下标字母1.1 继电器电路指令1表1.2表示下降脉冲指令的寄存器状态(注)在该程序举例中检测出的并非MB000100的下降而是IB00001的下降MB000100仅用于保存IB00001上次的值1.1.9线圈指令(COIL)概要位输入ON 时将映像寄存器的值置为1(ON)位输入OFF时置为0(OFF)格式参数程序举例MB000100为ON时MB000101为ON表1.2 下降脉冲指令的寄存器状态输入结果IB00001MB000100(IB00001上次的值)MB000100(IB00001的保存)MB000101OFF OFF OFFOFF OFF ONOFF ON ON OFF ON OFF ONONONOFF标记COIL 全称Coil 类别RELAY图标参数名称设定线圈编号比特型寄存器(#C 寄存器除外)同上带下标字母1章 梯形图指令1.1.10 置位线圈指令(S-COIL)1.1.10置位线圈指令(S-COIL)概要执行条件成立时将输出置为ON并保持ON的状态格式参数程序举例多次指定同一输出地点时上例将进行如下动作* OB00000为OFF 时在置位线圈指令下OB00000为ON 状态标记S-Coil 全称Set Coil 类别RELAY图标参数名称设定线圈编号比特型寄存器(#C 寄存器除外)同上带下标字母1.1 继电器电路指令11.1.11复位线圈指令(R-COIL)概要执行条件成立时将输出置为OFF并保持OFF的状态格式参数程序举例多次指定同一输出地点时上例将进行如下动作* OB00000为ON 时在复位线圈指令下OB00000为OFF 状态标记R-Coil 全称Reset Coil 类别RELAY图标参数名称设定线圈编号比特型寄存器(#C 寄存器除外)同上带下标字母1章 梯形图指令1.2.1 存储指令(STORE)1.2数值运算指令1.2.1存储指令(STORE)概要将Source 存储在Dest中格式参数标记STORE 全称Store 类别MATH图标参数名称设定Source所有整型长整型实型寄存器同上带下标字母下标寄存器常数Dest整型长整型实型寄存器(#C 寄存器除外)同上带下标字母下标寄存器1.2 数值运算指令1程序将长整型的数据存储到整型寄存器中时直接保留低16位存储的数据即使超出整数范围(-3276832767)也不会发生运算错误敬请注意1章 梯形图指令1.2.2 加法指令(ADD)1.2.2加法指令(ADD)概要进行整型长整型实型数的加法运算给Source A 加上Source B将其结果存储在Dest中整型的运算结果大于32767时发生数据上溢的运算错误长整型的运算结果大于2147483647时发生数据上溢的运算错误格式参数标记ADD 全称Add 类别MATH图标参数名称设定Source A所有整型长整型实型寄存器同上带下标字母下标寄存器常数Source B 所有整型长整型实型寄存器同上带下标字母下标寄存器常数Dest整型长整型实型寄存器(#C 寄存器除外)同上带下标字母下标寄存器1程序举例整型数的加法运算实型数的加法运算长整型的加减法指令(---)通常为32位但在余数补偿运算表达式(前一指令为乘法指令()后一指令为除法指令())中使用时为64位运算1.2.3 加法扩展指令(ADDX)1.2.3加法扩展指令(ADDX)概要进行整型长整型数的加法运算给Source A 加上Source B 将其结果存储在Dest中即使运算结果数据上溢也不会发生运算错误格式参数程序举例在整型数的加法运算中为避免发生运算错误而使用长整型的加减法指令(---)通常为32位但在余数补偿运算表达式(前一指令为乘法指令()后一指令为除法指令())中使用时为64位运算标记ADDX 全称Extended Add 类别MATH图标参数名称设定Source A所有整型长整型实型寄存器同上带下标字母下标寄存器常数Source B 所有整型长整型实型寄存器同上带下标字母下标寄存器常数Dest整型长整型实型寄存器(#C 寄存器除外)同上带下标字母下标寄存器11.2.4减法指令(SUB)概要进行整型长整型实型数的减法运算从Source A 减去Source B将其结果存储在Dest中整型的减法运算结果小于-32768时发生数据下溢的运算错误长整型的减法运算结果小于-2147483648时发生数据下溢的运算错误格式参数标记SUB 全称Subtract 类别MATH图标参数名称设定Source A所有整型长整型实型寄存器同上带下标字母下标寄存器常数Source B 所有整型长整型实型寄存器同上带下标字母下标寄存器常数Dest整型长整型实型寄存器(#C 寄存器除外)同上带下标字母下标寄存器1.2.4 减法指令(SUB)程序举例整型数的减法运算实型数的减法运算长整型的加减法指令(---)通常为32位但在余数补偿运算表达式(前一指令为乘法指令()后一指令为除法指令())中使用时为64位运算11.2.5减法扩展指令(SUBX)概要进行整型长整型数的减法运算即使运算结果数据下溢也不会发生运算错误格式参数程序举例在整型数的减法运算中为避免发生运算错误而使用长整型的加减法指令(---)通常为32位但在余数补偿运算表达式(前一指令为乘法指令()后一指令为除法指令())中使用时为64位运算标记SUB 全称Subtract 类别MATH图标参数名称设定Source A所有整型长整型实型寄存器同上带下标字母下标寄存器常数Source B 所有整型长整型实型寄存器同上带下标字母下标寄存器常数Dest整型长整型实型寄存器(#C 寄存器除外)同上带下标字母下标寄存器1.2.6 乘法指令(MUL)1.2.6乘法指令(MUL)概要进行整型长整型实型数的乘法运算Source A 乘以Source B将其结果存储在Dest中格式参数标记MUL 全称Multiply 类别MATH图标参数名称设定Source A所有整型长整型实型寄存器同上带下标字母下标寄存器常数Source B 所有整型长整型实型寄存器同上带下标字母下标寄存器常数Dest整型长整型实型寄存器(#C 寄存器除外)同上带下标字母下标寄存器1程序举例整型数的乘法运算长整型数的乘法运算1.2.6 乘法指令(MUL)实型数的乘法运算长整型的加减法指令(---)通常为32位但在余数补偿运算表达式(前一指令为乘法指令()后一指令为除法指令())中使用时为64位运算11.2.7除法指令(DIV)概要进行整型长整型实型数的除法运算Source A 除以Source B将其结果存储在Dest中格式参数标记DIV 全称Divide 类别MATH图标参数名称设定Source A所有整型长整型实型寄存器同上带下标字母下标寄存器常数Source B 所有整型长整型实型寄存器同上带下标字母下标寄存器常数Dest整型长整型实型寄存器(#C 寄存器除外)同上带下标字母下标寄存器1.2.7 除法指令(DIV)程序举例实型数的除法运算11.2.8整型余数指令(MOD)概要将整型长整型除法运算的余数存储在Dest中请在除法指令后立即执行若不在除法指令后立即执行其后到下次数值运算指令出现之间的运算结果将无法保证格式参数程序举例将整型除法运算的商存储在MW00101中余数存储在MW00102中标记MOD全称Integer Remainder 类别MATH图标参数名称设定Dest整型长整型实型寄存器(#C 寄存器除外)同上带下标字母下标寄存器1.2.9 实型余数指令(REM)1.2.9实型余数指令(REM)概要将实型除法运算的余数存储在Dest中此时所谓的余数是指从Source 连续减去Base所得的剩余即假设连续减去的次数为n则得到如下结果DestSource(Basen)(0≦DestBase)格式参数程序举例求出MF00200除以常数1.5的余数将其结果存储在DF00202中标记REM全称Real Remainder 类别MATH图标参数名称设定Source所有实型寄存器同上带下标字母常数Base所有实型寄存器同上带下标字母常数Dest实型寄存器(#C 寄存器除外)同上带下标字母11.2.10增量指令(INC)概要给整型长整型寄存器加1整型时加法运算结果即使大于32767也不会发生数据上溢的运算错误同样长整型也不会发生数据上溢的运算错误格式参数程序举例整型标记INC 全称Increment 类别MATH图标参数名称设定Dest整型长整型寄存器(#C 寄存器除外)同上带下标字母下标寄存器1.2.11 减量指令(DEC)长整型1.2.11减量指令(DEC)概要从整型长整型寄存器中减1整型时减法运算结果即使小于-32768也不会发生数据下溢的运算错误同样长整型也不会发生数据下溢的运算错误格式参数标记DEC 全称Decrement 类别MATH图标参数名称设定Dest整型长整型寄存器(#C 寄存器除外)同上带下标字母下标寄存器1程序举例整型长整型1.2.12时间加法指令(TMADD)概要进行两个时间数据(时/分/秒)的加法运算给Dest 加上Source(加时间)将其结果存储在Dest中Source 和Dest 的数据格式如下表1.3 数据格式寄存器偏置数据内容数据范围(BCD)0时/分高位字节(时)023低位字节(分)0591秒00000059。

DM9000中文手册

,011)被选 中

访问类型 高电平

是访问数据 端口;低电平 是访问地址 端口

字命令标志, 默认低电平 有效

当访问 外部数据存 储器是字或 双字宽度时, 被置位

100

INT

O

中断请求信 号

高电平 有效,极性能 修改

37~53 56

SD31~16

I/O

双字模式,高 16 位数据引 脚

注意:以上介质无关端口都内部自带 60K 欧姆的下拉电阻 处理器接口引脚

1

IOR#

I

2

IOW#

I

3

AEN#

I

处理器读命 令

低电平 有效,极性能 够被 EEPRO M 修改,详细 请参考对 EE PROM 内容 的描述

处理器写命 令

低电平 有效,同样能 修改极性

芯片选择,低

4

IOWAIT

O

14

RST

外部介质无 关接口发送 时钟

外部介质无 关接口发送 数据低 4 位

输出

TXD[2: 0]决定内部 存储空间基 址:TXD [2: 0]) * 10H +

300H

54

MDIO

I/O

外部介质无

关接口串行

数据通信

57

MDC

O

外部介质无 关串行数据 通信口时钟, 且与中断引 脚有关

该引脚 高电平时候, 中断引脚低 电平有效;否 则高有效

0 0 16 位

0 1 32 位

108 位

11未 定义

66

EECK

I

时钟信号

67

EECS

I/O

片选

也做 LE D 模式选择 引脚

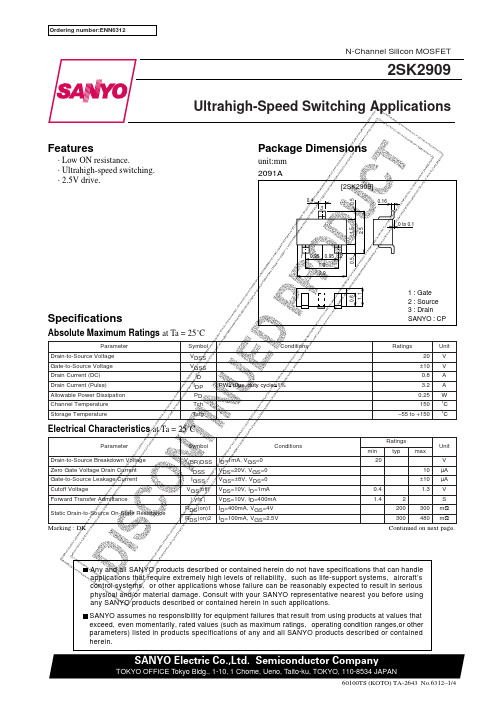

2SK2909中文资料

Switching Time Test Circuit

4V 0V VIN VDD=10V ID=400mA RL=25Ω D VOUT

VIN PW=10µs D.C.≤1%

G

2SK2909 P.G 50Ω S

1.0 0.9 0.8

ID - VDS

8.0V 6.0V 4.0V 3.0V

2.5 V 2.0 V

Package Dimensions

unit:mm 2091A

[2SK2909]

0.5

0.4 3 0.16

0 to 0.1

0.5

1

0.95 0.95 2 1.9 2.9

1.5

2.5

Specifications

Absolute Maximum Ratings at Ta = 25˚C

Parameter Drain-to-Source Voltage Gate-to-Source Voltage Drain Current (DC) Drain Current (Pulse) Allowable Power Dissipation Channel Temperature Storage Temperature Symbol VDSS VGSS ID I DP PD Tch Tstg PW≤10µs, duty cycle≤1% Conditions

op er at io n

Ta= 25˚C

2 3

1.0 7

0.1

2

3

5

7

Drain Current, ID – A

1.0

2

3

0.01 Single pulse 0.01 2 3 5 7 0.1

Drain-to-Source Voltage,VDS – V

OPPO_F29手机产品培训教材-PPT精品文档

我的世界 轻松掌控

核心卖点

双卡双待 持久续航

商务助理PDA

核心卖点

GSM双卡双待,双卡同时在线

Hale Waihona Puke 双卡双待独有双卡设置功能

可选择通话、信息、上网优先SIM卡, 真正人性化操作,双卡机功能,单卡机体 验

一键即可切换,不同身份,自如畅想

可随时关闭任意一张卡,自由选择工 作和生活 双卡均能自定义名称、通话风格和铃 声,心情自己做主

短信模块 通讯模块 音乐模块

设置模块 其他模块 电子相框

魅力卖点

高效配置

高效率核心处理器 55M机身内存 EDGE 2.75G上网 蓝牙核心BT2.0+EDR技术 JAVA虚拟机优化

魅力卖点

OBS音效系统

OBS(OPPO Basic System)是OPPO特有音效 系统的简称,是F29音质出众的基本元素:

魅力卖点

日立高清液晶显示屏

2.8英寸TFT显示屏 日立IPS技术 QVGA 240*320分辨率 支持160°宽视角

魅力卖点

USE-EASY体验设计

“Use-Easy”体验设计是OPPO本着“以人 为本”的设计理念,贯穿音乐、拍照、商务三 大系列手机的核心特质,以用户感受为基础进 行的人性化体验设计,让您在操作使用时感受 到不一样的方便与快捷

目标客户

他们接近或者恰过而立之年; 他们热爱自己的事业, 同时也执着地追求高品质生活; 他们需要的不是繁琐的操作, 而是人性化的设计, 以及满足个人需求的功能应用。

双卡双待消费群体

他们是追求生活品质,希望让工作 和生活彻底分开的一群人。 他们是经常奔波于两地,需求同时使用 不用区域电话卡的一群人。 他们是生活在现代化的一小时城市圈,手 机号码归属地频繁变动的人士。

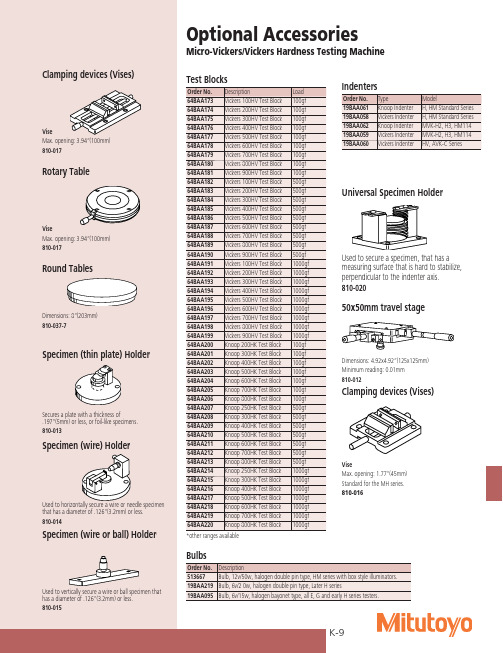

K-9可选配件,微维克斯硬度试验机剪子订单号型号及描述说明书

G

steel ball 1471N(150kgf) beryllium copper, phosphor bronze

H

1/8”

588.4N(60kgf) Bearing metal

E

diameter 980.7N(100kgf)

K

steel ball 1471N(150kgf)

L

1/4”

588.4N(60kgf) Plastics, lead

50x50mm travel stage

Dimensions: 4.92x4.92”(125x125mm) Minimum reading: 0.01mm 810-012

Clamping devices (Vises)

Vise Max. opening: 1.77”(45mm) Standard for the MH series. 810-016

Indenters

Order No. 19BAA061 19BAA058 19BAA062 19BAA059 19BAA060

Type Knoop Indenter Vickers Indenter Knoop Indenter Vickers Indenter Vickers Indenter

Model H, HM Standard Series H, HM Standard Series MVK-H2, H3, HM114 MVK-H2, H3, HM114 HV, AVK-C Series

Micro-Vickers/Vickers Hardness Testing Machine

Test Blocks

Order No. 64BAA173 64BAA174 64BAA175 64BAA176 64BAA177 64BAA178 64BAA179 64BAA180 64BAA181 64BAA182 64BAA183 64BAA184 64BAA185 64BAA186 64BAA187 64BAA188 64BAA189 64BAA190 64BAA191 64BAA192 64BAA193 64BAA194 64BAA195 64BAA196 64BAA197 64BAA198 64BAA199 64BAA200 64BAA201 64BAA202 64BAA203 64BAA204 64BAA205 64BAA206 64BAA207 64BAA208 64BAA209 64BAA210 64BAA211 64BAA212 64BAA213 64BAA214 64BAA215 64BAA216 64BAA217 64BAA218 64BAA219 64BAA220

步科K10无人机动力系统使用手册

最大允许电压

56V

最大允许电流(持续)

120A(有优良散热的情况下)

最大允许峰值电流(10秒) 140A(有优良散热的情况下)

PWM信号输入电平

3.3/5V(兼容)

工作脉宽

1100-1940μm

信号兼容频率

30-500Hz

螺旋桨 直径×螺距 重量

安装与连接

·整套动力系统出厂时已经组装完成,根据桨叶“CW”、“CCW”标记对应安装动力系统,带“CW”标记的动力系统安 装在需顺时针旋转的机臂上,带“CCW”标记的动力系统安装在需逆时针旋转的机臂上。 ·安装在外径为40mm的圆柱型机臂上。 ·并排摆放的三根黑线为电机信号输出线,白黑线为油⻔信号线,红黑线为电调电源输入线,多色排线为数据输出 和电调升级线。 ·电调油⻔固化为1100-1940μm,不支持油⻔校准。

3316 185g

信号线850±50 SignalWire850±50

2-M3

28.4

电源线 XT60(公头)

升级线 杜邦2.54-5P(⺟端)

信号线 杜邦2.54-3P(⺟端)

Ø40圆形管夹 Ø40RoundedJoinf

指示灯 PilofLamp

信号线850±50 UpgradeWire850±50

动力系统清单

① ③ ④ ⑤

⑥

⑦

②

⑧ ⑨

① 螺旋桨1pcs ② 电机1pc s ③ 电机座1pcs ④ 电源线1pcs ⑤ 电调数据线1pcs

⑥ 油 ⻔ 线1 p c s ⑦ 螺 钉若 干 ⑧ 航 灯 套 件 1 p c s ⑨ 电 调(内 置)1 p c s

拨码开关4 OFF OFF ON OFF ON ON ON OFF

LED颜色 绿色 红色 蓝色 ⻩色 紫色

MEMORY存储芯片M29W320EB70N6E中文规格书

32 Mbit (4Mbx8 or 2Mbx16, Uniform Parameter Blocks, Boot Block)3V supply Flash memoryFeaturesSupply voltage–V CC =2.7V to 3.6V for Program, Erase and Read–V PP =12V for Fast Program (optional)Access times: 70, 90nsProgramming time–10μs per byte/word typical–Double word/ Quadruple byte ProgramMemory Blocks–Memory Array: 63 Main Blocks–8 Parameter Blocks (T op or BottomLocation)Erase Suspend and Resume modes–Read and Program another Block during Erase SuspendUnlock Bypass Program command–Faster Production/Batch ProgrammingV PP/WP pin for fast Program and Write Protect Temporary Block Unprotection modeCommon Flash Interface–64 bit Security codeExtended memory Block–Extra block used as security block or to store additional informationLow power consumption–Standby and Automatic Standby100,000 Program/Erase cycles per blockElectronic signature–Manufacturer code: 0020h–Top Device code M29W320ET: 2256h–Bottom Device code M29W320EB: 2257h RoHS® packages availableCommon Flash Interface (CFI)M29W320ET, M29W320EB Appendix B Common Flash Interface (CFI)The Common Flash Interface is a JEDEC approved, standardized data structure that can be read from the Flash memory device. It allows a system software to query the device to determine various electrical and timing parameters, density information and functions supported by the memory. The system can interface easily with the device, enabling the software to upgrade itself when necessary. When the CFI Query Command is issued the device enters CFI Query mode and the data structure is read from the memory. Table23, Table24, Table25, Table26, Table27 and Table28 show the addresses used to retrieve the data.The CFI data structure also contains a security area where a 64 bit unique security number is written (see Table28: Security code area). This area can be accessed only in Read mode by the final user. It is impossible to change the security number after it has been written by Numonyx.Table 23.Query Structure Overview(1)AddressSub-section name Description x16x810h20h CFI Query Identification String Command set ID and algorithm data offset 1Bh36h System Interface Information Device timing & voltage information27h4Eh Device Geometry Definition Flash device layout40h80h Primary Algorithm-specific extendedQuery tableAdditional information specific to the PrimaryAlgorithm (optional)61h C2h Security code area64 bit unique device number1.Query data are always presented on the lowest order data outputs.Table 24.CFI Query Identification String(1)AddressData Description Value x16x810h20h0051h“Q”11h22h0052h Query unique ASCII string "QRY""R"12h24h0059h"Y"13h26h0002h Primary Algorithm Command Set and Control Interface ID code 16 bitID code defining a specific algorithmAMD Compatible14h28h0000h15h2Ah0040hAddress for Primary Algorithm extended query table (see Table27)P = 40h 16h2Ch0000h17h2Eh0000h Alternate Vendor Command Set and Control Interface ID code secondvendor - specified algorithm supported NA18h30h0000h19h32h0000hAddress for Alternate Algorithm extended Query table NA 1Ah34h0000h1.Query data are always presented on the lowest order data outputs (DQ7-DQ0) only. DQ8-DQ15 are ‘0’.M29W320ET, M29W320EB Common Flash Interface (CFI)Common Flash Interface (CFI)M29W320ET, M29W320EBTable 26. Device Geometry Definition(1)AddressData Description Value x16x827h4Eh0016h Device Size = 2n in number of bytes 4 Mbyte28h 29h 50h52h0002h0000hFlash Device Interface code descriptionx8, x16Async.2Ah 2Bh 54h56h0000h0000hMaximum number of bytes in multi-byte program or page = 2n NA2Ch58h0002h Number of Erase Block regions. It specifies the number ofregions containing contiguous Erase Blocks of the same size.22Dh 2Eh 5Ah5Ch0007h0000hRegion 1 informationNumber of Erase Blocks of identical size = 0007h+182Fh 30h 5Eh60h0020h0000hRegion 1 informationBlock size in Region 1 = 0020h * 256 byte8Kbyte31h 32h 62h64h003Eh0000hRegion 2 informationNumber of Erase Blocks of identical size = 003Eh+16333h 34h 66h68h0000h0001hRegion 2 informationBlock size in region 2 = 0100h * 256 byte64Kbyte1.For the M29W320EB, Region 1 corresponds to addresses 000000h to 007FFFh and Region 2 to addresses 008000h to1FFFFFh. For the M29W320ET, Region 1 corresponds to addresses 1F8000h to 1FFFFFh and Region 2 to addresses 000000h to 1F7FFFh.Table 27.Primary Algorithm-specific extended Query tableAddressData Description Value x16x840h80h0050hPrimary Algorithm extended Query table unique ASCII string “PRI”"P"41h82h0052h"R" 42h84h0049h"I" 43h86h0031h Major version number, ASCII"1" 44h88h0031h Minor version number, ASCII"1"45h8Ah0000h Address Sensitive Unlock (bits 1 to 0)00 = required, 01= not requiredSilicon Revision Number (bits 7 to 2)Yes46h8Ch0002h Erase Suspend00 = not supported, 01 = Read only, 02 = Read and Write247h8Eh0001h Block Protection00 = not supported, x = number of blocks in per group148h90h0001h Temporary Block Unprotect00 = not supported, 01 = supportedYes49h92h0004h Block Protect /Unprotect04 = M29W320E04M29W320ET, M29W320EB Common Flash Interface (CFI)4Ah 94h 0000h Simultaneous operations, 00 = not supported No 4Bh 96h 0000h Burst mode, 00 = not supported, 01 = supportedNo 4Ch 98h 0000h Page mode, 00 = not supported, 01 = 4 page word, 02 = 8 page word No 4Dh9Ah00B5hV PP Supply Minimum Program/Erase voltage bit 7 to 4 HEX value in volts bit 3 to 0 BCD value in 100 mV11.5V4Eh 9Ch 00C5h V PP Supply Maximum Program/Erase voltage bit 7 to 4 HEX value in volts bit 3 to 0 BCD value in 100 mV12.5V4Fh 9Eh0002h 0003hTop/Bottom Boot Block Flag02h = Bottom Boot device, 03h = Top Boot device–Table 27.Primary Algorithm-specific extended Query table (continued)Address DataDescriptionValue x16x8Table 28.Security code areaAddress DataDescriptionx16x861h C3h, C2h XXXX 64 bit: unique device number62h C5h, C4h XXXX 63h C7h, C6h XXXX 64hC9h, C8hXXXX。

K9F1208中文资料

NAND Flash芯片K9F1208资料一 NAND FlaSh和NOR Flash闪存(Flash Memory)由于其具有非易失性、电可擦除性、可重复编程以及高密度、低功耗等特点,被广泛地应用于手机、MP3、数码相机、笔记本电脑等数据存储设备中。

NAND Flash和NOR Flash是目前市场上两种主要的非易失闪存芯片。