基于FPGA_CPLD的数字光端机系统设计

基于fpga和cpld的程序设计流程

基于fpga和cpld的程序设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!基于FPGA和CPLD的程序设计流程详解在现代电子设计领域,FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)因其高度可配置性和快速原型设计能力而备受青睐。

逻辑设计中的FPGA与CPLD技术应用

逻辑设计中的FPGA与CPLD技术应用在现代电子行业中,逻辑设计是一个至关重要的环节。

FPGA (Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)技术作为两种主要的可编程设备,已经在逻辑设计中广泛应用。

它们具有灵活性、可编程性以及高度集成的特点,使得它们在各种应用领域中扮演着重要的角色。

一、FPGA技术应用FPGA是一种可编程逻辑器件,其内部可通过编程实现各种逻辑功能和数字电路设计。

FPGA通常由可编程逻辑单元(CLB)、输入输出引脚和输入输出模块等部分构成。

其设计过程包含RTL(Register-Transfer Level)描述、综合、布局布线以及配置等环节。

1. 通信与网络领域在通信领域,FPGA被广泛应用于协议转换、调制解调器设计以及网络加速器等方面。

由于FPGA的可编程性,可以根据需要灵活配置不同的协议,实现不同网络之间的无缝对接。

2. 数字信号处理(DSP)领域在数字信号处理领域,FPGA被广泛应用于图像处理、音频处理以及实时数据处理等方面。

由于FPGA具有并行处理的能力,能够同时处理多个数据流,因此在实时性要求较高的应用中表现出色。

3. 汽车电子领域在汽车电子领域,FPGA被广泛应用于汽车控制单元(ECU)和车载娱乐系统等方面。

由于汽车电子应用对可靠性和安全性要求较高,FPGA的可编程性以及自适应性能使其成为理想的选择。

二、CPLD技术应用CPLD是一种更小规模的可编程器件,与FPGA相比,CPLD通常更适用于复杂逻辑功能的实现。

CPLD通常由可编程逻辑阵列(PLA)、输入输出引脚以及输入输出缓冲区组成。

1. 控制系统领域在控制系统领域,CPLD被广泛应用于逻辑控制器的设计。

由于CPLD具有高速、低功耗以及可靠性强的特点,被广泛应用于各类自动化控制系统中。

2. 电源管理系统领域在电源管理系统领域,CPLD被广泛应用于电源管理单元(PMU)的设计。

CPLD & FPGA 数字系统的设计及应用

三、适配

将由综合器产生的网表文件配置于指定的目标器件中,使之产 生最终的下载文件,如J时序仿真 接近真实器件运行特性的仿真 功能仿真 直接对VHDL、原理图描述或其他描 述形式的逻辑功能进行测试模拟

五、编程下载

六、硬件测试

PLD设计流程

原理图/VHDL文本编辑

综合

FPGA/CPLD

器件和电路系统

1、isp方式下载 2、JTAG方式下载 3、针对SRAM结构的配置 4、OTP器件编程

功能仿真

逻辑综合器

FPGA/CPLD

适配

结构综合器

时序与功能 门级仿真

1、功能仿真 2、时序仿真

FPGA/CPLD 编程下载

常用的EDA设计工具

1、常用的集成CPLD/FPGA开发工具 2、设计输入工具 3、逻辑综合器 4 、仿真器 5 、下载器 6 、常用的其他EDA工具 Protel 99、SPICE 等 MAX+Plus II、ISE 等 HDL Designer Series、Ultra Edit 等

FPGA Compiler II、Synplify/Synplify Pro、

Leonardo Spectrum 等 Modelsim、Cadence、Synopsys 等

MAX+Plus II 的使用

1、设计输入 2 、编译 3 、仿真 4 、适配 5 、下载 6 、硬件测试

MAX+Plus II 实例应用一

在EDA软件的图形编辑界面上绘 制能完成特定功能的电路原理图

使用某种硬件描述语言(HDL)的电路设计文本,如 VHDL或Verilog的源程序,进行编辑输入。

PLD设计流程

二、 综合

整个综合过程就是将设计者在EDA平台上编辑输入的HDL文本、 原理图或状态图形描述,依据给定的硬件结构组件和约束控制条件 进行编译、优化、转换和综合,最终获得门级电路甚至更底层的电 路描述网表文件。

应用CPLD的数字光端机的设计与实现

A D变换 /

采集 模块

R 一8 S 4 5信号

远 程控制

文 献标志码 :A

Ab tac : To v r o te ia v na e o n lg pia tr n l e ., p o q ai o r n miso sr t o ec me h ds d a tg s f a ao o t l emia , .g c o r u ly f ta s sin, sg a dso t n a s d y t in l itri c u e b o

应 用 C L 的数 字光 端 机 的设 计 与 实 P D的数 字光 端机 的设 计 与实 现

De i ig a d Re l i g o h gi l t a er ia y Usn sgnn n ai n ft e Di t z a Op i l c T m n l ig CPL b D

̄e ue c i s o e s mpig  ̄e u n y t mpe n i s rn n e sn pia b rc a n 1 Th o g x e me s a d tmig q n y4 tme ft a ln h q e c o i lme tt me ha g a d r u ig o tc lf e h n e. i i ru h e p r nt n i n i smuain。te c re te s a d fa ii t o e s se ae v rfe . T sse i lt o h or cn s n e sbl y f t y tm r ei d i h i he y tm as e tr s smpl sr cu e, lw c s 。 a d tbe n lo f au e i e tu t r o ot n sa l i p ro a c e r n e。d fntl twi e te d v lpn rn fdgt pia em ias f m e i yi i e l b e eo ig te d o iia o tc ltr n l. l h l

基于FPGA的数字光端机的设计

( hj n ntueo o mu i t n Z ei gH n zo 10 8 C ia Z e a gIstt f m nc i , h j n a gh u3 0 1 , hn ) i i C ao a

Absr t: i p rito c st e d sg n t y o o g dit n e ta miso y tm ,wh c sb s d t ac Th spa e n r du e h e in a d sud ft L n — sa c r ns si n s se he ih i a e o GA i e n FP vd o,a d o a e e s a a u i nd r v r e d t .Th n i nay e h rn i l n h r i g pr c s . T i y t m e ta l s s t e p i cp e a d t e wo k n o e s h s s se i i l s smp e,e s o man a n a d c n be a p id i h i e n tr s se a y t it i n a p le n t e v d o mo io y t m. Ke r s:h i e p i r n miso y t m ;AGC;mo io y tm y wo d t e fb ro tc ta s s in s se n tr s se

原理 和 工作过 程 。该 系统 设备 简单 、 于 维护 。 便 可应 用 于视 频 监控 系统 中。

关键 词 : 字光 端机 ; 数 增益 自调 整 ; 控 系统 监

De i n o be sg fFi r Optc Tr n mi so Sy t m s d o FPGA i a s s i n se Ba e n 口 L in ,HU Yi1 n IL a g . a g,HAN i h n i Ru— e z

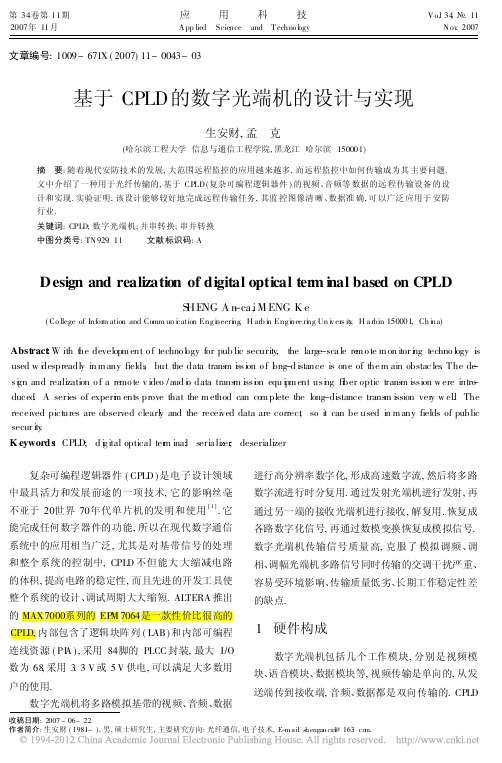

基于CPLD的数字光端机的设计与实现

第34卷第11期应用科技V o.l 34,l .112007年11月A pp lied Science and T echno l ogyN ov .2007文章编号:1009-671X (2007)11-0043-03基于CPLD 的数字光端机的设计与实现生安财,孟 克(哈尔滨工程大学信息与通信工程学院,黑龙江哈尔滨150001)摘 要:随着现代安防技术的发展,大范围远程监控的应用越来越多,而远程监控中如何传输成为其主要问题.文中介绍了一种用于光纤传输的,基于CPLD (复杂可编程逻辑器件)的视频、音频等数据的远程传输设备的设计和实现.实验证明,该设计能够较好地完成远程传输任务,其监控图像清晰、数据准确,可以广泛应用于安防行业.关键词:CPLD;数字光端机;并串转换;串并转换中图分类号:TN 929.11 文献标识码:ADesign and realization of digital optical ter m i nal based on CPLDS HENG A n -ca,i M ENG K e(Co llege of Infor m ation and Comm un i cation Eng i neeri ng ,H arb i n Eng i nee ri ng Un i v ers it y ,H a rbin 150001,Ch i na)Abst ract :W ith t h e developm ent o f techno l o gy for pub lic security ,the large -sca le re m o te m on itor i n g techno logy isused w i d espreadly in m any fields ,but the data trans m ission o f l o ng -d istance is one of the m ain obstac les .The de -si g n and realization o f a re mo te v ideo /aud i o data trans m issi o n equ i p m ent usi n g fi b er optic trans m ission w ere intro -duced .A series of experi m ents prove that the m ethod can co m plete the long -distance trans m ission ver y w el.l The received pictures are observed clearl y and the received data are correc,t so it can be used in m any fields of public secur ity .K eywords :CPLD;d i g ital optical ter m ina;l seria lizer ;deserializer 收稿日期:2007-06-22.作者简介:生安财(1981-),男,硕士研究生,主要研究方向:光纤通信,电子技术,E-m ai:l s h engan ca@i 163.co m.复杂可编程逻辑器件(CPLD )是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于20世界70年代单片机的发明和使用[1].它能完成任何数字器件的功能,所以在现代数字通信系统中的应用相当广泛,尤其是对基带信号的处理和整个系统的控制中,CPLD 不但能大大缩减电路的体积,提高电路的稳定性,而且先进的开发工具使整个系统的设计、调试周期大大缩短.ALTERA 推出的MAX7000系列的EP M 7064是一款性价比很高的CPLD,内部包含了逻辑块阵列(LAB )和内部可编程连线资源(PI A ),采用84脚的PLCC 封装,最大I/O 数为68,采用3.3V 或5V 供电,可以满足大多数用户的使用.数字光端机将多路模拟基带的视频、音频、数据进行高分辨率数字化,形成高速数字流,然后将多路数字流进行时分复用.通过发射光端机进行发射,再通过另一端的接收光端机进行接收,解复用.恢复成各路数字化信号,再通过数模变换恢复成模拟信号.数字光端机传输信号质量高,克服了模拟调频、调相、调幅光端机多路信号同时传输的交调干扰严重、容易受环境影响、传输质量低劣、长期工作稳定性差的缺点.1 硬件构成数字光端机包括几个工作模块,分别是视频模块、语音模块、数据模块等,视频传输是单向的,从发送端传到接收端,音频、数据都是双向传输的.CPLD是系统的核心,接收各个模块送来的数据,然后时分复用到信道上,通过光纤传到对端,对端再将接收到的数据发送给各个相对应的模块.收发芯片TI65LV1023A /1224B 的主要作用是实现并串/串并转换、数据帧的同步.系统的逻辑框图如图1所示.图1 系统模块图视频模块采用了德州仪器(TI)的A /D 转换芯片TLC5510和D /A 转换芯片TL5632,这2款芯片都是T I 公司针对视频数字化推出的高性价比产品.TLC5510为8位A /D 转换器,最高采样率为20MH z ,在使用时只需将8位数字输出与CPLD 的I/O 相连即可.在PAL 制的电视信号中,模拟视频信号的频率为4.43MH z ,根据奈奎斯特采样定理,采样速率最低为8.86MH z ,但在实际中所采用的A /D 采样速率为最优的17.7MH z ,系统传输的是实时数字视频流,在发送端将A /D 采集来的数字流发送出去,没有压缩与编码,在接收端将收到的数字信号经过D /A 芯片TL5632转换为模拟视频信号送到监视器.TL5632是一种低功耗的3路输出的D /A 转换器,最高转换速率为60MH z ,在实际使用中只需要将从CPLD 解调出来的8位数字视频信号与TL5632的一个输出通道相连,同时把相应通道的时钟输入接到CPLD 的视频时钟输出端即可.最后在监视器上显示出来的信号完全可以满足视频监控的要求.语音模块采用的是德州仪器(TI)的音频A /D 芯片PC M 1402将模拟音频信号转换为数字信号,采样率为48kH z .在接收端采用TI 的D /A 转换芯片PC M 1502将数字信号转换为模拟音频信号,转换后的信号通过R J11头与交换机相连,让接收端电话机接入语音网络.在实际中,应充分考虑电话振铃带来的干扰,并且使系统不稳定的影响.数据模块采用国家半导体(NS)的L M 331芯片,采用5V 电压供电,最高转换速率为1M bps ,完全可以满足要求.LM 331结构简单,外围电路少,使用非常方便,并且可以实现F /V 和V /F 的双向转换.并串转换模块串并转换模块采用德州仪器的T I 65LV1023A 和T I 65LV1224B ,它是一款1B 10的高性价比串行器,采用3.3V 电源供电,最大时钟为66MH z .在工作中它采用的是10B 12的转换,10位有效数据为加2位时钟位为一帧,所以最高的串行传输速率为60@12=720M bps [2].串行数据采用的是低电压差分信号(LVDS )传输.低电压差分信号的电压摆幅小,所以转换速度更快,可以实现更高的速度,且不会增加串扰、E M I 和功耗,可以大大地提高信噪比[3].在接收端,并行器1224B 具有自动恢复时钟的能力,当接收端接收到传过来的串行数据后,首先锁定、恢复出系统时钟,然后将串行数据转换为10位并行数据输出.激光发射/接收模块采用武汉电信器件公司的RTXM 123B -3-35-SC 和RTXM 123B -3-53-SC.这是一款收发一体的激光发射模块,分别采用1310n m 发射、1550nm 接收和1550发射、1310nm 接收,电路接口采用LVPECL 电平,电源采用3.3V 电源供电,最高传输速率为622M bps .2 软件设计CPLD 功能是通过V eril o g HDL 编程来实现的.Verilog 是一种功能强大的硬件描述语言,被广泛应用在电子设计中[4].在本系统的实现中,采用了模块化设计.对不同的接口构建不同的module ,在主程序中再调用这些m odu le .主程序主要完成对光纤接口处收发芯片的控制.在本系统中,光纤接口处的高速收发芯片选用T I 公司的T I 65LV1023A /1224B ,它是用于高速串行收发芯片与CPLD 相连的控制信号和数据信号,如图2所示,其他一些对T I 65LV1023A /1224B 进行初始化设置的信号线并未标出.主程序中发送模块设置了一个主计数器对t_#44#应 用 科 技 第34卷clk 发射时钟进行计数,根据计数值控制t_en 发送使能信号,使TI65LV1023A /1224B 输出一定格式的串行数据(可参见TI65LV1023A /1224Bdatasheet).在接收端,TI65LV1023A /1224B 收到串行数据后,实现帧定位,串/并转换,产生r_cl k 接收时钟信号和r_dv 数据有效指示信号送入CPLD,主程序中的接收模块根据c l k 、r_dv 信号将接收到的数据解复用后,传给各个对应的模块.图2 CPLD 与串行器/解串器T I65LV 1023A /1224B 的接口3 实际应用中的设计要点在实际的设计中,有几点需要特别注意,因为它们影响到整个系统的稳定性,甚至关系到整个系统设计的成败.3.1 视频信号的同步为了使视频信号在传输过程中始终保持同步,需要在发送端对模拟的视频信号提取同步信号,用于控制视频信号的同步,这里采用LM 1881加74H C123来实现.提取出的同步信号加到CPLD 的I/O 口,作为一个缓冲器的清零端,如果A /D 后的信号不同步,则进行清零,丢掉这一帧数据.在实际的工作中,这一方法很有效,可以较好地解决视频信号的同步问题.3.2 串行信号的电平转换由于并串/串并转换芯片TI65LV1023A /1224B的串行数据采用的是低电压差分信号(LVDS ),而激光发射/接收模块的接口为LVPECL 信号电平,所以需要进行LVDS 到LVPECL 和LVPECL 到LVDS 的转换,但在实际试验中,只需要做前者,LVPECL 到LVDS 不需要转换,直接对接就可以.采用电阻分配网络的方法进行转换,如图3所示,可以简单有效地完成转换[5].图3 LV PECL 到LVD S 的电平转换3.3 电源设计整个系统用到正5V 和正3.3V 电源,这里采用78M 05芯片来稳压,将外界电源转换为正5V 电源,采用L M 1117芯片将正5V 电压转换为正3.3V 电压.对于芯片的数字电源引脚,应接一个磁珠与电源相连,可以有效地对电源进行滤波.激光发射/接受模块的电源输入需要接一个C-L-C 滤波电路,因为任何的电源波动都会影响到该模块的发送与接受.4 结束语此套远程监控系统实现了各个监控点和总监控室的信号远程传输.经过试验,各监控点的摄像头传回视频信号,总监控室通过数据接口线对各个摄像头进行远程控制,远程两端之间还可以进行话音通信,能够较好地满足安防的要求.参考文献:[1]亿特科技.CPLD /FPGA 应用系统设计与产品开发[M ].北京:人民邮电出版社,2005.[2]T I Inc .10-MH z To 66-M H z ,10:1LV DS SER I A L IZERA nd DESER I AL IZER [Z ].A ustin :T I l nc ,2006.[3]NS Inc .D ata T rans m ission Comm un i cations Inte rfece D iv-ision[Z ].A tl anta :N S Inc ,2003.[4]夏宇闻.V eril ong 数字系统设计教程[M ].北京:北京航空航天大学出版社,2003.[5]NS Inc .C M L 、PECL 及LV DS 间的相互连接[Z ].A tlan -ta :NS Inc ,2001.[责任编辑:张晓京]#45#第11期生安财,等:基于CPLD 的数字光端机的设计与实现。

基于CPLD的数字光端机的设计

Ke y wo r d s : d i g i t l a o p t i c l a t r a n s c e i v e r ;v i d e o a u d i o ;r e mo t e mo n i t o i r n g;s e c u i r t y t e c h n o l o g y; o p t i c a l i f b e r

视频传榆 , 2路 音 频 传 输 和 一路 反 向 数 据 传 输 的数 字 光 端 机 的 设 计 。 实 验 证 明 , 系统 工 作 性 能稳 定 可 靠 , 实 时 传 输 效

果好 . 可广泛应用于安防行业。

关键词 : 数 字光端机 ; 视 频 ;音频 ; 远程监控 ; 安 防技 术 ; 光纤 中图 分 类 号 : T N 9 1 1 . 7 4 文献标识码 : A 文章 编 号 :1 6 7 4 — 6 2 3 6 ( 2 0 1 5 ) 2 0 — 0 0 5 3 — 0 3

Ex p e ime r n t s s h o w t h a t t h e s y s t e m p e r f o r ma n c e i s s t a b l e a n d r e l i a b l e, r e l- a t i me t r a n s mi s s i o n e f f e c t i s g o o d ,c a n b e w i d e l y u s e d

a n d b e c o me mo r e a n d mo r e wi d e l y . An d b y t h e o p t i c a l i f b e r a s t r a n s mi s s i o n me d i u m o f d i g i t a l o p t i c l a t r a n s c e i v e r , h a s b e c o me

基于FPGA处理器的数字光端机系统简介

基于FPGA处理器的数字光端机系统简介目前在高速公路、交通、电子警察、监控、安防、工业自动化、电力、海关、水利、银行等领域视频图像、音频、数据、以太网、电话等光端机开始普遍大量应用。

由于数字光端机具有传输信号质量高,没有模拟调频、调相、调幅光端机多路信号同传时交调干扰严重、容易受环境干扰影响、传输质量低劣、长期工作稳定性差的缺点,因此许多大型重点工程已普遍采用数字光端机。

系统框架与工作原理整个系统由核心控制模块FPGA、音频采样编解码模块、视频分离模块、视频放大模块、视频A/D 和D/A 转换模块、并串/串并转换模块、光纤调制收发模块、电源控制模块和485 数据传输模块。

图1 是该系统的系统框图。

图1 系统结构框图系统的工作原理为:光端机系统分为两部分,分别为:发射机和接收机。

在发射端,来自监视器或其他视频源的视频信号首先经过发射板上的视频滤波网络去除噪声干扰信号,然后对该视频信号进行视频分离和视频放大。

视频分离模块得到视频信号的行、场同步信号以及奇偶场信号、视频钳位等重要的视频信息。

接下来,对放大后的视频信号进行A/D 转换,得到的数字化的视频信号送入系统主控核心FPGA 中。

与此同时,如果系统检测到了有音频信号的存在,则对其进行音频滤波、音频数字化采样以及音频PCM编码。

经过PCM 编码后的音频信号,送入系统主控核心FPGA 中。

反向数据传输主要是485 信号,该信号也送入到FPGA。

这样,系统主控核心FPGA 对来自不同模块的视频、音频、数据等信号整合,时分复用地将各个信号编码成8 位并行信号流送入到并串转换模块。

信号流经过并串转换后变成高速的LVDS 信号驱动光纤收发模块以波分复用的方式完成了电/光变化和光发射。

在光端机的接收端,经过以上的逆过程,完成对原始信号的恢复。

系统硬件组成1 FPGA 核心控制器系统的核心控制部分是整个系统的心脏,为了满足对高速、。

(RTXM)基于FPGA的数字光端机的设计与实现

安徽理jI=大学硕士论文图中Ⅺ+和Ⅺ.接收光收发模块传来高速低压差分串行数据信号,ROUT0到ROUT9为转化后的低速并行的LVl]凡电平的数据信号,该数据信号直接和FPGA核心处理芯片的引脚相连。

FPGA再对低速的数据信号进行分接,传输到相应的模块。

3、发射端光收发部分电路设计光的收发主要有两种方式,一种是在发射端采用单独的激光器,配合控制驱动芯片(如AGC、APC)来完成光的发射,在接收端采用独立的PIN组件,再配以相应的放大电路来完成光的接收。

这种方式因为发射功率大,适合远距离传输,成本也低。

但是由于其电路结构复杂,集成度低,调试困难,可靠性差。

另一种方式是采用集成光模块。

发射模块集成了LD及控制驱动芯片,接收模块集成了PIN和后续的放大电路,输出信号一般符合PECL电平。

此种方式优点电路结构简单,集成度高,调试方便,可靠性高。

另外,随着科学技术不断提高,集成的光模块的价格也开始变的合理。

基于上述两种方案,综合考虑该数字光端机采用集成光模块。

该模块选用武汉电信器件公司的RTXMl23.3.35.SC光收发一体模块【16】。

其收发独立工作,3.3V供电电压,最高传输数据速率为622Mbps;采用标准的lX9封装;单纤双向传输,由于其内部集成了波分复用器,发射端光纤波长为1310nm,接收端光纤波长为1550nm;接口形式为SC接口:信号传输的电平为PECL电平。

其传输距离为20km。

其内部功能框图如下:SDlRDUrnitingAmplifieroD石c翻●-__-___一一)Signal。

PreamplifierDetectorRDTDMQWLaserOutputLDDrivingCircuit-—----—啼TDTll·,、^I。

L_JAInUl’1I图14RTXMl23-3.35.SC内部结构框图Fig14RTXMl23·-3—·35··SCInternalBlockDiagram●●●●3数字光端机的硬件实现(2)、LVDS接口输入电路LVDS输入差分阻抗为100Q,为适应共模电压宽范围内的变化,输入极还包含一个自动电平调整电路,将共模电压调整为一固定值,该电路后面是一个施密特触发器,主要是为防止不稳定,设计有一定的回滞特性,后级是差分放大电路,其输入结构见下图:P,1rK件Df狮aPT眦IEⅧ.SCHL^ln?rS丑卫r嗽IPaQOERh图18LVDS接口输入电路Fig18LVDSinterfaceinputcircuitLVDS的接收端需要有终端匹配电阻,没有终端匹配电阻,LVDS无法工作。

基于FPGA/CPLD控制系统的设计方法

蚌埠 234 ) 30 2

( 中国兵器工业第 24 究所 1研

摘 要

介绍 了用 F G / P D 实现控 制 系统 自顶 向下 的设 计 方 法 , PA CL 以一 个控 制 系统 实例 介 绍 了

控 制 系统 中小数 分频 的设 计方 法 , A D C公 司的 A t e 用 LE cv —HD i L进 行 状 态 图设 计 , 以及如 何 用流 水设

试, 以便最终验证项 目在 目标系统上 的实际工作 情况 , 排除错误 , 改进设计。

式在 E A软件中进行硬件设计 , D 非常直观、 简捷 。

3 F G / P D 控 制 系 统 设 计 方 法 P A CL 及设计实例

31 FG . P A控 制 系统 设 计举例

下面以一个实际控制系统 的一部分功能 为 例, 介绍用 F G / P D设计 控制 系统 的一般方 P A CL 法, 此控制系统 的具体设计要求 为: 输入系统 时

控制系统设计适合于大规模组合逻辑、 时序 电路设

计 , 可以替 代 几 十甚 至 上 百块 通 用 逻 辑 电路 芯 它

片, 这样的 F G / P D设计实际上就是一个子系 P A CL 统, 并且具有现场编程和在线升级 的功能 , 很容易

A t a o) u m tn 技术 的出现改变 了传统 的设计思路 , o i 使人们可 以通过对可编程逻辑器件的编程来实现 各种不同的功能。新的设计方法能够由设计者 自 己定义器件的内部逻辑 和管脚功能, 将原来 由电 路板设计完成的大部分工作放在芯片的编程设计 中进行。这样不仅可以通过芯片编程设计实现多 种数字逻辑功能 , 而且 由于管脚定义的灵活性 , 提 高了芯片使用效率 , 同时基于芯片的编程设计还 大大减少 了所用芯片的种类和数量, 缩小了体积 ,

基于CPLD的数字光端机的设计与实现

基 于 C L 的 数 字 光 端 机 的 设 计 与 实 现 PD

生安 财 , 孟 克

( 尔滨工程 大学 信 息与通信 工程 学院 , 哈 黑龙江 哈 尔滨 10 0 ) 5 0 1 摘 要: 随着现代安防技术的发展 , 范围远程监控 的应用越来越 多, 大 而远程监控中如何 传输 成为其 主要 问题 .

不 亚于 2 界 7 0世 0年 代单 片机 的发 明 和使 用 。它 .

能 完成 任何 数字器 件 的功 能 , 以 在现 代 数 字 通 信 所 系统 中的应 用相 当广 泛 , 其 是 对基 带 信 号 的处 理 尤 和整个 系 统 的 控 制 中 , P D 不 但 能 辨率数 字化 , 形成 高速数 字流 , 然后 将多路 数字 流进行 时分 复用 . 通过 发射光 端机 进行 发射 , 再 通过 另一 端的接 收光 端机 进行接 收 , 复用 . 复成 解 恢

各路 数字 化信号 , 再通 过数模 变换恢 复成 模拟 信号 . 数字 光端机 传输 信号 质 量 高 , 服 了模 拟 调 频 、 克 调

相 、 幅 光端 机 多路 信号 同时传输 的交 调干扰 严重 、 调 容易 受环境 影响 、 传输 质量 低劣 、 期工作 稳定 性差 长

的缺点 .

的体积 , 高电路 的稳定 性 , 提 而且先 进 的开发工 具 使

整个 系统 的设 计 、 调试周 期大 大缩 短 . L E A推 出 ATR 的 M X 0 0系列 的 E M 0 4是一 款性 价 比很 高 的 A 70 P 76 C L 内部包 含 了逻 辑块 阵列 ( A 和 内部 可 编程 P D, L B) 连线 资源 ( I , PA) 采用 8 4脚 的 P C L C封 装 , 大 IO 最 / 数为 6 , 8 采用 3 3V或 5V供 电 , 以满 足大 多数用 . 可 户 的使用 .

基于FPGA的数字光端机的设计与实现

2 0 年 5月 06

M a.20 v 0 6

基于 FG P A的数 字光 端机 的设计 与 实现

李 林 , 代华 3冯正 勇 4 ,谢 一 ,

(. 大学通信 工程 学院 , 1 重庆 重庆 404 ; . 004 2 重庆职业技 术 学院 , 重庆 401 ; 072 3电子科技 大学电子工程 学院 , . 四川 成都 605 ;. 1044西华师 范大学物 电学院 , 四川 南充 301 70)

以太网模块是设计的一个难点 ,通信接口芯片选用 的是 Bodo 公司的 A 11以太 网收发芯 片 。 C 0 racm C0 A 11 是 Bodo racm公司推 出的一款高性能的以太网收发芯片 .

集成度高,功耗低 。该芯片提供了标准的 MI接口, I I MI 可以用来进行芯片级( 集成电路)板级 。 , 或物理设备级 的 互联。 I l 个引脚被分为 4类: MI的 8 发送数据 、 接收数据、 网络状态及设备管理。本系统 中 F G P A与收发芯片之 间 采用 MI接 口实现芯片级的互联 , I l 个 引脚只用 I MI的 8 了其中与发送数据和接收数据有关的 l 个引脚 。 4 所有接 口信号都工作于 T L电平之上 。并被定义成和 3 V及 T . 3 5 V C SA I . MO SC相兼容。 0

1 硬 件构成

转换芯 片 A 98 . / D 20D A转换芯片 A 90 .这两款芯片 D 78 都是高性能器件, 完全满足监控系统视频质量的要求。 在 使用时控制方便 。与 开,A的数字接 口只需八位数据信 G 号线 ,一根时钟信号 线 .视频信号 的标 准采样频率 为 1. 在实际应用 中 , 3 M, 5 采用 1M 的采样时钟 。 6 系统 传输 的是实时的数字视频流 , 在远端通过 A D采样得到的数 / 字视频信号 ,没有经过编码和压缩 。直接传到局端通过 D A芯片l复出来 , / 炙 送入监视器。 这样将完全满足应用的 技术指标 , 得到满意的监控图像 。 语音模块采用的是国家半导体公司的 T 36 芯片 . P 07 实现音频信号的数字化 。在远端 , P0 7 T 36 芯片通过 R l J l 头与 电话连接 ; 在局端 ,P 07 T 36 芯片通过 R l 头与交换 Jl 机连接 , 让远段 电话机接入了话音网络 。 考虑到振铃 电路 给系统增加的功耗和使 系统不稳定 , 我们省略了该部分 , 采用蜂鸣器指示远端 电话被呼叫。 数据模块采用 了美信公司的 MA 40 X 9 ,电路结构简 单, 使用非常方便。 X 9 采用单 5 直流电源供 电, MA 4 0 v 数 据率可 以达到 2 Mb s . p.工作模式为差分全双工通信方 5 式, 可以双向传输数据 。

fpga光端机方案

fpga光端机方案FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具备可重新配置功能,广泛应用于各种计算机和电子设备中。

光端机(Optical Transmitter)是一种用于光纤通信的设备,将电信号转换为光信号进行传输。

本文将探讨基于FPGA的光端机方案,旨在提供一种灵活可靠的通信解决方案。

一、FPGA在光端机中的应用FPGA作为一种可编程器件,具备灵活性高、设计周期短等特点,非常适合用于光端机的设计和实现。

在光端机中,FPGA可以完成以下任务:1. 光信号调制解调:光信号的调制解调是光端机的核心功能之一。

通过编程FPGA,可以实现对光信号的高速调制解调,确保信号的准确传输和稳定性。

2. 信号处理:对于光信号来说,经过光纤传输后,可能会受到干扰和衰减等影响。

通过在FPGA中设计合适的信号处理算法,可以对信号进行增强、滤波等处理,提高传输质量和可靠性。

3. 协议转换:不同的设备和系统可能采用不同的通信协议,光端机需要将这些协议进行适配和转换。

通过在FPGA中实现协议转换的逻辑,可以实现不同协议之间的互通。

4. 自适应调节:FPGA具备较高的并行处理能力和即时性,可以实时监测光信号的质量,根据环境变化和失真情况进行自适应调节和优化,确保信号的稳定传输。

二、FPGA光端机方案的优势相比于传统的光端机方案,基于FPGA的光端机方案具有以下优势:1. 灵活性强:FPGA具备可编程的特点,可以根据实际需求进行灵活的功能设计和调整。

无需更换硬件设备,只需重新配置FPGA即可满足不同的应用需求。

2. 高性能:FPGA具备较高的计算和处理能力,能够满足高速、大容量的数据传输需求。

通过合理的设计和优化算法,可以实现更高效的信号调制解调,提高传输速度和质量。

3. 可靠性好:FPGA具备较强的容错性和自适应能力,可以根据实际环境进行实时调节和优化。

在光纤传输中可能遭受的噪声、干扰和衰减等问题,FPGA可以通过算法和逻辑调节来保证信号的稳定传输。

基于CPLD的多功能光端机设计与实现

分 配,就需要将 所有资源分配给 1 个用户 ,该 用户速 率 比例为 l ,其他用 户为 0 。静 态分配 秉持传输速率完全公平的原则 ,却忽略 了速率 比例的公平 ,所 以无法满足用户对速率 比例公

平 的需求。仅进行子信道分配后 ,每个用户均 已满足最低速率要求 ,在进行子信道 、功率分 配后 ,用户 间的速率按照 比例公平系数分布 ,

但是本文利用遗传 算法得 出的动态分配 算法 比

起 遍 历 子 信 道 的分 配 算 法 又 要 优 越 一 些 , 能够

率分配算法研 究 [ D 】 . 湖南大学 , 2 0 1 3 . [ 5 ]徐磊 . 无线协作通信 网络 中协作 中继传输

问题的研究 [ D 1 .安徽 大学 , 2 O 1 2 .

4 . 2 不 同 用 户 的 归 一 化 速 率 4 . 2 . 1参 数 设 定

4 . 3 . 2仿真结果 具体对比结果如图 6所示。 由图 6可 以看 出,遍 历子 信道 的功 率分 配算法能够对子信道进行合理分配 ,相 比起静 态分配 ,它能够更好 的保证用户 的最 小速率 ,

功能靠扩展模块实现 。各个功能模块与主板采 信 号发送至 光纤;光接 收端的主要任 务是将光 功能光端机的功能相对比较固定 ,除了传输视 用统一的通信协议 ,实现 了各个功能模块任意 信 号转变 成电信 号后,再从电信号中分接出各 频信 号之外,同一型号的多功能光端机只能传 路原始视频 、以太 网和扩展板信号 。 输音频、数据、以太网、开关量等其中的一个 组 合 、即 插 即 用 。

参考文献

[ 1 ]曹哲 . 无 线 中继 通 信 系统 中的功 率 分 配

与切 换 控 制 研 究 【 D 】 .南 京航 空 航 天 大 学, 2 0 1 2 . 【 2 】李荣凯 . A F协作通信 系统中节点选择 和功 率分配问题 的研 究 [ D ] .山东大学 , 2 0 1 1 . [ 3 ] 杨 晓峰 .协作通信 系统 中继选择 与功率分 配技 术研 究 [ D 】 .西南交通 大学 , 2 0 1 1 . [ 4 ] 殷 玲 .双向协作通信 系统的 中继选择 与功

应用CPLD的数字光端机的设计与实现

PRO CESS AUTOMATI ON I N STRU M ENTAT I ON Vol 132N o 11January 2011修改稿收到日期:2010-07-07。

第一作者姜鹏,男,1980年生,现为南京工业大学模式识别与智能系统专业在读硕士研究生;主要从事图像处理、嵌入式系统方面的研究。

应用CPLD 的数字光端机的设计与实现D esigni ng and R ealizi ng of the D igital Optical Term i nal by U si ng CPLD姜 鹏 何 毅(南京工业大学自动化与电气工程学院,江苏南京 211800)摘 要:针对模拟光端机传输质量低、信号易受环境干扰而失真、系统性能不稳定和电路设计复杂等缺点,采用CPLD 对四路数字光端机进行设计。

考虑到四路采样频率在满足以上要求的同时,还要通过一路光纤传输四路采样数据的情况,提出了并串转换频率为采样频率四倍的策略,实现了分时复用光纤通道。

通过实验和时序仿真,验证了该系统的正确性和可行性。

该系统结构简单、成本低、性能稳定,是未来数字光端机行业发展的方向。

关键词:复杂可编程逻辑器件 A /D 变换 采集模块 R S -485信号 远程控制中图分类号:TP39 文献标志码:AAbstract :T o overco m e t he di sadvantages of ana l og opti cal ter m i na,l e .g .,poor quality of trans m issi on ,si gnal di st orti on caused byenv i ron m ental i nterference ,unstabl e syste m perfor mance ,and co mp li cate circuitry desi gn ,the quadruplet d i g i ta l opti cal ter m i nal has been desi gned by usi ng compl ex progra mmabl e l og i c device (CPLD ).Consi der i ng the sa m pli ng frequency s hall m eet above require m ents ,and quadruplet sa mp li ng data s hallbe trans m itt ed t hrough the same optical fi ber path ,thus i t i s proposed t ha tm aking t he para ll e l to ser i al conversi on frequency 4tm i es of t he sa mpli ng frequency to m i ple m ent tm i e shar i ng and reusi ng opti cal fi ber channe.l Through experm i ents and tm i i ng sm i u l ati on ,t he correctness and feasi bilit y o f t he syste m are verifi ed .The syste m also f eatures sm i pl e struct ure ,lo w cos,t and stable i nperfor mance ,defi nitel y itw ill be t he devel opi ng trend of di g it a l optica l ter m i na l s .K ey words :Compl ex progra mmabl e l ogic dev i ce(CPLD ) A /D conversion A cquisi ti on modul e R S -485signa l R e mote contro l0 引言模拟视频光端机具有传输质量低、信号易受环境干扰而失真、系统性能不稳定和电路设计复杂等缺点[1]。

FPGACPLD数字电路设计经验分享

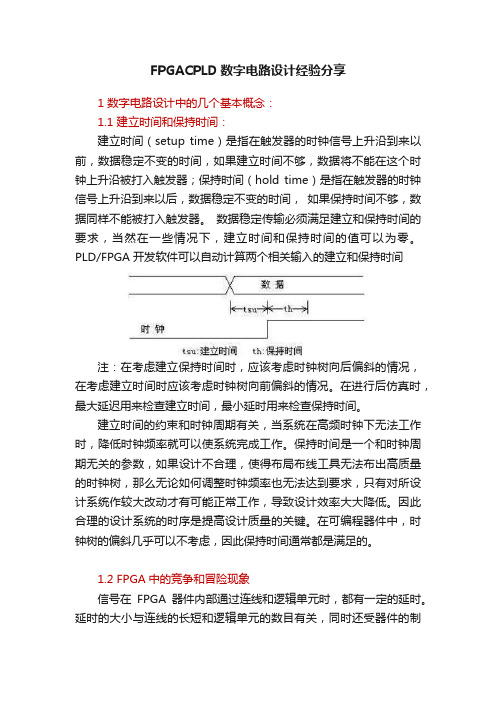

FPGACPLD数字电路设计经验分享1 数字电路设计中的几个基本概念:1.1 建立时间和保持时间:建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间注:在考虑建立保持时间时,应该考虑时钟树向后偏斜的情况,在考虑建立时间时应该考虑时钟树向前偏斜的情况。

在进行后仿真时,最大延迟用来检查建立时间,最小延时用来检查保持时间。

建立时间的约束和时钟周期有关,当系统在高频时钟下无法工作时,降低时钟频率就可以使系统完成工作。

保持时间是一个和时钟周期无关的参数,如果设计不合理,使得布局布线工具无法布出高质量的时钟树,那么无论如何调整时钟频率也无法达到要求,只有对所设计系统作较大改动才有可能正常工作,导致设计效率大大降低。

因此合理的设计系统的时序是提高设计质量的关键。

在可编程器件中,时钟树的偏斜几乎可以不考虑,因此保持时间通常都是满足的。

1.2 FPGA中的竞争和冒险现象信号在FPGA器件内部通过连线和逻辑单元时,都有一定的延时。

延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。

信号的高低电平转换也需要一定的过渡时间。

由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为'毛刺'。

如果一个组合逻辑电路中有'毛刺'出现,就说明该电路存在'冒险'。