synopsys简易教程

synopsys-dc中文教程(比较详细)

ASIC design flow

IP and Library Models

Verified RTL

Design Constraints

Logic Synthesis optimization&scan insertion Static Timing Analysis

no Time ok?

Floorplan placement, CT Insertion&Global routing

-output active_design+”.sdf” write_constraints –format sdf –cover_design\

-output constraints.sdf

ASIC design flow

Verification

利用SDF文件进行动态时序仿真:利用功能仿真时。用verilog 编写的test_bench 文件 形式验证:利用数学算法检查设计的逻辑的等效性,静态验证,需要的时间比动态仿真少,

方案。我们就以下几个方面对DC做以介绍:

script文件:由DC的命令构成,可使DC自动完成综合的整个过程。 DC支持的对象、变量、属性 DC支持的文件格式及类型 DC在HDL代码中的编译开关,控制综合过程

Translate_off/translate_on:指示DC终止或开始verilog 源代码转换的位置。 full_case:阻止case语句在不完全条件下生成latch。

பைடு நூலகம்

ASIC design flow

Compile and scan insert的scripts,采用bottom_up的编译方法

set_fix_multiple_port_net –buffer_constants –all compile –scan check_test create_test_pattern –sample 10 preview_scan insert_scan check_test 如果模块内的子模块具有dont_touch 属性需添加如下命令,因要插入扫描 remove_attribute find(-hierarchy design,”*”)dont_touch

SYNOPSYS界面操作课堂(一)

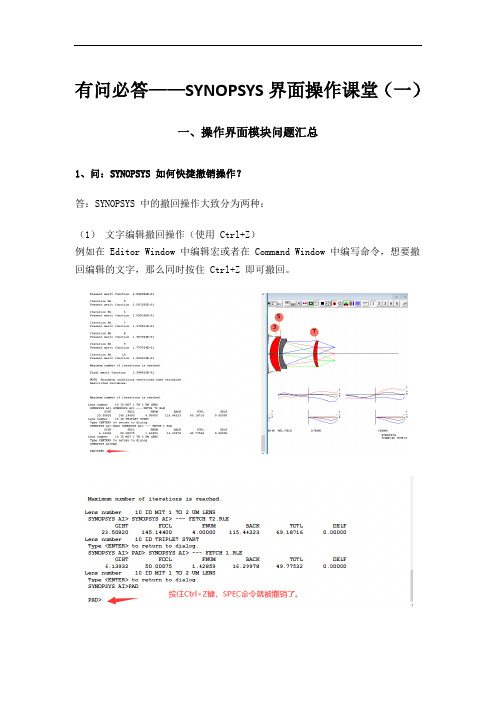

有问必答——SYNOPSYS界面操作课堂(一)一、操作界面模块问题汇总1、问:SYNOPSYS 如何快捷撤销操作?答:SYNOPSYS 中的撤回操作大致分为两种:(1)文字编辑撤回操作(使用 Ctrl+Z)例如在 Editor Window 中编辑宏或者在 Command Window 中编写命令,想要撤回编辑的文字,那么同时按住 Ctrl+Z 即可撤回。

(2)对镜头做出修改,之后返回到修改之前的镜头结构(使用 Ctrl+U 或者 F3 )例如:手动或者通过命令修改了镜头的厚度,或者优化了镜头,然后想要返回之前的结构,那么只需要直接使用 Ctrl+U 或者 F3 即可。

最多可以返回至10步之前。

通过 WS 修改表面1的厚度为 5mm。

然后关闭 WS 。

接着使用 Ctrl+U 或 F3 ,则镜头结构返回到修改之前。

再次打开 WS ,表面1厚度为 4mm。

若想要再返回到修改后的镜头结构,按 Ctrl+Y 就可以了。

2、问:输入命令 MMF,得到的 MTF 曲线图为什么不是彩色的?答:在CommandWindow中输入 MSS,在其打开的对话框中,将开关 35 打开。

或者直接在 Command Window 中输入 ON 35.3、问:SYNOPSYS 怎么缩小PAD窗口?答:点击 PAD 窗口的右上角图标。

4、问:点击按钮,为什么不显示图形呢?答:如下图5、问:SYNOPSYS 输入透镜的F数在哪里设置?答:你输入了透镜的曲率半径和材料,波长,系统的焦距就定了。

你输入了 YMP1 ,然后系统的 F 数就出来了。

或者,你想要使用最后一个面控制F数,那么可使用 UMC 命令UMC 1/(2*F/#)若想对 F 数进行修改,比例,F 数变为2。

这样的话,可以新建一个宏,输入如下代码:CHGFNO 2END6、问:下图中, X 方向不能取样?答:点击 Define skew field 按钮。

7、问: ZSEARCH 是否有类似 DSEARCH 中的 USE CURRENT 功能?答:目前 ZSEARCH 中没有 USE CURRENT功能。

Synopsys系列软件破@解及安装配置教程

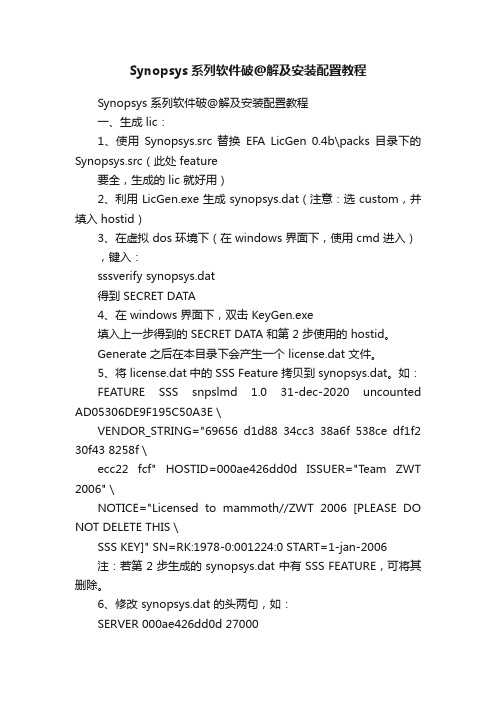

Synopsys系列软件破@解及安装配置教程Synopsys 系列软件破@解及安装配置教程一、生成 lic:1、使用Synopsys.src 替换EFA LicGen 0.4b\packs 目录下的Synopsys.src(此处 feature要全,生成的 lic 就好用)2、利用 LicGen.exe 生成 synopsys.dat(注意:选 custom,并填入 hostid)3、在虚拟 dos 环境下(在 windows 界面下,使用 cmd 进入),键入:sssverify synopsys.dat得到 SECRET DATA4、在 windows 界面下,双击 KeyGen.exe填入上一步得到的 SECRET DATA 和第 2 步使用的 hostid。

Generate 之后在本目录下会产生一个 license.dat 文件。

5、将 license.dat 中的 SSS Feature 拷贝到 synopsys.dat。

如:FEATURE SSS snpslmd 1.0 31-dec-2020 uncounted AD05306DE9F195C50A3E \VENDOR_STRING="69656 d1d88 34cc3 38a6f 538ce df1f2 30f43 8258f \ecc22 fcf" HOSTID=000ae426dd0d ISSUER="Team ZWT 2006" \NOTICE="Licensed to mammoth//ZWT 2006 [PLEASE DO NOT DELETE THIS \SSS KEY]" SN=RK:1978-0:001224:0 START=1-jan-2006注:若第 2 步生成的 synopsys.dat 中有 SSS FEATURE,可将其删除。

6、修改 synopsys.dat 的头两句,如:SERVER 000ae426dd0d 27000DAEMON snpslmd /home/eda/linux/bin/snpslmd其中:snpslmd 指向 SCL 的 snpslmd。

Synopsys安装和license制作简易教程

令$ hostname 可获取 localhost,而 snpslmd 后面的链接地址设置成绝对路径

~/eda/synopsys/scl/linux/bin/snpslmd(附录 A 为 synopsys.dat 更改后的部分内容)

(a) 选择 Synopsys.lpd

(b) 生成 synopsys.dat

GRUB_CMDLINE_LINUX="find_preseed=/preseed.cfg auto noprompt priority=critical locale=en_US net.ifnames=0 biosdevname=0"

键入命令# update-grub 键入命令# vim /etc/network/interfaces,添加

# hercules export HERCULES_HOME=$SYNOPSYS_HOME/hercules export PATH=$PATH:$HERCULES_HOME/bin

# starrc export STARRC_HOME=$SYNOPSYS_HOME/starrc export PATH=$PATH:$STARRC_HOME/bin

auto eth0 iface eth0 inet dhcp

重启系统 新建 synopsys 工具安装目录,并拷贝安装源 tar 压缩包到 sources 文件夹下,如图 3 所

示;同时将 installer_v3.2.tar 解压到文件夹 installer 中

图 3 安装目录树

以安装 Synopsys design compiler, dc 为例,而 scl、vcs 和 pt 的安装同 dc(注:synopsys 的其他工具的安装过程都相同) 键入命令$ ~/eda/synopsys/installer/setup.sh 开启图形安装界面,如图 4(a)所示 选择安装源路径为/home/jack/eda/synopsys/sources,如图 4(b)所示 选择安装 syn,即为 dc,如图 4(c)所示 选择安装路径为/home/jack/eda/synopsys/dc,如图 4(d)所示 其他未说明步骤按默认处理

三.Synopsys软件安装

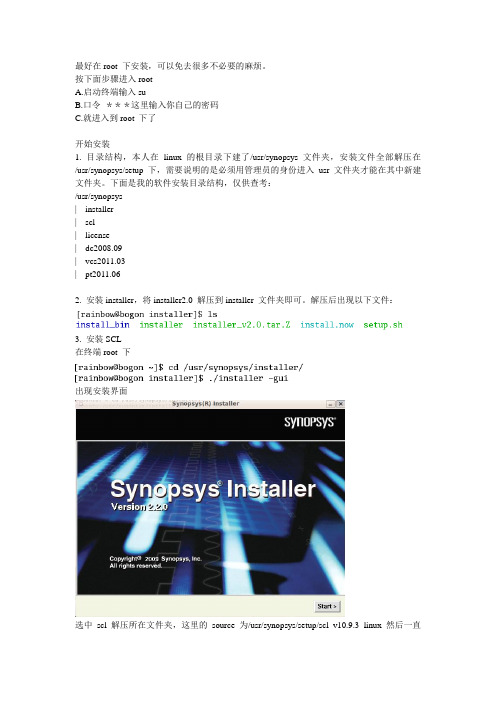

最好在root 下安装,可以免去很多不必要的麻烦。

按下面步骤进入rootA.启动终端输入suB.口令***这里输入你自己的密码C.就进入到root 下了开始安装1. 目录结构,本人在linux 的根目录下建了/usr/synopsys 文件夹,安装文件全部解压在/usr/synopsys/setup下,需要说明的是必须用管理员的身份进入usr 文件夹才能在其中新建文件夹。

下面是我的软件安装目录结构,仅供查考:/usr/synopsys|---installer|---scl|---license|---dc2008.09|---vcs2011.03|---pt2011.062. 安装installer,将installer2.0 解压到installer 文件夹即可。

解压后出现以下文件:3. 安装SCL在终端root 下出现安装界面选中scl 解压所在文件夹,这里的source 为/usr/synopsys/setup/scl_v10.9.3_linux 然后一直next,过程中有些选项都不需要管,也不需要填,直到选中安装目标路径,这里的安装路径是/usr/synopsys/scl,同样把scl_common 文件安装到scl。

4. dc2008安装同样的方法可以安装common 包和linux 包,安装这两个包的时候最好分开安装,先安装linux 包。

例如,我的common 和linux 包都放在/usr/synopsys/setup 下,安装common时source为/usr/synopsys/setup/Design_Compiler_2008.09_common,选中这个文件后按Done。

然后一路next,可能会出现替代呀,没有平台呀什么问题的对话框,不管它,只选能继续安装的。

但是安装目录一定要安装在一起!即都安装在/usr/synopsys/dc2008.09 下!5.vcs2011,pt2009安装安装文件解压在setup目录下,common 包和linux 包安装方法和上面的dc2008一样。

Synopsys系列软件安装说明

Synopsys系列软件安装说明magellan。

Synopsys软件一共有三个:VCS、formality、安装这是一套验证软件,现在我们说一下它们的安装流程:VWmare1.安装执行可执行文件。

安装无注意事项。

按照步骤安装直到完成。

REDHAT4.22.安装REDHAT 。

加载运行虚拟机,在file选项下选择new下的virtual mashine在左下角虚拟光驱中加载接下来按照提示加载在提示加载其他的光盘时,disc1.这。

加载之后记得connect(安装前提是硬盘空间最小要15G)剩下的光盘镜像,样直到安装完成。

3.安装VMware Tools开始启动系统,然后用安装完系统后,点击start this virtual machine账号登陆,密码就是在安装系统时自己设置的密码。

在上面的工具栏菜单root界面外,不LINUX选择VM\install VMware Tools(目的是鼠标可以直接移动到共享文件windowsLINUX界面的大小,同时也可以实现和再需要Ctrl+Alt;设置拷贝到任何目VMwareTools-6.0.0-45731.tar.gz夹),生成VmWare Tools后将zxvf录下,然后在终端中的该目录下用tar –命令进行解压,然后进入解压后得到的VMwareTools-7.8.4-126130.tar.gz一切选择./ vmware-install.pl进行安装(vmware-tools-distrib的目录,执行默认就行)。

安装目录下的一个另一种方法:如果第一种方法不行,出现错误,就加载VM里面有个文件linux.iso镜像,在系统中打开cd-romhomeTools压缩包。

把它拷贝到VMwareTools-8.1.3-203739.tar.gz就是VMwarexvzfVMwareTools-8.1.3-203739.tar.gz 解压缩文件,文件夹下,然后用tar – ./vmware-install.pl 进行安装。

synopsys工具安装教程

前言:这是本人经过两个星期的奋斗,从对linux命令的生涩到熟练,对后端工具的陌生到熟悉的一段战斗史!!!下面我把我的操作过程详细写下,供大家学习参考!!一:准备工作所需平台1、vmware92、RHEL(红帽企业版)6.3Synopsys 工具1、installer_v3.0(安装synopsys EDA tools 的图形界面的安装工具)2、scl_10.9。

3(synopsys license 管理工具,用于启动tools 的features)3、dc_2009.06(逻辑综合工具)4、icc_2009.06(布局布线工具)5、pt_2012。

12(时序分析工具)License生成工具1、EFA LicGen 0。

4b2、Synopsys SSS Feature Keygen3、Synposys。

src(最新的据我所知是40kb大小,有比较全的features)二:搭建RHEL1、安装vmware:本章节详见另一个文档。

文档名为“vmware安装手册”。

还有一份汉化包,需要可自行下载。

2、安装RHEL:本章详见另一个文档。

文档名为“RHEL6。

3安装手册"。

Ps:有一个页面会让你选择安装的软件包,这个时候人工勾上所有的软件包,不然启eda 工具的时候会发现很多系统库找不到。

三:vmware tools安装1、以root用户进入linux,找到左上角的VM选项,下拉之后选择安装wmwaretools.过一会儿会弹出来一个框框,显示vmwaretools—9.2.2-893683。

tar。

gz然后新开一个终端,输入cd /media 你会看到vmwaretools—9.2.2—893683.tar.gz 就在那里。

然后把他拷贝出来,后解压安装。

具体命令可以网上搜索。

四:license制作License制作要用到上述的材料,具体详见另一个文档。

文档名为“license制作". 将license文件,即synopsys.dat文件放到linux下的共享文件夹。

synopsys vdk使用方法

Synopsys VDK 使用方法Synopsys VDK(Virtualizer Development Kit)是一款用于虚拟开发和测试的软件工具。

它提供了一套完整的虚拟开发环境,包括模拟器、调试器和分析工具,帮助用户在不依赖硬件的情况下进行软件开发和测试。

本文将介绍Synopsys VDK的使用方法,包括安装、配置、使用和调试等方面的内容。

一、安装VDK1.1 下载VDK安装包在Synopsys冠方全球信息站上下载VDK的安装包,选择适合自己系统的版本进行下载。

1.2 安装VDK解压下载的安装包并按照提供的安装指南进行VDK的安装。

在安装过程中,可以根据自己的需求选择安装的组件和路径。

1.3 激活VDK安装完成后,根据提供的激活码激活VDK软件。

二、配置VDK2.1 创建新的虚拟开发项目在VDK中创建新的虚拟开发项目,设置项目的名称、目标处理器和其他相关配置信息。

2.2 导入软件模型将需要开发和测试的软件模型导入到VDK中,包括处理器模型、外设模型等。

2.3 配置虚拟开发环境配置VDK的虚拟开发环境,包括处理器的初始化、外设的连接和虚拟的外部环境设置等。

三、使用VDK3.1 虚拟化软件开发在VDK中进行软件的开发,包括编译、调试和运行等操作。

可以使用VDK提供的调试器进行软件的调试和分析。

3.2 虚拟化软件测试利用VDK进行软件的测试,包括单元测试、集成测试和系统测试等。

可以通过虚拟化的方式模拟各种复杂的场景和情况进行测试。

3.3 虚拟化性能分析使用VDK进行软件的性能分析,包括性能指标的监控、分析和优化等。

可以通过VDK提供的分析工具进行性能分析的工作。

四、调试VDK4.1 软件调试在VDK中进行软件的调试工作,包括断点设置、变量监视和程序运行状态检查等。

4.2 虚拟硬件调试利用VDK进行虚拟硬件的调试,包括外设的模拟、接口的调试和虚拟硬件的状态监控等。

4.3 软硬件协同调试在VDK中进行软硬件协同的调试工作,包括软硬件的交互调试、数据传输的监控和协同数据处理等。

Synopsys系列软件安装说明

Synopsys系列软件安装说明安装Synopsys软件一共有三个:VCS、formality、magellan。

这是一套验证软件,现在我们说一下它们的安装流程:1.安装VWmare执行可执行文件。

安装无注意事项。

按照步骤安装直到完成。

2.安装REDHAT4.2运行虚拟机,在file选项下选择new下的virtual mashine。

加载REDHAT disc1.在提示加载其他的光盘时,在左下角虚拟光驱中加载接下来按照提示加载剩下的光盘镜像,加载之后记得connect(安装前提是硬盘空间最小要15G)。

这样直到安装完成。

3.安装VMware Tools安装完系统后,点击start this virtual machine开始启动系统,然后用root账号登陆,密码就是在安装系统时自己设置的密码。

在上面的工具栏菜单选择VM\install VMware Tools(目的是鼠标可以直接移动到LINUX界面外,不再需要Ctrl+Alt;设置LINUX界面的大小,同时也可以实现和windows共享文件夹),生成VmWare Tools后将VMwareTools-6.0.0-45731.tar.gz拷贝到任何目录下,然后在终端中的该目录下用tar –zxvfVMwareTools-7.8.4-126130.tar.gz命令进行解压,然后进入解压后得到的vmware-tools-distrib的目录,执行./ vmware-install.pl进行安装(一切选择默认就行)。

另一种方法:如果第一种方法不行,出现错误,就加载VM安装目录下的一个linux.iso镜像,在系统中打开cd-rom里面有个文件VMwareTools-8.1.3-203739.tar.gz就是VMware Tools压缩包。

把它拷贝到home 文件夹下,然后用tar –xvzfVMwareTools-8.1.3-203739.tar.gz 解压缩文件,然后执行在解压好的文件路径下输入命令执行./vmware-install.pl 进行安装。

synopsys+dc中文教程(共126张)

ASIC design flow

ECO Engineering change order,不属于正常的ASIC流程,一般只有在ASIC设计的后期,需要改 变网表,可利用ECO,例如(lìrú),在tape-out(sign-off)以后,遇见设计的硬件bug。采用

ECO可仅对设计的一小部分重新布线不影响chip其他部分的位置及时序,通常,修改不能 大于10%。 最新版本的DC提供由ECO compiler, 可使设计者手工修改网表,节省时间。 一些layout工具也具有ECO功能。

Static Timing Analysis

no

Time ok?

Tape out

ASIC design flow

设计举例,tap控制器,已完成代码编写及功能仿真:

Tap_controller.v Tap_bypass.v Tap_instruction.v

Tap_state.v 完成全部设计还需经过如下几个(jǐ ɡè)步骤:

write_timing –format sdf-v2.1 \ -output active_design+”.sdf”

write_constraints –format sdf –cover_design\ -output constraints.sdf

第11页,共126页。

ASIC design flow

/* If real clock, set infinite drive strength */

if (find(port, clk) == {"clk"}) { set_drive 0 clk } /* Apply default timing constraints for modules */ set_input_delay 1.2 all_inputs() -clock clk_name set_output_delay 1.5 all_outputs() -clock clk_name

Synopsys软件安装步骤及说明

更改好保存即可。

5

环境配置内容一般包含以下两个变量: SNPSLMD_LICENSE_FILE(或者LM_LICENSE_FILE)和path(PATH:该变量是bashell设定环境的变量名)。

exportSYNOPSYSPT=/eda_tools/synopsys/PT_vD-10.06-SP3-4

exportPATH=$SYNOPSYSPT/bin:$PATH

cshell环境变量.cshrc部分配置:

setenvSNPSLMD_LICENSE_FILE 27000@localhost.localdomain

附录:

bashell环境变量.bashell部分配置:

exportSNPSLMD_LICENSE_FILE=27000@localhost.localdomain

################################DC10.03#############################

exportSYNOPSYSDC=/eda_tools/synopsys/DC10.03

Fatal: At least

这是license没有正确的启动。这是有可能是因为license制作过程有问题。

在制作时需要注意license工具里面的两个文件:一为EFALicGen0.4b文件加里面的licgen.dll,该文件不能是老版本的。另一文件为EFALicGen0.4b/packs/synopsys.src,license启动不成功很有可能是因为该文件导致生成的license不能启动。

Unable to obtain feature 'Design-Analyzer ' because:

Synopsys软件安装步骤及说明

DAEMONsnpslmdSCL文件夹路径/linux/bin/snpslmd

例如:我安装SCL的目录为/eda_tools/synopsys/scl10.9,查询计算机信息如图。

故:SERVER和DAEMON行应该为(端口可根据需要填写,我这里只是示例):

SERVERlocalhost.localdomain000c2988ffc628000

7、附录……………………………………………………………..…..13

Synopsys公司的软件都不用破解文件,图形安装流程几乎一样,关键在于license的制作,安装配置都较为简单,在制作license时需要细心。

1

1)、所要安装的软件的软件包

说明:软件包一般包含三个压缩包:common,amd64,linux。可以没有amd64或者linux包,但是必须有common包,amd64是64bit软件包,linux是32bit软件包,安装时可全部安装。

附录:

bashell环境变量.bashell部分配置:

exportSNPSLMD_LICENSE_FILE=27000@localhost.localdomain

################################DC10.03#############################

exportSYNOPSYSDC=/eda_tools/synopsys/DC10.03

2、软件安装….………………………………………………………..3

3、SCL安装….………………………………………………………...5

4、制作license……………………………………………………....6

SYNOPSYS界面操作课堂(二)

有问必答——SYNOPSYS界面操作课堂(二)二、命令设计模块问题汇总1、问:确定镜头系统的光阑位置方法有哪几种?答:(1).在 Command Window 中输入 WS(2)在 Command Window 中输入 SPEC(3)打开AI模式,在 CW 中输入 STOP ? 即可。

2、问:下面红色标注的两行会在优化函数中计算吗?答:只要在 AANT 文件中的命令都会在优化时被计算。

3、问:MTF怎么控制?答:(1)一开始在 DSEARCH 的时候,加个TOSHEAR,MTF可能会很好。

(2)也可以使用 MTF 像差命令直接控制4、问:模拟退火怎么理解,每次优化后都要使用一次?答:模拟退火是一种全局优化算法。

如果每次优化时一个树枝的话,模拟退火可以帮你从一个树枝跳到另外一个树枝,找到最小值。

5.请问,怎么查看镜头基本参数?答:在CW中输入SPEC。

6、问:如何查看每一面的孔径值?答:使用CAP命令,7、问:主光线角度用什么控制?答:使用LUL命令控制主光线角度的上限。

可以使用 HELP UNI ,获得该命令的详细解释。

8、问:查看离焦 MTF 曲线?答:9、问:请问下图中是怎么控制畸变的?答:实际像高和理想像高的差值,使差值等于0 ,就是在控制畸变。

10、问:控制1视场畸变小于1.4 ,怎么设置?答:LUA 1.4 .1 0.1 COMPOSITECD1 P YA 1CD2 GIHTCD3 CONST 1=100*(CD1-CD2*CD3)/(CD2*CD3)其中 LUA 是控制绝对值的最大值。

另外,LUL 和 LLL 的含义分别是不大于和不小于。

若想控制 0.7 视场的畸变,需要对上述命令中的 CD1 行和 CD3 行进行如下修改:CD1 P YA 0.7CD3 CONST 0.711、问:如何在 SYNOPSYS 中控制 CRA ?答:例如:LUL 30 10 1 A P UNI 1LUL 28 10 1 A P UNI .9LUL 26 10 1 A P UNI .8LUL 24 10 1 A P UNI .712、问:HBAR 的含义?答:HBAR 是指Y方向上物高的占比,就是 Y 方向视场。

Synopsys系列软件安装说明

Synopsys系列软件安装说明安装Synopsys软件一共有三个:VCS、formality、magellan。

这是一套验证软件,现在我们说一下它们的安装流程:1.安装VWmare执行可执行文件。

安装无注意事项。

按照步骤安装直到完成。

2.安装REDHAT4.2运行虚拟机,在file选项下选择new下的virtual mashine。

加载REDHAT disc1.在提示加载其他的光盘时,在左下角虚拟光驱中加载接下来按照提示加载剩下的光盘镜像,加载之后记得connect(安装前提是硬盘空间最小要15G)。

这样直到安装完成。

3.安装VMware Tools安装完系统后,点击start this virtual machine开始启动系统,然后用root账号登陆,密码就是在安装系统时自己设置的密码。

在上面的工具栏菜单选择VM\install VMware Tools(目的是鼠标可以直接移动到LINUX界面外,不再需要Ctrl+Alt;设置LINUX界面的大小,同时也可以实现和windows共享文件夹),生成VmWare Tools后将VMwareTools-6.0.0-45731.tar.gz拷贝到任何目录下,然后在终端中的该目录下用tar –zxvfVMwareTools-7.8.4-126130.tar.gz命令进行解压,然后进入解压后得到的vmware-tools-distrib的目录,执行./ vmware-install.pl进行安装(一切选择默认就行)。

另一种方法:如果第一种方法不行,出现错误,就加载VM安装目录下的一个linux.iso镜像,在系统中打开cd-rom里面有个文件VMwareTools-8.1.3-203739.tar.gz就是VMware Tools压缩包。

把它拷贝到home 文件夹下,然后用tar –xvzfVMwareTools-8.1.3-203739.tar.gz 解压缩文件,然后执行在解压好的文件路径下输入命令执行./vmware-install.pl 进行安装。

虚拟机Linux系统中安装SYNOPSYS工具图解教程

虚拟机Linux系统中安装SYNOPSYS工具图解教程陈浩利2011-05-16一、安装环境虚拟机:VMware 7.1操作系统:Fedora 10installer版本:2.0scl版本:10.9.3(据网上资料,有些用了11.1版本的,兼容性不是很好,故用此版本)dc版本:syn_vC-2009.06-SP5vcs版本:vcs-mx_vD-2009.12simif版本:simif_vC-2009.06-SP1pt版本:prime time pts_vD-2009.12-SP1(以上软件EETOP上均有下载链接)二、安装步骤2.1建立共享文件夹前提:VMware和Linux系统均安装了VMware Tools,如果没有可以将VMware Tools安装文件拷贝在U 盘中(Fedora 10可以识别U盘)进行安装。

新建一个虚拟机,然后编辑虚拟机:添加共享文件夹目录:设置的文件夹Windows系统和Linux系统均可对其进行读写,将Synopsy的各种安装文件放在这个文件夹,再拷贝到Linux系统自己的分区。

2.2 拷贝安装文件2.2.1 新建文件夹进入Fedora10 操作系统,在/home/chenhaoli(不同用户有不同的用户名,Fedora10中,用户只有在该路径下具有完全读写权限)下新建文件夹:/home/chenhaoli/eda(新建)/synopsys(新建)|--installer|--tar(存放installer安装文件)|--installer_v2.0(安装路径)|--scl|--tar(存放scl安装文件)|--scl_v10.9.3(scl安装路径)|--license(存放license)|--dc|--tar(存放dc安装文件)|--dc_2009(dc_2009安装路径)|--vcs|--tar(存放dc安装文件)|--vcs_2009(vcs_2009安装路径)|--simif|--tar(存放dc安装文件)|--simif_2009(simif_2009安装路径)|--pt|--tar(存放dc安装文件)|--pt_2009(pt_2009安装路径)2.2.2 拷贝安装文件将installer_v2.0.tar.Z拷贝到/synopsys/installer/tar中;scl_v10.9.3_common.tar、scl_v10.9.3_linux.tar拷贝到/synopsys/scl/tar中;syn_vC-2009.06-SP5_common.tar、syn_vC-2009.06-SP5_linux.tar拷贝到/synopsys/dc/tar中。

Synopsys安装和license制作简易教程

Synopsys 工具安装和 license 制作简易教程Linux virtual machine “Ubuntu_16_04_for_synopsys” Info,Username: jackPassword: login123Memory: 2GBHard disk: 64GBProcessor counts: 1Internet connection mode: NAT安装过程(软件环境:VMware12pro / ubuntu16.04 / 32 位版本;64 位版本运行不成功)事先安装好 VMware12pro 和 ubuntu16.04,之后在 ubuntu 中操作设置 Ubuntu 镜像源如图 1(a)所示,将 ubuntu software->Software & Updates->Download from 设置成中国的网站,设置成功后关闭窗口,不选择更新如图 1(b)所示,在终端中键入命令$ sudo apt-get update 进行更新(a) ubuntu software (b) apt update图 1 ubuntu 镜像源更新安装必要工具键入命令$ sudo apt-get install vim csh dconf-editor libjpeg62-dev设置 Ubuntu 显示中文键入命令$ dconf-editor如图 2 所示,将org->gnome->gedit->preferences->encodings->candidate-encodings 的值设置成['CURRENT', 'ISO-8859-15', 'GB18030', 'UTF-8', 'UTF-16']图 2 dconf-editor键入命令ifconfig,确定网卡名是否为eth0,否则按照下列步骤更改成eth0 键入命令$ su root键入命令# vim /etc/default/grub,在GRUB_CMDLINE_LINUX 中添加net.ifnames=0biosdevname=0,新GRUB_CMDLINE_LINUX 如下GRUB_CMDLINE_LINUX="find_preseed=/preseed.cfg auto noprompt priority=critical locale=en_USnet.ifnames=0 biosdevname=0"键入命令# update-grub键入命令# vim /etc/network/interfaces,添加auto eth0iface eth0 inet dhcp重启系统新建synopsys 工具安装目录,并拷贝安装源tar 压缩包到sources 文件夹下,如图3 所示;同时将installer_v3.2.tar 解压到文件夹installer 中图3 安装目录树以安装Synopsys design compiler, dc 为例,而scl、vcs 和pt 的安装同dc(注:synopsys的其他工具的安装过程都相同)键入命令$ ~/eda/synopsys/installer/setup.sh 开启图形安装界面,如图4(a)所示选择安装源路径为/home/jack/eda/synopsys/sources,如图4(b)所示选择安装syn,即为dc,如图4(c)所示选择安装路径为/home/jack/eda/synopsys/dc,如图4(d)所示其他未说明步骤按默认处理(a) 启动界面(b) 选择安装源路径(c) 选择安装DC (d) 选择安装路径图4 DC 安装过程制作license(注:各种synopsys license 制作包大同小异)键入命令$ ifconfig –a,记录eth0 的MAC 地址在Windows(不一定是本机,也可以是其他电脑)中进行操作,关掉一切杀毒软件运行license 制作包中的LicGen.exe点开Open 按钮,选择synopsys.lpd,如图5(a)所示如图5(b)所示在两处Host ID->Custom 键入eth0 的MAC 地址,点击Generate 生成的内容Save 成synopsys.dat将生成的synopsys.dat 文件保存到Synopsys SSS Feature Keygen 文件夹中打开cmd,进入Synopsys SSS Feature Keygen 目录后运行sssverify.exe synopsys.dat,复制生成的SECRET DATA,如图5(c)和图5(d)打开Synopsys SSS Feature Keygen 文件夹中的KeyGen.exe,如图5(e)所示,键入SECRET DATA 和eth0 的MAC 地址,生成license.dat如图5(f)所示,将license.dat 中的FEATURE SSS 内容粘贴到synopsys.dat 中,如果synopsys.dat 中存在则替换如图5(g)所示,在相应位置修改localhost 和snpslmd path;其中在ubuntu 中键入命令$ hostname 可获取localhost,而snpslmd 后面的链接地址设置成绝对路径~/eda/synopsys/scl/linux/bin/snpslmd(附录A 为synopsys.dat 更改后的部分内容)(a) 选择Synopsys.lpd (b) 生成synopsys.dat(c) 验证synopsys.dat(d) 生成SECRET DATA(e) 生成license.dat(f) license.dat(g) 修改后的synopsys.dat图5 license 制作过程验证license将制作好的license 拷贝到~/eda/synopsys/license 目录下,同时终端进来该目录如图6 所示,键入命令$ ~/eda/synopsys/scl/linux/bin/sssverify synopsys.dat,出现PASSED 表示OK图6 验证license环境变量配置键入命令$ vim ~/.bashrc,添加如图7 所示的环境变量,详见附件B图7 环境变量设置运行每次运行前先键入命令$ lmli2,启动scl,如图8(a)所示键入命令$ dc,启动dc 的图形界面,如图8(b)所示键入命令$ dve,启动vcs 的图形界面,如图8(c)所示键入命令$ pt,启动pt 的图形界面,如图8(d)所示(a) 启动scl(b) dc 的图形界面(c) vcs 的图形界面(d) pt 的图形界面(缺图)图8 运行界面遇到的问题记录1. 如在终端中显示缺什么,就试试安装什么,$ sudo apt-get install *2. lmgrd 找不到$ sudo apt install lsb-core3. grep: /etc/redhat-release: No such file or directory$ sudo > /etc/redhat-release4. /bin/sh: 0: Illegal option –h$ sudo mv /bin/dash /bin/dash~$ sudo ln -s /bin/bash /bin/dash附录ASERVER ubuntu 000c2960189e 27000DAEMON snpslmd /home/jack/eda/synopsys/scl/linux/bin/snpslmdFEATURE SSS snpslmd 1.0 31-dec-2020 uncounted 0EFAB50928B9EDBDB856 \ VENDOR_STRING="69656 d1d88 34cc3 35f9b 39561 08bdd 779a4 23589 \aa9a3 196" HOSTID=000c2960189e ISSUER="Team ZWT 2006" \NOTICE="Licensed to mammoth//ZWT 2006 [PLEASE DO NOT DELETE THIS \ SSS KEY]" SN=RK:1978-0:001224:0 START=1-jan-2006附录B# 添加以下环境变量到~/.bashrc# 适用于32 位,64 位只需将链接中linux 替换成amd64# (以下必选)# synopsysexport SYNOPSYS_HOME=/home/jack/eda/synopsys# licenseexport LM_LICENSE_FILE=$SYNOPSYS_HOME/license/sysnopsys.datexport SNPSLMD_LICENSE_FILE=27000@localhost.localdomain# sclexport SCL_HOME=$SYNOPSYS_HOME/sclexport PATH=$PATH:$SCL_HOME/linux/binalias lmli2="lmgrd -c $LM_LICENSE_FILE -l ~/syn_lic.log"# (以下可选)# vcsexport VCS_HOME=$SYNOPSYS_HOME/vcsexport PATH=$PATH:$VCS_HOME/bin# dcexport DC_HOME=$SYNOPSYS_HOME/dcexport PATH=$PATH:$DC_HOME/binalias dc=design_visionalias dcs=dc_shell# ptexport PT_HOME=$SYNOPSYS_HOME/ptexport PATH=$PATH:$PT_HOME/binalias pt=primetimealias pts=pt_shell# simifexport SIMIF_HOME=$SYNOPSYS_HOME/simif export PATH=$PATH:$SIMIF_HOME/bin# hspiceexport HSPICE_HOME=$SYNOPSYS_HOME/hspice export PATH=$PATH:$HSPICE_HOME/hspice/bin# sxexport SX_HOME=$SYNOPSYS_HOME/sxexport PATH=$PATH:$SX_HOME/binalias sx=sx2007# iccexport ICC_HOME=$SYNOPSYS_HOME/iccexport PATH=$PATH:$ICC_HOME/binalias iccs=icc_shell# herculesexport HERCULES_HOME=$SYNOPSYS_HOME/hercules export PATH=$PATH:$HERCULES_HOME/bin# starrcexport STARRC_HOME=$SYNOPSYS_HOME/starrc export PATH=$PATH:$STARRC_HOME/bin。

synopsysDC10.03图文安装配置详解

synopsysDC10.03图⽂安装配置详解喾林原创Synopsys DC10.03安装配置1、需准备安装包:1)、Synopsys DC(design compiler)安装包2)、SCL 安装包(注:此包为synopsys license 管理)。

3)、Synopsys 图像安装⼯具:installer2.0及以上均可。

(注:图形安装操作简单,不易出错,故采⽤图形安装界⾯)4)、Synopsys license 制作⼯具( EFA LicGen 0.4b 和Synopsys SSS Feature Keygen )。

2、开始安装DC : 1)、启动图形安装界⾯于linux 系统下解压installer2.0包(在windows 下解压⽂件易损坏)。

解压后运⾏setup.sh 得如图(⼀)所⽰界⾯。

图(⼀)喾林原创点击“start ”有如图(⼆)所⽰界⾯开始安装。

在“Source ”栏选中DC 安装⽂件所在上层⽬录。

“Done ”后“Next ”(此次“Next ”时间较长,耐⼼等待)。

图(⼆)之后可⼀直“NEXT ”到如图(三)所⽰。

图(三)在该界⾯勾选linux选项即可,继续下⼀步到如图(四)所⽰。

选择安装路径后继续下⼀步直到结束。

喾林原创图(四)⾄此DC安装结束。

3、开始安装SCL:此安装与DC安装步骤⼀直,⼏乎没有差别,唯⼀不同的就是安装路径不同。

4、license的制作:License的制作是在windows下制作的。

1)、打开EFA LicGen 0.4b⽂件夹运⾏LicGen.exe程序出现如图(五)所⽰界⾯。

喾林原创图(五)点击“OPEN”选择Synopsys.lpd⽂件,“打开”。

回到图(五)所⽰界⾯。

勾选上Custon、Use Daemon及最后⼀个Custon。

喾林原创在两个“Custon ”后输⼊Linux 系统的MAC 。

注:Linux MAC 获取命令。

A :lmhostid 下图(六)红线处即为 MAC 。

SYNOPSYS光学设计软件课程十五:开发一组实际透镜

SYNOPSYS光学设计软件课程⼗五:开发⼀组实际透镜在第14课中,我们设计了⼀个7⽚式透镜,从平⾯平⾏表⾯开始,并且符合设计要求,使⽤ARGLASS功能⾃动编⽬镜玻璃类型。

本课程将介绍⼀些有⽤的功能。

使它成为真正的实⽤软件,我们将展⽰设计师如何遵循各种线索以获得解决⽅案,以及为何不是所有⽅案都能带来成功,这⼀点也很重要:可以从失败中吸取经验。

当你作为镜⽚设计师提升⾃⼰的技能时,你会遇到很多⿇烦,但不应该⽓馁。

坚持不懈,通常可以找到成功的设计。

我们将以两种⽅式完成本课程;⾸先在DSEARCH的帮助下使⽤其他⼯具。

然后,在第17课中,我们展⽰了另⼀种实际上更快更容易的⽅法。

您应该了解这两种⽅法中使⽤的所有⼯具。

我们将⾸先使⽤DSEARCH找到⼀个好的初始结构。

这是输⼊:CORE 16DSEARCH 6 QUIETSYSTEMID DSEARCH SAMPLEOBB 0 20 12.7WAVL 0.6563 0.5876 0.4861UNITS MMENDGOALSELEMENTS 7FNUM 3.575BACK 50 .01STOP MIDDLESTOP FREERT 0.5FOV 0.0 0.75 1.0 0.0 0.0FWT 5.0 3.0 3DELAY 999RSTART 900THSTART 7ASTART 15NPASS 66ANNEAL 200 20 QCOLORS 3SNAPSHOT 10QUICK 44 66ENDSPECIAL PANTENDSPECIAL AANTLUL 150 1 1 A TOTLENDGO我们运⾏这个程序,并且返回的最佳镜头⾮常好。

我们使⽤⽂件DSEARCH_OPT进⾏优化和模拟退⽕,该⽂件位于新的编辑器窗⼝中。

假设我们希望镜头在从⼀⽶到⽆限远的物距范围内⼯作。

有两种⽅法可以实现这⼀要求:使⽤多重结构,这⾮常灵活但是很复杂,或者通过声明这是⼀个物距变焦的变焦镜头。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

以.cshrc 及用户根目录下的.synopsys_vss.setup .synopsys_dc.setup 已经配置为前提)1.创建工作目录;

2.编写vhdl源程序;

3.编写.synopsys_vss.setup 和.synopsys_dc.setup文件;

4.编译vhdl源程序;

5.运行vhdldbx 仿真器;

6.运行synopsys的综合器;

7.完成综合后的门级仿真;

以一个一位加法器为例,进行具体说明(用户界面为CDE):

1)创建adder 目录:

可以在资源管理器中完成,也可以在unix环境下完成:mkdir adder;

2)在adder目录下创建work目录;

3)编写.synopsys_vss.setup文件并存入adder目录;.synopsys_vss.setup的内容如下:WORK >DEFAULT

DEFAULT:work

TIMEBASE = NS

4)编写一位加法器的源程序(adder1.vhd)并存入adder目录下:

library ieee;

use ieee.std_logic_1164.all;

entity adder1 is

port(din1 : in std_logic;

din2 : in std_logic;

cin : in std_logic;

dout: out std_logic;

cout: out std_logic);

end adder1;

architecture rtl of adder1 is

begin

dout <= din1 xor din2 xor cin;

cout <= (din1 and din2) or (cin and (din1 xor din2));

end rtl;

5)编写一位加法器的测试基准(即test_bench)并存入adder目录下:(tb_adder1.vhd)library ieee;

use ieee.std_logic_1164.all;

entity tb_adder1 is

end tb_adder1;

architecture rtl of tb_adder1 is

component adder1 is

port(din1 : in std_logic;

din2 : in std_logic;

cin : in std_logic;

dout: out std_logic;

cout: out std_logic);

end component ;

signal din1 : std_logic:='1';

signal din2 : std_logic:='0';

signal cin : std_logic;

signal dout : std_logic;

signal cout : std_logic;

for all : adder1 use entity work.adder1(rtl);

begin

u1 : adder1 port map(din1,din2,cin,dout,cout);

din1 <= not din1 after 10 ns;

din2 <= not din2 after 20 ns;

cin <= '0','1' after 40 ns;

end rtl;

configuration test_adder1 of tb_adder1 is

for rtl

end for;

end test_adder1;

6)编译源程序:

有两种方法可供使用:

A:使用命令vhdlan adder1.vhd tb_adder1.vhd

B:用批处理文件。

如analyze.sh

vhdlan –noevent \

adder1.vhd \

tb_adder1.vhd

保存文件analyze.sh,并将其属性(property)改为可执行。

方法如下:可以在文件管理器中修改,也可以用unix命令:chmod 755 analyze.sh

7)模拟(仿真):

使用仿真命令:vhdldbx &

注:在仿真器中常用的命令如下:trace,step,next,monitor,run,list,lv (-v),quit等;具体用法参考相应的文档资料。

8)综合:

使用命令:design_analyzer &

注:(1)综合器中常用的命令如下:read,clock_specify,design_enviroment,optimization 等;具体用法参考相应的文档资料。

(2)如果有自己的工艺库,则应将根目录下的.synopsys_dc.setup 修改为:

search path :

link library =

target library =

symbol library =

9)保存文件:

将文件保存为vhdl格式,如adder_syn.vhd

10)修改原来的testbench:

将tb_adder1.vhd 中的for all : adder1 use entity work.adder1(rtl);改为:for all : adder1 use entity work.adder(syn_rtl);(syn_rtl为adder_syn.vhd中,adder1的结构体名)。

11)编译:与第6步相同。

12)仿真:与第7步相同。

注:若须打印波形,则应将其存为.ps文件(如:wave.ps);然后使用打印命令,选择打印选项为文件形式,并写入文件名(如:wave.ps)。