片上总线Wishbone 学习(二)Wishbone互联的类型

三种片上总线的分析与比较

三种常用SoC片上总线的分析与比较作者:李瑞张春元罗莉来源:国防科技大学发表时间:2006-02-22内容摘要随着集成电路设计技术的发展,在片上系统(SoC)中,越来越多地使用各种功能IP核部件构成系统。

总线是这些部件连接的主要方式,目前有数家公司和组织研发了多种面向SoC设计的总线系统。

本文介绍SoC中常用的三种片上总线AMBA、Wishbone和Avalon,分析和比较其特性,并针对其不同的特点阐述其使用范围。

引言 嵌入式系统是当今计算机工业发展的一个热点。

随着超大规模集成电路的迅速发展,半导体工业进入深亚微米时代,器件特征尺寸越来越小,芯片规模越来越大,可以在单芯片上集成上百万到数亿只晶体管。

如此密集的集成度使我们现在能够在一小块芯片上把以前由CPU和若干I/O接口等数块芯片实现的功能集成起来,由单片集成电路构成功能强大的、完整的系统,这就是我们通常所说的片上系统SoC (System on Chip)。

由于功能完整,SoC逐渐成为嵌入式系统发展的主流。

相比板上系统,具有许多优点:SoC ①充分利用IP技术,减少产品设计复杂性和开发成本,缩短产品开发的时间; ②单芯片集成电路可以有效地降低系统功耗; ③减少芯片对外引脚数,简化系统加工的复杂性; ④减少外围驱动接口单元及电路板之间的信号传递,加快了数据传输和处理的速度; ⑤内嵌的线路可以减少甚至避免电路板信号传送时所造成的系统信号串扰。

SoC的设计过程中,最具特色的是IP复用技术。

即选择所需功能的IP(给出IP定义)核,集成到一个芯片中用。

由于IP核的设计千差万别,IP核的连接就成为构造SoC的关键。

片上总线(On-Chip Bus,OCB)是实现SoC中IP核连接最常见的技术手段,它以总线方式实现IP核之间数据通信。

与板上总线不同,片上总线不用驱动底板上的信号和连接器,使用更简单,速度更快。

一个片上总线规范一般需要定义各个模块之间初始化、仲裁、请求传输、响应、发送接收等过程中驱动、时序、策略等关系。

第四章wishbone寄存器反馈总线周期

翻译者:huanhuan Email:********************第一章简介WISHBONE1片上系统(SoC)轻量级的IP核互联结构是使用半导体IP核进行设计的一种灵活的设计方法。

它的目的在于缓解片上系统集成的问题已促进设计的可重用用性。

这将通过在IP核之间建立一个共同的接口来完成。

这将提高系统的可移植性与稳定性,其结果将是使最终用户的产品能更快的上市。

以前,IP核使用非标准的互联方案,以致在系统集成式非常难。

这就需要创建一个依赖与用户的逻辑将核之间连在一起。

采用标准的互联方案,最终用户可以将IP核更快更容易的集成到系统中。

本说明文档可同时适用于软核,固核和硬核设计。

因为固核和硬核通常也是由软核产生的,所以本文档是以软核的立场来写的。

本说明文档对开发工具和目标硬件没有特定要求,并且兼容几乎所有的综合工具。

然而,本文档中列出的例子却是采用VHDL硬件描述语言描述的。

这仅仅是考虑方便读者,使用其它硬件描述语言的读者(如Verilog®)能够很容易看懂理解。

基于原理图的设计工具同样也是支持的。

WISHBONE互联技术是针对通用接口设计的。

严格意义上讲,它定义了IP核之间的数据交换标准,但是它没有去规范IP和的特殊应用功能。

WISHBONE总线结构设计师是受到三个因素的强烈影响:第一,存在一个对优秀的、可靠的片上系统互联技术解决方案的需求;第二,需要一种共同的接口规范,以缓解在基于结构化设计的大型团队项目中遇到的问题;第三,传统的微型计算机总线系统互连解决方案如:PCI 总线和VME总线,给他们以深刻的印象。

事实上,WISHBONE总线架构与微型计算机总线结构有一下相似之处:(a):提供一个灵活的系统集成解决方案,可以很容易的根据特定应用进行调整;(b):提供多种总线周期及多种数据路径宽度已解决各种系统问题;(c):允许产品在多个供应商之间完成设计(由此降低了成本提高的产品性能和质量)。

Wishbone标准

本文详细介绍了Wishbone标准,主要参考了Wishbone标准版本的核心内容,感兴趣的读者可去下载英文原文。

一、片上总线技术综述随着超大规模集成电路的迅速发展,半导体工业进入深亚微米时代,器件特征尺寸越来越小,芯片规模越来越大,可以在单芯片上集成上百万到数亿只晶体管。

如此密集的集成度使我们现在能够在一小块芯片上把以前由CPU和外设等数块芯片实现的功能集成起来,由单片集成电路构成功能强大的、完整的系统,这就是我们通常所说的片上系统。

IP复用是片上系统时代的核心技术之一。

由于IP核的设计千差万别,它们要能够直接连接,就要遵守相同的接口标准。

在片上系统中,处理器核和所有外设通过共享总线互通互联,因此这些IP核必须遵守相同的总线规范。

总线规范定义的是IP核之间的通用接口,因此它定义了一套标准的信号和总线周期,以连接不同的模块,而不是试图去规范IP核的功能和接口如何实现。

一个片上总线规范一般需要定义各个模块之间初始化、仲裁、请求传输、响应、发送接收等过程中驱动、时序、策略等关系。

芯片与电路板的资源和环境的不同,导致片上总线与板上总线存在若干明显差异,包括:①片上总线多采用单向信号线,而板上总线多采用三态信号。

片上三态总线无论在功耗、速度、可测性上都存在很大缺陷,而且一旦出现多驱动情况便会损毁芯片(比如若应该输出"Z"的信号实际输出为"1",而另有一个信号输出为"0",就形成一个低电阻通路,导致局部电流过大,热量难以及时释放,从而增加芯片功耗和大大降低芯片寿命)。

由于片上布线资源较为丰富,因此片上总线多采用单向信号线。

由于电路板上布线资源较为昂贵,因此板上总线多采用三态总线,但是由于三态总线的功耗问题和速度限制,目前板上总线也在向串行和非三态方向发展,如USB和PCI Express。

②片上总线比板上总线更加简单灵活。

首先片上总线结构要简单,这样可以占用较少的逻辑单元;其次时序要简单,以利于提高总线的速度;第三接口要简单,如此可减少与IP核连接的复杂度。

WISHBONE总线解析

WISHBONE总线解析2010-01-31 12:47WISHBONE为我们提供了灵活的连接结构,使我们能非常容易的定制自己的所需用途。

它通过提供标准的数据交换协议,使用户非常方便进行TEAMWORK,把系统组件化,增加了模块的重用性。

节省了二次开发的时间。

WISHBONE地址和数据位都是32位(如果小于32位也可以这行通信),最多可以连接8个主设备,16个从设备,当多个主设备申请控制时,通过仲裁机制决定什么时候哪个主设备能访问共享总线。

WISHBONE具有灵活的可变性连接方式,允许系统通过四种不同的方式实现IP CORES之间的互联:一。

点到点连接方式(point-to-point interconnection)这是IP CORES之间最简单的连接方式,只需要一主一从两个IP CORES 之间进行数据通信,例如,主设备可以是微处理器IP CORE ,从设备可以使串口的I/O PORT.二。

数据流连接方式(data flow interconnection)这种连接方式用于数据以时序的方式进行处理。

一些时候,这种方式可用作流水线作业。

比如下图三个IP CORES都是实现浮点运算,假设它们工作的时间都相同,这样三个IP CORES互联在一起,可以实现高速的类似并行化的时序操作,使处理数据的时间节省三分之二。

三。

共享总线的连接方式(share bus interconnection)这种方式通常用于两个或以上主设备和一个或以上从设备之间的互联,仲裁机制决定什么时候哪个主设备能够访问总线,这种连接方式的主要优点是结构紧凑,能够用较少的逻辑资源去实现相关结构。

缺点是:每次只能有一个主设备访问总线,其他的主设备在总线忙时只能处于等待状态,降低了数据传输的速度。

这种共享总线的连接方式我们可以在一些标准的总线中看到,例如PCI,VMEbus。

四,交叉开关连接方式(crossbar switch interconnection)这种连接方式主要用于两个或以上主设备和两个或以上从设备之间进行数据传递。

采用WISHBONE总线有效地解决IP核可移植性、设计复用问题

采用WISHBONE总线有效地解决IP核可移植性、设计复用问题清华大学嵌入式微处理器芯片设计为国家重点863项目,单芯片多处理器设计为项目的一个延伸。

单芯片多处理器是提高处理器性能的有效途径,具有低耦合度、粗粒度并行性的主要特点。

清华大学己成功开发出具有自主知识产权的MIPS4Kc架构的32位微处理器一THUMP107。

该处理器具有内核性能高、面积小、功耗低的优点。

使其经过裁减非常适合作为单芯片多处理器的内核。

本次单芯片多处理器的设计将两个ThUmPI07内核集成在一个芯片上,两个内核处于完全对等地位,实现进程级的粗粒度并行。

由于己经具有可以利用的内核,开发的重点就集中在高速缓存(CaChe)一致性的实现上。

芯片采用了基于内部总线写更新监听的高速缓存一致性协议,具有控制逻辑简单、可扩展性好的特点。

内部总线采用适合片上系统通信、高可配置性的W1SHBONE总线。

使用该片上总线有效地解决了IP核可移植性、设计复用的问题。

1、WISHBONE总线WISHBONE最先由Si1icore公司提出,现在被移交给OPenCoreS组织维护。

由于其开放性,现在已有不少用户群体。

特别是一些免费的IP核,大多数都采用W1SH-BONE标准。

该总线结构具有公用的按旦规范方便结构化设计,有效地解决了IP核可移植性、设计复用的问题。

WISHBON耳总线为主导住内核提供了可配置的互连方式,能够使各种内核互连起来形成片上系统;WISH-BONE总线具有很强的兼容性,提高了设计的可重用性;W1SHBONE总线的接口独立于半导体技术,其互连方式既可以支持EE或设备,也可以支持以IC设备;WISHBONE总线协议简单、易懂。

WISHBONE总线是一种主/从接口架构的总线技术,如果具有有效的仲裁机制,总线系统可以支持多个ne/从接口;W1SHBoNE总线的可配置性主要体现在支持点到点、共享总线、数据流、交叉开关型的互连方式;WISHBONE总线协议既包含了一种容易使用、可靠性高、易测试、所有总线事务都可以在一个时周期内协同的同步传输协议,也包含了标准时钟周期的异步传输协议;WISHBONE 总线的同步传输协议可以工作在一个大范围的时钟频率上。

基于WISHBONE总线的FLASH闪存接口设计

摘要:本文简要介绍了AMD公司AM29LV160D芯片的特点,并对Wishbone总线作了简单的介绍,详细说明了Flash memory 与Wishbone 总线的硬件接口设计及部分Verilog HDL程序源代码。

关键词:闪存;接口;Wishbone;FPGA引言随着半导体工艺技术的发展,IC设计者已能将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,即SoC芯片。

对片上系统(SoC)数据记录需要低功耗、大容量、可快速重复擦写的存储器。

常用的介质主要有:动态存储器(DRAM)、静态存储器(SRAM)和闪速存储器(Flash Memory)。

DRAM容量大,但需要不断刷新才能保持数据,会占用微处理器时间,同时增加了功耗;SRAM虽然不需要动态刷新,但价格太贵,并且断电后跟DRAM一样数据都无法保存。

Flash MEMORY是一种兼有紫外线擦除EPROM和电可擦除可编程只读存储器(EEPROM)两者优点的新型非易失存储器。

由于它可在线进行电可擦除和编程,芯片每区可独立擦写至少1000,000次以上,因而对于需周期性地修改被存储的代码和数据表的应用场合,以及作为一种高密度的、非易失的数据存储介质Flash是理想的器件选择。

在我们设计的系统中,处理器是Openrisc1200,所用的Flash是AMD与富士公司的Am29LV160D芯片。

利用FPGA实现接口,由于Openrisc1200(OR1200)采用Wishbone总线,所以本设计的接口具有可移植性。

Am29LV160D芯片特点Am29LV160D是一种仅需采用3.0V电源进行读写的闪存。

该器件提供了70ns、90ns、120ns读取时间,无需高速微处理器插入等待状态进行速度匹配。

为了消除总线竞争,芯片引入了片选使能(CE#),写使能(WE#)和输出使能(OE#)控制端口。

芯片采用分块结构,非常适用于要求高密度的代码或数据存储的低功耗系统。

Wishbone简介(完整板)

Wishbone简介一、背景介绍随着以IP核复用为基础的SoC设计技术的发展,工业界及研究组织积极从事相关IP 互联标准方案的制定工作,从目前的研究和发展看,影响力较大的有IBM公司的CoreConnect、ARM公司的AMBA 和Silicore Corp公司的Wishbone。

Wishbone现在由OpenCores组织维护,是OpenCores建议的片上总线标准,目前已有大量开源的IP Core使用Wishbone总线作为互连标准。

Wishbone总线只定义了信号和信号间的时序关系,因此可用于软核、固核和硬核,对硬件描述语言、综合工具和实现手段没有特殊要求。

与其他片上总线相比,Wishbone总线结构简单,互连灵活,对用户定制的支持良好,与其他片上总线的互连也较简单,因此随着SOPC技术的发展,有着广泛应用前景。

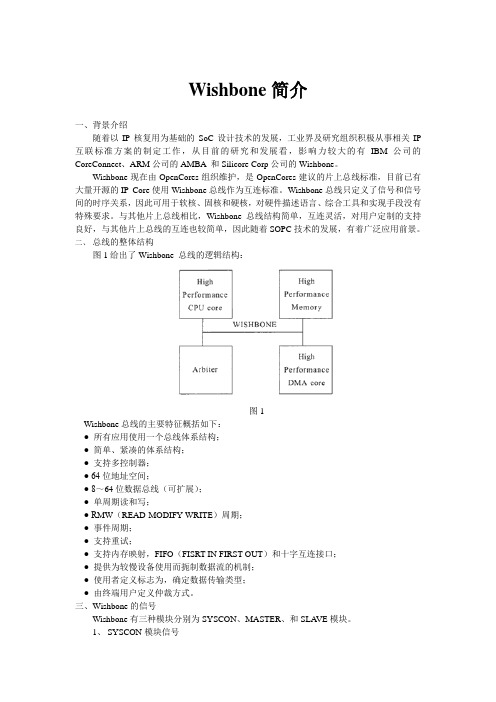

二、总线的整体结构图1给出了Wishbone 总线的逻辑结构:图1Wishbone总线的主要特征概括如下:● 所有应用使用一个总线体系结构;● 简单、紧凑的体系结构;● 支持多控制器;● 64位地址空间;● 8~64位数据总线(可扩展);● 单周期读和写;● R MW(READ-MODIFY-WRITE)周期;● 事件周期;● 支持重试;● 支持内存映射,FIFO(FISRT IN FIRST OUT)和十字互连接口;● 提供为较慢设备使用而扼制数据流的机制;● 使用者定义标志为,确定数据传输类型;● 由终端用户定义仲裁方式。

三、Wishbone的信号Wishbone有三种模块分别为SYSCON、MASTER、和SLA VE模块。

1、SYSCON模块信号CLK_O:系统时钟的输出,同步了Wishbone连接的所有模块,INTERCON模块将CLK_O 输出与MASTER和SLA VE的CLK_I信号相连。

RST_O:系统的复位输出,它强制将与Wishbone相连的模块重启,将自启动的状态机复位到初始状态,INTERCON模块将RST_O输出与MASTER和SLA VE的RST_I相连2、MASTER和SLA VE共有的信号CLK_I:模块的系统时钟输入DAT_I():数据输入,最大位宽到64位DAT_O():数据输出,最大位宽64位RST_I():模块的复位输入TGD_I():在MASTER和SLA VE接口中使用,它包含了与数据输入DAT_I()相关的信息,STB_I标记其有效TGD_O():同上,包含了与数据输出DAT_O()相关的信息,STB_O标记其有效3、MASTER模块的信号ACK_I:确认信号输入,当有效时表示一个正常的总线周期的结束ADR_O():二进制地址输出,如果它是以字节为粒度数的,当数据总线是32位时的它的最大地址数就是ADR_O(n..2),n最大为63。

基于片内WISHBONE总线的高速缓存一致性实现

*

欢迎邮购本刊 %&&$’%&&& 年光盘版 ! 每套 %"" 元

!电子技术应用 " !""# 年第 $ 期

计算机应用

表 & 协议状态

状 态 干 净 独 占 !’ " 干 净 修 改 ! () " 共 享 已 修 改 ! (* " 说 明 只有一个缓存有这一存储块的拷贝 #并且还没有被修改 !主存状态也有效"$ 潜在的两个或多个缓冲有这一存储块 #主存不一定是最新的 $ 潜 在的两个或多个缓冲有这一存储块 # 主存不是最新的 $ 该块 在 被 替 换 时 #要 更 新 主 存 !写 回 "$ 一 个 存 储 块 在 一 定 时 间 内 只能在一个缓冲内共享已修改状态$ 独 占 已 修 改 !* " 存储块的内容已经被修改#并且只在该存储块里#发生替换 需要更新主存的内容$

2+,@B 上 的 数 据 % 而 后 G 个 时 钟 周 期 内 # 每 个 时 钟 周 期 +2-@= 数 据 加 # # 2+,@B 上 的 数 据 根 据 地 址 相 应 地 变 化 # 在 第 G 个 数 据 传 输 的 时 钟 周 期 ),B@= 变 为 &&& # 告

诉远端从接口这是最后一个传 输时钟 周期 #下一个 时钟 周期将完成这个总线事务%最后一个时钟周期主接口撤 销 )1)@= 信 号 # 结 束 片 内 总 线 周 期 $ 片内块 传输 时序见 图 !$

(* # 基 于 写 更 新 协 议 # 由 本 地 主 接 口 通 过 片 内 总

线向远端数据高速缓存发出写请求# 远端从接口 通过片内总线应答请求$如果应答有该单元数据# 则通过一个单字写总线事务更新远端数据高速缓 存 单 元 %如 果 没 有 #结 束 片 内 总 线 周 期 $ 替换&实现写回协议#只有 被替 换出的 单元 状 态 为 (* 或 * 状 态 # 才 通 过 外 部 总 线 更 新 主 存 #其他 情况抛 弃即 可$ 注 意 & 完 成 上 述 操 作 后 要 根 据 2-+<=4 协 议 # 更 新本 地和远 端 2)!"# 单 元的 相关状 态 $

一种基于WISHBONE总线设计的功能验证平台的搭建方法[发明专利]

![一种基于WISHBONE总线设计的功能验证平台的搭建方法[发明专利]](https://img.taocdn.com/s3/m/7ec3d5e952ea551811a687c0.png)

专利名称:一种基于WISHBONE总线设计的功能验证平台的搭建方法

专利类型:发明专利

发明人:赵鑫鑫,姜凯,李朋

申请号:CN201510482827.5

申请日:20150803

公开号:CN105069227A

公开日:

20151118

专利内容由知识产权出版社提供

摘要:本发明涉及集成电路设计验证技术领域,尤其是涉及基于Wishbone总线设计的内部寄存器和RAM模块的验证方法和验证平台设计,具体是涉及一种基于WISHBONE总线设计的功能验证平台的搭建方法。

本方法首先根据被测设计内部寄存器和ram模块的参数建立寄存器信息文档;然后,设计自动脚本,用该自动脚本根据寄存器信息文档生成测试向量,若相关寄存器有特殊的数据处理过程,在测试向量中进行相应的调整;然后,设计验证平台的输出信息控制脚本和验证平台的运行脚本;最后,调试运行测试向量,完成验证过程。

通过该方法搭建的验证平台可以完成基于Wishbone 总线的设计中的寄存器和ram模块的测试,具有开发周期短、通用性强和自动化程度高的特点,可以大幅度提高芯片验证效率。

申请人:浪潮集团有限公司

地址:250101 山东省济南市高新区浪潮路1036号

国籍:CN

代理机构:济南信达专利事务所有限公司

代理人:姜明

更多信息请下载全文后查看。

四种片上总线分析比较

AMBA

AMBA

• AMBA AHB适用于高性能和高时钟频率的系统模块,主要 用于高性能和高吞吐量设备之间的连接,如CPU、片上存 储器、DMA、DSP等,其特点如下:

– – – – – – – – 支持多个总线主设备 支持突发、分裂、流水等数据传输方式 单周期总线主设备控制权转换 32~128位数据总线位宽 访问保护机制 数据突发传输最大为16段 地址空间32位 支持字节、半字和字传输

高性能嵌入式系统,小型 嵌入式系统

对IP核没特殊要求,而且 许多免费IP核可在网上下 载 完全免费

用于Altera Nios软核的系 统中

Altera公司建立了AMPP组 织,提供丰富的IP核 Altera所有,需要授权协 议

CoreConnect

• IBM公司设计提出的一套完备技术 • CoreConnect总线提供了三种基本类型连接功能块:

– PLB(Processor Local Bus)处理器内部总线 – OPB(On-Chip Peripheral Bus)片上外设总线 – DCR(Device Control Register)设备控制寄存器总线

CoreConnect

• PLB为总线传输的主要发出者和接受者之间提供高带宽、低延迟的连 接,主要特征有:

– – – – – – – – – – – – – – – 高性能处理器内部总线 交叠的读和写功能(最快每周期两次) 支持分段传输 地址流水(减少延迟) 读和写分开 32~64位数据总线 32位地址空间 支持16~64字节突发传输 支持字节使能 支持仲裁、REQ、GNT和LOCK 延迟和隐藏仲裁 4级仲裁优先权 特殊DMA模式,如快速的从内存到内存 地址和数据状态扼制 延迟计数器

Wishbone

soc复习题答案

Soc复习题1、集成电路的发展分哪几个阶段?2、SOC的构成及其优势是什么?构成:在目前的集成电路设计理念中,IP是构成soc的基本单元。

所谓IP可以理解为是满足特定规范,并能在设计中复用的功能模块,又称IP核(IPCcore)。

从IP的角度出发,SOC可以定义为基于IP模块的复用技术,以嵌入式系统为核心,把整个系统集成在单个(或少数几个)芯片上,从而完成整个系统功能的复杂的集成电路。

目前的SOC集成了诸如处理器、存储器及输入/输出端口等多种IP。

SOC的优势:与传统设计相比较,由于SOC将整个系统集成在一个芯片上,使得产品的性能大为提高,体积显著缩小。

此外.SOC适用于更复杂的系统,具有更低的设计成本和更高的可靠性,因此具有广阔的应用前景。

1.SOC可以实现更为复杂的系统。

2.SOC具有较低的设计成本。

3.SOC具有更高的可取性。

4.缩短产品设计时间。

5.减少产品反复的次数。

6.可以满足更小尺寸的设计要求。

7.可达到低功耗的设计要求3、soc设计中验证分为哪几类?1动态验证2静态验证比较动态验证和静态验证,各有优势和不足。

动态仿真主要是模拟电路的功能行为,必须给出适当的激励信号,然而很难选择激励来达到覆盖电路所有功能的目的。

同时动态仿真很耗费时间。

静态验证是针对模拟电路所有的工作环境,检查电路是否满足正常的性能指标,此类验证只限于数字逻辑电路,其准确性低于动态仿真,偶尔还会提供错误信息。

4、SOC中物理验证的分类如何?各自完成的功能是什么?1、设计规则检查就是由芯片代工厂提供的反映工艺水平及版图设计的必须满足的一些几何规则。

2.电气规则检查是检查版图中存在的一些违反基本电气规则的点。

这里的电气规则主要是指,电路开路、短路及浮动点等。

3、版图电路图同一性比较当完成版图设计之后,有必要进行Lvs,用来确认版图和原理图是否一致。

此类工具用于比较版图和原理图在晶体管级的连接是否正确,并用报告的形式列出其差异之处。

AMBA总线介绍

计算机基本知识AMBA总线介绍一:背景介绍ARM公司定义了AMBA(Advanced Microcontroller Bus Architecture)总线规范,它是一组针对基于ARM核的、片上系统之间通信而设计的标准协议。

因为ARM处理器的广泛使用而拥有众多第三方支持,被ARM公司90%以上的合作伙伴采用。

在AMBA总线规范中,定义了AHB ,APB ,ASB这3种总线。

最初的AMBA总线是ASB和APB。

在它的第二个版本中,ARM引入了AHB。

(l)AHB:Advanced High Performace Bus,用于高性能系统模块的连接,支持突发模式数据传输和事务分割;(2)ASB:Advanced System Bus,也用于高性能系统模块的连接,支持突发模式数据传输,这是较老的系统总线格式,后来由AHB总线替代;(3)APB:Advanced PeriPheral Bus,用于较低性能外设的简单连接,一般是接在AHB或ASB系统总线上的第二级总线。

图1 典型的基于AMBA总线的系统[1]一个以AMBA 为架构的SOC,图1是个典型的系统架构,一般来说包含了high-performance 的system bus –AHB以及low speed, low power 的peripheral bus - APB 。

System bus 是负责连接例如ARM 之类的embedded processor 以及DMA controller,on-chip memory 和其他interface,或其他需要high bandwidth的模块。

而peripheral bus 则是用来连接系统的外围慢速模块,其协议规则相对AHB来说较为简单,它以AHB之间则通过Bridge 相连,期望能減少system bus 的loading。

二:结构以及仲裁原理1 .AHB BusAHB System是由Master,Slave,Infrastructure 三部分所组成。

bus的协议的分类

bus的协议的分类总线(bus)是计算机系统中连接各种硬件组件的通信路径。

它是计算机系统中的关键组成部分,用于在不同的设备之间传输数据和控制信号。

根据其功能和特性,总线协议可以分为几个不同的分类。

在本文中,将介绍一些常见的总线协议分类,并对每个分类进行详细讨论。

一、根据传输方式分类1. 并行总线:并行总线是一种将多个位同时传输的总线协议。

在并行总线中,每个位都使用一个独立的导线进行传输。

它的主要优点是传输速度快,但缺点是需要较多的物理导线,并且在长距离传输时容易产生噪声干扰。

常见的并行总线协议包括:- PCI(Peripheral Component Interconnect):用于连接计算机内部的扩展设备,如显卡、网卡等。

- ISA(Industry Standard Architecture):早期PC机使用的总线标准,已经逐渐被更先进的总线协议所替代。

2. 串行总线:串行总线是一种逐位传输数据的总线协议。

在串行总线中,数据位按照顺序一个接一个地进行传输,使用较少的导线进行通信。

串行总线具有较低的成本和较小的物理占用空间,适用于长距离传输。

常见的串行总线协议包括:- USB(Universal Serial Bus):用于连接计算机和各种外部设备,如鼠标、键盘、打印机等。

- SATA(Serial ATA):用于连接硬盘、光驱等存储设备。

- Ethernet:用于连接计算机网络中的设备,实现数据的远程通信。

二、根据应用领域分类1. 系统总线:系统总线是计算机系统内部用于连接处理器、内存和其他主要组件的总线协议。

它负责在这些组件之间传输地址、数据和控制信号。

常见的系统总线协议包括:- PCI(Peripheral Component Interconnect):用于连接计算机内部的扩展设备。

- PCIe(Peripheral Component Interconnect Express):PCI的高速版本,用于连接高性能设备,如显卡、固态硬盘等。

标准Wishbone协议:流水线Wishbone协议

标准Wishbone协议:流水线Wishbone协议握手发生在主设备和从设备之间。

握手协议是主设备和从设备在握手时所遵守的共同规则。

除了,B3版中的标准模式之外,B4版的Wishbone官方手册中还新增了流水线模式。

下面将依次进行介绍。

标准Wishbone协议如图7所示,当主机准备传输数据时,应将STB_O置位,直到从机将以下任一信号(周期结束信号)置位:ACK_I、ERR_I或者RTY_I。

在每一个时钟(CLK_I)上升沿,系统都会对周期结束信号进行采样。

当任一周期结束信号被置位时,STB_O信号就会被复位。

这就让主机和从机接口都有机会来控制数据的传输速率。

图7 标准总线握手协议,异步从机图8 标准总线握手协议,同步从机允许3.10:在标准模式下,如果从设备保证能够在主设备发起操作时及时做出操作成功的响应,此时ERR_I和RTY_I信号可以不使用,ACK_O信号可以设计为STB_I和CYC_I 信号的逻辑与。

因此ERR_O和RTY_O信号是可选的,而ACK_O信号是必须的。

在点对点连接中,甚至可以将ACK_I信号直接置高。

当存在ERR_O和RTY_O信号,主设备当发现ERR_O和RTY_O信号之一有效时如何进行响应取决于主设备的设计。

注意3.25:在标准模式下,从机接口会置位一个周期结束信号来响应STB_I。

然而,STB_I 信号只有在CYC_I信号有效地时候才有效。

注意3.30:在总线周期期间置位ERR_I信号,会立即结束该周期,意味着从机通知主机在该周期期间发生了错误。

当从机逻辑电路检测到错误,便会置位ERR_I信号。

例如,如果从机使用了奇偶校检,当发生错误时,从机便会通过ERR_I做出反应。

在总线周期期间置位RTY_I信号,也会立即结束该周期,意味着从机通知主机在该周期期间发生了故障(Aborted)。

该信号一般用于共享内存或者总线桥接。

当本地资源处于忙。

Wishbone总线周期之复位操作

Wishbone总线周期之复位操作一个总线周期由多个不可分的时钟周期构成,完成单次读/写操作、块读/写操作或者读改写操作。

总线周期也分为单次读/写周期、块读/写周期和读改写周期。

一次块读/写总线周期完成多次数据读/写操作。

一般情况下,一次操作由主设备和从设备控制信号间的一次握手,以及同时进行的地址和数据总线的一次传输构成。

块操作表示整个操作需要完成多次数据传送。

在总线周期中主设备和从设备预先设定好的共同遵守控制信号握手规则,以及地址和数据总线的传输规则称作总线协议。

在下文(包括以后的博文中)所给图例中给出的信号均为主设备的输入输出信号。

因此,对操作的描述也从主设备信号的角度展开,以便于读者对照正文理解图例。

比如"在时钟上升沿1到达之前,从设备检测到主设备发起的操作,将适当的数据放到主设备的输入信号DAT_I()和TGD_I(),将主设备的ACK_I置高作为对主设备STB_O的响应。

"的等价描述为:"在时钟上升沿1到达之前,从设备检测到主设备发起的操作,将适当的数据放到其输出信号DAT_O()和TGD_O(),将输出信号ACK_O置高作为对主设备STB_O的响应。

"复位操作复位是数字系统最基本的操作。

复位后,系统进入预定的状态。

在遵守Wishbone总线规范的系统中,当RST_I信号有效,系统开始复位。

由于Wishbone规范规定的复位是同步复位,因此在复位信号有效后接下来的时钟上升沿,所有信号和寄存器进入预定状态。

因此,Wishbone规范要求RST_I信号有效时间至少要一个时钟周期。

在数字系统中,实际上更多的采用的是异步复位,而且复位信号的长度一般大于系统电平稳定时间和系统时钟频率稳定时间。

如果在Wishbone接口中使用的是异步复位,设计者需要在文档中说明,因为Wishbone接口默认的是同步复位。

图6 Wishbone总线的复位操作在图6中,我们只给出了STB_O和CYC_O这两个信号,而没有给出其它信号。

基于AMBA与WISHBONE的SoC总线桥KBar控制器的设计

基于AMBA与WISHBONE的SoC总线桥KBar控制器的设计陈俊锐;陈弟虎【期刊名称】《微计算机信息》【年(卷),期】2012(000)010【摘要】本文介绍了一种基于AMBA与WISHBONE的多总线SOC接口--KBar 控制器的设计方案。

本文提出了一种全新的SOC架构.并使用硬件描述语言实现了此架构中一个中枢系统SOCBridge--KBar控制器(下文简称KBar)。

KBar不仅实现了把SOC中的CPU与外围模块,片外Memory模块连接起来组成一个完整的SOC系统的功能,而且能成功实现对片外Memory(NORFLASH和SDRAM)的访问。

该控制器在AheraQuartusII9.0下,利用CyclonelIIEP3C25F324C8FPGA成功综合,并得到了验证。

%This article describes an AMBA Bus SOC with WISHBONE interfaces based-KBar controller design. Presented a new SOC architecture, and using hardware description language for the SOC Bridge-KBar a central system controller in this schema (hereinafter referred to as KBar). KBar not only implements the CPU and peripheral modules in SOC, connecting external Memory module con- sisting of a complete SOC system function, but also outside the successful achievement of on-chip Memory (NOR FLASH and SDRAM) access. The controller in the Ahera QuartuslI 9, CyclonelI EP2C35F672C6 FPGA integrated successfully and has been veri- fied.【总页数】3页(P157-159)【作者】陈俊锐;陈弟虎【作者单位】中山大学1;中山大学1【正文语种】中文【中图分类】TN492【相关文献】1.SOC设计中WISHBONE片上总线的设计与开发 [J], 宋廷强;刘川来;周艳2.基于Wishbone SoC总线接口的高性能SDRAM控制器 [J], 李争;李范鸣;陈捷;庄良3.片上系统中WISHBONE/AMBA AHB总线桥的前端设计 [J], 宋云扬;罗仁贵;侯立刚;董利民;吴武臣4.基于AMBA总线USB控制器的SOC设计与验证 [J], 贾凡;谢蒂;杨义先5.基于WISHBONE片上总线的USB2.0设备控制器IP核的设计 [J], 孙爱良;徐磊因版权原因,仅展示原文概要,查看原文内容请购买。

基于Wishbone总线结构的情景式IP核测试方案

基于Wishbone总线结构的情景式IP核测试方案

周俊;张金艺

【期刊名称】《上海大学学报(自然科学版)》

【年(卷),期】2005(011)005

【摘要】随着集成电路技术的发展,IP核复用成为集成电路SOC设计的主流.该文通过对广泛应用于SOC设计中的Wishbone总线体系结构和国际上常用IP核测试方法的研究,提出一种基于Wishbone总线结构的情景式IP核测试方案.通过对该方案应用于实际项目后所产生实验数据的分析,证明这种IP核测试方案能大大降低系统层测试难度,加快系统层设计速度,并能显著提高测试激励效率和可观电路结构测试覆盖率.

【总页数】6页(P460-464,471)

【作者】周俊;张金艺

【作者单位】上海大学,通信与信息工程学院,上海,200072;上海大学,通信与信息工程学院,上海,200072

【正文语种】中文

【中图分类】TN4

【相关文献】

1.基于Wishbone总线的UART IP核设计 [J], 王振华;何明华

2.基于Wishbone总线的CRC32 IP核的设计 [J], 张德学;桑圣锋

3.基于Wishbone片上总线的IP核的互联 [J], 陈光武;范多旺;于超;石文静

4.基于WISHBONE片上总线的USB2.0设备控制器IP核的设计 [J], 孙爱良;徐磊

5.基于Wishbone总线接口的以太网IP核设计 [J], 宋仁银;许川佩

因版权原因,仅展示原文概要,查看原文内容请购买。

Wishbone共享总线连接与点到点连接

Wishbone共享总线连接与点到点连接Wishbone共享总线连接与点到点连接同样重要。

在本例中,两个主设备和两个从设备通过SYSCON实现了共享总线连接,在后续章节中,我们将使用该例子对Or1200进行基本RTL验证。

系统复位后,一个或者多个主设备通过置高CYC_O请求使用总线,仲裁器(后文将讨论)选择其中一个主设备#X(X在0和N之间),只将该主设备对应的GNTX信号置高,而将其它GNT信号置低以通知INTERCON哪一个主设备可以使用总线。

一旦主设备选定,其输出信号将通过选择器送到共享总线进而送到各个从设备。

例如,如果主设备#0被中可以使用总线,则器ADR()、DAT_O()、SEL_O()、WE_O和STB_O信号将被送到各个从设备。

与此同时请求使用总线的其他设备,将永远接收不到总线周期结束信号ACK_I/ERR_I/RTY_I。

从设备是如何被选择的呢若系统中有M个从设备,则地址线被地址译码器分为M个部分,别代表每一个从设备的地址空间。

从设备#Y对应的译码输出信号与共享总线上的STB_I信号相与,如果STB_I信号和从设备#Y对应的译码输出信号同时为高,从设备#Y 才发起对主设备操作的响应。

各个从设备输出的总线周期结束ACK_O/ERR_O/RTY_O被通过或门送到各个主设备的ACK_I/ERR_I/RTY_I。

而从设备的DAT_O()输出则通过选择器送到各个主设备的输入端,这个选择器的输入为共享地址总线。

图22 基于选择器的Wishbone共享总线连接示例intercon模块的源码如下:module intercon2M2S(clk_i,rst_i,wb0s_data_i,wb0s_data_o,wb0_addr_i,wb0_sel_i,wb0_we_i,wb0_cyc_i,wb0_stb_i,wb0_ack_o,wb0_err_o,wb0_rty_o,wb0m_data_i,wb0m_data_o,wb0_addr_o,wb0_sel_o,wb0_we_o,wb0_cyc_o,wb0_stb_o,wb0_ack_i,wb0_err_i,wb0_rty_i,wb1s_data_i,。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

片上总线Wishbone 学习(二)Wishbone 互联的类型

Wishbone可变互连方式允许系统工程师可以采用不同的IP核互连方式,

以满足不同场合的要求。

Wishbone规范支持的互联类型有四种:点到点、数据流方式、共享总线、交叉(Crossbar)互连方式。

这四种互联方式在Wishbone 规范中有明确的定义。

下面介绍四种Wishbone总线互连形式。

点到点方式点到点互连是最简单一种的形式。

它适用于两个IP核之间的连接。

如图1所示,总线的一边是主端(如微控制器),一边是从端(如存储器)。

图1点到点互连

数据流方式数据流互连框图如图2所示,当数据以连续的方式进行处理时可

采用此模式。

图中每个IP核兼有主端和从端。

数据从一个IP核传送到下一个,与流水线相似。

图2数据流互连

IP核A处理完数据后将处理结果送给IP核B,IP核B处理完IP核A送来

的数据后再将处理结果送给IP核C处理。

数据从一个IP核送往另一个IP核,常常将这种处理方式称作流水线。

流水线在处理器设计中非常重要,其好处是

多个数据可以并行处理,从而提高系统的整体数据处理能力。

tips:感谢大家的

阅读,本文由我司收集整编。

仅供参阅!。