采用TLC5620设计各种波形发生器

基于TLC5620的低频函数信号发生器设计

LOAD

LD AC

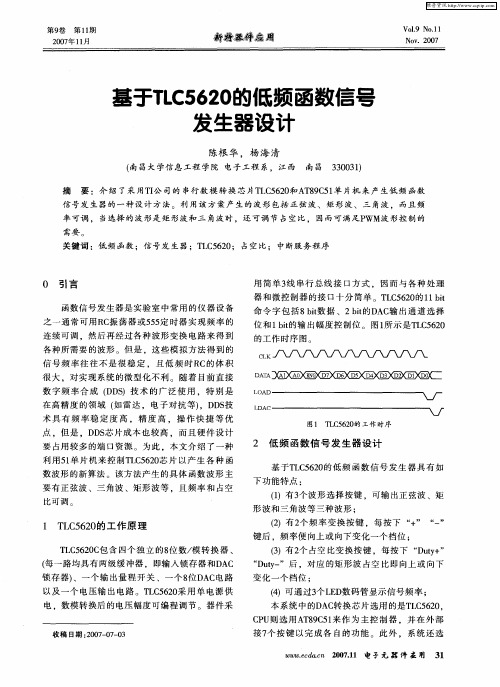

图1 T C 6 0 工作 时序 L 52 的

2 低 频 函数 信 号 发 生 器 设 计

基 于T J5 2 的低频 函数 信 号 发 生 器具 有 如 I 60 C

本 设 计 采用 P .~ 27 2 P .来分 别 连 接T C 6 0 4 L 5 2 的

( 一路 均具有 两级 缓 冲器 ,即输人 锁存 器 和D C 每 A

锁 存器1 、一个 输 出量程 开 关 、一个 8 D C电路 位 A

以及 一个 电压 输 出 电路 。T C 6 0 L 5 2 采用 单 电源 供

电 。数模 转 换后 的 电压 幅度可 编程 调节 。器件 采

f)可 通过3 E 数 码 管显示 信号频 率 ; 4 个L D

CLK

各 种所需 要 的波 形 。但是 。这 些模 拟 方 法得 到 的 信 号频 率 往 往 不 是 很 稳 定 。且 低 频 时R C的体 积

很 大 ,对 实现 系统 的微 型化 不 利 。随着 目前 直接

DAr r A

1 A0 R G D7 D6 D5 ]4 D3 D2 D1 X X NX X X X 3X X X

信 号 发 生 器 的 一 种 设 计 方 法 。 利 用 该 方 案 产 生 的 波 形 包括 正 弦 波 、 矩 形 波 、 三 角 波 。 而 且 频

率 可调 ,当选择 的 波形是 矩 形波和 三 角波 时 ,还 可调 节 占空 比 。因 而可满足 P WM波形控 制 的

需要

TLC5620实验报告

实验报告信息与通信工程学院TLC5620串行D/A实验1实验要求TLC5620是4通道8位的串行D/A转换器。

任务1:观察已给程序的实验现象,并结合实验结果理解原程序语句的含义,体会基本句话,模块的用法。

在掌握整个程序工作的原理后,修改程序,使其实现单通道的DA转换:在按下通道的按键之后,用数码管显示输入的数字量;停止按键,数码管计数停止,继续按键则继续计数。

按下复位键,则系统清零,数码管显示0值。

将转换后的模拟电压加到LED两端,观察LED亮度变化是否符合理论规律。

任务2:在任务1的基础上,进一步体会程序的编写思想,将顶层图形文件修改成一个用语言描述的模块,实现原程序所要求的各项功能:通过4个按键选择不同通道,每个通道的数字量输入都可以在数码管上进行显示。

松开按键,则计数显示保持前一状态,按下按键继续计数。

设置复位键,按下复位键,系统清零。

每个通道对应的模拟电压通过LED的亮度显示。

通过硬件实现,观察实验结果。

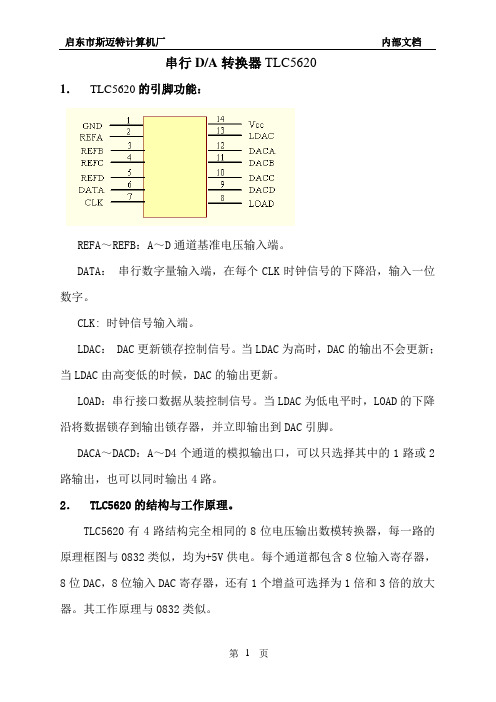

2实验原理2.1 TLC5620基本原理TLC5620封装如实验图1所示,是一个4通道8位的串行数模(D/A)转换器,其最大转换速度可达1MBps。

其管脚REFA~REFD为四个通道的参考电压,实验平台的参考电压均为 2.5V;DACA~DACD为4路四个模拟信号输出通道;DA TA为串行数据输入;CLK为DAC串行数据输入时钟,其下降沿锁存输入数据DA TA;LOAD为串行数据锁存信号,低电平锁存。

LDAC为DAC输出更新控制信号,当LDAC为低电平时,则把锁存在锁存器的数据送到DAC并转换为模拟信号,在相应的通道进行输出,故可以始终把LDAC信号置为低电平,也就是说加载信号一旦产生,数据立刻转换输出。

表1为TLC5620各引脚功能介绍。

图1 TLC5620封装示意图表1 TLC5620引脚功能引脚输入/输出功能描述名称序号GND 1 I 地回路及参考终端DACA 12 O DAC A模拟信号输出DACB 11 O DAC B模拟信号输出DACC 10 O DAC C模拟信号输出DACD 9 O DAC D模拟信号输出DATA 6 I 串行数字数据输入接口,在CLK下降沿时将输入的数字量转发到串行接口寄存器里CLK 7 I 串行接口时钟,用于控制串行数据的输入LDAC 13 I 加载DAC。

TLC5620

应用

可编程电压源

数字控制的放大器/衰减器 移动通信

自动测试设备

过程监测和控制

信号合成

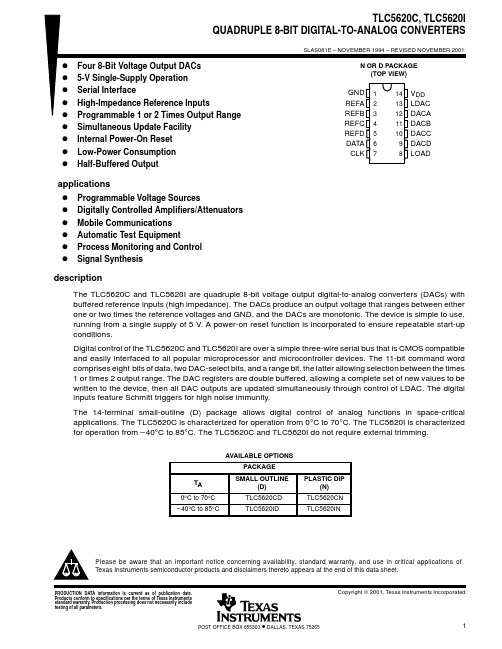

TLC5620是8位电压输出型数模转换器,

由单5V 电源供电,工作在0到70摄氏度。

数字是由三线串行总线控制的,11位命令字组成的8个位的数据。

双缓冲 DAC 寄存器输入具有高抗干扰性和施密特触发器。

引脚说明:

CLK :串行时钟,下降沿时输入数据被移入串行接口

DACA 、B 、C 、D :模拟量输出通道

DATA :串行接口数控输入,时钟下降沿时,数据位被移入寄存器

LDAC :加载DAC ,DAC 的输出只有在LDAC 由高电平跳变到低电平时

发生。

LOAD :串行接口负荷控制,当LDAC 引脚为低电平,负载的下降沿信号锁存到输出锁存器的数据。

REFFA 、B 、C 、D:

输入到DAC 的参考电压

TLC5620工作时序图

工作原理:LOAD 保持高电平,每当CLK 的下降沿来时,数据锁存在DATA 端,当所有的数据都被锁存时,LOAD 变为低电平,串行数据输入到选定的寄存器,当LDAC 和LOAD 同为低电平时,选定的DAC 输出电压变低,DAC 输出LDAC 引脚的电压。

当LDAC 为高电平时新值转移到DAC 的输出脉冲LDAC 引脚上,将数据转换为模拟电压输出。

8位串行数模转换器

5V 单电源供电

高阻抗基准输入

内部上电复位。

基于TLC5620信号发生器的设计与实现_郑润娜

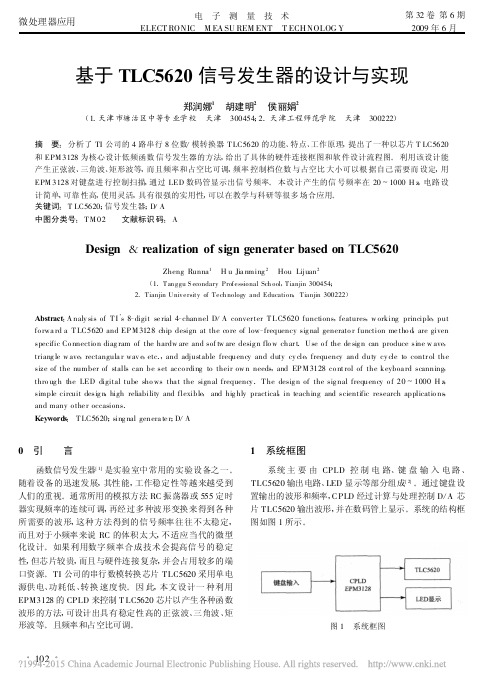

微处理器应用 电 子 测 量 技 术 ELECT RONIC M EA SU REM ENT T ECH NOLOG Y第32卷第6期2009年6月 基于TLC5620信号发生器的设计与实现郑润娜1 胡建明2 侯丽娟2(1.天津市塘沽区中等专业学校 天津 300454;2.天津工程师范学院 天津 300222)摘 要:分析了TI公司的4路串行8位数/模转换器T LC5620的功能、特点、工作原理,提出了一种以芯片T LC5620和EPM3128为核心设计低频函数信号发生器的方法,给出了具体的硬件连接框图和软件设计流程图。

利用该设计能产生正弦波、三角波、矩形波等,而且频率和占空比可调,频率控制档位数与占空比大小可以根据自己需要而设定,用EPM3128对键盘进行控制扫描,通过LED数码管显示出信号频率。

本设计产生的信号频率在20~1000H z,电路设计简单,可靠性高,使用灵活,具有很强的实用性,可以在教学与科研等很多场合应用。

关键词:T LC5620;信号发生器;D/A中图分类号:T M02 文献标识码:ADesign&realization of sign generater based on TLC5620Zheng Runna1 H u Jia nming2 Hou Lijuan2(1.Tan ggu S econdary Professional Sch ool,Tianjin300454;2.Tianjin University of Tech nology and Education,Tianjin300222)Abstract:A naly sis of T I s8-digit se rial4-channel D/A conver ter T L C5620functions,features,w orking principle,put fo rwa rd a T LC5620and EP M3128chip design at the co re of low-frequency sig nal generato r function me tho d,are given specific Co nnectio n diag ram of the hardw are and sof tw are desig n flo w char t.U se o f the de sig n can produce sine w ave, triang le w ave,rectangula r wav e,etc.,and adjustable frequency and duty cy cle,frequency and duty cy cle to contr ol the size of the number of stalls can be set acco rding to their ow n needs,and EP M3128co nt rol of the keyboa rd scanning, thro ug h the LED digital tube sho ws tha t the signal frequency.T he desig n of the sig nal frequency o f20~1000H z, simple circuit desig n,high reliability and flexible,and hig hly practical,in teaching and scientific research applicatio ns, and many o the r occasions.Keywords:T LC5620;sing nal genera te r;D/A0 引 言函数信号发生器[1]是实验室中常用的实验设备之一。

TLC5620中文

第四章后向通道的设计前面所述的只是测温部分,要想达到温度控制的目的,还必须对半导体激光器进行加热或制冷,这就是后向通道所要做的。

4.1 数模模块的设计由单片机计算得到得差值,经过处理后送到数模转换芯片,从而控制TEC的驱动电路,达到控温的目的。

本系统选用的DA芯片是TI公司的TLC5620。

4.1.1TLC5620简介TLC5620是一款具有高阻抗基准输入的4 路串行8位电压输出型数模转换芯片,它采用单一+5 V 电源供电,是一种低功耗芯片。

TLC5620 兼容CMOS 电平,只需要通过4 根串行总线就可以完成8位数据的串行输入,易于和工业标准的微处理器或微控制器(单片机)接口。

适用于可编程电压源、数字控制放大器/衰减器、信号合成、移动通信、自动测试装置以及工程监视和控制等工业控制场合[11]。

本系统使用的TLC5620的具体型号是塑料DIP(P)封装TLC5620CN,它的工作温度范围为0~70 ℃。

TLC5620可分别输入4个参考电压,从而有4种不同的模拟电压输出。

TLC5620是通过使用4个电阻网络实现来4路数模转换,每路DAC(数模转换)的核心是256 个独立电阻,对应串行输入的256个可能码值0~255。

每个电阻网络的一端连接到地GND,另一端从基准电压输入缓冲器的输出端反馈回来[11]。

TLC5620共有14个针脚,具体针脚定义如表所示:针脚号 针脚符号针脚功能简介。

1 GND 输入工作电压地端。

2~5 REFA~REFD4个参考电压输入端,其限定了模拟输出电压的最大值。

6 DATA 串口界面的数字数据输入端。

进行转化的数字信号是串行输入到寄存器的,且每一位数据是在时钟信号的下降沿被读入的。

7 CLK 串行时钟信号输入端。

用于控制串行数据的输入。

8 LOAD 串行界面数据装载控制端。

当LDAC是低电平的时候,在LOAD信号的下降沿,将输入的数字数据锁入输出门,并立即产生模拟电压输出。

[笔记].串型DACTLC5620生成锯齿波、三角波实验,Verilog版本

![[笔记].串型DACTLC5620生成锯齿波、三角波实验,Verilog版本](https://img.taocdn.com/s3/m/c87bd4394a73f242336c1eb91a37f111f1850d49.png)

[笔记].串型DACTLC5620⽣成锯齿波、三⾓波实验,Verilog版本原理图时序图思路源代码顶层模块module tlc5620_test(input CLOCK_50, // 板载50MHz时钟input RST_N,//output ADC549_CLK,output ADC549_CS_N,input ADC549_DATA,//output DAC5620_CLK,output DAC5620_DATA,output DAC5620_LOAD,//output [7:0] SEG7_SEG, // 七段数码管段脚output [7:0] SEG7_DIG // 七段数码管位脚);function integer log2(input integer n);integer i;for(i=0; 2**i <=n; i=i+1) log2=i+1;endfunction/*************************************** ⽣成20ms的tick时钟**************************************/reg [log2(1_1000_1000):1] cnt_20ms;always@(posedge CLOCK_50, negedge RST_N)if(!RST_N) cnt_20ms <= 0;else beginif(cnt_20ms < 999_999)cnt_20ms <= cnt_20ms + 1'b1;else cnt_20ms <= 0;endwire tick_20ms = (cnt_20ms == 999_999) ? 1 : 0;/*************************************** 锯齿波;接LED**************************************/reg [7:0] da0_data;always@(posedge CLOCK_50, negedge RST_N)if(!RST_N) da0_data <= 0;else if(tick_20ms) beginif(da0_data < 255)da0_data <= da0_data + 1'b1;else da0_data <= 0;end/*************************************** 三⾓波;接LED**************************************/reg da1_highest_level_flag;reg [7:0] da1_data;always@(posedge CLOCK_50, negedge RST_N)if(!RST_N) beginda1_data <= 0;da1_highest_level_flag <= 0;end else if(tick_20ms) beginif(da1_data == 255-1)da1_highest_level_flag <= 1;else if(da1_data == 0+1)da1_highest_level_flag <= 0;if(da1_highest_level_flag)da1_data <= da1_data - 1'b1;elseda1_data <= da1_data + 1'b1;endwire [7:0] da2_data = 0;wire [7:0] da3_data = 0;tlc5620_driver tlc5620_driver_inst(.CLOCK_50(CLOCK_50),.RST_N(RST_N),//.da_enable(1'b1),.da_range(0), // 0, 1倍参考电压; 1, 2倍参考电压 .da0_data(da0_data), // 0~255.da1_data(da1_data), // 0~255.da2_data(da2_data), // 0~255.da3_data(da3_data), // 0~255//.SCK(DAC5620_CLK),.SDI(DAC5620_DATA),.LOAD(DAC5620_LOAD));endmoduletlc5620驱动module tlc5620_driver(input CLOCK_50,input RST_N,//input da_enable,input da_range, // 0, 1倍参考电压; 1, 2倍参考电压 input [7:0] da0_data, // 0~255input [7:0] da1_data, // 0~255input [7:0] da2_data, // 0~255input [7:0] da3_data, // 0~255//output reg SCK,output reg SDI,output reg LOAD);function integer log2(input integer n);integer i;for(i=0; 2**i <=n; i=i+1) log2=i+1;endfunction/*************************************** ⽣成140ns的tick时钟**************************************/reg [log2(7):1]cnt_140ns;always@(posedge CLOCK_50, negedge RST_N) if(!RST_N) cnt_140ns <= 0;else beginif(cnt_140ns < 6)cnt_140ns <= cnt_140ns + 1'b1;else cnt_140ns <= 0;endwire tick_140ns = (cnt_140ns == 6) ? 1 : 0;/*************************************** 根据tick时钟⽣成da基准计数器**************************************/reg [log2(48):1] da_ref_cnt; // [0,47]always@(posedge CLOCK_50, negedge RST_N)if(!RST_N) da_ref_cnt <= 0;else beginif(!da_enable) da_ref_cnt <= 0;else beginif(tick_140ns) beginif(da_ref_cnt < 47)da_ref_cnt <= da_ref_cnt + 1'b1;else da_ref_cnt <= 0;endendendwire tick_6720ns = (da_ref_cnt == 47) ? 1 : 0;reg [1:0] da_sel_cnt;always@(posedge CLOCK_50, negedge RST_N)if(!RST_N) da_sel_cnt <= 2'b0;else if (tick_6720ns) beginif(da_sel_cnt < 3)da_sel_cnt <= da_sel_cnt + 1'b1;else da_sel_cnt <= 2'b0;end/*************************************** 根据基准计数器⽣成串⾏信号**************************************/reg [7:0] da_data;always@(posedge CLOCK_50, negedge RST_N)if(!RST_N) da_data <= 8'b0;else begincase(da_sel_cnt)2'b00: da_data <= da0_data;2'b01: da_data <= da1_data;2'b10: da_data <= da2_data;2'b11: da_data <= da3_data;endcaseendalways@(posedge CLOCK_50, negedge RST_N)if(!RST_N) beginSCK <= 0;SDI <= 0;LOAD <= 0;endelse beginif(tick_140ns) begin// ⽣成SCK信号case(da_ref_cnt)2,6,10,14,18,22,26,30,34,38,42: SCK <= 1; 4,8,12,16,20,24,28,32,36,40,44: SCK <= 0; default : ; // 缺省不操作endcase// ⽣成LOAD信号case(da_ref_cnt)0: LOAD <= 1;46: LOAD <= 0;default : ; // 缺省不操作endcase// 送⼊串型数据case(da_ref_cnt)3,4: SDI <= da_sel_cnt[1];7,8: SDI <= da_sel_cnt[0];11,12: SDI <= da_range;15,16: SDI <= da_data[7];19,20: SDI <= da_data[6];23,24: SDI <= da_data[5];27,28: SDI <= da_data[4];31,32: SDI <= da_data[3];35,36: SDI <= da_data[2];39,40: SDI <= da_data[1];43,44: SDI <= da_data[0];default : SDI <= 1'b1;endcaseendendendmoduleSignaltap硬件仿真。

基于TLC5620的低频函数信号发生器设计

Vol.9 No.11 Nov. 2007

图2 LED显示硬件电路示意图

用3个LED数 码 管 来 显 示 频 率 , 具 体 的 硬 件 电 路 示意图如图2所示。

本 设 计 采 用 P2.4~P2.7 来 分 别 连 接 TLC5620 的 CLK、DATA、LOAD、LDAC, 以驱动TLC5620工 作, P0.0~P0.6分别接正弦波、矩形波、三角波波 形选择按键以及频率增减按键和占空比增减按 键 。 P2.0~P2.2 作 为 3 位 数 码 管 频 率 显 示 的 位 选 地 址, P1口则作为数据线。

1 TLC5620的工作原理

TLC5620C包含四个独立的8位数 /模转换器、 (每一路均具有两级缓冲器, 即输入锁存器和DAC 锁 存 器 )、 一 个 输 出 量 程 开 关 、 一 个 8 位 DAC电 路 以 及 一 个 电 压 输 出 电 路 。 TLC5620 采 用 单 电 源 供 电, 数模转换后的电压幅度可编程调节。器件采

0 引言

函数信号发生器是实验室中常用的仪器设备 之 一 通 常 可 用 RC振 荡 器 或 555 定 时 器 实 现 频 率 的 连续可调, 然后再经过各种波形变换电路来得到 各种所需要的波形。但是, 这些模拟方法得到的 信 号 频 率 往 往 不 是 很 稳 定 , 且 低 频 时RC的 体 积 很大, 对实现系统的微型化不利。随着目前直接 数 字 频 率 合 成 (DDS) 技 术 的 广 泛 使 用 , 特 别 是 在高精度的领域 (如雷达, 电子对抗等), DDS技 术具有频率稳定度高, 精度高, 操作快捷等优 点, 但是, DDS芯片成本也较高, 而且硬件设计 要占用较多的端口资源。为此, 本文介绍了一种 利 用 51 单 片 机 来 控 制 TLC5620 芯 片 以 产 生 各 种 函 数波形的新算法。该方法产生的具体函数波形主 要有正弦波、三角波、矩形波等, 且频率和占空 比可调。

串行模数数模转换实验报告

串行模数/数模转换实验报告一.实验目的:1、掌握 TLC549同步串行接口的ADC模块的特性、编程原理,了解TLC5620的4种时序图以及产生波形幅度的计算方法。

2、能实现TLC549、TLC5620与MCS-51单片机的连接,分别进行数据采集和波形观测。

3、能采用Proteus ISIS软件进行串行模数转换的电路设计。

4、能运用MCS-51单片机汇编语言进行串行模数/数模转换实验的软件设计。

二.实验要求:1、将TLC549 与MCS-51单片机进行连接,利用汇编语言编写出数据采集程序,将转换的模拟电压以二进制的形式通过单片机的P0口输出显示。

1)将单片机的P0口与LED1~LED8连接起来,作为输出显示。

由于LED采用灌电流方式驱动,所以要将数据取反后再输出显示,以获得“正逻辑”效果2)利用P1口与TLC549的控制信号进行连接,TLC549的基准电压REF+端与基准电压+5V相连,将电位器的上端连接VCC、下端连接GND,抽头与TLC549的模拟输入ANIN连接。

在运行程序时,不断地调节电位器,使其抽头电压连续变化,通过LED1~LED8的状态观察ADC转换的结果。

3)运用Proteus ISIS软件完成串行模数转换实验的硬件电路设计。

4)实现KeilC与Proteus软件的联调。

2、设计软件程序,用单片机的I/O口控制TLC5620实现D/A转换,使其通道1产生一个三角波,而通道2产生一个和通道1周期、幅度均相同的方波。

1)短接B7区的电源供给跳线JP16,调节B7区的电位器W3,使其输出接线柱Verf的电压为2.6V。

2)将A2区P16、P17、T0、T1分别连接到B9区的CLK、DAT、LDAC、LOAD,将B7区Verf连接到B9区REF接线柱,短接B9区电源跳线JP13。

3)运行光盘中的相应程序,用双踪示波器的两个探头观察DACA、DACB输出的波形。

三.流水灯硬件电路图四.软件程序1. 串行模数实验程序流程图2.程序清单 1) 串行模数:SDO BIT P1.0 ;数据输出CS BIT P1.1 ;片选SCLK BIT P1.2 ;时钟ORG 8000HAJMP MAINORG 8100HMAIN: MOV SP,#60HLOOP: ACALL TLC549_ADCCPL A ;累加器A取反MOV P0,A ;数据给P0口ACALL DELAYSJMP MAINTLC549_ADC: PUSH 07HCLR A ;清零CLR SCLKMOV R6,#08H ;计数器赋初值CLR CS ;选中TLC549LOOP1:SETB SCLK ;SCLK置位,数据输出NOPNOPMOV C,SDORLC A ;累加器A循环左移CLR SCLK ;SDO=0,为读出下一位数据作准备 NOPDJNZ R6,LOOP1 ;R6-1→R6,判断R6=0SETB CS ;禁止TLC549,再次启动AD转换 SETB SCLKPOP 07HRETDELAY: PUSH 00HMOV R0,#00HDJNZ R0,$POP 00HRETEND2)串行数模:SCLA BIT P1.6SDAA BIT P1.7LOAD BIT P3.5LDAC BIT P3.4VOUTA DATA 30HVOUTB DATA 31HORG 8000HAJMP MAINORG 8100HMAIN:MOV SP,#60HNOPCLR SCLACLR SDAASETB LOADSETB LDACMOV R3,#0A2HMOV R4,#00HMOV VOUTA,#00HMOV R5,#0A2HMOV R6,#00HMOV VOUTB,#00HDACHANG:MOV R1,#01HMOV R2,VOUTALCALL DAC5620DJNZ R3,CONTINUEAMOV R3,#0A2HMOV A,R4CPL AMOV R4,ACONTINUEA:CJNE R4,#OFFH,CONTINUEB DEC R2SJMP CONTINUEC CONTINUEB:INC R2CONTINUEC:MOV VOUTA,R2MOV R1,#03HMOV R2,VOUTBLCALL DAC5620DJNC R5,CONTINUEDMOV R5,#042HMOV A,R6CPL AMOV R6,A CONTINUED:CJNE R6,#0FFH,CONTINUEE MOV R2,#OA2HSJMP CONTINUEF CONTINUEE:MOV R2,#00H CONTINUEF:MOV VOUTB,R2LJMP DACHANG DAC5620:MOV A,R1CLR SCLAMOV R7,#08HLCALL SENDBYTEMOV A,R2CLR SCLAMOV R7,#08HLCALL SENDBYTECLR LOADSETB LOADCLR LDACSETB LDACRETSENDBYTE:SETB SCLARLC AMOV SDAA,CCLR SCLADJNZ R7,SENDBYTE RETEND五.实验结果观察实验结果,可知道通过调节电位器,数字量在对应的发生改变。

TLC5620实验内容

TLC5620串行D/A实验实验原理2.1 TLC5620基本原理TLC5620封装如实验图1所示,是一个4通道8位的串行数模(D/A)转换器,其最大转换速度可达1MBps。

其管脚REFA~REFD为四个通道的参考电压,实验平台的参考电压均为2.5V;DACA~DACD为4路四个模拟信号输出通道;DATA为串行数据输入;CLK为DAC串行数据输入时钟,其下降沿锁存输入数据DATA;LOAD为串行数据锁存信号,低电平锁存。

LDAC为DAC输出更新控制信号,当LDAC为低电平时,则把锁存在锁存器的数据送到DAC 并转换为模拟信号,在相应的通道进行输出,故可以始终把LDAC信号置为低电平,也就是说加载信号一旦产生,数据立刻转换输出。

表1为TLC5620各引脚功能介绍图1 TLC5620封装示意图表1 TLC5620各引脚功能引脚输入/输出功能描述名称序号CLK 7 I 串行接口时钟。

引脚出现下降沿时将输入的数字量转发到串行接口寄存器里DACA 12 O DAC A模拟信号输出DACB 11 O DAC B模拟信号输出DACC 10 O DAC C模拟信号输出DACD 9 O DAC D模拟信号输出DATA 6 I 数字量串行输入接口;每个数据在时钟下降沿所存GND 1 I 地回路及参考终端LDAC 13 I 加载DAC。

当引脚出现高电平时,即使有数字量被读入串行口也不会对DAC的输出进行更新。

只有当引脚从高电平变为低电平时,DAC输出才更新。

LOAD 8 I 串口加载控制。

当LDAC是低电平,并且LOAD引脚出现下降沿时数字量被保存到锁存器,随后输出端产生模拟电压。

REFA 2 I 输入到DAC A的参考电压。

这个电压定义了输出模拟量的范围。

REFB 3 I 输入到DAC B的参考电压。

这个电压定义了输出模拟量的范围。

REFC 4 I 输入到DAC C的参考电压。

这个电压定义了输出模拟量的范围。

REFD 5 I 输入到DAC D的参考电压。

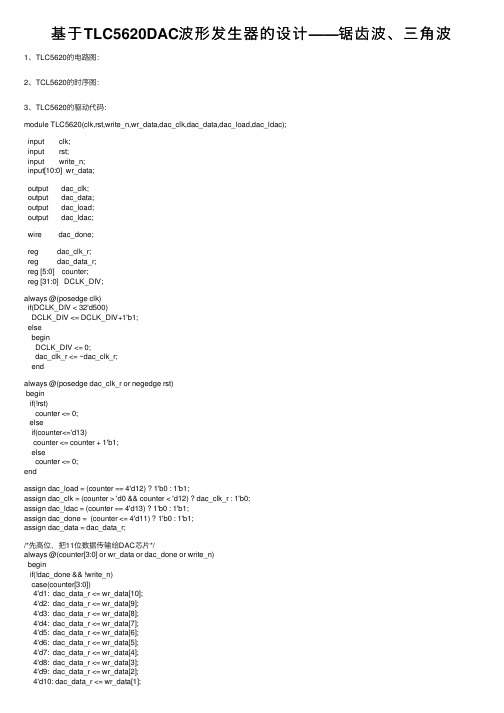

基于TLC5620DAC波形发生器的设计——锯齿波、三角波

基于TLC5620DAC波形发⽣器的设计——锯齿波、三⾓波1、TLC5620的电路图:2、TCL5620的时序图:3、TLC5620的驱动代码:module TLC5620(clk,rst,write_n,wr_data,dac_clk,dac_data,dac_load,dac_ldac);input clk;input rst;input write_n;input[10:0] wr_data;output dac_clk;output dac_data;output dac_load;output dac_ldac;wire dac_done;reg dac_clk_r;reg dac_data_r;reg [5:0] counter;reg [31:0] DCLK_DIV;always @(posedge clk)if(DCLK_DIV < 32'd500)DCLK_DIV <= DCLK_DIV+1'b1;elsebeginDCLK_DIV <= 0;dac_clk_r <= ~dac_clk_r;endalways @(posedge dac_clk_r or negedge rst)beginif(!rst)counter <= 0;elseif(counter<='d13)counter <= counter + 1'b1;elsecounter <= 0;endassign dac_load = (counter == 4'd12) ? 1'b0 : 1'b1;assign dac_clk = (counter > 'd0 && counter < 'd12) ? dac_clk_r : 1'b0;assign dac_ldac = (counter == 4'd13) ? 1'b0 : 1'b1;assign dac_done = (counter <= 4'd11) ? 1'b0 : 1'b1;assign dac_data = dac_data_r;/*先⾼位,把11位数据传输给DAC芯⽚*/always @(counter[3:0] or wr_data or dac_done or write_n)beginif(!dac_done && !write_n)case(counter[3:0])4'd1: dac_data_r <= wr_data[10];4'd2: dac_data_r <= wr_data[9];4'd3: dac_data_r <= wr_data[8];4'd4: dac_data_r <= wr_data[7];4'd5: dac_data_r <= wr_data[6];4'd6: dac_data_r <= wr_data[5];4'd7: dac_data_r <= wr_data[4];4'd8: dac_data_r <= wr_data[3];4'd9: dac_data_r <= wr_data[2];4'd10: dac_data_r <= wr_data[1];4'd11: dac_data_r <= wr_data[0];default: dac_data_r <= 1'b1;endcaseelsedac_data_r <= 1'b1;endendmodule4、锯齿波代码:module hackle(input clk, //50MHzinput reset,output write_n,output [10:0] write_data );reg[7:0] data;assign write_data = {1'b0,1'b0,1'b1,data}; assign write_n = 1'b0;reg clk_div = 1'b0;//1MHzreg[8:0] cnt;always @(posedge clk)beginif(cnt < 9'd500)cnt <= cnt + 1'b1;elsebegincnt <= 1'b0;clk_div <= ~clk_div;endendalways @(posedge clk_div or negedge reset) beginif(!reset) data <= 8'd0;else data <= data + 1'b1;endendmodule5、三⾓波代码:module triangle(input clk, //50MHzinput reset,output write_n,output [10:0] write_data );reg[7:0] data;assign write_data = {1'b0,1'b0,1'b1,data}; assign write_n = 1'b0;reg clk_div = 1'b0;//1MHzreg[8:0] cnt;always @(posedge clk)beginif(cnt < 9'd500)cnt <= cnt + 1'b1;elsebegincnt <= 1'b0;clk_div <= ~clk_div;endendreg flag = 1'b0;always @(posedge clk_div or negedge reset) beginif(!reset) data <= 8'd0;else if(!flag) data <= data + 1'b1;else data <= data - 1'b1;endalways @(posedge clk or negedge reset) beginif(!reset) flag <= 1'b0;else if(data== 8'd255) flag <= 1'b1;else if(data== 8'd0) flag <= 1'b0;endendmodule。

TLC5620--DA转换示例祥述

串行D/A转换器TLC56201.TLC5620的引脚功能:REFA~REFB:A~D通道基准电压输入端。

DATA:串行数字量输入端,在每个CLK时钟信号的下降沿,输入一位数字。

CLK: 时钟信号输入端。

LDAC: DAC更新锁存控制信号。

当LDAC为高时,DAC的输出不会更新;当LDAC由高变低的时候,DAC的输出更新。

LOAD:串行接口数据从装控制信号。

当LDAC为低电平时,LOAD的下降沿将数据锁存到输出锁存器,并立即输出到DAC引脚。

DACA~DACD:A~D4个通道的模拟输出口,可以只选择其中的1路或2路输出,也可以同时输出4路。

2.TLC5620的结构与工作原理。

TLC5620有4路结构完全相同的8位电压输出数模转换器,每一路的原理框图与0832类似,均为+5V供电。

每个通道都包含8位输入寄存器,8位DAC,8位输入DAC寄存器,还有1个增益可选择为1倍和3倍的放大器。

其工作原理与0832类似。

TLC5620输出电压Vo的计算公式为如下:Vo(DACA|B|C|D)=Vref×(CODE/256)×(1+RNG)其中:Vref是参考电压;CODE为串行输入的数字量(0~255);RNG为串行输入的增益选择,取值0或者1。

3.应用示例。

(1).参考连接线(与51单片机)。

以下为TLC5620与51单片机的引脚的具体联线明晰表(供读者参考,读者可按照以下方式自行使用扁平线焊接)。

51单片机引脚 TLC5620引脚P1.7 CLKP1.6 DATAP3.4 LDACP3.5 LOAD(2). 示例原理介绍。

利用TLC5620进行D/A转换,在A、B通道分别产生三角波和方波。

该方波与三角波幅度相等,周期相同,读者可以利用示波器对其输出波形进行实际观察。

如果需要增加其带负载能力,您可以使用运算放大器使用。

(3).ASM汇编源程序。

SCLA BIT P1.7 ;时钟线SDAA BIT P1.6 ;数据线SAN BIT 10H ;三角波升降标志位,为0表示下降FAN BIT 11H ;方波升降标志位,为0表示下降LOAD BIT P3.5 ;数据控制线LDAC BIT P3.4 ;DAC更新控制线VOUTA DATA 30H ;A通道数据暂存单元VOUTB DATA 31H ;B通道数据暂存单元ORG 000HAJMP MAINORG 0100HMAIN:MOV SP ,#600HNOPCLR SCLACLR SDAASETB LOADSETB LDACMOV R3,#0A2H ;三角波的半周期计数器CLR SAN ;三角波幅度递增/递减标志位,初始化为0时,表示下降MOV VOUTA,#00H ;三角波瞬态电压值存储器清0MOV R5,#0A2H ;方波的半周期计数器CLR FAN ;方波幅度高/低电平标志位,初始化为0时,表示低电平MOV VOUTB,#00H ;方波高低电平电压值存储器清0,其幅度与三角波幅度相等DACHANG: ;D/A转换程序开始MOV R1,#01H ;选择通道A输出(三角波),2倍增益MOV R2,#VOUTALCALL DAC5620 ;调用D/A转换子程序DJNZ R3,CONTINUEA ;判断三角波是否上升(或下降)到峰点(或谷点) MOV R3,#0A2HCPL SAN ;若已达到峰点(或谷点),则改变幅度递增或递减标志CONTINUEA:JB SAN,CONTINUEB ;判断当前处于上升还是下降状态,以决定转移方向DEC R2SJMP CONTINUECCONTINUEB:INC R2CONTINUEC:MOV VOUTA,R2 ;保存R2的值,使VOUTA继续用于三角波瞬态电压计算MOV R1,#03H ;选择通道B输出(方波),2倍增益MOV R2,VOUTBLCALL DAC5620DJNZ R5,CONTINUED ;判断方波是否应改变电平状态MOV R5,#0A2HCPL FAN ;若已达到改变电平状态的时刻,则改变方波电平标志位CONTINUED:JB FAN,CONTINUEE ;根据方波高/低电平标志们决定输出状态DEC R2SJMP CONTINUEFCONTINUEE:INC R2MOV R2,#00HCONTINUEF:MOV VOUTB,R2 ;保存R2的值,使VOUTB继续用于方波瞬态电压计算LJMP DACHANG ;周期地进行转换,形成三角波和方波的周期信号DAC5620:MOV A,R1 ;准备发控制字CLR SCLALCALL SENDBYTEMOV A,R2 ;准备发数据字CLR SCLALCALL SENDBYTECLR LOADSETB LOADCLR LDACSETB LDACRETSENDBYTE: ;发送时序要求中的1字节MOV R7,#08SEND:SETB SCLARLC AMOV SDAA,CCLR SCLADJNZ R7,SENDRETEND。

任意波形发生器设计

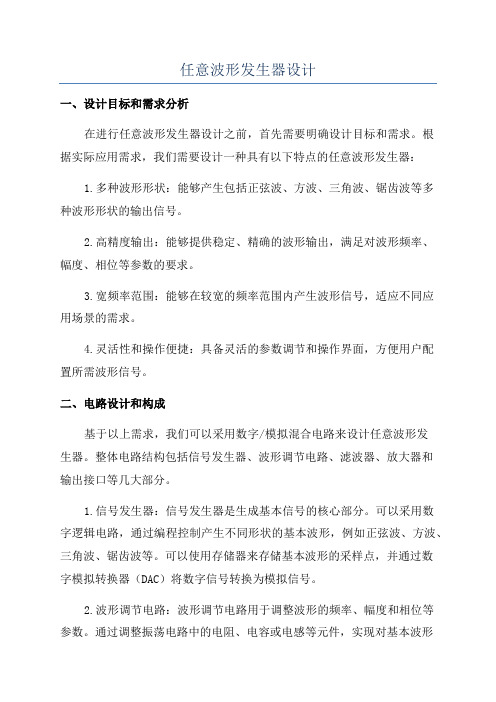

任意波形发生器设计一、设计目标和需求分析在进行任意波形发生器设计之前,首先需要明确设计目标和需求。

根据实际应用需求,我们需要设计一种具有以下特点的任意波形发生器:1.多种波形形状:能够产生包括正弦波、方波、三角波、锯齿波等多种波形形状的输出信号。

2.高精度输出:能够提供稳定、精确的波形输出,满足对波形频率、幅度、相位等参数的要求。

3.宽频率范围:能够在较宽的频率范围内产生波形信号,适应不同应用场景的需求。

4.灵活性和操作便捷:具备灵活的参数调节和操作界面,方便用户配置所需波形信号。

二、电路设计和构成基于以上需求,我们可以采用数字/模拟混合电路来设计任意波形发生器。

整体电路结构包括信号发生器、波形调节电路、滤波器、放大器和输出接口等几大部分。

1.信号发生器:信号发生器是生成基本信号的核心部分。

可以采用数字逻辑电路,通过编程控制产生不同形状的基本波形,例如正弦波、方波、三角波、锯齿波等。

可以使用存储器来存储基本波形的采样点,并通过数字模拟转换器(DAC)将数字信号转换为模拟信号。

2.波形调节电路:波形调节电路用于调整波形的频率、幅度和相位等参数。

通过调整振荡电路中的电阻、电容或电感等元件,实现对基本波形的变换和调节。

可以设计多种电路模块来完成这一任务,例如可变电容二极管电路、可调电阻电路等。

3.滤波器:滤波器用于对产生的波形信号进行滤波处理,除去高频或低频的杂散分量,保留所需频率范围内的信号。

可以采用各种类型的滤波器电路,例如RC滤波器、有源滤波器或数字滤波器等。

4.放大器:放大器用于增强波形信号的幅度,确保输出的信号具备足够的驱动能力,可以驱动接收端电路。

可以采用运放等放大电路,根据需要选择合适的增益。

5.输出接口:输出接口用于将产生的波形信号输出给外部设备。

可以设计多种类型的输出接口,例如模拟输出接口(BNC接口)、数字输出接口(USB接口)等,方便用户接入不同类型的设备。

三、实现方法和关键技术在设计任意波形发生器时,需要考虑以下关键技术和实现方法:1.数字信号处理技术:通过数字信号处理技术,实现对基本波形的生成、存储和输出。

多路波形发生器的设计与实现

多路波形发生器的设计与实现引言多路波形发生器是一种能够同时输出多种不同信号波形的设备。

它的设计与实现涉及到信号发生器、电路设计以及软件编程等多个方面的知识。

本文将详细探讨多路波形发生器的设计与实现过程。

设计要求在设计多路波形发生器时,需要满足以下要求: 1. 能够同时输出多路信号波形;2. 支持多种常见的信号波形,例如正弦波、方波、三角波等;3. 能够调节不同信号波形的频率、幅度和相位等参数;4. 需要提供友好的用户界面,方便用户进行操作;5. 设备的输出稳定性和精度要求较高。

设计方案基于以上设计要求,我们可以采用以下设计方案来实现多路波形发生器:电路设计模拟信号生成电路1.使用数字模拟转换器(DAC)将数字信号转换为模拟信号;2.通过运放电路放大模拟信号,并根据用户设置的幅度参数进行调节;3.按照用户设置的频率参数生成模拟信号的周期性变化。

控制电路设计1.使用微控制器或FPGA作为控制核心,负责接收用户的输入,控制信号的生成和输出等操作;2.通过按键、旋钮或者触摸屏等输入设备与用户进行交互;3.控制电路还需要生成相位差来实现多路信号波形的同步输出。

软件编程1.使用适当的编程语言开发控制软件,实现用户界面的设计和数据的处理;2.根据用户输入的参数,生成对应的波形参数,并通过控制电路输出;3.控制软件还需要实现相位差的计算和同步输出的控制。

实现步骤下面将介绍具体的实现步骤:步骤一:电路设计与组装1.根据电路设计方案,选择合适的元器件,设计并制作模拟信号生成电路;2.设计并制作控制电路,使其能够与模拟信号生成电路有效地协作;3.对于大规模的多路波形发生器,可能需要使用多个模块进行串联或并联。

步骤二:软件编程与调试1.根据设计方案,使用适当的编程语言进行控制软件的开发;2.实现用户界面的设计,包括输入参数的显示和调节;3.编写波形参数生成的算法,并将生成的参数发送给控制电路;4.调试软件功能及与控制电路之间的通信问题。

TLC5620C中文资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)TLC5620CD ACTIVE SOIC D 1450Pb-Free (RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-220C-UNLIM TLC5620CDR ACTIVE SOIC D 142500Pb-Free (RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-220C-UNLIM TLC5620CN ACTIVE PDIP N 1425Pb-Free (RoHS)CU NIPDAU Level-NA-NA-NA TLC5620ID ACTIVE SOIC D 1450Pb-Free (RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-220C-UNLIM TLC5620IDR ACTIVE SOIC D 142500Pb-Free (RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-220C-UNLIM TLC5620INACTIVEPDIPN1425Pb-Free (RoHS)CU NIPDAULevel-NA-NA-NA(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -May not be currently available -please check /productcontent for the latest availability information and additional product content details.None:Not yet available Lead (Pb-Free).Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean "Pb-Free"and in addition,uses package materials that do not contain halogens,including bromine (Br)or antimony (Sb)above 0.1%of total product weight.(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standardclassifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM18-Feb-2005Addendum-Page 1IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

串行数模转换器TLC5620I与TMS320F2812接口设计

串行数模转换器TLC5620I与TMS320F2812接口设计1 引言近年来,数字信号处理器(DSP)的应用越来越广泛,其中TMS320F2812 作为目前数字控制领域中性能较高的DSP 芯片,被广泛应用于电机控制、工业自动化、家用电器和消费电子等领域。

由于TMS320F2812 本身不具有D/A 转换模块,因此在很多需要模拟量输出的控制场合受到限制。

所以D/A 转换芯片如何与TMS320F2812 进行接口,成为数字信号处理系统需要解决的一个重要问题。

这里介绍了四路8 位电压输出数字一模拟转换器TLC5620I,并给出TLC5620I 与TMS320F2812 串口接口的软、硬件设计实现方法。

2 TMS320F2812 的SPI 工作原理TMS320F2812 的SPI 模块的9 个寄存器用来控制SPI 的操作,其中SPICCR 设置SPI 的软件复位、移位时钟极性字符长度;SPICTL 设置SPI 的时钟相位、工作模式等;SPISTS 中包括溢出标志位、中断标志位等;SPIBRR 设置SPI 波特率;SPIRXBUF 和SPITXBUF 为数据接收和发送缓冲寄存器,SP-IDAT 用于发送/接收移位寄存器;SPIRXEMU 仅用于仿真;SPIPRI 控制中断优先级。

该器件的SPI 接口有一个16 级的FIFO,用来减少CPU 的开销。

图1 为SPI 模块与CPU 接口结构框图。

由图1 可知,SPI 模块数据传输由40、41、34、35 引脚完成,其引脚功能见表1。

TMS320F2812 支持125 种不同的波特率和4 种不同的时钟模式。

根据SPI的工作模式(从动或主控),引脚SPICLK 可分别接收一个外部的SPI 时钟信号或由片内提供SPI 时钟信号。

在该设计中,SPI 工作在主控模式,SPI 时钟由。

波形发生器电路设计与制作

波形发生器电路设计与制作波形发生器电路设计与制作是电子技术中非常重要的一部分。

波形发生器主要用于产生各种类型的电子信号,如正弦波、方波、三角波、锯齿波等,广泛应用于实验室、电子产品测试和各种电子系统中。

在这篇文章中,我们将介绍波形发生器电路的设计与制作过程。

接下来,我们需要选择合适的电子元件来实现波形发生器电路。

根据波形类型的不同,我们需要选择不同的电子元件。

例如,要产生正弦波,可以使用一个运放芯片和一组电阻、电容来实现。

在电路设计过程中,我们需要考虑一些重要的因素,如频率稳定性、波形失真、输出幅度等。

频率稳定性是指波形发生器电路产生的波形频率在一定范围内保持稳定。

为了提高频率稳定性,我们可以使用一个稳压电源和一个精度较高的电容。

波形失真是指波形发生器产生的波形与理想的波形之间的偏差。

为了减小波形失真,我们可以使用滤波电路对波形进行滤波处理。

输出幅度是指波形发生器输出的信号的幅度大小。

为了调整输出幅度,可以使用电阻分压电路或放大电路。

在电路设计完成后,我们可以进行电路调试和测试。

首先,我们需要验证电路的基本功能,即产生所需的波形类型。

然后,可以使用示波器和频谱分析仪等测试设备,对波形发生器电路进行性能测试。

电路制作是波形发生器电路设计的最后一步。

在制作电路时,我们需要选取合适的电子元件和电路板,并按照电路设计图进行布线和焊接。

制作完成后,我们需要进行电路测试和性能调试。

综上所述,波形发生器电路设计与制作是一项繁琐的工作,但在电子技术中具有广泛应用。

通过合理选择电子元件、合理设计电路和仔细调试电路,我们可以获得高质量的波形发生器电路。

希望通过本文的介绍,读者能够对波形发生器电路的设计与制作有所了解。

单片机,多种波形发生器设计

单片机课程设计报告书课题名称多种波形发生器设计 姓 名 学 号 院、系、部电气工程系 专 业电气工程及其自动化 指导教师2013年7月10日※※※※※※※※※※※ ※※ ※※※※※※※※※※※2010级单片机课程设计目录一、设计目的 (1)二、设计要求 (1)三、硬件电路 (1)3.1系统框图 (1)3.2AT89C52单片机介绍 (2)3.3DAC0832数模转换器 (4)3.4按键电路 (5)3.5驱动与显示电路 (6)3.6 系统电路原理图 (6)四、流程图设计 (8)五、程序设计 (9)六、调试与仿真结果 (13)七、设计总结 (14)八、参考文献 (15)多种波形发生器设计一、设计目的设计一个能产生方波,三角波,梯形波,锯齿波,正弦波的波形发生器。

二、设计要求1、产生指定波形可以通过DAC来实现,不同波形产生实质上是对输出的二进制数字量进行相应改变来实现的。

方波信号可以利用定时器中断产生的,每次中断时,将输出的信号按位反即可;三角波信号是将输出的二进制数字信号依次加1,达到0xff时依次减1,并实时将数字信号经D/A转换得到;锯齿波信号是将输出的二进制数字信号依次加1,达到0xff时置为0x00,并实时将数字信号经D/A转换得到的;梯形波是将输出的二进制数字信号依次加1,达到0xff时保持一段时间,然后依次减1直至0x00,并实时将数字信号经D/A转换得到的;正弦波可以预先写出正弦波表,通过读出表中的值然后经D/A转换后输出。

2、用按键来控制输出的波形,如可设计5个按键S0、S1、S2、S3,S4按一次S1键,不断输出三角波等。

3、用一位数码管显示波形代码:如输出三角波,显示代码“1”等。

4、要求用实验箱实现。

三、硬件电路3.1系统框图多种波形发生器由单片机、按钮、运放等部分组成。

系统框图如图3-1所示。

图3-1 系统框图3.2AT89C52单片机介绍AT89C52是一个低电压,高性能CMOS 8位单片机,片内含8k bytes的可反复擦写的Flash只读程序存储器和256 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器和Flash存储单元,AT89C52单片机在电子行业中有着广泛的应用。

DA实验

实验名称:D/A 实验实验目的:学习使用串行数模转换芯片TLC5620产生所需模拟电压波形。

实验原理:TLC5620 8位串行D/A 1、概述:TLC5620是美国德州仪器(TI )公司生产的8位带有高阻抗缓冲输入的4通道D/A 转换芯片。

可产生单调的、1到2倍于基准电压和接地电压差值的输出。

通常情况下TLC5620的供电电压为5V ,器件内部集成上电复位功能。

通用微处理器通过CLK 、DATA 、LOAD 和LDAC 四根控制线可实现对该芯片的控制。

2、器件引脚和内部结构(1) GND :输入电压地端(2) REFA-REFD :4个参考电压输入端,限定了模拟输出电压的最大值 (3) DATA :串口界面的数字数据输入端。

进行转化的数字信号的串行输入到寄存器,且每一位数据是在时钟信号的下降沿被读入。

(4) CLK :串行时钟信号输入端。

用于控制串行数据的输入。

(5) LOAD :串行界面数据装载控制端。

当LDAC 是低电平,在LOAD 信号的下降沿,将输入的数字数据锁入输出门,并立即产生模拟电压输出。

(6) DACD-DACA :4个模拟电压输出端。

(7) LDAC :装载DAC 控制端。

当LDAC 是高电平时,有数字信号写入的时候DAC 输出不会被更新。

只有LDAC 信号由高电平下降为低电平时才会更新模拟输出。

(8) VDD :输入工作电压正端。

(|||)(1)256O CODEV DACA B C D REF RNG =⨯⨯+3、工作时序:TLC5620共有四种工作时序。

(1)工作时序一:当LOAD 为高电平、LDAC 为低电平时,串行数据在CLK 每一个下降沿由时钟同步送入DATA 端口。

一旦8位数据位都送入,LOAD 变为低脉冲电平,以便把数据锁存至串行数据寄存器中。

由于LDAC 为低电平,锁存在串行数据寄存器中的数据自动锁存至所选择的DAC中,更新DAC输出。

(2)工作时序二:当LOAD为高电平、LDAC为高电平时,串行数据在CLK每一个下降沿由时钟同步送入DATA端口。

采用TLC5620设计各种波形发生器(DOC)

sbit juchi=P3^3;//按键

sbit tixing=P3^4;//按键

sbit Sinanjian=P3^5;//按键

uchar flag=0;

void sanjiaowave();

void juchiwave();

void tixingwave();

void SinWave();

/**************************************************************************************************

第二章 系统概述

2.1.1单片机的选择

随着微电子技术的飞速发展,CPU已经变成低成本器件。在可能的情况下,各种机电设备已经或者正在嵌入CPU构成的嵌入式系统。据Virginia Tech公司报告,嵌入式系统中所使用的CPU数量已经超过通用PC中CPU数量的30倍。 现在系统研究的重点已从通用系统转向专用系统,以及从一般性能转向可靠性、可用性、安全性、自主性、可扩展性、功能性、灵活性、成本、体积、功耗及可管理性上。

AT89C52有PDIP、PQFP/TQFP及PLCC等三种封装形式,以适应不同产品的需求。

主要功能特性:

·兼容MCS51指令系统· 8k可反复擦写(>1000次)FlashROM

· 32个双向I/O口· 256x8bit内部RAM

tlv5620芯片工作原理

tlv5620芯片工作原理

TLV5620是一种12位数字至模拟转换器(DAC)芯片,它的工

作原理可以从几个方面来解释。

首先,TLV5620接收来自控制器或微处理器的数字输入信号,

通常是一个12位的数字信号。

这个数字信号代表了所需的模拟输出

电压值。

芯片内部的数字至模拟转换器模块会将这个数字信号转换

成相应的模拟电压输出。

其次,TLV5620的工作原理涉及到其内部的参考电压源。

它通

常需要外部提供一个参考电压,这个参考电压会被DAC模块用来将

数字信号转换成对应的模拟电压输出。

通过调整参考电压的大小,

可以改变TLV5620的输出范围。

另外,TLV5620还包括一个集成的运算放大器,用来增益和缓

冲输出信号。

这个放大器可以帮助提高输出的精度和稳定性。

除此之外,TLV5620还可能包括一些其他功能,比如电源管理、接口控制等。

这些功能也会影响其工作原理。

总的来说,TLV5620的工作原理是将输入的数字信号转换成相应的模拟电压输出,同时通过参考电压和其他内部模块来实现对输出信号的控制和调节。

这样的工作原理使得TLV5620成为了在各种应用中广泛使用的数字至模拟转换器芯片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

采用DA设计各种波形发生器

第一章 引言

1.1系统背景介绍

D/A转换器,作为实验用的模拟信号源,是现今各种电子电路实验设计应用中必不可少的仪器设备之一。目前,市场上常见的D/A转换器多为纯硬件的搭接而成,且波形种类有限,多为锯齿、正弦、1.1单片机的选择

随着微电子技术的飞速发展,CPU已经变成低成本器件。在可能的情况下,各种机电设备已经或者正在嵌入CPU构成的嵌入式系统。据Virginia Tech公司报告,嵌入式系统中所使用的CPU数量已经超过通用PC中CPU数量的30倍。 现在系统研究的重点已从通用系统转向专用系统,以及从一般性能转向可靠性、可用性、安全性、自主性、可扩展性、功能性、灵活性、成本、体积、功耗及可管理性上。

当今是科学技术及仪器设备高度智能化飞速发展的信息社会,电子技术的进步,给人们带来了根本性的转变。现代电子领域中,单片机的应用正在不断的走向深入,这必将导致传统控制与检测技术的日益革新。单片机构成的仪器具有高可靠性、高性能价格比,在智能仪表系统和办公自动化等诸多领域得以极为广泛的应用,并走入家庭,从洗衣机、微波炉到音响汽车,处处可见其应用。因此,单片机技术开发和应用水平已逐步成为一个国家工业发展水平的标志之一。

· 2个外部中断源· 共6个中断源

· 2个读写中断口线 · 3级加密位

· 低功耗空闲和掉电模式· 软件设置睡眠和唤醒功能

2.2 D/A

2.2.1

D/A转换器的输入为数字量,经转换后输出为模拟量。有关D/A转换器的技术性能指标很多,例如绝对精度,相对精度,线性度,输出电压范围,温度系数,输入数字代码种类等等。对这些技术性能指标,这里不做全面的详细说明,仅对几个与接口有关的技术性能指标作以介绍。

AT89C52有40个引脚,32个外部双向输入/输出(I/O)端口,同时内含2个外中断口,3个16位可编程定时计数器,2个全双工串行通信口,2 个读写口线,AT89C52可以按照常规方法进行编程,也可以在线编程。其将通用的微处理器和Flash存储器结合在一起,特别是可反复擦写的 Flash存储器可有效地降低开发成本。

利用单片机采用程序设计方法来产生低频信号,其频率底线很低。具有线路相对简单,结构紧凑,价格低廉,频率稳定度高,抗干扰能力强,用途广泛等优点,并且能够对波形进行细微调整,改良波形,使其满足系统的要求。只要对电路稍加修改,调整程序,即可完成功能升级。

1.2 D/A转换器的工作原理

数字/模拟转换器(D/A)用来将数字量转变为模拟量。本设计是基于C52单机的D/A转换器,其可以产生正弦波,锯齿波,方波以及三角波。本设计的原理大概为:以正弦波为例,它实现的原理是把正弦波在一个周期分为256或者64或者32个点,点和点之间的间隔是相等的并通过延时程序来实现。我们先使单片机P0口先输出00H,然后间隔一段时间再输出第二个点,再延时相同的时间输出第三个点,直到输出FFH。这样算一个周期完成。但单片机这样输出的信号只是正弦波的大概,并不是一个平滑完整的波形。我们必须通过一个D/A转换器件把它从数字信号变为模拟信号,但是此时又产生了一个问题,通过D/A转换的模拟信号为电流信号。这样的信号示波器是无法识别的,这样我们就必须通过一个运算放大器把电流信号转换为标准电压信号。这样就基本完成了发生器的设计。当然方波和三角波的实现和正弦波的实现原理基本相同,所以在此我们就不必赘述。我设计的D/A转换器是可以调频的。其调频的原理是:把单片机定时/计数器的最大可计数的时间计算出来,然后我们就可以等间隔步进的从最小的一个计数值来改变计数的时间,使得定时/计数器的溢出时间长短不同,这样就可以改变波形的频率。

AT89C52有PDIP、PQFP/TQFP及PLCC等三种封装形式,以适应不同产品的需求。

主要功能特性:

·兼容MCS51指令系统· 8k可反复擦写(>1000次)FlashROM

· 32个双向I/O口· 256x8bit内部RAM

· 3个16位可编程定时/计数器中断· 时钟频率0-24MHz

· 2个串行中断· 可编程UART串行通道

D/A作为一种常见的应用电子仪器设备,传统的波形产生一般可以完全由硬件电路搭接而成,如采用555振荡电路发生正弦波、三角波和方波的电路便是可取的路径之一,不用依靠单片机。但是这种电路存在波形质量差,控制难,可调范围小,电路复杂和体积大等缺点。在科学研究和生产实践中,如工业过程控制,生物医学,地震模拟机械振动等领域常常要用到低频信号源。而由硬件电路构成的低频信号其性能难以令人满意,而且由于低频信号源所需的RC要很大。大电阻,大电容在制作上有困难,参数的精度亦难以保证。体积大,漏电,损耗显著更是其致命的弱点。一旦工作需求功能有增加,则电路复杂程度会大大增加。

2.1.2AT89C52单片机介绍:

图1.AT89C52单片机引脚图

AT89C52是一个低电压,高性能CMOS 8位单片机,片内含8k bytes的可反复擦写的Flash只读程序存储器和256 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器和Flash存储单元,功能强大的AT89C52单片机可为您提供许多较复杂系统控制应用场合。

采用DA设计各种波形发生器

导师:欧阳斌林

班级:电信1001

组员:杨利红A07100205

张甲林A07100206

日期:2013年6月18日

摘 要

本次D/A转换器设计以单片机AT89S52为主控制器,实现了波形的产生,频率的选择以及波形的选择等功能。本设计的主要功能是用单片机产生三角波,正弦波等波形,然后通过开关按键选择不同的频率和波形输出。本设计采用常用的D/A转换器件TLC5620来使单片机输出的数字信号转换为模拟信号,然后再通过运算放大器把D/A输出的电流信号转换为电压信号输出,这样以便用示波器对波形信号进行测量。这样就完成了D/A转换器的核心部分的设计。