完整word版逻辑地址转换为物理地址

逻辑地址转物理地址

逻辑地址转物理地址逻辑地址转物理地址参考如下1.物理地址和逻辑地址为什么会有这两种地址?个人觉的原因在于逻辑地址分配更加灵活,可以允许不唯一,看起来也较为直观,例如,一段代码中分配数组,逻辑地址上是连续的,然而在物理地址上,这个数组所占用的页可能分散开来,物理地址上就是不连续的,这样对程序的可理解性上有影响。

另外,有了逻辑地址这个概念,才能使用虚拟内存技术。

CPU将一个虚拟内存空间中的地址转换为物理地址,需要进行两步:首先将给定一个逻辑地址(其实是段内偏移量,这个一定要理解!!!),CPU要利用其段式内存管理单元,先将为个逻辑地址转换成一个线程地址,再利用其页式内存管理单元,转换为最终物理地址。

物理地址(physicaladdress)用于内存芯片级的单元寻址,与处理器和CPU连接的地址总线相对应。

——这个概念应该是这几个概念中最好理解的一个,但是值得一提的是,虽然可以直接把物理地址理解成插在机器上那根内存本身,把内存看成一个从0字节一直到最大空量逐字节的编号的大数组,然后把这个数组叫做物理地址,但是事实上,这只是一个硬件提供给软件的抽像,内存的寻址方式并不是这样。

所以,说它是“与地址总线相对应”,是更贴切一些,不过抛开对物理内存寻址方式的考虑,直接把物理地址与物理的内存一一对应,也是可以接受的。

也许错误的理解更利于形而上的抽像。

虚拟内存(virtualmemory)这是对整个内存(不要与机器上插那条对上号)的抽像描述。

它是相对于物理内存来讲的,可以直接理解成“不直实的”,“假的”内存,例如,一个0x08000000内存地址,它并不对就物理地址上那个大数组中0x08000000-1那个地址元素;有了这样的抽像,一个程序,就可以使用比真实物理地址大得多的地址空间。

(拆东墙,补西墙,银行也是这样子做的),甚至多个进程可以使用相同的地址。

不奇怪,因为转换后的物理地址并非相同的。

逻辑地址(logicaladdress)Intel为了兼容,将远古时代的段式内存管理方式保留了下来。

北京交通大学《微机原理与接口技术》作业答案

目录《微机原理与接口技术》第一章作业 (2)一、书上P22作业题 2、3、7 (2)《微机原理与接口技术》第二章作业 (2)一、书上P59作业题 2、5、6、9、14 (2)《微机原理与接口技术》第三章作业 (3)一、书上P95作业题 4、5、6、7、10、11、12、13、14、15、16、17、18、22、27 4《微机原理与接口技术》第四章作业 (8)一、课本P155 8、12、13、14 (8)《微机原理与接口技术》第五章作业 (10)一、作业P180 2、5、7、8、9、10 (11)《微机原理与接口技术》第六章作业 (13)一、P207: 1,3,5,10,14。

18,19,20 (13)《微机原理与接口技术》第七章作业(一) (17)一、P268: 3, 6 , 7, 10 , 11 , 12 (17)《微机原理与接口技术》第七章作业(二) (20)一、P268: 15 , 16 , 19, 21,25 (20)《微机原理与接口技术》第八章作业 (24)一、P292 6、7 (24)《微机原理与接口技术》第一章作业一、书上P22作业题 2、3、72.完成下列数制之间的转换。

(1)01011100B=92D(3)135D=10000111B(5)10110010B=262Q=B2H3.组合型BCD码和非组合型BCD码有什么区别?写出十进制数254的组合型BCD数和非组合型BCD数。

答:组合型BCD码的储存格式用一个字节存放2位BCD码,高4位表示十进制的十位数,低4位表示十进制的个位数,数值表示范围为0~99;非组合型的储存格式是用一个字节的低4位存放1位BCD码,高四位可以为0或任意数,数值表示范围为0~9。

254D的组合型BCD码:0254D的非组合型BCD码:007.计算机中为什么采用补码的形式储存数据?当计算机的字长n=16时,补码的数据表示范围是多少?答:是为了便于进行加减运算,简化机器硬件结构。

2022-2023年软件水平考试《初级程序员》考前冲刺卷I(答案解析12)

2022-2023年软件水平考试《初级程序员》考前冲刺卷I(答案解析)全文为Word可编辑,若为PDF皆为盗版,请谨慎购买!第I卷一.综合考点题库(共50题)1.根据《计算机软件保护条例》的规定,当软件()后,其软件著作权才能得到保护。

A.作品发表B.作品创作完成并固定在某种有形物体上C.作品创作完成D.作品上加注版权标记正确答案:C本题解析:根据《中华人民共和国著作权法》和《计算机软件保护条例》的规定,计算机软件著作权的权利自软件开发完成之日起产生,故应选择C。

2.()can help organizations to better understand the information contained within the data and will also help identify the data that is most important to the business and future business decisions.A.Data processing systemB.Big Data analyticsC.Cloud computingD.Database management正确答案:A本题解析:数据处理系统可以帮助组织更好地了解数据中包含的信息,还可以帮助识别对业务和未来业务决策最重要的数据,因此选A。

3.()是一种客户端脚本语言,它采用解释方式在计算机上执行。

A.PythonB.JavaC.PHPD.JavaScript正确答案:D本题解析:本题考查程序设计语言基础知识。

JavaScript是一种解释性脚本语言(代码不进行预编译),已经被广泛用于Web应用开发,用来为网页添加各式各样的动态功能,用户提供更流畅美观的浏览效果,D选项正确。

4.()模式将企业主要的数据处理过程从个人计算机或服务器转移到大型的数据中心,将计算能力、存储能力当作服务来提供。

A.人工智能B.物联网C.云计算D.移动互联网正确答案:C本题解析:云计算是利用高速互联网的传输能力,将数据的处理过程从个人计算机或服务器转移到一个大型的计算中心,并将计算能力、存储能力当作服务来提供。

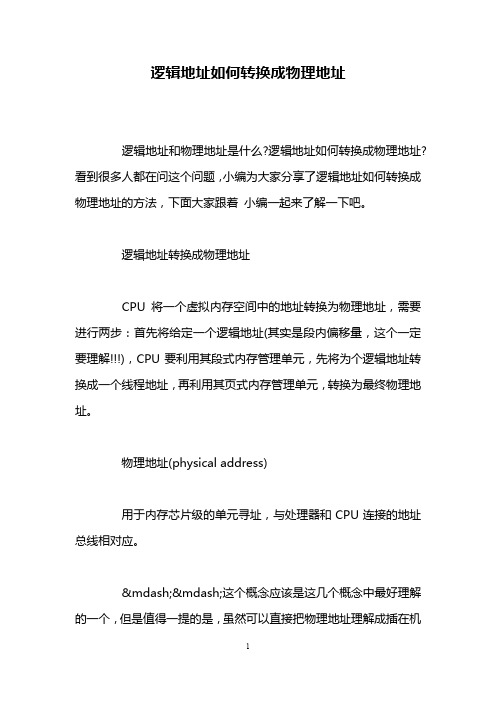

逻辑地址如何转换成物理地址

逻辑地址如何转换成物理地址逻辑地址和物理地址是什么?逻辑地址如何转换成物理地址?看到很多人都在问这个问题,小编为大家分享了逻辑地址如何转换成物理地址的方法,下面大家跟着店铺一起来了解一下吧。

逻辑地址转换成物理地址CPU将一个虚拟内存空间中的地址转换为物理地址,需要进行两步:首先将给定一个逻辑地址(其实是段内偏移量,这个一定要理解),CPU要利用其段式内存管理单元,先将为个逻辑地址转换成一个线程地址,再利用其页式内存管理单元,转换为最终物理地址。

物理地址(physical address)用于内存芯片级的单元寻址,与处理器和CPU连接的地址总线相对应。

——这个概念应该是这几个概念中最好理解的一个,但是值得一提的是,虽然可以直接把物理地址理解成插在机器上那根内存本身,把内存看成一个从0字节一直到最大空量逐字节的编号的大数组,然后把这个数组叫做物理地址,但是事实上,这只是一个硬件提供给软件的抽像,内存的寻址方式并不是这样。

所以,说它是“与地址总线相对应”,是更贴切一些,不过抛开对物理内存寻址方式的考虑,直接把物理地址与物理的内存一一对应,也是可以接受的。

也许错误的理解更利于形而上的抽像。

虚拟内存(virtual memory)这是对整个内存(不要与机器上插那条对上号)的抽像描述。

它是相对于物理内存来讲的,可以直接理解成“不直实的”,“假的”内存,例如,一个0x08000000内存地址,它并不对就物理地址上那个大数组中0x08000000 - 1那个地址元素;之所以是这样,是因为现代操作系统都提供了一种内存管理的抽像,即虚拟内存(virtual memory)。

进程使用虚拟内存中的地址,由操作系统协助相关硬件,把它“转换”成真正的物理地址。

这个“转换”,是所有问题讨论的关键。

有了这样的抽像,一个程序,就可以使用比真实物理地址大得多的地址空间。

(拆东墙,补西墙,银行也是这样子做的),甚至多个进程可以使用相同的地址。

完整word版操作系统试题及答案

完整word版操作系统试题及答案操作系统试题⼀⼀、单选题(每⼩题1分,共20分)1、操作系统中采⽤多道程序设计技术提⾼CPU和外部设备的【A】。

A、利⽤率B、可靠性 C 、稳定性D、兼容性2、如果分时操作系统的时间⽚⼀定,那么【C】,则响应时间越短。

A、内存越少B、内存越多C、⽤户数越少D、⽤户数越多3、若把操作系统看作资源管理者,下列的【C】不属于操作系统所管理的资源。

A、CPUB、内存C、中断D、程序4、操作系统是通过【D 】感知进程存在的。

A、程序名B、进程的状态C、中断D、进程控制块5、当【B 】时,进程从执⾏状态变为就绪状态。

A、进程被进程调度程序选中B、时间⽚⽤完C、等待某⼀事件D、等待的事件发⽣6、以下的进程状态变化中,不可能发⽣的变化是【D 】。

A、执⾏状态到就绪状态B、等待状态到就绪状态C、执⾏状态到等待状态D、等待状态到执⾏状态7、若P、V操作的信号量S初值为2,当前值为-3,则表⽰有【D】个等待进程。

A、0个B、1个C、2个D、3个8、P、V操作是【A】A、两条低级进程通信原语B、两条⾼级进程通信原语C、两条系统调⽤命令D、两组不同的机器指令9、⽤V操作唤醒⼀个等待进程时,被唤醒的进程状态变为【B 】。

A、等待B、就绪C、执⾏D、完成10、资源的有序分配策略破坏【D 】条件,是⼀种死锁预防策略。

A、互斥条件B、保持和请求条件C、不剥夺条件D、环路等待条件11、银⾏家算法是⼀种【B 】算法。

A、死锁预防B、死锁避免C、死锁检测D、死锁解除12、某系统中有同类资源10个,每个进程的资源需求量为3个,则不会发⽣死锁的最⼤并发进程数为【C】A、2B、3C、4D、513、分区管理中采⽤⾸次适应分配算法时,应把空闲区按【C】次序进⾏管理。

A、⼤⼩递增B、⼤⼩递减C、地址递增D、地址递减14、很好地解决了内存碎⽚问题的存储管理⽅案是【C 】。

A、固定分区管理B、可变分区管理C、页式存储管理D、段式存储管理15、虚拟存储管理系统的基础是程序的【C】理论。

(完整word版)计算机操作系统第三版第4章练习题

一、单项选择题1.要保证一个程序在主存中被改变了存放位置后仍能正确执行,则对主存空间应采用()技术。

A.动态重定位B.静态重定位C.动态分配D.静态分配2.固定分区存储管理把主存储器划分成若干个连续区,每个连续区称一个分区。

经划分后分区的个数是固定的,各个分区的大小()。

A.是一致的B.都不相同C.可以相同,也可以不相同,但根据作业长度固定D.在划分时确定且长度保持不变3.采用固定分区方式管理主存储器的最大缺点是()。

A.不利于存储保护B.主存空间利用率不高C.要有硬件的地址转换机构D.分配算法复杂4.采用可变分区方式管理主存储器时,若采用最优适应分配算法,宜将空闲区按()次序登记在空闲区表中。

A.地址递增B.地址递减C.长度递增D.长度递减5.在可变分区存储管理中,某作业完成后要收回其主存空间,该空间可能要与相邻空闲区合并。

在修改未分配区表时,使空闲区个数不变且空闲区始址不变的情况是()空闲区。

A.无上邻也无下邻B.无上邻但有下邻C.有上邻也有下邻D.有上邻但无下邻6.在可变分区存储管理中,采用“紧凑"技术可以()。

A.汇集主存中的空闲区B.增加主存容量C.缩短访问周期D.加速地址转换7.页式存储管理中的页表是由()建立的。

A.操作员B.系统程序员C.用户D.操作系统8.采用页式存储管理时,重定位的工作是由()完成的。

A.操作系统B.用户C.地址转换机构D.主存空间分配程序9.采用段式存储管理时,一个程序如何分段是在()决定的。

A.分配主存时B.用户编程时C.装人作业时D.程序执行时10.采用段式存储管理时,一个程序可以被分成若干段,每一段的最大长度是由( )限定的。

A.主存空闲区的长度B.硬件的地址结构C.用户编程时D.分配主存空间时11.实现虚拟存储器的目的是()。

A.扩充主存容量B.扩充辅存容量C.实现存储保护D.加快存取速度12.LRU页面调度算法是选择( )的页面先调出.A.最近才使用B.最久未被使用C.驻留时间最长D.驻留时间最短13.若进程执行到某条指令时发生了缺页中断,经操作系统处理后,当该进程再次占用处理器时,应从()指令继续执行。

(完整word版)微机原理和接口技术课后习题和参考答案解析

第一章课后习题1.1 把下列十进制数转换成二进制数、八进制数、十六进制数。

① 16。

25 ② 35.75 ③ 123。

875 ④ 97/1281.2 把下列二进制数转换成十进制数。

① 10101.01 ② 11001。

0011 ③ 111。

01 ④ 1010.11。

3 把下列八进制数转换成十进制数和二进制数。

① 756.07 ② 63。

73 ③ 35.6 ④ 323。

451.4 把下列十六进制数转换成十进制数。

① A7。

8 ② 9AD.BD ③ B7C。

8D ④ 1EC1。

5 求下列带符号十进制数的8位补码。

① +127 ② -1 ③ -0 ④ -1281.6 求下列带符号十进制数的16位补码。

① +355 ② -11.7 计算机分那几类?各有什么特点?1.8 简述微处理器、微计算机及微计算机系统三个术语的内涵。

1。

9 80X86微处理器有几代?各代的名称是什么?1。

10 你知道现在的微型机可以配备哪些外部设备?1。

11 微型机的运算速度与CPU的工作频率有关吗?1。

12 字长与计算机的什么性能有关?习题一参考答案1.1 ① 16。

25D=10000。

01B=20.2Q=10.4H② 35.75D=100011。

11B=43.6Q=23.CH③ 123。

875D=1111011。

111B=173.7Q=7B。

EH④ 97/128D=64/123+32/128+1/128=0。

1100001B=0。

604Q=0。

C2H1.2 ① 10101.01B=21.25D ② 11001.0011B=25。

1875D③ 111。

01B=7。

25D ④ 1010。

1B=10。

5D1。

3 ① 756.07Q=111101110.000111B=494.109D ② 63。

73Q=110011.111011B=51。

922D③ 35。

6Q=11101.110B=29。

75D ④ 323.45Q=11010011。

《微机原理及接口技术》课后习题详细解答(期末复习)

《微机原理及接⼝技术》课后习题详细解答(期末复习)第1章微型计算机系统概述〔习题1.3〕微型计算机主要由哪些基本部件组成?各部件的主要功能是什么?〔解答〕微机主要有存储器、I/O设备和I/O接⼝、CPU、系统总线、操作系统和应⽤软件组成,各部分功能如下:CPU:统⼀协调和控制系统中的各个部件系统总线:传送信息存储器:存放程序和数据I/O设备:实现微机的输⼊输出功能I/O接⼝:I/O设备与CPU的桥梁操作系统:管理系统所有的软硬件资源〔习题1.10〕简述计算机中“数”和“码”的区别,计算机中常⽤的数制和码制各有哪些?〔解答〕(1)数—⽤来直接表征量的⼤⼩,包括:定点数、浮点数。

(2)码—⽤来指代某个事物或事物的某种状态属性,包括:⼆进制、⼋进制、⼗进制,⼗六进制区别:使⽤场合不同,详见P16.〔习题1.12〕请写出与数据+37和-37对应的8位机器数原码、反码、补码和移码,并分别⽤⼆进制和⼗六进制表⽰出来。

〔解答〕原码反码补码+37 00100101/25H 00100101/25H 00100101/25H-37 10100101/A5H 11011010/DAH 11011011/DBH〔习题1.13〕请将上题中+37和-37的8位补码机器数分别扩充为16位和32位的形式,⽤⼗六进制表⽰出来。

〔解答〕+37 -3716位 32位 16位 32位00 25H 00 00 00 25H FF 5BH FF FF FF 5BH第2章微处理器指令系统〔习题2.1〕微处理器内部具有哪3个基本部分?8088分为哪两⼤功能部件?其各⾃的主要功能是什么?〔解答〕算术逻辑单元ALU、寄存器组和控制器;总线接⼝单元BIU:管理8088与系统总线的接⼝负责cpu对接⼝和外设进⾏访问执⾏单元EU:负责指令译码、执⾏和数据运算;8位CPU在指令译码前必须等待取指令操作的完成,8088中需要译码的指令已经取到了指令队列,不需要等待取指令。

微机原理与接口技术(第四版)课后习题答案

第1章微型电脑系统①处理器每个单位时间可以处理的二进制数据位数称电脑字长。

②总线信号分成三组,分别是数据总线、地址总线和控制总线。

③PC机主存采用DRAM组成。

④高速缓冲存储器Cache是处理器与主存之间速度很快但容量较小的存储器。

⑤ROM-BIOS是“基本输入输出系统”,操作系统通过对BIOS的调用驱动各硬件设备,用户也可以在应用程序中调用BIOS中的许多功能。

⑥中断是CPU正常执行程序的流程被某种原因打断、并暂时停止,转向执行事先安排好的一段处理程序,待该处理程序结束后仍返回被中断的指令继续执行的过程。

⑦主板芯片组是主板的核心部件,它提供主板上的关键逻辑电路。

⑧MASM是微软开发的宏汇编程序。

⑨指令的处理过程。

处理器的“取指—译码—执行周期”是指处理器从主存储器读取指令〔简称取指〕,翻译指令代码的功能〔简称译码〕,然后执行指令所规定的操作〔简称执行〕的过程。

⑩机器语言层,即指令集结构。

〔学生很多认为是:汇编语言层。

前4章主要涉及汇编语言,但本书还有很多处理器原理等内容〕〔习题1.3〕填空题①Central Processing Unit,中央处理单元,处理器②1MB,4GB③216,64KB④EXE,COM⑤Instruction Set Architecture⑥目录⑦MMX,SSE3⑧64⑨IBM,DOS⑩PCI〔习题1.4〕说明微型电脑系统的硬件组成及各部分作用。

〔解答〕CPU:CPU也称处理器,是微机的核心。

它采用大规模集成电路芯片,芯片内集成了控制器、运算器和假设干高速存储单元〔即寄存器〕。

处理器及其支持电路构成了微机系统的控制中心,对系统的各个部件进行统一的协调和控制。

存储器:存储器是存放程序和数据的部件。

外部设备:外部设备是指可与微机进行交互的输入〔Input〕设备和输出〔Output〕设备,也称I/O设备。

I/O设备通过I/O接口与主机连接。

总线:互连各个部件的共用通道,主要含数据总线、地址总线和控制总线信号。

逻辑地址转物理地址

逻辑地址转物理地址物理地址是明确的、最终用在总线上的编号。

那么逻辑地址转物理地址怎么转? 小编为大家介绍逻辑地址转物理地址的解决方法。

希望大家喜欢。

逻辑地址转物理地址参考如下1. 物理地址和逻辑地址物理地址:加载到内存地址寄存器中的地址,内存单元的真正地址。

在前端总线上传输的内存地址都是物理内存地址,编号从0开始一直到可用物理内存的最高端。

这些数字被北桥(Nortbridge chip)映射到实际的内存条上。

物理地址是明确的、最终用在总线上的编号,不必转换,不必分页,也没有特权级检查(no translation, no paging, no privilege checks)。

逻辑地址:CPU所生成的地址。

逻辑地址是内部和编程使用的、并不唯一。

例如,你在进行C语言指针编程中,可以读取指针变量本身值(&操作),实际上这个值就是逻辑地址,它是相对于你当前进程数据段的地址(偏移地址),不和绝对物理地址相干。

为什么会有这两种地址?个人觉的原因在于逻辑地址分配更加灵活,可以允许不唯一,看起来也较为直观,例如,一段代码中分配数组,逻辑地址上是连续的,然而在物理地址上,这个数组所占用的页可能分散开来,物理地址上就是不连续的,这样对程序的可理解性上有影响。

另外,有了逻辑地址这个概念,才能使用虚拟内存技术。

CPU将一个虚拟内存空间中的地址转换为物理地址,需要进行两步:首先将给定一个逻辑地址(其实是段内偏移量,这个一定要理解!!!),CPU要利用其段式内存管理单元,先将为个逻辑地址转换成一个线程地址,再利用其页式内存管理单元,转换为最终物理地址。

物理地址(physical address)用于内存芯片级的单元寻址,与处理器和CPU连接的地址总线相对应。

——这个概念应该是这几个概念中最好理解的一个,但是值得一提的是,虽然可以直接把物理地址理解成插在机器上那根内存本身,把内存看成一个从0字节一直到最大空量逐字节的编号的大数组,然后把这个数组叫做物理地址,但是事实上,这只是一个硬件提供给软件的抽像,内存的寻址方式并不是这样。

钱晓捷新版汇编语言程序设计习题答案(修改)

钱晓捷新版汇编语言程序设计习题答案第一章汇编语言基础知识1.1、简述计算机系统的硬件组成与各部分作用1.2、明确下列概念或符号:主存和辅存,RAM和ROM,存储器地址和I/O端口,KB、MB、GB和TB1.3、什么是汇编语言源程序、汇编程序、目标程序?1.4、汇编语言与高级语言相比有什么优缺点?1.5、将下列十六进制数转换为二进制和十进制表示〔1〕FFH 〔2〕0H 〔3〕5EH 〔4〕EFH〔5〕2EH 〔6〕10H 〔7〕1FH 〔8〕ABH1.6、将下列十进制数转换为BCD码表示〔1〕12 〔2〕24 〔3〕68 〔4〕127〔5〕128 〔6〕255 〔7〕1234 〔8〕24581.7、将下列BCD码转换为十进制数〔1〕10010001 〔2〕10001001 〔3〕00110110 〔4〕10010000〔5〕00001000 〔6〕10010111 〔7〕10000001 〔8〕000000101.8、将下列十进制数分别用8位二进制数的原码、反码和补码表示〔1〕0 〔2〕-127 〔3〕127 〔4〕-57〔5〕126 〔6〕-126 〔7〕-128 〔8〕681.9、完成下列二进制数的运算〔1〕1011+1001 〔2〕1011-1001 〔3〕1011×1001 〔4〕10111000÷1001〔5〕1011 ∧~1011 〔8〕1011 ⊕1001 1001〔6〕1011 ∨1001〔7〕1.10数码0~9、大写字母A~Z、小写字母a~z对应的ASCII码分别是多少?ASCII码为0dh、0ah对应的是什么字符?1.11、计算机中有一个"01100001〞编码,如果把它认为是无符号数,它是10进制什么数?如果认为它是BCD码,则表示什么数?又如果它是某个ASCII码,则代表哪个字符?1.12、简述Intel 80x86系列微处理器在指令集方面的发展.1.13、什么是DOS和ROM-BIOS?1.14、简述PC机最低1MB主存空间的使用情况.1.15、罗列8086CPU的8个8位和16位通用寄存器,并说明各自的作用.1.16、什么是标志,它有什么用途?状态标志和控制标志有什么区别?画出标志寄存器FLAGS,说明各个标志的位置和含义.1.17、举例说明CF和OF标志的差异.溢出标志OF和进位标志CF是两个意义不同的标志进位标志表示无符号数运算结果是否超出X围,运算结果仍然正确;溢出标志表示有符号数运算结果是否超出X围,运算结果已经不正确•例1:3AH + 7CH=B6H无符号数运算:58+124=182,X围内,无进位有符号数运算: 58+124=182 ,X围外,有溢出•例2:AAH + 7CH=〔1〕26H无符号数运算:170+124=294,X围外,有进位有符号数运算:-86+124=28 ,X围内,无溢出1.18、字和双字在存储器中如何存放,什么是"小端方式〞?对字和双字存储单元,什么是它们的对齐地址?为什么要对齐地址?1.19、什么是8086中的逻辑地址和物理地址?逻辑地址如何转换成物理地址?请将如下逻辑地址用物理地址表达:〔1〕FFFFh:0 〔2〕40h:17h 〔3〕2000h:4500h 〔4〕B821h:4567h1.20、8086有哪4种逻辑段,各种逻辑段分别是什么用途?〔解答〕代码段〔Code Segment〕用来存放程序的指令序列.处理器利用CS : IP取得下一条要执行的指令•堆栈段〔Stack Segment〕确定堆栈所在的主存区域.处理器利用SS : SP操作堆栈中的数据•数据段〔Data Segment〕存放当前运行程序所用的数据.处理器利用DS : EA存取数据段中的数据•附加段〔Extra Segment〕是附加的数据段,也用于数据的保存.处理器利用ES : EA存取数据段中的数据第二章8086指令系统2.1已知DS = 2000H、BX = 0100H、SI = 0002H,存储单元[20100H] ~ [20103H]依次存放12 34 56 78H,[21200H] ~ [21203H]依次存放2A 4C B7 65H,说明下列每条指令执行完后AX寄存器的内容.〔1〕 mov ax,1200h ;AX=1200h〔2〕 mov ax,bx ; AX=0100h〔3〕 mov ax,[1200h] ; AX=4C2Ah〔4〕 mov ax,[bx] ; AX=3412h〔5〕 mov ax,[bx+1100h] ;AX=4C2Ah〔6〕 mov ax,[bx+si] ; AX=7856h〔7〕 mov ax,[bx][si+1100h] ; AX=65B7h2.2指出下列指令的错误<1> mov cx,dl 两操作数类型不匹配<2> mov ip,ax IP指令指针禁止用户访问<3> mov es,1234h 立即数不允许传给段寄存器<4> mov es,ds段寄存器之间不允许传送<5> mov al,300 两操作数类型不匹配<6> mov [sp],ax目的操作数应为[ BP ]<7> mov ax,bx+di源操作数应为[BX+DI]<8> mov 20h,ah立即数不能作目的操作数2.3已知数字0 ~ 9对应的格雷码依次为:18H、34H、05H、06H、09H、0AH、0CH、11H、12H、14H,它存在于以table为首地址〔设为200H〕的连续区域中.请为如下程序段的每条指令加上注释,说明每条指令的功能和执行结果.lea bx,table ;获取table的首地址,BX=200Hmov al,8 ;传送欲转换的数字,AL=8xlat ;转换为格雷码,AL=12H2.4什么是堆栈,它的工作原则是什么,它的基本操作有哪两个,对应哪两种指令?堆栈是一种按"先进后出〞原则存取数据的存储区域.堆栈的两种基本操作是压栈和出栈,对应的指令是PUSH和POP.2.5已知SS = FFA0H、SP = 00B0H,画图说明执行下面指令序列时,堆栈区和SP的内容如何变化?mov ax,8057hpush axmov ax,0f79hpush axpop bx ;bx=0f79hpop [bx] ;DS:[0f79h]=8057h2.6给出下列各条指令执行后AL值,以与CF、ZF、SF、OF和PF的状态:mov al,89h AL=89h CF ZF SF OF PFadd al,al AL=12h 1 0 0 1 1add al,9dh AL=0afh 0 0 1 0 1cmp al,0bch AL=0afh 1 0 1 0 1sub al,al AL=00h 0 1 0 0 1dec al AL=0ffh 0 0 1 0 1inc al AL=00h 0 1 0 0 12.7 设X、Y、Z均为双字数据,分别存放在地址为X、X+2;Y、Y+2;Z、Z+2的存储单元中,它们的运算结果存入W单元.阅读如下程序段,给出运算公式.mov ax,Xmov dx,X+2add ax,Yadc dx,Y+2add ax,24adc dx,0sub ax,Zsbb dx,Z+2mov W,axmov W+2,dxW=X+Y+24-Z2.8请分别用一条汇编语言指令完成如下功能:〔1〕把BX寄存器和DX寄存器的内容相加,结果存入DX寄存器. ADD DX,BX〔2〕用寄存器BX和SI的基址变址寻址方式把存储器的一个字节与AL寄存器的内容相加,并把结果送到AL中.ADD AL,[BX+SI]〔3〕用BX和位移量0B2H的寄存器相对寻址方式把存储器中的一个字和CX寄存器的内容相加,并把结果送回存储器中.ADD [BX+0B2H],CX〔4〕用位移量为0520H的直接寻址方式把存储器中的一个字与数3412H相加,并把结果送回该存储单元中. ADD WORD PTR [0520H],3412H〔5〕把数0A0H与AL寄存器的内容相加,并把结果送回AL中.ADD AL,0A0H2.9;设X、Y、Z、V均为16位带符号数,分别装在X、Y、Z、V存储单元中,阅读如下程序段,得出它的运算公式,并说明运算结果存于何处.为了避免与操作数地址混淆,将题中X,Y,Z,V 字操作数改为A,B,C,Dmov ax,X ;ax=Aimul Y ;dx,ax = A*B <将操作数看作符号数,以下同〕mov cx,axmov bx,dx ;bx,ax <-- dx,ax =A*Bmov ax,Z ;ax = Ccwd ;dx,ax =C 〔扩展符号后为双字〕add cx,axadc bx,dx ;bx,cx <-- bx,cx+dx,ax=A*B+Csub cx,540sbb bx,0 ;bx,cx<-- A*B+C-540mov ax, V ;ax= Dcwd ;dx,ax= D 〔扩展符号后为双字〕sub ax, cxsbb dx, bx ;dx,ax = dx,ax - bx,cx = D-<A*B+C-540>idiv X ;运算结果:[D-<A*B+C-540h>]/A ;ax存商,dx存余数2.10;〔1〕xchg [si],30h xchg的操作数不能是立即数〔2〕pop cs不能对CS直接赋值〔3〕 sub [si],[di] 两个操作数不能都是存储单元〔4〕push ah堆栈的操作数不能是字节量〔5〕 adc ax,ds adc的操作数不能是段寄存器〔6〕 add [si],80h没有确定是字节还是字操作〔7〕 in al,3fch in不支持超过FFH的直接寻址〔8〕 out dx,ah out只能以AL/AX为源操作数2.11; 给出下列各条指令执行后的结果,以与状态标志CF、OF、SF、ZF、PF的状态. 指令 AX的值CF OF SF ZF PFMov ax,1470h 1470h - - - - -And ax,ax 1470h0 0 0 00Or ax,ax 1470h 0 0 0 0 0Xor ax,ax 0 0 0 0 1 1Not ax 0ffffh - - - - -Test ax,0f0f0h 0ffffh 0 0 1 0 1注意: 1. mov, not指令不影响标志位2. 其他逻辑指令使CF=OF=0, 根据结果影响其他标志位.2.12; 假设例题2.32的程序段中,AX = 08H,BX = 10H,请说明每条指令执行后的结果和注意:1. 左移N次相当于乘于2的N次方,右左移N次相当于除乘于2的N次方.2. 移位指令根据是否移入"1〞到CF,设置CF,根据移位后的结果影响SF,ZF,PF.根据最高符号位是否改变设置OF,如改变OF=1.3. ‘u ’表示无定义,‘- ’表示无影响.2.13编写程序段完成如下要求:<1> 用位操作指令实现AL〔无符号数〕乘以10;不考虑进位mov bl,almov cl,3shl al,cladd al,bl ;shl bl,1add al,bl;考虑进位xor ah,ahmov bx,axmov cl,3shl ax,cladd ax,bx ;shl bx,1add ax,bx<2> 用逻辑运算指令实现数字0 ~ 9的ASCII码与非压缩BCD码的互相转换数字0~9的ASCII码是:30h~39h非压缩BCD码的0~9是:00h~09h方法一:and al,0fh ;实现ASCII到非压缩BCD码的转换or al,30h ;实现非压缩BCD码到ASCII的转换方法二:xor al,30h ;求反D5D4位,其他不变;即高4位为3,则变为0;高4位为0,则变为3mov cl,4again: shr dx,1 ;实现逻辑右移;采用"sar dx,1〞,则实现算术右移rcr ax,1dec cljnz again<3> 把DX:.AX中的双字右移4位MOV CL, 4SHR AX, CLMOV BL, DLSHR DX, CLSHL BL, CLOR AH, BL2.14; 已知AL = F7H〔表示有符号数-9〕,分别编写用SAR和IDIV指令实现的除以2的程序段,并说明各自执行后,所得的商是什么?〔1〕用sar编写mov al,0f7h ;-9送alsar al,1 ;结果:al=0fbh 即-5〔2〕用idiv编写mov al,0f7h ;-9送alcbw ;字节符号扩展位字mov bl,2 ;注意除数不可为立即数idiv bl ;结果:商为al=fch <-4>;余数为ah=ffh <-1>结论:符号数的除法用idiv 准确2.15、已知数据段500h ~600h处存放了一个字符串,说明下列程序段执行后的结果:mov si,600hmov di,601hmov ax,dsmov es,axmov cx,256stdrep movsb2.16、说明下列程序段的功能cldmov ax,0fefhmov cx,5mov bx,3000hmov es,bxmov di,2000hrep stosw2.17、指令指针IP是通用寄存器还是专用寄存器?有指令能够直接它赋值吗?哪类指令的执行会改变它的值?调试程序DEBUG环境下,如何改变IP数值?2.18、控制转移类指令中有哪三种寻址方式?2.19;什么是短转移short jump、近转移near jump和远转移far jump?什么是段内转移和段间转移?8086有哪些指令可以实现段间转移?短转移:指段内-128~127之间的转移,位移量用一个字节表示近转移:指段内±32K之间的转移,位移量用一个字表示远转移:指段间1MB X围的转移段内转移:指在同一个代码段内的转移,可以是短转移或者近转移段间转移:指转移到另外一个代码段,就是远转移8086/8088CPU的JMP、CALL和INT n指令可以实现段间转移2.20; 8086的条件转移指令的转移X围有多大?实际编程时,你如何处理超出X围的条件转移?8086的条件转移的转移X围:在当前指令地址的+127---- -128之内.如条件转移的转移X围超出此X围,可在此X围内安排一条无条件转移,再转移到X围外的目标地址.2.21; 假设DS=2000H,BX=1256H,SI=528FH,位移量TABLE=20A1H,[232F7H]=3280H,[264E5H]=2450H,试问执行下列段内间接寻址的转移指令后,转移的有效地址是什么?<1>JMP Bx ;转移的有效地址EA=BX=1256h<2>JMP tABLE[Bx] ;转移的有效地址EA=[ds:20a1h+1256h]=[232f7]=3280h<3>JMP [Bx][si] ;转移的有效地址EA=[ds:1256h+528fh]=264e5h=2450h2.22、判断下列程序段跳转的条件〔1〕 xor ax,1e1ehje equal;AX=1e1eh〔异或后为0〕〔2〕test al,10000001bjnz there;AL的D0或D7至少有一位为1〔3〕 cmp cx,64hthere;CX〔无符号数〕< 64h2.23; 设置CX = 0,则LOOP指令将循环多少次?例如mov cx,0 ;不循环,因为一进入循环就判cx=0? 如cx=0 就退出循环delay:loop delay循环次数是2的16次方,即2^16=65536.2.24 假设AX和SI存放的是有符号数,DX和DI存放的是无符号数,请用比较指令和条件转移指令实现以下判断:〔1〕若DX > DI,转到above执行cmp dx,dija above ;=jnbe above〔2〕若AX > SI,转到greater执行cmp ax,sijg greater ;=jnle greater〔3〕若CX = 0,转到zero执行cmp cx,0 jcxz zerojz zero〔4〕若AX-SI产生溢出,转到overflow执行;cmp ax,dijo overflow〔5〕若SI≤AX,转到less_eq执行;cmp si,axcmp ax,sijle less_eqjge less_eq〔6〕若DI≤DX,转到below_eq执行.cmp di,dxcmp dx,die below_eqjae below_eq2.25有一个首地址为array的20个字的数组,说明下列程序段的功能.mov cx,20mov ax,0mov si,axsum_loop:add ax,array[si]add si,2loop sum_loopmov total,ax; 答:将首地址为array得20个字的数组求和,并将结果存入total 单元中.2.26 按照下列要求,编写相应的程序段:<1> 起始地址为string的主存单元中存放有一个字符串〔长度大于6〕,把该字符串中的第1个和第6个字符〔字节量〕传送给DX寄存器.mov si,0mov dl,string[si] ;第1个字符送dl寄存器mov si,5mov dh,string[si] ;第6个字符送dh寄存器<2> 从主存buffer开始的4个字节中保存了4个非压缩BCD码,现按低〔高〕地址对低〔高〕位的原则,将它们合并到DX中.xor si,si ;si清零mov al,buffer[si] ;第一字节inc simov ah,buffer[si] ;第二字节mov cl,4shl ah,cl ;BCD码移到高半字节or al,ah ;组合成压缩BCD码mov dl,al ;存入dl寄..inc simov al,buffer[si] ;第三字节inc simov ah,buffer[si] ;第四字节mov cl,4shl ah,cl ;BCD码移到高半字节or al,ah ;组合成压缩BCD码mov dh,al ;存入dh寄..<3> 编写一个程序段,在DX高4位全为0时,使AX = 0;否则使AX = -1.test dx,0f000hjz zeromov ax,-1jmp donezero: mov ax,0done: ret<4> 有两个64位数值,按"小端方式〞存放在两个缓冲区buffer1和buffer2中,编写程序段完成buffer1-buffer2功能.lea bx,buffer1lea dx,buffer2mov cx,8 ;8个字节xor si,si ;si=0clc ;CF=0<5> 假设从B800h : 0开始存放有100个16位无符号数,编程求它们的和,并把32位的和保存在DX.AX中.mov ax,0b800hmov ds,ax ;段地址xor si,si ;地址偏移量si=0xor dx,dx ;和的高字dx=0mov cx,99 ;加的次数mov ax,[si] ;第一个数again: inc si ;指向下一个字单元inc siadd ax,[si] ;加下一个数jnc noc ;无进位转inc dx ;有进位dx=dx+1noc: dec cx ;次数-1jnz cx,again ;非0继续加ret<6> 已知字符串string包含有32KB内容,将其中的’$’符号替换成空格.mov si,offset stringmov cx,8000h ;32k=2^15=8000hagain: cmp [si],’$’jnz nextmov [si],20h ;if [si]=’$’[si]<-- ’’next: inc siloop again<7> 有一个100个字节元素的数组,其首地址为array,将每个元素减1〔不考虑溢出〕存于原处.xor si,si ;si<--0mov cx,100 ;循环次数again: dec array[si]dec cxjnz again<8> 统计以’$’结尾的字符串srting的字符个数.xor si,si ;si<--0coun: cmp string[si],’$’je doneinc sijmp coundone: ret2.27; 对下面要求,分别给出3种方法,每种方法只用一条指令.<1>使CF=0 :clc ;and ax,ax ;or ax,ax<2>使AX=0 :xor ax,ax ;and ax,0 ;mov ax,0<3>同时使AX=0和CF=0:and ax,0 ;xor ax,ax ;sub ax,ax2.28、参照本习题的示意图,分析调用序列,画出每次调用与返回时的堆栈状态.其中CALL前是该指令所在的逻辑地址;另外,段内直接调用指令的机器代码的字节数为3,段间直接调用指令则为5个字节.2.29已知AX 、BX存放的是4位压缩BCD表示的十进制数,请说明如下子程序的功能和出口参数.add al,bldaaxchg al,ahadc al,bhdaaxchg al,ahret压缩BCD码加法:AX←AX+BX出口参数:AX=BCD码和2.30、AAD指令是用于除法指令之前,进行非压缩BCD码调整的.实际上,处理器的调整过程是:AL←AH×10+AL,AH←0.如果指令系统没有AAD指令,请用一个子程序完成这个调整工作.2.31、解释如下有关中断的概念:〔1〕内部中断和外部中断〔2〕单步中断和断点中断〔3〕除法错中断和溢出中断〔4〕中断向量号和中断向量表2.32、试比较INT n和段间CALL指令、IRET和段间RET指令的功能.2.33、什么是系统功能调用?汇编语言中,它的一般格式是怎样的?2.34; 补充例2.38,当有溢出时显示"Error! Overflow!〞,无溢出时显示"OK〞.okmsg db ‘OK’,‘$’errmsg db ‘Error! Overflow !’,‘$’…mov ax,Xsub ax,Yjo overflowmov dx,offset okmsgjmp nextoverflow: mov dx,errmsgnext: mov ah,9int 21h错误:mov ax,Xsub ax,Yjo overflowmov dx,offset okmsgokmsg db ‘OK’,‘$’mov dx,errmsg ;错误1:数据定义在代码中mov ah,9int 21hoverflow: errmsg db ‘Error! Overflow !’,‘$’mov dx,errmsg ; 错误2:缺少JMP指令mov ah,9int 21h2.35、补充例2.39,显示"1〞的个数;注意首先将个数转换为ASCII码.2.36、先提示输入数字"Input Number:0 ~ 9〞,然后在下一行显示输入的数字,结束;如果不是键入了0 ~ 9数字,就提示错误"Error!〞,继续等待输入数字.2.37 从键盘输入一个字符串〔不超过255个〕,将其中的小写字母转换成大写字母,然后按原来的顺序在屏幕上显示.;xt237.asm.model small.stack.dataarray db 255db 0array1 db 255 dup<'$'>array2 db 0dh,0ah,'$'.code.startupmov ah,0ah ; 键盘输入字符串mov dx,offset arrayint 21hmov dx,offset array2 ; 回车换行mov ah,09hint 21hmov bx,offset array1again: mov al,[bx]cmp al,'$'jz donecmp al,'a' ; 小于a和大于z的字符不是小写字母nextcmp al,'z'ja nextsub al,20h ; 在a和z之间的字符才是小写字母,转换为大写mov [bx],al ; 保存到原位置next: inc bxjmp againdone: mov dx,offset array1mov ah,09hint 21h.exit 0end2.38、指令对状态标志的作用可以分成多种情况,例如无影响、无定义、按结果影响、特别说明的影响等,你能区别这些情况吗?分别用具体的指令来说明.2.39、8086指令系统分成哪6个功能组?各组主要包含什么指令,举例说明.2.40、总结8086指令系统所采用的各种寻址方式,包括一般的数据寻址、外设数据寻址、堆栈数据寻址、串操作数据寻址、转移指令目的地址的寻址等,并举例说明.另外找的!第1章汇编语言基础知识〔习题1.1〕简述计算机系统的硬件组成与各部分作用.〔解答〕CPU:包括运算器、控制器和寄存器组.运算器执行所有的算术和逻辑运算;控制器负责把指指令逐条从存储器中取出,经译码分析后向机器发出各种控制命令,并正确完成程序所要求的功能;寄存器组为处理单元提供所需要的数据.存储器:是计算机的记忆部件,它用来存放程序以与程序中所涉与的数据.外部设备:实现人机交换和机间的通信.〔习题1.2〕明确下列概念或符号:主存和辅存,RAM和ROM,存储器地址和I/O端口,KB、MB、GB和TB〔解答〕主存又称内存是主存储器的简称,主存储器存放当前正在执行的程序和使用的数据,CPU可以直接存取,它由半导体存储器芯片构成其成本高、容量小、但速度快.辅存是辅助存储器的简称,辅存可用来长期保存大量程序和数据,CPU需要通过I/O接口访问,它由磁盘或光盘构成,其成本低、容量大,但速度慢.RAM是随机存取存储器的英语简写,由于CPU可以从RAM读信息,也可以向RAM写入信息,所以RAM也被称为读写存储器,RAM型半导体存储器可以按地址随机读写,但这类存储器在断电后不能保存信息;而ROM中的信息只能被读出,不能被修改,ROM型半导体通常只能被读出,但这类存储器断电后能保存信息.存储器由大量存储单元组成.为了区别每个单元,我们将它们编号,于是,每个存储单元就有了一个存储地址,I/O接口是由一组寄存器组成,为了区别它们,各个寄存器进行了编号,形成I/O地址,通常称做I/O端口.KB是千字节、MB是兆字节、GB是吉字节和TB是太字节,它们都是表示存储器存储单元的单位.〔习题1.3〕什么是汇编语言源程序、汇编程序、目标程序?〔解答〕用汇编语言书写的程序就称为汇编语言源程序;完成汇编工作的程序就是汇编程序;由汇编程序编译通过的程序就是目标程序.〔习题1.4〕汇编语言与高级语言相比有什么优缺点?〔解答〕汇编语言与高级语言相比的优点:由于汇编语言本质就是机器语言,它可以直接地、有效地控制计算机硬件,因而容易产生运行速度快,指令序列短小的高效目标程序,可以直接控制计算机硬件部件,可以编写在"时间〞和"空间〞两方面最有效的程序.汇编语言与高级语言相比的缺点:由于与处理器密切相关导致通用性差、可移植性差,汇编语言功能有限,又涉与寄存器、主存单元等硬件细节,编写汇编语言比较繁琐,调试起来也比较困难,编译程序产生的目标程序往往比较庞大、程序难以优化,运行速度慢.〔习题1.5〕将下列十六进制数转换为二进制和十进制表示〔1〕FFH 〔2〕0H 〔3〕5EH 〔4〕EFH〔5〕2EH 〔6〕10H 〔7〕1FH 〔8〕ABH〔解答〕〔1〕FFH 11111111B 255D〔2〕0H 0B 0D〔3〕5EH 1011110B 94D〔4〕EFH 11101111B 239D〔5〕2EH 101110B 46D〔6〕10H 10000B 16D〔7〕1FH 11111B 31D〔8〕ABH 10101011B 171D〔习题1.6〕将下列十进制数转换为BCD码表示〔1〕12 〔2〕24 〔3〕68 〔4〕127〔5〕128 〔6〕255 〔7〕1234 〔8〕2458〔解答〕〔1〕12 00010010〔2〕24 00100100〔3〕68 01101000〔4〕127 000100100111〔5〕128 000100101000〔6〕255 001001010101〔习题1.7〕将下列BCD码转换为十进制数〔1〕10010001 〔2〕10001001 〔3〕00110110 〔4〕10010000〔5〕00001000 〔6〕10010111 〔7〕10000001 〔8〕00000010〔解答〕〔1〕91〔2〕89〔3〕36〔4〕90〔5〕08〔6〕97〔7〕81〔8〕02〔习题1.8〕将下列十进制数分别用8位二进制数的原码、反码和补码表示〔1〕0 〔2〕-127 〔3〕127 〔4〕-57〔5〕126 〔6〕-126 〔7〕-128 〔8〕68〔解答〕〔1〕0 +0 00000000 00000000 00000000-0 10000000 11111111 00000000〔2〕-127 11111111 10000000 10000001〔3〕127 01111111 01111111 01111111〔4〕-57 10101111 11010000 11010001〔5〕126 01111110 01111110 01111110〔6〕-126 11111110 10000001 10000010〔7〕-128 10000000〔8〕68 01000100 01000100 01000100〔习题1.9〕完成下列二进制数的运算〔1〕1011+1001 〔2〕1011-1001 〔3〕1011×1001 〔4〕10111000÷1001 〔5〕1011 ∧1001 〔6〕1011 ∨1001 〔7〕~1011 〔8〕1011 ? 1001 〔解答〕〔1〕1011+1001=10100〔2〕1011-1001=0010〔3〕1011×1001=1100011〔4〕10111000÷1001=10100,余数1000〔5〕1011 ∧1001=1001〔6〕1011 ∨1001=1011〔7〕~1011=0100<8> 1011?1001=0010<?代表异或>〔习题1.10〕数码0~9、大写字母A~Z、小写字母a~z对应的ASCII码分别是多少?ASCII码为0dh、0ah对应的是什么字符?〔解答〕数码0~9:30H~39H大写字母A~Z:41H~5AH小写字母a~z:61H~7AHASCII码为0dh、0ah分别对应回车和换行控制字符.〔习题1.11〕计算机中有一个"01100001〞编码,如果把它认为是无符号数,它是十进制什么数?如果认为它是BCD码,则表示什么数?又如果它是某个ASCII码,则代表哪个字符?〔解答〕十进制无符号数:01100001B=61H=97BCD码:61ASCII码:a〔习题1.12〕简述Intel 80x86系列微处理器在指令集方面的发展.〔解答〕1978年Intel,正式推出了16位8086CPU,1979年Intel推出了准16位微处理器8088,随后,Intel 推出了80186/80188,80186/80188指令系统比8086指令系统新增了若干条实用的指令,涉与堆栈操作、移位指令、过程指令和边界检测与乘法指令,1982年Intel推出80286 CPU, 80286指令系统包括全部80186指令与新增的保护指令15条,其中有些保护方式在实方式下也可以使用,1985年,Intel80x86推出微处理器地进入第三代80386 CPU, 80386指令系统在兼容原来16位指令系统的基础上,全面升级为32位,还新增了有关位操作、条件设置指令以与控制、调试和测试寄存器的传送指令等,1989年,Intel推出了80486CPU,80486将浮点处理单元FPU集成进来,还采用了精简指令集计算机技术RISC和指令流水线方式,还新增了用于多处理器和内部Cache操作的6条指令,1993年Intel制成了俗称586的微处理器,取名Pentium.Pentium仍为32位结构,地址总线为32位,对常用的简单指令用硬件实现,重新设计指令的微代码等,Pentium新增了一条8字节比较交换指令和一条处理器识别指令,以与4条系统专用指令,1996年推出了MMX Pentium,新增了57条多媒休指令,1995年Intel推出Pentium Pro新增了3条指令,1999年推出了PentiumⅢ新增了70条SSE指令,20##推出的Pentium4新增了76条SSE2指令〔习题1.13〕什么是DOS和ROM-BIOS?〔解答〕DOS是Diskette Operating system的缩写,意思是磁盘操作系统,DOS主要是面向磁盘的系统软件,说得简单些,就是人与机器的一座桥梁,是罩在机器硬件外面的一层"外壳〞,是1981~1995年的个人电脑上使用的一种主要的操作系统.BIOS〔Basic Input/Output System〕即基本输入输出系统,通常是固化在只读存储器〔ROM〕中,所以又称为ROM-BIOS.它直接对计算机系统中的输入、输出设备进行设备级、硬件级的控制,是连接软件程序和硬件设备之间的枢纽.ROM-BIOS是计算机系统中用来提供最低级、最直接的硬件控制的程序.〔习题1.14〕简述PC机最低1MB主存空间的使用情况.〔解答〕〔1〕基本RAM区<00000H—9FFFFH>该区共640KB,由DOS进行管理.在这个区域中操作系统要占用掉一部分低地址空间,其它则向用户程序开放.〔2〕保留区RAM〔A0000H--BFFFFFH〕该区为系统安排的"显示缓冲存储区〞,共126KB,是显卡上的芯片提供支持,用于存放屏幕显示信息.但这部分地址空间实际上并没有全部使用.〔3〕扩展区ROM〔C0000H--DFFFFH〕该区128KB,由接口卡上的芯片提供支持,用于为系统不直接支持的外设安排设备驱动程序.用户固化的程序就可[安排在这一段,系统的会对它进行确认和连接.〔4〕系统区ROM〔E0000H--FFFFFH〕该区共128KB,由系统占用,它主要提供ROM--BIOS 程序,基本输入输出程序BIOS,是操作系统的重要组成部分,主要用来驱动输入输出设备,也负责系统的上电检测,磁盘引导等初始化操作,在ROM--BIOS中还有CMOS微机设置程序以与使用的字符图符信息等内容.〔习题1.15〕罗列8086CPU的8个8位和16位通用寄存器,并说明各自的作用.〔解答〕〔1〕数据寄存器:AX称为累加器,使用频度最高,用于算术、逻辑运算以与与外设传送信息等;BX称为基址寄存器,常用做存放存储器地址;CX称为计数器,作为循环和串操作等指令中的隐含计数器;DX称为数据寄存器,常用来存放双字长数据的高16位,或存放外设端口地址.〔2〕指针与变址寄存器包括SI,DI,BP,S P,四个寄存器,常用于存储器寻址时提供地址.SI是源变址寄存器,DI是目的变址寄存器,一般与DS联用确定数据段和附加段中某一存储单元地址,在串指令中,SI与DS联用、DI和ES联用,分别寻址数据段和附加段;同时,在串指令中,SI和DI还都具有自动增量或减量的功能.S P,为堆栈指针寄存器,指示栈顶的偏移地址;BP为基地址指针寄存器,表示堆栈段中的基地址.S P与BP寄存器均可与SS段寄存器联合使用以确定堆栈段中的存储单元地址.〔习题1.16〕什么是标志,它有什么用途?状态标志和控制标志有什么区别?画出标志寄存器FLAGS,说明各个标志的位置和含义.〔解答〕标志用于反映指令执行结果或控制指令执行形式.它是汇编语言程序设计中必须特别注意的一个方面,状态用来记录运行的结果的状态信息,许多指令的执行都将相应地设置它,控制标志位可由程序根据需要用指令设置,用来控制处理器执行指令的方式.CF是进位标志;ZF 是零标志;SF是符号标志;PF奇偶标志;OF溢出标志;AF辅助进位标志;DF方向标志;IF中断允许标志;TF陷阱标志.〔习题1.17〕举例说明CF和OF标志的差异.〔解答〕溢出标志OF和进位标志CF是两个意义不同的标志.进位标志表示无符号数运算结果是否超出X围,运算结果仍然正确;溢出标志表示有符号数运算结果是否超出X围,运算结果已经不正确.例1:3AH + 7CH=B6H无符号数运算:58+124=182,X围内,无进位有符号数运算:58+124=182 ,X围外,有溢出例2:AAH + 7CH=〔1〕26H无符号数运算:170+124=294,X围外,有进位有符号数运算:-86+124=28 ,X围内,无溢出〔习题1.18〕字和双字在存储器中如何存放,什么是"小端方式〞?对字和双字存储单元,什么是它们的对齐地址?为什么要对齐地址?〔解答〕字或双字在存储器中占相邻的2个或4个存储单元;存放时,低字节存入低地址,高字节存入高地址;字或双字单元的地址用它的低地址来表示.80x86处理器采用的这种"低对低,高对高〞的存储形式,被称为"小端方式〞;将字单元安排在偶地址,双字节单元安排在模4地址,被称为"地址对齐方式〞因为对于不对齐地址的数据,处理器访问时,需要额外的访问时间,所以通常应该将数据的地址对齐,以取得较高的存取速度.〔习题1.19〕什么是8086中的逻辑地址和物理地址?逻辑地址如何转换成物理地址?请将如下逻辑地址用物理地址表达:〔1〕FFFFh:0 〔2〕40h:17h 〔3〕2000h:4500h 〔4〕B821h:4567h〔解答〕在8086处理器中,对应每个物理存储单元都有一个唯一的20位编号,就是物理地址,从00000H~FFFFFH.在8086内部和用户编程时,采用的段基地址: 段内偏移地址形式称为逻辑地址.将逻辑地址中的段地址左移二进制4位〔对应16进制是一位,即乘以16〕,加上偏移地址就得到20位物理地址如下逻辑地址用物理地址表达:〔1〕FFFFh:0=FFFF0H〔2〕40h:17h=00417H〔3〕2000h:4500h=24500H〔4〕B821h:4567h=BC777H 〔不要算错〕〔习题1.20〕8086有哪4种逻辑段,各种逻辑段分别是什么用途?〔解答〕代码段〔Code Segment〕用来存放程序的指令序列.处理器利用CS : IP取得下一条要执行的指令.堆栈段〔Stack Segment〕确定堆栈所在的主存区域.处理器利用SS : SP操作堆栈中的数据.数据段〔Data Segment〕存放当前运行程序所用的数据.处理器利用DS : EA存取数据段中的数据.附加段〔Extra Segment〕是附加的数据段,也用于数据的保存.处理器利用ES : EA存取数据段中的数据〔习题1.21〕数据的默认段是哪个,是否允许其他段存放数据?如果允许,如何实现,有什么要求?〔解答〕数据的默认段是安排在数据段,也经常安排在附加段,尤其是串操作的目的区必须是附加段,允许其它段存放数据,数据的存放比较灵活的,实际上可以存放在任何一种逻辑段中,这时,只要明确指明是哪个逻辑段就可以了.〔习题1.22〕什么是操作码、操作数和寻址方式?有哪三种给出操作数的方法?〔解答〕操作码说明计算机要执行哪种操作,它是指令中不可缺少的组成部分,操作数是指令执行的参与者,也是各种操作的对象,我们把寻找数的方式叫做操作数的寻址方式.给出操作数的三种方法是直接给出,间接给出,隐藏操作数方式给出.〔习题1.23〕什么是有效地址EA?8086的操作数如果在主存中,有哪些寻址方式可以存取它?〔解答〕。

把逻辑地址转换为物理地址

• 动态地址变换:地址变换是在程序执行时由系统硬件完成从逻辑地址 到物理地址的转换的。

data1: dw 32

0x300 00000020

…

…

…

start: lw r1,0(data1)

0x900 8C2000C0

jal checkit

0x904 0C000340

loop: addi r1, r1, -1

0x908 2021FFFF

bnz loop

…

0x90C 1420FFFF

checkit: …

– 逻辑地址空间-由程序所生成的所有逻辑地址的集合;可以是一维线 性空间,也可以是多维空间

• 物理地址-把内存分成若干个大小相等的存储单元,每个单元给一 个编号,这个编号称为内存地址,即内存单元所用的地址

– 物理地址空间-与逻辑地址相对应的内存中所有物理地址的集合,一 维的线性空间

• 用户程序看不见真正的物理地址。用户只生成逻辑地址,且认为进 程的地址空间为0到max。物理地址范围从R+0到R+max,R为基 地址

– 需要硬件对动态地址变换的支持,例如基 址和限长寄存器

– 基址寄存器这时称为重定位寄存器。用户 进程所生成的地址在送交内存之前,都将 加上重定位寄存器的值。

使用重定位寄存器的动态重定位

地址变换方式

• 编程或编译时确定地址变换关系:编程时确定虚-实地址的关系是指 在用机器指令编程时,程序员直接按物理内存地址编程,这种程序在 系统中是不能做任何移动的,否则就会出错。

– 进程和内核的工作状态取决于存储在内存/寄存器中的相关数据 – 不同的进程/线程控制部分不能使用内存的同一部分

• Physics: 不同部分的数据不能使用内存的同一地址

汇编语言程序设计(第四版)第1~5章【课后答案】

第1章汇编语言基础知识〔习题1.1〕简述计算机系统的硬件组成及各部分作用。

〔解答〕CPU:包括运算器、控制器和寄存器组。

运算器执行所有的算术和逻辑运算;控制器负责把指指令逐条从存储器中取出,经译码分析后向机器发出各种控制命令,并正确完成程序所要求的功能;寄存器组为处理单元提供所需要的数据。

存储器:是计算机的记忆部件,它用来存放程序以及程序中所涉及的数据。

外部设备:实现人机交换和机间的通信。

〔习题1.2〕明确下列概念或符号:主存和辅存,RAM和ROM,存储器地址和I/O端口,KB、MB、GB和TB。

〔解答〕主存又称内存是主存储器的简称,主存储器存放当前正在执行的程序和使用的数据,CPU可以直接存取,它由半导体存储器芯片构成其成本高、容量小、但速度快。

辅存是辅助存储器的简称,辅存可用来长期保存大量程序和数据,CPU 需要通过I/O接口访问,它由磁盘或光盘构成,其成本低、容量大,但速度慢。

RAM是随机存取存储器的英语简写,由于CPU可以从RAM读信息,也可以向RAM写入信息,所以RAM也被称为读写存储器,RAM型半导体存储器可以按地址随机读写,但这类存储器在断电后不能保存信息;而ROM中的信息只能被读出,不能被修改,ROM型半导体通常只能被读出,但这类存储器断电后能保存信息。

存储器由大量存储单元组成。

为了区别每个单元,我们将它们编号,于是,每个存储单元就有了一个存储地址,I/O接口是由一组寄存器组成,为了区别它们,各个寄存器进行了编号,形成I/O地址,通常称做I/O端口。

KB是千字节、MB是兆字节、GB是吉字节和TB是太字节,它们都是表示存储器存储单元的单位。

〔习题1.3〕什么是汇编语言源程序、汇编程序、目标程序?〔解答〕用汇编语言书写的程序就称为汇编语言源程序;完成汇编工作的程序就是汇编程序;由汇编程序编译通过的程序就是目标程序。

〔习题1.4〕汇编语言与高级语言相比有什么优缺点?〔解答〕汇编语言与高级语言相比的优点:由于汇编语言本质就是机器语言,它可以直接地、有效地控制计算机硬件,因而容易产生运行速度快,指令序列短小的高效目标程序,可以直接控制计算机硬件部件,可以编写在“时间”和“空间”两方面最有效的程序。

(完整word版)综合题(word文档良心出品)

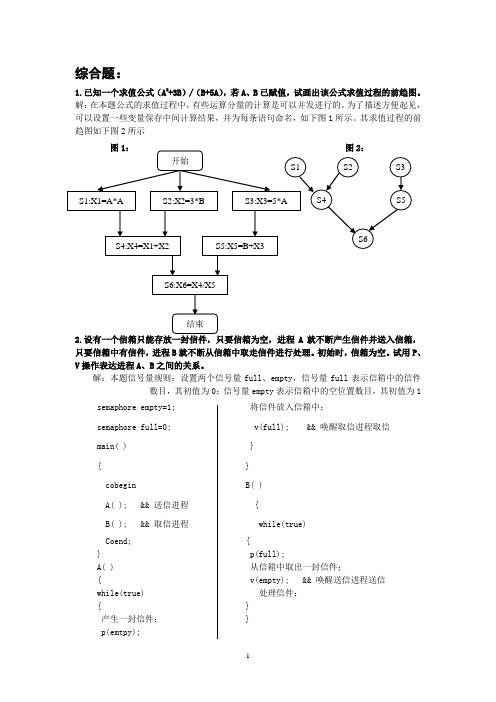

综合题:1.已知一个求值公式(A2+3B)/(B+5A),若A、B已赋值,试画出该公式求值过程的前趋图。

解:在本题公式的求值过程中,有些运算分量的计算是可以并发进行的。

为了描述方便起见,可以设置一些变量保存中间计算结果,并为每条语句命名,如下图1所示。

其求值过程的前趋图如下图2所示只要信箱中有信件,进程B就不断从信箱中取走信件进行处理。

初始时,信箱为空。

试用P、V操作表达进程A、B之间的关系。

解:本题信号量规则:设置两个信号量full、empty,信号量full表示信箱中的信件数目,其初值为0;信号量empty表示信箱中的空位置数目,其初值为1 semaphore empty=1; 将信件放入信箱中;semaphore full=0; v(full); && 唤醒取信进程取信main( ) }{ }cobegin B( )A( ); && 送信进程 {B( ); && 取信进程 while(true)Coend; {} p(full);A( ) 从信箱中取出一封信件;{ v(empty); && 唤醒送信进程送信while(true) 处理信件;{ }产生一封信件; }p(emtpy);3.有两个程序,A程序按顺序使用CPU 10秒,使用设备甲5秒,使用CPU 5秒,使用设备乙10秒,最后使用CPU 10秒。

B程序按顺序使用设备甲10秒,使用CPU 10秒,使用设备乙5秒,使用CPU 5秒,使用设备乙10秒。

在顺序执行环境下,先执行A程序,再执行B 程序,问CPU的利用率是多少?解:有题目所给条件可知,两个程序顺序执行,先执行程序A,后执行程序B。

A程序的执行时间为:10+5+5+10+10=40秒其中使用CPU的时间为:10+5+10=25秒B程序的执行时间为:10+10+5+5+10=40秒其中使用CPU的时间为:10+5=15秒两个程序的总执行时间为:40+40=80秒其中使用CPU时间为:15+25=40秒故CPU利用率为:40/80*100%=50%4.某虚拟存储器的用户编程空间共32个页面,每页为1KB,内存为16KB。

(完整word版)操作系统第四版课后习题答案

第一章1.设计现代OS的主要目标是什么?答:(1)有效性(2)方便性(3)可扩充性(4)开放性2.OS的作用可表现在哪几个方面?答:(1)OS作为用户与计算机硬件系统之间的接口(2)OS作为计算机系统资源的管理者(3)OS实现了对计算机资源的抽象5.何谓脱机I/O和联机I/O?答:脱机I/O 是指事先将装有用户程序和数据的纸带或卡片装入纸带输入机或卡片机,在外围机的控制下,把纸带或卡片上的数据或程序输入到磁带上.该方式下的输入输出由外围机控制完成,是在脱离主机的情况下进行的。

而联机I/O方式是指程序和数据的输入输出都是在主机的直接控制下进行的。

8.为什么要引入实时OS?答:实时操作系统是指系统能及时响应外部事件的请求,在规定的时间内完成对该事件的处理,并控制所有实时任务协调一致地运行.引入实时OS 是为了满足应用的需求,更好地满足实时控制领域和实时信息处理领域的需要。

13.OS有哪几大特征?其最基本的特征是什么?答:并发性、共享性、虚拟性和异步性四个基本特征;最基本的特征是并发性.17.文件管理有哪些主要功能?其主要任务是什么?答:文件管理主要功能:文件存储空间的管理、目录管理、文件的读/写管理和保护。

文件管理的主要任务:管理用户文件和系统文件,方便用户使用,保证文件安全性。

18.是什么原因使操作系统具有异步性特征?答:操作系统的异步性体现在三个方面:一是进程的异步性,进程以人们不可预知的速度向前推进,二是程序的不可再现性,即程序执行的结果有时是不确定的,三是程序执行时间的不可预知性,即每个程序何时执行,执行顺序以及完成时间是不确定的。

20.在微内核OS中,为什么要采用客户/服务器模式?答:C/S 模式具有独特的优点:⑴数据的分布处理和存储.⑵便于集中管理。

⑶灵活性和可扩充性.⑷易于改编应用软件.21.试描述什么是微内核OS。

答:1)足够小的内核2)基于客户/服务器模式3)应用机制与策略分离原理4)采用面向对象技术。

(完整word版)逻辑地址转换为物理地址

【例2】若在一分页存储管理系统中,某作业的页表如下所示。

已知页面大小为1024字节,试将逻辑地址1011,2148,4000,5012转化为相应的物理地址。

页号块号0 1 2 32 3 1 6分析页式存储管理的地址结构是一维的,即逻辑地址(或物理地址)只用一个数值即可表示。

若给定逻辑地址A,页面的大小为L,则页号p和页内地址d可按照下式求得:p=int [A/L]d=A mod L其中,int是取整函数(取数值的整数部分),mod是取余函数(取数值的余数部分).下图显示了页式管理系统的地址转换机构.页表的作用是实现从页号到物理块号的地址映射。

以逻辑地址的页号检索页表,得到该页的物理块号;同时将页内地址d直接送入物理地址寄存器的块内地址字段中。

这样物理块号和块内地址拼接成了实际访问内存的地址,从而完成了从逻辑地址到物理地址的转换。

所以物理地址的计算公式为:物理地址=块的大小(即页的大小L)′块号f+页内地址d解本题中,为了描述方便,设页号为p,页内位移为d,则:(1)对于逻辑地址1011,p=int(1011/1024)=0,d=1011 mod 1024=1011。

查页表第0页在第2块,所以物理地址为1024′2+1011=3059。

(2)对于逻辑地址2148,p=int(2148/1024)=2,d=2148 mod 1024=100。

查页表第2页在第1块,所以物理地址为1024+100=1124。

(3)对于逻辑地址4000,p=int(4000/1024)=3,d=4000 mod 1024=928。

查页表第3页在第6块,所以物理地址为1024′6+928=7072.(4)对于逻辑地址5012,p=int(5012/1024)=4,d=5012 mod 1024=916。

因页号超过页表长度,该逻辑地址非法。

【例3】某虚拟存储器的用户编程空间共32个页面,每页为1KB,内存为16KB.假定某时刻一用户页表中已调入内存的页面的页号和物理块号的对照表如下:则逻辑地址0A5C(H)所对应的物理地址是什么?分析页式存储管理的逻辑地址分为两部分:页号和页内地址.由已知条件“用户编程空间共32个页面",可知页号部分占5位;由“每页为1KB",1K=210,可知内页地址占10位.由“内存为16KB”,可知有16块,块号为4位。

逻辑地址如何转换成物理地址

逻辑地址如何转换成物理地址逻辑地址和物理地址是什么?逻辑地址如何转换成物理地址?看到很多人都在问这个问题,小编为大家分享了逻辑地址如何转换成物理地址的方法,下面大家跟着小编一起来了解一下吧。

逻辑地址转换成物理地址CPU将一个虚拟内存空间中的地址转换为物理地址,需要进行两步:首先将给定一个逻辑地址(其实是段内偏移量,这个一定要理解!!!),CPU要利用其段式内存管理单元,先将为个逻辑地址转换成一个线程地址,再利用其页式内存管理单元,转换为最终物理地址。

物理地址(physical address)用于内存芯片级的单元寻址,与处理器和CPU连接的地址总线相对应。

——这个概念应该是这几个概念中最好理解的一个,但是值得一提的是,虽然可以直接把物理地址理解成插在机器上那根内存本身,把内存看成一个从0字节一直到最大空量逐字节的编号的大数组,然后把这个数组叫做物理地址,但是事实上,这只是一个硬件提供给软件的抽像,内存的寻址方式并不是这样。

所以,说它是“与地址总线相对应”,是更贴切一些,不过抛开对物理内存寻址方式的考虑,直接把物理地址与物理的内存一一对应,也是可以接受的。

也许错误的理解更利于形而上的抽像。

虚拟内存(virtual memory)这是对整个内存(不要与机器上插那条对上号)的抽像描述。

它是相对于物理内存来讲的,可以直接理解成“不直实的”,“假的”内存,例如,一个0x08000000内存地址,它并不对就物理地址上那个大数组中0x08000000 - 1那个地址元素;之所以是这样,是因为现代操作系统都提供了一种内存管理的抽像,即虚拟内存(virtual memory)。

进程使用虚拟内存中的地址,由操作系统协助相关硬件,把它“转换”成真正的物理地址。

这个“转换”,是所有问题讨论的关键。

有了这样的抽像,一个程序,就可以使用比真实物理地址大得多的地址空间。

(拆东墙,补西墙,银行也是这样子做的),甚至多个进程可以使用相同的地址。

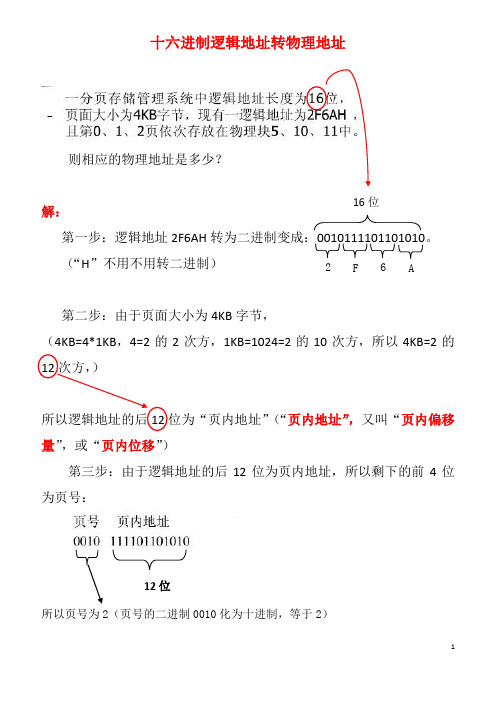

分页存储--逻辑地址转物理地址

十六进制逻辑地址转物理地址则相应的物理地址是多少?解:第一步:逻辑地址2F6AH 转为二进制变成:0010111101101010。

(“H ”不用不用转二进制)第二步:由于页面大小为4KB 字节,(4KB=4*1KB ,4=2的2次方,1KB=1024=2的10次方,所以4KB=2的(“页内地址”,又叫“页内偏移量”,或“页内位移”)第三步:由于逻辑地址的后12位为页内地址,所以剩下的前4位为页号:所以页号为2(页号的二进制0010化为十进制,等于2)16位26FA第五步:由于页号为2,所以从页表中可以查出对应的帧号为11,而“11”的十六进制为B第六步:所以逻辑地址对应的物理地址为: 页号 页内地址 1011 111101101010 化成十六进制为:BF6AH 。

(实际把原来逻辑地址2F6AH 的2换成B 就可以了,因为页内地址没变)答案:物理地址为BF6AH。

逻辑地址2F6AH 的2十进制逻辑地址转物理地址已知某个分页系统,页面大小为1K(即1024字节),某一个作业有4个页面,分别装入到主存的第3、4、6、8块中,求逻辑地址2100对应的物理地址。

解:第一步:求逻辑地址的页号 = 2100 / 1024 = 2 (整除)第二步:求页内偏移量 = 2100 % 1024 = 52 (取余)第三步:产生页表第四步:根据逻辑地址的页号查出物理地址的帧号:逻辑地址的第2页对应物理地址第6页。

第五步:求出物理地址 = 6 * 1024 + 52 = 6196页面大小6 * 1024 + 52 = 6196物理地址页面大小“虚地址”、“逻辑地址”、“相对地址”这三个概念是等价的。

“实地址”、“物理地址”、“绝对地址”这三个概念是等价的。

地址转换步骤当逻辑地址为16进制、八进制、二进制时,第一步:把逻辑地址转为二进制;第二步:按页的大小分离出页号和页内偏移量(高位部分为页号,低位部分为页内偏移量)第三步:根据题意产生页表;第四步:将逻辑地址的页内偏移量直接复制到物理地址的页内偏移量上(即:逻辑地址的页内偏移量= 物理地址的页内偏移量)第五步:以逻辑地址的页号查页表,查出物理地址的帧号,再把帧号转为二进制,复制到物理地址的的帧号上,从而得出物理地址。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

】若在一分页存储管理系统中,某作业的页表如下所示。

已知页面大2【例转化为相应,5012,10112148,4000小为1024字节,试将逻辑地址的物

理地址。

块号页号20

31

12

63

分析页式存储管理的地址结构是一维的,即逻辑地址(或物理地址)只用一个数值即可表示。

若给定逻辑地址A,页面的大小为L,则页号p和页内地址d可按照下式求得:

p=int [A/L]d=A mod L

其中,int是取整函数(取数值的整数部分),mod是取余函数(取数值的余

数部分)。

下图显示了页式管理系统的地址转换机构。

页表的作用是实现从页号到物理块号的地址映射。

以逻辑地址的页号检索页表,

得到该页的物理块号;同时将页内地址d直接送入物理地址寄存器的块内地址

字段中。

这样物理块号和块内地址拼接成了实际访问内存的地址,从而完成了从逻辑地址到物理地址的转换。

所以物理地址的计算公式为:

物理地址=块的大小(即页的大小L)′块号f+页内地址d

解本题中,为了描述方便,设页号为p,页内位移为d,则:

(1)对于逻辑地址1011,p=int(1011/1024)=0,d=1011 mod 1024=1011。

查页表第0页在第2块,所以物理地址为1024′2+1011=3059。

(2)对于逻辑地址2148,p=int(2148/1024)=2,d=2148 mod 1024=100。

查页表第2页在第1块,所以物理地址为1024+100 。

1124=

(3)对于逻辑地址4000,p=int(4000/1024)=3,d=4000 mod 1024=928。

查页表第3页在第6块,所以物理地址为1024′6+928=7072。

(4)对于逻辑地址5012,p=int(5012/1024)=4,d=5012

mod 1024=916。

因页号超过页表长度,该逻辑地址非法。

【例3】某虚拟存储器的用户编程空间共32个页面,每页为1KB,内存为16KB。

逻辑地址0A5C(H)所对应的二进制表示形式是:000 1010 0101 1100,根据上面的分析,下划线部分为页内地址,编码“000 10”为页号,表示该逻辑地址对应的页号为2。

查页表,得到物理块号是4(十进制),即物理块地址为:01 00 ,拼接块内地址10 0101 1100,得01 0010 0101 1100,即125C(H)。

解逻辑地址0A5C(H)所对应的物理地址是125C(H)。