计算机组成原理课设 定点原码一位除法器的设计

2020年恢复余数法定点原码一位除法器的设计精品版

****************课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:恢复余数法定点原码一位除法器的设计院(系):*************专业:*************班级:*************学号:*************姓名:*************指导教师:*************完成日期:*************目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (1)1.3设计环境 (3)第2章详细设计方案 (4)2.1顶层方案图的设计与实现 (4)2.1.1创建顶层图形设计文件 (4)2.1.2器件的选择与引脚锁定 (5)2.1.3 编译、综合、适配 (6)2.2功能模块的设计与实现 (6)2.2.1寄存器模块的设计与实现 (6)2.2.2数据选择器模块的设计与实现 (8)2.2.3补码器模块的设计与实现 (12)2.2.4加法器模块的设计与实现 (13)2.2.5移位寄存器模块的设计与实现 (15)2.3仿真调试 (18)第3章编程下载与硬件测试 (20)3.1编程下载 (20)3.2硬件测试及结果分析 (20)参考文献 (22)附录(电路原理图) (23)第1章总体设计方案1.1 设计原理定点原码一位除法器的原理是根据人工进行二进制除法的规则:判断被除数与除数的大小,若被除数小,则上商0,并在余数最低位补0,再用余数和右移一位的除数比,若够除,则上商1,否则上商0。

然后继续重复上述步骤,直到除尽(即余数为0)或已得到的商的位数满足精度要求为止。

上述计算方法要求加法器的位数为除数位数的两倍。

但分析后,会发现右移除数,可以通过左移被除数(余数)来代替,左移出界的被除数(余数)的高位都是无用的0,对运算不会产生任何影响。

另外,上商0还是1是计算者用观察比较的办法确定的,而计算机只能用做减法判断结果的符号为负还是为正来确定。

当差为负时,上商为0,同时还应把除数再加到差上去,恢复余数为原来的正值之后再将其左移一位。

计算机组成原理除法课程设计

课程设计说明书题目: 设计指令系统院系:计算机科学与工程学院专业班级:计算机10-03班学号: 2010303089学生姓名:胡敬杰指导教师:刘向举2013年1 月10日安徽理工大学课程设计(论文)任务书计算机科学与工程学院监控与嵌入式技术系学号2010303089 学生姓名胡敬杰专业(班级)计算机10-3班设计题目设计指令系统设计技术参数1.本系统采用DJ-CPTH超强型计算机组成原理教学实验系统搭建电路图,在实验箱上实现指令系统。

2.利用软件工程中的可行性研究以及分析方法,进行系统分析。

设计要求1在基本模型机的基础上设计取数、存数、输入、输出、与、或、非、加法、减法、移位指令等,用这些指令的助记符不得与指导书上相同。

2.指令包括立即数寻址、寄存器直接寻址、存储器直接寻址三种寻址方式。

3.利用新构建的指令系统编程,分别实现求补、同或、异或、乘法、除法、两存储单元数据交换等功能。

工作量1.课程设计说明书2000字;2.画出流程图,编写微指令代码和程序。

工作计划1.首先认真研究老师所给的题目,了解题目要求做什么。

2.查阅资料,解决难题。

3.编写源程序并调试之。

4.写课程设计说明书参考资料[1] 蒋本珊.计算机组成原理(第2版).北京:清华大学出版社,2011[2] 白中英.计算机组成原理(第二版).北京:科学出版社,2008[3] DJ-CPTH超强型计算机组成原理与系统结构实验指导书[4] 沈美明.汇编语言程序设计北京:清华大学出版社指导教师签字教研室主任签字2012年 12月17日安徽理工大学课程设计(论文)成绩评定表指导教师评语:成绩:指导教师:年月日摘要本次计算机组成原理课程设计课题是基本模型机的设计与实现。

利用CPU与简单模型机来实现计算机组成原理课程设计,编写指令的应用程序,用微程序控制器实现一系列的指令功能,最终达到将理论与实践相联系。

本次设计完成了相关指令的格式以及编码的设计,实现了机器指令微代码,完成具有一定功能的程序。

最新 《计算机组成原理》之定点运算器的课件设计与开发-精品

摘要:《组成原理》之定点运算器的课件设计与开发利用Flash的强大功能,它集成了文字、图像、声音、动画、视频等多媒体信息,能更好的实现多媒体教学,使学习者加深对所学知识的理解,提高学生学习兴趣和教学效率,同时也能为课件增加生动的效果。

《计算机组成原理》之定点运算器的课件共设计和开发了6个模块:“数据与文字的表示方法”、“定点加减运算”、“定点乘法运算”、“定点除法运算与阵列除法器”、“定点运算器的组成”、“浮点运算方法和浮点运算器”。

关键词:计算机组成原理;定点运算器;Flash;Photoshop 中图分类号:TP393文献标识码:A文章编号:1009-3044(2011)28-6988-02 The Courseware Design and Development for the Fixed-point Arithmetic in the Principle of Computer Organization CHEN Si-si, WANG Feng (College of Physics and Electronic Information Engineering, Wenzhou University, Wenzhou 325035, China) Abstract: The courseware design and development for the fixed-point arithmetic in the Principles of Computer Composition includes six modules: "the representation of data and text", "fixed-point addition and subtraction", "the multiplication of fix-point", "the divide of fix-point and the array of the division", "the composition of the fix-point arithmetic", "the methods of the floating point and the floating arithmetic". Key words: multimedia; constitution principle of computer; fix-point arithmetic; flash 目前,《计算机组成原理》之定点运算器[1-2]的课件仅限于用Powerpoint制作,用这种技术做的PPT很枯燥不能调动学生学习的兴趣,而用Flash制作课件可以生动形象的描述各种教学问题,有效激发学生的学习兴趣,增加教学效果,提高教学效率,具有传统教学所不能比拟的优越性。

定点原码一位除法器的设计

课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:定点原码一位除法器的设计(系):业: 级: 号: 名:指导教师:完成日期:第1章总体设计方案1.1设计原理1.2设计环境第2章详细设计方案2.1顶层方案图的设计与实现.......2.1.1创建顶层图形设计文件........2.1.2器件的选择与引脚锁定........2.2功能模块的设计与实现.........2.2.1选择移位模块的设计与实现.2.2.2余数选择器模块的设计与实现2.2.3控制器模块的设计与实现... 2.3仿真调试...................... 第3章编程下载与硬件测试.......... . (4) (4) (4) (6) (6) (9)..10 .11.133.1编程下载..........3.2硬件测试及结果分析参考文献............... 13 13 14第1章总体设计方案1.1 设计原理定点原码一位除法的计算有恢复余数和加减交替两种算法,商的符号为除数与被除数两符号位的异或值,数值则为两数绝对值相除后的结果。

此设计方案仅采用恢复余数法进行设计。

恢复余数定点原码一位除法器实现的功能如表 1.1所示,设计的电路应实现表1.1中给定的功能。

设:X=X0 X1……X nY=Y0 Y1……Y nX0 X1,丫0丫1分别为符号位,K为两符号位的异或值X/Y=K*|X|/|Y||X|/|Y|利用恢复余数法求的,在计算机中,商只能用做减法判结果的符号为正还是为负来确定。

当差为负时,上商为0,同时还应该把除数再加到差上去,恢复余数为原来的正值之后再左移一位。

若减得的差为0或为正值时,就没有恢复余数的操作,上商为1,余数左移一位。

其计算过程如下:例:已知:X=0.0100丫=0.1000求:X/Y表1.1恢复余数定点原码一位除法器功能表恢复余数定点原码一位除法器的整体设计包含两输入寄存器模块,一个加法运算模块,一个余数移位模块,一个商移位模块和一个由触发器和计数器构成的控制模块,移位模块采用Verilog设计输入方式,其余采用原理图设计输入方式。

不恢复余数法定点原码一位除法器的的设计汇总

沈阳航空航天大学课程设计报告目录学术诚信声明 ................................................................................... 错误!未定义书签。

第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (1)1.3设计环境 (2)第2章详细设计方案 (3)2.1顶层方案图的设计与实现 (3)2.1.1创建顶层图形设计文件 (3)2.1.2器件的选择与引脚锁定 (4)2.1.3编译、综合、适配 (5)2.2功能模块的设计与实现 (6)2.2.1 输入模块的设计与实现 (6)2.2.移位模块的设计与实现 (7)2.2.3加法器模块的设计与实现 (9)2.2.4 相反补码模块的设计与实现 (10)2.3仿真调试 (11)第3章编程下载与硬件测试 (13)3.1编程下载 (13)3.2硬件测试及结果分析 (13)参考文献 (15)附录(电路原理图) (16)第1章总体设计方案1.1 设计原理减交替法的实现是当某一次求得的差值(余数Ri)为负时,不恢复它,继续求下一位的商,但用加上除数(+[—Y]补)的办法来取代(-Y)的操作,其他操作依然不变。

(1)当余数为正时,商上“1”,求下一位商的办法是余数左移一位,再减去除数;(2)当余数为负数时,商上“0”,求下一位商的办法是余数左移一位,再加上除数。

(3)这种方法不用恢复余数,但若最后一次上商为“0”,而又需要得到正确的余数,则在这最后一次仍需恢复余数。

1.2 设计思路课程设计的要求为:(1)采用定点原码一位除法器由一个除数寄存模块,一个被除数寄存模块,一个加法模块,一个移位模块,一个移位模块、一个商寄存模块,采用逻辑电路设计输入方式。

(2)定点原码一位除法器的顶层采用原理图设计输入方式。

课程设计的思路为:(1)由于是不恢复余数法,所以需要修正余数为负的情况,所以原理图如图1.2:图1.2 不恢复余数法一位除法器设计总框图1.3 设计环境(1)硬件环境•伟福COP2000型计算机组成原理实验仪COP2000计算机组成原理实验系统由实验平台、开关电源、软件三大部分组成实验平台上有寄存器组R0-R3、运算单元、累加器A、暂存器B、直通/左移/右移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单元、微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总线插孔区、微动开关/指示灯、逻辑笔、脉冲源、20个按键、字符式LCD、RS232口。

计算机组成原理第2章4-定点原码一位乘法运算

从例中可知:(1)两个n位数参加乘法运算要做n次加法和移位操作。 (2)用循环累加和移位操作实现乘法运算。

信 息 科 学 与 工 程 学 院9

第二章 运算方法和运算器

原码一位乘法逻辑结构原理图

部分积Z R0

加数器

LDR0 ∑/2Z

Yn

乘数Y R1

Yn Yn

LDR1 Y/2Y

Zs

计数器i T1 , T2, … +1

信 息 科 学 与 工 程 学 院5

第二章 运算方法和运算器

原码一位乘法(4/7)

令Zi表示第i次部分积,则上式可写成如下递推公式:

z0=0

z1=2-1(ynx+z0)

z2=2-1(yn-1x+z1) i+1

iቤተ መጻሕፍቲ ባይዱ

:

zi=2-1(yn-i+1x+zi-1) :

zn=x•y=2-1(y1x+zn-1)

显然,欲求x·y,则需设置一个保存部分积的累加器。乘法开始时,令部分积 的初值z0=0,然后求ynx加上z0,右移1位得第1个部分积z1。又将yn-1加上z1, 再右移1位得第2个部分积z2.依此类推,直到求得y1x加上zn-1并右移1位得最 后部分积zn,即得乘积x·y=zn。显然,两个n位数相乘,需重复进行n次“加” 及"右移”操作,才能得到最后乘积。这就是实现原码一位乘法的规则.

Ti

R

Cx

S

Q 乘法启动

被乘数X

R2

Xs Ys

信 息 科 学 与 工 程 学 1院0

第二章 运算方法和运算器

原码一位乘法(6/7)

工作原理 (I) 乘法开始时,“启动”信号使控制触发器Cx置“1”,于是开启时序脉冲T。 (II) 当乘数寄存器R1最末位为“1”时,部分积Zi和被乘数X在加法器中相加,其 结果输出至R0的输入端。 (III)一旦打入控制脉冲T到来,控制信号LDR0使部分积右移一位,与此同时,R1 也在控制信号LDR1作用下右移一位,且计数器i计数一次。 (IV)当计数器i=n时,计数器的溢出信号使触发器Cx置“0”,关闭时序脉冲T, 乘法宣告结束。 若将R0和R1连接起来,乘法结束时乘积的高n位部分在R0,低n位部分在R1,R1中 原来的乘数Y由于移位而全部丢失。所得乘积为2n+1位(其中包括1位符号位).

计算机组成原理教案(第二章)

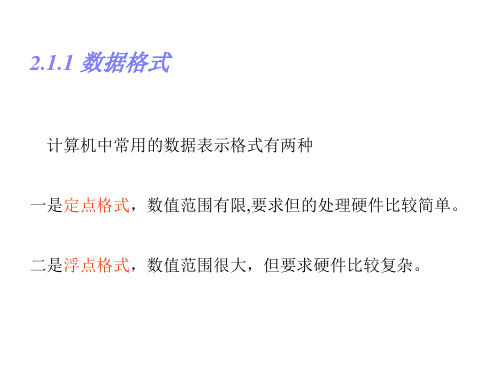

为便于软件移植,按照 IEEE754 标准,32位浮点数和 64位浮点数的标准格式为

浮点数 符号位

小数点 (隐含的)

阶符采用隐含方式,即采用移码方式来表示正负指数。

将浮点数的指数真值e 变成阶码E 时,应将指数 e 加上 一个固定的偏移值127(01111111),即 E=e+127.

不规格的例子:

2.1.5 校验码

最简单且应用广泛的检错码是采用一位校验位的奇校验或偶校验

设x=(x0x1…xn-1)是一个n位字,则奇校验位C定义为 C=x0⊕x1⊕…⊕xn-1

式中⊕代表按位加,表明只有当x中包含有奇数个1时,才使C=1, 即C=0。

同理,偶校验位C定义为

C=x0⊕x1⊕…⊕xn-1

即x中包含偶数个1时,才使C=0。

[例4]将十进制真值(-127,-1,0,+1,+127)列表表示成二进制数及原 码、反码、补码、移码值。

[例5]设机器字长16位,定点表示,尾数15位,数符1位,问: (1)定点原码整数表示时,最大正数是多少?最小负数是多少?

(2)定点原码小数表示时,最大正数是多少?最小负数是多少?;

(1)定点原码整数表示 最大正数值=(215-1)10=(+32767)10 0 111 111 111 111 111

0.1011

1.0101

10.0000 0.0000

对定点整数,补码表示的定义是 [x]补= {

x

2n>x≥0 (mod 2n+1)

2n+1+x=2n+1-|x| 0≥x≥-2n

3.反码表示法

我们比较定点小数反码与补码的公式 [x]反=(2-2-n)+x [x]补=2+x

[x]补=[x]反+2-n

计算机组成原理课设 定点原码一位除法器的设计

沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:定点原码一位除法器的设计院(系):计算机学院专业:计算机科学与技术班级:94010101学号:2009040101013姓名:胡桂林指导教师:周大海完成日期:2012年1月13日沈阳航空航天大学课程设计报告目录第1章总体设计方案 (1)1.1设计环境 (1)1.2设计原理 (2)第2章详细设计方案 (4)2.1总流程图 (4)2.2上商置0模块流程图 (6)2.3上商置1模块流程图 (6)2.4商的符号流程图 (7)第3章测试结果 (9)3.1程序仿真 (9)3.2仿真测试一 (9)3.3仿真测试二 (10)附录 (11)参考文献 (14)第1章总体设计方案1.1 设计环境伟福COP2000实验箱,用汇编语言编程实现定点原码一位除法器COP2000 计算机组成原理实验系统由实验平台、开关电源、软件三大部分组成。

实验平台上有寄存器组R0-R3、运算单元、累加器A、暂存器W、直通/左移/右移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单元、微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总线插孔区、微动开关/指示灯、逻辑笔、脉冲源、20 个按键、字符式LCD、RS232 口。

COP2000集成调试软件(即仿真测试软件)共分为6部分:(1)主菜单区实现实验仪的各项功能的菜单,包括[文件][编辑][汇编][运行][帮助]五大项,各项线面做详细介绍。

(2)快捷图标区快速实现各项功能按键(3)源程序/机器码区在此区域有源程序窗口,反汇编窗口,EM程序代码窗口。

源程序用于输入,显示,编辑汇编源程序:反汇编窗口显示程序编译后的机器码及反汇编的程序;EM程序代码窗口用数据方式机器码。

(4)机构图/逻辑波形区结构图能结构化显示模型机的各部件,以及运行时数据走向寄存器值;逻辑波形图能显示模型机运行时所有信号的程序。

恢不复余数法定点原码一位除法器的的设计

沈阳航空航天大学课程设计报告目录学术诚信声明 ................................................................................. 错误!未定义书签。

第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (1)1.3设计环境 (2)第2章详细设计方案 (3)2.1顶层方案图的设计与实现 (3)2.1.1创建顶层图形设计文件 (3)2.1.2器件的选择与引脚锁定 (4)2.1.3编译、综合、适配 (5)2.2功能模块的设计与实现 (6)2.2.1 输入模块的设计与实现 (6)2.2.移位模块的设计与实现 (7)2.2.3加法器模块的设计与实现 (9)2.2.4 相反补码模块的设计与实现 (10)2.3仿真调试 (11)第3章编程下载与硬件测试 (13)3.1编程下载 (13)3.2硬件测试及结果分析 (13)参考文献 (15)附录(电路原理图) (16)第1章 总体设计方案1.1 设计原理减交替法的实现是当某一次求得的差值(余数Ri )为负时,不恢复它,继续求下一位的商,但用加上除数(+[—Y]补)的办法来取代(-Y )的操作,其他操作依然不变。

(1)当余数为正时,商上“1”,求下一位商的办法是余数左移一位,再减去除数;(2)当余数为负数时,商上“0”,求下一位商的办法是余数左移一位,再加上除数。

(3)这种方法不用恢复余数,但若最后一次上商为“0”,而又需要得到正确的余数,则在这最后一次仍需恢复余数。

1.2 设计思路课程设计的要求为:(1)采用定点原码一位除法器由一个除数寄存模块,一个被除数寄存模块,一个加法模块,一个移位模块,一个移位模块、一个商寄存模块,采用逻辑电路设计输入方式。

(2)定点原码一位除法器的顶层采用原理图设计输入方式。

课程设计的思路为:(1)由于是不恢复余数法,所以需要修正余数为负的情况,所以原理图如图1.2:被除数加法器求补器除数加法器商寄存器余数寄存器图1.2 不恢复余数法一位除法器设计总框图1.3 设计环境(1)硬件环境•伟福COP2000型计算机组成原理实验仪COP2000计算机组成原理实验系统由实验平台、开关电源、软件三大部分组成实验平台上有寄存器组R0-R3、运算单元、累加器A、暂存器B、直通/左移/右移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单元、微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总线插孔区、微动开关/指示灯、逻辑笔、脉冲源、20个按键、字符式LCD、RS232口。

COP2000实现原码一位除法.

沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:COP2000实现原码一位除法院(系):计算机学院专业:计算机科学与技术班级:24010103学号:******************指导教师:***完成日期:2015年01月15日沈阳航空航天大学课程设计报告目录第1章总体设计方案 (2)1.1设计原理 (2)1.2设计思路 (2)1.3设计环境 (2)第2章详细设计方案 (4)2.1总体方案的设计与实现 (4)2.1.1总体方案的逻辑图 (4)2.1.2算法流程图 (5)2.2功能模块的设计与实现 (6)2.2.1 模块的设计与实现 (6)第3章验证测试 (9)3.1验证测试 (9)参考文献 (10)附录(源代码) (11)第1章总体设计方案1.1设计原理原码一位除,即两个原码数相除,商的符号为除数和被除数的符号异或值。

采用汇编语言实现定点原码一位除法器,算法为恢复余数法。

利用恢复余数的方法来进行运算。

1.2设计思路算法为恢复余数法,先用被除数减去除数,如果结果为正数商1,然后左移,如果是负数商0然后加上Y的补,继续运算。

实验开始时将实验数据从实验箱的开关输入到R0,R1,R2三个寄存器中,R0为被除数,R1为除数,R2为商。

运算过程采用恢复余数法。

主要判断被除数减去除数的商值。

如果为负,商0然后加除数然后左移。

如果商值为正商1,左移。

数据都存放在寄存器中,最后结果在OUT寄存器中显示。

1.3设计环境COP2000 模型机包括了一个标准CPU 所具备所有部件,这些部件包括:运算器ALU、累加器A、工作寄存器W、左移门L、直通门D、右移门R、寄存器组R0-R3、程序计数器PC、地址寄存器MAR、堆栈寄存器ST、中断向量寄存器IA、输入端口IN、输出端口寄存器OUT、程序存储器EM、指令寄存器IR、微程序计数器uPC、微程序存储器uM,以及中断控制电路、跳转控制电路。

计算机组成原理》课程设计报告

课程设计说明书《计算机组成原理》算法实现(五)专业 计算机科学与技术学生夏晶晶 班级 M 计算机101 学号1051401122指导教师花小朋完成日期2013年6月21日目录1 课程设计目的 (2)2 课程设计容与要求 (2)2.1课程设计的容 (2)2.2 课程设计的要求 (2)3 实现方法 (2)3.1 系统目标 (2)3.2 主体设计 (4)3.2.1 主窗体的设计 (4)3.2.2 定点整数真值还原窗体的设计 (6)3.2.3 定点整数单符号位补码加减法 (8)3.2.4 定点整数的原码乘法 (10)3.2.5 浮点数的加减运算 (12)4 设计小结 (13)参考文献 (13)1 课程设计目的本课程设计是在学完本课程教学大纲规定的全部容、完成所有实践环节的基础上,旨在深化学生学习的计算机组成原理课程基本知识,进一步领会计算机组成原理的一些算法,并进行具体实现,提高分析问题、解决问题的综合应用能力。

2 课程设计容与要求2.1课程设计的容计算机组成原理算法实现(五)2.2 课程设计的要求能够实现机器数的真值还原(定点整数)、定点整数的单符号位补码加减运算、定点整数的原码乘法运算和浮点数的加减运算。

3 实现方法3.1 系统目标本程序含有以下几个功能模块,分别能够实现如设计容所设计的功能。

共有5个类,各类之间的关系如图3-1所示:系统流程图:3.2 主体设计3.2.1 主窗体的设计程序菜单需要在输入口令正确后方可使用,若口令输入错误需给出重新输入口令的提示,三次口令输入错误则禁止使用。

登陆算法的流程图:输入密码判断密码计数器减1激活菜单栏隐藏登陆显示欢迎界面弹出错误窗口判断计数器值是否大于零结束开始3.2.2 定点整数真值还原窗体的设计选择主窗体中“机器数的真值还原(定点整数)”时进入下图所示的窗体。

在上面的窗体中按“输入”按扭时,将输入焦点设置为最上面的一个文本框上。

输入一个机器数(如10001000)后,按“原->真值”、“反->真值”、“补->真值”或“移->真值”按扭中的任一个后,将在第二文本框中显示对应操作的结果。

计算机组成原理课设_定点补码一位乘法器的设计

课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:定点补码一位乘法器的设计院(系):计算机学院专业:计算机科学与技术班级:*****学号:*****姓名:*****指导教师:*****完成日期:2006年12月31日沈阳航空工业学院课程设计报告目录第1章总体设计方案 (2)1.1补码乘法器设计原理 (2)1.2设计思路 (4)1.3设计环境 (5)第2章详细设计方案 (5)2.1补码乘法器电路图的设计与实现 (6)2.1.1 补码乘法器设计 (6)2.1.2 器件的选择与引脚锁定 (8)2.1.3 编译、综合、适配 (8)2.2功能模块的设计与实现 (9)2.2.1 两输入三选一选择器模块的设计与实现 (9)2.2.2 半加器模块的设计与实现 ........................................... 错误!未定义书签。

2.3仿真调试 (10)第3章编程下载与硬件测试 (12)3.1编程下载 (12)3.2硬件测试及结果分析 (12)参考文献 (14)第1章总体设计方案1.1 补码乘法器设计原理原码乘法的主要问题是符号位不能参加运算,单独用一个异或门产生乘积的符号位,故自然提出能否让符号数字化后也参加乘法运算,补码乘法就可以实现符号位直接参加运算。

布斯(Booth)算法,它采用相加和相减的操作计算补码数据的乘积,Booth算法对乘数从低位开始判断,根据两个数据位的情况决定进行加法、减法还是仅仅移位操作。

Booth算法操作表示判断的两个数据位为当前位及其右边的位(初始时需要增加一个辅助位0),移位操作是向右移动。

判断被乘数中的最低位以及右边的位(辅助位0),如果为00,则只进行移位操作;之后在判断移位之后的最后两位,如果为01,则进行加法操作并进行移位操作;如果最后两位为10,则进行减法操作并移位,这个减法操作相当于减去2x的值;判断最后的差值,如为1,则部分积加[X]补;如为0,则不分积加0;如为-1,则部分积加[-X]补,最后一次不移位。

定点原码一位乘法器的设计 (2)

沈阳航空工业学院课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:定点原码一位乘法器的设计院(系):计算机学院专业:计算机科学与技术班级:4401102学号:*****************指导教师:***完成日期:2006年12月31日目录第1章总体设计方案 (1)1.1设计原理................................................................................................ .1 1.2 设计思路 (3)1.3 设计环境 (3)第2章详细设计方案................................................................................... . 4 2.1 顶层原理的设计与实现. (4)2.1.1创建顶层图形设计文件 (4)2.1.2器件的选择与引脚锁定 6 2.1.3编译、综合、适配 (6)2.2 功能模块的设计与实现 (7)2.2.1移位电路模块的设计与实现 (7)2.2.2 二选一选择器模块的设计与实现 (8)2.2.3移位寄存器模块的设计与实现 (8)2.2.4控制电路模块的设计与实现 (9)2.3 仿真调试 (10)第3章编程下载与硬件测试 (12)3.1 编程下载 (12)3.2 硬件测试及结果分析 (12)参考文献 (13)附录(电路原理图) (14)第1章总体设计方案1.1 设计原理在定点计算机中,两个原码表示的数相乘的运算规则是:乘积的符号位由两数的符号按异或运算得到,而乘积的数值部分则是两个数相乘之积。

设n位被乘数和乘数用定点小数表示(定点整数也同样适用)被乘数[x]原 = x f .x0 x1 x2 … x n乘数[y]原 = y f .y0 y1 y2 … y n= ( x f⊕y f ) . (0. x0 x1 x2 …x n)(0 . y1 y2 …y n)则乘积[ z ]原式中,x f为被乘数符号,y f为乘数符号。

加减交替法定点原码一位除法器

课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:加减交替法定点原码一位除法器设计院(系):专业:班级:学号:姓名:指导教师:完成日期:目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (2)1.3设计环境 (3)第2章详细设计方案 (5)2.1顶层方案图的设计与实现 (5)2.1.1创建顶层图形设计文件 (5)2.1.2器件的选择与引脚锁定 (6)2.1.3编译、综合、适配 (7)2.2功能模块的设计与实现 (7)2.2.1输入寄存器的设计与实现 (7)2.2.2 选择器模块的设计与实现 (9)2.2.3 移位电路模块的设计与实现 (11)2.2.4 加法器模块的设计与实现 (12)2.2.5 相反数补码模块的设计与实现 (14)2.2.6 控制器模块的设计与实现 (15)2.2.7 商寄存器模块的设计与实现 (17)2.2.8 恢复余数寄存器模块的设计与实现 (18)2.3仿真调试 (21)第3章编程下载与硬件测试 (22)3.1编程下载 (22)3.2硬件测试及结果分析 (22)参考文献 (26)附录(电路原理图) (27)第1章总体设计方案1.1 设计原理定点除法运算有两种不同的实现方法,一种是恢复余数法,即在运算过程中,必须先算减法,若余数为正,才知道够减,若余数为负,则知道不够减,不够减时必须恢复原来的余数,以便再继续往下运算。

另一种是不恢复余数法,又称加减交替法,此次设计即是采用加减交替法来实现四位二进制数的定点原码一位除法。

加减交替法的实现是对恢复余数法的一种修正,当某一次求得的差值(余数Ri)为负时,不恢复它,继续求下一位的商,但用加上除数(+[—Y]补)的办法来取代(-Y)的操作,其他操作依然不变。

即:(1)当余数为正时,商上“1”,求下一位商的办法是余数左移一位,再减去除数;(2)当余数为负数时,商上“0”,求下一位商的办法是余数左移一位,再加上除数。

恢复余数法定点原码一位除法器设计方案

****************课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:恢复余数法定点原码一位除法器的设计院(系):*************专业:*************班级:*************学号:*************姓名:*************指导教师:*************完成日期:**************************课程设计报告目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (1)1.3设计环境 (3)第2章详细设计方案 (4)2.1顶层方案图的设计与实现 (4)2.1.1创建顶层图形设计文件 (4)2.1.2器件的选择与引脚锁定 (5)2.1.3 编译、综合、适配 (6)2.2功能模块的设计与实现 (6)2.2.1寄存器模块的设计与实现 (6)2.2.2数据选择器模块的设计与实现 (8)2.2.3补码器模块的设计与实现 (12)2.2.4加法器模块的设计与实现 (13)2.2.5移位寄存器模块的设计与实现 (15)2.3仿真调试 (18)第3章编程下载与硬件测试 (20)3.1编程下载 (20)3.2硬件测试及结果分析 (20)参考文献 (22)附录(电路原理图) (23)第1章总体设计方案1.1 设计原理定点原码一位除法器的原理是根据人工进行二进制除法的规则:判断被除数与除数的大小,若被除数小,则上商0,并在余数最低位补0,再用余数和右移一位的除数比,若够除,则上商1,否则上商0。

然后继续重复上述步骤,直到除尽(即余数为0)或已得到的商的位数满足精度要求为止。

上述计算方法要求加法器的位数为除数位数的两倍。

但分析后,会发现右移除数,可以通过左移被除数(余数)来代替,左移出界的被除数(余数)的高位都是无用的0,对运算不会产生任何影响。

另外,上商0还是1是计算者用观察比较的办法确定的,而计算机只能用做减法判断结果的符号为负还是为正来确定。

《计算机组成原理》之定点运算器的课件设计与开发

《计算机组成原理》之定点运算器的课件设计与开发作者:陈思思,王峰来源:《电脑知识与技术》2011年第28期摘要:《计算机组成原理》之定点运算器的课件设计与开发利用Flash的强大功能,它集成了文字、图像、声音、动画、视频等多媒体信息,能更好的实现多媒体教学,使学习者加深对所学知识的理解,提高学生学习兴趣和教学效率,同时也能为课件增加生动的艺术效果。

《计算机组成原理》之定点运算器的课件共设计和开发了6个模块:“数据与文字的表示方法”、“定点加减运算”、“定点乘法运算”、“定点除法运算与阵列除法器”、“定点运算器的组成”、“浮点运算方法和浮点运算器”。

关键词:计算机组成原理;定点运算器;Flash;Photoshop中图分类号:TP393文献标识码:A文章编号:1009-3044(2011)28-6988-02The Courseware Design and Development for the Fixed-point Arithmetic in the Principle of Computer OrganizationCHEN Si-si, WANG Feng(College of Physics and Electronic Information Engineering, Wenzhou University, Wenzhou 325035, China)Abstract: The courseware design and development for the fixed-point arithmetic in the Principles of Computer Composition includes six modules: "the representation of data and text", "fixed-point addition and subtraction", "the multiplication of fix-point", "the divide of fix-point and the array of the division", "the composition of the fix-point arithmetic", "the methods of the floating point and the floating arithmetic".Key words: multimedia; constitution principle of computer; fix-point arithmetic; flash目前,《计算机组成原理》之定点运算器[1-2]的课件仅限于用Powerpoint制作,用这种技术做的PPT很枯燥不能调动学生学习的兴趣,而用Flash制作课件可以生动形象的描述各种教学问题,有效激发学生的学习兴趣,增加教学效果,提高教学效率,具有传统教学所不能比拟的优越性。

定点原码一位除法器的设计

沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:定点原码一位除法器的设计院(系):计算机学院专业:计算机科学与技术班级:学号:姓名:指导教师:完成日期:2011年01月14日沈阳航空航天大学课程设计报告目录第1章总体设计方案 (2)1.1设计原理 (2)1.2设计思路 (2)1.3设计环境 (2)第2章详细设计方案 (4)2.1总体方案的设计与实现 (4)2.1.1总体方案的逻辑图 (4)2.1.2算法流程图 (5)2.2功能模块的设计与实现 (6)2.2.1 模块的设计与实现 (6)第3章验证测试 (9)3.1验证测试 (9)参考文献 (10)第1章总体设计方案1.1设计原理原码一位除,即两个原码数相除,商的符号为除数和被除数的符号异或值。

采用汇编语言实现定点原码一位除法器,算法为恢复余数法,除数为4位。

利用恢复余数的方法来进行运算。

1.2设计思路算法为恢复余数法,先用被除数减去除数,如果结果为正数商1,然后左移,如果是负数商0然后加上Y的补,继续运算。

本题目是要求4位所以到结果是4位时结束运算。

实验开始时将实验数据从实验箱的开关输入到R0,R1,R2三个寄存器中,R0为被除数,R1为除数,R2为商。

运算过程采用恢复余数法。

主要判断被除数减去除数的商值。

如果为负,商0然后加除数然后左移。

如果商值为正商1,左移。

数据都存放在寄存器中,最后结果在OUT寄存器中显示。

1.3设计环境COP2000 模型机包括了一个标准CPU 所具备所有部件,这些部件包括:运算器ALU、累加器A、工作寄存器W、左移门L、直通门D、右移门R、寄存器组R0-R3、程序计数器PC、地址寄存器MAR、堆栈寄存器ST、中断向量寄存器IA、输入端口IN、输出端口寄存器OUT、程序存储器EM、指令寄存器IR、微程序计数器uPC、微程序存储器uM,以及中断控制电路、跳转控制电路。

其中运算器和中断控制电路以及跳转控制电路用CPLD 来实现,其它电路都是用离散的数字电路组成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

沈阳航空航天大学

课程设计报告

课程设计名称:计算机组成原理课程设计课程设计题目:定点原码一位除法器的设计

院(系):计算机学院

专业:计算机科学与技术

班级:94010101

学号:2009040101013

姓名:胡桂林

指导教师:周大海

完成日期:2012年1月13日

沈阳航空航天大学课程设计报告

目录

第1章总体设计方案 (1)

1.1设计环境 (1)

1.2设计原理 (2)

第2章详细设计方案 (4)

2.1总流程图 (4)

2.2上商置0模块流程图 (6)

2.3上商置1模块流程图 (6)

2.4商的符号流程图 (7)

第3章测试结果 (9)

3.1程序仿真 (9)

3.2仿真测试一 (9)

3.3仿真测试二 (10)

附录 (11)

参考文献 (14)

第1章总体设计方案

1.1 设计环境

伟福COP2000实验箱,用汇编语言编程实现定点原码一位除法器

COP2000 计算机组成原理实验系统由实验平台、开关电源、软件三大部分组成。

实验平台上有寄存器组R0-R3、运算单元、累加器A、暂存器W、直通/左移/右移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单元、微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总线插孔区、微动开关/指示灯、逻辑笔、脉冲源、20 个按键、字符式LCD、RS232 口。

COP2000集成调试软件(即仿真测试软件)共分为6部分:

(1)主菜单区实现实验仪的各项功能的菜单,包括[文件][编辑][汇编][运行][帮助]五大项,各项线面做详细介绍。

(2)快捷图标区快速实现各项功能按键

(3)源程序/机器码区在此区域有源程序窗口,反汇编窗口,EM程序代码窗口。

源程序用于输入,显示,编辑汇编源程序:反汇编窗口显示程序编译后的机器码及反汇编的程序;EM程序代码窗口用数据方式机器码。

(4)机构图/逻辑波形区结构图能结构化显示模型机的各部件,以及运行时数据走向寄存器值;逻辑波形图能显示模型机运行时所有信号的程序。

(5)微程序/跟踪区微程序表格用来显示程序运行时微程序的时序,及每个时钟脉冲各控制位的状态,跟踪表用来记录显示程序及微程序执行的轨迹,指令系统可以帮助你设计新的指令系统。

(6)寄存器状态区用来显示程序执行时各内部寄存器的值。

1.2 设计原理

定点原码一位除法器因为对余数的处理不同,又可分为恢复余数法和加减交替法,课设要求用恢复余数法进行计算,但余数为负时,需加上除数,将其恢复成原来的余数,商符由两数符号位进行异或求得,商值由两数绝对值相除求得。

恢复余数定点原码一位除法器实现的功能如表1.1所示,设计的电路应实现表1.1中给定的功能。

设:X=X0 X1……X n

Y=Y0 Y1……Y n

X0 X1 ,Y0Y1分别为符号位,K为两符号位的异或值

X/Y=K*|X|/|Y|

|X|/|Y|利用恢复余数法求的,商根据余数的符号是正或负来判断。

当为负时,上商为0,同时还应该把除数再加到差上去,恢复余数为原来的正值之后再左移一位。

若差为0或为正值时,就没有恢复余数的操作,上商为1,余数左移一位。

其计算过程如下:

例:已知:X=0.1011

Y=0.1101

求:X/Y

表1.1恢复余数定点原码一位除法器功能表

商的符号位为:X0○+Y0=1○+1=0

商值为:X/Y=0.1101

第2章详细设计方案

2.1 总流程图

用存储器R1和R2存储除数X和被除数Y,再将除数和被除数送到外存9FH 和9EH,X*,Y*,[—Y*]补存入存储器R1,R2和9CH中。

(1):余数R2加上[—Y*],判断余数正负,如果余数为正执行商置1模块;否则执行商置0模块。

并判断计数数值C是否为零,不为零执行(1);为零执行(2):余数R2加上[—Y*],判断余数正负,如果余数为正把商R0的最低位置1;否则把商R0的最低位置0。

将9FH和9EH地址存的除数和被除数的符号位进行异或,求出商的符号。

输出商和余数,由OUT和R2分别显示。

图2.1 总流程图

2.2上商置0模块流程图

上商置0模块中要进行恢复余数,原码一位除法器恢复余数法进行计算,区别于加减交替算法。

当余数为负时,将商的最后一位添0,这时,需要进行恢复,余数加上[Y*]补,再将得到的余数和商同时左移一位,然后余数再加上[—Y*]补存到R2上,再判断余数的正负,如果余数为负时,循环进行上商置0的操作,否则,进行上商置1的操作。

图2.2 上商置0模块流程图

2.3上商置1模块流程图

上商置1的算法比较简单,不存在不同的算法,原码一位除法都是相同的计算。

当余数为正时上商置1,这时,再将得到的余数和商同时向左移一位,然后余数加上[—Y*]补存到R2上,在判断余数的正负。

如果余数为正时,循环进行上商置1的操作,否则,进行上商置0的操作。

图2.3 上商置1模块流程图

2.4商的符号流程图

商的符号计算原码一位除法和原码一位乘法一样都是单独处理的,商符由两数的符号位进行异或运算求得,商值是由两数绝对值相除求得。

将9FH和9EH 地址的除数X和被除数Y分别右移四位,得到X1和Y1再将两数进行相加运算,得到一个值是Z,然后判断Z的最低位是否为零,如果为零,则商的符号为正,否则商的符号为负。

图2.4 商的符号流程图

第3章测试结果

3.1程序仿真

将事先编好的汇编程序输入到列表里,保存将格式改写成.asm,再进行仿真,仿真可以一步一步进行仿真,你可以看到每步执行过程中,寄存器R0~R3和累加器A的变化,根据变化可以知道每步执行是否正确,直到最后输出OUT和R2。

3.2仿真测试一

当X=0.1011B,Y=0.1101B时的仿真结果如下图所示。

已知X=0.1011B,Y=0.1101B,根据原码一位除法恢复余数法进行计算可得出商为0.1101,再将X 和Y的符号位进行异或可得出商的符号为正,所以最终商为0.1101,余数为0.0111。

OUT显示出商结果:0DH R2显示余数结果:07H

3.3仿真测试二

当X=0.1001B,Y=—0.1101B时的仿真结果如下图所示。

已知X=0.1001B,Y=—0.1101B,根据原码一位除法恢复余数法进行计算可得出商为0.1011,再将X 和Y的符号位进行异或可得出商的符号为负,所以最终商为 1.1101,余数为1.1001。

OUT显示出商结果:1BH R2显示余数结果:19H

附录

参考文献

[1] 曹昕燕.EDA技术实验与课程设计[M].北京:清华大学出版社,2006

[2] 范延滨.微型计算机系统原理、接口与EDA设计技术[M].北京:北京邮电大学

出版社,2006

[3] 王爱英.计算机组成与结构(第4版)[M].北京:清华大学出版社,2006

[4] William Stallings 张昆藏[译] 计算机组织与结构—性能设计(第五版)[M]北

京:电子工业出版社2001

[5] 黄任.编著VHDL入门·解惑·经典实例·经验总结. [M]北京:北京航空航

天大学出版社,2005

[6]李勇.计算机原理与设计(修订本).[M]长沙:国防科技大学出版社,1984

[7] 白中英主编.计算机组成原理.[M]北京:科学出版社,1994

沈阳航空航天大学程设计报告。