微机接口实习报告范例

《微机原理与接口》实验报告模板

《微机原理与接口》实验报告学院:信息学院专业:班级学号:学生姓名:实验日期:指导老师:五邑大学信息学院接口与通信实验室实验一一、实验名称:微机原理实验平台操作及汇编程序设计二、实验目的:1、了解MFID实验平台组成结构及使用方法;2、熟悉MFID实验平台的工作原理和MF2K编程环境;3、熟悉80X86的汇编语言程序设计方法;4、掌握BCD码转换为二进制的的原理及汇编程序设计;5、理解INT 21H DOS 字串显示功能的调用。

三、实验内容:1、MFID实验平台MF2K编程环境的熟悉2、屏幕输出字串的简单汇编程序设计3、进行汇编语言程序的编辑、汇编、连接和运行实验;4、编制16进制转换为ASCII码的子程序HEX_ASCII;5、编制BCD转换为二进制的子程序BCD_B;6、调用BCD_B和HEX_ASCII子程序完成十进制数转换为二进制数四、实验设备:MFID 微型计算机与接口技术实验平台五、实验步骤:1、进入MF2K汇编语言开发环境,开始汇编程序设计;2、设计主程序框架:堆栈段、数据段和代码段;3、设计“字符串显示程序”,调试并在屏幕自己的“班级”、“学号”及“名字”的拼音字母;4、设计“十六进制转换为ASCII码子程序”HEX_ASCII,调试并通过5、设计“BCD码转换为二进制子程序”BCD_B;6、在主程序中将自己的“班级号+学号”定义成4位BCD码然后调用BCD_B子程序转换为二进制;7、调用HEX_ASCII在屏幕上显示学号转换的运行结果。

六、实验结果1、调试通过的汇编实验程序源代码如下:[将源代码粘帖到下面]2、班号学号屏幕输出结果:3、四位BCD班号+学号:5123 转换结果:七、分析讨论(不少于200字)八、本次实验成绩。

微机原理与接口技术实验报告

微机原理与接口技术实验报告

本次实验是关于微机原理与接口技术的实验报告,通过本次实验,我们将深入

了解微机原理与接口技术的相关知识,并通过实际操作来加深对这些知识的理解和掌握。

实验一,微机原理。

在本次实验中,我们首先学习了微机的基本原理,包括微机的组成结构、工作

原理和基本功能。

通过实际操作,我们了解了微机的主要组成部分,如中央处理器(CPU)、内存、输入输出设备等,并学习了它们之间的工作原理和相互配合关系。

同时,我们还学习了微机的基本指令系统和数据传输方式,加深了对微机工作原理的理解。

实验二,接口技术。

在接口技术的实验中,我们学习了微机与外部设备之间的接口技术,包括并行

接口、串行接口和通用接口等。

我们通过实际操作,了解了这些接口技术的工作原理和应用场景,学会了如何通过接口技术实现微机与外部设备的数据交换和通信。

实验三,实验综合。

在本次实验的最后,我们进行了一个综合实验,通过实际操作来综合运用微机

原理和接口技术的知识,实现一个具体的功能。

通过这个实验,我们加深了对微机原理与接口技术的理解,掌握了如何将理论知识应用到实际操作中。

总结。

通过本次实验,我们深入学习了微机原理与接口技术的相关知识,并通过实际

操作加深了对这些知识的理解和掌握。

微机原理与接口技术作为计算机科学与技术的基础知识,对我们今后的学习和工作都具有重要意义。

希望通过这次实验,能够对大家的学习和工作有所帮助,并为今后的学习打下坚实的基础。

以上就是本次实验的实验报告,希望对大家有所帮助。

感谢大家的阅读!。

微机原理与接口技术实验报告

微机原理与接口技术实验报告实验目的:本次实验旨在通过实际操作,加深对微机原理与接口技术的理解,掌握接口技术的基本原理和应用方法,提高学生的动手能力和实际应用能力。

实验内容:1. 学习并掌握微机原理与接口技术的基本知识;2. 了解并熟悉常见的接口技术及其应用;3. 进行实际操作,设计并完成一个简单的接口电路。

实验仪器与设备:1. 个人电脑;2. 电子元件,电阻、电容、集成电路等;3. 实验板、示波器、示教电脑等。

实验步骤:1. 阅读相关的微机原理与接口技术的教材,了解基本原理;2. 学习常见的接口技术,例如并行接口、串行接口等;3. 进行实际操作,设计一个简单的接口电路,包括硬件设计和软件编程;4. 调试电路,确保接口电路能够正常工作;5. 编写实验报告,总结实验过程和实验结果。

实验结果与分析:经过实际操作,我们成功设计并完成了一个简单的接口电路。

在实验过程中,我们深入理解了微机原理与接口技术的相关知识,掌握了接口技术的基本原理和应用方法。

通过调试电路,我们验证了接口电路的正常工作,加深了对接口技术的理解。

结论:本次实验使我们更加深入地了解了微机原理与接口技术,提高了我们的动手能力和实际应用能力。

通过设计和完成接口电路,我们对接口技术有了更加直观的认识,为今后的学习和工作打下了坚实的基础。

总结:微机原理与接口技术是计算机专业的重要课程,通过实验学习,我们不仅加深了对知识的理解,还提高了动手能力和实际应用能力。

希望同学们能够认真对待每一次实验,不断提升自己的能力,为未来的发展打下坚实的基础。

至此,本次微机原理与接口技术实验报告完毕。

微机原理与接口技术实验报告

微机原理与接口技术实验报告实验目的:本次实验旨在熟悉并掌握微机原理与接口技术的相关知识,通过实例操作和分析实验数据,加深对微机原理与接口技术的理解。

一、实验器材与软件1. 硬件器材:计算机主机、外设设备2. 软件工具:操作系统、编程软件二、实验步骤及结果分析1. 实验1:计算机开机自检在实验中,通过开机启动计算机,观察计算机进行自检的过程。

根据显示屏上的自检信息,可以判断计算机硬件的工作状态。

2. 实验2:串口通信测试在本实验中,通过串口通信实现计算机与外设设备之间的数据传输。

首先,将串口接口连接到计算机主机,然后进行相应的设置,包括波特率、数据位、停止位和校验位等。

在实验中,通过编写相应的程序,实现计算机与外设设备之间的数据交互。

通过观察实验结果,判断串口通信是否正常。

3. 实验3:并口通信测试本实验旨在通过并行口通信实现计算机与外设设备之间的数据传输。

首先,将并行口接口连接到计算机主机。

然后,根据实验要求进行相应的设置,包括数据总线的宽度、传输模式等。

通过编写程序,实现计算机与外设设备之间的数据交互。

观察实验结果,判断并口通信是否正常。

4. 实验4:USB接口测试在本实验中,通过USB接口实现计算机与外设设备之间的数据传输。

首先,将USB接口连接到计算机主机。

然后,在计算机中安装相应的驱动程序。

通过编写程序,实现计算机与外设设备之间的数据交互。

观察实验结果,判断USB接口是否正常工作。

5. 实验5:网络接口测试本实验旨在通过网络接口实现计算机之间的数据传输。

首先,将计算机连接到局域网中的其他计算机。

然后,进行相应的设置,包括IP地址、子网掩码等。

通过编写程序,实现计算机之间的数据交互。

观察实验结果,判断网络接口是否正常工作。

三、实验总结通过本次实验,我对微机原理与接口技术有了更深入的了解,掌握了串口、并口、USB接口和网络接口等常用接口的使用方法。

通过实验的操作和分析,我对接口通信的原理和实现方式有了更详细的了解,对计算机与外设设备之间的数据传输有了更清楚的认识。

微机原理与接口技术实验报告参考

微机原理与接口技术实验报告实验一显示程序实验一、实验目的1. 掌握在PC机上以十六进制形式显示数据的方法;2. 掌握部分DOS功能调用使用方法;3. 熟悉Tddebug调试环境和Turbo Debugger的使用。

二、实验所用设备1. PC微机一台。

三、实验内容一般来说,程序需要显示输出提示运行的状况和结果,有的还需要将数据区中的内容显示在屏幕上。

本实验要求将指定数据区的数据以十六进制数形式显示在屏幕上,并通过DOS功能调用完成一些提示信息的显示。

实验中可使用DOS功能调用(INT 21H)。

(1) 显示单个字符输出入口:AH=02H调用参数:DL=t出字符(2) 显示字符串入口:AH=09H调用参数:DS:DX串地址,’$'为结束字符(3) 键盘输入并回显入口:AH=01H返回参数:AL=t出字符(4) 返回DO系统入口:AH=4CH调用参数:AL=M回码四、实验步骤1. 运行Tddebug软件,选择Edit菜单,根据实验内容的描述编写实验程序,本实验显示部分参考实验流程如图1-1示;2. 使用Compile菜单中的Compile和Link对实验程序进行汇编、连接;3. 使用Rmrun菜单中的Run,运行程序,观察运行结果;4. 使用Rmrun菜单中的Debug调试程序,观察调试过程中,数据传输指令执行后,各寄存器及数据区的内容;5. 更改数据区中的数据,考察程序的正确性。

图1-1显示程序实验流程图五、程序清单DATA SEGMENTMES DB 'laoshihao:', 0AH,0DH,'$' SD DB 'b'DATA ENDSCODE SEGMENTASSUME CS:CODE, DS:DATASTART: MOV AX, DATAMOV DS, AXMOV DX, OFFSET MESMOV AH, 09HINT21HMOV DI, OFFSET SDMOV AL, DS:[DI]AND AL, 0F0HSHR AL,4CMP AL, 0AHJB L1ADD AL, 07HL1: ADD AL, 30HMOV DL, ALMOV AH, 02HINT21HMOV AL, DS:[DI]AND AL, 0FHCMP AL, 0AHJB L2ADD AL, 07HL2: ADD AL, 30HMOV DL, ALMOV AH, 02HINT21HMOV AX, 4C00HINT21HCODE ENDSEND START六、实验调试过程调试过程中出现警告,显示没有使用堆栈段。

最新微机接口实验报告

最新微机接口实验报告实验目的:1. 熟悉微机接口的基本原理和功能。

2. 掌握微机接口的编程和操作技巧。

3. 通过实验加深对微机接口技术的理解。

实验环境:- 微机接口实验箱- 个人电脑- 相关软件和驱动程序实验内容:1. 实验一:了解微机接口的基本结构和工作原理。

- 学习微机接口的基本概念,包括数据总线、地址总线、控制总线等。

- 观察实验箱中的微机接口模块,识别各部分的功能。

2. 实验二:编写简单的输入输出程序。

- 使用汇编语言或C语言编写程序,实现对微机接口的控制。

- 通过程序实现LED灯的点亮和熄灭,以及按键的读取。

3. 实验三:中断和DMA操作。

- 学习中断的基本概念和处理流程。

- 实现一个基于中断的键盘输入程序。

- 了解DMA的工作原理,并编写相应的数据传输程序。

实验步骤:1. 准备实验环境,确保所有设备和软件均已正确安装和配置。

2. 按照实验指导书的要求,逐步完成各个实验项目。

3. 在实验过程中记录关键步骤和结果,以便撰写实验报告。

4. 对遇到的问题进行分析和解决,记录解决方案。

实验结果:1. 成功理解微机接口的基本结构和功能。

2. 编写的输入输出程序能够正确控制LED灯和读取按键状态。

3. 中断和DMA操作实验顺利完成,实现了预期的功能。

实验结论:通过本次实验,加深了对微机接口技术的理解,掌握了基本的编程和操作技能。

实验中遇到的问题和挑战也有助于提高解决问题的能力。

通过实践,更加明确了理论知识与实际应用之间的联系。

建议和反思:- 在实验过程中,应更加注重对理论知识的应用,以提高实验效率。

- 对于复杂的问题,应采取分步解决的策略,避免在实验中出现混乱。

- 未来应加强实验前的准备工作,确保实验能够顺利进行。

微机实习报告

微机实习报告第一篇:微机实习报告计算机上机实习报告一、实习目的:本次上机实习的目的是使同学们熟悉office软件。

1、能用WORD做基本的文档录入和编辑。

会设置常见的文字格式和版式。

2、能用ppt做基本的幻灯片。

会设置常见幻灯片效果和格式。

会播放幻灯片。

3、会使用Excel录入数据,会设置数据格式。

会基本的表格统计和分析。

二、实习任务:1、选定一个主题,收集资料,整理成为一篇综述性报告;2、假定为某班班主任,根据本班成绩进行成绩分析,撰写一篇班级成绩分析报告;3、制作一个以第一题的主题为演讲内容的演示文稿;4、选做题:利用PS进行平面艺术创作;5、将以上操作所产生的文件打包压缩成一个文件上交;6、写一份关于本次上机实习的实习报告。

三、实习总结:1、第一大题的论文内容不是很完美,但总体上,成绩分析表将学生的加权平均分、名次、各分数段人数、优秀生名单等分析到位,运算到位。

演示文稿花了很多心思去做,用来很多效果,出来还是不错的。

2、此次实习时间虽不是很长,但我学会了许多东西,特别是一些课堂上没弄懂的问题,实习中通过操作将其弄懂了。

另外,我也学会了如何调试word文档,总而言之,实际操作比课堂上更容易掌握知识,课堂上老师讲的很好,可我一次并不能消化多少,而上机操作则不同,不会就不能进行下一步,必须弄懂才能做接下来的工作,而且能够掌握得更好。

3、此次实习收获最大的并不是对office的掌握,而是对学习方法的认识,实习过程中经常遇到各种各样的问题,老师虽然能帮助我解决一部分,但最终还是需靠自己,多动脑,多思考,再加上细心,许多问题都能迎刃而解。

4、对于意见和建议的话,我只想说由于早上第一节上机就要对着大频幕台式电脑会带来身体上的不适,希望以后上机实习中能将时间更好的科学安排好。

第二篇:微机实习报告微机控制系统实习报告微机实习是我们专业的一门必修的专业实习课,也是大学期间最后的一门实习课,实习的目的是使我们进一步加深对《微机原理与接口技术》、《单片机原理与应用》等课程相关理论知识的理解,并基本掌握将这些理论知识应用于自动控制系统设计的基本方法与技能,掌握收集、分析、应用资料的基本方法,通过技术方案的选择论证、硬件设计、程序设计,掌握自控原理、微机原理、单片机、计算机控制等课程理论知识在自动控制中的应用方法,掌握基于微型计算机的自动控制装置、自动测试仪器等的设计方法与技能为今后从事相关技术工作奠定必要的基础。

微机原理与接口技术实验报告

微机原理与接口技术实验报告实验一,微机原理实验。

1. 实验目的。

本实验旨在通过对微机原理的实验,加深学生对微机原理相关知识的理解,提高学生的动手能力和实验技能。

2. 实验内容。

本实验主要包括微机原理的基本知识、微处理器的结构和功能、微机系统的总线结构、存储器与I/O接口。

3. 实验步骤。

(1)了解微机原理的基本知识,包括微处理器的分类、功能和工作原理。

(2)学习微机系统的总线结构,掌握总线的分类、功能和工作原理。

(3)了解存储器与I/O接口的基本概念和工作原理。

(4)进行实际操作,通过实验板进行微机原理实验,加深对微机原理知识的理解。

4. 实验结果。

通过本次实验,我深刻理解了微机原理的基本知识,掌握了微处理器的结构和功能,了解了微机系统的总线结构,以及存储器与I/O接口的工作原理。

通过实际操作,我对微机原理有了更深入的认识,提高了自己的动手能力和实验技能。

实验二,接口技术实验。

1. 实验目的。

本实验旨在通过对接口技术的实验,加深学生对接口技术相关知识的理解,提高学生的动手能力和实验技能。

2. 实验内容。

本实验主要包括接口技术的基本知识、接口电路的设计与调试、接口技术在实际应用中的作用。

3. 实验步骤。

(1)了解接口技术的基本知识,包括接口的分类、功能和设计原则。

(2)学习接口电路的设计与调试,掌握接口电路设计的基本方法和调试技巧。

(3)了解接口技术在实际应用中的作用,包括各种接口的应用场景和实际案例。

(4)进行实际操作,通过实验板进行接口技术实验,加深对接口技术知识的理解。

4. 实验结果。

通过本次实验,我深刻理解了接口技术的基本知识,掌握了接口电路的设计与调试方法,了解了接口技术在实际应用中的作用。

通过实际操作,我对接口技术有了更深入的认识,提高了自己的动手能力和实验技能。

总结。

通过微机原理与接口技术的实验,我对微机原理和接口技术有了更深入的理解,提高了自己的动手能力和实验技能。

希望通过今后的学习和实践,能够更加深入地掌握微机原理与接口技术的知识,为将来的工作和研究打下坚实的基础。

微机接口实验报告

微机接口实验报告实验一:显示程序实验(2021年4月22日)1、实验目的及实验内容实验目的:1.掌握在PC机上以十六进制数形式显示数据的方法2.掌握部分DOS功能调用的使用方法3.熟悉Tddebug调试环境和Turbo Debugger的使用实验内容及说明:本实验要求将指定的数据区的数据以十六进制数形式显示在屏幕上,并通过DOS功能调用完成一些提示信息的显示。

0~9的ASII码为:30H~39H,转换时,直接在原数据后面加上30H即可;A以后的数据ASII码为:41H~ 在原数据上加上7H,再加上30H即可。

实验中可使用DOS功能调用(INT21H)。

1.显示单个字符入口:AH=02H调用参数:DL=输出字符 2.显示字符串入口:AH=09H调用参数:DS:DX:串地址,’$’为结束字符 3.键盘输入并回显入口:AH=01H调用参数:AL=输出字符若不回显,入口:AH=07H 或 AH=10H 4.返回DOS系统入口:AH=4CH调用参数:AL=返回码2、实验环境及实验步骤实验环境:PC机一台实验步骤:1.运行Tddebug软件,选择Edit菜单,根据实验内容的描述编写实验程序。

显示部分实验流程图如下:2.使用Compile菜单中的Compile和Link对实验程序进行汇编、连接3.使用Run菜单中的Run运行程序,观察运行结果4.使用Run菜单中的Debug调试程序,观察调试过程中的数据传输指令执行后各寄存器及数据区的内容5.更改数据区中的数据,考察程序的正确性本实验的显示部分试验流程如图所示取字节的高4位N数据是否大于等于A?Y是A-F,加7H转换成ASCH码送屏幕显示取字节的低四位数据是否大于等于A?NY是A-F,加7H转换成ASCH码送屏幕显示3、实验过程与分析(1).取字节的高四位的实现首先将一个字节读入寄存器,将该字节同0F0H相与,即可将该字节的高四位保持不变而第四位变为全0。

然后将相与后的字节右移四位即得到原始字节的高四位。

中南大学微机接口实验报告模板

中南大学课题名称:微机原理与接口技术课程实验报告学院:信息科学与工程学院班级:学号:姓名:指导老师:实验一、使用 ADC0809 的 A/D 转换实验一、实验目的1、加深理解逐次逼近法模数转换器的特征和工作原理,掌握 ADC0809 的接口方法以及A/D输入程序的设计和调试方法。

二、预备知识逐次逼近法 A/D 也称逐次比较法 A/D。

它由结果寄存器、D/A、比较器和置位控制逻辑等部件组成,如图 6-1 所示图 6-1 逐次逼近法三、实验原理1、本实验采用 ADC0809 做 A/D 转换实验。

ADC0809 是一种 8 路模拟输入、8 位数字输出的逐次逼近法 A/D 器件,转换时间约 100us,转换精度为±1/512,适用于多路数据采集系统。

ADC0809片内有三态输出的数据锁存器,故可以与 8088 微机总线直接接口。

2、实验代码:MOV CX,0500HDELAY: LOOP DELAYMOV DX,ADPORTIN AL,DXMOV CL,ALCALL CONVERSCALL LEDDISPJMP ADCONCONVERS:MOV BH,0HAND AL,0FHMOV BL,ALMOV AL,CS:[BX+DATA2]MOV BX,DATA1+7MOV DS:[BX],ALDEC BXPUSH BXMOV AL,CLMOV CL,04HSHR AL,CLMOV BL,ALMOV BH,0HMOV AL,CS:[BX+DATA2]POP BXMOV DS:[BX],ALRETLEDDISP:MOV AL,90HMOV DX,CONTPORTOUT DX,ALMOV BYTE PTR DS:[0600H],00LED1: CMP BYTE PTR DS:[0600H],07H JA LED2MOV BL,DS:[0600H]MOV BH,0HMOV AL,CS:[BX+DATA1]MOV DX,DATAPORTOUT DX,ALADD BYTE PTR DS:[0600H],01HJNZ LED1LED2: RETCODE ENDSEND START四、实验过程1、准确连接线路。

微型计算机原来与接口技术实验报告(全)

微机接口实验报告实验一简单I/O口扩展实验一、实验目的1、熟悉74LS273,74LS244的应用接口方法。

2、掌握用锁存器、三态门扩展简单并行输入、输出口的方法。

二、实验内容1、由键盘输入字符,然后通过74LS273将其ASCII码锁存输出,并通过LED显示出来。

2、逻辑电平开关的状态输入74LS244,经过PCI总线读入并以16进制显示在屏幕上。

3、逻辑电平开关的状态输入74LS244,然后通过74LS273锁存输出,利用LED显示电路作为输出的状态显示。

三、实验原理介绍本实验用到两部分电路:开关量输入输出电路,简单I/O口扩展电路。

四、实验步骤1、实验接线:(←→表示相互连接)CS0←→CS244,CS1←→CS273,平推开关的输出K1~K8←→IN0~IN7(对应连接)00~07←→发光二极管的输入LED1~LED8。

2、编辑程序,用debug调试程序,单步运行。

3、调试通过后,全速运行程序,观看实验结果。

4、编写实验报告。

五、实验提示74LS244或74LS273的片选信号可以改变,例如连接CS2,此时应同时修改程序中相应的地址。

六、实验结果程序全速运行后,逻辑电平开关的状态改变应能在LED上显示出来。

例如:K2置于L位置,则对应的LED2 应该点亮。

七、程序框图(如图1)实验程序:实验 1; * cs0<->cs273,D0~D7依次接LED1~LED8*;IOPOR T EQU 0A800HLS273 EQU IOPORT+0A0HCODE SEGMENTASSUME CS:CODESTART: MOV AH,2 ;回车符MOV DL,0DHINT 21HMOV AH,1 ;等待键盘输入INT 21HCMP AL,27 ;判断是否为ESC键JE EXIT ;若是则退出MOV DX,LS273 ;若不是,从2A8H输出其ASCII码OUT DX,ALJMP START ;转startEXIT: MOV AH,4CH ;返回INT 21HCODE ENDSEND START实验结果:从键盘输入数字0~9可以通过LED显示相应的二进制代码(亮灯为0,熄灯为1)例如从键盘输入数字3,灯亮情况led4~led1对应0011;即led4~led1从到左表示0011,led4、led3低位,led2、led1高位。

微机接口实验报告

微机接口实验报告实验一:I/O地址译码一、实验目的掌握I/O 地址译码电路的工作原理。

二、实验原理和内容实验电路如图(1)所示,其中74LS74 为D 触发器,可直接使用实验台上数字电路实验区的D 触发器,74LS138 为地址译码器。

译码输出端Y0~Y7 在实验台上I/O 地址输出端引出,每个输出端包含8 个地址,Y0:280H~287H,Y1:288H~28FH,……当CPU 执行I/ O 指令且地址在280H~2BFH 范围内,译码器选中,必有一根译码线输出负脉冲。

例如:执行下面两条指令Y4 输出一个负脉冲,执行下面两条指令MOV DX, 2A0HOUT DX,AL(或IN AL,DX)Y5 输出一个负脉冲。

MOV DX,2A8HOUT DX,AL(或IN AL,DX)利用这个负脉冲控制L7 闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现。

三、实验程序L1: MOV DX, 2A0H //选通74LS138的11口OUT DX, AL //使端口A输出,给D触发器一个时钟信号LOOP $ //延时LOOP $ //延时MOV DX, 2A8H //选用74LS138的10口OUT DX, AL //使D触发器清零LOOP $ //延时LOOP $ //延时MOV AH, 11 //十一号功能调用INT 21H //如果有键按下INC AL //AL加一,退出循环JNZ L1 // 如果没键按下,则继续循环四、总结第一次实验比较简单、主要是学会了通过程序控制芯片及其端口的选通,其方法是根据芯片外围搭建的电路使DX进行写或读的操作、例如本实验里,要想选通74LS138的11口操作8255的端口A,则需要使,同理操作10口时,则使DX=2A8H,再加上延时DELAY功能,即可使LED灯循环亮灭。

但是如果不给芯片断电,则LED灯会一直循环,不能进进行人为的控制,所以又在后面加上了11号功能调用,只要当AL=0,循环结束。

微型计算机接口技术实验报告(二)

微型计算机接口技术实验报告实验一:交通灯实验一.实验目的了解可编程并行接口芯片8255 的内部结构、工作方式、初始化编程及应用。

二.实验内容说明1、8255A 的内部结构(1)数据总线缓冲器:这是一个双向三态的8 位数据缓冲器,它是8255A与微机系统数据总线的接口。

输入输出的数据、CPU输出的控制字以及CPU输入的状态信息都是通过这个缓冲器传送的。

(2)三个端口A,B和C:A端口包含一个8位数据输出锁存器和缓冲器,一个8位数据输入锁存器。

B 端口包含一个8 位数据输入/输出锁存器和缓冲器,一个8位数据输入缓冲器。

C 端口包含一个8位数据输出锁存器及缓冲器,一个8位数据输入缓冲器(输入没有锁存器)。

(3)A组和B组控制电路:这是两组根据CPU输出的控制字控制8255工作方式的电路,它们对于CPU而言,共用一个端口地址相同的控制字寄存器,接收CPU输出的一字节方式控制字或对C口按位复位字命令。

方式控制字的高5位决定A组工作方式,低3位决定B组的工作方式。

对C口按位复位命令字可对C口的每一位实现置位或复位。

A组控制电路控制A口和C口上半部,B组控制电路控制B口和C口下半部。

(4)读写控制逻辑:用来控制把CPU输出的控制字或数据送至相应端口,也由它来控制把状态信息或输入数据通过相应的端口送到CPU。

2、8255A 的工作方式方式0—基本输入输出方式;方式1—选通输入输出方式;方式2—双向选通输入输出方式。

3、8255A 的状态字图 6-3-1 8255 方式1 的状态字图6-3-2 8255 方式2 的状态字三.实验原理图图6-3-5 可编程并行接口8255 电路四.实验步骤(1) 实验连线(如图所示)该模块的 WR、RD分别连到ISA总线接口模块的IOWR、IORD。

该模块的数据(AD0~AD7)、地址线(A0~A7)分别连到ISA总线接口模块的数据(LD0~LD7)、地址线(LA0~LA7)。

8255 模块选通线CE 连到ISA 总线接口模块的0000H。

微机接口机原理实验报告

微机原理及接口技术——实验报告学号: xxxxxx姓名: xxxxx专业: 网络工程实验一: 系统认知1.1实验目的掌握 TD 系列微机原理及接口技术教学实验系统的操作, 熟悉Wmd86 联机集成开发调试软件的操作环境。

通过顺序程序设计与分支程序设计来进行举例。

1.2实验设备PC 机一台, TD-PITE 实验装置一套。

1.3实验内容内存从BUFF开始的单元中存放着两个字数据X、Y, 完成X+Y, 并将相加的和(假设仍为一个字数据)存放于内存从RESULT开始的存储单元中。

DATA SEGMENTBUFF DW X,YRESULT DW ?DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATASTART: MOV AX,DATAMOV DS,AXMOV AX,BUFFADD AX,BUFF+2MOV RESULT,AXMOV AH,4CHINT 21HCODE ENDSEND START加载程序后调试, R寄存器;U反汇编;D显示数据;E修改数据。

1.4实验截图实验二分支程序设计2.1实验目的1.掌握分支程序的结构.2.掌握分支程序的设计、调试方法.2.2实验设备PC 机一台, TD-PITE 实验装臵一套。

2.3实验内容1, X>0求函数Y= 0, X=0-1, X<0程序如下:DATA SEGMENTVAR1 DB XVAR2 DB ?DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA START:MOV AX,DATAMOV DS,AXMOV AL, VAR1CMP AL, 0JGE BIGMOV VAR2,0FFHJMP DONEBIG:JE EQULMOV VAR2,1JMP DONEEQUL:MOV VAR2, 0DONE:MOV AH, 4CHINT 21HCODE ENDSEND START实验三循环程序设计3.1实验目的1)加深对循环结构的理解。

微机原理及接口技术实验报告

微机原理及接口技术实验报告一、实验目的本实验旨在通过掌握微机原理和接口技术的实验操作,实践相关理论知识,加深对微机原理和接口技术的理解。

二、实验设备和材料1.计算机主机2.操作系统3.接口卡4.编程软件三、实验原理微机原理是指通过学习微机的结构、功能和工作原理,从硬件层面掌握微机的基本知识。

接口技术是指连接不同设备之间的通信和数据交换技术,通过学习接口技术可以实现设备的互联和数据的传输。

四、实验步骤1.将接口卡插入计算机主机的扩展槽中。

2.启动计算机,并加载操作系统。

3.打开编程软件,编写实验程序。

4.将编写好的程序烧录到接口卡中。

5.连接外部设备和接口卡,并确认连接正确无误。

6.运行程序,并观察外部设备和接口卡之间的数据交互情况。

7.分析实验结果,并记录实验数据。

8.关闭程序和计算机。

五、实验结果及分析通过实验我们成功连接了外部设备和接口卡,并实现了数据的传输和交互。

在程序运行过程中,我们观察到外部设备正常工作,并且与接口卡之间的通信稳定可靠。

根据实验数据分析,我们可以得出接口卡的性能良好,并且能够满足实际应用需求。

六、实验心得通过这次实验,我对微机原理和接口技术有了更深入的理解。

实践操作让我加深了对硬件设备和软件编程的认识,掌握了实现设备互联和数据传输的基本方法。

在实验过程中,我遇到了一些问题,如接口卡的插入和连接问题,但通过查阅资料和请教老师同学,最终成功解决了这些问题。

我发现实验不仅帮助我巩固了理论知识,也提高了我的实践能力和解决问题的能力。

总结起来,微机原理和接口技术是计算机相关专业的基础课程之一,通过实验的方式学习可以更好地将理论知识与实际应用相结合。

我相信通过不断的实践和学习,我会在微机原理和接口技术方面有进一步的提高和发展。

微机接口实验报告四

汇编语言程序设计上机实验报告(实验四)

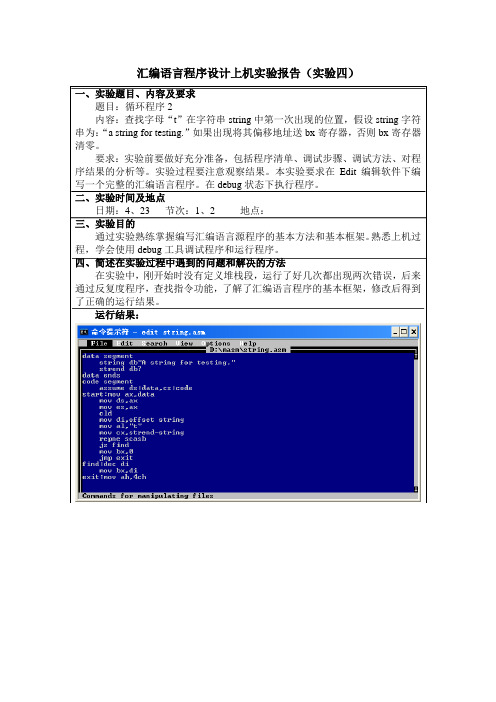

一、实验题目、内容及要求

题目:循环程序2

内容:查找字母“t”在字符串string中第一次出现的位置,假设string字符串为:“a string for testing.”如果出现将其偏移地址送bx寄存器,否则bx寄存器清零。

要求:实验前要做好充分准备,包括程序清单、调试步骤、调试方法、对程序结果的分析等。

实验过程要注意观察结果。

本实验要求在Edit编辑软件下编写一个完整的汇编语言程序。

在debug状态下执行程序。

二、实验时间及地点

日期:4、23 节次:1、2 地点:

三、实验目的

通过实验熟练掌握编写汇编语言源程序的基本方法和基本框架。

熟悉上机过程,学会使用debug工具调试程序和运行程序。

四、简述在实验过程中遇到的问题和解决的方法

在实验中,刚开始时没有定义堆栈段,运行了好几次都出现两次错误,后来通过反复度程序,查找指令功能,了解了汇编语言程序的基本框架,修改后得到了正确的运行结果。

运行结果:

程序结束地址

程序运行结果课后练习

结果分析及实验体会

通过这次编写的一个简短的、完整的汇编语言程序,基本掌握了汇编语言源程序的基本方法和基本框架,熟悉了汇编语言的上机过程,进一步体会到程序的不唯一性,比如,不用字符串查找指令也能完成字符的查找。

总之,通过本次实验,对debug的命令更熟悉,运用的也更灵活了。

微机原理与接口技术实习报告

实习报告实习性质:《微机原理与接口技术》课程实习学生姓名:**专业班级:计算计控制技术131班指导教师:周桐、李新实习时间:2014年2月29日- 2015年1月4日实习地点:1403实训室重庆工程职业技术学院学生实习考核表目录1 实习目的 (1)2 实习概况 (1)2.1 实习要求 (1)2.2 实习时间 (1)2.3 实习环境 (2)2.4开发环境 (2)3 实习内容 (2)3.1实习任务和流程图 (2)3.2用记事本建立汇编语言源程序文件(.ASM文件) (3)3.3用汇编程序MASM将ASM文件汇编成目标程序文件(.OBJ文件) (5)3.4用连接程序LINK生成可执行程序文件(.EXE文件) (6)3.5验证和检查文件是否能运行 (7)4 实习总结 (8)4.1学习所得 (8)4.2 经验教训 (8)4.3实习体会 (8)1实习目的编写的汇编语言源程序能在DOS环境下运行时,必须了解汇编语言是如何同DOS操作系统接口的。

用编辑程序把源程序输入到机器中,用汇编程序把它转换为目标程序,用连接程序对其进行连接和定位时,操作系统为每一个用户程序建立了一个程序段前缀区PSP,其长度为256个字节,主要用于存放所要执行程序的有关信息,同时也提供了程序和操作系统的接口。

操作系统在程序段前缀的开始处(偏移地址0000H)安排了一条INT 20H软中断指令。

INT 20H中断服务程序由DOS提供,执行该服务程序后,控制就转移到DOS,即返回到DOS管理的状态。

因此,用户在组织程序时,必须使程序执行完后能去执行存放于PSP开始处的INT 20H指令,这样便返回到DOS,否则就无法继续键入命令和程序。

DOS在建立了程序段前缀区PSP之后,将要执行的程序从磁盘装入内存。

在定位程序时,DOS将代码段置于PSP下方,代码段之后是数据段,最后放置堆栈段。

内存分配好之后,DOS就设置段寄存器DS和ES的值,以使它们指向PSP的开始处,即INT 20H的存放地址,同时将CS设置为PSP后面代码段的段地址,IP设置为指向代码段中第一条要执行的指令位置,把SS设置为指向堆栈的段地址,让SP指向堆栈段的栈底,然后系统开始执行用户程序。

微机原理与接口技术实验报告

微机原理与接口技术实验报告实验目的,通过本次实验,掌握微机原理与接口技术的基本知识,了解并掌握微机接口技术的应用方法。

实验仪器与设备,微机实验箱、接口卡、示波器、电源等。

实验原理,微机接口技术是指微机与外部设备进行数据交换的技术。

它是微机与外部设备之间的桥梁,通过接口技术可以实现微机与外部设备之间的数据传输和通信。

实验内容与步骤:1. 实验一,串行通信接口实验。

a. 将串行通信接口卡插入微机实验箱的接口槽中;b. 连接示波器和外部设备,并进行数据传输测试;c. 观察并记录数据传输的波形和数据传输情况。

2. 实验二,并行通信接口实验。

a. 将并行通信接口卡插入微机实验箱的接口槽中;b. 连接外部设备,并进行数据传输测试;c. 观察并记录数据传输的情况。

3. 实验三,AD转换接口实验。

a. 将AD转换接口卡插入微机实验箱的接口槽中;b. 连接外部模拟信号源,并进行模拟信号转换测试;c. 观察并记录模拟信号转换的波形和数据传输情况。

实验结果与分析:1. 串行通信接口实验结果分析:通过实验发现,在串行通信接口实验中,数据传输的波形稳定,数据传输速度较快,适用于对数据传输速度要求较高的应用场景。

2. 并行通信接口实验结果分析:在并行通信接口实验中,数据传输稳定,但数据传输速度相对较慢,适用于对数据传输速度要求不高的应用场景。

3. AD转换接口实验结果分析:经过实验发现,AD转换接口可以将模拟信号转换为数字信号,并且转换精度较高,适用于对信号转换精度要求较高的应用场景。

实验总结与展望:通过本次实验,我们深入了解了微机原理与接口技术的基本知识,掌握了串行通信接口、并行通信接口和AD转换接口的应用方法。

同时,也发现不同接口技术在数据传输速度、稳定性和精度方面各有优劣,需要根据实际应用场景进行选择。

未来,我们将继续深入学习和探索微机接口技术的应用,为实际工程项目提供更好的技术支持。

结语:通过本次实验,我们对微机原理与接口技术有了更深入的了解,实验结果也验证了接口技术在数据传输和信号转换方面的重要作用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1概述概述实习的目的1.1实习的目的微机接口实习是计算机应用专业重要的一个实践性内容。

其目的和作用是使学生能将已学过微机原理与接口技术知识综合运用于电子系统的设计中,从而培养学生对电子系统的设计和实现能力,培养学生的团结合作精神,培养学生的自主学习、实践能力,培养学生的创新思维。

课题的背景1.2课题的背景(1)微机控制越来越广泛地用于各行各业,身为工科院校的学生理应掌握其在工业领域的一些应用;(2)作为本专业硬件课程的一次综合性实践;(3)提高工厂此类产品质检的效率,准确完成质检要求;(4)便于用户对产品功能的确认。

课题的任务1.3课题的任务1.3.1基本要求给定集成电路芯片74LS32 ,其基本要求如下:(1)利用微机实验系统设计一个硬件电路;(2)编写软件实现对给定芯片功能正常与否的测试;(3)当被测芯片各组的功能均正常时,显示芯片功能完好的信息,否则显示出芯片损坏的信息,并指出对应的功能组;(4)进行软、硬件的调试,实现要求的功能。

扩展要求::1.3.2 扩展要求(1)功能扩展:同一软硬件环境可测试多种芯片的逻辑功能;(2)输入输出界面:信息显示友好,含义明确,易理解;2课题需求分析功能需求2.1功能需求设计一个硬件电路,编写软件实现对给定芯片74LS32功能正常与否的测试。

当被测芯片各组的功能均正常时,显示芯片功能完好的信息,否则显示出芯片损坏的信息,并且可以指出对应坏掉的功能组。

若芯片功能完好,则要求可以自行设置模拟某些引脚出错状况。

环境需求2.2环境需求在对74LS32集成芯片进行逻辑功能测试时,需要硬件及软件的支持。

硬件方面:需要用到8086、并行可编程外围接口芯片8255、完成片选功能的74LS138,同时需要用到进行芯片间连接的微机接口技术实验箱表1硬件实验器材实验器材仪器编号数量PC机20051721 1台74LS32芯片2个单片机及接口实验箱AEDK-EAT59805-04-24 1台软件方面:需要AEDK88软件和PROTEL99软件的支持,在此软件基础上编译、连接、加载程序,通过与实验箱相连,完成测试。

表2软件实验器材实验器材仪器编号数量 Windows XP SP2操作系统 一套 LCA88ET 调试软件 1套 Protel99软件1套2.3被测芯片介绍被测芯片介绍((包括其逻辑图包括其逻辑图,,真值表真值表,,工作条件等工作条件等))表3 芯片主要电特性引出端口符引出端口符号号:1A ——4A 输入端,1B ——4B 输入端,1Y ——4Y 输出端 逻辑图逻辑图::图1逻辑图 功能表:图2功能表3课题设计测试原理3.1测试原理特性3.1.1 8255特性(1)8255是一个并行输入/输出的LSI芯片,多功能的I/O器件,可作为CPU总线与外围的接口.(2)8255具有24个可编程设置的I/O口,即使3组8位的I/O口为PA口,PB口和PC口.它们又可分为两组12位的I/O口,A组包括A口及C口(高4位,PC4~PC7),B 组包括B口及C口(低4位,PC0~PC3).A组可设置为基本的I/O口,闪控(STROBE)的I/O闪控式,双向I/O3种模式;B组只能设置为基本I/O或闪控式I/O两种模式,而这些操作模式完全由控制寄存器的控制字决定.引脚功能3.1.28255引脚功能RESET:复位输入线,当该输入端外于高电平时,所有内部寄存器(包括控制寄存器)均被清除,所有I/O口均被置成输入方式。

CS:芯片选择信号线,当这个输入引脚为低电平时,即/CS=0时,表示芯片被选中,允许8255与CPU进行通讯;/CS=1时,8255无法与CPU做数据传输.RD:读信号线,当这个输入引脚为低电平时,即/RD=0且/CS=0时,允许8255通过数据总线向CPU发送数据或状态信息,即CPU从8255读取信息或数据。

WR:写入信号,当这个输入引脚为低电平时,即/WR=0且/CS=0时,允许CPU将数据或控制字写入8255。

D0~D7:三态双向数据总线,8255与CPU数据传送的通道,当CPU 执行输入输出指令时,通过它实现8位数据的读/写操作,控制字和状态信息也通过数据总线传送。

PA0~PA7:端口A输入输出线,一个8位的数据输出锁存器/缓冲器, 一个8位的数据输入锁存器。

PB0~PB7:端口B输入输出线,一个8位的I/O锁存器, 一个8位的输入输出缓冲器。

PC0~PC7:端口C输入输出线,一个8位的数据输出锁存器/缓冲器, 一个8位的数据输入缓冲器。

端口C可以通过工作方式设定而分成2个4位的端口, 每个4位的端口包含一个4位的锁存器,分别与端口A和端口B配合使用,可作为控制信号输出或状态信号输入端口。

A0,A1:地址选择线,用来选择8255的PA口,PB口,PC口和控制寄存器。

控制字3.1.3 8255控制字8255是并行输入、输出接口芯片,有A,B,C三个端口,对其进行初始化时,为:10000001,含义是A端口设置为输入,方式为0;B端口设置为输入,方式为0;C端口高4位为输入,方式为0;C端口低四位为输出,方式为0。

图3 8255控制字3.1.4 74LS138介绍138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其主要电特性的典型值如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图4 74LS32硬件电路原理图74LS32测试的程序框图如图8所示,流程图如图9所示图5 74LS32程序框图是图6 74LS32流程图3.4系统实现系统实现3.4.1 硬件测试(1)通讯口检验打开电脑和单片机及接口实验箱,运行LCA88ET调试软件,然后选择通讯口菜单,选择测试通讯口,当测试成功后,单击确定。

如果有错,可以选择换一个通讯端口或者重新打开实验箱,然后重新测试。

(2)发光二极管测试用导线将8个单色L1到L8灯分别与8个电平开关K1到K8相连接,如果电平给单色灯低电平后单色灯亮,说明单色灯完好,反之坏掉。

.(3)双色灯测试将双色灯DR1~DR4,DG1~DG1分别与电平开关K0~K7相连。

如果双色灯与电平开关的关系如下表3.4.1所示,说明双色灯正常工作。

表4交通灯的状态表输入输出DR DG YL L 黄L H 红H L 绿H H 灭是否正常工作(4)测试8255是否正常工作将8255片选信号接在74LS138译码器的F220端上。

分3次分别将8255的PA0~PA7、PB0~PB7、PC0~PC7端口分别连接8个发光二极管,编写程序运行,如果三次灯全亮,表示端口全好,否则,相对应的端口坏掉。

①测试8255的PA口作输出是否正常工作PA55 EQU 220HPB55 EQU 221HPC55 EQU 222HPCTRL EQU 223HDATA SEGMENTDATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATASTART: MOV DX,PCTRLMOV AL,10000001BOUT DX,ALMOV DX,PA55OUT DX,ALJMP STARTCODE ENDSEND START8255的PA口作输出正常工作口作输出是否正常工作②测试8255的PB口作输出是否正常工作PA55 EQU 220H PB55 EQU 221H PC55 EQU 222H PCTRL EQU 223H DATA SEGMENT DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA START: MOV DX,PCTRL MOV AL,10000001B OUT DX,AL MOV DX,PB55 OUT DX,AL JMP START CODE ENDSEND START8255的PB 口作输出正常工作③测试8255的PC 口低四位作输入口低四位作输入、、高四位作输出是否正常工作高四位作输出是否正常工作PA55 EQU 220H PB55 EQU 221H PC55 EQU 222H PCTRL EQU 223H DATA SEGMENT DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA START: MOV DX,PCTRL MOV AL,10000001B OUT DX,AL MOV DX,PC55 OUT DX,AL JMP START CODE ENDS END START8255的PC 口低四位作输入、高四位作输出正常工作 3.4.2测试7474LS32LS32逻辑功能的实现PA55 EQU 220H PB55 EQU 221H PC55 EQU 222H PCTRL EQU 223H DATA SEGMENT DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATASTART:MOV DX,PCTRLMOV AL,10000001B ;对8255进行初始化OUT DX,ALP1: MOV DX,PC55MOV AL,10H ;单色灯灭OUT DX,ALMOV DX,PA55MOV AL,0FFH ; 交通灯灭OUT DX,ALMOV DX,PB55MOV AL,00HOUT DX,ALMOV DX,PC55IN AL,DXAND AL,0FHCMP AL,00HJZ OKTEST AL,01HJZ GR1MOV AL,0EFH ;门一红灯JMP M2GR1: MOV AL,0FEH ;门一绿灯M2: MOV BL,AL ;保持门一状态MOV DX,PC55IN AL,DXTEST AL,02HJZ GR2MOV AL, 0DFH ;门二红灯JMP M3GR2: MOV AL, 0FDH ;门二绿灯M3: AND BL,AL ;保持前两个门的状态MOV DX,PC55IN AL,DXTEST AL,04HJZ GR3MOV AL, 0BFH ;门三红灯JMP M4GR3: MOV AL, 0FBH ;门三绿灯M4: AND BL,AL ;保持前三个门的状态MOV DX,PC55IN AL,DXTEST AL,08HJZ GR4MOV AL, 07FH ;门四红灯JMP NEXTGR4: MOV AL, 0F7H ;门四绿灯NEXT:AND AL,BL ;保持前四个门的状态MOV DX,PA55OUT DX,ALJMP P1OK: MOV DX,PA55MOV AL,0F0H ;显示四绿OUT DX,ALMOV DX,PC55MOV AL,0EFHOUT DX,ALJMP P1CODE ENDSEND START3.5重点难点技术分析重点难点技术分析74LS32实现2输入4或门功能,根据真值表,当两个输入的信号至少一个为1时,输出信号就为1,这样通过测试输入信号为00时就可以测试芯片74LS02是否正常工作。