S3C2416芯片手册-中文不完整版

S3C2410中文手册第1章_产品综述

UART................................................................................................................................................ 4 DMA控制器 .....................................................................................................................................5 A/D转换和触摸屏接口 ...................................................................................................................5 LCD控制器STN LCD显示特性 ......................................................................................................5 TFT彩色显示屏 ............................................................................................................................... 5 看门狗定时器.................................................................................................................................. 5 IIC总线接口 ....................................................................................................................................6 IIS总线接口 .....................................................................................................................................6 USB主设备 ......................................................................................................................................6 SD主机接口 ..................................................................................................................................... 6 SPI接口 ............................................................................................................................................ 6 工作电压.......................................................................................................................................... 7 操作频率.......................................................................................................................................... 7 封装.................................................................................................................................................. 7 1.2 内部结构图....................................................................................................................................8 表 1-1 272-FBGA 引脚分配及顺序..........................................................................................9 表 1-2 272-FBGA封装的引脚分配..........................................................................................12 信号描述........................................................................................................................................ 21 表 1-3 S3C2410A信号描述.........................................................................................................21 表 1-4 S3C2410A 专用寄存器...................................................................................................25

S3C2410中文手册第5章_存储器控制器

S3C2410A 中文数据手册(第五章)

杭州立宇泰电子有限公司编著(Version 1.0)

SDRAM的BANK地址引脚连接

表 5-2. SDRAM Bank 地址结构

Bank大小 2MB 4MB 8MB 16MB

32MB 64MB 128MBห้องสมุดไป่ตู้

总线宽度 x8 x16 x8 x16 x32 x16 x32 x8 x8 x16 x16 x32 x32 x8 x8 x16 x16 x32 x32 x8 x16 x16 x16 x32 x32 x16 x32 x8 x16 x32 x16 x32 x8 x32

0x307f_ffff

0x30ff_ffff

0x3000_0000 0x31ff_ffff

0x3000_0000 0x3000_0000

0x33ff_ffff

0x37ff_ffff

Bank 7

起始 0x3020_0000 0x3040_0000 0x3080_0000

地址

0x3100_0000

终址 地址

OM0 (操作模式0) 0 1 0 1

导入ROM 数据宽度 Nand Flash Mode

16-bit 32-bit Test Mode

存储器(SROM/SDRAM)地址引脚的连接

MEMORY ADDR. PIN

A0 A1

S3C2410A ADDR. @ 8-bit DATA BUS A0 A1

•••

x32

(8M x 16 x 4banks) x 2 ea

5.2.1nWAIT 引脚的作用

如果对每个bank使能WAIT功能,当对某个bank区进行访问时,nOE的低电平有效时间 就会在nWAIT引脚的控制下延长。从tacc-1时刻开始检测nWAIT的状态。在采样到nWAIT为 高电平后的下一个时钟,nOE将恢复高电平。nWAIT对nWE信号的作用与对nOE信号相同。

S3C2410中文手册第14章 中断控制器

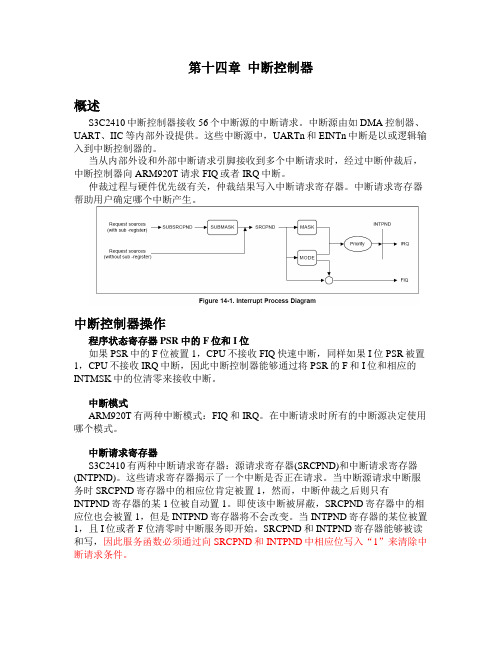

第十四章中断控制器概述S3C2410中断控制器接收56个中断源的中断请求。

中断源由如DMA控制器、UART、IIC等内部外设提供。

这些中断源中,UARTn和EINTn中断是以或逻辑输入到中断控制器的。

当从内部外设和外部中断请求引脚接收到多个中断请求时,经过中断仲裁后,中断控制器向ARM920T请求FIQ或者IRQ中断。

仲裁过程与硬件优先级有关,仲裁结果写入中断请求寄存器。

中断请求寄存器帮助用户确定哪个中断产生。

中断控制器操作程序状态寄存器PSR中的F位和I位如果PSR中的F位被置1,CPU不接收FIQ快速中断,同样如果I位PSR被置1,CPU不接收IRQ中断,因此中断控制器能够通过将PSR的F和I位和相应的INTMSK中的位清零来接收中断。

中断模式ARM920T有两种中断模式:FIQ和IRQ。

在中断请求时所有的中断源决定使用哪个模式。

中断请求寄存器S3C2410有两种中断请求寄存器:源请求寄存器(SRCPND)和中断请求寄存器(INTPND)。

这些请求寄存器揭示了一个中断是否正在请求。

当中断源请求中断服务时SRCPND寄存器中的相应位肯定被置1,然而,中断仲裁之后则只有INTPND寄存器的某1位被自动置1。

即使该中断被屏蔽,SRCPND寄存器中的相应位也会被置1,但是INTPND寄存器将不会改变。

当INTPND寄存器的某位被置1,且I位或者F位清零时中断服务即开始。

SRCPND和INTPND寄存器能够被读和写,因此服务函数必须通过向SRCPND和INTPND中相应位写入“1”来清除中断请求条件。

中断屏蔽寄存器INTMSK通过中断屏蔽寄存器的哪个屏蔽位被置1可以知道哪个中断被禁止。

如果INTMSK的某个屏蔽位为0,此中断将会被正常服务。

如果中断源产生了一个请求,SRCPND中的源请求位被置位,即使相应屏蔽位为1。

中断源下表列出了中断控制器支持的56个中断源中断优先级产生模块其中32个中断请求的优先级逻辑有由个rotation based仲裁位组成:6个一级仲裁位和一个二级位,如图14-2所示。

S3C2410_第六章NAND

S3C2410A中文数据手册(第六章)第六章 NAND FLASH控制器6.1概述 (2)6.2特性 (2)6.2.1自动导入模式步骤 (3)6.2.2NAND FLASH 模式配置 (3)6.2.3NAND FLASH 存储器时序 (4)6.2.4管脚配置 (4)6.2.5系统引导和NAND FLASH配置 (4)6.2.6NAND Flash存储空间分布 (5)6.3专用寄存器 (6)6.3.1NAND FLASH 配置(NFCONF)寄存器 (6)6.3.2NAND FLASH 命令设置(NFCMD)寄存器 (7)6.3.3NAND FLASH地址设置 (NFADDR)寄存器 (8)6.3.4NAND FLASH 数据 (NFDATA)寄存器 (8)6.3.5NAND FLASH ECC (NFECC) 寄存器 (9)第 1 页共 9 页S3C2410A中文数据手册(第六章).0)6.1概述当前,NOR flash存储器的价格比较昂贵,而SDRAM和NAND flash存储器的价格相对来说比较合适,这样就激发了一些用户产生希望从NAND flash启动和引导系统,而在SDRAM上执行主程序代码的想法。

S3C2410A恰好满足这一要求,它可以实现从NAND flash上执行引导程序。

为了支持NAND flash的系统引导,S3C2410A具备了一个内部SRAM缓冲器,叫做“Steppingstone”。

当系统启动时,NAND flash存储器的前面4KByte字节将被自动载入到Steppingstone中,然后系统自动执行这些载入的引导代码。

一般情况下,这4K的引导代码需要将NAND flash中程序内容拷贝到SDRAM中,在引导代码执行完毕后跳转到SDRAM执行。

使用S3C2410A内部硬件ECC功能可以对NAND flash的数据进行有效性的检测。

6.2特性z NAND Flash模式:支持读/擦/编程NAND flash存储器。

基于S3C2416芯片开发及其应用(嵌入式大作业)

题目:针对某一个或一类CPU,提出以其为核心的嵌入式系统完整开发方案。

要求:1 相应CPU介绍;2 硬件开发平台选择与介绍;3 软件开发平台选择与介绍;4 典型应用实例介绍;5 相关参考文献。

题目:基于S3C2416芯片开发及其应用目录摘要 (1)1 CPU介绍 (2)1.1 芯片简介 (2)1.2 芯片特性 (2)1.3 芯片架构框图 (7)1.4 芯片引脚分配 (8)2硬件开发平台选择与介绍 (9)2.1 ICOOL2416 概述 (9)2.2 ICOOL2416开发板硬件资源说明 (10)3软件开发平台选择与介绍 (12)3.1 嵌入式Linux 系统简介 (12)3.2 嵌入式Linux 交叉开发环境的搭建 (13)3.2.1 嵌入式Linux 交叉开发软件环境的搭建 (13)3.2.2 超级终端的配置 (13)3.3 Linux 操作系统移植 (13)4典型应用实例介绍 (15)4.1 纸币清分机 (15)4.1.1硬件设计 (15)4.1.2软件系统设计与实现 (16)4.2多功能公交车载终端系统 (17)4.2.1硬件整体设计 (17)4.2.2系统软件设计与实现 (17)参考文献 (19)摘要随着现代计算机和互联网技术的快速发展,嵌入式系统已然成为当前软件开发领域最热的焦点之一。

ARM 凭借其高性能低功耗等特征,正在逐渐成为目前应用最广泛的32位嵌入式处理器。

其中S3C2416是一款低功耗、高性能、低成本的SAMSUNG ARM9(ARM926EJ)处理器,最具性价比优势的芯片,S3C2440最完美的替代者,可应用于消费类电子、低功耗产品和高性能控制设备。

Linux 是一套免费使用和自由传播的类Unix操作系统,其具有模块化程度高;源码公开;广泛的硬件支持;安全性及可靠性好等优点,得到非常广泛的应用。

本文针对S3C2416芯片,阐述了其构成与特性。

并介绍了一款基于此芯片的硬件开发平台——ICOOL2416开发板,以及相应的Linux开发平台的搭建。

S3C2410 中文手册.asp

二、开发板特性及资源 .............................................................. 6

八、使用 EMBEST IDE 调试软件 ............................................... 35

1、 测试例程........................................................................................................................35 2、 操作步骤........................................................................................................................36

Embest® is registered trademarks of Embest Info&Tech Co.,LTD.

2004 英蓓特公司版权所有

2

目录

前 言 .................................................................................. 4

2004 英蓓特公司版权所有

1

版本说明

本指导书为 Embest S3CEB2410 开发系统使用指导 Version 1.0 版本。因时间仓促,该 版本仅简单介绍了 Embest S3CEB2410 开发系统的硬件及部分软件测试,我们将在后续的 修订版本中加入更详细的内容。关于 Embest S3CEB2410 开发系统使用指导书的最新版本, 敬请关注英蓓特公司网站或直接联系英蓓特公司市场部。

三星S3C2416开发板手册

第四章 结构框图 ..........................................................................................................................26

第五章 电源设计 ..........................................................................................................................27

第二章 硬件特性 ............................................................................................................................4

2.1 参数特性 .......................................................................................................................................4 2.2 核心板外观 ...................................................................................................................................5 2.3 规格尺寸 .......................................................................................................................................5 2.4 底板正面图 ...................................................................................................................................6 2.5 底板结构布局 ...............................................................................................................................6 2.6 底板硬件接口 ...............................................................................................................................7 2.7 液晶屏模块(UT_LCD43C) .....................................................................................................8 2.8 核心板引脚定义 ...........................................................................................................................9

S3C2410中文手册第7章 时钟和功率管理

第七章时钟和功率管理概述时钟和功率管理模块由三部分组成:时钟控制,USB控制和功率控制。

S3C2410A的时钟控制逻辑能够产生系统所需要的时钟,包括CPU的FCLK,AHB总线接口的HCLK,和APB总线接口的PCLK。

S3C2410A有两个PLL,一个用于FCLK,HCLK,PCLK,另一个用于USB模块(48MHZ)。

时钟控制逻辑能够由软件控制不将PLL连接到各接口模块以降低处理器时钟频率,从而降低功耗。

S3C2410A有各种针对不同任务提供的最佳功率管理策略,功率管理模块能够使系统工作在如下4种模式:正常模式,低速模式,空闲模式和掉电模式。

正常模式:功率管理模块向CPU和所有外设提供时钟。

这种模式下,当所有外设都开启时,系统功耗将达到最大。

用户可以通过软件控制各种外设的开关。

例如,如果不需要定时器,用户可以将定时器时钟断开以降低功耗。

低速模式:没有PLL的模式。

与正常模式不同,低速模式直接使用外部时钟(XTIpll或者EXTCLK)作为FCLK,这种模式下,功耗仅由外部时钟决定。

空闲模式:功率管理模块仅关掉FCLK,而继续提供时钟给其他外设。

空闲模式可以减少由于CPU核心产生的功耗。

任何中断请求都可以将CPU从中断模式唤醒。

掉电模式:功率管理模块断开内部电源。

因此CPU和除唤醒逻辑单元以外的外设都不会产生功耗。

要执行掉电模式需要有两个独立的电源,其中一个给唤醒逻辑单元供电,另一个给包括CPU在内的其他模块供电。

在掉电模式下,第二个电源将被关掉。

掉电模式可以由外部中断EINT[15:0]或RTC唤醒。

功能描述时钟结构图7-1描述了时钟架构的方块图。

主时钟源由一个外部晶振或者外部时钟产生。

时钟发生器包括连接到一个外部晶振的振荡器和两个PLL(MPLL和UPLL)用于产生系统所需的高频时钟。

时钟源选择表7-1描述了模式控制引脚(OM3和OM2)和选择时钟源之间的对应关系。

OM[3:2]的状态由OM3和OM2引脚的状态在nRESET的上升沿锁存得到。

s3c2410中文手册

s3c2410中文手册简介S3C2410 是一种嵌入式处理器,由韩国三星电子公司设计和制造。

它是一款高度集成的 ARM 架构芯片,广泛应用于各种移动设备中,如智能手机、平板电脑、PDA 等。

本手册将详细介绍 S3C2410 芯片的特性、功能和使用方法,帮助开发人员更好地理解和应用该芯片。

芯片特性S3C2410 芯片具有以下主要特性:1.ARM920T 内核: S3C2410 芯片采用了 ARM920T 内核,它是一种高性能、低功耗的 32 位 RISC 处理器。

ARM920T 内核支持 ARMv4T 指令集,并具有强大的计算和处理能力。

2.高度集成的外设: S3C2410 芯片内集成了许多常用的外围设备,包括 UART、SPI、I2C、PWM 等。

这些外设可满足各种应用需求,简化了系统设计和连接。

3.多种接口: S3C2410 芯片提供了丰富的接口,如LCD 控制器、触摸屏控制器、SDIO 控制器等。

这些接口允许连接各种外部设备,如显示屏、输入设备、存储卡等,实现更丰富的功能。

4.低功耗设计: S3C2410 芯片采用先进的低功耗设计技术,具有很低的静态功耗和动态功耗。

这使得它非常适合于移动设备,延长了电池寿命。

芯片功能GPIOS3C2410 芯片提供了多个 GPIO 管脚,用来实现输入和输出功能。

GPIO 管脚可以通过软件配置为输入模式或输出模式,并可以设置电平状态。

开发人员可以利用GPIO 实现各种功能,如控制 LED 灯、读取按键状态等。

UARTS3C2410 芯片内集成了多个 UART 模块,用于串口通信。

每个 UART 模块都提供了数据传输和接收的功能,并支持多种通信协议,如 RS232、RS485 等。

开发人员可以使用 UART 实现与外部设备的串口通信。

LCD 控制器S3C2410 芯片具有强大的 LCD 控制器,支持多种显示模式和分辨率。

LCD 控制器可以控制显示屏的像素点,实现图形显示和文字显示功能。

HC24C16数据手册_v0.01

特征

工作电压 z 1.8 V~ 5.5V

内部结构 z 2048*8(16K)

支持 16 字节页写模式 标准二线双向串行接口 双向数据传输协议 兼容 1Mz (5V),400 kHz (1.8V,2.5V,2.7V)

操作 写周期内部定时(最大 5ms)

支持硬件数据写保护 输入引脚经施密特触发器滤波抑制噪声 高可靠性

单位

VCC ICC1 ICC2 ISB ILI ILO VIL VIH VOL3 VOL2 VOL1

电源电压 电源电流 电源电流 等待态电流 输入漏电流 输出漏电流 输入低电平 输入高电平 输出低电平 输出低电平 输出低电平

VCC=5.0V,在 100 KHz 工作频率下读 VCC=5.0V,在 100 KHz 工作频率下写

地址正确匹配,器件将应答一个“0”;否则,芯片将返回等待模式。

图 5 器件地址

-8-

HC24C16

写操作

字节写:在输入器件地址并得到器件应答后,需要一个 8 位数据地址和一个 8 位数据来进 行写操作;器件收到数据地址并再次返回应答信号后,时钟将前 8 位数据送入器件;接收到这 8 位数据后,器件返回应答信号,并且主控器件在收到停止命令后结束写操作(参见图 6)。

V

0.4

1.0

mA

2.0

3.0

mA

—

1.0

μA

—

3.0

μA

0.05

3.0

μA

—

VCC×0.3 V

— VCC+0.3 V

—

0.4

V

—

0.4

V

—

0.2

V

-5-

HC24C16

MEMORY存储芯片S3C2416X40-Y640中文规格书

1 OVERVIEWThe S3C2416 RISC microprocessor can support one channels of multi-master IIC-bus serial interface. A dedicated serial data line (SDA) and a serial clock line (SCL) carry information between bus masters and peripheral devices which are connected to the IIC-bus. The SDA and SCL lines are bi-directional.In multi-master IIC-bus mode, multiple S3C2416 RISC microprocessors can receive or transmit serial data to or from slave devices. The master S3C2416 can initiate and terminate a data transfer over the IIC-bus. The IIC-bus in the S3C2416 uses Standard bus arbitration procedure.To control multi-master IIC-bus operations, values must be written to the following registers:•Multi-master IIC-bus control register, IICCON•Multi-master IIC-bus control/status register, IICSTAT•Multi-master IIC-bus Tx/Rx data shift register, IICDS•Multi-master IIC-bus address register, IICADDWhen the IIC-bus is free, the SDA and SCL lines should be both at High level. A High-to-Low transition of SDA can initiate a Start condition. A Low-to-High transition of SDA can initiate a Stop condition while SCL remains steady at High Level.The Start and Stop conditions can always be generated by the master devices. A 7-bit address value in the first data byte, which is put onto the bus after the Start condition has been initiated, can determine the slave device which the bus master device has selected. The 8th bit determines the direction of the transfer (read or write). Every data byte put onto the SDA line should be eight bits in total. The bytes can be unlimitedly sent or received during the bus transfer operation. Data is always sent from most-significant bit (MSB) first, and every byte should be immediately followed by acknowledge (ACK) bit.Figure 17-1. IIC-Bus Block Diagram1.1 IIC-BUS INTERFACEThe S3C2416 IIC-bus interface has four operation modes:•Master transmitter mode•Master receive mode•Slave transmitter mode•Slave receive modeFunctional relationships among these operating modes are described below.1.2 START AND STOP CONDITIONSWhen the IIC-bus interface is inactive, it is usually in Slave mode. In other words, the interface should be in Slave mode before detecting a Start condition on the SDA line (a Start condition can be initiated with a High-to-Low transition of the SDA line while the clock signal of SCL is High). When the interface state is changed to Master mode, a data transfer on the SDA line can be initiated and SCL signal generated.A Start condition can transfer a one-byte serial data over the SDA line, and a Stop condition can terminate the data transfer. A Stop condition is a Low-to-High transition of the SDA line while SCL is High. Start and Stop conditions are always generated by the master. The IIC-bus gets busy when a Start condition is generated. A Stop condition will make the IIC-bus free.When a master initiates a Start condition, it should send a slave address to notify the slave device. One byte of address field consists of a 7-bit address and a 1-bit transfer direction indicator (showing write or read).If bit 8 is 0, it indicates a write operation (transmit operation); if bit 8 is 1, it indicates a request for data read (receive operation).The master will complete the transfer operation by transmitting a Stop condition. If the master wants to continue the data transmission to the bus, it should generate another Start condition as well as a slave address. In this way, the read-write operation can be performed in various formats.Figure 17-2. Start and Stop ConditionFigure 17-4. Data Transfer on the IIC-Bus1.4 ACK SIGNAL TRANSMISSIONTo complete a one-byte transfer operation, the receiver should send an ACK bit to the transmitter. The ACK pulse should occur at the ninth clock of the SCL line. Eight clocks are required for the one-byte data transfer. The master should generate the clock pulse required to transmit the ACK bit.The transmitter should release the SDA line by making the SDA line High when the ACK clock pulse is received. The receiver should also drive the SDA line Low during the ACK clock pulse so that the SDA keeps Low during the High period of the ninth SCL pulse.The ACK bit transmit function can be enabled or disabled by software (IICSTAT). However, the ACK pulse on the ninth clock of SCL is required to complete the one-byte data transfer operation.Figure 17-5. Acknowledge on the IIC-Bus。

S3C2410X中文数据手册

S3C2410X中文数据手册S3C2410X32位RISC微处理器用户手册第一章产品综述 (5)介绍: (5)1.1特性 (6)体系结构 (6)系统管理器 (6)NAND Flash 启动引导 (7)Cache 存储器 (7)时钟和电源管理 (7)中断控制器 (8)具有脉冲带宽调制功能的定时器 (8)RTC(实时时钟) (8)通用I/O端口 (8)UART (9)DMA控制器 (9)A/D转换和触摸屏接口 (9)LCD控制器STN LCD显示特性 (9)TFT彩色显示屏 (10)看门狗定时器 (10)IIS总线接口 (10)USB主设备 (10)USB从设备 (10)SD主机接口 (11)SPI接口 (11)工作电压 (11)操作频率 (11)封装 (11)1.2 内部结构图 (12)表1-1 272-FBGA引脚分配及顺序 (14)表1-2 272-FBGA封装的引脚分配 (16)表1-3 S3C2410X信号描述 (24)表1-4 S3C2410X特殊功能寄存器 (30)第二章处理器工作模式 (45)2.1 概述 (46)2.2 处理器工作状态 (46)2.3 切换状态 (47)2.4指令长度 (48)2.5操作模式 (48)2.6 寄存器 (49)2.7程序寄存器状态 (51)2.8 异常 (53)第三章 ARM指令集 (59)3.1 指令格式 (60)3.2 条件码 (62)3.3 分支和转换指令(BX) (63)3.4转移及带链接的转移指令(B,BL) (64)3.5 数据处理指令 (65)3.6 PSR 转移指令(MRS,MSR) (71)3.7 乘法及乘加指令(MUL,MLA) (75)3.8 长乘及长乘加指令(MULL,MLAL) (77)3.9单数据传输指令(LDR,STR) (79)3.10半字和带符号的数据传输(LDRH/STRH/LDRSB/LDRSH) (82) 3.11块数据传输(LDM,STM) (87)3.12 单数据传输指令(SWP) (94)3.13 软件中断指令(SWI) (95)3.14 协处理器数据操作(CDP) (97)3.15 协处理器数据传输指令(LDC,STC) (98)3.16 协处理器寄存器传输指令(MRC,MCR) (99)3.17 未定义指令 (99)第五章存储器控制器 (99)5.1 概述 (99)5.2 功能描述 (101)5.2.1 bank0总线宽度 (101)5.2.2 nWAIT引脚的作用 (103)5.2.3 nXBREQ/nXBACK引脚操作 (104)5.3 存储器接口举例 (105)5.4 特殊功能寄存器 (111)5.4.1 总线宽度和等待控制寄存器(BWSCON) (111)5.4.2 总线控制寄存器(BANKCONN:nGCS0-nGCS5) (113)5.4.3 BANK控制寄存器(BANKCONn:nGCS6-nGCS7) (114) 5.4.4 刷新控制寄存器 (115)5.4.5 BANKSIZE 寄存器 (115)5.4.6 SDRAM模式寄存器集寄存器(MRSR) (116)第六章 NAND FLASH寄存器 (117)6.1 概述 (117)6.2 特性 (117)6.2.1 自动导入模式步骤 (118)6.2.3 NAND FLASH存储器时序 (119)6.2.4 管脚配置 (119)6.2.6 NAND Flash存储空间分布 (121)6.3 专用寄存器 (122)6.3.1 NAND FLASH 配置(NFCONF)寄存器 (122)6.3.2 NAND FLASH命令设置(NFCMD)寄存器 (122)6.3.3 NAND flash地址设置(NFADDR)寄存器 (123)6.3.4 NAND FLASH 数据(NFDATA)寄存器 (123)6.3.5 NAND FLASH ECC(NFECC)寄存器 (123)第七章时钟与电源管理 (124)7.1概述: (124)7.2 功能描述 (125)7.2.1 时钟结构: (125)7.2.2锁相环(PLL): (126)7.2.3时钟控制逻辑: (128)7.2.4 加电重启:(XTIpll) (128)7.2.5 USB时钟控制: (130)7.2.7电源管理: (131)7.3 特殊功能寄存器 (138)第8章DMA (141)8.1 概述 (141)8.2 DMA工作过程 (142)8.3 DMA特殊功能寄存器 (146)第九章I/O端口 (152)9.1 概述 (152)9.2 端口功能控制描述 (156)9.3 I/O端口控制专用寄存器 (156)第十章PWM Timer (172)9.1 概述 (172)9.2特性 (173)预定标器和分割器 (174)定时器基本操作 (175)自动加载和双缓冲模式 (175)用手动更新位和逆变器位对定时器进行初始化 (176) 定时器操作步骤: (176)脉宽调制 (177)输出电平控制 (178)死区发生器 (178)DMA请求模式 (179)9.3 PWM定时器专用寄存器 (180)第十一章UART (185)11.1 概述 (185)11.2 UART操作: (186)数据传输: (187)2. 数据接收: (187)3.自动流控制 (187)4.非自动流控制实例(软件控制nRTS及nCTS) (188)5. 中断/DMA请求的产生 (188)6.UART错误状态FIFO (189)7.波特率的产生 (190)8.回环模式 (190)9.红外模式 (191)11.3 UART特殊功能寄存器 (192)第十四章中断控制器 (198)14.1 S3C2410X 中断概述 (198)14.2S3C2410X 中断控制器的操作 (199)14.3S3C2410X 中断源 (199)14.4S3C2410X 中断控制器的特殊功能寄存器 (202) 第十七章RTC (210)17.1 概述 (210)17.2 实时时钟操作 (211)17.3 RTC特殊功能寄存器 (212)第十八章看门狗 (216)18.1 概述 (216)18.2 看门狗定时器特殊功能寄存器 (216)第十九章SD接口 (218)19.1 概述 (218)19.2 SDI特殊功能寄存器 (219)第二十章 IIC (226)20.1 概述 (226)20.2 IIC总线接口 (227)20.3 IIC总线接口特殊功能寄存器 (233)第二十一章IIS总线接口 (235)21.1 概述: (235)21.2 功能描述 (236)21.3 S3C2410X 音频串行接口格式 (236)21.4 S3C2410X IIS接口特殊功能寄存器 (238)第二十二章 SPI (241)22.1 概述 (241)22.2 SPI特殊功能寄存器 (245)第二十三章总线优先权 (248)23.1 概述 (248)23.2 总线优先权 (248)第一章产品综述介绍:本手册描述了三星公司推出的16/32位RISC微处理器S3C2410X。

s3c2440芯片中文手册-16 ADC&TSC

ADCDLY 位

描述

初始值

DELAY

[15:0] (1) 普通转换模式,XY坐标模式,自动坐标模式。

00ff

->AD转换开始延迟值。

(2) 等待中断模式。

当光标按下出现在睡眠模式时,产生一个用于退出睡眠模式

的唤醒信号,有几个毫秒的时间间隔。注:不要用 0 值

注:在ADC转换前,触摸屏使用晶振时钟(3.68MHz),在AD转换中使用GCLK(最大

(3) 自动(连续)XY坐标转换模式

自动(连续)XY坐标转换模式是如下操作,触摸屏控制器连续的转换触摸X坐标和Y坐

标。在触摸控制器写X测量数据到ADCDAT0 且写Y测量数据到ADCDAT1 后,触摸屏接口

产生中断源到自动坐标转换模式下的中断控制器。

XP

XM

YP

YM

X Position Conversion Y Position Conversion

50MHz)。

16.5.4 ADC 转换数据寄存器 0

ADC CONVERSION DATA REGISTER (ADCDAT0)

寄存器

地址

读写

描述

ADCDAT0

0x5800000C

R/W ADC转换数据寄存器

复位值 -

ADCDAT0

UPDOWN

AUTO_PST XY_PST

保留 XPDATA

位

[15]

无操作模式)

XP

XM

YP

YM

Waiting for Interrupt Mode Pull up

Hi-Z

备用模式:

AIN[5]

GND

备用模式在ADCCON[2]置 1 时激活。在此模式下,AD转换操作停止,ADCDAT0 和

S3C2410中文手册:SPI总线

S3C2410中文手册:SPI总线SPI总线概述S3C2410的串行外设接口SPI可以进行串行数据传输接口。

S3C2410具有两个SPI,每个SPI具有两个8位移位寄存器用于独立地发送和接收数据。

在SPI传输过程中,数据时同时发送和接收的(全双工),8位串行数据传输频率由相应的控制寄存器设置,如果希望仅发送数据,则接收数据can be dummy,同样如果只希望接收数据,则应该发送dummy '1' data。

有4个与SPI传输相关的引脚:SCK (SPICLK0,1)、MISO (SPIMISO0,1)数据线、MOSI (SPIMOSI0,1) 数据线、SS (nSS0,1)-低电平有效。

特性— SPI 2.11版协议兼容8位发送移位寄存器—— 8位接收移位寄存器— 8位预定标器逻辑Polling、中断、DMA传输模式—方框图图22-1 SPI方框图SPI操作使用SPI接口,S3C2410能够与外部设备同时收发8位数据。

一个串行时钟线SCK用于同步两根数据线来以为和采样信息。

当SPI为主机时,可以通过设置SPPREn寄存器的适当的位来控制传输频率,你可以通过调整波特率寄存器的值修改它的的频率。

如果SPI是从机,由另外的主机提供时钟。

当用户向SPTDATn寄存器中写入数据时,SPI接收/发送操作将同步开始。

某些情况下,nSS应该在数据写入SPTDATn之前有效。

编程流程当一个数据被写入SPTDATn寄存器时,如果ENSCK和SPCONn寄存器中的MSTR位被置位,则启动数据发送。

可以根据如下步骤对SPI模块进行编程:1. 设置波特率预定标器寄存器SPPREn2. 设置SPCONn来恰当地配置SPI模块3. 向SPTDATn写入10次0XFF来初始化MCC或SD卡4. 设置作为nSS的GPIO,配置为低电平使MCC或SD卡生效5. Tx数据—>检查Transfer Ready flag (REDY = 1)的状态,然后向SPTDATn写入数据。

MEMORY存储芯片S3C2416XH-40中文规格书

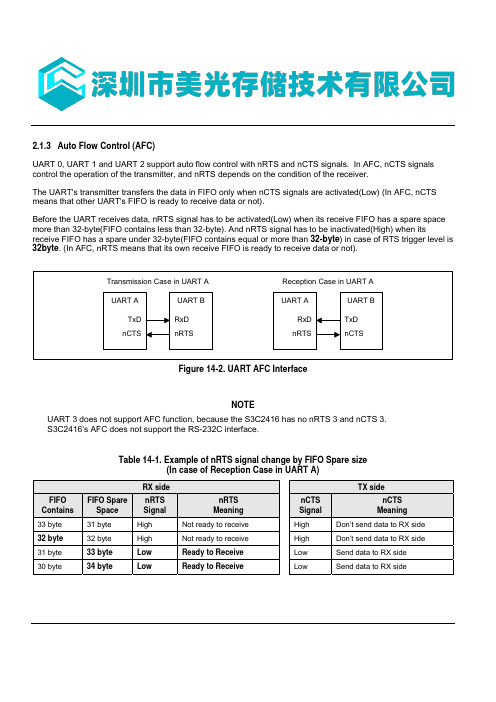

2.1.3 Auto Flow Control (AFC)UART 0, UART 1 and UART 2 support auto flow control with nRTS and nCTS signals. In AFC, nCTS signals control the operation of the transmitter, and nRTS depends on the condition of the receiver.The UART's transmitter transfers the data in FIFO only when nCTS signals are activated(Low) (In AFC, nCTS means that other UART's FIFO is ready to receive data or not).Before the UART receives data, nRTS signal has to be activated(Low) when its receive FIFO has a spare space more than 32-byte(FIFO contains less than 32-byte). And nRTS signal has to be inactivated(High) when itsreceive FIFO has a spare under 32-byte(FIFO contains equal or more than 32-byte ) in case of RTS trigger level is 32byte . (In AFC, nRTS means that its own receive FIFO is ready to receive data or not).Figure 14-2. UART AFC InterfaceNOTEUART 3 does not support AFC function, because the S3C2416 has no nRTS 3 and nCTS 3. S3C2416’s AFC does not support the RS-232C interface.Table 14-1. Example of nRTS signal change by FIFO Spare size(In case of Reception Case in UART A)RX sideTX sideFIFO Contains FIFO Spare Space nRTS Signal nRTS MeaningnCTS Signal nCTS Meaning33 byte 31 byte High Not ready to receive High Don’t send data to RX side 32 byte 32 byte High Not ready to receive High Don’t send data to RX side 31 byte 33 byte Low Ready to Receive Low Send data to RX side 30 byte34 byteLowReady to ReceiveLowSend data to RX side2.1.6 Interrupt/DMA Request GenerationEach UART of the S3C2416 has seven status (Tx/Rx/Error) signals: Overrun error, Parity error, Frame error, Break, Receive buffer data ready, Transmit buffer empty, and Transmit shifter empty, all of which are indicated by the corresponding UART status register (UTRSTATn/UERSTATn).The overrun error, parity error, frame error and break condition are referred to as the receive error status. Each of which can cause the receive error status interrupt request, if the receive-error-status-interrupt-enable bit is set to one in the control register, UCONn. When a receive-error-status-interrupt-request is detected, the signal causing the request can be identified by reading the value of UERSTSTn.When the receiver transfers the data of the receive shifter to the receive FIFO register in FIFO mode and the number of received data reaches Rx FIFO Trigger Level, Rx interrupt is generated. If the Receive mode is in control register (UCONn) and is selected as 1 (Interrupt request or polling mode). In the Non-FIFO mode, transferring the data of the receive shifter to receive holding register will cause Rx interrupt under the Interrupt request and polling mode.When the transmitter transfers data from its transmit FIFO register to its transmit shifter and the number of data left in transmit FIFO reaches Tx FIFO Trigger Level, Tx interrupt is generated, if Transmit mode in control register is selected as Interrupt request or polling mode. In the Non-FIFO mode, transferring data from the transmit holding register to the transmit shifter will cause Tx interrupt under the Interrupt request and polling mode.Note that the Tx interrupt is always requested whenever the number of data in the transmit FIFO is smaller than the trigger level. This means that an interrupt is requested as soon as you enable the Tx interrupt unless you fill the Tx buffer prior to that. It is recommended to fill the Tx buffer first and then enable the Tx interrupt.If the Receive mode and Transmit mode in control register are selected as the DMAn request mode then DMAn request occurs instead of Rx or Tx interrupt in the situation mentioned above.Table 14-2. Interrupts in Connection with FIFOType FIFO Mode Non-FIFO ModeRx Interrupt Generated whenever receive data reaches thetrigger level of receive FIFO.Generated when the number of data in FIFO doesnot reaches Rx FIFO trigger Level and does notreceive any data during 3 words time (receive timeout). This interval follows the setting of Word Lengthbit. Generated by the receiving holding register whenever receive buffer becomes full.Tx Interrupt Generated whenever transmit data reaches thetrigger level of transmit FIFO (Tx FIFO triggerLevel). Generated by the transmitting holding register whenever transmit buffer becomes empty.Error Interrupt Generated when frame error, parity error, or break signal are detected.Generated when it gets to the top of the receiveFIFO without reading out data in it (overrun error). Generated by all errors. However if another error occurs at the same time, only one interrupt is generated.2.1.7 UART Error Status FIFOUART has the error status FIFO besides the Rx FIFO register. The error status FIFO indicates which data, among FIFO registers, is received with an error. The error interrupt will be issued only when the data, which has an error, is ready to read out. To clear the error status FIFO, the URXHn with an error and UERSTATn must be read out.For example,It is assumed that the UART Rx FIFO receives A, B, C, D and E characters sequentially and the frame error occurs while receiving 'B', and the parity error occurs while receiving 'D'.The actual UART receive error will not generate any error interrupt because the character which is received with an error would have not been read. The error interrupt will occur once the character is read.Figure 14-3 shows the UART receiving the five characters including the two errors.Time Sequence Flow Error Interrupt Note#0 When no character is read out −#1 A, B, C, D, and E is received −#2 After A is read out The frame error (in B) interrupt occurs.The 'B' has to be read out.#3 After B is read out −#4 After C is read out The parity error (in D) interrupt occurs.The 'D' has to be read out.#5 After D is read out −#6 After E is read out −Figure 14-3. Example showing UART Receiving 5 Characters with 2 Errors。

S3C2410A中文数据手册 ADC和触摸屏接口

S3C2410的ADC和触摸屏接口16.1概述 (2)16.2特性 (2)16.3ADC和触摸屏接口操作 (2)16.3.1结构图 (2)16.3.2触摸屏接口举例 (3)16.4功能描述 (4)16.4.1 A/D转换时间 (4)16.4.2 触摸屏接口工作模式 (4)(1)普通转换模式 (4)(2)分离的X/Y轴坐标转换模式 (4)(3)自动(连续)X/Y轴坐标转换模式。

(5)(4)等待中断模式 (5)(5)静态(Standby)模式 (6)16.5编程要点 (6)16.6ADC和触摸屏接口专用寄存器 (7)ADC控制寄存器(ADCCON) (7)ADC触摸屏控制寄存器(ADCTSC) (8)ADC起始延迟寄存器(ADCDLY) (9)ADC转换数据寄存器(ADCDAT0) (10)ADC转换数据寄存器(ADCDAT1) (11)16.1概述S3C2410A的具有8通道模拟输入的10位CMOS模数转换器(ADC)。

它将输入的模拟信号转换为10位的二进制数字代码。

在2.5MHz的A/D转换器时钟下,最大转化速率可达到500KSPS。

A/D转换器支持片上采样和保持功能,并支持掉电模式。

S3C2410A的AIN[7]和AIN[5]用于连接触摸屏的模拟信号输入。

触摸屏接口电路一般由触摸屏,4个外部晶体管和一个外部电压源组成(见图16-2)。

触摸屏接口的控制和选择信号(nYPON, YMON, nXPON 和 XMON) 连接切换X坐标和Y 坐标转换的外部晶体管。

模拟输入引脚(AIN[7],AIN[5])则连接到触摸屏引脚。

触摸屏控制接口包括一个外部晶体管控制逻辑和具有中断产生逻辑的ADC接口逻辑。

16.2特性— 分辩率:10-位— 微分线性度误差:± 1.0 LSB— 积分线性度误差:± 2.0 LSB— 最大转换速率:500 KSPS— 低功耗— 供电电压:3.3V— 输入模拟电压范围:0 ~ 3.3V— 片上采样保持功能— 普通转换模式— 分离的X/Y轴坐标转换模式— 自动(连续) X/Y轴坐标转换模式— 等待中断模式16.3ADC和触摸屏接口操作16.3.1结构图图16-1是S3C2410A上的A/D转换器和触摸屏接口的功能框图。

S3C2410中文手册第7章_时钟及电源管理模块

S3C2410中文手册第7章_时钟及电源管理模块第七章时钟及电源管理模块时钟电源管理模块包含了3部分:Clock控制、USB控制、POWER控制.时钟控制逻辑单元能够产生s3c2440需要的时钟信号,包括CPU 使用的主频FCLK,AHB总线设备使用的HCLK,以及APB总线设备使用的PCLK.2440内部有2个PLL(锁相环):一个对应FCLK、HCLK、PCLK,另外一个对应的是USB使用(48MHz)。

时钟控制逻辑单元可以在不使用PLL情况下降低时钟CLOCK的频率,并且可以通过软件来驱使时钟和各个模块的连接/断开,以减少电源消耗。

对于电源控制逻辑单元,2440有许多钟电源管理方案来针对所给的任务保持最优的电源消耗。

S3c2440中的电源管理模块对应4种模式:NORMAL模式、SLOW模式,IDLE模式,SLEEP 模式。

NORMAL模式:这个模块给CPU时钟以及2440相应的外围设备提供时钟。

这个模式下,当所有的外围设备都被打开,电源消耗被最大化。

它允许用户通过软件来控制外部设备的操作。

例如,如果一个定时器不需要时,那么用户可以通过CLKCON寄存器来关闭时钟和定时器的连接,来降低电源消耗。

SLOW模式:NON-PLL模式,不同于Normal模式,这个模式使用的一个外部时钟(XTlpll 或EXTCLK)来直接作为2440的主频FCLK,而没有使用PLL。

在这个模式下,电源的消耗仅依赖于外部时钟频率,电源同PLL有关的消耗可以被排除。

IDLE模式:这个模式下CPU的时钟FCLK被断开,而还继续提供其他外围设备的时钟。

因此空闲模式导致减少了CPU核相应的电源消耗。

任何中断请求都能够将CPU唤醒。

Sleep模式:这个模式断开了内部电源。

因此在这个模式下CPU &内部的逻辑单元都没有电源消耗,除了一个wake-up逻辑单元。

激活sleep模式需要2个独立的电源。

一个给wake-up逻辑模块提供电源,另外一个给内部逻辑包括CPU提供电源,并且其是对于poweron/off可控的。

S3C2416核心板、开发板硬件手册

第一章S3C2416核心板规格 (3)第一节 SOM2416-I概述 (5)第二节 SOM2416-II概述 (5)第三节 SOM2416-I核心板引脚定义 (一) (6)第三节 SOM2416-I核心板引脚定义 (二) (7)第四节 SOM2416-II核心板引脚定义(一) (8)第四节 SOM2416-II核心板引脚定义 (二) (9)第四节 SOM2416-II核心板引脚定义 (三) (10)第四节 SOM2416-II核心板引脚定义 (四) (11)第二章S3C2416开发板规格 (12)第一节KIT2416-I规格概述 (13)第二节 KIT2416-II规格概述 (13)第三节KIT2416-I开发板硬件接口概述 (14)第四节 KIT2416-II开发板硬件接口概述 (19)第三章S3C2416开发板要点说明 (26)第四章WinCE 5.0 and 6.0驱动介绍 (27)第五章Linux2.6驱动介绍 (28)声明尽管我们已经对本文件中的所有信息进行了检查并确信信息的准确性,但对信息的不准确之处不负任何责任。

我们保留随时对产品说明和规范进行更改而不事先通知的权利。

请在提交产品订单之前联系您当地的 销售处索取最新规范。

双方明确,所有的销售活动均以购买方在下订单前接受 我们公司的最新版本标准销售协议条款为前提条件。

产品可能包含设计缺陷或错误等不规则情况,而这会导致产品的功能与发布的规格不同。

如果要求,我们会为您提供不规则情况表。

我们产品不设计用于, 意在用于, 授权或保证用于因产品故障可能直接或间接导致人身伤害或严重资产损失的任何生命维系或其他应用。

若由于未经我们事先书面同意而用于此类用途和/或进一步测试和/或修改而导致的风险,由客户自行承担。

本文件或其他资料以及销售协议条款的副本可以从我们的网站获得。

本文中提涉及到的各个商标归商标注册商所有!第一章S3C2416核心板规格S3C2416核心板(SOM2416-I和SOM2416-II)是面向手持设备(电子书、行业PDA、GPS、手持抄表机等)、医疗行业(便携式监护仪、视力测试仪)、工业控制(HMI、数据记录仪、气体频谱仪、气体在线分析仪)、汽车电子(车载调度系统、车载电脑检测仪)等行业提供的高性能低成本系统解决方案。

(word完整版)S3C2416芯片手册整理

S3C2416芯片手册整理V1.0版本历史2014-2—20版权所有目录第一章简介概述 (3)1.1 芯片简介 (3)1.2 芯片特性 (3)1.2.1 系统管理 (3)1.2.2 NAND Flash 启动引导(BootLoader) (3)1。

2.3 时钟和电源管理 (4)1。

2.4 中断控制器 (4)1。

2.5 带脉宽调制(PWM)的定时器 (4)1.2.6 RTC (4)1.2。

7 通用输入/输出端口 (4)1。

2.8 DMA控制器 (5)1。

2.9 UART (5)1。

2。

10 LCD控制器 (5)1。

2.11 ADC和触摸屏接口 (5)1。

2.12 看门狗定时器 (5)1。

2.13 IIC总线接口 (5)1。

2。

14 IIS音频接口 (6)1。

2。

15 AC97音频接口 (6)1.2.16 PCM音频接口 (6)1.2.17 USB Host (主机) (6)1。

2。

18 USB Device (设备) (6)1。

2。

19 SD/MMC主机接口 (6)1.2.20 SPI接口 (7)1。

2.21 2D (7)1.2.22 工作电压范围 (7)1.2。

23 封装 (7)1.3 芯片架构框图 (8)1。

4 芯片引脚分配 (9)第二章中央处理平台ARM选型需求 (9)2。

1 运算能力及吞吐量需求 (9)2.2 必要接口需求 (10)2。

3 可选接口需求 (10)第三章选型参数对比 (10)第一章简介概述1。

1 芯片简介三星S3C2416是一款32位RISC处理器,应用于消费类电子、低功耗产品和高性能控制设备。

S3C2416基于ARM926EJ内核,65nm工艺制程,采用新的高性能微控制器总线(AMBA)架构设计,具有低功耗、高性能和低成本的特性。

1.2 芯片特性S3C2416提供一整套完整的系统外设,最大限度的减少系统额外成本和额外组件。

S3C2416芯片集成以下片上功能:1、ARM926EJ内核,主频400MHz,16KB I/D—Cache和MMU功能2、支持外部存储器mSDR、mDDR、DDR2 、SDRAM3、LCD控制器,最高支持256K色显示,提供1通道LCD专用DMA4、6通道DMA控制器并有外部请求引脚5、4通道UART(IrDA1.0, 64—Byte Tx FIFO, and 64-Byte Rx FIFO)6、1通道高速SPI7、1通道IC总线接口(支持多主机)8、支持IIS/AC97音频接口9、兼容支持高速MMC和SD接口协议10、2路USB Host/1路USB Device11、4通道PWM定时器/ 1通道内部定时器/看门狗定时器12、10通道 12位ADC和触摸屏接口13、RTC时钟,带日历功能14、138个通用I / O端口, 16路外部中断源15、5种电源管理模式:工作、空闲、待机、深度待机和休眠模式16、芯片内有PLL时钟发生器1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微软中国[键入公司地址] [键入电话号码] [键入传真号码][选取日期]微软中国[在此处键入文档摘要。

摘要通常为文档内容的简短概括。

在此处键入文档摘要。

摘要通常为文档内容的简短概括。

]目录1、产品概述 (3)1、引言 (3)2、特点 (3)3、框图 (3)4、引脚分配 (1)4.1信号说明 (13)2系统控制器 (35)1概述 (35)2、特点 (35)3、框图 (36)4、功能说明 (36)4.1复位管理及类型 (36)4.2硬件复位 (37)4.3看门狗复位 (38)4.4软件复位 (38)4.5唤醒复位 (38)5时钟管理 (39)5.1时钟发生器概述 (39)5.2时钟源选择 (39)5.3PLL(锁相回路) (40)5.4在正常操作下,改变PLL设置 (41)5.5系统时钟控制 (41)5.6ARM和总线时钟分频比 (42)5.7配置时钟寄存器以产生AMBA时钟特定的频率 (42)5.8ESYSCLK控制 (43)6、电源管理 (43)6.1功率模式状态图 (43)6.2节能模式 (44)6.3唤醒事件 (47)6.4输出端口状态,以及停止和睡眠模式 (47)6.5省电模式进入/退出条件 (48)7寄存器说明 (48)7.1地址映射 (48)8独立的寄存器说明 (49)8.1时钟源控制寄存器(LOCKCON0,LOCKCON1,OSCSET,MPLLCON,与EPLLCON) (49)8.2时钟控制寄存器(CLKSRC,CLKDIV,HCLKCON,PCLKCON,与SCLKCON) (51)8.3电源管理寄存器(PWRMODE与PWRCFG) (54)8.4复位控制寄存器(SWRST和RSTCON) (56)8.5在普通模式和从休眠模式唤醒下,(I/O)保持位控制。

(56)8.6系统控制器状态寄存器(WKUPSTAT与RSTSTAT) (57)8.7总线配置寄存器(BUSPRI0,BUSPRI1,与BUSMISC) (57)8.8信息寄存器0,1,2,3 (59)8.9USB PHY控制寄存器(PHYCTRL) (59)8.10USB PHY电源控制寄存器(PHYPWR) (60)8.11USB复位控制寄存器(URSTCON) (60)8.12USB时钟控制寄存器(UCLKCON) (60)3总线矩阵和EBI (61)1概述 (61)2特殊功能寄存器 (61)2.1矩阵芯0优先级寄存器(BPRIORITY0) (61)2.2矩阵芯1优先级寄存器(BPRIORITY1) (61)2.3EBI控制寄存器(EBICON) (62)4总线优先事项 (63)1概述 (63)1.1总线优先图 (63)5静态存储控制器(SMC) (64)1概述 (64)2特点 (64)3框图 (65)3.1异步读 (65)3.2同步读/同步突发阅读 (66)21LCD控制 (68)1概述 (68)1.1特性 (68)1.1.1LCD控制器特点是: (68)2功能描述 (69)2.1子块简述 (69)2.2数据流程 (69)2.3接口 (70)2.4颜色数据概述 (70)1、产品概述1、引言本用户手册描述了三星的S3C2416X16/32-位RISC微处理器。

三星的S3C2416X的目的是提供手持设备和一般应用的低功率,高性能的微小裸片尺寸控制器解决方案。

为了降低系统总成本中,S3C2416X包含以下组件。

该S3C2416X开发与ARM926EJ内核,65纳米CMOS标准单元和存储编译器。

其低电源,简单,优雅和全静态设计特别适合于对成本和功耗敏感的应用。

它采用被称为高级微控制器总线架构(AMBA)的一个新的总线架构。

该S3C2416X提供出色的功能在其CPU内核,一个16/32-位ARM926EJ RISC处理器设计通过先进RISC机器公司的ARM926EJ实现了MMU,AMBA总线,和哈佛缓存结构,具有独立的16KB指令和16KB数据缓存,每一个8字线的长度。

通过提供一套完整的通用系统外设,S3C2416X最大限度地减少整体系统成本和无需配置额外的组件。

这是在所描述的集成在芯片上的功能,这份文件包括:•大约400MHz@1.3V,266MHz的@TBDV核心,1.8V/2.5V/3.0V/3.3V ROM/SRAM,1.8V/2.5VmSDR/mDDR/DDR2的SDRAM,1.8V/2.5V/3.3V外部I/O微处理器,16KB I/D-缓存/MMU •外部存储器控制器(mSDR/mDDR/DDR2SDRAM控制和片选逻辑)•LCD控制器(高达256K色)液晶专用DMA•6通道DMA控制器,外部请求引脚•4通道的UART(IrDA1.0,64字节TX FIFO和64字节RX FIFO)•1路高速SPLS•1IIC总线接口(支持多主器件)•1IIS音频编解码器接口(24位,端口0支持5.1声道)•AC97/PCM编解码器接口(复用与I2S)•2高速MMC和SDMMC二合一(SD主机2.0和MMC协议4.2兼容)•2路USB主机控制器(版本1.1兼容)/1路USB设备控制器(版本2.0)•4通道PWM定时器/1通道内部定时器/看门狗定时器•10通道12位ADC和触摸屏接口•RTC,带日历功能•138个通用I/O端口/16路外部中断源•电源控制:正常,怠速,停机,深度停止和休眠模式•片上带有PLL时钟发生器2、特点2.1.1建筑•集成系统,用于手持设备和通用嵌入式应用。

•16/32-位RISC架构和强大的指令集的ARM926EJ CPU核心。

•增强的ARM构架的MMU来支持WinCE的,EPOC32和Linux。

•指令缓存,数据缓存,写缓冲和物理地址TAG RAM来降低疗效主内存带宽和延迟上性能。

•ARM926EJ CPU核支持ARM调试架构。

•内部高级微控制器总线架构(AMBA)(AMBA2.0,AHB/APB)2.1.2系统管理•小/大端支持。

•两个独立的内存总线-一个用于ROM/ SRAM总线(ROM存储区0BANK5)和一个对于DRAM总线(mSDR/mDDR/DDR2SDRAM的存储区0 Bank1的)•地址空间:64M字节的罗BANK0 BANK5,128M字节的SDRAM BANK0 bank1的。

•支持可编程8/16-位数据总线宽度对于ROM/SRAM bank和可编程16/32-位数据总线宽度的SDRAM银行•从ROM组0定期bank起始地址bank5和SDRAM组0到BANK1。

•八个记忆库:-六个内存组ROM,SRAM和其他(NAND等)。

-两个内存银行同步DRAM。

•所有完整的可编程访问周期记忆库。

•支持外部等待信号扩展总线周期。

•支持自刷新模式,在SDRAM中的断电。

•支持多种类型的ROM用于启动(NOR闪存,EEPROM,OneNAND闪存,和IROM 其他)。

2.1.3NAND闪存•支持从NAND闪存启动,选择OM为IROM 启动模式。

(只有8位NAND和8ECC引导时支持)•64KB的内部SRAM缓冲器(8KB内部缓冲区用于引导)•支持存储存储器,用于NAND闪存开机后内存。

•支持先进的NAND闪存2.1.4高速缓存•4路与I-缓存组相联高速缓存(16KB)和D-缓存(16KB)。

•每一个有效位和两个线8words长度脏位每行。

•伪随机或循环赛更换算法。

•通过写或回写高速缓存操作更新主存储器。

•写缓冲器可容纳16字数据和四个地址。

2.1.5时钟和电源管理器•片上MPLL和EPLL:EPLL产生操作USB主机的时钟,IIS,UART等MPLL产生于MCU 的运行时钟最大400MHz@1.3五•时钟可以被选择性地供给到每个函数通过软件拦截。

•电源模式:正常,怠速,停机,深度和停止,睡眠模式普通模式:正常工作模式空闲模式:仅用于CPU的时钟停止。

停止模式:所有时钟都停止。

深停止模式:CPU功率门控和所有时钟停止。

睡眠模式:核心电源,包括所有外围设备被关闭。

•唤醒了EINT[15:0]或RTC报警及从休眠模式中断和(深)停止模式。

2.1.6中断控制器•71中断源(一个看门狗定时器,5个定时器,12个UART,16外部中断,6DMA,2RTC,2个ADC,1个IIC,1个SPI,2个SDI,2个USB,4个液晶显示,1电池故障,1NAND,1AC97和I2S1,1PCM,12D)•外部中断源电平/边沿模式边缘和水平•可编程极性•支持快速中断请求(FIQ)和紧急中断请求2.1.7定时器脉冲宽度调制(PWM)•4通道16位定时器,PWM/1通道16位内部定时器基于DMA或基于中断的作业•可编程占空比,频率,极性•死区代•支持外部时钟源2.1.8RTC(实时时钟)•完整的时钟功能:毫秒,秒,分,小时,日期,星期,月和年•32.768千赫操作•报警中断•时钟节拍中断2.1.9通用输入/输出端口•16个外部中断端口•138多路输入/输出端口2.1.10DMA控制器•6通道DMA控制器•支持内存到内存,IO内存,内存到IO和IO到IO传输•突发传输模式,以提高传输速率2.1.11LCD控制器•支持1,2,4或8BPP(位每像素)调色板,彩色显示器的颜色•支持16位,24BPP非调色板真彩色,彩色显示器•支持最大16M色,24BPP模式•支持多种屏幕尺寸-典型的实际屏幕尺寸:640×480,320×240,160x160的,等等。

-最大帧缓冲区的大小为4M字节。

-在64K色最大虚拟屏幕尺寸模式:2048×2048,以及其他•支持2个叠加窗口的LCD2.1.12UART•4通道UART,具有基于DMA或中断基于操作•支持5位,6位,7位或8位串行数据发送/接收(TX/RX)•支持外部时钟的UART操作(EXTUARTCLK)•可编程的波特率高达3Mbps的•支持IrDA1.0•环回模式下进行测试•每个通道都有内部64字节TX FIFO和64字节的接收FIFO。

2.1.13A/D转换器和触摸屏接口•10通道多路复用ADC•最大。

500KSPS和12位分辨率•内部FET,可直接触摸屏人机界面2.1.14看门狗定时器•16位看门狗定时器•中断请求或系统复位时超时2.1.15IIC-Bus接口•1通道多主IIC总线•串行,8位导向,双向数据传输可以在高达100千比特/秒中进行标准模式或高达400Kbit/s的快速模式。

2.1.162D•线/点图形•位块传送,颜色扩展。

•最大2040*2040的图像尺寸•窗口剪辑•90°/180°/270°/X-flip/Y-flip旋转•全2563操作数光栅操作(ROP)•Alpha混合•16/24/32-bpp颜色格式支持2.1.17多IIS音频接口•1端口,基于DMA的音频接口操作。