数电课件verilog_intr

数字电路中Verilog HDL语言基础知识课件

6-3Vrilog HDL语言简介硬件描述语言HDL是EDA技术中的重要组成部分,常用的硬件描述语言有Verilog HDL 、VHDL、System Verilog、System C、ABEL HDL和AHDL等,而Verilog HDL和VHDL是当前最流行的并成为IEEE标准的硬件描述语言。

3.1 HDL简介VHDL是超高速集成电路硬件描述语言(Very-High-Speed Integrated Circuit Hardware Description Language)的缩写。

VHDL作为IEEE标准的硬件描述语言和EDA的重要组成部分,经过十几年的发展、应用和完善,以其强大的系统描述能力、规范的程序设计结构、灵活的语言表达风格和多层次的仿真测试手段,在电子设计领域受到了普遍的认同和广泛的接受,成为现代EDA领域的重要的硬件设计语言。

HDL的特点1、HDL具有强大的功能,覆盖面广,描述能力强。

HDL支持门级电路的描述,也支持寄存器传输级电路的描述,还支持以行为算法描述为对象的电路的描述。

2、HDL有良好的可读性。

它可以被计算机接受,也容易被读者理解。

用HDL书写的源文件,既是程序又是文档,既是工程技术人员之间交换信息的文件,又可作为合同签约者之间的文件。

3、HDL具有良好的可移植性。

作为一种已被IEEE承认的工业标准,HDL事实上已成为通用的硬件描述语言,可以在各种不同的设计环境和系统平台中使用。

4、使用HDL可以延长设计的生命周期。

用HDL描述的硬件电路与工艺无关,不会因工艺而过时。

与工艺有关的参数可以通过HDL提供的属性加以描述,工艺改变时,只需要修改相应程序中属性参数即可。

5、HDL支持对大规模设计的分解和已有设计的再利用。

HDL可以描述复杂的电路系统,支持对大规模设计的分解,由多人、多项目组来共同承担和完成。

标准化的规则和风格,为设计的再利用提供了有力的支持。

6、HDL有利于保护知识产权。

verilog数字系统设计教程PPT课件

• 复杂数字系统的构成; • 基本电路和 Verilog 的对应关系; • 同步有限状态机在电路中的作用; • 时钟树与自动综合技术

数字逻辑电路的构成

- 组合逻辑:输出只是输入逻辑电平的函

数(有延时),与电路的原始状态无关。

• 时序逻辑:输出不只是输入的逻辑电

平的函数,还与电路所处的状态有关。

8 ‘ d 31

8‘d

t

out[15:0]

202

16 ‘ d

16‘ d

t

Sn 开

93

606

t 关

全局时钟网和平衡树结构

触发器1

全局时钟网络 触发器 图1 全局时钟网示意图

缓冲器

触发器n

图2 平衡树结构示意图

避免冒险和竞争

• 由于组合逻辑和布线的延迟引起

a

c

b

a

b

t

c

t

clock

避免冒险和竞争与流水线

t

t

带寄存器的八位数据通路控制器的波形

ControlSwitch

in[7]

out[7]

CLOCK

out[7]

D Q[7]

ControlSwitch

in[0]

out[0]

CLOCK

out[0]

D Q[0]

带寄存器的八位数据通路控制器的Verilog描述

`define ON 1 ‘b 1 `define OFF 1 ‘b 0 wire ControlSwitch; wire clock wire [7:0] out, in;

ControlSwitch in[7]

out[7]

…... …...

in[0]

第10章Verilog操作符ppt课件

module negation(); reg [3: 0] rega, regb; reg [3: 0] bit; reg log; initial begin rega = 4'b1011; regb = 4'b0000; end initial fork #10 bit = ~rega; // num = 0100 #20 bit = ~regb; // num = 1111 #30 log = !rega; // num = 0 #40 log = !regb; // num = 1 #50 $finish; join endmodule

• 按位操作符对矢量中相对应位运算。

• 位值为x时不一定产生x结果。如#50时 的or计算。

当两个操作数位数不同时,位数少 的操作数零扩展到相同位数。

a = 4'b1011; b = 8'b01010011; c = a | b; // a零扩展为 8'b00001011

逻辑操作符

! && || not and or

• 将负数赋值给reg或其它无符号变量 使用2的补码算术。

• 如果操作数的某一位是x或z,则结 果为x • 在整数除法中,余数舍弃 • 模运算中使用第一个操作数的符号

按位操作符

~ & | ^ ~^ ^~ not and or xor xnor xnor

regb = 4'b1 0 1 0 regc = 4'b1 x 1 0 num = regb & regc = 1 0 1 0 ; module bitwise (); reg [3: 0] rega, regb, regc; reg [3: 0] num; initial begin rega = 4'b1001; regb = 4'b1010; regc = 4'b11x0; end initial fork #10 num = rega & 0; // num = 0000 #20 num = rega & regb; // num = 1000 #30 num = rega | regb; // num = 1011 #40 num = regb & regc; // num = 10x0 #50 num = regb | regc; // num = 1110 #60 $finish; join endmodule

第四章 Verilog基本语法(一)PPT教学课件

2020/12/11

玉溪师范学院

参数

➢ 参数是一个常量。用parameter定义一个标识符来代表 一个常量。参数经常用于定义时延和变量的宽度。

格式: parameter param1 = const_expr1,

param2 = const_expr2,

…,

paramN = const_exprN;

assign #XOR_DELAY S=A^B;

assign #AND_DELAY C=A&B;

endmodule

19

TOP HA

2020/12/11

玉溪师范学院

参数值的模块引用

module TOP3(NewA,NewB,NewS,NewC); input NewA, NewB; output NewS,NewC; HA #(5,2) Ha1 (NewA, NewB, NewS, NewC);ut

selb

26

2020/12/11

玉溪师范学院

reg型

寄存器是数据存储单元的抽象 reg型数据常用来表示always块内的指定信号,常代表触

发器 reg型数据用initial或者always块中指定信号 reg型数据的缺省值是x。可以被赋正值或者负值。当它作

为一个表达式中的操作数时候,作为无符号数。 reg数据类型定义格式为

2.0 ; -0.1等

科学记数法,例如:

235.1e2 等于23510.0

234_12e2

等于2341200.0

实数小数通过四舍五入被隐式地转换为最相近的整数。例如:

42.446, 42.45 转换为整数42

92.5, 92.699 转换为整数93

-5.62 转换为整数-6

verilog第一讲课件

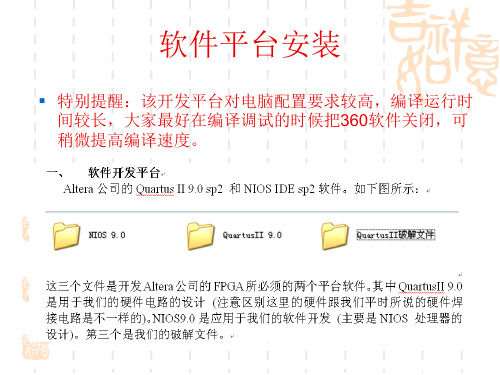

特别提醒:该开发平台对电脑配置要求较高,编译运行时 间较长,大家最好在编译调试的时候把360软件关闭,可 稍微提高编译速度。

0引言 FPGA开发的几个概念介绍 硬件描述语言HDL(Hardware Description Language) 类似于高级程序设计语言.它是一种以文本 形式来描述数字系统硬件的结构和行为的 语言,用它可以表示逻辑电路图、逻辑表达 式,复杂数字逻辑系统所的逻辑功能。 HDL是高层次自动化设计的起点和基础.

2.关键词 Verilog HDL 定义了一系列保留字,叫做关键词。注意只有小 写的关键词才是保留字。例如,标识符always (这是个关键 词)与标识符ALWAYS(非关键词)是不同的。

always and assign begin buf buf if0 bufif1 case casex casez cmos deassign default defparam disable edge else end endcase endmodule endfunction endprimitive endspecify endtable endtask event for force forever fork function highz0 highz1 if ifnone initial inout input integer join large macrmodule medium module nand negedge nmos nor not notif0 notif1 or output parameter pmos posedge primitive pull0 pull1 pullup pulldown rcmos real realtime reg release repeat rnmos rpmos rtran rtranif0 rtranif1 scalared small specify specparam strong0 strong1 supply0 supply1 table task time trantranif0 tranif1 tri tri0 tri1 triand trior trireg vectored wait wand weak0 weak1 while wire wor xnor xor

VerilogHDL数字集成电路设计原理与应用教学课件ppt作者蔡觉平_第2章

第2章 Verilog HDL基础知识2.1 Verilog HDL的语言要素2.2 数据类型2.3 运算符2.4 模块本章小结12 Verilog HDL 语法来源于C 语言基本语法,其基本词法约定与C 语言类似。

程序的语言要素也称为词法,是由符号、数据类型、运算符和表达式构成的,其中符号包括空白符、注释符、标识符和转义标识符、关键字、数值等。

2.1 Verilog HDL 的语言要素2.1.1 空白符 空白符包括空格符(\b)、制表符(\t)、换行符和换页符。

空白符使代码看起来结构清晰,阅读起来更方便。

在编译和综合时,空白符被忽略。

Verilog HDL程序可以不分行,也可以加入空白符采用多行编写。

3 例2.1-1空白符使用示例。

initial begin a = 3'b100; b = 3'b010; end 相当于: initial begin a = 3'b100; b = 3'b010; end452.1.2 注释符 Verilog HDL语言中允许插入注释,标明程序代码功能、修改、版本等信息,以增强程序的可阅读性和帮助管理文档。

Verilog HDL中有两种形式的注释。

(1) 单行注释:单行注释以“//”开始,Verilog HDL忽略从此处到行尾的内容。

(2) 多行注释:多行注释以“/*”开始,到“*/”结束,Verilog HDL忽略其中的注释内容。

需要注意的是,多行注释不允许嵌套,但是单行注释可以嵌套在多行注释中。

例2.1-2 注释符使用示例。

单行注释: assign a=b & c; //单行注释 多行注释: assign a[3:0]=b[3:0]&c[3:0;]; /*注释行1 注释行2 */ 非法多行注释:/*注释内容 /*多行注释嵌套多行注释*/ 注释内容*/ 合法多行注释:/*注释内容 //多行注释嵌套单行注释*/672.1.3 标识符和转义标识符 在Verilog HDL中,标识符(Identifier)被用来命名信号名、模块名、参数名等,它可以是任意一组字母、数字、$符号和_(下划线)符号的组合。

第四章 Verilog基本语法(一)PPT教学课件

14

2020/12/11

玉溪师范学院

字符串

➢ 字符串是双引号内的字符串列。 ➢ 一个字符可用八位二进制表示。如:

“INTEGER” 需要 8*7位。 例:reg [8*14:1] Message;

Message = “INTERNAL ERROR”;

15

2020/12/11

玉溪师范学院

课堂练习

下列表达式的位模式是什 么?写出其具体的二进制 表示值 7'o44, 'Bx0, 5'bx110, 'hA0, 10'd2, 'hzF

13

2020/12/11

玉溪师范学院

常量的位数

,x(或z)在十六进制值中代表4位x(或z),在八进制中代表3位x (或z),在二进制中代表1位x(或z)

当常量不说明位数时候默认是32位,每个字母用8位ASCII码来表示 10 =32’d10 =32’b1010 1=32’d1 =32’b1 -1 = -32’d1 =32’hFFFF_FFFF ‘BX=32’BX=32’BXXXXXXXXXX... “AB”=16’B 010000001_01000010 A的ASCII值是85,B的值是86

比如

16’b1010_1011_11111_000 //合法格式

8’b_0011_1011 //非法格式

Байду номын сангаас10

2020/12/11

玉溪师范学院

负数

一个数字可以被定义成负数,只要在位宽表达式前加一个减 号 - 8’d5 // 合法格式 8’d-5 //非法格式

11

2020/12/11

玉溪师范学院

简单的十进制格式

➢ 如: parameter Delay = 1;

数字电路与逻辑设计课件-Verilog语言总结

specparam、event

数字电路与逻辑设计2016

7

Verilog HDL语言基础

Verilog HDL数据类型和变量

例: wire a,b; wire [7:0] c; reg [7:0] buffer;

数字电路与逻辑设计2016

8

Verilog HDL语言基础

基础运算符

与(&&)、或(||)、非(!) 按位与(&)、按位或(|)、按位取反(~) 异或(^)、同或(^~ 或者 ~^) 移位运算符(<<、>>) 关系运算符(>、<、>=、<=) 等式运算符(==、!=、===、!==) 拼接运算符({})

为10进制

例 10

'o7 1'b1 8'Hc5 6'hF0 6'hF 6'hZ

未定长 10进制 未定长 8进制 1 bit 2进制 8 bits 16进制 6 bits 16进制 6 bits 16进制 6 bits 16进制

说明 0...01010 (32-bits)

0...00111 (32-bits) 1 11000101 110000 (高位被截断) 001111 (高位由0填充) ZZZZZZ (高位由Z填充)

Verilog HDL数据类型和变量

连线型(Net Type)

wire、tri

wor、wand、trior、triand、tri0、tri1、supply0、supply1、 trireg

寄存器型(Reg Type)

在时序部分出现

reg

integer、time、real

其他

parameter

数模混合信号电路设计第三讲verilog基本概念和仿真工具使用幻灯片

Ch.1概述10

V e功局r能部ilo定。g义 有:三根模种块本方中概法最念可重在要模的块局中部产是生逻华逻辑侨辑功大。能学I定C设义计中心

a, b, sel是输入端口,out是输 出端口。所有信号通过这些端 口从模块输入/输出。

另一个模块可以通过模块名及 端口说明使用多路器。实例化 多路器时不需要知道其实现细

wire out, a, b, sel; wire sel_, a1, b1; // The netlist

多路器由关键 词module和 endmodule 开始及结束。

Ch.1概述3

Verilog根本概念

模块 module( )

module是层 次化设计的基 本构件

逻辑描述放在 module内部

华侨大学IC设计中心

模块由关键词:module 模块名, endmodule构成

Ch.1概述4

Verilog 根本概念

华侨大学IC设计中心

模块的构造由在module和endmodule 关

如: reg [width-1 : 0]

Verilog w根ir本e [w概id念th-1 :

R变量1华,侨R大变学量IC2设…计;中心 0] W变量1,W变量

2 …;

Ch.1概述9

Verilog主要有两类数据类型华:侨大学IC设计中心

wire〔线网〕 :线网类型主要表示Verilog HDL 中构造化元件之间的物理连线,其数值由驱动 元件决定。如果没有驱动元件接到线网上,那 么其默认值为高阻z。Verilog程序模块中输入 输出信号类型缺省时自动定义为wire型

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Introduction to Verilog Course Objectivesn Learn the basic constructs of Verilogn Learn the modeling structure of Verilogn Learn the concept of delays and their effects in simulationCourse Outlinen Verilog Overviewn Basic Structure of a Verilog Model n Components of a Verilog Module –Ports–Data Types–Assigning Values and Numbers–Operators–Behavioral Modeling•Continuous Assignments•Procedural Blocks–Structural Modelingn Summary: Verilog Environment VerilogOverview What is Verilog?n IEEE industry standard Hardware Description Language(HDL) - used to describe a digital system n For both Simulation & SynthesisVerilog Historyn Introduced in 1984 by Gateway Design Automation n1989 Cadence purchased Gateway (Verilog-XL simulator)n1990 Cadence released Verilog to the publicn O pen V erilog I nternational (OVI) was formed to control the language specifications.n1993 OVI released version 2.0n1993 IEEE accepted OVI Verilog as a standard, Verilog 1364Verilog Structuren Verilog HDL : Consists of Keywords, syntax and semantics used to describe hardware functionalityand timing.n PLI : P rogramming L anguage I nterface provides C language routines used to interact between Verilog and EDA tools. (Simulators,Waveform displays) n SDF : S tandard D elay F ormat - a file used to back-annotate accurate timing information to simulatorsand other tools.Terminologyn HDL - Hardware Description Language is a software programming language that is used to model a piece of hardwaren Behavior Modeling - A component is described by its input/output responsen Structural Modeling - A component is described by interconnecting lower-level components/primitives Behavior Modelinginput 1, .., input n output 1, .., output nif (input 1)for (j=0, j<8, j=j+2)#5 output 1 = 1’b0;elsefor (j=1, j<8, j=j+2)#5 output 1 = 1’b1;n Only the functionality of the circuit, no structure n No specific hardware intentn For the purpose of synthesis, as well as simulationMore Terminologyn Register Transfer Level (RTL) - A type of behavioral modeling, for the purpose of synthesis.–Hardware is implied or inferred–Synthesizablen Synthesis - Translating HDL to a circuit and then optimizing the represented circuitn RTL Synthesis - The process of translating a RTL model of hardware into an optimized technologyspecific gate level implementationn Verilog–“Tell me how your circuit should behave and I will give you the hardware that does the job.”n VHDL–Similar to Verilogn ABEL, PALASM, AHDL–“Tell me what hardware you want and I will give it to you”n Verilog–“Give me a circuit whose output only changes when there isa low-to-high transition on a particular input. When thetransition happens, make the output equal to the input untilthe next transition.”–Result: Verilog Synthesis provides a positive edge-triggered flipflopn ABEL, PALASM, AHDL–“Give me a D-type flipflop.”–Result: ABEL, PALASM, AHDL synthesis provides a D-type flipflop. The sense of the clock depends on the synthesistool.VerilogModeling module Module_name (Port_list)Port declarations (if ports are present)Parameters (optional)Data type declarationsContinuous Assignments (assign)Procedural Blocks (initial and always)- behavioral statementsInstantiation of lower-level modulesTasks and FunctionsTiming SpecificationsendmoduleSchematic Representation - MACPortsn Port List:– A listing of the port names–Example:module mult_acc (out, ina, inb, clk, clr);n Port Types:–input--> input port–output--> output port–inout--> bidirectional portn Port Declarations:–<port_type><port_name>;–Example:input [7:0] ina, inb;input clk, clr;output [15:0] out;n wire--> represents a noden tri--> represents a tri-state noden Bus Declarations:–<data_type> [MSB : LSB ] <signal name> ;–<data_type> [LSB : MSB] <signal name> ;n Examples:–wire<signal name> ;–wire [15:0] mult_out, adder_out;n reg- unsigned variable of any bit sizen integer- signed variable (usually 32 bits)n Bus Declarations:–<data_type> [MSB : LSB ] <signal name> ;–<data_type> [LSB : MSB] <signal name> ;n Examples:–reg<signal name> ;–reg [7 : 0] out ;Data Typen Every signal (which includes ports) must have a data type–Signals must be explicitly declared in the data typedeclarations of your module–Ports are, by default, wire net data types if theyare not explicitly declaredAssigning Values - NumbersandOperatorsAssigning Values - Numbersn Are sized or unsized: <size>‘<base format><number>–Sized example: 3’b010 = 3-bit wide binary number•The prefix (3) indicates the size of number–Unsized example: 123 = 32-bit wide decimal number by default •Defaults–No specified <base format> defaults to decimal–No specified <size> defaults to 32-bit wide number n Base Format:–Decimal (‘d or ‘D) 16’d255 = 16-bit wide decimal number–Hexadecimal (‘h or ‘H) 8’h9a = 8-bit wide hexadecimal number–Binary (‘b or ‘B) ’b1010 = 32-bit wide binary numer–Octal (‘o or ‘O) ‘o21 = 32-bit wide octal numbern Negative numbers - specified by putting a minus sign before the <size>–Legal: -8’d3 = 8-bit negative number stored as 2’s complement of 3–Illegal: 4’d-2 = ERROR!!n Special Number Characters:–‘_’ (underscore): used for readability•Example: 32’h21_65_bc_fe = 32-bit hexadecimal number –‘x’ or ‘X’ (unknown value)•Example: 12’h12x = 12-bit hexadecimal number; LSBs unknown –‘z’ or ‘Z’ (high impedance value)•Example: 1’b z = 1-bit high impedance numbern Extended–If MSB is 0, x, or z, number is extended to fill MSBs with 0, x,or z, respectively•Examples: 3’b01 = 3’b001, 3’bx1 = 3’bxx1, 3’bz = 3’bzzz –If MSB is 1, number is extended to fill MSBs with 0•Example: 3’b1 = 3’b001Short Quizn Short Quiz:–Q: What is the actual value for 4’d017 in binary? Answersn Short Quiz:–Q: What is the actual value for 4’d017 in binary?–A: 4’b0001, MSB is truncated (10001)Operator Precedencen Operators default precedence+ , - , ! , ~ (unary)Highest Priority+ , - (Binary)<< , >>< , > , <= , >=== , !=&^ , ^~ or ~^|&&||?: (ternary)Lowest Priority n( ) can be used to override default。