数字电路实验 洗衣机程序设计

数电课程设计 洗衣机定时控制器

数字电子技术课程设计报告题目:洗衣机定时控制器班级:洗衣机定时控制器一、设计任务及要求:1.设计脉冲信号源(秒脉冲)2.至少能显示 1:00—12:593.具备校时功能4.附加特殊功能设计(报时功能)二、方案设计与论证:所谓数字钟,是指利用电子电路构成的计时器。

相对机械钟而言,数字钟能达到准确计时,并显示小时、分、秒,同时能对该钟进行调整。

在此基础上,还能够实现整点报时的功能。

其中有振荡器,分频器,校时电路,报时电路,计数器,译码器和显示器七部分组成。

振荡器和分频器组成标准秒信号发生器,不同进制的计数器产生计数,译码器和显示器进行显示,通过校时电路实现对时,分的校准方案一:使用 COMS 数字芯片,使用专用时钟芯片,使用十进制计数器,以及使用万用板焊接电路,分模块搭建电路,使用专用电源供电。

优点:计时准确,反应灵敏,思路简单,性能稳定,成功率高,便于调试。

缺点:驱动能力弱,走线复杂,对数电知识的利用并不充分。

方案二:使用 TTL 数字芯片,使用 74LS93 多进制计数器,用 555 定时器自建时钟模块,使用 USB 供电,使用 PCB 制板。

优点:电路驱动能力强,不必考虑输入脚悬空的问题,充分利用了模电、数电的知识,外观漂亮,供电方便。

缺点:整体布局比较麻烦,排查错误比较麻烦,时钟性能一般。

在比较两个方案的优缺点后,选择了第二个方案,进行由上而下层次化的设计,先定义和规定各个模块的结构,再对模块内部进行详细设计。

通过仿真,原理图设计,PCB 制作,分步骤调试,来解决方案二的不足。

使做出来的效果又好,又能充分利用学过的数电知识。

可以体现数电课设的真正内涵。

我们设计的电子钟,严格按照设计要求,具有整点报时,调时,调分等功能;特别是,我们的调时调分开关,都加上了消抖电路,使用了模拟电路消抖,省去了一些数字芯片,这些都是我们组,区别于其他组的地方。

设计原理及框图定时控制器实际上是一个对标准频率进行计数的计数电路,由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的 1kHZ 时间信号必须做到准确稳定。

洗衣机VHDL控制器实验报告

数字电路和逻辑设计综合实验实验报告实验名称:洗衣机控制器班级:班内序号:姓名:学号:数电设计综合实验—洗衣机控制器一.设计课题的任务要求设计制作一个全自动洗衣机的控制器:●洗衣机的工作步骤为洗衣、漂洗和脱水三个过程,工作时间分别为:洗衣20秒,漂洗30 秒,脱水15 秒;●用一个按键实现洗衣程序的手动选择:A、单洗涤;B、单漂洗;C、单脱水;D、漂洗和脱水;E、洗涤、漂洗和脱水全过程;●用显示器件显示洗衣机的工作状态(洗衣、漂洗和脱水),并倒计时显示每个状态的工作时间,全部过程结束后,应提示使用者;●用一个按键实现暂停洗衣和继续洗衣的控制,暂停后继续洗衣应回到暂停之前保留的状态;●选做:三个过程的时间有多个选项供使用者选择。

●选做:可以预约洗衣时间。

●选做:自拟其它功能。

二.系统设计(包括设计思路、总体框图、分块设计)◆设计思路首先从题目进行分析,采用VHDL模块化的设计方法来进行洗衣机控制器的设计,即自顶向下,从系统总体要求出发,自上至下地将设计任务分解为不同的功能模块.最后将各功能模块连接形成顶层模块,完成系统硬件的整体设计。

本控制器基本功能描述洗衣机控制器可工作于五种模式下:单洗涤、单漂洗、单脱水、漂洗十脱水、洗涤十漂洗+脱水,可以使洗衣机控制器工作在任意一种模式,并显示出洗衣机的工作状态和剩余工作时间,在剩余时间结束后有报警声提示使用者,并且可实现暂停洗衣和继续的功能,此外,加入附加功能,可自选三个过程是使用时间并且可预约洗衣时间。

由此分析可将洗衣机控制器分为控制模块、倒计时模块,初始模式选择模块,报警模块,洗衣时间选择模块,选通译码模块和分频器模块。

【设计过程】:1)审题,初步确定思路。

2)用VHDL语言进行编程。

3)适时对程序进行修改。

4)编译成功后,进行仿真,观察波形图。

5)将程序下载到实验板上,调试各功能。

6)通过计算机仿真和下载调试,发现问题,返回原程序进行修改。

7)进行总体的调试。

全自动洗衣机程序设计

全自动洗衣机程序设计第一部分总体思路全自动洗衣机的工作原理:开始-进水-洗衣-排水-脱水-结束第二部分电气设计部分如下图为全自动洗衣机的PLC控制系统电路图。

通过PLC来实现电动机的正反转,并且实现洗衣机按预先设置的程序自动执行,完成洗衣。

当需要手动排水与脱水时,可强制止自动程序的运行,跳出自动切换到手动操作。

为防止全自动洗衣机在工作过程中,电路发生短路,损坏电动机和电路中的各种电气设备,因此在主电路中安装了熔断器,当电路出现短路故障时,能迅速、可靠的断开电源。

全自动洗衣机在无人问津的情况下可能长时间运行,为防止电机绕组的温升超过额定值而损坏,采用热继电器作为保护元件,与熔断器搭配使用,可靠地保护电动机。

人机接口部分的按钮等都选择低压电器元件,保护操作者的安全。

第三部分PLC设计部分3.1正常运行流程图如下图所示。

3 2强制运行流程图如下1)程序的构成这个程序有自动方式和手动方式两种。

在自动方式下,PLC将运行已经设置好的程序和参数(适用于机械一切都正常工作的情况下)。

在手动方式下是在紧急停止情况下,可以手动排水和脱水。

2)程序的下载、安装和调试将各个输入输出端子和实际控制系统中的按钮。

所需控制设备正确连接,完成硬件的安装。

全自动洗衣机程序是由GX Developer软件的指令完成,正常工作是程序存放在存储卡中,若要修改程序,先将PLC设定在STOP状态下,运行GX Developer编程软件,打开全自动洗衣机程序,即可在线调试,也可用编程器进行调试。

第四部分全自动洗衣机控制系统PLC程序4.2.1系统资源分配1.数字量输入部分这个控制系统的输入有启动按钮、停止按钮、水位选择开关(高水位、中水位、低水位)、手动排水、自动排水开关、高水位浮球开关、中水位浮球开关,低水位浮球开关、水排空浮球开关、压力开关共12个。

具体的输入地址分配如表4.1所示。

表4.1 输入地址分配输入地址对应的元器件对应的外部设备X001 SB1 启动按钮X002 SB2 停止按钮X003 SB3 高水位选择开关X004 SB4 中水位选择开关X005 SB5 低水位选择开关X006 SQ1 水排空检测开关X007 SQ2 高水位检测开关X010 SQ3 中水位检测开关X011 SQ4 低水位检测开关X012 SB6 手动排水X013 SB7 手动脱水X014 SP1 压力开关2.数字量输出部分这个控制系统需要控制的外部设备有进水电磁阀、排水电磁阀、洗涤电动机、脱水桶、报警器共五个设备。

数字设计 时序逻辑电路 自动洗衣机控制器课程设计

电子科技大学

数字电路

课程设计报告

姓名:张华博

学号:2011091010004

选课号:132

指导老师:张刚

时序逻辑电路课程设计

——————自动洗衣机控制器

设计要求:假设自动洗衣机的定时操作顺序是,洗衣10min,排水2min,脱水3min,然后停止。

分析:自动洗衣机开机后,系统开始运行,首先进入初始状态,当系统收到有效指令信号后开始自动循环,进入洗衣状态,10分钟之后,进入排水状态,经2分钟,进入脱水状态3分钟,再次进入初始状态;期间任何时刻输入有效复位信号,系统将重新开始自动循环状态;系统处于每一个工作状态时,均有一个LED 灯管与其对应,处于发光状态。

由上分析知:该系统的主体应为10分、2分、3分计时器,当一个计时器计时结束后,输出一个使能信号作用于下一个计时器,激发其开始计时。

开始的指令信号作用于第一个计时器的一个使能端,以激发整个循环系统开始工作;当输入有效复位信号时,计时器全部清空置零,并重新开始循环。

逻辑电路图如下:

十分钟计时器逻辑电路

两分钟计时器逻辑电路

三分钟计时器逻辑电路

自动洗衣机系统逻辑电路

逻辑电路仿真:

输入2Hz的时钟信号CLK,ENT为指令信号,CLRN为复位信号,Z1、Z2、Z3、Z4分别对应于洗衣状态、排水状态、脱水状态、初始状态。

波形仿真效果

仿真结果显示该电路设计正确,该系统基本可实现预期的操作功能。

总结感想无需赘言,见组合逻辑课程设计报告……。

数电模拟洗衣机控制设计正转反转停机实现计秒计分功能

要实现数电模拟洗衣机控制,包括正转、反转和停机功能,并且添加计秒和计分功能,可以考虑使用数字逻辑电路和计时器集成电路来完成。

控制设计步骤:1. 逻辑控制电路设计:使用数字逻辑电路设计控制正转、反转和停机的逻辑控制功能。

这可以通过使用触发器、逻辑门等元件组合设计而成。

2. 计时器集成电路应用:使用集成的计时器电路,比如555定时器、计数器等,来实现计秒和计分功能。

这些电路可以用于测量时间并触发相应的控制信号。

3. 状态机设计:设计一个状态机来管理洗衣机的工作状态,根据当前状态和传感器输入确定下一个状态,并触发相应的控制信号。

4. 显示和输出控制:使用数码显示器或LED灯来显示剩余时间(秒和分),以及洗衣机当前的工作状态。

5. 传感器输入:添加传感器来检测洗衣机的转动状态、水位和其他参数,并将这些输入信息送入控制系统中。

6. 安全保护功能:考虑添加安全保护功能,如过载保护、温度监控等,确保洗衣机的安全运行。

需要的器件和模块:-触发器、逻辑门芯片:用于控制正转、反转和停机功能的逻辑控制。

- 555定时器、计数器芯片:用于实现计时功能。

-数码显示器或LED灯:显示剩余时间和工作状态。

-传感器**:用于检测洗衣机的实时状态。

总体设计流程:1. 根据洗衣机的功能需求,设计逻辑控制电路,实现正转、反转和停机功能。

2. 使用计时器电路,设计计时和计分功能。

3. 结合逻辑控制和计时功能,设计状态机和控制逻辑,实现洗衣机的自动控制。

4. 添加显示和输出模块,显示剩余时间和工作状态。

5. 考虑安全保护和故障检测功能,确保洗衣机的稳定运行。

以上是基于数字逻辑电路和计时器集成电路的洗衣机控制设计方案,具体的实施需要根据实际需求和具体的电路设计进行调整和优化。

8086%2B综合实验%2B洗衣机程序设计

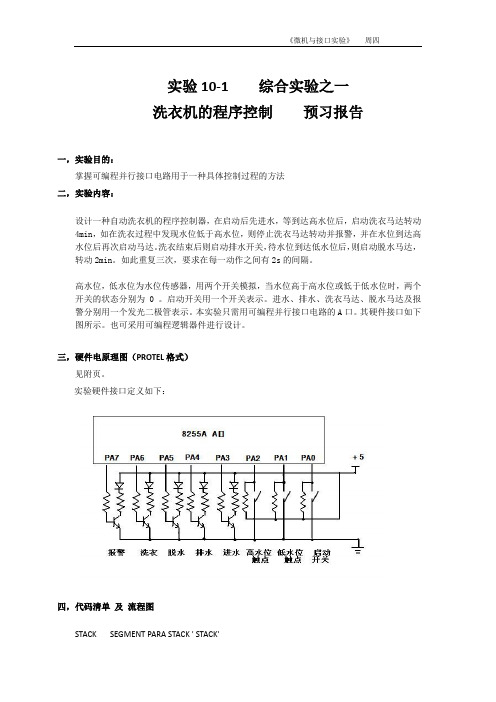

实验10-1 综合实验之一洗衣机的程序控制预习报告一,实验目的:掌握可编程并行接口电路用于一种具体控制过程的方法二,实验内容:设计一种自动洗衣机的程序控制器,在启动后先进水,等到达高水位后,启动洗衣马达转动4min,如在洗衣过程中发现水位低于高水位,则停止洗衣马达转动并报警,并在水位到达高水位后再次启动马达。

洗衣结束后则启动排水开关,待水位到达低水位后,则启动脱水马达,转动2min。

如此重复三次,要求在每一动作之间有2s的间隔。

高水位,低水位为水位传感器,用两个开关模拟,当水位高于高水位或低于低水位时,两个开关的状态分别为0 。

启动开关用一个开关表示。

进水、排水、洗衣马达、脱水马达及报警分别用一个发光二极管表示。

本实验只需用可编程并行接口电路的A口。

其硬件接口如下图所示。

也可采用可编程逻辑器件进行设计。

三,硬件电原理图(PROTEL格式)见附页。

实验硬件接口定义如下:四,代码清单及流程图STACK SEGMENT PARA STACK ' STACK'DB 256 DUP(0)STACK ENDSDATA SEGMENT PARA PUBLIC 'DATA'DATA ENDSCODE SEGMENT PARA PUBLIC 'CODE'ASSUME CS:CODESTART: MOV AX,DATAMOV DS,AXMOV DX,2C3HMOV AL,82H ;A口输出,B口输入OUT DX,AL ;写8255方式字CALL DELAYRES: MOV DX,2C0HMOV AL,00H ;设置LED灯全亮OUT DX,ALCALL DELAYMOV AL,0FFH ;设置LED灯全灭OUT DX,ALCALL DELAYL0: MOV DX,2C1HIN AL,DXTEST AL,01H ;检测是否启动JZ L0 ;为0则继续查询CALL DELAYMOV DX,2C0HMOV AL,11110111B ;进水灯OUT DX,ALL1: MOV DX,2C1HIN AL,DXTEST AL,01H ;检测是否重启JZ RESTEST AL,04H ;高水位?JZ L1 ;若0则继续查询MOV DX,2C0HMOV AL,10111111B ;洗衣灯OUT DX,ALL2: CALL DELAYDEC CXJZ FULLCALL DISPLAYMOV DX,2C1HIN AL,DXTEST AL,01H ;重启?JZ RESTEST AL,08HJNZ FULLTEST AL,02H ;低水位JZ L2 ;为0则继续查询MOV DX,2C0HMOV AL,01111111B ;报警灯OUT DX,ALL3: MOV DX,2C1HIN AL,DXTEST AL,01H ;重启?JZ RESTEST AL,02H ;低水位结束?JNZ L3 ;为1则继续查询JMP L2FULL: MOV DX,2C0HMOV AL,11101111B ;排水灯OUT DX,ALCALL DELAYL4: MOV DX,2C1HIN AL,DXTEST AL,01H ;重启?JZ RESTEST AL,02H ;低水位?JZ L4 ;为0则继续查询MOV DX,2C0HMOV AL,11011111B ;脱水灯OUT DX,ALCALL DELAYL5: CALL DELAYDEC CXJZ L0CALL DISPLAYMOV DX,2C1HIN AL,DXTEST AL,01H ;重启?JZ RESTEST AL,08HJNZ L0JMP L5STOP: MOV AH,4CHINT 21HDELAY PROC NEAR ;延时子程序PUSH BXPUSH CXMOV BX,0200HD2: MOV CX,0FFFHD1: MOV AH,01H ;检测键盘输入INT 16HJNZ STOP ;任意键退出,否则循环DEC CXJNZ D1DEC BXJNZ D2POP CXPOP BXRETDELAY ENDPDISPLAY PROC NEAR ;显示CX为入口PUSH DXPUSH CXPUSH AXMOV DL,0HC3: CMP CX,03E8H ;千位JNAE C4INC DLSUB CX,03E8HJMP C3C4: OR DL,30H ;ASCII转换MOV AH,02H ;显示INT 21HMOV DL,0HC5: CMP CX,64H ;百位JNAE C6INC DLSUB CX,64HJMP C5C6: OR DL,30HMOV AH,02HINT 21HMOV DL,0HC7: CMP CX,0AH ;十位JNAE C8INC DLSUB CX,0AHJMP C7C8: OR DL,30HMOV AH,02HINT 21HMOV DL,CLOR DL,30HMOV AH,02H ;个位INT 21HMOV DL,20HINT 21HPOP AXPOP CXPOP DXRETDISPLAY ENDPCODE ENDSEND START程序流程图:五,程序运行说明本程序系自主设计流程图,自主研发程序,对题目要求稍加改动,改动及添加如下:1,为记忆方便,将所有开关定义为‘1’有效,‘0’无效,方便实验时的操作2,实验中的4min和2min在验收时等待太久,故添加了一个加速按键,跳过剩余时间,对实验的实际效果没有影响3,在洗衣4min和脱水2min的过程中,由于时间较长,如果没有任何标记无法判断程序是否正常进行,故在上述过程中添加倒计时,程序运行时在屏幕上显示,这样便可指示程序此时的准确状态4,如果程序运行顺利,拟用步进电机模拟洗衣电机和脱水电机,虽然没有太大的实际意义,权当了解步进电机的工作方式,增加自己的实验器材熟悉程度了程序操作说明:1,上机检测LED点亮条件,程序设计为0点亮,检查硬件,如有错误则更改程序。

数字电子技术课程设计--简易洗衣机控制器设计

课程设计任务书题目: 简易洗衣机控制器设计初始条件:利用定时器、数码管、LED等数字电路器件设计实现简易洗衣机功能。

(也可以使用单片机系统设计)要求完成的主要任务:(包括课程设计工作量及技术要求,以及说明书撰写等具体要求)1 课程设计工作量:1周内完成对简易洗衣机控制电路的设计、仿真与调试。

2技术要求:洗衣机电机的工作顺序:启动——>正转20s——>暂停10s——>反转20s——>暂停10s——>停止①设计一个定时器控制洗衣机电机的运转,②三只LED灯表示“正转”、“反转”和“暂停”3个状态。

③用数码管显示洗涤时间,按倒计时方式对洗涤过程作计时显示,直到时间到停机,并发出音响信号报警。

④设置停止键,在洗涤过程中随时按该键可终止动作,并使显示器清0。

3 查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:第17周(7、8节):理论讲解第18周:理论设计及实验室安装调试;地点:鉴主15通信工程实验室(1),鉴主13通信工程专业实验室;第19周:撰写设计报告及答辩;地点:鉴主17楼研究室。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录1 绪论 (3)2设计任务要求及总体思路 (3)3设计基本原理 (4)4设计方案 (4)5单元电路的设计和元件的选择 (6)5.1秒脉冲发生器 (6)5.2分秒计数器 (8)5.3时间译码及控制门 (11)5.4总电路图 (12)6仿真结果 (13)6.1秒脉冲发生器 (13)6.2分秒计数器 (13)6.2.1正转 (14)6.2.2暂停 (15)6.2.3反转 (16)6.2.4定时时间到 (17)7仿真结果分析 (18)8体会 (18)9元器件清单 (19)10 参考文献 (20)摘要现代生活人民生活水平越来越高,家家户户几乎都有一台洗衣机。

洗衣机由于洗涤方便受到广大用户的喜爱。

数字逻辑电路课程设计-全自动洗衣机控制器的设计课案

数字逻辑电路课程设计设计题目全自动洗衣机控制器的设计姓名学号专业班级完成日期目录一、实验目的 (3)二、设计题目与思路 (3)三、总体方案的设计与选择 (4)四、使用元件 (5)五、分析与心得 (5)六、附件一:实验代码 (5)一、实验目的1.进一步掌握数字电路课程所学的理论知识。

2.了解数字电路设计的基本思想和方法,学会科学分析和解决问题。

3.熟悉几种常用集成数字芯片,并掌握其工作原理,进一步学会使用其进行电路设计。

4. 培养认真严谨的工作作风和实事求是的工作态度。

二、设计题目与思路本次数字电路课程设计我选择的题目是“全自动洗衣机控制器”。

这个系统的主要功能是:1.设计一个全自动洗衣机控制器电路,实现对洗衣机的全自动控制。

根据全自动洗衣机的控制原理设计一个控制电路,使之能够控制全自动洗衣机完成整个工作过程。

洗衣机工作过程如下:当按下复位按钮时,洗衣机上电,控制电路复位到初始状态(默认水位为“中”);使用者可根据衣服的多少,按下水位控制按钮,改变水位设置,以控制上水时加水的多少;当按下启动/暂停按钮时,洗衣机开始洗衣的第一个操作:进水阀门打开,开始上水,并根据水位设置(高、中、低、少)历时不同的时间timeadd(8s、7s、6s、5s);然后进水阀门关闭,电机开始运转,开始洗衣过程,并历时9s;然后电机停止运转,排水阀门打开,开始排水,并根据水位设置(高、中、低、少)历时不同的时间timedrain(7s、6s、5s、4s);然后排水阀门关闭,进水阀门打开,开始第二次上水,并历时timeadd……当甩干结束后,整个洗衣过程完成,扬声器发出持续15秒的急促的“嘀嘀”音,提示用户洗衣结束。

洗衣机工作过程简记如下:空闲(idle)→第一次加水(water1)7s→洗衣(wash)9s→第一次排水(drain1)6s→第二次加水(water2)7s→漂洗(rinse)9s→第二次排水(drain2)6s→甩干(dry)5s→蜂鸣15s2、控制器只要送出对应的控制信号就可以了。

数电课程设计报告--洗衣机自动控制电路

洗衣机自动控制电路一、设计要求1.洗衣时间设定范围:1—99分钟(预设为30min)2.显示漂洗时间(显示分钟就好),时间到后会自动报警3.漂洗时(用发光二极管代替电动机)显示正转、反转、暂停4.定时时间内电机工作要求如下:启动正转20s 暂行10s 反转20s 暂行停止定时未到二、设计方案由于受现有知识的限制,我们不能使用单片机以及编写程序的方法来实现。

只能采用CMOS和TTL集成器件等中小型集成块,如计数器,锁存器,与非门,555定时器等构成洗衣机控制电路。

洗衣机的洗衣流程如框图:三、具体电路设计及工作原理说明1、多谐振荡器多谐振荡器是一种自激振荡器,产生振荡信号,用于计时。

在许多场合对多谐振荡器的频率稳定性要求严格,一般采用石英晶体振荡器。

但是由于洗衣机对时间的精确度要求不是很高,所以我们采用555定时器接成的500HZ多谐振荡器。

电路如图:图中是把555定时器接成施密特触发器,在用施密特触发器接成多谐振荡器的方法接成。

其中R7=100Ω,R8=200Ω,C3=5.77μF ,C4=1μF(滤波电容)把数据带入T=(R1+2R2)C2ln2 ,得T约为0.002s。

即周期为0.002秒,输出500HZ 的信号。

4号管脚即为脉冲信号输出管脚。

2、时钟电路及74LS192D功能表时钟电路采用计数器对输入的500HZ振荡信号进行计数,从而实现计时。

用十进制计数器接成两个60进制计数器,分别用于计秒和计分。

分和秒的计数图如下:加减计数器74LS192D(四个)、数码显示管等74LS192的功能表3、电机正转、反转、暂停的表示把秒十位上的数作为正反转控制系统的输入信号,把秒十位上输出的二进制数经74LS138 译码器译码成8个输出,然后再各取两位输出经由译码器、与非门、取反器作用到相应的3个指示灯(U15号灯亮表示正转,U13号亮表示反转,U14灯亮表示停止)。

4、分显示电路原理两个代表分的个位和十位的192的输出端接到74LS138D(3-8译码器)的对应输入端,然后经过74LS04D和74LS00D的处理,LED灯从左到右依次为正传、暂停、翻转。

洗衣机数字电路控制设计.doc

目录1、设计任务与要求12、基本原理13、设计方案24、单元电路的设计和元件的选择34.1秒脉冲发生器34.260秒计数器和分钟定时计数器联合电路.5 4.3输出信号控制器74.4总电路图.85仿真结果.95.1秒脉冲发生器95.2分秒计数器95.2.1正转105.2.2暂停.115.2.3反转125.2.4定时时间到.136仿真结果分析147体会158元器件清单.169参考文献161、设计任务与要求设计一个电子定时器,控制洗衣机按如图1洗涤模式进行工作启动—>正转20s —> 暂行10s—> 反转20s— >暂行10 s—>停止并报警^ ^| ________________________________ | 定时到定时未到图1 洗涤模式(1)当按下启动,洗衣机开始转动,同时对分钟进行置数,并进行正转、暂停、反转。

(2)用两位数码管显示洗涤的预置时间(以分钟为单位),按倒计时方式对洗涤过程作计时显示,直到时间变为00,洗衣机停止转动。

(3)两只LED灯表示“正转”、“反转”和“暂停”,L1L2=11为正转,01为暂行,10为反转,00为停止。

2、基本原理经过任务书要求我们可以分析出,首先秒脉冲是必需的,然后要实现60秒钟的循环,和分钟计数,那么可以选用192这一十进制加/减计数器,要实现LED等显示状态的变化,我们可以选用151数据选择器来实现LED灯在特定时间显示不同的高低电平,而且要停止并报警,这需要设计一个报警器控制电路电路。

机器启动后利用秒脉冲发生器发出秒脉冲,利用两片192实现60秒钟的倒数循环,再利用秒钟的两个192,带动另外两片192进行倒计数,来实现预置分钟数的递减。

与此同时60秒计时器十位数字大小通过一片151进行数据选择输出,控制洗衣机电机灯的亮灭,使得洗衣机两个LED灯在一个60秒循环中前20秒亮11,再亮01秒10,再亮20秒10,再回到01。

PLC全自动洗衣机程序设计

PLC全自动洗衣机程序设计PLC全自动洗衣机程序设计1. 引言PLC(可编程逻辑控制器)是一种常用于自动化控制系统中的工控设备,广泛应用于各行各业。

本文将介绍如何进行PLC全自动洗衣机的程序设计,以实现洗衣机的自动化运行。

基于PLC的洗衣机程序设计可以提高生产效率、节约资源,也能够提升洗衣机的智能化水平。

2. PLC全自动洗衣机的工作原理PLC全自动洗衣机的工作原理包括以下几个步骤:- 步骤1:用户选择洗衣模式和洗衣时间等参数。

- 步骤2:用户放入衣物,并关闭洗衣机的门。

- 步骤3:PLC根据用户选择的参数,控制洗衣机的加热、水位、转速等。

- 步骤4:洗衣机开始工作,根据设定的程序依次进行水洗、漂洗、脱水等操作。

- 步骤5:洗衣机完成工作,发出提示音,等待用户取出洗好的衣物。

3. PLC全自动洗衣机程序设计流程根据洗衣机的工作原理,我们可以设计出以下的PLC全自动洗衣机程序:3.1 程序初始化程序初始化主要包括以下内容:- PLC系统与洗衣机的连接和通信检测。

- 初始化各个传感器,如温度传感器、水位传感器等。

- 检测洗衣机的状态,确保门已关闭,并将状态设置为“待机”。

3.2 用户输入参数用户通过操作洗衣机的控制面板,输入洗衣模式、洗衣时间等参数。

PLC需要读取这些参数,并进行验证和显示。

3.3 洗衣机工作控制根据用户输入的参数,PLC需要控制洗衣机的各个组件进行相应的工作控制,包括:- 控制加热器的启停,根据用户选择的洗衣模式和温度要求来调节加热器的工作状态。

- 控制水泵的启停,根据用户选择的洗衣模式和水位要求来调节水泵的工作状态。

- 控制电机的转速,根据用户选择的洗衣模式和转速要求来调节电机的转速。

- 监测洗衣机的状态,如水位、温度、转速等,确保工作在正常范围内。

3.4 工作结束处理当洗衣机完成工作后,PLC需要进行相应的处理,包括:- 发出提示音,提醒用户取出洗好的衣物。

- 将洗衣机的状态设置为“待机”,等待下一次操作。

数电实验 洗衣机

数电实验报告——简易全自动洗衣机控制器03111班09号迟帅简易全自动洗衣机控制器实验报告摘要:我们制作的系统可以模拟全自动洗衣机控制器。

分为4个按键,分别为模式选择、暂停、开始和复位。

有五个指示灯来显示当前工作模式,分别为单洗涤、单漂洗、单脱水、漂洗和脱水以及洗涤漂洗脱水。

有三个指示灯显示当前工作状态,红灯是正在工作中,黄灯是暂停中,绿灯是停止中。

通过数码管显示当前操作的剩余时间,当操作完成时蜂鸣器会报警提示完成。

通过两个指示灯显示剩余操作数。

Abstract:We made a system that control washing machine. It has 4 buttons: mode choosing, pause, start, reset. We use 5 green lights to show working mode and it has 5 modes. It has one red light to show it is working, one yellow light to show it is pausing and one green light to show it is stopping. The system can show leaving-time and give an alarm when it has finished. It shows how many acts left by two light.设计任务要求:制作一个简易全自动洗衣机控制器:1、洗衣机的动作有洗涤、漂洗和脱水,每个动作持续的时间分别为20秒、15秒和10秒;2、用一个按键实现洗衣程序的手动选择:A、单洗涤B、单漂洗C、单脱水D、漂洗和脱水E、洗涤、漂洗和脱水全过程3、无论选择何种洗衣服的程序,在所选择的程序完成之后,控制器应处于暂停状态;4、用一个按键实现暂停洗衣和继续洗衣的控制,暂停后继续洗衣应回到暂停之前的状态;5、用发光二极管指示当前状态;6、用数码管以倒计时的方式显示当前状态的剩余时间。

数字逻辑电路课程设计-全自动洗衣机控制器的设计课案

数字逻辑电路课程设计设计题目全自动洗衣机控制器的设计姓名学号专业班级完成日期目录一、实验目的 (3)二、设计题目与思路 (3)三、总体方案的设计与选择 (4)四、使用元件 (5)五、分析与心得 (5)六、附件一:实验代码 (5)一、实验目的1.进一步掌握数字电路课程所学的理论知识。

2.了解数字电路设计的基本思想和方法,学会科学分析和解决问题。

3.熟悉几种常用集成数字芯片,并掌握其工作原理,进一步学会使用其进行电路设计。

4. 培养认真严谨的工作作风和实事求是的工作态度。

二、设计题目与思路本次数字电路课程设计我选择的题目是“全自动洗衣机控制器”。

这个系统的主要功能是:1.设计一个全自动洗衣机控制器电路,实现对洗衣机的全自动控制。

根据全自动洗衣机的控制原理设计一个控制电路,使之能够控制全自动洗衣机完成整个工作过程。

洗衣机工作过程如下:当按下复位按钮时,洗衣机上电,控制电路复位到初始状态(默认水位为“中”);使用者可根据衣服的多少,按下水位控制按钮,改变水位设置,以控制上水时加水的多少;当按下启动/暂停按钮时,洗衣机开始洗衣的第一个操作:进水阀门打开,开始上水,并根据水位设置(高、中、低、少)历时不同的时间timeadd(8s、7s、6s、5s);然后进水阀门关闭,电机开始运转,开始洗衣过程,并历时9s;然后电机停止运转,排水阀门打开,开始排水,并根据水位设置(高、中、低、少)历时不同的时间timedrain(7s、6s、5s、4s);然后排水阀门关闭,进水阀门打开,开始第二次上水,并历时timeadd……当甩干结束后,整个洗衣过程完成,扬声器发出持续15秒的急促的“嘀嘀”音,提示用户洗衣结束。

洗衣机工作过程简记如下:空闲(idle)→第一次加水(water1)7s→洗衣(wash)9s→第一次排水(drain1)6s→第二次加水(water2)7s→漂洗(rinse)9s→第二次排水(drain2)6s→甩干(dry)5s→蜂鸣15s2、控制器只要送出对应的控制信号就可以了。

洗衣机自动控制电路 数字逻辑课程设计

《数字逻辑》课程设计报告题目:洗衣机自动控制电路目录1 设计任务书2 总体方案设计2.1 功能和逻辑需求分析2.2 总体方案设计3 单元模块设计3.1分倒数单元电路设计3.2 秒倒数单元电路设计3.4 计数器单元电路设计3.2 状态译码器单元电路设计3.5总体电路设计(画出总体电路图)4 电路调试与测试4.1分倒数单元模块4.2秒倒数单元模块4.3计数器单元模块4.4状态译码器单元模块4.5全部器件5 总结1 设计任务书洗衣机自动控制电路为洗衣机设计一控制电路,当洗衣机控制开关打开后,电动机先正转20S,然后暂停10S,随后反转20S,再然后暂停10S;如果定时时间没到,则开始循环,若定时时间到,则停机断电。

定时时间设定范围为0~60分,显示分秒的倒计时。

用LED指示灯表示电机的正转、反转和暂停状态。

2 总体方案设计(1)、计时器:由两片芯片来分别完成分、秒的倒计时功能,分芯片提供预置功能,两片芯片的模均为60.(2)、计数器:通过计数来完成输出洗衣机四种状态(正转 > 暂停 > 反转 > 暂停 > 正转)的切换(3)、状态译码器:将输入的四种状态转换为三种状态(正转、暂停、反转)(4)、所有芯片都使用每秒一脉冲的统一脉冲,实现同步。

2.1 功能和逻辑需求分析1)、计时器:①由于平常用的基础器件无法简单做到倒数功能,所以决定用GAL器件,通过编写ABEL-HEL并在GAL器件上实现。

②计数器的分和秒分别需要8位输出(4位作为十位,另外4位作为个位,每4位二进制数在数码管上显示为一个十进制的数。

)③所以计数器的分和秒必须分为两个GAL器件,但同时秒需要有一个退位输出信号,分需要一个抑制秒继续倒数的输出信号,所以每个芯片需要9个输出端。

④总结:计数器需要两个GAL22v10分别实现分和秒的倒数。

2)、按周期显示正、反灯和暂停灯:①该功能仍然需要GAL器件来实现,首先需要内部能自己计数,电动机先正转20S,然后暂停10S,随后反转20S,再然后暂停10S,按20+10+20+10=60秒为一周期,所以需要6个输出来计数(作为内部计数,可以不必显示)。

FGPD洗衣机控制电路_数电实验

2010—2011学年第二学期《数字电子技术课程设计》报告课题:简易洗衣机控制电路专业班级:姓名:学号:设计日期:目录一、设计任务及要求-------------------------------------------------------------------------------2(一)具体要求--------------------------------------------------------------------------------2 (二)输入输出资源说明--------------------------------------------------------------------2二、设计原理与方案--------------------------------------------------------------------------------4(一)顶层设计方案---------------------------------------------------------------------------4 (二)分频器设计方案------------------------------------------------------------------------5 (三)计时器(倒计时)设计方案---------------------------------------------------------5 (四)显示器设计方案------------------------------------------------------------------------5 (五)暂停设计方案---------------------------------------------------------------------------5三、电路设计、仿真与实现-----------------------------------------------------------------------6(一)顶层的设计实现------------------------------------------------------------------------6(二)分频器的设计实现---------------------------------------------------------------------8 (三)计数器(倒计时)的设计实现-----------------------------------------------------10 (四)显示器设计实现-----------------------------------------------------------------------15 (五)暂停设计实现--------------------------------------------------------------------------17 (六)Fit Design 结果------------------------------------------------------------------------18四、分析与讨论-------------------------------------------------------------------------------------18一、设计任务及要求:洗衣机是家庭常用电器,一般可以有多种工作模式可供选择。

数字电路课程设计洗衣机

总体方案分析及选择:洗衣机电路包含有总的控制模块,洗涤控制模块,洗涤记时模块,电动机控制模块以及LCD 液晶板的动态显示模块.经过分析后,我们把前四个模块进行组合,把他们合成一个模块即:总控制模块.他们之间的逻辑联结关系,是对数电课程的一个很好总结,也是自己对新知识(LCD 液晶板的动态显示)学习理解运用能力的一个很好的提升机会。

基本功能要求:1要求设计制作一个普通功能洗衣机控制电路,使之能控制洗衣机的进水阀,排水阀,洗涤程序电机,甩干驱动装置等按预定程序工作.总体过程包括:进水浸泡洗涤排水甩干五个过程.进水从电路启动开始.其中浸泡可供选择,洗涤时间可以预置,洗涤结束时发出铃声进行提示并自动切断电源.发生故障如:缺水或进水超时排水超时甩干碰桶等时也可自动切断电源!2用中小规模集成电路芯片或CPLD/FPGA设计符合上述任务要求的电路,并制作出能实际运行的装置.3安装并调试电路,测试各部分电路功能或模型.4演示并交验硬件装置.下载实现图:局部功能模块总控模块:该模块实现了对洗衣机整个运行过程的控制,打开电源后由模块内部进行控制,按洗涤过程工致洗衣机的运转.同时在输入端还给了报警输入,当发生故障时洗衣机自动短电.复位端可以让洗衣机进入初始状态.在输入端还有10个总线输入可以人为进行置数,从而控制各个过程的时间长短.当给甩干时间一个时间,其他都置为0可以让洗衣机只进行甩干操作.VHDL文件:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity xiyiji isport(clk0, clk1, rst, alarm: in std_logic;-----clk0:控制开关脉冲.clk1:记时开关脉冲.Rst:复位端.alarm:报警输入端.------- water_inh, water_inl, im_th, im_tl, wash_th: in std_logic_vector(3 downto0);wash_tl, water_outh, water_outl, dry_th, dry_tl: in std_logic_vector(3 downto 0); -----进水,浸泡,洗涤,出水,甩干置数端高位和低位输入端-----------water_in, water_out, immersion, dry, z1, z2, voice, poweroff: out std_logic; -----进水,出水,浸泡,甩干,洗涤,响铃,断电输出端-------display_th, display_tl: out std_logic_vector(3 downto 0)-------------------输出时间显示高位低位输出端-------------);end entity xiyiji;architecture behave of xiyiji issignal js, js_ten : std_logic;signal im, im_ten : std_logic;signal wa, wa_ten : std_logic;signal wa1, wa2, pwf: std_logic;signal cs, cs_ten : std_logic;signal dr, dr_ten : std_logic;signal xl, xl_ten : std_logic;signal js_dh, js_dl: std_logic_vector(3 downto 0);signal im_dh, im_dl: std_logic_vector(3 downto 0);signal wa_dh, wa_dl: std_logic_vector(3 downto 0);signal cs_dh, cs_dl: std_logic_vector(3 downto 0);signal dr_dh, dr_dl: std_logic_vector(3 downto 0);signal xl_dh, xl_dl: std_logic_vector(3 downto 0);signal dis_th,dis_tl: std_logic_vector(3 downto 0);begin-----------------------控制:控制器件实现洗衣机的功能:进水->浸泡->洗涤->出水->甩干->响铃->断电---------------control:process(clk0, rst,alarm)variable n: integer;beginif alarm = '1' thenpwf <= '1';elseif rst = '1' thenn := 0;im_ten <= '0';js_ten <= '0';wa_ten <= '0';cs_ten <= '0';dr_ten <= '0';xl_ten <= '0';pwf <= '0';elsif clk0 = '1' and clk0 'event thenif n = 0 thenif water_inh = "0000"and water_inl = "0000"thenn := 1;elsejs_ten <= '1';if js = '1' thenn := 1;end if;end if;elsif js = '0' and n = 1 thenif im_th = "0000"and im_tl = "0000"thenn := 2;elseim_ten <= '1';if im = '1' thenn := 2;end if;end if;elsif im = '0' and n = 2 thenif wash_th = "0000"and wash_tl = "0000"thenn := 3;elsewa_ten <= '1';if wa = '1' thenn := 3;end if;end if;elsif wa = '0' and n = 3 thenif water_outh = "0000"and water_outl = "0000"thenn := 4;elsecs_ten <= '1';if cs = '1' thenn := 4;end if;end if;elsif cs = '0' and n = 4 thenif dry_th = "0000"and dry_tl = "0000"thenn := 5;elsedr_ten <= '1';if dr = '1' thenn := 5;end if;end if;elsif dr = '0' and n = 5 thenxl_ten <= '1';if xl = '1' thenn := 6;end if;elsif xl = '0' and n = 6 thenpwf <= '1';end if;end if;end if;end process;-----------------------------记时----------------------------- ------------------进水记时--------------------------js_jishiqi:process(clk1, js_ten)beginif js_ten = '0' thenjs_dh <= water_inh;js_dl <= water_inl;js <= '0';elsif clk1 = '1' and clk1 'event thenif js_dh = "0000"and js_dl = "0000"thenjs <= '0';elsejs <= '1';if js_dl = "0000"thenjs_dl <= "1001";js_dh <= js_dh - 1;elsejs_dl <= js_dl - 1;end if;end if;end if;end process;-------------浸泡记时-----------------------im_jishiqi:process(clk1, im_ten)beginif im_ten = '0' thenim_dh <= im_th;im_dl <= im_tl;im <= '0';elsif clk1 = '1' and clk1 'event thenif im_dh = "0000"and im_dl = "0000"then im <= '0';elseim <= '1';if im_dl = "0000"thenim_dl <= "1001";im_dh <= im_dh - 1;elseim_dl <= im_dl - 1;end if;end if;end if;end process;-----------------洗涤记时---------------------- wa_jishiqi:process(clk1, wa_ten)variable m: integer;beginif wa_ten = '0' thenwa_dh <= wash_th;wa_dl <= wash_tl;wa <= '0';wa1 <= '0';wa2 <= '0';m := 0;elsif clk1 = '1' and clk1 'event thenif wa_dh = "0000"and wa_dl = "0000"then wa <= '0';elsewa <= '1';if m = 0 thenwa1 <= '1';wa2 <= '1';elsif m = 10 thenwa1 <= '0';wa2 <= '1';elsif m = 13 thenwa1 <= '1';wa2 <= '0';elsif m = 23 thenwa1 <= '0';wa2 <= '0';elsif m = 26 thenm := 0;end if;m := m + 1;if wa_dl = "0000"thenwa_dl <= "1001";wa_dh <= wa_dh - 1;elsewa_dl <= wa_dl - 1;end if;end if;end if;end process;--------------出水记时--------------------------- cs_jishiqi:process(clk1, cs_ten)beginif cs_ten = '0' thencs_dh <= water_outh;cs_dl <= water_outl;cs <= '0';elsif clk1 = '1' and clk1 'event thenif cs_dh = "0000"and cs_dl = "0000"then cs <= '0';elsecs <= '1';if cs_dl = "0000"thencs_dl <= "1001";cs_dh <= cs_dh - 1;elsecs_dl <= cs_dl - 1;end if;end if;end if;end process;--------------甩干记时-----------------------dr_jishiqi:process(clk1, dr_ten)beginif dr_ten = '0' thendr_dh <= dry_th;dr_dl <= dry_tl;dr <= '0';elsif clk1 = '1' and clk1 'event thenif dr_dh = "0000"and dr_dl = "0000"then dr <= '0';elsedr <= '1';if dr_dl = "0000"thendr_dl <= "1001";dr_dh <= dr_dh - 1;elsedr_dl <= dr_dl - 1;end if;end if;end if;end process;------------------响铃记时---------------------- xl_jishiqi:process(clk1, xl_ten)beginif xl_ten = '0' thenxl_dh <= "0010";xl_dl <= "0000";xl <= '0';elsif clk1 = '1' and clk1 'event thenif xl_dh = "0000"and xl_dl = "0000"then xl <= '0';elsexl <= '1';if xl_dl = "0000"thenxl_dl <= "1001";xl_dh <= xl_dh - 1;elsexl_dl <= xl_dl - 1;end if;end if;end if;end process;----------------------------显示时间--------------------------xianshishijian: process(clk1, js_ten, im_ten, wa_ten)beginif js_ten = '1' and im_ten = '0' and wa_ten = '0' and cs_ten = '0' and dr_ten = '0' and xl_ten = '0' thenif clk1 = '1' and clk1 'event thendis_th <= js_dh;dis_tl <= js_dl;end if;elsif im_ten= '1' and wa_ten= '0' and cs_ten= '0' and dr_ten= '0' and xl_ten = '0' thenif clk1 = '1' and clk1 'event thendis_th <= im_dh;dis_tl <= im_dl;end if;elsif wa_ten = '1' and cs_ten = '0' and dr_ten = '0' and xl_ten = '0' then if clk1 = '1' and clk1 'event thendis_th <= wa_dh;dis_tl <= wa_dl;end if;elsif cs_ten = '1' and dr_ten = '0' and xl_ten = '0' thenif clk1 = '1' and clk1 'event thendis_th <= cs_dh;dis_tl <= cs_dl;end if;elsif dr_ten = '1' and xl_ten = '0' thenif clk1 = '1' and clk1 'event thendis_th <= dr_dh;dis_tl <= dr_dl;end if;elsif xl_ten = '1' thenif clk1 = '1' and clk1 'event thendis_th <= xl_dh;dis_tl <= xl_dl;end if;end if;end process;----------------------------输出-----------------------------output:process(dis_th, dis_tl, im, js, cs, dr, wa1, wa2, xl, pwf)begindisplay_th <= dis_th;display_tl <= dis_tl;immersion <= im;water_in <= js;water_out <= cs;dry <= dr;z1 <= wa1;z2 <= wa2;voice <= xl;poweroff <= pwf;end process;end behave;测试文件:-------------------------------------------------------------- VHDL Testbench for xiyiji-- 2009 9 25 11 16 3-- Created by "EditVHDL"-- "Copyright (c) 2002 Altium Limited"------------------------------------------------------------Library IEEE;Use IEEE.std_logic_1164.all;Use IEEE.std_logic_textio.all;Use STD.textio.all;------------------------------------------------------------------------------------------------------------------------entity Testxiyiji isend Testxiyiji;------------------------------------------------------------------------------------------------------------------------architecture stimulus of Testxiyiji isfile RESULTS: TEXT open WRITE_MODE is"results.txt";procedure WRITE_RESULTS(alarm: std_logic;clk0: std_logic;clk1: std_logic;display_th: std_logic_vector(3 downto 0);display_tl: std_logic_vector(3 downto 0);dry: std_logic;dry_th: std_logic_vector(3 downto 0);dry_tl: std_logic_vector(3 downto 0);im_th: std_logic_vector(3 downto 0);im_tl: std_logic_vector(3 downto 0);immersion: std_logic;poweroff: std_logic;rst: std_logic;voice: std_logic;wash_th: std_logic_vector(3 downto 0);wash_tl: std_logic_vector(3 downto 0);water_in: std_logic;water_inh: std_logic_vector(3 downto 0);water_inl: std_logic_vector(3 downto 0);water_out: std_logic;water_outh: std_logic_vector(3 downto 0);water_outl: std_logic_vector(3 downto 0);z1: std_logic;z2: std_logic) isvariable l_out : line;beginwrite(l_out, now, right, 15);write(l_out, alarm, right, 2);write(l_out, clk0, right, 2);write(l_out, clk1, right, 2);write(l_out, display_th, right, 5);write(l_out, display_tl, right, 5);write(l_out, dry, right, 2);write(l_out, dry_th, right, 5);write(l_out, dry_tl, right, 5);write(l_out, im_th, right, 5);write(l_out, im_tl, right, 5);write(l_out, immersion, right, 2);write(l_out, poweroff, right, 2);write(l_out, rst, right, 2);write(l_out, voice, right, 2);write(l_out, wash_th, right, 5);write(l_out, wash_tl, right, 5);write(l_out, water_in, right, 2);write(l_out, water_inh, right, 5);write(l_out, water_inl, right, 5);write(l_out, water_out, right, 2);write(l_out, water_outh, right, 5);write(l_out, water_outl, right, 5);write(l_out, z1, right, 2);write(l_out, z2, right, 2);writeline(RESULTS, l_out);end procedure;component xiyijiport (alarm: in std_logic;clk0: in std_logic;clk1: in std_logic;display_th: out std_logic_vector(3 downto 0);display_tl: out std_logic_vector(3 downto 0);dry: out std_logic;dry_th: in std_logic_vector(3 downto 0);dry_tl: in std_logic_vector(3 downto 0);im_th: in std_logic_vector(3 downto 0);im_tl: in std_logic_vector(3 downto 0);immersion: out std_logic;poweroff: out std_logic;rst: in std_logic;voice: out std_logic;wash_th: in std_logic_vector(3 downto 0);wash_tl: in std_logic_vector(3 downto 0);water_in: out std_logic;water_inh: in std_logic_vector(3 downto 0);water_inl: in std_logic_vector(3 downto 0);water_out: out std_logic;water_outh: in std_logic_vector(3 downto 0);water_outl: in std_logic_vector(3 downto 0);z1: out std_logic;z2: out std_logic);end component;signal alarm: std_logic;signal clk0: std_logic;signal clk1: std_logic;signal display_th: std_logic_vector(3 downto 0);signal display_tl: std_logic_vector(3 downto 0);signal dry: std_logic;signal dry_th: std_logic_vector(3 downto 0);signal dry_tl: std_logic_vector(3 downto 0);signal im_th: std_logic_vector(3 downto 0);signal im_tl: std_logic_vector(3 downto 0);signal immersion: std_logic;signal poweroff: std_logic;signal rst: std_logic;signal voice: std_logic;signal wash_th: std_logic_vector(3 downto 0);signal wash_tl: std_logic_vector(3 downto 0);signal water_in: std_logic;signal water_inh: std_logic_vector(3 downto 0);signal water_inl: std_logic_vector(3 downto 0);signal water_out: std_logic;signal water_outh: std_logic_vector(3 downto 0);signal water_outl: std_logic_vector(3 downto 0);signal z1: std_logic;signal z2: std_logic;beginDUT:xiyiji port map (alarm => alarm,clk0 => clk0,clk1 => clk1,display_th => display_th,display_tl => display_tl,dry => dry,dry_th => dry_th,dry_tl => dry_tl,im_th => im_th,im_tl => im_tl,immersion => immersion,poweroff => poweroff,rst => rst,voice => voice,wash_th => wash_th,wash_tl => wash_tl,water_in => water_in,water_inh => water_inh,water_inl => water_inl,water_out => water_out,water_outh => water_outh,water_outl => water_outl,z1 => z1,);STIMULUS0:processbeginalarm <= '0';dry_th <= "1000";dry_tl<= "0000";im_th <= "0000";im_tl <= "0000";wash_th <= "0000";wash_tl <= "0000";water_inh <= "0000";water_inl <= "0000";water_outh <= "0000";water_outl <= "0000";rst <= '1';wait for 10ns;rst <= '0';wait for 1000ns;alarm <= '1';wait;end process;processbeginclk0 <= '1';clk1 <= '1';wait for 1ns;clk0 <= '0';clk1 <= '0';wait for 1ns;end process;WRITE_RESULTS(alarm,clk0,clk1,display_th,display_tl,dry,dry_th,dry_tl,im_th,im_tl,immersion,poweroff,rst,voice,wash_th,wash_tl,water_in,water_inh,water_inl,water_outh,water_outl,z1,z2);end architecture; 波形图:显示模块:此模块实现将由控制器件产生的时间显示的BCD码与地址选择信号同步的转化成可供LCD显示的ASCII码并同时显示字母WELCOME的功能!VHDL文件:LIBRARY IEEE;USE IEEE.std_Logic_1164.ALL;ENTITY OUTPUT ISPORT(R, CP, BUSY :IN Std_Logic;-----使能输入端,脉冲输入端,输入信号忙输入端--------LINE_OUT,STROBE,RST:OUT STD_LOGIC;------行选择输出端,输入数据使能输出端,复位输出端--- TIME_IN :IN STD_LOGIC_VECTOR(7 DOWNTO 0);--------输入时间-----------ADDR_OUT :OUT Std_Logic_Vector( 3DOWNTO 0);--------地址输出端----------DATA_OUT : OUT Std_Logic_Vector(7 DOWNTO 0));-----数据输出端---------END OUTPUT;ARCHITECTURE XS OF OUTPUT ISTYPE State_type IS(S0,S1,S2,S3,S4);SIGNAL S :State_Type;SIGNAL LCDPT:INTEGER RANGE 0 TO 9;BEGINPROCESS(CP,R)BEGINIF R='1' THENS<=S0;LCDPT<=0;RST<='1';ELSIF CP='1' AND CP 'EVENT THENCASE S ISWHEN S0=> S<=S1;LCDPT<=0;RST<='1';WHEN S1=> RST<='0';STROBE<='0';IF BUSY='0' THENLCDPT<=LCDPT+1;IF LCDPT=8 THENS<=S3;ELSES<=S2;END IF;END IF;WHEN S2=> S<=S1;STROBE<='1';WHEN S3=> STROBE<='0';IF BUSY='0' THENIF LCDPT=9 THENLCDPT<=8;LCDPT<=LCDPT+1;END IF;S<=S4;END IF;WHEN S4=> STROBE<='1';S<=S3;WHEN OTHERS=> NULL;END CASE;END IF;END PROCESS;PROCESS (LCDPT)BEGINCASE LCDPT ISWHEN 0 => NULL;WHEN 1 => DATA_OUT<="01010111" ; ADDR_OUT<="0011"; LINE_OUT<='0';WHEN 2 => DATA_OUT<="01000101" ; ADDR_OUT<="0100"; LINE_OUT<='0';WHEN 3 => DATA_OUT<="01001100" ; ADDR_OUT<="0101"; LINE_OUT<='0';WHEN 4 => DATA_OUT<="01000011" ; ADDR_OUT<="0110"; LINE_OUT<='0';WHEN 5 => DATA_OUT<="01001111" ; ADDR_OUT<="0111"; LINE_OUT<='0';WHEN 6 => DATA_OUT<="01001101" ; ADDR_OUT<="1000"; LINE_OUT<='0';WHEN 7 => DATA_OUT<="01000101" ; ADDR_OUT<="1001"; LINE_OUT<='0';WHEN 8 => DATA_OUT<="0011"&TIME_IN(7 DOWNTO4);ADDR_OUT<="0101";LINE_OUT<='1';WHEN 9 => DATA_OUT<="0011"&TIME_IN(3 DOWNTO0);ADDR_OUT<="0110";LINE_OUT<='1';END CASE;END PROCESS;END ARCHITECTURE;-------1,2,3,4,5,6,7输入字母WELCOME,8,9输入时间变化----------TEST文件:-- VHDL Testbench for output-- 2009 9 23 16 13 33-- Created by "EditVHDL"-- "Copyright (c) 2002 Altium Limited"------------------------------------------------------------Library IEEE;Use IEEE.std_logic_1164.all;Use IEEE.std_logic_textio.all;Use STD.textio.all;------------------------------------------------------------------------------------------------------------------------entity Testoutput isend Testoutput;------------------------------------------------------------------------------------------------------------------------architecture stimulus of Testoutput isfile RESULTS: TEXT open WRITE_MODE is"results.txt";procedure WRITE_RESULTS(ADDR_OUT: std_logic_vector(3 downto 0);CP: std_logic;DATA_OUT: std_logic_vector(7 downto 0);LINE_OUT: std_logic;Reset: std_logic;RST: std_logic;STROBE: std_logic) isvariable l_out : line;beginwrite(l_out, now, right, 15);write(l_out, ADDR_OUT, right, 5);write(l_out, BUSY, right, 2);write(l_out, CP, right, 2);write(l_out, DATA_OUT, right, 9);write(l_out, LINE_OUT, right, 2);write(l_out, Reset, right, 2);write(l_out, RST, right, 2);write(l_out, STROBE, right, 2);writeline(RESULTS, l_out);end procedure;component outputport (ADDR_OUT: out std_logic_vector(3 downto 0);BUSY: in std_logic;CP: in std_logic;DATA_OUT: out std_logic_vector(7 downto 0);LINE_OUT: out std_logic;Reset: in std_logic;RST: out std_logic;STROBE: out std_logic);end component;signal ADDR_OUT: std_logic_vector(3 downto 0);signal BUSY: std_logic;signal CP: std_logic;signal DATA_OUT: std_logic_vector(7 downto 0);signal LINE_OUT: std_logic;signal Reset: std_logic;signal RST: std_logic;signal STROBE: std_logic;beginDUT:output port map (ADDR_OUT => ADDR_OUT,BUSY => BUSY,CP => CP,DATA_OUT => DATA_OUT,LINE_OUT => LINE_OUT,Reset => Reset,RST => RST,STROBE => STROBE);STIMULUS0:processbeginRESET<='1';BUSY <= '0';WAIT FOR 2NS;RESET<='0';WAIT FOR 100NS ;RESET <= '1';WAIT FOR 100NS;wait;end process;PROCESSBEGINCP<='0';WAIT FOR 1NS ;CP<='1';WAIT FOR 1NS;END PROCESS;WRITE_RESULTS(ADDR_OUT,BUSY,CP,DATA_OUT,LINE_OUT,Reset,RST,STROBE);end architecture; 波形图:模块运用了器件库里的LCD显示器件:1、模块运用AD6现有资源,由晶振产生的10MHZ的基准时钟和分频器CDIV可将基准时钟分频,即后续模块所需要的不同频率脉冲及LCD(CLK0)控制器时钟.心得体会本次课程设计是一个很好的锻炼机会。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1数字电路与逻辑设计实验报告题目: 洗衣机控制器设计2一、洗衣机控制器要求设计制作一个全自动洗衣机的控制器:_ 洗衣机的工作步骤为洗衣、漂洗和脱水三个过程,工作时间分别为:洗衣20 秒,漂洗30 秒,脱水15 秒;_ 用一个按键实现洗衣程序的手动选择:A 、单洗涤;B 、单漂洗;C 、单脱水; D 、漂洗和脱水;E 、洗涤、漂洗和脱水全过程;_ 用显示器件显示洗衣机的工作状态(洗衣、漂洗和脱水),并倒计时显示每个 状态的工作时间,全部过程结束后,应提示使用者;_ 用一个按键实现暂停洗衣和继续洗衣的控制,暂停后继续洗衣应回到暂停之前 保留的状态;_ 选做:三个过程的时间有多个选项供使用者选择。

_ 选做:可以预约洗衣时间。

_ 选做:自拟其它功能。

二、系统设计基本思想电路由模式选择、计数器、报警模块以及译码驱动电路和数字显示电路等模块组成。

1、模式选择模块五种洗衣模式可供用户选择,模式选择模块将用户的选择信息传递到控制模块。

2、减计数计数器模块计数器洗衣以倒计时模块的方式提示用户当前剩余的洗衣时间,该计数器能读取不同的模值进行计数。

计时单位为一秒钟。

3、译码和数码显示电路译码和数码显示电路是将计时状态直观清晰地反映出来,被人们的视觉器官所接受。

显示器件选用LED 七段数码管。

在译码显示电路输出的驱动下,显示出清晰、直观的数字符号。

4、报警模块当系统运行到“报警”状态时,蜂鸣器将会报警,时间为5 秒。

4、分频器模块设计一个大小合适的分频器使得系统能够正确的实现一秒的计时。

三、总体设计图以及转移图流程图示:3状态选择开始信号输入变量A 为1YESNO进行洗涤变量B 为1YESNO进行漂洗变量C 为1YES进行脱水NO完成洗衣后报警提示完成4总体逻辑设计图:状态转移图示:控制器分频器OSC时间计数器洗涤漂洗脱水译码时间显示ClkClk1Clk2T15 T20 T2Cnt clr 报警Pause状态选择 译码5管脚设计图:WAITA =’1’进行洗涤进行漂洗A =’0’ B=‘1’B =’0’B =’1’进行脱水A =’0’ B=‘0’C =’1’C =’0’完成洗衣报警提示仿真情况:6简要说明:本次仿真执行的是第五个状态即洗涤、漂洗和脱水全过程。

通过此仿真可以7发现当输出选择模式信号change 时,洗衣机模式开始发生变化。

输入第一个change 信号的时候进入单洗涤状态,输入第二个change 信号进入单漂洗状态,输入第三个change 信号进入了单脱水的状态,输入第四个change 信号进入了脱水和漂洗的状态,当输入最后一个change 信号的时候进入洗涤、漂洗和脱水的全状态。

而在选择每个状态的同时时间信号(q[0]、q[1]、q[2]、q[3]、q[4]、q[5]、q[6])也发生变化,显示出每个状态时的时间。

而设定的led 灯(cat0、cat1)则依次闪亮。

当start 开始后change 信号不再起作用,而系统进入了运行状态,时间开始逐秒变化。

当程序最终运行结束后,进入报警状态,sound 开始显示为高电平,而时间均为0。

(特别说明:由于本实验分2次去做,管脚设定的时候进行了新建工程,代码粘贴过去的,实体名字取得和第二周验收时候不一致,不是其他原因。

)四、代码示例LIBRARY ieee;USE ieee.std_logic_1164.ALL; ENTITY xiyiji IS PORT ( START: IN STD_LOGIC;PAUSE: IN STD_LOGIC; --------暂停信号 CLOCK: IN STD_LOGIC;Q: OUT STD_LOGIC_VECTOR(6 DOWNTO 0); ----数码管显示信号CAT : OUTSTD_LOGIC_VECTOR(5 DOWNTO 0) ----数码管选通信号);END xiyiji;ARCHITECTURE washer OF xiyiji IS SIGNAL STATE: STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL MODE: STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL TEMP: INTEGER RANGE 45 DOWNTO 0; -------时间中间变量 SIGNAL TIME: INTEGER RANGE 60 DOWNTO 0; -------倒计时时间 SIGNAL TMP: INTEGER RANGE 999 DOWNTO 0; -------分频变量 SIGNAL MA: INTEGER RANGE 9 DOWNTO 0; -------数码管译码变量SIGNAL CLK: STD_LOGIC; ------分频时钟输出BEGIN PROCESS(CLOCK)BEGIN IF (CLOCK'EVENT AND CLOCK='1') THEN ----分频模块 TMP<=TMP + 1; IF (TMP=999) THEN TMP<=0;CLK<= NOT CLK;END IF;END IF;8END PROCESS;PROCESS (START,CLK,PAUSE,CHANGE)----洗衣控制进程BEGIN IF ( START = '0' ) THEN --------开始前模式选择模块 IF(CHANGE'EVENT AND CHANGE='1') THEN CASE MODE ISWHEN "000"=>MODE<="001"; WHEN "001"=>MODE<="010"; WHEN "010"=>MODE<="100"; WHEN "100"=>MODE<="110"; WHEN "110"=>MODE<="111"; WHEN OTHERS=>MODE<="000"; END CASE; END IF; STATE <= MODE;------------选择洗衣模式BUZZER <= '0'; CASE STATE IS ------设置模式时间以及中间变量的值 WHEN "001" =>TEMP <= 0 ;TIME <= 20;WHEN "010" =>TEMP <= 0 ;TIME <= 25;WHEN "100" =>TEMP <= 0 ;TIME <= 15;WHEN "110" =>TEMP <= 25 ;TIME <= 40;WHEN "111" =>TEMP <= 40 ;TIME <= 60;WHEN "000" =>TEMP <= 0 ;TIME <= 0;WHEN OTHERS =>TEMP<= 0 ;TIME<= 0;END CASE ;ELSE IF ( PAUSE = '0') THEN ----设置暂停信号IF ( CLK'EVENT AND CLK = '1' AND TIME/=0) THEN TIME <= TIME - 1 ; ------时间自减 IF ( TIME=1 ) THENSTATE <="000";BUZZER<= '1';------蜂鸣信号启动ELSIF ( TIME = TEMP ) THEN ----洗衣中模式的切换 CASE STATE IS WHEN "111" =>STATE <= "110";TEMP <= 20;WHEN "110" =>STATE <= "100";9TEMP <= 0;WHEN OTHERS =>TEMP <= 0 ;STATE <= "000";END CASE;END IF;END IF;END IF;END IF;MODEEND <= STATE; ------中间变量赋值给结果变量END PROCESS;PROCESS (CLOCK,TIME)BEGIN IF (CLOCK='1') THEN ------提取十位数CAT<="111110"; ------数码管选通END IF;END PROCESS;process (MA) ---------将数字译码为七段共阴数码管码 begin case MA is when 1 => q <= "0110000" ; when 2 => q <= "1101101" ; when 3 => q <= "1111001" ; when 4 => q <= "0110011" ; when 5 => q <= "1011011" ; when 6 => q <= "1011111" ; when 7 => q <= "1110000" ; when 8 => q <= "1111111" ; when 9 => q <= "1111011" ;when others => q <= "1111110";end case;end process;end washer; ----------洗衣机控制器结束首先根据实验题目的要求可以将洗衣机控制器分解成为如下的几个模块:洗衣机模式选择、计数器、报警模块以及译码驱动电路和数字显示电路。

1、模式选择模块:总共五种洗衣模式可供用户选择,模式选择模块将用户的选择信息传递到控制模块,这个模式选择模块将在洗衣机的开始按键start 按下前进行模式选择。