SD引脚定义

SD卡设计基础指南

SD卡设计基础指南目录1、概述 (3)2、SD卡硬件设计规范指导 (3)2.1 SD卡接口总线分类 (3)2.1.1 SD总线拓扑 (4)2.1.2 SPI总线拓扑 (4)2.2 SD卡接口定义 (5)2.3 SD卡工作原理以及总线协议 (7)2.4 SD卡典型应用电路图 (8)2.7 SD卡PCB布局与走线规范 (10)3、SD卡规格总览 (13)3.1 SD卡种类 (13)3.2总线速 (13)3.3 智能型SDIO(iSDIO,无线局域网络SD) (15)4、SD卡的测试 (16)5、参考文献 (16)1、概述SD卡全名:Secure Digital Memory Card,它是由日本松下、东芝及美国SanDisk 公司于1999年8月共同开发研制,具有高记忆容量、快速数据传输率、极大的移动灵活性以及很好的安全性。

SD存储卡是特别为符合新出现的音频和视频消费电子设备的安全性、容量、性能和环境要求而设计的一种存储卡,它有比较高的数据传送速度,而且不断更新标准。

SD卡系统是一个新的大容量存储系统,基于半导体技术的变革。

它的出现,提供了一个便宜的、结实的卡片式的存储媒介,为了消费多媒体应用。

SD卡可以设计出便宜的播放器和驱动器而没有可移动的部分。

一个低耗电和广供电电压的可以满足移动电话、电池应用比如音乐播放器、个人管理器、掌上电脑、电子书、电子百科全书、电子词典等等。

它使用非常有效的数据压缩比如MPEG,SD 卡可以提供足够的容量来应付多媒体数据。

SD卡在24mm*32mm*2.1mm的体积内结合了快闪记忆卡控制与MLC技术和东芝的NAND技术,通过9针的接口与专门的驱动器相连接,不需要额外的电源来保持其上的记忆信息。

无论是听音乐、摄影、拍照、存档、或使用智能型手机,SD规格让制造商每天用效能更高的产品,传递更美好的日常使用经验给上百万个消费者。

作为一种产业通用技术标准,SD提供移动储存产业一个多元化的市场区隔应用,包括:移动电话、数码相机、MP3播放器、个人计算机个人电脑、平板计算机平板电脑、列表机打印机、汽车导航系统、电子书、以及更多消费性电子设备。

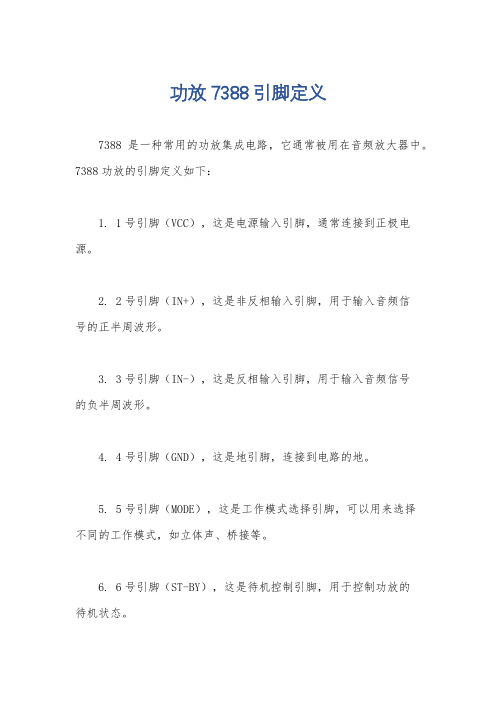

功放7388引脚定义

功放7388引脚定义

7388是一种常用的功放集成电路,它通常被用在音频放大器中。

7388功放的引脚定义如下:

1. 1号引脚(VCC),这是电源输入引脚,通常连接到正极电源。

2. 2号引脚(IN+),这是非反相输入引脚,用于输入音频信

号的正半周波形。

3. 3号引脚(IN-),这是反相输入引脚,用于输入音频信号

的负半周波形。

4. 4号引脚(GND),这是地引脚,连接到电路的地。

5. 5号引脚(MODE),这是工作模式选择引脚,可以用来选择

不同的工作模式,如立体声、桥接等。

6. 6号引脚(ST-BY),这是待机控制引脚,用于控制功放的

待机状态。

7. 7号引脚(SD),这是过热保护和短路保护引脚,用于保护功放免受过热和短路的损害。

8. 8号引脚(OUT+),这是输出端的非反相引脚,连接到负载(如扬声器)的正极。

9. 9号引脚(OUT-),这是输出端的反相引脚,连接到负载(如扬声器)的负极。

以上是7388功放的典型引脚定义,这些引脚在设计和应用7388功放电路时需要正确连接和使用,以确保功放电路正常工作并达到预期的音频放大效果。

电源芯片引脚定义(特制材料)

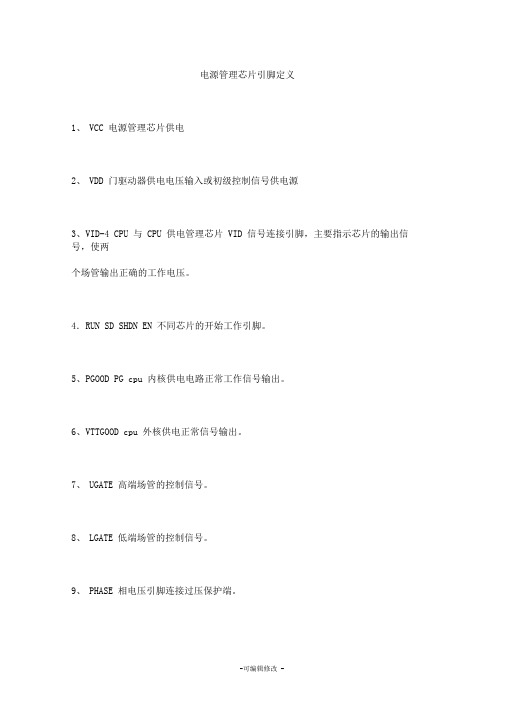

电源管理芯片引脚定义1、VCC 电源管理芯片供电2、VDD 门驱动器供电电压输入或初级控制信号供电源3、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

4.RUN SD SHDN EN 不同芯片的开始工作引脚。

5、PGOOD PG cpu内核供电电路正常工作信号输出。

6、VTTGOOD cpu外核供电正常信号输出。

7、UGATE 高端场管的控制信号。

8、LGATE 低端场管的控制信号。

9、PHASE 相电压引脚连接过压保护端。

10、VSEN 电压检测引脚。

11、FB 电流反馈输入即检测电流输出的大小。

12、COMP 电流补偿控制引脚。

13、DRIVE cpu外核场管驱动信号输出。

14、OCSET 12v供电电路过流保护输入端。

15、BOOT 次级驱动信号器过流保护输入端。

16、VIN cpu外核供电转换电路供电来源芯片连接引脚。

17、VOUT cpu外核供电电路输出端与芯片连接。

18、SS 芯片启动延时控制端,一般接电容。

19、AGND GND PGND 模拟地,地线,电源地20、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。

21、SET 调整电流限制输入。

22、SKIP 静音控制,接地为低噪声。

23、TON 计时选择控制输入。

24、REF 基准电压输出。

25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC丧失过压保护功能。

26、FBS 电压输出远端反馈感应输入。

27、STEER 逻辑控制第二反馈输入。

28、TIME/ON 5 双重用途时电容和开或关控制输入29、RESET 复位输出V1-0v跳变,低电平时复位。

30、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时5v输出在3.3v之前。

SEQ接REF上,3.3v 5v各自独立。

SEQ接v1上时3.3v输出在5v之前。

SD卡原理及内部结构

摘要SD卡(Secure Digital Memory Card)是一种为满足安全性、容量、性能和使用环境等各方面的需求而设计的一种新型存储器件,它的出现提供了一种便宜的、结实的卡片式的存储媒介。

SD卡允许在两种模式下工作,即SD模式和SPI模式,SD卡在24mm×32mm×2.1mm的体积内结合了〔SanDisk〕快闪记忆卡控制与MLC (Multilevel Cell)技术和Toshiba(东芝)0.16u及0.13u的NAND技术,通过9针的接口界面与专门的驱动器相连接,不需要额外的电源来保持其上记忆的信息。

而且它是一体化固体介质,没有任何移动部分,所以不用担心机械运动SD卡的容量从16兆字节到最高32GB不等。

容量范围如此之宽,可为众多应用提供充足的外部存储空间。

SD卡做为各种消费电子产品外部存储的应用、开发技术己经非常成熟、广泛。

关键字SD卡存储器一SD卡发展历程SD卡的技术是基于MultiMedia卡(MMC)格式上发展而来,大小和MMC卡差不多,尺寸为32mm x 24mm x 2.1mm。

长宽和MMC卡一样,只是比MMC卡厚了0.7mm,以容纳更大容量的存贮单元。

SD卡与MMC卡保持着向上兼容,也就是说,MMC卡可以被新的SD设备存取,兼容性则取决于应用软件,但SD卡却不可以被MMC设备存取。

(SD卡外型采用了与MMC卡厚度一样的导轨式设计,以使SD设备可以适合MMC卡)。

SD卡接口除了保留MMC卡的7针外,还在两边加多了2针,作为数据线。

采用了NAND 型Flash Memory,基本上和SmartMedia的一样,平均数据传输率能达到2MB/s。

设有SD卡插槽的设备能够使用较簿身的MMC卡,但是标准的SD卡却不能插入到MMC卡插槽。

SD卡能够插于CF卡和PCMCIA卡上,插上转接器使用;而miniSD卡和microSD卡亦能插上转接器于SD卡插槽使用。

一些USB连接器能够插上SD卡,而且一些读卡器亦能够插上SD卡,并由许多连接埠,例如USB、FireWire等存取使用。

7851L功放引脚定义

7851L功放引脚定义7851L功放是一种高性能、低噪声、低失真的功率放大器,广泛应用于各种音频设备、通信设备和电视机等电子产品中。

在使用7851L 功放时,正确理解和使用其引脚定义是非常重要的。

本文将详细介绍7851L功放引脚的定义及其作用。

引脚定义7851L功放共有14个引脚,分别为:VIN、VCC、GND、SPKR、SPKL、BYPASS、MUTE、SD、MODE、STBY、OUT、FB、GAIN1、GAIN2。

下面分别对这些引脚进行解释。

VIN:音频输入引脚,接收音频信号。

VCC:电源输入引脚,接收正极电源。

GND:地引脚,接收负极电源和地。

SPKR:扬声器输出引脚,用于连接扬声器。

SPKL:左声道扬声器输出引脚,用于连接左声道扬声器。

BYPASS:旁路控制引脚,当该引脚接通时,输入信号将直接通过,不经过功放放大。

MUTE:静音控制引脚,当该引脚接通时,功放输出将被静音。

SD:过热保护引脚,当该引脚接通时,功放将进入过热保护模式。

MODE:模式选择引脚,用于选择功放的工作模式。

STBY:待机控制引脚,当该引脚接通时,功放将进入待机模式。

OUT:输出引脚,用于输出功放放大后的信号。

FB:反馈引脚,用于接收反馈信号。

GAIN1:增益控制引脚1,用于控制功放的增益。

GAIN2:增益控制引脚2,用于控制功放的增益。

引脚作用VIN引脚接收音频信号,是功放的输入端,输入的音频信号将通过功放进行放大。

VCC引脚接收正极电源,为功放提供电源。

GND引脚接收负极电源和地,为功放提供电源和地。

SPKR和SPKL引脚分别为扬声器输出引脚和左声道扬声器输出引脚,用于连接扬声器,将功放放大后的信号输出到扬声器。

BYPASS引脚为旁路控制引脚,当该引脚接通时,输入信号将直接通过,不经过功放放大。

MUTE引脚为静音控制引脚,当该引脚接通时,功放输出将被静音。

SD引脚为过热保护引脚,当该引脚接通时,功放将进入过热保护模式,以保护功放不受损坏。

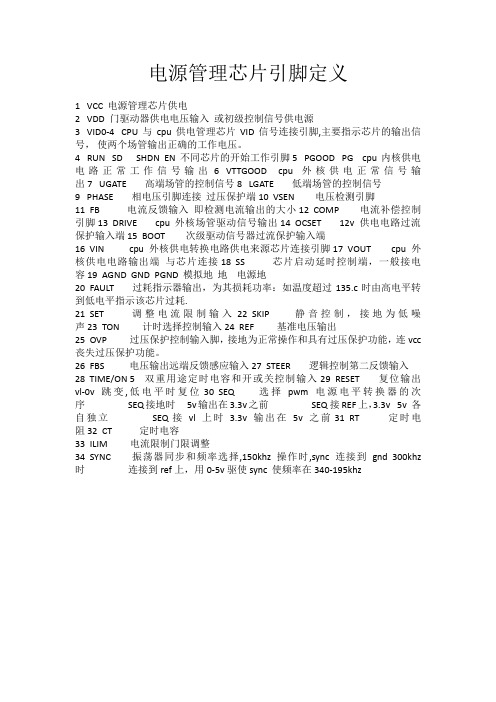

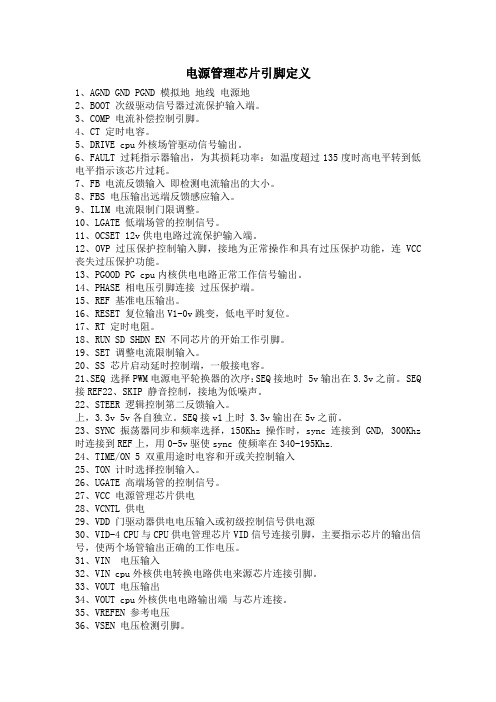

电源管理芯片引脚定义

电源管理芯片引脚定义1 VCC 电源管理芯片供电2 VDD 门驱动器供电电压输入或初级控制信号供电源3 VID0-4 CPU与 cpu供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

4 RUN SD SHDN EN 不同芯片的开始工作引脚5 PGOOD PG cpu内核供电电路正常工作信号输出6 VTTGOOD cpu外核供电正常信号输出7 UGATE 高端场管的控制信号8 LGATE 低端场管的控制信号9 PHASE 相电压引脚连接过压保护端 10 VSEN 电压检测引脚11 FB 电流反馈输入即检测电流输出的大小 12 COMP 电流补偿控制引脚 13 DRIVE cpu 外核场管驱动信号输出 14 OCSET 12v供电电路过流保护输入端 15 BOOT 次级驱动信号器过流保护输入端16 VIN cpu外核供电转换电路供电来源芯片连接引脚 17 VOUT cpu外核供电电路输出端与芯片连接 18 SS 芯片启动延时控制端,一般接电容 19 AGND GND PGND 模拟地地电源地20 FAULT 过耗指示器输出,为其损耗功率:如温度超过135.c时由高电平转到低电平指示该芯片过耗.21 SET 调整电流限制输入 22 SKIP 静音控制,接地为低噪声 23 TON 计时选择控制输入 24 REF 基准电压输出25 OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连vcc 丧失过压保护功能。

26 FBS 电压输出远端反馈感应输入 27 STEER 逻辑控制第二反馈输入28 TIME/ON 5 双重用途定时电容和开或关控制输入 29 RESET 复位输出vl-0v跳变,低电平时复位 30 SEQ 选择pwm电源电平转换器的次序 SEQ接地时 5v输出在3.3v之前 SEQ 接REF上,3.3v 5v 各自独立 SEQ 接vl上时 3.3v输出在5v之前 31 RT 定时电阻 32 CT 定时电容33 ILIM 电流限制门限调整34 SYNC 振荡器同步和频率选择,150khz操作时,sync连接到gnd 300khz 时连接到ref上,用0-5v驱使sync 使频率在340-195khz。

电源芯片引脚定义

电源芯片引脚定义Document serial number【UU89WT-UU98YT-UU8CB-UUUT-UUT108】电源管理芯片引脚定义1、VCC 电源管理芯片供电2、VDD 门驱动器供电电压输入或初级控制信号供电源3、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

4.RUN SD SHDN EN 不同芯片的开始工作引脚。

5、PGOOD PG cpu内核供电电路正常工作信号输出。

6、VTTGOOD cpu外核供电正常信号输出。

7、UGATE 高端场管的控制信号。

8、LGATE 低端场管的控制信号。

9、PHASE 相电压引脚连接过压保护端。

10、VSEN 电压检测引脚。

11、FB 电流反馈输入即检测电流输出的大小。

12、COMP 电流补偿控制引脚。

13、DRIVE cpu外核场管驱动信号输出。

14、OCSET 12v供电电路过流保护输入端。

15、BOOT 次级驱动信号器过流保护输入端。

16、VIN cpu外核供电转换电路供电来源芯片连接引脚。

17、VOUT cpu外核供电电路输出端与芯片连接。

18、SS 芯片启动延时控制端,一般接电容。

19、AGND GND PGND 模拟地,地线,电源地20、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。

21、SET 调整电流限制输入。

22、SKIP 静音控制,接地为低噪声。

23、TON 计时选择控制输入。

24、REF 基准电压输出。

25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC丧失过压保护功能。

26、FBS 电压输出远端反馈感应输入。

27、STEER 逻辑控制第二反馈输入。

28、TIME/ON 5 双重用途时电容和开或关控制输入29、RESET 复位输出V1-0v跳变,低电平时复位。

30、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时5v输出在之前。

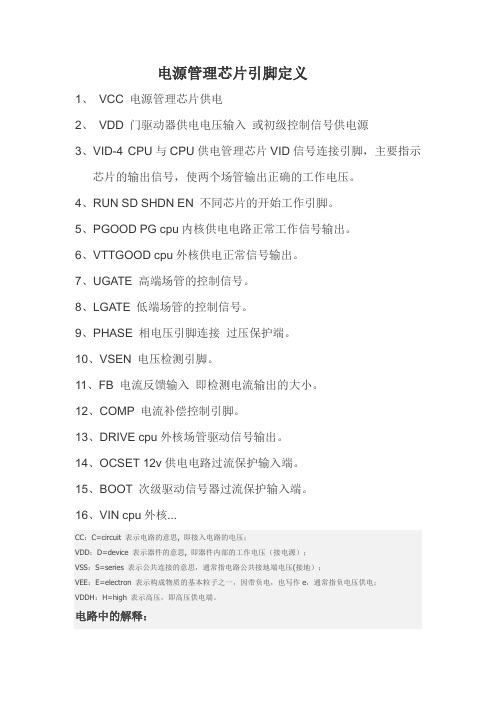

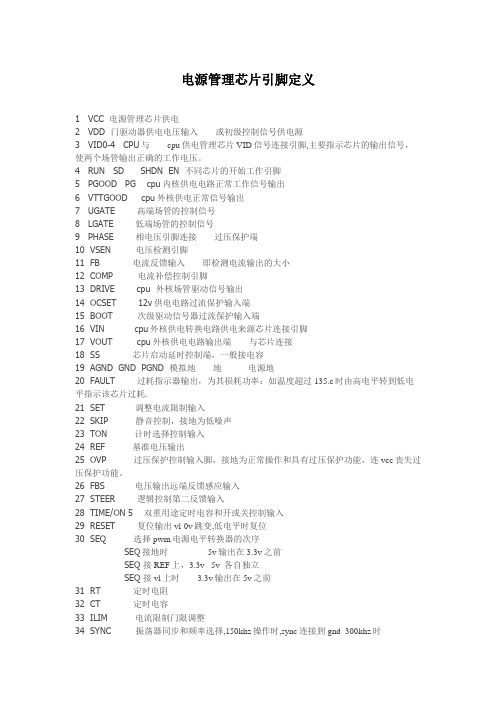

电源管理芯片引脚定义

电源管理芯片引脚定义1、VCC 电源管理芯片供电2、VDD 门驱动器供电电压输入或初级控制信号供电源3、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

4、RUN SD SHDN EN 不同芯片的开始工作引脚。

5、PGOOD PG cpu内核供电电路正常工作信号输出。

6、VTTGOOD cpu外核供电正常信号输出。

7、UGATE 高端场管的控制信号。

8、LGATE 低端场管的控制信号。

9、PHASE 相电压引脚连接过压保护端。

10、VSEN 电压检测引脚。

11、FB 电流反馈输入即检测电流输出的大小。

12、COMP 电流补偿控制引脚。

13、DRIVE cpu外核场管驱动信号输出。

14、OCSET 12v供电电路过流保护输入端。

15、BOOT 次级驱动信号器过流保护输入端。

16、VIN cpu外核...CC:C=circuit 表示电路的意思, 即接入电路的电压;VDD:D=device 表示器件的意思, 即器件内部的工作电压(接电源);VSS:S=series 表示公共连接的意思,通常指电路公共接地端电压(接地);VEE:E=electron 表示构成物质的基本粒子之一,因带负电,也写作e,通常指负电压供电;VDDH:H=high 表示高压,即高压供电端。

电路中的解释:单解:VDD:电源电压(单极器件);电源电压(4000系列数字电路);漏极电压(场效应管)VCC:电源电压(双极器件);电源电压(74系列数字电路);声控载波(Voice Controlled Carrier) VSS::地或电源负极VEE:负电压供电;场效应管的源极(S)VPP:编程/擦除电压。

(注:文档可能无法思考全面,请浏览后下载,供参考。

可复制、编制,期待你的好评与关注)。

存储卡标准.CF.SD.SDHC.MMC.TF卡引脚定义对应关系

3

VSS1

电源地1 电源地1

4 VSS1

3 VSS1

4

VDD

电源

电源

5

6

VDD1 VDD2 4

VDD

4 VDD VDD

电源

电源

5

CLK

时钟 时钟SCK

7 CLK 5 CLK 5 CLK SCLK

时钟 时钟sck

6

VSS2

电源地2 电源地2

8 VSS2

6 VSS2

6 VSS VSS

电源地 电源地

7

DAT0

数据线0 主入从出

9 DAT0

7 DAT 7 DAT0 DO

数据线0 主入从出

8 DAT1

10 DAT1

8 DAT1

X

数据线1 保留

TF卡, 又叫 microS D卡,8 pin,外 形以及 在SD和 SPI工作 模式下 引脚定

数据线2 数据线3 命令线 电ห้องสมุดไป่ตู้ 时钟 电源地 数据线0

保留 片选/从选SS 主出从入 电源 时钟sck 电源地 主入从出

数据线1

保留

三星 MMC Micro卡 (512MB) 基本特征 卡式类型 MMC Micro 闪存卡容 量 512MB 外形尺寸 14*12*1. 1 产品重量 1 电压(V) 2.7V3.6V 其他性能 读:10 MB/s; 写:7 MB/s

SD

概念 SD卡, 数字安 全记忆 卡 (Secur

e Digital

Memory Card) ,是用 于移动 设备的 标准记 忆卡。 SD卡数 据传送 和物理 规范由 MMC发 展而 来,大 小和 MMC差 不多。 长宽和 MMC一 样,比 MMC稍 微外厚形了及 接口定 义SD卡为

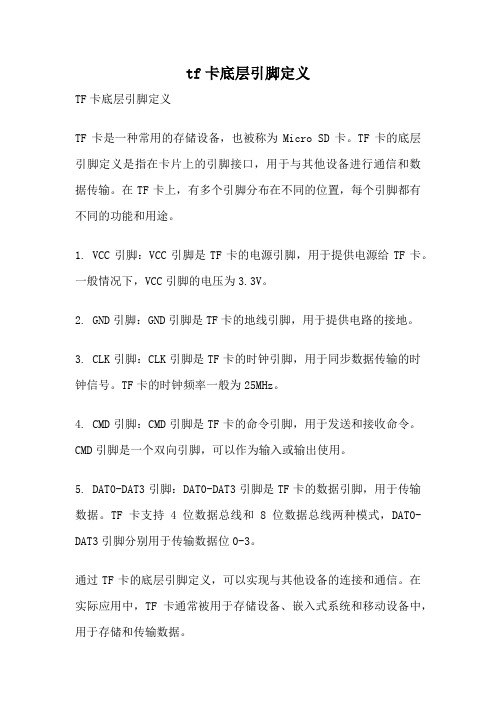

tf卡底层引脚定义

tf卡底层引脚定义TF卡底层引脚定义TF卡是一种常用的存储设备,也被称为Micro SD卡。

TF卡的底层引脚定义是指在卡片上的引脚接口,用于与其他设备进行通信和数据传输。

在TF卡上,有多个引脚分布在不同的位置,每个引脚都有不同的功能和用途。

1. VCC引脚:VCC引脚是TF卡的电源引脚,用于提供电源给TF卡。

一般情况下,VCC引脚的电压为3.3V。

2. GND引脚:GND引脚是TF卡的地线引脚,用于提供电路的接地。

3. CLK引脚:CLK引脚是TF卡的时钟引脚,用于同步数据传输的时钟信号。

TF卡的时钟频率一般为25MHz。

4. CMD引脚:CMD引脚是TF卡的命令引脚,用于发送和接收命令。

CMD引脚是一个双向引脚,可以作为输入或输出使用。

5. DAT0-DAT3引脚:DAT0-DAT3引脚是TF卡的数据引脚,用于传输数据。

TF卡支持4位数据总线和8位数据总线两种模式,DAT0-DAT3引脚分别用于传输数据位0-3。

通过TF卡的底层引脚定义,可以实现与其他设备的连接和通信。

在实际应用中,TF卡通常被用于存储设备、嵌入式系统和移动设备中,用于存储和传输数据。

TF卡底层引脚定义的功能和用途如下:1. 电源供应:VCC引脚和GND引脚提供电源给TF卡,保证其正常工作。

2. 时钟同步:CLK引脚提供时钟信号,用于同步数据传输,确保数据的准确性和完整性。

3. 数据传输:CMD引脚用于发送和接收命令,DAT0-DAT3引脚用于传输数据。

通过这些引脚,TF卡可以与其他设备进行数据的读取和写入。

TF卡的底层引脚定义是TF卡与其他设备进行通信和数据传输的关键。

通过准确地连接和配置这些引脚,可以实现TF卡与其他设备的稳定和可靠的数据交互。

总结一下,TF卡底层引脚定义包括VCC引脚、GND引脚、CLK引脚、CMD引脚和DAT0-DAT3引脚。

这些引脚在TF卡与其他设备的通信和数据传输中起到了重要的作用。

了解和掌握TF卡底层引脚定义,可以帮助我们更好地使用和应用TF卡,实现数据的存储和传输。

电源芯片引脚定义

电源管理芯片引脚定义1、 VCC 电源管理芯片供电2、 VDD 门驱动器供电电压输入或初级控制信号供电源3、VID-4 CPU 与 CPU 供电管理芯片 VID 信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

4.RUN SD SHDN EN 不同芯片的开始工作引脚。

5、PGOOD PG cpu 内核供电电路正常工作信号输出。

6、VTTGOOD cpu 外核供电正常信号输出。

7、 UGATE 高端场管的控制信号。

8、 LGATE 低端场管的控制信号。

9、 PHASE 相电压引脚连接过压保护端。

10、VSEN 电压检测引脚。

11、FB 电流反馈输入即检测电流输出的大小。

12、COMP 电流补偿控制引脚。

13、 DRIVE cpu 外核场管驱动信号输出。

14、 OCSET 12v 供电电路过流保护输入端。

15、BOOT 次级驱动信号器过流保护输入端。

16、 VIN cpu 外核供电转换电路供电来源芯片连接引脚。

17、 VOUT cpu 外核供电电路输出端与芯片连接。

18、SS 芯片启动延时控制端,一般接电容。

19、 AGND GND PGND 模拟地,地线,电源地20、FAULT 过耗指示器输出,为其损耗功率:如温度超过 135 度时高电平转到低电平指示该芯片过耗。

21、SET 调整电流限制输入。

22、SKIP 静音控制,接地为低噪声。

23、TON 计时选择控制输入。

24、REF 基准电压输出。

25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC 丧失过压保护功能。

26、FBS 电压输出远端反馈感应输入。

27、STEER 逻辑控制第二反馈输入。

28、 TIME/ON 5 双重用途时电容和开或关控制输入29、RESET 复位输出 V1-0v 跳变,低电平时复位。

30、SEQ 选择 PWM 电源电平轮换器的次序: SEQ 接地时 5v 输出在 3.3v 之前。

芯片引脚定义

电源管理芯片引脚定义1、AGND GND PGND 模拟地地线电源地2、BOOT 次级驱动信号器过流保护输入端。

3、COMP 电流补偿控制引脚。

4、CT 定时电容。

5、DRIVE cpu外核场管驱动信号输出。

6、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。

7、FB 电流反馈输入即检测电流输出的大小。

8、FBS 电压输出远端反馈感应输入。

9、ILIM 电流限制门限调整。

10、LGATE 低端场管的控制信号。

11、OCSET 12v供电电路过流保护输入端。

12、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC 丧失过压保护功能。

13、PGOOD PG cpu内核供电电路正常工作信号输出。

14、PHASE 相电压引脚连接过压保护端。

15、REF 基准电压输出。

16、RESET 复位输出V1-0v跳变,低电平时复位。

17、RT 定时电阻。

18、RUN SD SHDN EN 不同芯片的开始工作引脚。

19、SET 调整电流限制输入。

20、SS 芯片启动延时控制端,一般接电容。

21、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时 5v输出在3.3v之前。

SEQ 接REF22、SKIP 静音控制,接地为低噪声。

22、STEER 逻辑控制第二反馈输入。

上,3.3v 5v各自独立。

SEQ接v1上时 3.3v输出在5v之前。

23、SYNC 振荡器同步和频率选择,150Khz操作时,sync连接到GND, 300Khz 时连接到REF上,用0-5v驱使sync 使频率在340-195Khz.24、TIME/ON 5 双重用途时电容和开或关控制输入25、TON 计时选择控制输入。

26、UGATE 高端场管的控制信号。

27、VCC 电源管理芯片供电28、VCNTL 供电29、VDD 门驱动器供电电压输入或初级控制信号供电源30、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

SD卡引脚及spi模式基本操作过程精编版

SD卡引脚及spi模式基本操作过程(摘自网络)对于SD卡的硬件结构,在官方的文档上有很详细的介绍,如SD卡内的存储器结构、存储单元组织方式等内容。

要实现对它的读写,最核心的是它的时序,笔者在经过了实际的测试后,使用51单片机成功实现了对SD卡的扇区读写,并对其读写速度进行了评估。

下面先来讲解SD卡的读写时序。

SD卡的引脚定义SD卡引脚功能详述:引脚编号SD模式SPI模式名称类型描述名称类型描述1 CD/DAT3 IO或PP 卡检测/数据线3#CS I 片选2 CMD PP 命令/回应DI I 数据输入3 VSS1 S 电源地VSS S 电源地4 VDD S 电源VDD S 电源5 CLK I 时钟SCLK I 时钟6 VSS2 S 电源地VSS2 S 电源地7 DAT0 IO或PP 数据线0 DO O或PP 数据输出8 DAT1 IO或PP 数据线1 RSV9 DAT2 IO或PP 数据线2 RSV注:S:电源供给I:输入O:采用推拉驱动的输出PP:采用推拉驱动的输入输出SD卡SPI模式下与单片机的连接图:SD卡支持两种总线方式:SD方式与SPI方式。

其中SD方式采用6线制,使用CLK、CMD、DAT0~DAT3进行数据通信。

而SPI方式采用4线制,使用CS、CLK、DataIn、DataOut进行数据通信。

SD方式时的数据传输速度与SPI方式要快,采用单片机对SD卡进行读写时一般都采用SPI模式。

采用不同的初始化方式可以使SD卡工作于SD方式或SPI 方式。

这里只对其SPI方式进行介绍。

SPI方式驱动SD卡的方法SD卡的SPI通信接口使其可以通过SPI通道进行数据读写。

从应用的角度来看,采用SPI接口的好处在于,很多单片机内部自带SPI控制器,不光给开发上带来方便,同时也见降低了开发成本。

然而,它也有不好的地方,如失去了SD卡的性能优势,要解决这一问题,就要用SD方式,因为它提供更大的总线数据带宽。

tf卡底层引脚定义

tf卡底层引脚定义TF卡底层引脚定义:TF卡,又称为Micro SD卡,是一种常见的存储设备,广泛应用于移动设备、数码相机等领域。

TF卡底层引脚定义了TF卡与外部设备之间的连接方式和通信规则。

本文将从TF卡底层引脚定义的角度,探讨TF卡的工作原理和应用场景。

一、TF卡底层引脚定义TF卡底层引脚一般包括以下几个引脚:1. VCC:供电引脚,用于提供电源给TF卡,一般连接到3.3V或5V 电源。

2. GND:地引脚,用于连接地线,与外部设备共享地。

3. CLK:时钟引脚,用于传输时钟信号,控制数据的读写。

4. CMD:命令引脚,用于发送读写命令给TF卡。

5. DAT0-DAT3:数据引脚,用于传输数据。

二、TF卡工作原理TF卡是一种闪存存储设备,采用了SPI(Serial Peripheral Interface)或SD(Secure Digital)接口协议。

TF卡通过底层引脚与外部设备进行通信,实现数据的读写和存储。

在TF卡的工作过程中,外部设备首先通过时钟引脚(CLK)发送时钟信号给TF卡,TF卡根据时钟信号进行同步。

然后,外部设备通过命令引脚(CMD)发送读写命令给TF卡,TF卡根据命令进行相应的操作。

同时,外部设备通过数据引脚(DAT0-DAT3)与TF卡进行数据的传输。

TF卡根据命令和数据进行存储或读取操作,并将结果返回给外部设备。

三、TF卡的应用场景TF卡由于其小巧、便携的特点,在各种移动设备和数码产品中得到了广泛应用。

以下是TF卡的几个主要应用场景:1. 手机存储扩展:由于手机内置存储容量有限,用户可以通过插入TF卡来扩展手机的存储空间,方便存储大量的照片、音乐和视频等文件。

2. 数码相机存储:数码相机通常使用TF卡作为存储介质,用户可以将拍摄的照片和视频保存在TF卡中,并通过TF卡读卡器将数据传输到电脑进行编辑和存储。

3. 智能穿戴设备:智能手表、智能眼镜等智能穿戴设备中,也常常使用TF卡作为存储介质,用于存储用户的健康数据、运动轨迹等信息。

电源管理芯片引脚定义

电源管理芯片引脚定义1 VCC 电源管理芯片供电2 VDD 门驱动器供电电压输入或初级控制信号供电源3 VID0-4 CPU与cpu供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

4 RUN SD SHDN EN 不同芯片的开始工作引脚5 PGOOD PG cpu内核供电电路正常工作信号输出6 VTTGOOD cpu外核供电正常信号输出7 UGATE 高端场管的控制信号8 LGATE 低端场管的控制信号9 PHASE 相电压引脚连接过压保护端10 VSEN 电压检测引脚11 FB 电流反馈输入即检测电流输出的大小12 COMP 电流补偿控制引脚13 DRIVE cpu 外核场管驱动信号输出14 OCSET 12v供电电路过流保护输入端15 BOOT 次级驱动信号器过流保护输入端16 VIN cpu外核供电转换电路供电来源芯片连接引脚17 VOUT cpu外核供电电路输出端与芯片连接18 SS 芯片启动延时控制端,一般接电容19 AGND GND PGND 模拟地地电源地20 FAULT 过耗指示器输出,为其损耗功率:如温度超过135.c时由高电平转到低电平指示该芯片过耗.21 SET 调整电流限制输入22 SKIP 静音控制,接地为低噪声23 TON 计时选择控制输入24 REF 基准电压输出25 OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连vcc丧失过压保护功能。

26 FBS 电压输出远端反馈感应输入27 STEER 逻辑控制第二反馈输入28 TIME/ON 5 双重用途定时电容和开或关控制输入29 RESET 复位输出vl-0v跳变,低电平时复位30 SEQ 选择pwm电源电平转换器的次序SEQ接地时5v输出在3.3v之前SEQ 接REF上,3.3v 5v 各自独立SEQ 接vl上时 3.3v输出在5v之前31 RT 定时电阻32 CT 定时电容33 ILIM 电流限制门限调整34 SYNC 振荡器同步和频率选择,150khz操作时,sync连接到gnd 300khz时连接到ref上,用0-5v驱使sync 使频率在340-195khz。

SD卡原理及内部结构

1、简介:SD卡(Secure Digital Memory Card)是一种为满足安全性、容量、性能和使用环境等各方面的需求而设计的一种新型存储器件,SD卡允许在两种模式下工作,即SD模式和SPI模式,本系统采用SPI模式。

本小节仅简要介绍在SPI模式下,STM32处理器如何读写SD卡,如果读者如希望详细了解SD卡,可以参考相关资料。

SD 卡内部结构及引脚如下图所示:SD卡内部图.JPG2、SD卡管脚图:SD卡图.JPG3、SPI模式下SD各管脚名称为:sd 卡:SPI模式下SD各管脚名称为.JPG注:一般SD有两种模式:SD模式和SPI模式,管脚定义如下:(A)、SD MODE 1、CD/DATA3 2、CMD 3、VSS1 4、VDD 5、CLK 6、VSS2 7、DATA0 8、DATA1 9、DATA2(B)、SPI MODE 1、CS 2、DI 3、VSS 4、VDD 5、SCLK 6、VSS2 7、DO 8、RSV 9、RSVSD 卡主要引脚和功能为:CLK:时钟信号,每个时钟周期传输一个命令或数据位,频率可在0~25MHz之间变化,SD卡的总线管理器可以不受任何限制的自由产生0~25MHz 的频率;CMD:双向命令和回复线,命令是一次主机到从卡操作的开始,命令可以是从主机到单卡寻址,也可以是到所有卡;回复是对之前命令的回答,回复可以来自单卡或所有卡;DAT0~3:数据线,数据可以从卡传向主机也可以从主机传向卡。

SD卡以命令形式来控制SD卡的读写等操作。

可根据命令对多块或单块进行读写操作。

在SPI 模式下其命令由6个字节构成,其中高位在前。

SD卡命令的格式如表1所示,其中相关参数可以查阅SD卡规范。

4、MicroSD卡管脚图:MicroSD卡管脚图.JPG5、MicroSD卡管脚名称:MicroSD卡管脚名称.JPGSD 卡与MicroSD卡仅仅是封装上的不同,MicroSD卡更小,大小上和一个SIM卡差不多,但是协议与SD卡相同。

SD卡与TF卡的引脚定义

December 2007 Rev 31/61512 MByte and 1 GByte, 3.3V Supply Secure Digital™ CardFeatures■SD Memory Card Specification Version 1.01-compliant■Up to 1 Gbyte of Formatted Data Storage ■Bus Mode–SD Protocol (1 to 4 Data Lines)–SPI Protocol■Operating Voltage Range:–Basic Communication (CMD0, CMD15, CMD55 and ACMD41): 2.0V to 3.6V–Other C ommands a nd M emory A ccess: 2.7V to 3.6V ■Variable Clock Rate: 0 to 25 MHz ■Read Access (using 4 Data Lines)–Sustained Multiple Block: 6.3 Mb/s ■Write Access (using 4 Data Lines)–Sustained Multiple Block: 3.0 Mb/s ■Maximum Data Rate with up to 10 Cards ■Aimed at Portable and Stationary Applications ■Communication Channel Protocol Attributes:–Six-wire communication channel (clock, command, 4 data lines)–Error-proof data transfer–Single or Multiple block oriented data transfer■Memory Field Error Correction ■Safe Card Removal during Read■Write Protect Feature using Mechanical Switch ■Built-in Write Protection Features (Permanent and Temporary)■SD, MiniSD and MicroSD Packages –ECOPACK ® compliant –Halogen free –Antimony freeMicroSDTable 1.Device summaryPart Number Package Form Factor Operating Voltage RangeSMS128AF SD (full size)2.7V to3.6VSMS256AF SMS512AF SMS01GAF SMS064BF MiniSD SMS128BF SMS064FF MicroSDSMS128FF SMS256FF SMS512FFDescription SMSxxxAF, SMSxxxFF, SMSxxxBF1 DescriptionThe Secure Digital Memory Card (SD Memory Card) is a Flash-Based Memory Card. It is specifically designed to meet the security, capacity, performance and environmentalrequirements of the latest-generation audio and video consumer electronic devices, that is mobile phones, digital cameras, digital recorders, PDAs, organizers, electronic toys, etc. The Secure Digital Memory Card is a high-mobility, high-performance, low-cost and low-power consumption device that features high data throughput at the memory card interface. It includes a copyright protection mechanism that complies with the security of the SDMI (Secure Digital Music Initiative) standard. The Secure Digital Memory Card security system uses mutual authentication and a “cipher algorithm” that protects the card from illegal use. Unsecured access to the user's personal content is also available.The Secure Digital Memory Cards have an advanced communication interface designed to operate in a low voltage range. The full-size Secure Digital Memory Card has a 9-pin interface whereas the Mini Secure Digital Memory Card has a 11-pin interface but can be fitted with a 9-pin adapter. Only the 9-pin interface is described in this document. The MicroSD Memory Card has an 8-pin interface, and can also be fitted with a 9-pin adapter.Table 2,T able 3,Table 4,Table 5, and Table 6 give an overview of the Secure Digital Memory Card features.In order to meet environmental requirements, the devices are offered in ECOPACK ®packages. ECOPACK packages are Lead-free. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.The SD, MiniSD and MicroSD packages are also Halogen free and Antimony free.Related documentation●Secure Digital Memory Card Specifications: Part 1 Physical Layer Specification, Version 1.01●MiniSd Memory Card Specifications: Addendum to SD Memory Card Specifications Part 1 Physical layer Specification, Version 1.02●MicroSD Memory Card Specifications: Addendum to SD Memory Card Specifications Part 1, Physical Layer Specification, Version 1.00Table 2.System performanceSystem performanceMax.Typ.Unit Sleep to Ready30µs Sustained Multiple Block Read (1)1.43X, 20X, 12X and 5X Speed grade markings where 1X = 150 KBytes/s.6.3 (43X)MBytes/s Burst Single Block Read (1) 1.8 (12X)MBytes/s Sustained Multiple Block Write (1) 3.0 (20X)MBytes/s Burst Single Block Write (1)0.8 (5X)MBytes/s Power-up to Ready150msSMSxxxAF, SMSxxxFF, SMSxxxBFDescriptionTable 3.Power consumption (1)1.T A = 25°C, V DD = 3.6V.ModeMax. Current ConsumptionStandby 200 µA Read 30 mA Write30 mATable 4.Environmental specifications (1)1.NA = Not Applicable; RH = Relative Humidity; ESD = ElectroStatic DischargeEnvironmental specifications Operating Non-Operating T emperature− 25°C to 85°C − 40°C to 85°C Humidity (non- condensing)NA 85°C - 85%RHESDProtectionContact PadsNA±4kV , Human body model according to ANSI EOS/ESD-S5.1-1998Other±8kV (coupling plane discharge)±15kV (air discharge) Human body model perIEC61000-4-2Salt Water Spray NA T A = 35 °C 3% NaCl (MIL Std Method 1009)Vibration (peak-to-peak)NA 15 Gmax ShockNA1,000G Drop NA2000GBending20N (middle of the card)20N (border of the card)UV light exposure254nm, 15Ws/cm2Table 5.Physical dimensionsParameter SD MiniSD MicroSD Unit Width 2420 11mmHeight3221.515 mm Thickness 2.1 1.4Inter Connect Area 0.7±0.1mmMax. Card Thickness 0.95 Max. Pull Area1.0±0.1Weight Approx. 2Approx. 1<1g Number of Pins9118N/ADescriptionSMSxxxAF, SMSxxxFF, SMSxxxBFTable 6.System reliability and maintenanceMTBF (1)1.MTBF = Mean Time Between Failures.>1,000,000hrsPreventive Maintenance NoneData Reliability 1 non-recoverable bit in 1014 bit read Endurance>2,000,000 Program/Erase CyclesSMSxxxAF, SMSxxxFF, SMSxxxBF Memory array partitioning2 Memory array partitioningThe basic unit of data transfer to/from the SD Memory Card is the Byte. The memory array is divided into several structures as described below and summarized in Table 17.BlockThe Block is the unit structure related to block-oriented read and write commands. Its size is the number of Bytes that are transferred when a block-oriented read or write command is sent by the host. The SD Memory Card Block size is either programmable or fixed. The information about allowed block sizes and programmability is stored in the CSD Register. The details of the Memory Array Structure and the number of addressable Blocks are shown in T able 17.SectorThe sector is the unit structure related to the erase commands. Its size is the number of blocks that are erased at any one time. The sector size is fixed for each device. The information about the sector size (in blocks) is stored in the CSD register.Write Protect Group (WP-Group)The WP-Group is the smallest structure that may be individually protected. Its size is the number of Sectors that are Write Protected with one bit. The information about the Write Protect Group size is stored in the CSD Register.Table 7.Memory array structuresType of Structure Number of structures in deviceUnit 32 MByte Devices 64 MByte Devices 128 MByte Devices 256 MByte Devices 512 MByte Devices 1 GByte Devices Blocks 512 Bytes 5977612262424832049971210024961999872Sector Block 128128128128128128WP-GroupsSector12481632Memory array partitioning SMSxxxAF, SMSxxxFF, SMSxxxBFSMSxxxAF, SMSxxxFF, SMSxxxBF Secure digital memory card interface3 Secure digital memory card interfaceThis section applies to the full-size SD Memory Card only, or to the MiniSD and MicroSD card when used with an adapter.Details on the 11-pin communication interface of the MiniSD card used without an adapter are still to be announced. Figure 3: MicroSD pin assignment shows the MicroSD pinout.The Secure Digital Memory Card has an advanced 9-pin communication interface (Clock, Command, 4 Data pins and 3 Power Supply pins) designed to operate in a low voltage range. The Secure Digital Card has its nine pins exposed on one side (see Figure 2). The signal/pin assignments are listed in Table 8 The pin types are Power Supply, Input, Output and Push-Pull. The signals include six communication lines CMD, DAT0, DAT1, DAT2, DAT3, CLK and three supply lines V DD , V SS1 and V SS2.Table 8.Full-size SD Memory Card pin assignmentPin #SD modeSPI modeNameType (1)1.S: power supply; I: input; O: output using push-pull drivers; PP: I/O using push-pull drivers.DescriptionName Type Description1CD/DA T3(2)2.The extended DAT lines (DAT1-DAT3) are input on power-up. They start to operate as DAT lines after SET_BUS_WIDTHcommand.I/O/PP (3)3.After power-up this line is input with 50kW pull-up (can be used for card detection or SPI mode selection). The pull-upshould be disconnected by the user, during regular data transfer, with SET_CLR_CARD_DETECT (ACMD42) command.Card Detect / Data Line [Bit 3]CS I Chip Select (active Low)2CMD PP Command/Response DI I Data In3V SS1S Supply voltage ground V SS S Supply voltage ground 4V DD S Supply voltage V DD S Supply voltage 5CLK I ClockSCLK I Clock6V SS2S Supply voltage ground V SS2SSupply voltage ground7DA T0I/O/PP Data Line [Bit 0]DOO/PP Data Out8DA T1(2)I/O/PP Data Line [Bit 1]Reserved 9DA T2(2)I/O/PPData Line [Bit 2]ReservedSecure digital memory card interfaceSMSxxxAF, SMSxxxFF, SMSxxxBFTable 9.MicroSD Contact Pad AssignmentPin SD ModeSPI ModeName Type (1)1.S: power supply; I: input; O: output using push-pull drivers; PP: I/O using push-pull drivers.Description Name TypeDescription1 DA T2 I/O/PP Data Line [Bit 2] RSV Reserved2CD/DA T3(2)2.The extended DAT lines (DAT1-DAT3) are input on power up. They start to operate as DAT lines after SET_BUS_WIDTH command. The Host shall keep its own DAT1-DAT3 lines in input mode, as well, while they are not used. It is defined so, in order to keep compatibility to MultiMediaCards.I/O/PP (3)3.After power up this line is input with 50KOhm pull-up (can be used for card detection or SPI modeselection). The pull-up should be disconnected by the user, during regular data transfer, with SET_CLR_CARD_DETECT (ACMD42) command.Card Detect / Data Line[Bit 3]CSIChip Select (neg true)3 CMD PP Command/Response DI I Data In4 V DDS Supply voltageV DD S Supply voltage 5 CLK I Clock SCLK I Clock 6 V SSSSupply voltage groundV SS SSupply voltage ground7 DA T0 I/O/PP Data Line [B it 0] DOO/PP Data Out8 DA T1RSVReservedSMSxxxAF, SMSxxxFF, SMSxxxBF Secure digital memory card interface3.1 Secure digital memory card bus topologyThe Secure Digital Memory Card system defines two alternative communications protocols:SD and SPI that correspond to two operating modes.Either mode can be selected in the application, mode selection is transparent to the host.The host automatically detects the operating mode of the card by issuing the Resetcommand (refer to Section7.2.1: Mode Selection) and will expect all furthercommunications to use the same mode. Therefore, applications that use only onecommunication mode do not have to be aware of the other.The SD bus includes the following signals:●CLK: Host to card clock signal●CMD: Bi-directional Command/Response signal●DAT0 - DAT3: 4 Bi-directional data signals.●V DD, V SS1, V SS2: Power and ground signals.The SD Memory Card bus has a synchronous star topology (refer to Figure4: Secure DigitalMemory Card system bus topology) with a single master (the application) and multipleslaves (the cards). The Clock, power and ground signals are common to all cards. Thecommand (CMD) and data (DAT0 - DAT3) signals are dedicated to the cards, they providecontinuous point-to-point connection to all the cards.During the initialization process, commands are sent to each card individually, allowing theapplication to detect the cards and assign logical addresses to the physical slots. Data isalways sent (received) to (from) each card individually. However, in order to simplify thehandling of the card stack, after the initialization process, all commands may be sentconcurrently to all cards. Addressing information is provided in the command packet.The SD bus allows dynamic configuration of the number of data lines. After power-up the SDMemory Card defaults to using only DAT0 for data transfer. After initialization the host canchange the bus width (number of active data lines). This feature is an easy trade off betweenhardware cost and system performance.Secure digital memory card interfaceSMSxxxAF, SMSxxxFF, SMSxxxBF1.DAT1 and DAT2 not connected.3.2 SD bus protocolCommunication over the SD bus is based on command and data bit streams which areinitiated by a start bit and terminated by a stop bit.●Command: a command is a token which starts an operation. A command is sent from the host either to a single card (addressed command) or to all connected cards (broadcast command). Commands are transferred serially on the CMD line. See Figure 5: "No Response" and "No Data" operations .The Command token format is shown in Figure 8●Response: a response is a token which is sent from an addressed card, or(simultaneously) from all connected cards, to the host, as an answer to a previously received command. Responses are transferred serially on the CMD line. A response is illustrated in Figure 5: "No Response" and "No Data" operations .The Response token format is shown in Figure 9●Data: data can be transferred from the card to the host or from the host to the card. Data is transferred via the data lines. See Figure 6: (Multiple) Block Read operation for an illustration.The Data Packet format is shown in Figure 10Card addressing is implemented using a session address assigned to the card during the initialization phase (See SD Memory Card Specification, Chapter 4). The basic transaction on the SD bus is the command/response transaction. In this type of bus transactions, the information is directly transferred within the command or response structure. In addition, some operations have a data token. Data transfers to/from the SD Memory Card are done in blocks. Data blocks are always followed by CRC bits.Single and Multiple Block operations are supported. Note that the Multiple Block operation mode improves the speed of write operations. A Multiple Block transmission is terminated by issuing a STOP_TRANSMISSION command on the CMD line (See Figure 6 and Figure 7).Data transfer can be configured by the host to use single or multiple data lines (provided that the card supports this feature).A busy signal on DAT0 is used to indicate that a Block Write operation is ongoing (see Figure7). The same busy signaling is used regardless of the number of data lines used to transfer the data.Response tokens (see Figure9) have four coding schemes depending on their content. The token length is either 48 or 136 bits (See SD Memory Card Specification, Chapter 4.5 for detailed definitions of the commands and responses). The CRC protection algorithm for data block is a 16-bit CCITT polynomial (see SD Memory Card Specification, chapter 4.5). On the CMD line, the MSB bit is transmitted first and the LSB bit last. When the wide bus option is used, the data is transferred 4 bits at a time (refer to Figure10). Start bits, End bits and CRC bits, are transmitted on all the DAT lines used. CRC bits are calculated and checked for every DAT line individually. The CRC status response and Busy indication are sent by the card to the host on DAT0 only (DAT1-DAT3 are Don’t Care).3.3 SD Memory Card Functional DescriptionAll communications between the host and the cards are controlled by the host (master).The host sends commands of two types:●Broadcast commands which are intended for all cards. Some of these commandsrequire a response.●Addressed (point-to-point) commands that are sent to the addressed card and arefollowed by a response from the card.Modes3.4 OperationFigure11 and Figure12 show an overview of the command flow for the Card Identificationmode and the Data Transfer mode, respectively.Table10 shows the relationship between operation modes and card states. Each state in theSD Memory Card state diagram (see Figure16 and Figure17) is associated with oneoperation mode.Table 10.Card States vs. Operation ModesCard state Operation modeInactive State InactiveIdle StateReady StateCard Identification ModeIdentification State3.4.1 Card Identification ModeThe host enters the Card Identification mode after reset and remains in this mode until it hasfinished searching for new cards on the bus.Cards enter the Card Identification mode after reset and remain in this mode until they receive the SEND_RCA command (CMD3) (or the SET_RCA command for MultiMediaCards).While in Card Identification mode the host resets all the cards that are in Card Identification mode, validates the operation voltage range, identifies every card and asks them to publish their Relative Card Addresses (RCA). This operation is done separately for each card on its own CMD line. In this mode, all data communications use the command line (CMD) only.The host starts the card identification process at the identification clock rate f OD . The SD Memory Card has push-pull CMD line output drives.Once the bus has been activated the host asks each card to send their valid operation conditions (ACMD41 preceded by APP_CMD - CMD55 with RCA=0000h).The response to ACMD41 is the Operation Condition Register of the card. The same command is sent to all the new cards in the system. Incompatible cards are switched to Inactive State.The host then issues the ALL_SEND_CID command (CMD2), to every card to get their unique card identification (CID) numbers. All unidentified cards (which are in Ready State) answer by sending their CID numbers (on the CMD line) and switch to the Identification State. Then the host issues a CMD3 (SEND_RELATIVE_ADDR) command to ask the cards to publish a relative card address (RCA). The RCA is shorter than the CID, and will be used to address the card (typically at a clock rate higher than f OD ) once this is in Data Transfer mode. Once the RCA is received the card state changes to Standby. At this point, the host may ask the card to publish another RCA number by sending anotherSEND_RELATIVE_ADDR command to the card. The last published RCA is the actual RCA of the card.The host repeats the identification process, that is the cycles with CMD2 and CMD3, for each card in the system. Once all the SD Memory Cards have been initialized, the host initializes the MultiMediaCards that are in the system (if any) by issuing CMD2 and CMD3 as explained in the MultiMediaCard specification. Note that in the SD system all the cards are connected separately so each MultiMediaCard has to be initialized individually.Stand-by State Data Transfer ModeT ransfer State Sending-data State Receive-data State Programming State Disconnect StateTable 10.Card States vs. Operation Modes (continued)Card stateOperation mode3.4.2 Data Transfer ModeCards enter the Data Transfer mode once their Relative Card Addresses (RCA) have beenpublished.The host enters the Data Transfer mode after identifying all the cards on the bus.The host issues SEND_CSD (CMD9) to obtain the contents of the Card Specific Data (CSD)Register for each card. The CSD Register contains information like the block length and thecard storage.Until the host knows the contents of all the CSD Registers, the f PP clock rate must remain atf OD because some cards may have operating frequency limitations.The broadcast command SET_DSR (CMD4) configures the driver stages of all identifiedcards. It programs their Driver Stage Registers (DSR) according to the application buslayout (length), the number of cards on the bus and the data transfer frequency. The clockrate is changed from f OD to f PP at that point. The SET_DSR command is an option for thecard and the host.CMD7 is used to select one card and switch it to the Transfer State. Only one card can be inTransfer State at a given time. If a previously selected card is still in Transfer State when thehost uses CMD7 to switch another card to the Transfer state, then the connection betweenthe previously selected card and the host is released and the card reverts to the StandbyState.When CMD7 is issued with the reserved relative card address "0000h", all cards revert to the Standby State. This function may be used before identifying new cards, to avoid resetting already registered cards. When in Standby state the cards that already have an RCA do not respond to identification commands (CMD41, CMD2, CMD3).Note that a card is deselected when it receives a CMD7 with an RCA that does not match. Card deselection is automatic if another card in a system is selected and the cards share the same CMD lines.So, in an SD Memory Card system, the host may either have a common CMD line for all SD Memory Cards (in which case card deselection is automatic just like in a MultiMediaCard system) or the host may have separate CMD lines, in which case it must be aware of the necessity of deselecting cards.All data communications in the Data Transfer Mode are point-to point between the host and the selected card (using addressed commands). All addressed commands are acknowledged by a response on the CMD line.The relationships between the various states in the Data Transfer mode are summarized below (see Figure12):●All Data Read commands (CMD17, CMD18, CMD30, CMD56, ACMD51) can beaborted at any time using the Stop command (CMD12). The data transfer will terminate and the card will return to the T ransfer State.●All Data Write commands (CMD24,CMD25, CMD26, CMD27, CMD42, CMD56) can beaborted at any time using the Stop command (CMD12). The write commands must be stopped prior to deselecting the card using CMD7.●As soon as the data transfer has completed, the card switches from the Data Writestate to either the Programming state (if the transfer was successful) or the T ransfer state (if the transfer failed).●If a Block Write operation is stopped and the block length and CRC of the last block arevalid, the data will be programmed.●The card can provide buffering during Block Write. This means that the data to beprogrammed to the next block can be sent to the card while the previous block is being programmed.If all write buffers are full, the DAT0 line will remain Low (BUSY) as long as the card is in the Programming state (see Figure12).●There is no buffering option for Write CSD, Write CID, Write Protection and erase. Thismeans that while the card is busy with any one of these commands, no other Data Transfer command will be accepted. The DAT0 line will remain Low as long as the card is busy and in the Programming state.●Parameter Set commands (CMD16, CMD32, CMD33) are not allowed while the card isprogramming.●Read commands are not allowed while the card is programming.●Switching another card from the Standby to the Transfer state (using CMD7) will notterminate erase and programming operations. The card will switch to the Disconnect state and release the DAT line.● A card in the Disconnect state can be reselected using CMD7. The card will then revertto the Programming state and reactivate the busy signaling.●Resetting a card (using CMD0 or CMD15) will terminate any pending or ongoingprogramming operation. This may result in the loss of card contents. It is up to the host to prevent possible data loss.3.5 CommandsFour types of commands are used to control the SD Memory Card:1.Broadcast commands (bc), no response: The broadcast feature is available only ifall the CMD lines are interconnected at the level of the host. If they are notinterconnected then each individual card will accept the command in turn.2. Broadcast commands with response (bcr): Since there is no Open Drain mode inSD Memory Cards, this type of command is used only if the host does not use acommon CMD line. The command is accepted by every individual Card and theresponses from all cards are sent simultaneously.3. addressed (point-to-point) commands (ac): There is no data transfer on DAT.4. addressed (point-to-point) data transfer commands (adtc): There is a data transferon DAT.All commands have a fixed code length of 48 bits for a transmission time of 2.4µs at 20MHz.All commands and responses are sent over the CMD line of the SD Memory Card.Command transmission always starts with the most significant bit (MSB) of the commandcodeword. All commands are protected by a CRC. All Command codewords are terminatedby the end bit (always '1'). T able11 shows the command format. All commands and theirarguments are specified in the SD Memory Card Specification.Table 11.SD Card Command Format3.6 ResponsesAll responses are sent via the command line CMD. Response transmission always starts with the leftmost bit of the response codeword. The code length depends on the response type. A response always starts with a start bit (always '0'), followed by the bit indicating the direction of transmission (from card = '0').A value denoted by 'X' in T able 12,Table 13,T able 14 and Table 15 indicates a variable entry.All responses (except for R3 Responses) are protected by a CRC. All response codewords are terminated by the end bit (always '1').There are five types of responses. Their formats are defined as follows:1.R1 (normal response command): the code length is 48 bits. Bits 45 to 40 indicate the index of the command to respond to. The index is a binary coded number (between 0 and 63). The status of the card is coded in 32 bits (see Table 12).Note that if data transfer to the card takes place, then a busy signal may appear on the data line after the transmission of each block of data. The host has to check for busy after data block transmission. 2.R1b is identical to R1 with an optional busy signal transmitted on the data line. The card may become busy after receiving these commands, depending on the state it was in prior to receiving the command. The Host has to check for busy in the response.3.R2 (CID, CSD Register): the code length is 136 bits. The contents of the CID Register are sent as a response to the CMD2 and CMD10 commands. The contents of the CSD Register are sent as a response to CMD9. Only the bits [127...1] of the CID and CSD Registers are transferred, the reserved bit [0] of these registers is replaced by the end bit of the response (see Table 13).4. R3 (OCR register): the code length is 48 bits. The contents of the OCR register are sent as a response to ACMD41 (see Section Table 14. on page 25).5.R6 (Published RCA response): the code length is 48 bits. Bits 45 to 40 indicate the index of the command to respond to. In this case it is '000011' (together with bit 5 in the status bits it means = CMD3) as shown in Table 15 The 16 MSB bits of the argument field are used for the Published RCA number.For more details about Response formats, please refer to the SD Memory Card Specification.Bit position 474645:4039:87:10Width 1163271Value '0''1'x x x '1'DescriptionStart bitT ransmissionbitCommand indexArgumentCRC7End bitTable 12.Response R1Table 13.Response R2Table 14.Response R3Table 15.Response R6Bit Position 4746[45:40][39:8][7:1]0Width (bits)1163271Value ‘0’‘0’X X X ‘1’DescriptionStart BitTransmissionBitCommand IndexCard StatusCRC7End BitBit Position 135134[133:128][127:1]0Width (bits)1161271Value ‘0’‘0’‘111111’X ‘1’DescriptionStart BitTransmission BitReservedCID or CSD register incl. internal CRC7End BitBit Position 4746[45:40][39:8][7:1]0Width (bits)1163271Value ‘0’‘0’‘111111’X ‘111111’‘1’DescriptionStart BitTransmissionBitReservedOCR RegisterReservedEnd BitBit Position 4746[45:40][39:8] Argument Field [7:1]0Width (bits)116161671Value ‘0’‘0’X X X X ‘1’DescriptionStart BitT ransmission BitCommand Index (‘000011’)New published RCA [31:16] of the card[15:0] Card Status Bits: 23, 22, 19 and 12 to 0CRC7end bit。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

希望我的回答能帮到你,有想法还有不懂的话,可以问我。我手把手教你!淘宝商城首页:

5[ 标签:卫星电视,指点,poo ] 急啊来高手啊! 匿名 回答:7 人气:11 解决时间:2010-10-21 14:25

满意答案好评率:33% 由于网络共享的兴起,DM机亦在TVRO界风靡。作为一名星友谁都想拥有一台DM,来享受共享节目的刺激与温馨!! DM却具有其可玩性——如果摸透了它的秉性,他就会很温顺,任你在卫视海洋中遨游;如果你对他很陌生,他就是一匹脱缰的野马,难以驾驭。因此,在购买DM前一定要对DM500S进行一些了解,特别要做好有关DM工具、技术储备 一、1、DM500S为欧洲出口机型,采用250 MHz IBM PowerPC 处理器 (350 Mips),机器内安装Linux操作系统,运算速度快,画质清晰,细腻,遥控反应灵敏。接收机机身小巧、时尚,接收机通过安装软件(插件)可以实现支持多系统卡片以及多系统共享(法国电信、爱迪德、Conax等),联接网络稳定,自动连接,可直接在接收上联网下载更新软件!国内目前都是盗版机器,所以物美价廉,但国内盗版的厂商很多,特别是一些没有技术和资金实力的小作坊,生产的机器质量很差,所以买DM500S,一定要找信誉好的商家,千成不能通过淘宝随便拍下一台价格低的机器! 2、共享,打个简单的比喻,就是我买一张卫星解密正版卡,通过电脑把卡片读出来,再通过网络,把我的解密数据传输到你的DM500S机器里,你也就和我一样,可以把加密的卫星节目解密出来,和我一样看几百个加密节目!所以如果要买DM500S机器,你必须有互联网,否则只能看几十个免费的节目,因为只用来发送密码数据,所以占用的带宽很小,但网络必须是通的。除了要有互联网,你还得有卫星天线(俗称小锅子,0。45米大就OK)和高频头,才可以从卫星上接收卫星电视节目!这里有一个问题必须要搞清楚,什么是一次共享,什么是二次共享,一次共享,就是做服务器的,每一个卫星解密,自已都会有解密卡片,如果买的是一次共享,那么你的DM500S就能直接登读到这个服务器上读取解密数据,所以速度快,延时小,稳定,换台快,有绝对的控制权,基本无风险(因为买了很多正版解密卡,投资很大)。如果是二次共享,就是说,做共享的人,自已没有一张卫星电视解密卡,他的服务器是转接了做一次共享的服务器数据,只需要交给做一次共享几千元在家里通过ADSL就可以搞定,所以如果是买了二次共享,那你的DM500S机器就要先登陆到二次共享服务器,再通过二次服务器登陆到一次共享服务器才可以取到解密数据,这样读取密码的速度就会慢,因为要经过两个网段,所以延时也大,在数据传输中,延时太大,就会有数据丢失,所以也会不稳定,换台也就慢,也没有控制权,如果一次共享服务器为了保证自已服务器的稳定,可以随时把二次共享的服务器断开。还有一些奸商,因为做二次共享服务器的投资小,所以只做两三个月,赚到钱,就会把服务器关掉,再找不到人!所以买共享,一定要买有可靠售后保证的信誉高的做一次共享的商家,如果买了不稳定的二次共享,看电视就变成受罪,看一秒停三秒,白白浪费了钱!还有一些奸商,为了抢客户,会提供测试帐号,在你测试时,会给你一个一次共享帐号,可以看几天,也稳定,等你交了钱,就会给你二次共享帐号。做一次共享服务器的,一般是不提供测试的!因为测试会把服务器地址和端口暴露给测试的人,随之带来被攻击的可能性。 3、DM500S还有一些原来所有接收机都无法实现的功能,比如:只要家里有一台DM500S,电脑里只要装一个软件,你家里的所有电脑也可以很流畅的看到卫星电视节目,还可以把你喜欢的节目录下来,这都是通过一个免费的软件就可以实现,不再需要投入任何设备。4、但DM500S也有一个不足,就是接上黑白电视机,是不会有图像的,所以用小黑白电视机调信号的朋友要注意了。 二、DM500S通过共享解密,能看些什么节目:以目前最热门的卫星138度KU波段为例,可以收到以下节目: 138度卫星可以共享收看的节目(近120个频道,高清析度,DVD画质,24小时播出)三、DM500S的选购必读 经烧机24小时后,以出售的出口型稳定版DM500S与目前市场上的小作坊机器及全冠无光纤机器相比: 卫星电视,接收机,430,HBO1、不出现死机的现像(小作坊机器有);2、没有出现声音图像不同步的情况(小作坊机器会有) 3、没有出现视频卡死的情况(换台后正常,全冠改版无光纤机有) 4、关机后没有出现冷开机没反应情况 6、四切一支持良好,目前用的ALPS高频头多为二手或拆机货,四切一都有问题 7、

6 Css2 S 地

7 DAT0 I/O/PP 数据位0

8 DAT1PP 数据位2

我的卫星电视(俗称小锅)一个台都没,一开机就是POO检测信号,信号强度还不到25%这是杂回事,望高手指点下,急啊!

SD卡引脚定义:

针脚 名称 类型 描述

1 CD DAT3 I/O/PP 卡监测数据位3

2 CMD PP 命令/回复

3 Vss S 地

4 Vcc S 供电电压

5 CLK I 时钟