蔡觉平老师,verilog上机作业

Verilog HDL数字集成电路设计原理与应用 作者 蔡觉平_ 第1章

HDL语言发展至今,产生了很多种对于数字集成电路 的描述性设计语言,并成功地应用于设计的各个阶段(建模、 仿真、验证和综合等)。20世纪80年代至今,已出现了上百 种硬件描述语言,它们对设计自动化起到了极大的促进和 推动作用,主要有Gateway Design Automation公司提出的 Verilog HDL、美国国防部高级研究计划局(DARPA)设计的 VHDL、美国国防部RPASSP(Rapid Prototyping of Application Specification Signal Processing)计划提出的基于 18 面向对象的OO VHDL(Object Oriented VHDL)、美国杜克 大学的DE VHDL(Duke Extended VHDL)

第1章 Verilog HDL数字集成电路 设计方法概述

➢1.1 数字集成电路的发展和设计方法的演变

➢ 1.2 硬件描述语言

➢1.3 Verilog HDL的发展和国际标准

➢1.4 Verilog HDL和VHDL

➢1.5 Verilog HDL在数字集成电路设计中的优点

➢1.6 功能模块的可重用性

20世纪80年代(第二次变革时期)是标准工艺加工线 (Foundry)公司与IC设计公司共同发展的阶段,主流产品是 MPU、微控制器(Micro Control Unit,MCU)及专用 IC(Application-Specific IC,ASIC)。这时,Foundry和IC设 计公司相结合的方式开始成为集成电路产业发展的新模式。 这一时期,IC产业开始进入以客户为导向的阶段。首先, 标准化功能的IC已难以满足整机客户对系统成本、可靠性 等的要求;其次,由于小尺寸加工技术的进步,软件的硬 9 件化已成为可能,超大规模集成电路(Very Large Scale Integrated,VLSI)开始成为主流芯片;

Verilog练习参考答案

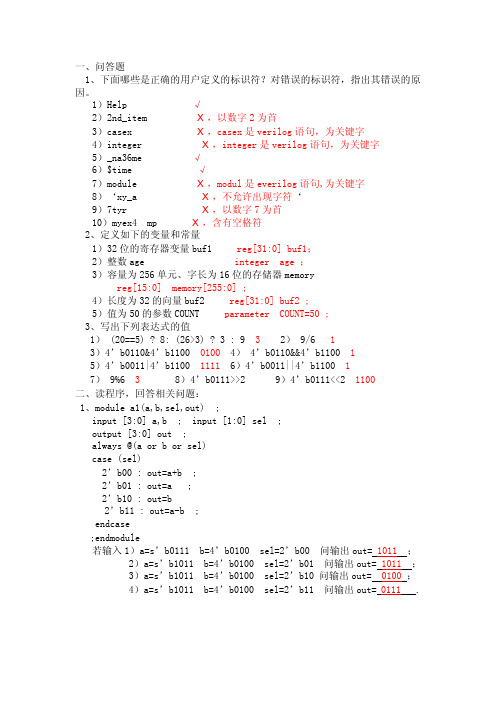

一、问答题1、下面哪些是正确的用户定义的标识符?对错误的标识符,指出其错误的原因。

1)Help √2)2nd_item Χ,以数字2为首3)casex Χ,casex是verilog语句,为关键字4)integer Χ,integer是verilog语句,为关键字5)_na36me √6)$time √7)module Χ,modul是everilog语句,为关键字8)‘xy_a Χ,不允许出现字符‘9)7tyr Χ,以数字7为首10)myex4 mp Χ,含有空格符2、定义如下的变量和常量1)32位的寄存器变量buf1 reg[31:0] buf1;2)整数age integer age ;3)容量为256单元、字长为16位的存储器memoryreg[15:0] memory[255:0] ;4)长度为32的向量buf2 reg[31:0] buf2 ;5)值为50的参数COUNT parameter COUNT=50 ;3、写出下列表达式的值1) (20==5) ? 8: (26>3) ? 3 : 9 3 2) 9/6 13)4’b0110&4’b1100 0100 4) 4’b0110&&4’b1100 15)4’b0011|4’b1100 1111 6)4’b0011||4’b1100 17) 9%6 3 8)4’b0111>>2 9)4’b0111<<2 1100二、读程序,回答相关问题:1、module a1(a,b,sel,out) ;input [3:0] a,b ; input [1:0] sel ;output [3:0] out ;always @(a or b or sel)case (sel)2’b00 : out=a+b ;2’b01 : out=a ;2’b10 : out=b2’b11 : out=a-b ;endcase;endmodule若输入1)a=s’b0111 b=4’b0100 sel=2’b00 问输出out= 1011;2)a=s’b1011 b=4’b0100 sel=2’b01 问输出out= 1011;3)a=s’b1011 b=4’b0100 sel=2’b10 问输出out= 0100;4)a=s’b1011 b=4’b0100 sel=2’b11 问输出out= 0111 .2timescale 100ns/10nsmodule gete2( a,b,out) ;input a,b ;output out ;and # (10.46, 5.87) (z,a,b) ;nor # (9.49,5.37) (out,z,a) ;endmodule问:仿真时,当输入a、b从11变到01时,则输出out如何变化?相对a的变化,out的变化延时多少时间?延时1540ns3、module a2( clk,clr,set,a, z) ;input a,clk,clr ;output reg z ;reg[3:0] q ;always @(posedge clk or posedge clr)begin if (clr) q<=4’b0 ;else if (set) q<=4`hf ; else begin q<<1 ; q[0]<=a; end endassign z=q[3] ;endmodule试判断该逻辑电路的逻辑功能;若输入信号set、clr、clk、a的波形如下,试画出输出4、结构描述电路如下,请画出其逻辑电路。

verilog代码练习题

verilog代码练习题Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

在学习和掌握Verilog代码编写的过程中,练习题是非常重要的一环。

通过多做一些练习题,可以提高对Verilog语言的理解和运用能力,进而更好地应对实际的电路设计和开发项目。

本文将介绍一些常见的Verilog代码练习题,帮助读者提升自己的编程能力。

具体的练习题如下:练习题一:整数加法器设计一个4位整数加法器,输入两个4位的二进制整数A和B,输出它们的和。

请使用Verilog代码描述该加法器,并给出仿真结果和波形图。

练习题二:时钟分频器设计一个时钟分频器,将输入时钟信号分频为两个输出时钟信号。

其中,输出时钟信号A频率为输入时钟信号的一半,输出时钟信号B 频率为输入时钟信号的四分之一。

请使用Verilog代码描述该时钟分频器,并给出仿真结果和波形图。

练习题三:数字比较器设计一个4位数字比较器,输入两个4位的二进制整数A和B,输出A是否大于B的结果(1表示大于,0表示不大于)。

请使用Verilog代码描述该数字比较器,并给出仿真结果和波形图。

练习题四:有限状态机设计一个简单的有限状态机,实现一个计数器的功能。

输入信号CLK表示时钟信号,每个上升沿计数器加1,输出信号OUT表示计数器的值,初始值为0,最大值为9,超出后回到0。

请使用Verilog代码描述该有限状态机,并给出仿真结果和波形图。

练习题五:位宽可调的加法器设计一个位宽可调的加法器,输入为两个任意位宽的二进制整数A和B,输出为它们的和。

请使用Verilog代码描述该位宽可调的加法器,并给出仿真结果和波形图。

以上是几个常见的Verilog代码练习题,通过多做这些练习题,可以提高对Verilog语言的掌握和运用能力。

在实际的电路设计和开发中,良好的Verilog编程能力是非常重要的。

希望本文对你有所帮助,加油!。

蔡觉平老师西电VerilogHDL上机大作业硬件描述语言_微电子学院

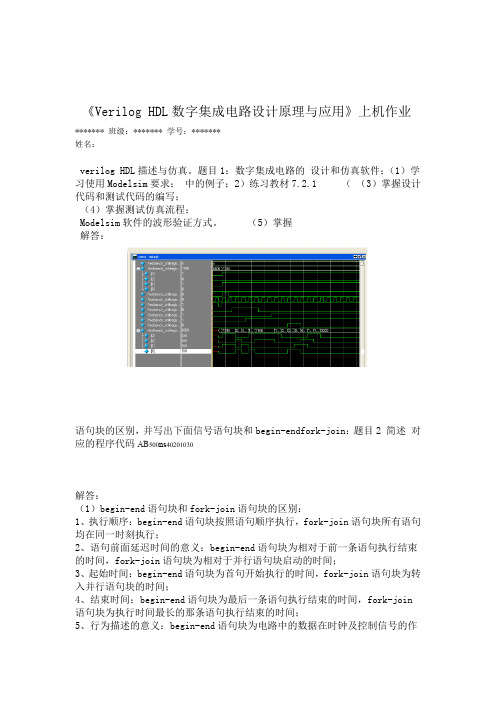

《Verilog HDL数字集成电路设计原理与应用》上机作业******* 班级:******* 学号:*******姓名:verilog HDL描述与仿真。

题目1:数字集成电路的设计和仿真软件;(1)学习使用Modelsim要求:中的例子;2)练习教材7.2.1 ((3)掌握设计代码和测试代码的编写;(4)掌握测试仿真流程;Modelsim软件的波形验证方式。

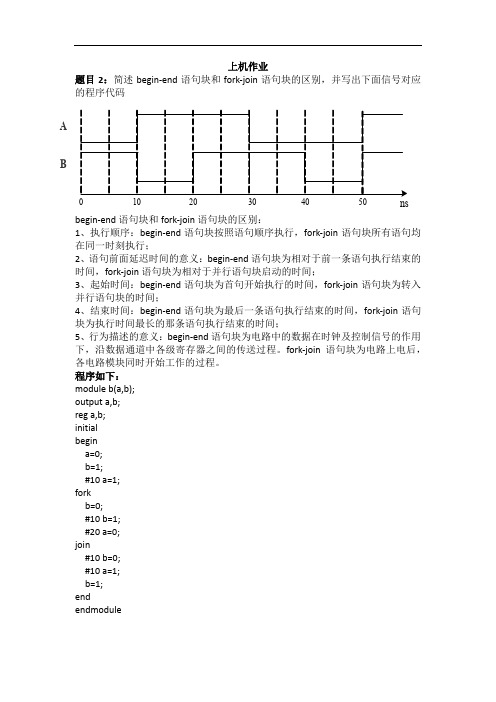

(5)掌握解答:语句块的区别,并写出下面信号语句块和begin-endfork-join:题目2 简述对应的程序代码AB500ns40201030解答:(1)begin-end语句块和fork-join语句块的区别:1、执行顺序:begin-end语句块按照语句顺序执行,fork-join语句块所有语句均在同一时刻执行;2、语句前面延迟时间的意义:begin-end语句块为相对于前一条语句执行结束的时间,fork-join语句块为相对于并行语句块启动的时间;3、起始时间:begin-end语句块为首句开始执行的时间,fork-join语句块为转入并行语句块的时间;4、结束时间:begin-end语句块为最后一条语句执行结束的时间,fork-join 语句块为执行时间最长的那条语句执行结束的时间;5、行为描述的意义:begin-end语句块为电路中的数据在时钟及控制信号的作用下,沿数据通道中各级寄存器之间的传送过程。

fork-join语句块为电路上电后,各电路模块同时开始工作的过程。

(2)程序代码:Begin-end语句:module initial_tb1;reg A,B;initialbeginA=0;B=1;#10 A=1;B=0;#10 B=1;#10 A=0;#10 B=0;#10 A=1;B=1;endendmoduleFrk-join语句:module wave_tb2;reg A,B;parameter T=10;initialforkA=0;B=1;#T A=1;B=0;#(2*T) B=1;#(3*T) A=0;#(4*T) B=0;#(5*T) A=1;B=1;joinendmodule3. 分别用阻塞和非阻塞赋值语句描述如下图所示移位寄存器的电路图。

verilog硬件描述语言上机

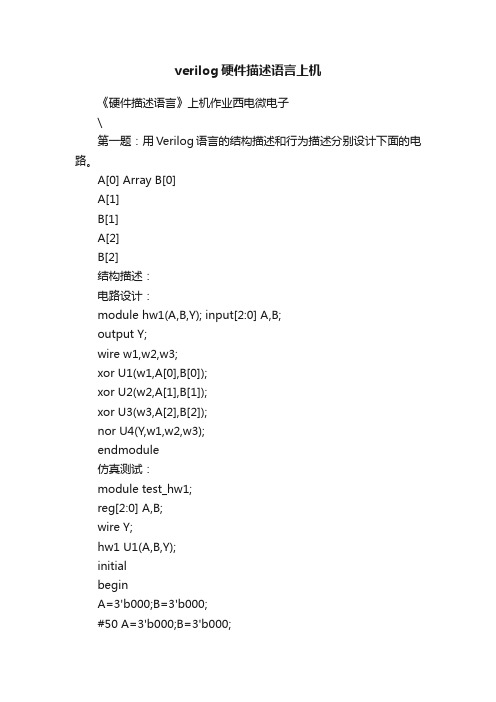

verilog硬件描述语言上机《硬件描述语言》上机作业西电微电子\第一题:用Verilog语言的结构描述和行为描述分别设计下面的电路。

A[0] Array B[0]A[1]B[1]A[2]B[2]结构描述:电路设计:module hw1(A,B,Y); input[2:0] A,B;output Y;wire w1,w2,w3;xor U1(w1,A[0],B[0]);xor U2(w2,A[1],B[1]);xor U3(w3,A[2],B[2]);nor U4(Y,w1,w2,w3);endmodule仿真测试:module test_hw1;reg[2:0] A,B;wire Y;hw1 U1(A,B,Y);initialbeginA=3'b000;B=3'b000;#50 A=3'b000;B=3'b000;#50 A=3'b111;B=3'b111;#50 A=3'b000;B=3'b110;#50 A=3'b111;B=3'b000;#50 A=3'b110;B=3'b110;#50 A=3'b011;B=3'b010;#50 A=3'b001;B=3'b011;#50 A=3'b111;B=3'b010;#50 $stop;endinitial $monitor($time,"\tA=%d\tB=%d\tY=%d",A,B,Y); Endmodule行为描述:电路设计:module hw2(A,B,Y);input[2:0] A,B;output Y;wire Y;assign Y=~((A[0]^B[0])||(A[1]^B[1])||(A[2]^B[2])); endmodule 仿真测试:module test_hw2;reg[2:0] A,B;wire Y;hw2 U1(A,B,Y);initialbeginA=3'b000;B=3'b000;#50 A=3'b000;B=3'b000;#50 A=3'b111;B=3'b111;#50 A=3'b000;B=3'b110;#50 A=3'b111;B=3'b000;#50 A=3'b110;B=3'b110;#50 A=3'b011;B=3'b010;#50 A=3'b001;B=3'b011;#50 A=3'b111;B=3'b010;#50 $stop;endinitial $monitor($time,"\tA=%b\tB=%b\tY=%b",A,B,Y); endmodule第二题:参数化电路设计1. 用行为描述方式实现下图所示的具有“one -hot”(独热)状态的环形计数器。

数字电子技术基础Verilog语言编程设计习题

数字电子技术基础Verilog语言编程设计习题Verilog语言是数字电子技术中广泛应用的硬件描述语言,本文将介绍一些基础的Verilog编程设计习题。

通过完成这些习题,读者能够加深对数字电子技术和Verilog语言的理解,并提高Verilog编程的能力。

一、多输入多输出逻辑门设计习题1. 设计一个四位全加器,实现任意两个四位二进制数的相加运算功能。

module full_adder(input [3:0] A,input [3:0] B,input Cin,output [3:0] S,output Cout);wire [3:0] sum;assign sum[0] = A[0] ^ B[0] ^ Cin;assign sum[1] = A[1] ^ B[1] ^ (A[0] & B[0]) ^ Cin;assign sum[2] = A[2] ^ B[2] ^ (A[1] & B[1]) ^ (A[0] & B[0]) ^ Cin;assign sum[3] = A[3] ^ B[3] ^ (A[2] & B[2]) ^ (A[1] & B[1]) ^ (A[0] & B[0]) ^ Cin;assign S = sum;assign Cout = (A[3] & B[3]) ^ (A[2] & B[2]) ^ (A[1] & B[1]) ^ (A[0] & B[0]) ^ Cin;endmodule2. 设计一个八位比较器,判断两个八位二进制数是否相等。

module comparator(input [7:0] A,input [7:0] B,output EQ);wire [7:0] difference;assign difference = A ^ B;assign EQ = (difference[7] | difference[6] | difference[5] | difference[4] | difference[3] | difference[2] | difference[1] | difference[0])==0;endmodule二、时序逻辑电路设计习题1. 设计一个六位计数器,实现每秒钟加一功能。

Verilog习题

Verilog习题一.简答题1.电子电路CAD的基本含义是什么?2.利用Protel99进行原理图设计的基本步骤有那些?3.归纳总结,Protel99中,画线、画图工具有什么区别?4.两个节点通过哪些方法可以实现电气连接?5.网单文件中包含哪些内容?6.在Protel99的PCB中,有那些主要板层,作用分别是什么?7.PCB元件布局时应遵守那些原则?8.采用CPLD/FPGA设计复杂数字逻辑的一般流程是什么?9.论述构成数字系统的基本组成部分有哪些,作用如何?a)数字系统是指能进行数字信号的处理、存储、传输,完成某一特定功能的数字电路和软件系统的总和。

如计算机。

b)数字系统硬件主要由各种不同功能的组合逻辑(编码/译码等)和时序逻辑电路(计数器/寄存器/状态计)组合而成。

c)系统硬件单元有:(1)CPU:主控单元(2)RAM:内部数据存储、交换(3)输入输出设备,通信接口:输入指令、输出结果d)软件有:(1)操作系统:完整软件系统(2)嵌入式系统:简化的操作系统(3)监控程序:实现简单功能的循环程序10.论述数字逻辑EDA设计的一般流程是什么?系统任务——> 模块划分——> 图形或HDL行为语言描述——> 逻辑前仿真——> 综合——> 综合后仿真——> 布局布线——> 后仿真——> 下装ASIC11.举例说明流水线工作原理a)所谓流水线就是指把大规模、层次多,延时大的组合逻辑电路分为几个级,在每一级接入寄存器,暂存中间数据,从而增加数据处理能力得方法。

b)K级流水线就是在功能逻辑输入输出间恰好有K组寄存器,上一级输出是下一个输入c)流水线增加了数据吞吐量,带来了首位数据时间延迟,增加了KT.15.综述:Pspice可以进行那些分析,其作用如何?16.综述:pspice的信号源有那些类型,语法如何描述?17.FPGA内部逻辑单元的基本组成是什么?18.说出三个以上世界知名EDA公司的名称和主要产品。

verilog上机指导书

“Verilog硬件描述语言”课程上机指导书程军2007-3第1次上机(2学时):1. ModelSim概览ModelSim仿真软件是由MentorGraphic公司的子公司Model技术公司开发的工业界上最为通用的仿真器之一,它可以用于Verilog仿真,VHDL仿真或者两者的混合仿真。

ModelSim仿真软件产品的类型很多,我们在这里要介绍的是ModelSim/SE,它是ModleSim主要的版本,功能最为强大,包含了ModelSim/PLUS的所有功能及其附加功能。

ModelSim/SE随着时间的推移不断地推出新的版本,我们要介绍的是Mentor Graphis公司于2005年6月推出的ModelSim/Se 6.1版本的使用。

首先要准备本实验教程的实验数据,请每个同学将目录/cad/Labs/mentor/modelsim/下的的modelsimLab文件夹(内部包含lab1、lab2、lab3、lab4四个文件夹)复制到自己的home目录下你新建的自己名字的目录内。

执行以下命令:unix%cd ~ unix%mkdir yourname unix%cd /cad/Labs/mentor/modelsim unix%cp -r modelsimLab ~/yourname unix%cd ~/yourname/modelsimLab/lab1 输入fpga.setup命令,然后输入vsim命令,便可以得到图1.1所示的ModelSim图形用户界面。

fpga.setup命令是为了设置环境变量,在每一个要运行modelsim的Terminal中只要执行一次。

unix%fpga.setup unix%vsim2. 基本的使用步骤ModelSim 有三种实现方法。

第一种是交互式的命令行,这种操作方法没有用户界面,唯一的界面是控制台的命令行。

第二种是用户界面(UI),它能够接收菜单输入和命令行输入。

Verilog数字系统设计教程第二版课后练习题含答案

Verilog数字系统设计教程第二版课后练习题含答案练习题1:IGT上的闪光灯设计一个闪光灯电路,该电路使用维托吞尔(Vitold Kern)的交替时间生成器(IGT)控制LED的开关。

闪光灯的频率为每秒2次,LED的工作周期为2ms。

解答module flash(input clk,output reg led);reg[10:0] cnt;// 11 bit counteralways@(posedge clk)begincnt <= cnt +1;endalways@(posedge cnt[10])beginled <=~led;endendmodule练习题2:7段数码管设计一个数字系统,在7段数码管上显示0到9。

解答module seven_segment(input[3:0] digit,output reg[6:0] sseg);parameter COMMON_ANODE =0;// COMMON_ANODE = 1 for commo n anode displayalways@(*)begincase(digit)4'h0: sseg =7'b100_0000;4'h1: sseg =7'b111_1001;4'h2: sseg =7'b010_0100;4'h3: sseg =7'b011_0000;4'h4: sseg =7'b001_1001;4'h5: sseg =7'b001_0010;4'h6: sseg =7'b000_0010;4'h7: sseg =7'b111_1000;4'h8: sseg =7'b000_0000;4'h9: sseg =7'b001_1000;default: sseg =7'b111_1111;endcaseif(COMMON_ANODE ==0)beginsseg =~sseg;endendendmodule练习题3:模数计数器设计一个二进制数模数计数器,输出分别为0到3的二进制数。

Verilog HDL数字集成电路设计原理与应用 作者 蔡觉平_ 第2章

字,它是Verilog HDL语言内部的专用词,是事先定义好的 确认符,用来组织语言结构。用户不能随便使用这些关键

字。需注意的是,所有关键字都是小写的。例如,

ALWAYS不是关键字,它只是标识符,与always(关键字) 是不同的。表2.1-1所示为Verilog HDL的常用关键字。 11

2.1.1 空白符

空白符包括空格符(\b)、制表符(\t)、换行符和换页符。

空白符使代码看起来结构清晰,阅读起来更方便。在编译 和综合时,空白符被忽略。

Verilog HDL程序可以不分行,也可以加入空白符采用

多行编写。

4

例2.1-1 空白符使用示例。

initial begin a = 3'b100; b = 3'b010; end

表2.1-1 Verilog HDL中的常用关键字

always and assign attribute begin buf bufif0 bufif1 case casex casez cmos deassign end endattribute endcase endmodule endfunction endprimitive endspecify endtable endtask event for force forever fork function highz0 highz1 if initial inout input integer join large macromodule medium module nand negedge nmos nor not notif0 notif1 or output parameter pmos posedge primitive pull0 pull1 pullup pulldown rcmos real realtime reg release repeat rtran rtranif0 rtranif1 scalared signed small specify specparam strength strong0 strong1 supply0 supply1 table task time tran tranif0 tranif1 tri tri0 tri1 triand trior trireg unsigned vectored wait wand weak0 weak1 while wire wor xnor xor

eda verilog HDL上机考试

EDA上机考试题目及考试说明

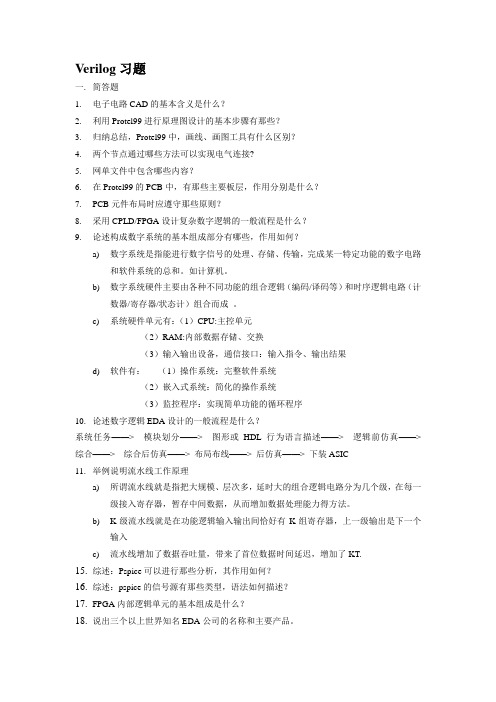

第一部分基础题(计数器)必须抽取一道

1.设计一个具有异步清零,同步使能,同步置数功能的60进制(0~59)的BCD 码输出的计数器;

2.设计一个具有异步清零,同步使能,同步置数功能的24进制(0~23)的BCD 码输出的计数器;

3.设计一个具有异步清零,同步使能,同步置数功能的50进制(0~49)的BCD 码输出的计数器;

4.设计一个四位二进制计数器,要求具有异步清零,同步使能,同步置数功能;5.设计一个三位二进制计数器,要求具有异步清零,同步使能,同步置数功能;

第二部分基础题(译码器)必须抽取一道

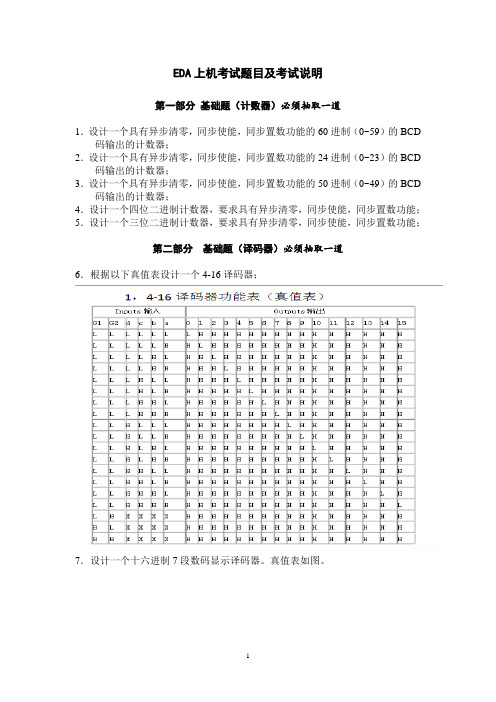

6.根据以下真值表设计一个4-16译码器;

7.设计一个十六进制7段数码显示译码器。

真值表如图。

8.根据以下真值表设计一个3-8译码器

第三部分基础题(其他)必须抽取一道

9.设计一个4选1的多路数据选择器;

10.设计一个4位全加器,要求有输入进位cin和输出进位cout;

11.设计一个分频器,实现分频比为10的设计。

12.设计一个分频器,实现分频比为8的设计。

13.设计一移位寄存器,实现移位模式可控的8位移位,包含带进位循环左移,自循环左移,带进位循环右移,自循环右移。

14.利用循环语句设计一个4位乘法器设计。

15.利用if-else语句设计8-3优先编码器。

蔡觉平老师,verilog上机作业解析

上机作业题目2:简述begin-end 语句块和fork-join 语句块的区别,并写出下面信号对应的程序代码begin-end 语句块和fork-join 语句块的区别:1、执行顺序:begin-end 语句块按照语句顺序执行,fork-join 语句块所有语句均在同一时刻执行;2、语句前面延迟时间的意义:begin-end 语句块为相对于前一条语句执行结束的时间,fork-join 语句块为相对于并行语句块启动的时间;3、起始时间:begin-end 语句块为首句开始执行的时间,fork-join 语句块为转入并行语句块的时间;4、结束时间:begin-end 语句块为最后一条语句执行结束的时间,fork-join 语句块为执行时间最长的那条语句执行结束的时间;5、行为描述的意义:begin-end 语句块为电路中的数据在时钟及控制信号的作用下,沿数据通道中各级寄存器之间的传送过程。

fork-join 语句块为电路上电后,各电路模块同时开始工作的过程。

程序如下: module b(a,b); output a,b; reg a,b; initial begin a=0; b=1; #10 a=1; fork b=0; #10 b=1; #20 a=0; join#10 b=0; #10 a=1; b=1; endendmoduleA B题目3.分别用阻塞和非阻塞赋值语句描述如下图所示移位寄存器的电路图。

D Q D Q dinclk D Q D Qout3out2out1out0程序如下:module block1(din,clk,out0,out1,out2,out3); input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout3=out2;out2=out1;out1=out0;out0=din;endendmodulemodule non_block1(din,clk,out0,out1,out2,out3); input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout0<=din;out1<=out0;out2<=out1;out3<=out2;endendmodule题目4:设计16位同步计数器要求:(1)分析16位同步计数器结构和电路特点;(2)用硬件描述语言进行设计;(3)编写测试仿真并进行仿真。

Verilog设计练习十例及答案

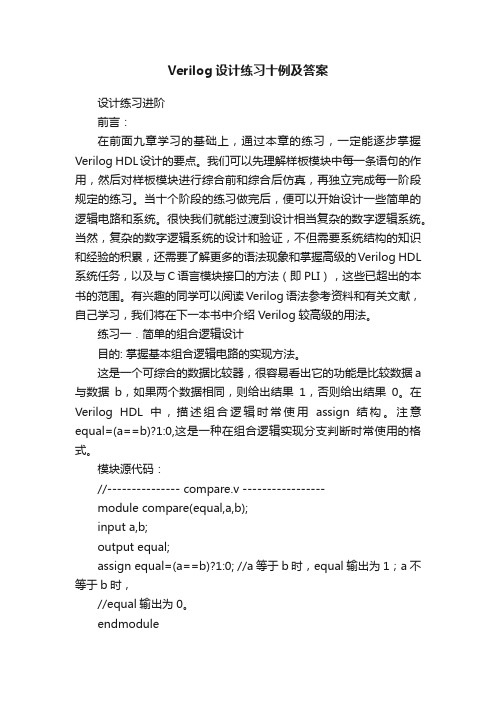

Verilog设计练习十例及答案设计练习进阶前言:在前面九章学习的基础上,通过本章的练习,一定能逐步掌握Verilog HDL设计的要点。

我们可以先理解样板模块中每一条语句的作用,然后对样板模块进行综合前和综合后仿真,再独立完成每一阶段规定的练习。

当十个阶段的练习做完后,便可以开始设计一些简单的逻辑电路和系统。

很快我们就能过渡到设计相当复杂的数字逻辑系统。

当然,复杂的数字逻辑系统的设计和验证,不但需要系统结构的知识和经验的积累,还需要了解更多的语法现象和掌握高级的Verilog HDL 系统任务,以及与C语言模块接口的方法(即PLI),这些已超出的本书的范围。

有兴趣的同学可以阅读Verilog语法参考资料和有关文献,自己学习,我们将在下一本书中介绍Verilog较高级的用法。

练习一.简单的组合逻辑设计目的: 掌握基本组合逻辑电路的实现方法。

这是一个可综合的数据比较器,很容易看出它的功能是比较数据a 与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使用assign 结构。

注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

模块源代码://--------------- compare.v -----------------module compare(equal,a,b);input a,b;output equal;assign equal=(a==b)?1:0; //a等于b时,equal输出为1;a不等于b时,//equal输出为0。

endmodule测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。

测试模块源代码:`timescale 1ns/1ns //定义时间单位。

`include "./compare.v" //包含模块文件。

数字系统设计与VerilogHDL课后习题

数字系统设计与VerilogHDL课后习题习题11.1现代EDA技术的特点有哪些?1.2什么是T op-down设计方式?1.3数字系统的实现方式有哪些?各有什么优缺点?1.4什么是IP复用技术? IP核对EDA技术的应用和发展有什么意义?1.5用硬件描述语言设计数字电路的优势是什么?1.6结合自己的使用情况谈谈对EDA工具的认识。

1.7基于FPGA/CPLD的数字系统设计流程包括哪些步骤?1.8什么是综合?常用的综合工具有哪些?1.9功能仿真与时序仿真有什么区别?1.10 FPGA与ASIC在概念上有什么区别?习题22.1 PLA和PAL在结构上有什么区别?2.2说明GAL的OLMC有什么特点,它怎样实现可编程组合电路和时序电路?2.3简述基于乘积项的可编程逻辑器件的结构特点。

2.4基于查找表的可编程逻辑结构的原理是什么?2.5基于乘积项和基于查找表的结构各有什么优点?2.6 CPLD和FPGA在结构上有什么明显的区别?各有什么特点?2.7 FPGA器件中的存储器块有何作用?2.8 Altera的MAX II器件是属于CPLD还是FPGA,请查阅有关资料并进行分析。

2.9边界扫描技术有什么优点?2.10说说JTAG接口都有哪些功能。

2.11 FPGA/CPLD器件未来的发展趋势有哪些?习题44.1 用Verilog设计一个8位加法器,进行综合和仿真,查看综合和仿真结果。

4.2 用Verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真,查看综合和仿真结果。

4.3用Verilog设计一个模60的BCD码计数器,进行综合和仿真,查看综合和仿真结果。

习题66.1阻塞赋值和非阻塞赋值有什么本质的区别?6.2用持续赋值语句描述一个4选1数据选择器。

6.3用行为语句设计一个8位计数器,每次在时钟的上升沿,计数器加1,当计数器溢出时,自动从零开始重新计数。

计数器有同步复位端。

6.4设计一个4位移位寄存器。

Verilog HDL数字集成电路设计原理与应用 作者 蔡觉平 第3章

1. 显式连续赋值语句

显式连续赋值语句的语法格式如下:

<net_declaration><range><name>; assign #<delay><name>= Assignment expression;

这种格式的连续赋值语句包含两条语句:第一条语句

是对连线型变量进行类型说明的语句;第二条语句是对这 个连线型变量进行连续赋值的赋值语句。赋值语句是由关 键词assign引导的,它能够用来驱动连线型变量,而且只能 5 对连线型变量进行赋值,主要用于对wire型变量的赋值。

计数字电路更类似于使用一些高级语言(如C语言)进行编程,

17 而且Verilog HDL行为级建模的语法结构与C语言也非常相 似。Verilog HDL提供了许多行为级建模语法结构,为设计 者的使用提供了很大的灵活性。

行为描述常常用于复杂数字逻辑系统的顶层设计中,

也就是通过行为建模把一个复杂的系统分解成可操作的若

end initial过程块在进行仿真时从模拟0时刻开始执行,它

在仿真过程中只执行一次,在执行完一次后该initial过程块

就被挂起,不再执行。如果一个模块中存在多个initial过程 块,则每个initial过程块都是同时从0时刻开始并行执行的。

initial过程块内的多条行为语句可以是顺序执行的,也可以

图3.2-1 Verilog HDL行为描述中模块的构成框架

表3.2-1 Verilog HDL行为描述语句及其可综合性

类 别 过程语句 initial always 串行语句块 begin-end 并行语句块 fork-join 连续赋值语句 assign 过程赋值语句=、<= if-else case,casez,casex forever 循环语句 repeat while for `define 编译向导语句 `include `ifdef,`else,`endif √ √ √ √ √ √ √ √ √ 语 句 可综合性

verilog hdl 习题答案

verilog hdl 习题答案Verilog HDL 习题答案Verilog HDL(硬件描述语言)是一种用于描述数字电路的硬件描述语言,它被广泛应用于数字系统的设计和验证。

在学习Verilog HDL的过程中,练习题是非常重要的,通过解答习题可以加深对Verilog HDL语言的理解,并提高设计和编程的能力。

下面我们将为您提供一些Verilog HDL习题的答案,希望能够帮助您更好地掌握这门语言。

1. 请编写一个Verilog HDL模块,实现一个4位全加器。

module full_adder(input wire a, b, cin,output wire sum, cout);assign sum = a ^ b ^ cin;assign cout = (a & b) | (b & cin) | (a & cin);endmodule2. 请编写一个Verilog HDL模块,实现一个4位加法器。

module adder_4bit(input wire [3:0] a, b,output wire [3:0] sum);wire c0, c1, c2;full_adder fa0(a[0], b[0], 1'b0, sum[0], c0);full_adder fa1(a[1], b[1], c0, sum[1], c1);full_adder fa2(a[2], b[2], c1, sum[2], c2);full_adder fa3(a[3], b[3], c2, sum[3], );endmodule3. 请编写一个Verilog HDL模块,实现一个4位移位寄存器。

module shift_register(input wire clk, rst, shift,input wire [3:0] in,output wire [3:0] out);reg [3:0] reg_data;always @(posedge clk or posedge rst) beginif(rst)reg_data <= 4'b0;else if(shift)reg_data <= {reg_data[2:0], in[0]};elsereg_data <= in;endassign out = reg_data;endmodule以上是一些常见的Verilog HDL习题的答案,通过这些习题的练习,相信您对Verilog HDL语言的掌握会更加深入。

Verilog HDL数字集成电路设计原理与应用(第二版)(蔡觉平) (4)

本章通过数字电路中基本逻辑电路的Verilog HDL程序设计 进行讲述,要求读者掌握基本逻辑电路的可综合性设计,为 具有特定功能的复杂电路的设计打下基础。

组合电路的设计需要从以下几个方面考虑:首先,所 用的逻辑器件数目最少,器件的种类最少,且器件之间的连 线最简单,这样的电路称为“最小化”电路。其次,为了满 足速度要求,应使级数尽量少,以减少门电路的延迟;电路 的功耗应尽可能地小,工作时稳定可靠。

组合逻辑电路的描述方式有四种:真值表、逻辑代数、 结构描述、抽象描述。采用Verilog HDL进行组合逻辑电路 设计主要采用的就是这几种方式。下面结合具体的实例简单 介绍达四种描述方式。 20

6

例4.1-1 用Verilog HDL语言设计模256(8 bit)计数 器。

(a) 可综合程序描述方式: module counter (count,clk,reset); output count; input clk,reset; reg [7:0] count; reg out; always @(posedge clk) 7

wire [1:0] sum; reg OUT; assign sum=A+B+C; always @(sum)

if (sum>1) else

endmodule

OUT=1; OUT=0;

32

可以看到,以上4种Verilog HDL描述方式都可以对表决 电路进行设计。这里应该指出的是,Verilog HDL程序是对 逻辑电路功能的描述性设计,并非最终得到的电路。EDA综 合工具可以将Verilog HDL程序综合成物理电路形式,通过 电路优化,从而得到符合设计要求的最简化电路。采用 Synplify软件对上面4种方法中任一种方法设计的Verilog HDL程序进行综合(采用Altera公司的Stratix Ⅱ器件),可 以得到相同的最简化电路,如图4.2-4所示。

蔡觉平老师,verilog上机作业

上机作业题目2:简述begin-end 语句块和fork-join 语句块的区别,并写出下面信号对应的程序代码begin-end 语句块和fork-join 语句块的区别:1、执行顺序:begin-end 语句块按照语句顺序执行,fork-join 语句块所有语句均在同一时刻执行;2、语句前面延迟时间的意义:begin-end 语句块为相对于前一条语句执行结束的时间,fork-join 语句块为相对于并行语句块启动的时间;3、起始时间:begin-end 语句块为首句开始执行的时间,fork-join 语句块为转入并行语句块的时间;4、结束时间:begin-end 语句块为最后一条语句执行结束的时间,fork-join 语句块为执行时间最长的那条语句执行结束的时间;5、行为描述的意义:begin-end 语句块为电路中的数据在时钟及控制信号的作用下,沿数据通道中各级寄存器之间的传送过程。

fork-join 语句块为电路上电后,各电路模块同时开始工作的过程。

程序如下: module b(a,b); output a,b; reg a,b; initial begin a=0; b=1; #10 a=1; fork b=0; #10 b=1; #20 a=0; join#10 b=0; #10 a=1; b=1; endendmoduleA B题目3.分别用阻塞和非阻塞赋值语句描述如下图所示移位寄存器的电路图。

程序如下:module block1(din,clk,out0,out1,out2,out3);input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout3=out2;out2=out1;out1=out0;out0=din;endendmodulemodule non_block1(din,clk,out0,out1,out2,out3); input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout0<=din;out1<=out0;out2<=out1;out3<=out2;endendmodule题目4:设计16位同步计数器要求:(1)分析16位同步计数器结构和电路特点;(2)用硬件描述语言进行设计;(3)编写测试仿真并进行仿真。

VerilogHDL数字集成电路设计原理与应用作者蔡觉平第7章

7.1.3 设计输入

设计输入是指将设计划分阶段定义好的模块借助一定 的设计输入手段转换为EDA工具能接受的信息格式。目前 主要的设计输入手段有高级硬件描述语言HDL(Verilog HDL/VHDL)和原理图等。HDL语言支持不同层次的描述, 不依赖于各个厂家的工艺器件,便于修改。

逻辑输入工具的功能是把逻辑图、状态机、真值表输 入到计算机中,并进行语法、可综合性检查等。目前主流 8 工具有Cadence公司的Composer、Synopsys公司的Leda以及 UltraEdit、Vim等第三方编辑工具。

7.1 数字集成电路设计流程简介

在EDA技术高度发达的今天,没有一个设计工程师队 伍能够用人工方法有效、全面、正确地设计和管理含有几 3 百万个门的现代集成电路。利用EDA工具,工程师可以从 概念、算法、协议等开始设计电子系统,

大量工作可以通过计算机完成,并可以将电子产品从系统 规划、电路设计、性能分析到封装、版图的整个过程在计 算机上自动完成。这样做有利于缩短设计周期、提高设计 正确性、降低设计成本、保证产品性能,尤其是可增加一 次投片的成功率,因此这种方法在大规模集成电路设计中 已经普遍被采用。

读者可以通过官方网站的链接下载Verilog HDL/VHDL的 语法文件,并把下载的文件复制到WordFile.txt文件中(在 UltraEdit的安装目录下),一般加在最后。这样就可以使用 UltraEdit编辑HDL源代码了。

10

7.1.4 仿真

设计输入后,经HDL编译器检查没有语法错误后,就 可以对设计进行验证了。这里的验证是指通过仿真软件验 证其功能是否符合制定的设计规范,这一阶段的验证常被 称为功能仿真或行为仿真。布局布线后,提取有关的器件 延迟、连线延迟等时序参数(这些信息在反标注文件中)。 在此基础上进行的仿真称为后仿真,也称时序仿真,它是 接近真实器件运行的仿真。 11

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

上机作业题目2:简述begin-end 语句块和fork-join 语句块的区别,并写出下面信号对应的程序代码begin-end 语句块和fork-join 语句块的区别:1、执行顺序:begin-end 语句块按照语句顺序执行,fork-join 语句块所有语句均在同一时刻执行;2、语句前面延迟时间的意义:begin-end 语句块为相对于前一条语句执行结束的时间,fork-join 语句块为相对于并行语句块启动的时间;3、起始时间:begin-end 语句块为首句开始执行的时间,fork-join 语句块为转入并行语句块的时间;4、结束时间:begin-end 语句块为最后一条语句执行结束的时间,fork-join 语句块为执行时间最长的那条语句执行结束的时间;5、行为描述的意义:begin-end 语句块为电路中的数据在时钟及控制信号的作用下,沿数据通道中各级寄存器之间的传送过程。

fork-join 语句块为电路上电后,各电路模块同时开始工作的过程。

程序如下: module b(a,b); output a,b; reg a,b; initial begin a=0; b=1; #10 a=1; fork b=0; #10 b=1; #20 a=0; join#10 b=0; #10 a=1; b=1; endendmoduleA B题目3.分别用阻塞和非阻塞赋值语句描述如下图所示移位寄存器的电路图。

程序如下:module block1(din,clk,out0,out1,out2,out3);input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout3=out2;out2=out1;out1=out0;out0=din;endendmodulemodule non_block1(din,clk,out0,out1,out2,out3); input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout0<=din;out1<=out0;out2<=out1;out3<=out2;endendmodule题目4:设计16位同步计数器要求:(1)分析16位同步计数器结构和电路特点;(2)用硬件描述语言进行设计;(3)编写测试仿真并进行仿真。

程序如下:module b;reg clk;reg reset;wire [3:0]count,result;always #5 clk=~clk;initial begin clk=0;reset=0; #20 reset=1;enda U1(.clk(clk),.reset(reset),.result(result),.count(count)); endmodulemodule a(count,clk,reset,result);output count,result;input clk,reset;reg [3:0]count;always@(posedge clk)beginif(!reset) count=4'b0000;else count=count+1;endassign result=count[0]||count[1]||count[2]||count[3]; endmodule题目5.试用Verilog HDL门级描述方式描述如下图所示的电路。

Z程序如下:module diwuti(D0,D1,D2,D3,S1,S2,Z);output Z;input D0,D1,D2,D3,S1,S2;wire wi1,wi2,w3,w4,w5,w6;not U1(w1,S1),U2(w2,S2);and U3(w6,D3,S2),U4(w5,D2,S1,w2),U5(w4,D1,S1,w1),U6(w3,D0,w1,w2); or U7(Z,w3,w4,w5,w6); endmoduleoutput SUM,C_OUT; input A,B,C_IN;reg SUM,C_OUT; always@(A or B or C_IN) case({A,B,C_IN})3'b000:SUM<=0;3'b000:C_OUT<=0;3'b001:SUM<=1;3'b001:C_OUT<=0;3'b010:SUM<=1;3'b010:C_OUT<=0;3'b011:SUM<=0;3'b011:C_OUT<=1;3'b100:SUM<=1;3'b100:C_OUT<=0;3'b101:SUM<=0;3'b101:C_OUT<=1;3'b110:SUM<=0;3'b110:C_OUT<=1;3'b111:SUM<=1;3'b111: C_OUT<=1;endcaseendmodule题目7:设计16位同步加法器和乘法器要求:(1)分析16位同步加法器和乘法器结构和电路特点;(2)用硬件描述语言进行设计;(3)编写测试仿真并进行仿真。

程序如下:module c;parameter adder16_width=16;reg [adder16_width-1:0]ain,bin;reg Cin;wire [adder16_width-1:0]sum;wire Cout;initialbeginain=10;bin=10;Cin=1;endinitialbegin#5 ain=16'b1111111111111111;#10 bin=1;enda U1(.ain(ain),.bin(bin),.Cin(Cin),.Cout(Cout),.sum(sum)); endmodulemodule d;parameter width=16;reg [width-1:0]ain,din;wire [width*2-1:0]mul;initial begin ain=2;din=2; endinitial begin #10 ain=100;#15 din=100; endb U1(.ain(ain),.din(din),.mul(mul));endmodulemodule a(bin,ain,sum,Cout,Cin);parameter width=16;output [width-1:0]sum; output Cout;input [width-1:0]ain,bin;input Cin;assign {Cout,sum}=ain+bin+Cin; endmodulemodule c(ain,din,mul);parameter width=16;input [width-1:0]ain,din;output [width*2-1:0]mul;assign mul=ain*din; endmodule题目8.将下面的状态转移图用Verilog HDL描述。

入只与状态的跳转有关,与状态机的输出无关,因此该状态机为摩尔型状态机。

下面为三段式描述方式程序如下:module b(clk,out,step,clr);output [2:0]out;input step,clk,clr;reg [2:0]out;reg [1:0]state,next_state;always @(posedge clk)state<=next_state;always @(state or clr)if(clr)next_state<=0;elsecase(state)2'b00:case(step)1'b0:begin next_state<=2'b00;out<=3'b001;end1'b1:begin next_state<=2'b01; out<=3'b001;endendcase2'b01:beginout<=3'b010;next_state<=2'b11;end2'b11:case(step)1'b0:begin next_state<=2'b00;out<=3'b100;end1'b1:begin next_state<=2'b10;out<=3'b100;endendcase2'b10:case(step)1'b0:begin next_state<=2'b10;out<=3'b111;end1'b1:begin next_state<=2'b00;out<=3'b111;endendcaseendcaseendmodulemodule a;reg clk,step,clr;wire [3:0]out;always#5 clk=~clk;Initialbegin clk=0; clr=1;step=1;endinitialbegin #5clr=0; #80 step=0; #100step=1;endb U1(clk,out,step,clr);endmodule题目9. 如下图所示电路,若其延迟时间设定如表所示,试写Verilog HDL 程序设计该电路。

module a(a,s,b,y,s0); input a,b,s,s0; output y;assign y=(s&&b)||(s0&&a); specify(a=>y)=(10,12,14); (b=>y)=(10,12,14); (s=>y)=(11,13,15); (s0=>y)=(11,13,15); endspecify endmodulemodule b(a,s,b,y); input s,a,s,b; output y; wire s0;not #(4)U1(s0,s);delay_door U2(a,s,b,y,s0); endmodule题目10.设计一个8位数字显示的简易频率计。

要求: ①能够测试10Hz~10MHz 方波信号;②电路输入的基准时钟为1Hz ,要求测量值以8421BCD 码形式输出; ③系统有复位键;④采用分层次分模块的方法,用Verilog HDL 进行设计。