MIPS单周期CPU实验报告

单周期CPU实验报告

MIPS-CPU设计实验报告实验名称:32位单周期MIPS-CPU设计姓名学号:刘高斯11072205实验日期:2014年12月19日目录前言MIPS简介------------------------------------------------------------- 3 实验目的------------------------------------------------------------- 3第一部分VERILOG HDL 语言实现部分实验内容------------------------------------------------------------- 4 试验环境------------------------------------------------------------- 4 模块简介------------------------------------------------------------- 4 实验截图------------------------------------------------------------- 5 实验感想------------------------------------------------------------- 5 实验代码------------------------------------------------------------- 6第二部分LOGISIM 语言实现部分实验内容------------------------------------------------------------- 16 实验环境------------------------------------------------------------- 16模块设计------------------------------------------------------------- 16 试验感想------------------------------------------------------------- 23前言一、MIPS简介MIPS是世界上很流行的一种RISC处理器。

MIPS单周期CPU实验报告材料

《计算机组成原理实验》实验报告(实验二)学院名称:专业(班级):学生姓名:学号:时间:2017 年11 月25 日成绩 :实验二:单周期CPU设计与实现一.实验目的(1) 掌握单周期CPU数据通路图的构成、原理及其设计方法;(2) 掌握单周期CPU的实现方法,代码实现方法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的方法;(5) 掌握单周期CPU的实现方法。

二.实验内容设计一个单周期的MIPSCPU,使其能实现下列指令:==> 算术运算指令说明:以助记符表示,是汇编指令;以代码表示,是机器指令功能:rd←rs + rt。

reserved为预留部分,即未用,一般填“0”。

符号扩展再参加“加”运算。

(3)sub rd , rs , rt功能:rd←rs - rt==> 逻辑运算指令(4)ori rt , rs ,immediate功能:rt←rs | (zero-extend)immediate;immediate做“0”扩展再参加“或”运算。

(5)and rd , rs , rt功能:rd←rs & rt;逻辑与运算。

功能:rd←rs | rt;逻辑或运算。

==>移位指令==>比较指令功能:if (rs<rt) rd =1 else rd=0, 具体请看表2 ALU运算功能表,带符号==> 存储器读/写指令(9)sw rt ,immediate(rs) 写存储器功能:memory[rs+ (sign-extend)immediate]←rt;immediate符号扩展再相加。

即将rt寄存器的内容保存到rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中。

(10) lw rt , immediate(rs) 读存储器功能:rt ← memory[rs + (sign-extend)immediate];immediate符号扩展再相加。

华中科技大学HUST类MIPS单周期微处理器设计实验报告

类MIPS单周期微处理器设计实验报告专业:班级:学号:姓名:一、微处理器各模块设计各模块的框图结构如上图所示。

由图可知,该处理器包含指令存储器、数据存储器、寄存器组、ALU单元、符号数扩张、控制器、ALU控制译码以及多路复用器等。

图中还忽略了一个单元:时钟信号产生器,而且以上各个部件必须在时钟信号的控制下协调工作。

1.指令存储器的设计指令寄存器为ROM类型的存储器,为单一输出指令的存储器。

因此其对外的接口为clk、存储器地址输入信号(指令指针)以及数据输出信号(指令)。

(1)在IP wizard 中配置ROM,分配128个字的存储空间,字长为32位宽。

(2)选择输入具有地址寄存功能,只有当时钟上升沿有效时,才进行数据的输出。

(3)配置ROM内存空间的初始化COE文件。

最后单击Generate按钮生成IROM模块。

2.数据存储器的设计数据存储器为RAM类型的存储器,并且需要独立的读写控制信号。

因此其对外的接口输入信号为clk、we、datain、addr;输出信号为dataout。

数据存储器基本建立过程同ROM的建立。

3.寄存器组设计寄存器组是指令操作的主要对象,MIPS中一共有32个32位寄存器。

在指令的操作过程中需要区分Rs、Rt、Rd的地址和数据,并且Rd的数据只有在寄存器写信号有效时才能写入,因此该模块的输入为clk、RegWriteAddr、RegWriteData、RegWriteEn、RsAddr、RtAddr、reset;输出信号为RsData、RtData。

由于$0一直输出0,因此当RsAddr、RtAddr为0时,RsData以及RtData 必须输出0,否则输出相应地址寄存器的值。

另外,当RegWriteEn有效时,数据应该写入RegWriteAddr寄存器。

并且每次复位时所有寄存器都清零。

代码如下:module regFile(input clk,input reset,input [31:0] regWriteData,input [4:0] regWriteAddr,input regWriteEn,output [31:0] RsData,output [31:0] RtData,input [4:0] RsAddr,input [4:0] RtAddr);reg[31:0] regs[0:31];assign RsData = (RsAddr == 5'b0)?32'b0:regs[RsAddr];assign RtData = (RtAddr == 5'b0)?32'b0:regs[RtAddr];integer i;always @(posedge clk)beginif(!reset)beginif(regWriteEn==1)beginregs[regWriteAddr]=regWriteData;endendelsebeginfor(i=0;i<31;i=i+1)regs[i]=0;regs[31]=32'hffffffff;endendendmodule4.ALU设计在这个简单的MIPS指令集中,微处理器支持add、sub、and、or、slt运算指令,需要利用ALU单元实现运算,同时数据存储指令sw、lw也需要ALU单元计算存储器地址,条件跳转指令beq需要ALU来比较两个寄存器是否相等。

单周期CPU设计实验报告

单周期CPU设计实验报告一、引言计算机是现代信息社会必不可少的工具,而CPU作为计算机的核心部件,承担着执行指令、进行运算和控制系统资源的任务。

随着科技的进步和计算能力的需求,CPU的设计也趋于复杂和高效。

本次实验旨在设计一种单周期CPU,探究其设计原理和实现过程,并通过实验验证其正确性和性能。

二、理论基础1.单周期CPU概述单周期CPU即每个时钟周期内只完成一条指令的处理,它包括指令取址阶段(IF)、指令译码阶段(ID)、执行阶段(EX)、访存阶段(MEM)和写回阶段(WB)等多个阶段。

每条指令都顺序地在这些阶段中执行,而不同的指令所需的时钟周期可能不同。

2.控制信号单周期CPU需要根据不同的指令类型产生不同的控制信号来控制各个阶段的工作。

常见的控制信号包括时钟信号(clk)、使能信号(En)、写使能信号(WE)和数据选择信号(MUX)等。

这些信号的产生需要通过译码器、控制逻辑电路和时序逻辑电路等来实现。

三、实验设计本次实验采用的单周期CPU包括以下五个阶段:指令取址阶段、指令译码阶段、执行阶段、访存阶段和写回阶段。

每个阶段的具体操作如下:1.指令取址阶段(IF)在IF阶段,通过计数器实现程序计数器(PC)的自增功能,并从存储器中读取指令存储地址所对应的指令码。

同时,设置PC使能信号,使其可以更新到下一个地址。

2.指令译码阶段(ID)在ID阶段,对从存储器中读取的指令码进行解码,确定指令的操作类型和操作数。

同时,根据操作类型产生相应的控制信号,如使能信号、写使能信号和数据选择信号等。

3.执行阶段(EX)在EX阶段,根据ID阶段产生的控制信号和操作数,进行相应的算术逻辑运算。

这里可以包括加法器、乘法器、逻辑运算器等。

4.访存阶段(MEM)在MEM阶段,根据EX阶段的结果,进行数据存储器的读写操作。

同时,将读取的数据传递给下一个阶段。

5.写回阶段(WB)在WB阶段,根据MEM阶段的结果,将数据传递给寄存器文件,并将其写入指定的寄存器。

MIPS单周期CPU实验报告

MIPS单周期CPU实验报告一、实验目的本实验旨在设计一个基于MIPS指令集架构的单周期CPU,具体包括CPU的指令集设计、流水线的划分与控制信号设计等。

通过本实验,可以深入理解计算机组成原理中的CPU设计原理,加深对计算机体系结构的理解。

二、实验原理MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集(RISC)架构的处理器设计,大大简化了指令系统的复杂性,有利于提高执行效率。

MIPS指令集由R、I、J三种格式的指令组成,主要包括算术逻辑运算指令、存储器访问指令、分支跳转指令等。

在单周期CPU设计中,每个指令的执行时间相同,每个时钟周期只执行一个指令。

单周期CPU的主要部件包括指令内存(IM)、数据存储器(DM)、寄存器文件(RF)、运算单元(ALU)、控制器等。

指令执行过程主要分为取指、译码、执行、访存、写回等阶段。

三、实验步骤1.设计CPU指令集:根据MIPS指令集的格式和功能,设计符合需求的指令集,包括算术逻辑运算指令、存储器访问指令、分支跳转指令等。

2.划分CPU流水线:将CPU的执行过程划分为取指、译码、执行、访存、写回等阶段,确定每个阶段的功能和控制信号。

3.设计控制器:根据CPU的流水线划分和指令集设计,设计控制器实现各个阶段的控制信号生成和时序控制。

4.集成测试:进行集成测试,验证CPU的指令执行功能和正确性,调试并优化设计。

5.性能评估:通过性能评估指标,如CPI(平均时钟周期数)、吞吐量等,评估CPU的性能优劣,进一步优化设计。

四、实验结果在实验中,成功设计了一个基于MIPS指令集架构的单周期CPU。

通过集成测试,验证了CPU的指令执行功能和正确性,实现了取指、译码、执行、访存、写回等阶段的正常工作。

同时,通过性能评估指标的测量,得到了CPU的性能参数,如CPI、吞吐量等。

通过性能评估,发现了CPU的性能瓶颈,并进行了相应的优化,提高了CPU的性能表现。

MIPS单周期CPU实验报告材料

《计算机组成原理实验》实验报告(实验二)学院名称:专业(班级):学生姓名:学号:时间:2017 年11 月25 日成绩:实验二:单周期CPU设计与实现一.实验目的(1) 掌握单周期CPU数据通路图的构成、原理及其设计方法;(2) 掌握单周期CPU的实现方法,代码实现方法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的方法;(5) 掌握单周期CPU的实现方法。

二.实验内容设计一个单周期的MIPSCPU,使其能实现下列指令:==> 算术运算指令(1)add rd , rs, rt(说明:以助记符表示,是汇编指令;以代码表示,是机器指令)功能:rd←rs + rt。

reserved为预留部分,即未用,一般填“0”。

(2)addi rt , rs ,immediate功能:rt←rs + (sign-extend)immediate;immediate符号扩展再参加“加”运算。

(3)sub rd , rs , rt功能:rd←rs - rt==> 逻辑运算指令(4)ori rt , rs ,immediate功能:rt←rs | (zero-extend)immediate;immediate做“0”扩展再参加“或”运算。

(5)and rd , rs , rt功能:rd←rs & rt;逻辑与运算。

(6)or rd , rs , rt功能:rd←rs | rt;逻辑或运算。

==>移位指令(7)sll rd, rt,sa功能:rd<-rt<<(zero-extend)sa,左移sa位,(zero-extend)sa==>比较指令(8)slt rd, rs, rt 带符号数功能:if (rs<rt) rd =1 else rd=0, 具体请看表2 ALU运算功能表,带符号==> 存储器读/写指令(9)sw rt ,immediate(rs) 写存储器功能:memory[rs+ (sign-extend)immediate]←rt;immediate符号扩展再相加。

单周期设计实验报告

一、实验目的1. 了解单周期CPU的基本原理和设计方法。

2. 掌握单周期CPU的数据通路结构及其实现过程。

3. 熟悉单周期CPU的指令集和指令格式。

4. 通过实验验证单周期CPU的功能和性能。

二、实验内容1. 单周期CPU的数据通路结构单周期CPU的数据通路主要由以下几个部分组成:(1)指令寄存器(IR):存储从内存中取出的指令。

(2)程序计数器(PC):存储下一条指令的地址。

(3)寄存器文件(RF):用于存储操作数和中间结果。

(4)算术逻辑单元(ALU):执行指令中的算术运算和逻辑运算。

(5)数据内存(DM):存储数据和指令。

(6)控制单元:根据指令操作码生成相应的控制信号。

2. 单周期CPU的指令集和指令格式本实验所采用的指令集包括以下几种:(1)算术运算指令:如加法、减法、乘法、除法等。

(2)逻辑运算指令:如与、或、非等。

(3)数据传输指令:如将寄存器中的数据传送到内存或寄存器中。

(4)跳转指令:改变程序计数器的值,实现程序跳转。

指令格式如下:| 操作码 | 操作数1 | 操作数2 | 目标寄存器 ||--------|--------|--------|------------|| 5位 | 5位 | 5位 | 5位 |3. 单周期CPU的设计与实现(1)硬件设计根据实验要求,设计单周期CPU的硬件结构,包括各个模块的连接和功能实现。

(2)软件设计编写指令译码程序,根据指令操作码生成相应的控制信号,控制各个模块执行指令。

4. 实验验证(1)编译测试程序将测试程序编译成机器码,存入数据内存。

(2)运行测试程序通过程序计数器逐条取出指令,执行指令,观察结果。

(3)分析实验结果根据实验结果,分析单周期CPU的功能和性能。

三、实验结果与分析1. 单周期CPU能够正确执行指令,实现算术运算、逻辑运算、数据传输和跳转等功能。

2. 单周期CPU的数据通路结构简单,指令执行速度快,但资源利用率较低。

3. 实验结果表明,单周期CPU具有较高的性能,但在实际应用中,需要根据具体需求进行优化设计。

MIPS单周期CPU实验报告

MIPS单周期CPU实验报告一、实验目标本次实验的主要目标是设计并实现一个基于MIPS单周期CPU的计算机系统。

具体要求如下:1.能够识别并执行MIPS指令集中的常见指令,包括算术逻辑运算、分支跳转和存取指令等。

2.实现基本的流水线结构,包括指令译码阶段、执行阶段、访存阶段和写回阶段。

3.能够在基本结构的基础上添加异常处理和浮点数运算支持。

二、实验环境三、实验过程1.确定CPU的基本组成部分,包括指令存储器、数据存储器、寄存器、ALU和控制单元等,并进行电路设计。

2.编写MIPS汇编程序,并使用MARS进行仿真调试,验证指令的正确性和计算结果的准确性。

3.将MIPS汇编程序烧录到指令存储器中,并将数据存储器中的初始数据加载进去。

4.运行程序,观察CPU的工作状态,并进行时序仿真,验证CPU设计的正确性。

5.对CPU进行性能测试,包括执行时间、指令吞吐量和时钟周期等指标的测量。

四、实验结果经过实验和测试,我们成功地设计并实现了一个基于MIPS单周期CPU的计算机系统。

该系统能够正确执行MIPS指令集中的常见指令,并支持流水线结构、异常处理和浮点数运算。

1.指令执行的正确性:通过在MARS中进行调试和仿真,我们发现CPU能够正确地执行各种指令,包括算术逻辑运算、分支跳转和存取指令等。

并且,在时序仿真中,CPU的各个组件的信号波形也符合预期。

2.流水线结构的实现:我们根据MIPS指令的特点和处理流程,设计了基本的流水线结构,并在MARS中进行了时序仿真。

仿真结果表明,各个流水线级的操作都能够正确无误地进行,并且能够顺利地在一个时钟周期内完成。

3.异常处理和浮点数运算的支持:通过在MIPS汇编程序中加入异常处理和浮点数运算的指令,我们验证了CPU对这些功能的支持。

在异常处理时,CPU能够正确地转入异常处理程序,并根据异常类型进行相应的处理。

在浮点数运算时,CPU能够正确地进行浮点数的加减乘除等运算,并将结果正确地写回寄存器。

CPU设计实验报告

数字逻辑与处理器基础实验32位mips cpu设计综述:我们的最后验收结果时钟频率是84.9mhz。

本实验报告主要分为实验设计说明与实验收获总结两个部分。

附件中有cpu工程文档与模块代码。

第一部分实验设计一、 alu设计1、设计思路实现基本的算术、逻辑、关系、位与移位运算,尽量优化以达到最小的面积延时积。

结构图如下:主要设计思想:a. 加法运算实现可以采用逐次进位、超前进位等结构,减法可以通过加法实现(参见见面理论课讲义或者前面实验);同时输出z(结果为零)、v(结果溢出)、n (结果为负)等标志位,注意有符号数和无符号数标志产生的不同。

b. 比较运算根据减法运算的结果(z/v/n)产生,自行分析比较操作与算术运算之间的关系。

c. 移位运算可以考虑将移位操作拆分为16 位移位、8 位移位、4 位移位、2 位移位、1位移位等几个子运算的组合,然后级联形成最后的运算结果。

d. 逻辑运算可以根据要求直接产生。

功能表接口说明2、主要模块a) 32bit加法器采用8个4bit超前进位加法器极连的方式,构成32bit加法器。

对于逸出位v的处理如下:由有符号数的性质可知,对最高位32和次高位31位取抑或,输出信号则为是否逸出。

对32位运算结果取反后,再对相邻两位反复取与,最终得到结果是否为零的输出z.如果是有符号数,则符号位=n。

由于这一方法部分程度上减弱了高位计算对低位计算的依赖程度,因此可以实现延时的降低。

同时,由于其超前进位网络的大量逻辑运算,较大程度上提升了电路的面积,造成最终的面积延时积特性恶化。

关键代码见附录1 b) 32bit减法器对加法器按位取反,再加一。

关键代码见附录1 c) 32bit 右移 32bit 左移 32bit 算术右移将移位操作拆分为16 位移位、8 位移位、4 位移位、2 位移位、1位移位等几个子运算的组合,然后级联得到最后的运算结果。

关键代码见附录1 d) 32bit 逻辑比较单元采用行为级语句直实现逻辑比较功能。

单周期MIPS CPU实验(8条指令)

单周期M I P S C P U设计实验目的⏹掌握硬布线控制器设计的基本原理⏹能利用相关原理在Logisim平台中设计实现MIPS单周期CPU⏹主要任务☐绘制MIPS CPU数据通路☐实现单周期硬布线控制器☐测试联调核心指令集(可实现内存区域冒泡排序)#MIPS指令RTL功能描述1add$rd,$rs,$rt R[$rd]←R[$rs]+R[$rt]溢出时产生异常,且不修改R[$rd] 2slt$rd,$rs,$rt R[$rd]←R[$rs]<R[$rt]小于置1,有符号比较3addi$rt,$rs,imm R[$rt]←R[$rs]+SignExt(imm)溢出产生异常16b4lw$rt,imm($rs)R[$rt]←Mem4B(R[$rs]+SignExt16b(imm))5sw$rt,imm($rs)Mem4B(R[$rs]+SignExt16b(imm))←R[$rt]6beq$rs,$rt,imm if(R[$rs]=R[$rt])PC←PC+SignExt18b({imm,00})7bne$rs,$rt,imm if(R[$rs]!=R[$rt])PC←PC+SignExt18b({imm,00})8syscall系统调用,这里用于停机单周期MIPS 参考数据通路MemtoReg MemWrite Branch AluOP ALUSrc RegDstRegWritePCSrcCLKPCRDA指令存储器指令字4PC+45:020:1625:2115:1115:0Sign ExtendSignImmR1#R2#W#WDWE 寄存器堆R1R2101011<<2+PCBranchSrcB SrcA EqualA L UALUResult WriteDataWERD A 数据存储器WD ReadData WriteBackData++BranchAddress31:26CLK CLKPC+4控制器FuncOp rsrtrd步骤1:构建MIPS主机通路⏹在MIPS单周期CPU子电路中,利用如下组件构建MIPS 单周期CPU数据通路☐PC、IMEM、RegFile、ALU、DMEM、Controller步骤2:设计单周期MIPS控制器⏹输入信号⏹指令字Opcode,Func字段(12位)⏹输出信号⏹多路选择器选择信号⏹内存访问控制信号⏹寄存器写使能信号⏹运算器控制信号、指令译码信号⏹纯组合逻辑电路、无时序逻辑控制信号功能说明(8条核心指令集)#控制信号信号说明产生条件1MemToReg写入寄存器的数据来自存储器lw指令2MemWrite写内存控制信号sw指令未单独设置MemRead信号3Beq Beq指令译码信号Beq指令4Bne Bne指令译码信号Bne指令5AluOP运算器操作控制符加法,比较两种运算6AluSrcB运算器第二输入选择Lw指令,sw指令,addi7RegWrite寄存器写使能控制信号寄存器写回信号8RegDst写入寄存器选择控制信号R型指令9Halt停机信号,取反后控制PC使能端syscall指令完善硬布线控制器内部逻辑⏹打开CPU.circ打开单周期硬布线控制器电路⏹实现指令译码、ALU控制逻辑完善控制信号逻辑⏹增加简单的组合逻辑⏹根据给出的指令译码信号,实现所有控制信号逻辑步骤3:CPU测试⏹在指令存储器中载入排序程序sort.hex⏹时钟自动仿真,Windows:Ctrl+k Mac: command+k运行程序⏹程序停机后,查看数据存储器中排序情况,有符号降序排列下节课再见…。

mips 实验报告

mips 实验报告MIPS 实验报告摘要:本实验报告介绍了MIPS(Microprocessor without Interlocked Pipeline Stages)处理器的基本结构和工作原理,以及在实验中对MIPS处理器进行了仿真和验证的过程和结果。

通过本次实验,我们深入了解了MIPS处理器的指令集架构、流水线设计和性能特点,同时也对计算机体系结构有了更深入的认识。

1. 背景MIPS处理器是一种经典的RISC(Reduced Instruction Set Computer)架构的处理器,其设计简洁高效,广泛应用于嵌入式系统和高性能计算领域。

MIPS处理器采用了五级流水线结构,包括取指、译码、执行、访存和写回等阶段,能够实现指令级并行和流水线加速,提高了处理器的运行效率和性能。

2. 实验目的本次实验旨在通过对MIPS处理器的仿真和验证,加深对计算机体系结构和处理器设计的理解,掌握MIPS指令集架构的特点和流水线设计的原理,培养学生的计算机系统分析和设计能力。

3. 实验内容本次实验主要包括以下内容:(1)MIPS处理器的指令集架构和寄存器组设计;(2)MIPS处理器的流水线结构和控制信号设计;(3)使用Verilog HDL对MIPS处理器进行建模和仿真;(4)通过仿真验证MIPS处理器的正确性和性能。

4. 实验步骤(1)熟悉MIPS指令集架构和寄存器组设计;(2)设计MIPS处理器的流水线结构和控制信号;(3)使用Verilog HDL对MIPS处理器进行建模和仿真;(4)编写测试程序,对MIPS处理器进行功能验证和性能评估;(5)分析仿真结果,验证MIPS处理器的正确性和性能。

5. 实验结果通过对MIPS处理器的仿真和验证,我们得到了以下实验结果:(1)MIPS处理器能够正确执行各类指令,并能够实现指令级并行和流水线加速;(2)MIPS处理器的性能优秀,能够在较短的时钟周期内完成指令的执行;(3)MIPS处理器的流水线结构设计合理,能够有效提高处理器的运行效率和性能。

CPU实验——单周期MIPS处理器设计

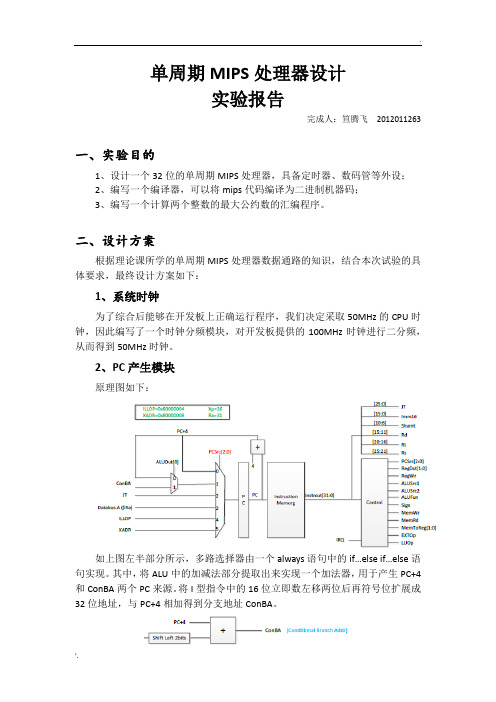

单周期MIPS处理器设计实验报告完成人:笪腾飞2012011263一、实验目的1、设计一个32位的单周期MIPS处理器,具备定时器、数码管等外设;2、编写一个编译器,可以将mips代码编译为二进制机器码;3、编写一个计算两个整数的最大公约数的汇编程序。

二、设计方案根据理论课所学的单周期MIPS处理器数据通路的知识,结合本次试验的具体要求,最终设计方案如下:1、系统时钟为了综合后能够在开发板上正确运行程序,我们决定采取50MHz的CPU时钟,因此编写了一个时钟分频模块,对开发板提供的100MHz时钟进行二分频,从而得到50MHz时钟。

2、PC产生模块原理图如下:如上图左半部分所示,多路选择器由一个always语句中的if…else if…else语句实现。

其中,将ALU中的加减法部分提取出来实现一个加法器,用于产生PC+4和ConBA两个PC来源。

将I型指令中的16位立即数左移两位后再符号位扩展成32位地址,与PC+4相加得到分支地址ConBA。

将跳转指令中的26位目标地址左移两位后,与当前PC的高四位拼接得到跳转地址JT。

将第一个操作数寄存器中的值取出作为PC的一个输入,这是为了实现jr和jalr指令,从$Xp和$Ra寄存器中读取跳转地址。

ILLOP和XADR分别是发生中断和异常时的跳转地址。

下一指令地址的选择由PCSrc决定,而PCSrc是译码后由控制信号模块根据每条指令的操作码(opcode)和函数码(funct)产生。

3、译码模块原理图如上图右半部分所示,将PC作为ROM模块的地址输入,输出即为PC所对应的指令。

分别取出指令中的某些片段,得到$Rs,$Rt,$Rd,shamt,funct,16位立即数和26位跳转地址。

4、控制模块控制模块即控制信号产生模块,六位操作码OpCode,六位函数码[5:0] Funct,定时器中断信号irq和PC最高位PC31作为输入,输出为以下控制信号:(1) R型指令指示信号IsR,值为1表示当前指令为R型指令,否则非R型指令;(2) PC产生的选择信号[2:0] PCSrc,取值0,1,2,3,4及其它,分别选择下一指令不同的PC;(3) 目的寄存器选择信号[1:0]RegDst,被写入的寄存器有四种选择:$Rd,$Rt,$Ra,$Xp,分别由RegDst不同取值完成选择;(4) 写寄存器使能信号RegWr,值为1表示允许对寄存器进行写操作;(5) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将移位量shamt进行0扩展后作为输入,值为0表示将$Rs寄存器中的值作为输入;(6) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将扩展后的32位立即数作为输入,值为0表示将$Rt寄存器中的值作为输入;(7) ALU运算控制信号[5:0] ALUFunc,作为ALU的输入选择不同的运算操作;(8) 有无符号数指示信号Sign,值为1表示有符号数,值为0表示无符号数;(9) 写存储器使能信号MemWr,值为1表示允许对存储器进行写操作;(10) 读存储器使能信号MemRd,值为1表示允许对存储器进行读操作;(11) 写寄存器值的选择信号[1:0] MemToReg,选择ALU结果,存储器读取结果和PC+4其中之一作为写入目的寄存器的值;(12) 符号位扩展指示信号EXTOp,值为1表示对16位立即数进行符号位扩展,值为0表示0扩展;(13) 立即数高位取指令指示信号LUOp,值为1表示当前指令为lui指令,选择将立即数载入高16位低位填0的32位立即数作为ALU输入,值为0表示将正常扩展后的32位立即数作为ALU输入;控制信号的具体产生过程此处略去,在控制信号说明文件中进行详述。

MIPS单周期CPU实验报告

《计算机组成原理实验》实验报告(实验二)学院名称:专业(班级):学生姓名:学号:时间:2017 年11 月25 日成绩: 实验二:单周期CPU设计与实现一.实验目的(1) 掌握单周期CPU数据通路图的构成、原理及其设计方法;(2) 掌握单周期CPU的实现方法,代码实现方法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的方法;(5) 掌握单周期CPU的实现方法。

二.实验内容设计一个单周期的MIPSCPU,使其能实现下列指令:==> 算术运算指令==> 逻辑运算指令功能:rd←rs | rt;逻辑或运算。

==>移位指令==>比较指令==> 存储器读/写指令将rt寄存器的内容保存到rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中。

即读取rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中的数,然后保存到rt寄存器中。

==> 分支指令功能:if(rs=rt) pc←pc + 4 + (sign-extend)immediate <<2 else pc ←pc + 4特别说明:immediate是从PC+4地址开始和转移到的指令之间指令条数。

immediate 符号扩展之后左移2位再相加。

为什么要左移2位?由于跳转到的指令地址肯定是4的倍数(每条指令占4个字节),最低两位是“00”,因此将immediate放进指令码中的时候,是右移了2位的,也就是以上说的“指令之间指令条数”。

12特别说明:与beq不同点是,不等时转移,相等时顺序执行。

功能:if(rs>0) pc←pc + 4 + (sign-extend)immediate <<2 else pc ←pc + 4==>跳转指令==> 停机指令三.实验原理1.时间周期:单周期CPU指的是一条指令的执行在一个时钟周期内完成,然后开始下一条指令的执行,即一条指令用一个时钟周期完成。

华中科技大学HUST类MIPS单周期微处理器设计实验报告

类MIPS单周期微处理器设计实验报告|专业:班级::学号:姓名:一、(二、微处理器各模块设计各模块的框图结构如上图所示。

由图可知,该处理器包含指令存储器、数据存储器、寄存器组、ALU单元、符号数扩张、控制器、ALU控制译码以及多路复用器等。

图中还忽略了一个单元:时钟信号产生器,而且以上各个部件必须在时钟信号的控制下协调工作。

1.指令存储器的设计指令寄存器为ROM类型的存储器,为单一输出指令的存储器。

因此其对外的接口为clk、存储器地址输入信号(指令指针)以及数据输出信号(指令)。

(1)在IP wizard 中配置ROM,分配128个字的存储空间,字长为32位宽。

(2)选择输入具有地址寄存功能,只有当时钟上升沿有效时,才进行数据的输出。

…(3)配置ROM内存空间的初始化COE文件。

最后单击Generate按钮生成IROM模块。

2.数据存储器的设计数据存储器为RAM类型的存储器,并且需要独立的读写控制信号。

因此其对外的接口输入信号为clk、we、datain、addr;输出信号为dataout。

数据存储器基本建立过程同ROM的建立。

3.寄存器组设计《寄存器组是指令操作的主要对象,MIPS中一共有32个32位寄存器。

在指令的操作过程中需要区分Rs、Rt、Rd的地址和数据,并且Rd的数据只有在寄存器写信号有效时才能写入,因此该模块的输入为clk、RegWriteAddr、RegWriteData、RegWriteEn、RsAddr、RtAddr、reset;输出信号为RsData、RtData。

由于$0一直输出0,因此当RsAddr、RtAddr为0时,RsData以及RtData 必须输出0,否则输出相应地址寄存器的值。

另外,当RegWriteEn有效时,数据应该写入RegWriteAddr寄存器。

并且每次复位时所有寄存器都清零。

代码如下:module regFile(input clk,input reset,input [31:0] regWriteData,input [4:0] regWriteAddr,$input regWriteEn,output [31:0] RsData,output [31:0] RtData,input [4:0] RsAddr,input [4:0] RtAddr);reg[31:0] regs[0:31];<assign RsData = (RsAddr == 5'b0)32'b0:regs[RsAddr];assign RtData = (RtAddr == 5'b0)32'b0:regs[RtAddr];integer i;always @(posedge clk)beginif(!reset)begin|if(regWriteEn==1)beginregs[regWriteAddr]=regWriteData;endendelsebeginfor(i=0;i<31;i=i+1)。

Logisim完成MIPS单周期处理器开发实验报告

Logisim完成MIPS单周期处理器开发实验报告Project3Logisim完成单周期处理器开发实验报告⼀.总体设计⼆.模块定义(1)IFU(2)GPR(3)ALU(4)EXT(5)DM(6)Controller四.控制器设计单周期真值表Func100000100010N/AOp000000000000001101100011000100001111add sub ori lw sw beq lui RegDst1100X X0 ALUSrc0011101 MemtoReg0001X X X RegWrite1111002 MemWrite0000100 nPC_sel0000010 ExtOp X X000X1ALUctr Add Subtract Or Add Add Subtract X五.测试要求16.测试程序lui$t0,0x0004#lui测试程序要实现:⽴即数0x0004加载⾄t0寄存器的⾼位lui$t1,0x0008#lui测试程序要实现:⽴即数0x0008加载⾄t1寄存器的⾼位ori$t3,$zero,0x00002000#ori测试程序要实现:zero寄存器中的内容与⽴即数0x00002000进⾏或运算,储存在t3寄存器中sw$t0,4($t3)#sw测试程序要实现:把t0寄存器中值(1Word),存储到t3的值再加上偏移量4,所指向的RAM中sw$t0,8($t3)#sw测试程序要实现:把t0寄存器中值(1Word),存储到t3的值再加上偏移量8,所指向的RAM中loop:add$t2,$t2,$t1#add测试程序要实现:t1寄存器中的值加上t2寄存器中的值后存到t2寄存器中lw$t4,4($t3)#lw测试程序要实现:把t3寄存器的值+4当作地址读取存储器中的值存⼊t4 lui$t5,0x0004#lui测试程序要实现:⽴即数0x0004加载⾄t5寄存器的⾼位sub$t7,$t6,$t5#sub测试程序要实现:t6寄存器中的值减去t5寄存器中的值后存到t7寄存器中add$t0,$t0,$t5#sub测试程序要实现:t0寄存器中的值减去t5寄存器中的值后存到t0寄存器中add$t6,$t6,$t0#add 测试程序要实现:t6寄存器中的值加上t0后存到t6寄存器中beq$t0,$t1,loop#beq测试程序要实现:判断t0的值和t1的值是否相等,相等转loopadd$t0,$t0,$t5#add测试程序要实现:t0寄存器中的值加上t5后存到t0寄存器中lui$v0,0x0001#lui测试程序要实现:⽴即数0x0001加载⾄v0寄存器的⾼位lui$v1,0x0002#lui测试程序要实现:⽴即数0x0002加载⾄v1寄存器的⾼位add$v0,$v0,$v1#add测试程序要实现:v0寄存器中的值加上v1后存到v0寄存器中add$v1,$v0,$v1#add测试程序要实现:v0寄存器中的值加上v1后存到v1寄存器中ori$a0,$v0,0xffff#ori测试程序要实现:v0寄存器中的内容与⽴即数0xffff进⾏或运算,储存在a0寄存器中sub$a1,$a0,0x0000ffff#sub测试程序要实现:a0寄存器中的值减去⽴即数0x0000ffff后存到a1寄存器中loop2:sub$a2,$v1,$v0#sub测试程序要实现:v1寄存器中的值减去v0中的值后存到a2寄存器中add$a1,$a2,$a1#add测试程序要实现:a2寄存器中的值加上a1后存到a1寄存器中beq$a1,$v1,loop2#beq测试程序要实现:判断a1的值和v1的值是否相等,相等转loop2机器码:3c0800043c090008340b2000ad680004014950208d6c00043c0d000401cd7822010d402001c870201109fff9010d40203c0200013c03000200431020004318203444ffff3c010*******ffff008128220062302200c52820 10a3fffdMARS模拟结果:Logism:GPR:DM:六、问答18.对于Figure5、Figure6中的与或阵列来说,1个3输⼊与门最终转化为2个2输⼊与门,1个4输⼊与门最终转化为3个2输⼊与门,依次类推。

微机原理实验类MIPS单周期微处理器设计

微机原理实验类MIPS单周期微处理器设计MIPS单周期微处理器设计是一种常见的计算机体系结构,采用简化指令集和单个时钟周期执行指令的方式。

下面将详细介绍MIPS单周期微处理器的设计。

1.指令集架构MIPS单周期微处理器采用五个基本的指令类型,包括加载/存储指令、算术逻辑指令、跳转指令、分支指令和数据传输指令。

这些指令类型可以通过相应的操作码和寄存器编号来确定具体的指令操作。

2.寄存器文件MIPS单周期微处理器使用了32个通用寄存器,每个寄存器的位宽为32位。

其中,除了$0寄存器始终为零,其他的寄存器可用于存储数据和进行运算。

3.控制单元控制单元是MIPS单周期微处理器的核心部分,负责解码指令,生成相应的控制信号,控制数据通路的各个部件以正确执行指令。

控制单元包括指令寄存器、程序计数器、指令解码器等。

4.数据通路MIPS单周期微处理器的数据通路由多个组成部分组成,包括寄存器文件、算术逻辑单元(ALU)、数据存储器(DM)等。

数据通路用于执行指令的各个操作步骤,如指令的读取、寄存器操作、运算和数据存储。

5.指令执行过程MIPS单周期微处理器的指令执行过程包括指令的取指、指令解码、操作数的读取、指令执行和结果的写回等步骤。

在每个时钟周期中,通过控制信号控制数据通路的各个部件,按照指令的操作要求完成相应的操作。

总体而言,MIPS单周期微处理器设计简洁高效,适用于大多数应用场景。

然而,由于单周期处理器的指令执行时间较长,且不支持流水线技术,所以在一些对性能要求较高的应用中可能会受到限制。

综上所述,MIPS单周期微处理器设计是一种常用的计算机体系结构,通过合理的指令集架构、寄存器文件、控制单元和数据通路的设计,实现了对指令的有效执行和数据操作。

该设计具有一定的优势和限制,需要根据实际需求进行选用和改进。

类MIPS单周期微处理器设计实验报告

课程名称:微机原理与接口技术实验类MIPS单周期微处理器设计1.实验任务、目标利用Verilog HDL语言,基于Xilinx FPGA nexys4实验平台,设计一个能够执行以下MIPS指令集的单周期类MIPS处理器,要求完成所有支持指令的功能仿真,验证指令执行的正确性,要求编写汇编程序将本人学号的ASCII码存入RAM的连续内存区域。

▪支持基本的算术逻辑运算如add,sub,and,or,slt,andi指令▪支持基本的内存操作如lw,sw指令▪支持基本的程序控制如beq,j指令(由于特殊情况,此次实验仅完成Reg、ALU、ALUCtr三个模块并分别加以仿真和验算)2.微处理器各个模块硬件设计原理、verilog代码(1)Reg设计Reg是指令操作地主要对象,MIPS微处理器中一共32个32位寄存器。

该模块输入为 RsAddr,RtAddr,WriteAddr,RegWr,WriteData,clk,reset有两项输出 RsData,RtData。

其中当复位信号reset为1时所有寄存器清零,当复位信号为0且写信号有效时数据才写入writedata寄存器。

(其中0号寄存器永远为0)具体代码如下:module RegFile(input [4:0] RsAddr,input [4:0] RtAddr,input [4:0] WriteAddr,input RegWr,input [31:0] WriteData,input clk,input reset,output [31:0] RsData,output [31:0] RtData);reg [31:0] regs[0:31];assign RsData =(RsAddr==5'b0) ? 32'b0:regs[RsAddr];assign RtData =(RtAddr==5'b0) ? 32'b0:regs[RtAddr];integer i;always @(negedge clk) //下降沿回写到寄存器if(!reset&RegWr)regs[WriteAddr]=WriteData;else if(reset)for(i=0;i<32;i=i+1)regs[i]=4*i; //寄存器的值初始化为编号乘以4Endmodule(2)ALU设计微处理器支持add,sub,and,or,slt运算指令,需要用ALU单元实现运算,同时sw,lw,beq等指令也要用到ALU单元计算地址,比较数据,因此我们设计此模块输入为in1,in2,(此处要设置为signed类型,不然无法执行slt指令),ALUctr两个输出Res,zero。

MIPS单周期CPU实验报告

《计算机组成原理实验》实验报告(实验二)学院名称:专业(班级):学生姓名:学号:时间:2017 年11 月25 日成绩: 实验二:单周期CPU设计与实现一.实验目的(1) 掌握单周期CPU数据通路图的构成、原理及其设计方法;(2) 掌握单周期CPU的实现方法,代码实现方法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的方法;(5) 掌握单周期CPU的实现方法。

二.实验内容设计一个单周期的MIPSCPU,使其能实现下列指令:==> 算术运算指令==> 逻辑运算指令功能:rd←rs | rt;逻辑或运算。

==>移位指令==>比较指令==> 存储器读/写指令rt寄存器的内容保存到rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中。

即读取rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中的数,然后保存到rt寄存器中。

==> 分支指令特别说明:immediate是从PC+4地址开始和转移到的指令之间指令条数。

immediate 符号扩展之后左移2位再相加。

为什么要左移2位?由于跳转到的指令地址肯定是4的倍数(每条指令占4个字节),最低两位是“00”,因此将immediate放进指令码中的时候,是右移了2位的,也就是以上说的“指令之间指令条数”。

12特别说明:与beq不同点是,不等时转移,相等时顺序执行。

==>跳转指令==> 停机指令三.实验原理1.时间周期:单周期CPU指的是一条指令的执行在一个时钟周期内完成,然后开始下一条指令的执行,即一条指令用一个时钟周期完成。

电平从低到高变化的瞬间称为时钟上升沿,两个相邻时钟上升沿之间的时间间隔称为一个时钟周期。

时钟周期一般也称振荡周期(如果晶振的输出没有经过分频就直接作为CPU的工作时钟,则时钟周期就等于振荡周期。

若振荡周期经二分频后形成时钟脉冲信号作为CPU的工作时钟,这样,时钟周期就是振荡周期的两倍。

单周期CPU实验报告

MIPS-CPU设计实验报告实验名称:32位单周期MIPS-CPU设计姓名学号:刘高斯11072205实验日期:2014年12月19日目录前言MIPS简介------------------------------------------------------------- 3 实验目的------------------------------------------------------------- 3第一部分VERILOG HDL 语言实现部分实验内容------------------------------------------------------------- 4 试验环境------------------------------------------------------------- 4 模块简介------------------------------------------------------------- 4 实验截图------------------------------------------------------------- 5 实验感想------------------------------------------------------------- 5 实验代码------------------------------------------------------------- 6第二部分LOGISIM 语言实现部分实验内容------------------------------------------------------------- 16 实验环境------------------------------------------------------------- 16模块设计------------------------------------------------------------- 16 试验感想------------------------------------------------------------- 23前言一、MIPS简介MIPS是世界上很流行的一种RISC处理器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《计算机组成原理实验》实验报告(实验二)学院名称:专业(班级):学生姓名:学号:时间:2017 年11 月25 日成绩: 实验二:单周期CPU设计与实现一.实验目的(1) 掌握单周期CPU数据通路图的构成、原理及其设计方法;(2) 掌握单周期CPU的实现方法,代码实现方法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的方法;(5) 掌握单周期CPU的实现方法。

二.实验内容设计一个单周期的MIPSCPU,使其能实现下列指令:==> 算术运算指令==> 逻辑运算指令功能:rd←rs | rt;逻辑或运算。

==>移位指令==>比较指令==> 存储器读/写指令将rt寄存器的内容保存到rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中。

即读取rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中的数,然后保存到rt寄存器中。

==> 分支指令功能:if(rs=rt) pc←pc + 4 + (sign-extend)immediate <<2 else pc ←pc + 4特别说明:immediate是从PC+4地址开始和转移到的指令之间指令条数。

immediate 符号扩展之后左移2位再相加。

为什么要左移2位?由于跳转到的指令地址肯定是4的倍数(每条指令占4个字节),最低两位是“00”,因此将immediate放进指令码中的时候,是右移了2位的,也就是以上说的“指令之间指令条数”。

12特别说明:与beq不同点是,不等时转移,相等时顺序执行。

功能:if(rs>0) pc←pc + 4 + (sign-extend)immediate <<2 else pc ←pc + 4==>跳转指令==> 停机指令三.实验原理1.时间周期:单周期CPU指的是一条指令的执行在一个时钟周期内完成,然后开始下一条指令的执行,即一条指令用一个时钟周期完成。

电平从低到高变化的瞬间称为时钟上升沿,两个相邻时钟上升沿之间的时间间隔称为一个时钟周期。

时钟周期一般也称振荡周期(如果晶振的输出没有经过分频就直接作为CPU的工作时钟,则时钟周期就等于振荡周期。

若振荡周期经二分频后形成时钟脉冲信号作为CPU的工作时钟,这样,时钟周期就是振荡周期的两倍。

)CPU在处理指令时,一般需要经过以下几个步骤:(1) 取指令(IF):根据程序计数器PC中的指令地址,从存储器中取出一条指令,同时,PC根据指令字长度自动递增产生下一条指令所需要的指令地址,但遇到“地址转移”指令时,则控制器把“转移地址”送入PC,当然得到的“地址”需要做些变换才送入PC。

(2) 指令译码(ID):对取指令操作中得到的指令进行分析并译码,确定这条指令需要完成的操作,从而产生相应的操作控制信号,用于驱动执行状态中的各种操作。

(3) 指令执行(EXE):根据指令译码得到的操作控制信号,具体地执行指令动作,然后转移到结果写回状态。

(4) 存储器访问(MEM):所有需要访问存储器的操作都将在这个步骤中执行,该步骤给出存储器的数据地址,把数据写入到存储器中数据地址所指定的存储单元或者从存储器中得到数据地址单元中的数据。

(5) 结果写回(WB):指令执行的结果或者访问存储器中得到的数据写回相应的目的寄存器中。

单周期CPU,是在一个时钟周期内完成这五个阶段的处理。

对于不同的指令,需要执行的步骤是不同的,其中取字指令(lw)需要执行全部五个步骤。

因此,CPU的时间周期由取字指令决定。

2.指令类型:MIPS的三种指令类型:其中,op:为操作码;rs:只读。

为第1个源操作数寄存器,寄存器地址(编号)是00000~11111,00~1F;rt:可读可写。

为第2个源操作数寄存器,或目的操作数寄存器,寄存器地址(同上);rd:只写。

为目的操作数寄存器,寄存器地址(同上);sa:为位移量(shift amt),移位指令用于指定移多少位;funct:为功能码,在寄存器类型指令中(R类型)用来指定指令的功能与操作码配合使用;immediate:为16位立即数,用作无符号的逻辑操作数、有符号的算术操作数、数据加载(Load)/数据保存(Store)指令的数据地址字节偏移量和分支指令中相对程序计数器(PC)的有符号偏移量;address:为地址。

在本CPU设计中,由于指令的类型较少,所以所有指令均由操作码(op)确定。

在R 型指令中,功能码(funct)为000000。

3.控制线路图与数据通路:上图为CPU的数据通路和必要的控制线路图,其中Ins.Mem为指令存储器,Data.Mem 为数据存储器。

访问存储器时,先给出内存地址,然后由读或写信号控制操作。

对于寄存器组,先给出寄存器地址,读操作时,输出端就直接输出相应数据;而在写操作时,在WE 使能信号为1,在时钟边沿触发将数据写入寄存器。

4.控制信号:控制信号的作用控制信号名状态“0”状态“1”Reset初始化PC为0 PC接收新地址PCWre PC不更改,相关指令:halt PC更改,相关指令:除指令halt外ALUSrcA 来自寄存器堆data1输出,相关指令:add、sub、addi、or、and、ori、beq、bne、bgtz、slt、sw、lw来自移位数sa,同时,进行(zero-extend)sa,即{{27{0}},sa},相关指令:sllALUSrcB 来自寄存器堆data2输出,相关指令:add、sub、or、and、sll、slt、beq、bne、bgtz 来自sign或zero扩展的立即数,相关指令:addi、ori、sw、lwDBDataSrc 来自ALU运算结果的输出,相关指令:add、addi、sub、ori、or、and、slt、sll 来自数据存储器(Data MEM)的输出,相关指令:lwRegWre 无写寄存器组寄存器,相关指令:beq、bne、bgtz、sw、halt、j 寄存器组写使能,相关指令:add、addi、sub、ori、or、and、slt、sll、lwALU功能表附:本CPU的指令集并未用到ALU的全部功能。

5.主要模块接口说明:Instruction Memory:指令存储器,address,指令存储器地址输入端口DataIn,指令存储器数据输入端口(指令代码输入端口)DataOut,指令存储器数据输出端口(指令代码输出端口)InsMemRW,指令存储器读写控制信号,为0写,为1读Data Memory:数据存储器,address,数据存储器地址输入端口DataOut,数据存储器数据输出端口/RD,数据存储器读控制信号,为0读/WR,数据存储器写控制信号,为0写Register File:寄存器组Read Reg1,rs寄存器地址输入端口Read Reg2,rt寄存器地址输入端口Write Reg,将数据写入的寄存器端口,其地址来源rt或rd字段Write Data,写入寄存器的数据输入端口Read Data1,rs寄存器数据输出端口Read Data2,rt寄存器数据输出端口WE,写使能信号,为1时,在时钟边沿触发写入RST,寄存器清零信号,为0时寄存器清零ALU:算术逻辑单元result,ALU运算结果zero,运算结果标志,结果为0,则zero=1;否则zero=0sign,运算结果标志,结果最高位为0,则sign=0,正数;否则,sign=1,负数四.实验器材电脑一台,Xilinx Vivado 软件一套,Basys3板一块。

五.实验过程与结果1.各个指令对应的控制信号除异或运算(111)外,ALU 所有功能均被使用。

2.主要模块代码及仿真(1)控制单元(control unit) Verilog 代码:1.module controlUnit(2. input [5:0] opcode,3. input zero,4. input sign,5. output reg PCWre,6. output reg ALUSrcA,7. output reg ALUSrcB,8. output reg DBDataSrc,9. output reg RegWre,10. output reg InsMemRW,11. output reg RD,12. output reg WR,13. output reg RegDst,14. output reg ExtSel,15. output reg [1:0] PCSrc,16. output reg [2:0] ALUOp17.);18. initial begin19. RD = 1;20. WR = 1;21. RegWre = 0;22. InsMemRW = 0;23. end24. always@ (opcode) begin25.case(opcode)26. 6'b000000:begin // add27. PCWre = 1;28. ALUSrcA = 0;29. ALUSrcB = 0;30. DBDataSrc = 0;31. RegWre = 1;32. InsMemRW = 1;33. RD = 1;34. WR = 1;35. RegDst = 1;36. ALUOp = 3'b000;37. end38. 6'b000001:begin //addi39. PCWre = 1;40. ALUSrcA = 0;41. ALUSrcB = 1;42. DBDataSrc = 0;43. RegWre = 1;44. InsMemRW = 1;46. WR = 1;47. RegDst = 0;48. ExtSel = 1;49. ALUOp = 3'b000;50. end51. 6'b000010:begin //sub52. PCWre = 1;53. ALUSrcA = 0;54. ALUSrcB = 0;55. DBDataSrc = 0;56. RegWre = 1;57. InsMemRW = 1;58. RD = 1;59. WR = 1;60. RegDst = 1;61. ALUOp = 3'b001;62. end63. 6'b010000:begin // ori64. PCWre = 1;65. ALUSrcA = 0;66. ALUSrcB = 1;67. DBDataSrc = 0;68. RegWre = 1;69. InsMemRW = 1;70. RD = 1;71. WR = 1;72. RegDst = 0;73. ExtSel = 0;74. ALUOp = 3'b011;75. end76. 6'b010001:begin //and77. PCWre = 1;78. ALUSrcA = 0;79. ALUSrcB = 0;80. DBDataSrc = 0;81. RegWre = 1;82. InsMemRW = 1;83. RD = 1;84. WR = 1;85. RegDst = 1;86. ALUOp = 3'b100;87. end88. 6'b010010:begin // or90. ALUSrcA = 0;91. ALUSrcB = 0;92. DBDataSrc = 0;93. RegWre = 1;94. InsMemRW = 1;95. RD = 1;96. WR = 1;97. RegDst = 1;98. ALUOp = 3'b011;99. end100. 6'b011000:begin //sll 101. PCWre = 1;102. ALUSrcA = 1; 103. ALUSrcB = 0; 104. DBDataSrc = 0; 105. RegWre = 1;106. InsMemRW = 1; 107. RD = 1;108. WR = 1;109. RegDst = 1;110. ALUOp = 3'b010; 111. end112. 6'b011100:begin //slt 113. PCWre = 1;114. ALUSrcA = 0; 115. ALUSrcB = 0; 116. DBDataSrc = 0; 117. RegWre = 1;118. InsMemRW = 1; 119. RD = 1;120. WR = 1;121. RegDst = 1;122. ALUOp = 3'b110; 123. end124. 6'b100110:begin //sw 125. PCWre = 1;126. ALUSrcA = 0; 127. ALUSrcB = 1; 128. RegWre = 0;129. InsMemRW = 1; 130. RD = 1;131. WR = 0;132. ExtSel =1;133. ALUOp = 3'b000; 134. end135. 6'b100111:begin //lw 136. PCWre = 1;137. ALUSrcA = 0; 138. ALUSrcB = 1; 139. DBDataSrc = 1; 140. RegWre = 1;141. InsMemRW = 1; 142. RD = 0;143. WR = 1;144. RegDst = 0;145. ExtSel = 1;146. ALUOp = 3'b000; 147. end148. 6'b110000:begin //beq 149. PCWre = 1;150. ALUSrcA = 0; 151. ALUSrcB = 0; 152. RegWre = 0;153. InsMemRW = 1; 154. RD = 1;155. WR = 1;156. ExtSel = 1;157. ALUOp = 3'b001; 158. end159. 6'b110001:begin //bne 160. PCWre = 1;161. ALUSrcA = 0; 162. ALUSrcB = 0; 163. RegWre = 0;164. InsMemRW = 1; 165. RD = 1;166. WR = 1;167. ExtSel = 1;168. ALUOp = 3'b001; 169. end170. 6'b110010:begin171. PCWre = 1;172. ALUSrcA = 0; 173. ALUSrcB = 0; 174. RegWre = 0;175. InsMemRW = 1; 176. RD = 1;177. WR = 1;178. ExtSel = 1;179. ALUOp = 3'b001;180. end181. 6'b111000:begin //j182. PCWre = 1;183. RegWre = 0;184. InsMemRW = 1;185. RD = 1;186. WR = 1;187. ALUOp = 3'b010;188. end189. 6'b111111:begin //halt190. PCWre = 1;191. RegWre = 0;192. InsMemRW = 1;193. RD = 1;194. WR = 1;195. end196.default:begin197. RD = 1;198. WR = 1;199. RegWre = 0;200. InsMemRW = 0;201. end202. endcase203. end204. always@(opcode or zero or sign) begin205.if(opcode == 6'b111000) // j206. PCSrc = 2'b10;207.else if(opcode[5:3] == 3'b110) begin 208.if(opcode[2:0] == 3'b000) begin 209.if(zero == 1)210. PCSrc = 2'b01;211.else212. PCSrc = 2'b00;213. end214.else if(opcode[2:0] == 3'b001) begin 215.if(zero == 0)216. PCSrc = 2'b01;217.else218. PCSrc = 2'b00;219. end220.else begin221.if(zero == 0 && sign == 0) 222. PCSrc = 2'b01;223.else224. PCSrc = 2'b00;225. end226. end227.else begin228. PCSrc = 2'b00;229. end230. end231.endmodule仿真截图:(2)程序计数器(PC)Verilog代码:1.module PC(2. input clk,3. input [31:0] PCin,4. input PCWre,5. input Reset,6. output reg [31:0] PCout7.);8. initial begin9. PCout <= 0;10. end11. always@(posedge clk) begin12.if(Reset == 0) begin13. PCout <= 0;14. end15.else if(PCWre == 0) begin16. PCout <= PCout;17. end18.else begin19. PCout <= PCin;20. end21. end22.endmodule仿真截图:(3)程序存储器(instruction memory)Verilog代码:1.module IMemory(2. input InsMemRW,3. input [31:0] address,4. output reg [31:0] DataOut5.);6. reg [7:0] mem [0:127];7. initial begin8. DataOut = 32'b111111_0000000_0000000_0000000_00000;9. $readmemb("C:/Users/ACER/Desktop/-p/project_1/rom_data.coe", mem);10. end11. always@(address or InsMemRW) begin12.if(InsMemRW == 1) begin13. DataOut[31:24] <= mem[address];14. DataOut[23:16] <= mem[address+1];15. DataOut[15:8] <= mem[address+2];16. DataOut[7:0] <= mem[address+3];17. end18. end19.endmodule仿真截图:(4)ALUVerilog代码:1.module ALU(2. input [2:0] ALUopcode,3. input [31:0] rega,4. input [31:0] regb,5. output reg [31:0] result,6. output zero,7. output sign8.);9.assign zero = (result==0)?1:0;10.assign sign = result[31];11.always @( ALUopcode or rega or regb ) begin12.case (ALUopcode)13. 3'b000 : result = rega + regb;14. 3'b001 : result = rega - regb;15. 3'b010 : result = regb << rega;16. 3'b011 : result = rega | regb;17. 3'b100 : result = rega & regb;18. 3'b101 : result = (rega < regb)?1:0; // 不带符号比较19. 3'b110 : begin // 带符号比较20.if (rega<regb &&(( rega[31] == 0 && regb[31]==0) ||21. (rega[31] == 1 && regb[31]==1))) result = 1;22.else if (rega[31] == 0 && regb[31]==1) result = 0;23.else if ( rega[31] == 1 && regb[31]==0) result = 1;24.else result = 0;25. end26. 3'b111 : result = rega ^ regb;27. endcase28.end29.endmodule仿真截图:(5)寄存器堆Verilog代码:1.module RegFile(2. input CLK,3. input RST,4. input RegWre,5. input [4:0] ReadReg1,6. input [4:0] ReadReg2,7. input [4:0] WriteReg,8. input [31:0] WriteData,9. output [31:0] ReadData1,10. output [31:0] ReadData211.);12. reg [31:0] regFile[1:31]; // 寄存器定义必须用reg 类型13. integer i;14. assign ReadData1 = (ReadReg1 == 0) ? 0 : regFile[ReadReg1]; // 读寄存器数据15. assign ReadData2 = (ReadReg2 == 0) ? 0 : regFile[ReadReg2];16. always @ (negedge CLK) begin // 必须用时钟边沿触发17.if (RST==0) begin18.for(i=1;i<32;i=i+1)19. regFile[i] <= 0;20. end21.else if(RegWre == 1 && WriteReg != 0) begin22. regFile[WriteReg] <= WriteData;23. end24. end25.26.endmodule仿真截图:(6)数据存储单元(Data Memory)Verilog代码:1.module DataMemory(2. input clk,3. input [31:0] address,4. input RD,5. input WR,6. input [31:0] DataIn,7. output [31:0] DataOut8.);9.10.reg [7:0] ram[0:127];11.integer i;12.initial begin;13.for(i=0;i<128;i=i+1)14. ram[i]<=0;15.end16.// output17.assign DataOut[7:0] = (RD == 0)? ram[address+3]:8'bz;18.assign DataOut[15:8] = (RD == 0)? ram[address+2]:8'bz;19.assign DataOut[23:16] = (RD == 0)? ram[address+1]:8'bz;20.assign DataOut[31:24] = (RD == 0)? ram[address]:8'bz;21.// input22.always@(negedge clk) begin23.if(WR == 0) begin24.if(address>=0 && address<128) begin25. ram[address] <= DataIn[31:24];26. ram[address+1] <= DataIn[23:16];27. ram[address+2] <= DataIn[15:8];28. ram[address+3] <= DataIn[7:0];29. end30. end31.end32.endmodule仿真截图:3.测试程序:测试程序如下:地址汇编程序指令代码op(6)rs(5) rt(5) rd(5)/immediate(16)16进制数代码0x00000000 addi $1,$0,8 000001 00000 00001 0000 0000 0000 1000 0401 0008 0x00000004 ori $2,$0,2 010000 00000 00010 0000 0000 0000 0010 4002 0002 0x00000008 add $3,$2,$1 000000 00010 00001 00011 00000 000000 0041 1800 0x0000000C sub $5,$3,$2 000010 00011 00010 00101 00000 000000 0862 2800 0x00000010 and $4,$5,$2 010001 00011 00010 00100 00000 000000 4462 20000x00000014 or $8,$4,$2 010010 00100 00010 01000 00000 000000 4882 4000 0x00000018 sll $8,$8,1 011000 00000 01000 01000 00001 000000 6008 4040 0x0000001C bne $8,$1,-2 (≠,转110001 01000 00001 1111 1111 1111 1110 C501 FFFE18)0x00000020 slt $6,$2,$1 011100 00010 00001 00110 00000 000000 7041 3000 0x00000024 slt $7,$6,$0 011100 00110 00000 00111 00000 000000 70C0 3800 0x00000028 addi $7,$7,8 000001 00111 00111 0000 0000 0000 1000 04E1 0008 0x0000002C beq $7,$1,-2 (≠,转110000 00111 00001 1111 1111 1111 1110 C0E1 FFFE28)0x00000030 sw $2,4($1) 100110 00001 00010 0000 0000 0000 0100 9822 0000 0x00000034 lw $9,4($1) 100111 00001 01001 0000 0000 0000 0100 9C29 0004 0x00000038 bgtz $9,2 (=0) 110010 01001 00000 0000 0000 0000 0010 C920 0002 0x0000003C addi $9,$0,15 000001 00000 01001 0000 0000 0000 1111 0409 000F 0x00000040 j 0x00000038 111000 00 0000 0000 0000 0000 0000 1110 E000 000E 0x00000044 halt 111111 00 0000 0000 0000 0000 0000 0000 FC00 0000 机器代码(.roe):仿真截图:(1)addi $1, $0, 8 至bne $1, $8, -2(2)slt $6, $2, $1 至lw $9, 4($1) (3)bgtz $9, $2 至halt4 烧板(1)addi $1,$0,8:当前PC和下一条PC:Rs寄存器:Rt寄存器:ALU结果及写寄存器数据:(2)ori $2,$0,2当前PC和下一条PC:Rs寄存器:Rt寄存器:ALU结果及写寄存器数据:(3)add $3,$2,$1 当前PC和下一条PC:Rs寄存器:Rt寄存器:ALU结果及写寄存器数据:六.实验心得这次实验中,在设计CPU中各个模块时,遇到的问题并不大。