单周期CPU设计

计算机组成原理实验报告 单周期CPU的设计与实现

1个时钟周期 Clock 电子科技大学计算机科学与工程学院标 准 实 验 报 告(实验)课程名称: 计算机组成原理实验 电子科技大学教务处制表电 子 科 技 大 学 实 验 报 告学生姓名: 郫县尼克杨 学 号: 2014 指导教师:陈虹 实验地点: 主楼A2-411 实验时间:12周-15周一、 实验室名称:主楼A2-411二、 实验项目名称:单周期CPU 的设计与实现。

三、 实验学时:8学时四、 实验原理:(一) 概述单周期(Single Cycle )CPU 是指CPU 从取出1条指令到执行完该指令只需1个时钟周期。

一条指令的执行过程包括:取指令→分析指令→取操作数→执行指令→保存结果。

对于单周期CPU 来说,这些执行步骤均在一个时钟周期内完成。

(二) 单周期cpu 总体电路本实验所设计的单周期CPU 的总体电路结构如下。

(三) MIPS 指令格式化MIPS 指令系统结构有MIPS-32和MIPS-64两种。

本实验的MIPS 指令选用MIPS-32。

以下所说的MIPS 指令均指MIPS-32。

MIPS 的指令格式为32位。

下图给出MIPS 指令的3种格式。

本实验只选取了9条典型的MIPS 指令来描述CPU 逻辑电路的设计方法。

下图列出了本实验的所涉及到的9条MIPS 指令。

五、 实验目的1、掌握单周期CPU 的工作原理、实现方法及其组成部件的原理和设计方法,如控制器、运算器等。

?2、认识和掌握指令与CPU 的关系、指令的执行过程。

?3、熟练使用硬件描述语言Verilog 、EDA 工具软件进行软件设计与仿真,以培养学生的分析和设计CPU 的能力。

六、 实验内容(一)拟定本实验的指令系统,指令应包含R 型指令、I 型指令和J 型指令,指令数为9条。

(二)CPU 各功能模块的设计与实现。

(三)对设计的各个模块的仿真测试。

(四)整个CPU 的封装与测试。

七、 实验器材(设备、元器件):(一)安装了Xilinx ISE Design Suite 13.4的PC 机一台(二)FPGA 开发板:Anvyl Spartan6/XC6SLX45(三)计算机与FPGA 开发板通过JTAG (Joint Test Action Group )接口连接,其连接方式如图所示。

CPU设计实践教程6-Minisys-1单周期CPU控制器的设计

指令操作码 ori

addiu

lw

sw

beq jump

RegDst

0

0

0

000000 R-format

1

RegDST = R-format

wire R_format;

assign R_format = (Opcode==6'b000000)? 1'b1:1'b0; assign RegDST = R_format; //说明目标是rd,否则是rt

output Sftmd; output[1:0] ALUOp;

// 他I-类型指令 // 为1表明是移位指令 // 是R-类型或I_format=1时位1为1, beq、bne指令则 // 位0为1

2021/9/5 P.22

单周期控制器设计

RegDST的控制电路

op 001101 001001 100011 101011 000100 000010

output nBranch; // 为1表明是Bne指令

output Jmp;

// 为1表明是J指令

output Sftmd; // 为1表明是移位指令

2021/9/5 P.25

单周期控制器设计

练习2

请给出下列控制信号电路的Verilog描述

assign Sw = ????? assign ALUSrc = ????? assign Branch = ????? assign nBranch = ????? assign Jmp = ?????

2021/9/5 P.10

创建一个项目

在打开的Default Port对话框中选择的FPGA器件为 xc7a100tfgg484-1,如图所示,点击Next。

单周期CPU设计实验报告

单周期CPU设计实验报告一、引言计算机是现代信息社会必不可少的工具,而CPU作为计算机的核心部件,承担着执行指令、进行运算和控制系统资源的任务。

随着科技的进步和计算能力的需求,CPU的设计也趋于复杂和高效。

本次实验旨在设计一种单周期CPU,探究其设计原理和实现过程,并通过实验验证其正确性和性能。

二、理论基础1.单周期CPU概述单周期CPU即每个时钟周期内只完成一条指令的处理,它包括指令取址阶段(IF)、指令译码阶段(ID)、执行阶段(EX)、访存阶段(MEM)和写回阶段(WB)等多个阶段。

每条指令都顺序地在这些阶段中执行,而不同的指令所需的时钟周期可能不同。

2.控制信号单周期CPU需要根据不同的指令类型产生不同的控制信号来控制各个阶段的工作。

常见的控制信号包括时钟信号(clk)、使能信号(En)、写使能信号(WE)和数据选择信号(MUX)等。

这些信号的产生需要通过译码器、控制逻辑电路和时序逻辑电路等来实现。

三、实验设计本次实验采用的单周期CPU包括以下五个阶段:指令取址阶段、指令译码阶段、执行阶段、访存阶段和写回阶段。

每个阶段的具体操作如下:1.指令取址阶段(IF)在IF阶段,通过计数器实现程序计数器(PC)的自增功能,并从存储器中读取指令存储地址所对应的指令码。

同时,设置PC使能信号,使其可以更新到下一个地址。

2.指令译码阶段(ID)在ID阶段,对从存储器中读取的指令码进行解码,确定指令的操作类型和操作数。

同时,根据操作类型产生相应的控制信号,如使能信号、写使能信号和数据选择信号等。

3.执行阶段(EX)在EX阶段,根据ID阶段产生的控制信号和操作数,进行相应的算术逻辑运算。

这里可以包括加法器、乘法器、逻辑运算器等。

4.访存阶段(MEM)在MEM阶段,根据EX阶段的结果,进行数据存储器的读写操作。

同时,将读取的数据传递给下一个阶段。

5.写回阶段(WB)在WB阶段,根据MEM阶段的结果,将数据传递给寄存器文件,并将其写入指定的寄存器。

单周期CPU设计总结

单周期CPU设计总结单周期CPU⼀、设计思路1、CPU的意义CPU是计算机的核⼼,因为它是计算机指令的处理单元。

计算机体系结构包含两个⽅⾯,⼀个⽅⾯是指令集,⼀个⽅⾯是硬件实现。

指令集是计算机被定义拥有的执⾏指令,计算机通过⽀持指令集的运⾏,来完成计算⼯作并为程序员编程服务。

硬件实现则是具体的硬件去实现指令集,这个硬件实现的核⼼就是CPU的设计。

这⾥写的CPU的设计是32位机器的CPU,指令和数据均为32位。

⽀持指令为简化mips指令集。

2、CPU的设计CPU的设计包含数据通路的设计和控制器的设计。

数据通路是执⾏指令必须的硬件(ALU、IM、DM、GRF等),控制器则是根据指令产⽣相应控制信号,来控制相应硬件以⽀持多条指令。

数据通路设计CPU的功能是⽀持指令集,因此硬件设计是为了执⾏指令。

设计CPU的结构的⽅法:先选择⼀条需要经过最多硬件的指令,来为它构建数据通路。

再依据其他指令在已有数据通路上添加硬件或线路,直到数据通路⽀持所有指令。

控制器设计在已有的数据通路基础上,针对每⼀条指令,列出其所需要的控制信号,每⼀组控制信号对应⼀种指令的全部执⾏。

将指令相应字段和部分计算结果作为控制器的输⼊,控制信号作为输出,依据上述映射关系(真值表)设计控制器。

⼆、实际操作0、设计说明CPU架构的设计是没有很多约束的,基本要求就是能够⽀持指令集,基于不同的考量可以有不同的设计。

举例来说:对于beq指令是否跳转的判断,可以借⽤ALU的减法计算,也可以直接增设CMP⽐较器得出,两种⽅式都可以,因为功能正确。

为了提⾼吞吐量,或者为了节省成本,会选择⼀些特别的设计,这⼀点在流⽔线CPU 的设计上可以明显地看出。

CPU具体设计的⽅法是我下⾯进⾏的⼏步:列出所需指令,写出功能模块,连接模块,构造控制器,全部连接起来。

这些表格对最终代码实现⼗分重要,因为代码量较⼤,先从表格检查起,再依据表格写码可以减少bug。

1、⽀持指令列出⽀持指令并将其分类:str ld cal_r cal_i lui b_type j jr jal jalr shamtsw lw addu ori beq sllsubu slti sraslt addiu srlsllvsravsrlv2、功能模块先按照lw指令列出所需功能模块(lw经过模块最多),再依次检查现有模块是否⽀持其余指令,若不能⽀持,则添加相应模块。

第5章单周期CPU及其Verilog HDL设计

op 6 bits

rs 5 bits

rt 5 bits

rd 5 bits

sa 5 bits

funct 6 bits

I Format

31

(rs, rt: Register Numbers, imm: Immediate)

26 25 21 20 16 15 0

时钟上升沿(0到 1的变化) 一个周期

Clock

下降沿

指令1

指令2

指令3

指令4

在时钟上升沿保存指令的结果和下一条指令的地址

c

5.1 执行指令所需的硬件电路

• 指令的执行过程

取指令 执行指令

—读取指令

程序计数器的值作为地址从存储器中 取指令 形 成 下 一 条 指 令 地 址

—分析指令 —按指令规定内容执行指令 —检查有无中断请求

c

取指部件(Instruction Fetch Unit)

• 每条指令都有的公共操作

– 取指令: M[PC] – 更新PC:PC ← PC + 4

转移(Branch and Jump)时,PC内容再次被更新为 “转移目标地址 ” 下地址 逻辑

Next Address Logic Address Instruction Word

rs rt P C a do Inst mem

we rna

rnb qa wn Regfile d clk qb b ALU

rd

a

aluc z r

clock

c

Sll指令 (Shift Left Logical)

sll rd, rt, sa ; rd <-- rt << sa

MIPS单周期CPU实验报告

MIPS单周期CPU实验报告一、实验目的本实验旨在设计一个基于MIPS指令集架构的单周期CPU,具体包括CPU的指令集设计、流水线的划分与控制信号设计等。

通过本实验,可以深入理解计算机组成原理中的CPU设计原理,加深对计算机体系结构的理解。

二、实验原理MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集(RISC)架构的处理器设计,大大简化了指令系统的复杂性,有利于提高执行效率。

MIPS指令集由R、I、J三种格式的指令组成,主要包括算术逻辑运算指令、存储器访问指令、分支跳转指令等。

在单周期CPU设计中,每个指令的执行时间相同,每个时钟周期只执行一个指令。

单周期CPU的主要部件包括指令内存(IM)、数据存储器(DM)、寄存器文件(RF)、运算单元(ALU)、控制器等。

指令执行过程主要分为取指、译码、执行、访存、写回等阶段。

三、实验步骤1.设计CPU指令集:根据MIPS指令集的格式和功能,设计符合需求的指令集,包括算术逻辑运算指令、存储器访问指令、分支跳转指令等。

2.划分CPU流水线:将CPU的执行过程划分为取指、译码、执行、访存、写回等阶段,确定每个阶段的功能和控制信号。

3.设计控制器:根据CPU的流水线划分和指令集设计,设计控制器实现各个阶段的控制信号生成和时序控制。

4.集成测试:进行集成测试,验证CPU的指令执行功能和正确性,调试并优化设计。

5.性能评估:通过性能评估指标,如CPI(平均时钟周期数)、吞吐量等,评估CPU的性能优劣,进一步优化设计。

四、实验结果在实验中,成功设计了一个基于MIPS指令集架构的单周期CPU。

通过集成测试,验证了CPU的指令执行功能和正确性,实现了取指、译码、执行、访存、写回等阶段的正常工作。

同时,通过性能评估指标的测量,得到了CPU的性能参数,如CPI、吞吐量等。

通过性能评估,发现了CPU的性能瓶颈,并进行了相应的优化,提高了CPU的性能表现。

单周期cpu课程设计

单周期cpu课程设计一、课程目标知识目标:1. 学生能理解单周期CPU的工作原理,掌握其内部结构及功能。

2. 学生能描述单周期CPU的指令执行过程,包括取指、译码、执行、访存、写回等阶段。

3. 学生能解释单周期CPU中时钟、指令和数据的关系,并分析其性能特点。

技能目标:1. 学生能运用所学知识,设计并实现一个简单的单周期CPU。

2. 学生能运用仿真软件对单周期CPU进行功能仿真,验证其正确性。

3. 学生能通过课程学习,培养自己的逻辑思维和问题解决能力。

情感态度价值观目标:1. 学生能对计算机硬件及CPU产生兴趣,激发学习热情。

2. 学生能认识到CPU在计算机系统中的核心地位,增强对计算机科学的尊重和热爱。

3. 学生能在团队协作中发挥积极作用,培养合作精神和沟通能力。

课程性质:本课程为计算机科学与技术专业核心课程,旨在让学生了解CPU的基本原理,掌握单周期CPU的设计方法。

学生特点:学生已经具备一定的数字逻辑电路基础,具有一定的编程能力和逻辑思维能力。

教学要求:结合学生特点,注重理论与实践相结合,引导学生通过课程学习,达到课程目标所规定的知识、技能和情感态度价值观要求。

在教学过程中,关注学生的个体差异,鼓励学生积极参与,培养其独立思考和解决问题的能力。

通过课程目标的分解,确保教学设计和评估的针对性和有效性。

二、教学内容1. 单周期CPU概述:介绍CPU的发展历程,单周期CPU的概念及其在计算机系统中的作用。

教材章节:第1章 计算机系统概述2. 单周期CPU内部结构:讲解CPU的内部组成部分,包括控制单元、算术逻辑单元(ALU)、寄存器组、程序计数器等。

教材章节:第2章 CPU内部结构3. 指令集与指令执行过程:分析指令集的设计,讲解单周期CPU指令执行过程中各阶段的任务和实现方法。

教材章节:第3章 指令集与指令执行4. 时序控制与性能分析:探讨时钟、指令和数据的关系,分析单周期CPU的性能特点。

教材章节:第4章 时序控制与性能分析5. 单周期CPU设计方法:介绍设计单周期CPU的步骤,包括电路设计、指令集设计、时序控制等。

单周期cpu设计文档

Extop

O

控制 ext 拓展方式 00:无符号扩展 01:高 16 位补 0 10:低 16 位补 0

Aluop[2:0]

O

控制 cpu 进行相应的运算 000:加 001:减 01unc[5:0]

100001 000000 100011 000000 001101 100011 101011 000100 001111 000000 000000

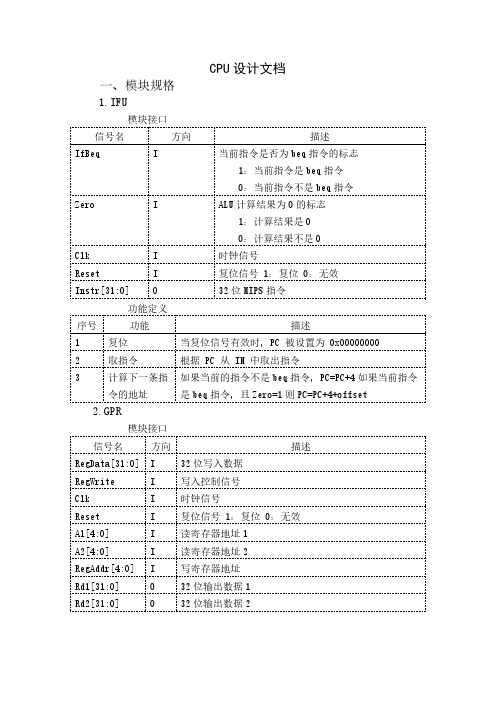

2.GPR

模块接口 信号名 RegData[31:0] RegWrite Clk Reset A1[4:0] A2[4:0] RegAddr[4:0] Rd1[31:0] Rd2[31:0] 方向 I I I I I I I O O 32 位写入数据 写入控制信号 时钟信号 复位信号 1:复位 0:无效 读寄存器地址 1 读寄存器地址 2 写寄存器地址 32 位输出数据 1 32 位输出数据 2 描述

Opcode[5:0]

addu RegDst RegWrite ALUsrc MemtoReg MemWrite nPC_sel 1 1 0 0 0 0

subu 1 1 0 0 0 0

ori 0 1 1 0 0 0

lw 0 1 1 1 0 0

sw X 0 1 X 1 0

beq X 0 0 X 0 1

功能定义 序号 1 2 3 复位 取指令 计算下一条指 令的地址 功能 描述 当复位信号有效时,PC 被设置为 0x00000000 根据 PC 从 IM 中取出指令 如果当前的指令不是 beq 指令,PC=PC+4 如果当前指令 是 beq 指令,且 Zero=1 则 PC=PC+4+offset

MemtoReg= o5 o4 o3 o2 o1o0

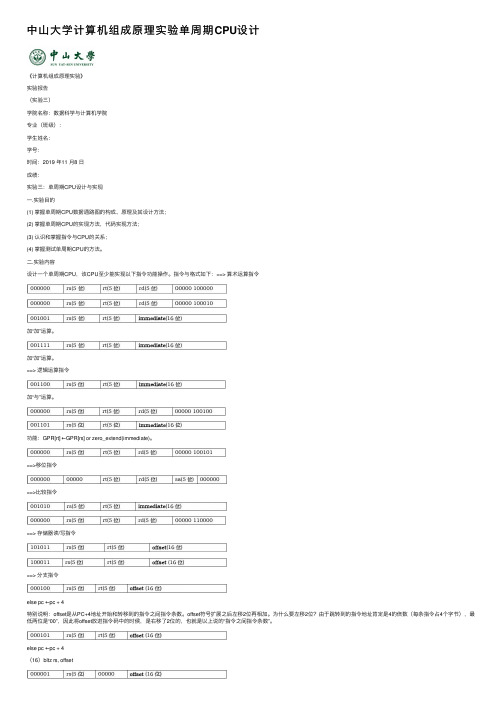

中山大学计算机组成原理实验 单周期CPU设计

《计算机组成原理实验》实验报告(实验三)学院名称:数据科学与计算机学院专业(班级):学生姓名:学号:时间:2019 年11 月8 日成绩:实验三:单周期CPU设计与实现一.实验目的(1) 掌握单周期CPU数据通路图的构成、原理及其设计方法;(2) 掌握单周期CPU的实现方法,代码实现方法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的方法。

二.实验内容设计一个单周期CPU,该CPU至少能实现以下指令功能操作。

指令与格式如下:==> 算术运算指令加“加”运算。

加“加”运算。

==> 逻辑运算指令加“与”运算。

功能:GPR[rt] ←GPR[rs] or zero_extend(immediate)。

==>移位指令==>比较指令==> 存储器读/写指令==> 分支指令else pc ←pc + 4特别说明:offset是从PC+4地址开始和转移到的指令之间指令条数。

offset符号扩展之后左移2位再相加。

为什么要左移2位?由于跳转到的指令地址肯定是4的倍数(每条指令占4个字节),最低两位是“00”,因此将offset放进指令码中的时候,是右移了2位的,也就是以上说的“指令之间指令条数”。

else pc ←pc + 4(16)bltz rs, offsetelse pc ←pc + 4。

==>跳转指令(17)j addr说明:由于MIPS32的指令代码长度占4个字节,所以指令地址二进制数最低2位均为0,将指令地址放进指令代码中时,可省掉!这样,除了最高6位操作码外,还有26位可用于存放地址,事实上,可存放28位地址,剩下最高4位由pc+4最高4位拼接上。

==> 停机指令功能:停机;不改变PC的值,PC保持不变。

三.实验原理单周期CPU指的是一条指令的执行在一个时钟周期内完成,然后开始下一条指令的执行,即一条指令用一个时钟周期完成。

电平从低到高变化的瞬间称为时钟上升沿,两个相邻时钟上升沿之间的时间间隔称为一个时钟周期。

mips单周期cpu课程设计

mips单周期cpu课程设计一、课程目标知识目标:1. 掌握MIPS单周期CPU的基本结构和工作原理;2. 了解指令集、指令执行过程和指令周期;3. 学会分析并设计简单的MIPS指令;4. 理解CPU性能指标,如时钟频率、吞吐率等。

技能目标:1. 能够运用硬件描述语言(如Verilog)进行单周期CPU的设计与仿真;2. 能够独立编写简单的MIPS汇编程序,并在单周期CPU上运行;3. 能够分析单周期CPU的性能,并进行优化;4. 培养学生的团队合作能力和问题解决能力。

情感态度价值观目标:1. 培养学生对计算机组成原理和硬件设计的兴趣,激发学生的创新意识;2. 增强学生的工程素养,使其认识到工程实践在计算机科学领域的重要性;3. 培养学生严谨、细致、负责任的科学态度,提高学生的自主学习能力。

本课程针对高中年级学生,课程性质为实践性较强的硬件课程。

结合学生特点,课程目标注重理论与实践相结合,通过设计单周期CPU,使学生深入理解计算机硬件原理,提高实践能力。

在教学要求上,注重培养学生的团队合作精神,提高学生分析和解决问题的能力,为后续计算机组成原理及相关课程打下坚实基础。

通过本课程的学习,学生将能够独立完成单周期CPU的设计与仿真,具备一定的硬件编程能力。

二、教学内容1. 引言:介绍CPU在计算机系统中的作用,引出MIPS单周期CPU的概念及其重要性。

相关教材章节:第一章 计算机系统概述2. MIPS单周期CPU基本结构:讲解CPU的基本组成部分,包括寄存器组、控制单元、算术逻辑单元(ALU)、数据通路等。

相关教材章节:第二章 计算机组成原理3. 指令集与指令执行:分析MIPS指令集特点,讲解指令执行过程和指令周期。

相关教材章节:第三章 指令系统4. 硬件描述语言与单周期CPU设计:介绍Verilog硬件描述语言,通过实例讲解如何使用Verilog设计单周期CPU。

相关教材章节:第四章 硬件描述语言与数字电路设计5. 单周期CPU仿真与优化:指导学生进行单周期CPU的仿真,分析性能瓶颈,探讨优化方案。

电子科技大学CPU设计:精简指令集(RISC)32位单周期cpu设计

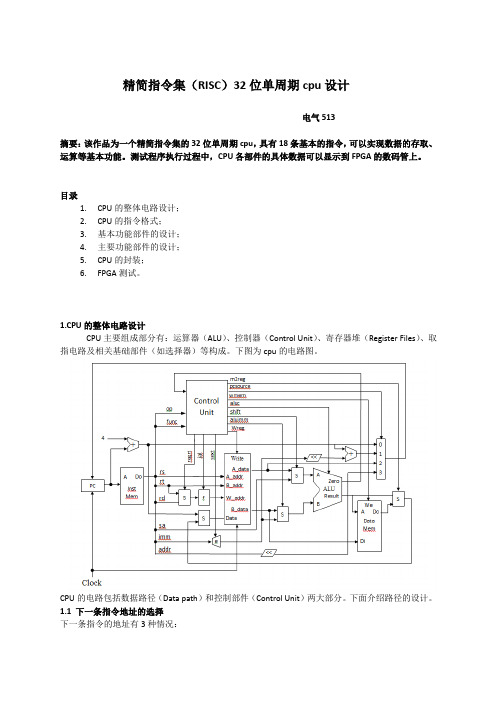

精简指令集(RISC)32位单周期cpu设计电气513摘要:该作品为一个精简指令集的32位单周期cpu,具有18条基本的指令,可以实现数据的存取、运算等基本功能。

测试程序执行过程中,CPU各部件的具体数据可以显示到FPGA的数码管上。

目录1.CPU的整体电路设计;2.CPU的指令格式;3.基本功能部件的设计;4.主要功能部件的设计;5.CPU的封装;6.FPGA测试。

1.CPU的整体电路设计CPU主要组成部分有:运算器(ALU)、控制器(Control Unit)、寄存器堆(Register Files)、取指电路及相关基础部件(如选择器)等构成。

下图为cpu的电路图。

CPU的电路包括数据路径(Data path)和控制部件(Control Unit)两大部分。

下面介绍路径的设计。

1.1 下一条指令地址的选择下一条指令的地址有3种情况:1.程序不转移时下一条指令的地址为PC+4;2.执行beq和bne指令发生转移时,下一条指令的地址是PC加4,再加上符号扩展的偏移量左移2位的和;3.执行j指令时转移的目标地址是指令中的低26位地址左移2位,再与PC+4的高4位拼接在一起。

下一条指令地址的产生和选择电路如图所示。

图中控制器(Control Unit)根据op、func和zero(对于beq和bne指令)信号产生相应的转移控制选择信号pcsource。

1.2 ALU的输入端ALU的输入端有2个:A输入端和B输入端。

A、B输入端分别有2种输入情况。

对于A输入端,有寄存器堆的A_data和移位数sa输入。

对于B输入端,有寄存器堆的B_data和符号扩展后的立即数imm输入。

其输入数据路径如图所示。

ALU的A、B端具体输入哪路数据由控制器(Control Unit)根据指令译码产生控制信号shift和aluimm 来选择。

1.3寄存器堆的输入端寄存器堆的A_addr和B_addr的输入来自指令,分别只有一种输入,W_addr有2种,而Data有4种输入。

【最新】CPU实验——单周期MIPS处理器设计

单周期MIPS处理器设计实验报告完成人:笪腾飞2012011263一、实验目的1、设计一个32位的单周期MIPS处理器,具备定时器、数码管等外设;2、编写一个编译器,可以将mips代码编译为二进制机器码;3、编写一个计算两个整数的最大公约数的汇编程序。

二、设计方案根据理论课所学的单周期MIPS处理器数据通路的知识,结合本次试验的具体要求,最终设计方案如下:1、系统时钟为了综合后能够在开发板上正确运行程序,我们决定采取50MHz的CPU时钟,因此编写了一个时钟分频模块,对开发板提供的100MHz时钟进行二分频,从而得到50MHz时钟。

2、PC产生模块原理图如下:如上图左半部分所示,多路选择器由一个always语句中的if…else if…else语句实现。

其中,将ALU中的加减法部分提取出来实现一个加法器,用于产生PC+4和ConBA两个PC来源。

将I型指令中的16位立即数左移两位后再符号位j m扩展成32位地址,与PC+4相加得到分支地址ConBA 。

将跳转指令中的26位目标地址左移两位后,与当前PC的高四位拼接得到跳转地址JT。

将第一个操作数寄存器中的值取出作为PC的一个输入,这是为了实现jr和jalr指令,从$Xp和$Ra寄存器中读取跳转地址。

ILLOP和XADR分别是发生中断和异常时的跳转地址。

下一指令地址的选择由PCSrc决定,而PCSrc是译码后由控制信号模块根据每条指令的操作码(opcode)和函数码(funct)产生。

3、译码模块原理图如上图右半部分所示,将PC作为ROM模块的地址输入,输出即为PC所对应的指令。

分别取出指令中的某些片段,得到$Rs,$Rt,$Rd,shamt,funct,16位立即数和26位跳转地址。

4、控制模块控制模块即控制信号产生模块,六位操作码OpCode,六位函数码[5:0] Funct,定时器中断信号irq和PC最高位PC31作为输入,输出为以下控制信号:(1) R型指令指示信号IsR,值为1表示当前指令为R型指令,否则非R型指令;(2) PC产生的选择信号[2:0] PCSrc,取值0,1,2,3,4及其它,分别选择下一指令不同的PC;(3) 目的寄存器选择信号[1:0]RegDst,被写入的寄存器有四种选择:$Rd,$Rt,$Ra,$Xp,分别由RegDst不同取值完成选择;(4) 写寄存器使能信号RegWr,值为1表示允许对寄存器进行写操作;(5) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将移位量shamt 进行0扩展后作为输入,值为0表示将$Rs寄存器中的值作为输入;(6) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将扩展后的32位立即数作为输入,值为0表示将$Rt寄存器中的值作为输入;(7) ALU运算控制信号[5:0] ALUFunc,作为ALU的输入选择不同的运算操作;(8) 有无符号数指示信号Sign,值为1表示有符号数,值为0表示无符号数;(9) 写存储器使能信号MemWr,值为1表示允许对存储器进行写操作;(10) 读存储器使能信号MemRd,值为1表示允许对存储器进行读操作;(11) 写寄存器值的选择信号[1:0] MemToReg,选择ALU结果,存储器读取结果和PC+4其中之一作为写入目的寄存器的值;(12) 符号位扩展指示信号EXTOp,值为1表示对16位立即数进行符号位扩展,值为0表示0扩展;(13) 立即数高位取指令指示信号LUOp,值为1表示当前指令为lui指令,选择将立即数载入高16位低位填0的32位立即数作为ALU输入,值为0表示将正常扩展后的32位立即数作为ALU输入;控制信号的具体产生过程此处略去,在控制信号说明文件中进行详述。

精品单周期CPU设计.docx

■=・NINGBO UNIVERSITY短学期综合实验报告实验名称:单周期CPU设计院系:信息科学与工程学院专业:计算机科学与技术组员: XXXXXXXXXXXXXXXXXXXXXX指导老师:XXXXXXX _____________二o—一年七月八日摘要中央处理器(CPU)是计算机取指令和执行指令的部件,它是由算术逻辑单元(ALU)、寄存器和控制器组成,简称处理器(或CPU), CPU 是计算机系统的核心部件,在各类信息终端中得到了广泛的应用。

处理器的设计及制造技术也是计算机技术的核心之一。

CPU设计的第一步应当根据指令系统来建立数据路径,再定义各个部件的控制信号,确定时钟周期,完成控制器的设计。

然后建立数据路径,进而可以进行数字设计、电路设计,最后完成物理实现。

而在本次试验中,我们研究的重点是数据路径的建立和控制器的实现。

一个机器的性能由三个关键因素决定:指令数、时钟周期,以及执行每条指令所需的时钟周期数(CPI)。

然而不论是时钟周期,还是每条指令所需的时钟周期数目,都是由处理器的实现情况决定的。

在本次试验中,我们构造了单周期的数据路径和组合逻辑实现的控制器。

本次试验屮,我们运用Quartus II 8.0软件设计出了一个拥有6 条指令的单周期CPU,并对它进行了简单的测试,最终完成了一个正确的单周期CPU的设计。

关键词:数据路径,控制器,控制信号,单周期AbstractCentral processing unit (CPU) is a computer instraction fetch and execution ofcomponents, it is an arithmetic logic unit (ALU), registers and a controller, referred to as the processor (or CPU), CPU is the core component of computer systems in all type information terminal has been widely used・Processor design and manufacturing technology is one of the core computer technology.The first step should be based on CPU design instraction to create a data path, and then define the various components of the control signals to determine the clock cycle, the controller design. Then set up a data path, and then can be digital design, circuit design, physical implementation finalized. In this experiment, the focus of our research is to establish the data path and controller implementation.The performance of a machine consists of three key factors: the number of instructions, clock cycles to execute each instruction as well as the required number of clock cycles (CPI). Whether it be a clock cycle, each instruction or the number of clock cycles required are determined by the achievement of the processor. In this study, we constructed single-cycle data path and the combinational logic to achieve the controller.This experiment, we use Quartiis II 8.0 software to design a single-cycle instruction with 6 CPU, and it conducted a simple test, thefinal completion of a proper single-cycle CPU design.Keywords:Data path, Controller, Control Signal,Single-cycle实验内容:1、通过实验的学习,基本熟悉quarters II软件的使用,并能熟练运用试验所需元件。

MIPS单周期CPU实验报告

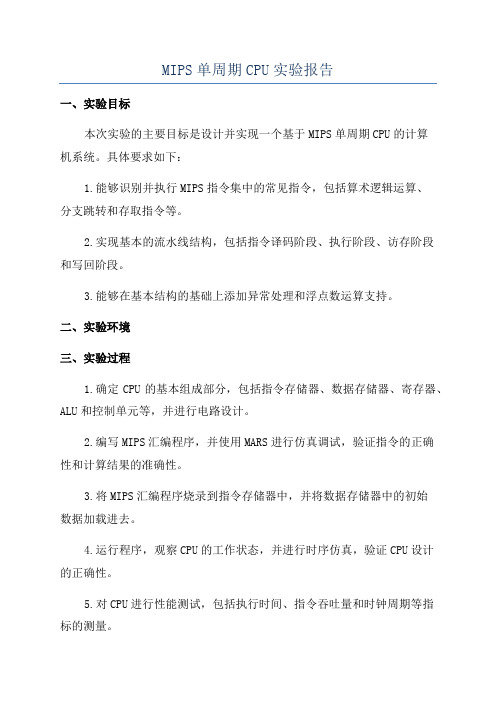

MIPS单周期CPU实验报告一、实验目标本次实验的主要目标是设计并实现一个基于MIPS单周期CPU的计算机系统。

具体要求如下:1.能够识别并执行MIPS指令集中的常见指令,包括算术逻辑运算、分支跳转和存取指令等。

2.实现基本的流水线结构,包括指令译码阶段、执行阶段、访存阶段和写回阶段。

3.能够在基本结构的基础上添加异常处理和浮点数运算支持。

二、实验环境三、实验过程1.确定CPU的基本组成部分,包括指令存储器、数据存储器、寄存器、ALU和控制单元等,并进行电路设计。

2.编写MIPS汇编程序,并使用MARS进行仿真调试,验证指令的正确性和计算结果的准确性。

3.将MIPS汇编程序烧录到指令存储器中,并将数据存储器中的初始数据加载进去。

4.运行程序,观察CPU的工作状态,并进行时序仿真,验证CPU设计的正确性。

5.对CPU进行性能测试,包括执行时间、指令吞吐量和时钟周期等指标的测量。

四、实验结果经过实验和测试,我们成功地设计并实现了一个基于MIPS单周期CPU的计算机系统。

该系统能够正确执行MIPS指令集中的常见指令,并支持流水线结构、异常处理和浮点数运算。

1.指令执行的正确性:通过在MARS中进行调试和仿真,我们发现CPU能够正确地执行各种指令,包括算术逻辑运算、分支跳转和存取指令等。

并且,在时序仿真中,CPU的各个组件的信号波形也符合预期。

2.流水线结构的实现:我们根据MIPS指令的特点和处理流程,设计了基本的流水线结构,并在MARS中进行了时序仿真。

仿真结果表明,各个流水线级的操作都能够正确无误地进行,并且能够顺利地在一个时钟周期内完成。

3.异常处理和浮点数运算的支持:通过在MIPS汇编程序中加入异常处理和浮点数运算的指令,我们验证了CPU对这些功能的支持。

在异常处理时,CPU能够正确地转入异常处理程序,并根据异常类型进行相应的处理。

在浮点数运算时,CPU能够正确地进行浮点数的加减乘除等运算,并将结果正确地写回寄存器。

单周期MIPS CPU实验(8条指令)

单周期M I P S C P U设计实验目的⏹掌握硬布线控制器设计的基本原理⏹能利用相关原理在Logisim平台中设计实现MIPS单周期CPU⏹主要任务☐绘制MIPS CPU数据通路☐实现单周期硬布线控制器☐测试联调核心指令集(可实现内存区域冒泡排序)#MIPS指令RTL功能描述1add$rd,$rs,$rt R[$rd]←R[$rs]+R[$rt]溢出时产生异常,且不修改R[$rd] 2slt$rd,$rs,$rt R[$rd]←R[$rs]<R[$rt]小于置1,有符号比较3addi$rt,$rs,imm R[$rt]←R[$rs]+SignExt(imm)溢出产生异常16b4lw$rt,imm($rs)R[$rt]←Mem4B(R[$rs]+SignExt16b(imm))5sw$rt,imm($rs)Mem4B(R[$rs]+SignExt16b(imm))←R[$rt]6beq$rs,$rt,imm if(R[$rs]=R[$rt])PC←PC+SignExt18b({imm,00})7bne$rs,$rt,imm if(R[$rs]!=R[$rt])PC←PC+SignExt18b({imm,00})8syscall系统调用,这里用于停机单周期MIPS 参考数据通路MemtoReg MemWrite Branch AluOP ALUSrc RegDstRegWritePCSrcCLKPCRDA指令存储器指令字4PC+45:020:1625:2115:1115:0Sign ExtendSignImmR1#R2#W#WDWE 寄存器堆R1R2101011<<2+PCBranchSrcB SrcA EqualA L UALUResult WriteDataWERD A 数据存储器WD ReadData WriteBackData++BranchAddress31:26CLK CLKPC+4控制器FuncOp rsrtrd步骤1:构建MIPS主机通路⏹在MIPS单周期CPU子电路中,利用如下组件构建MIPS 单周期CPU数据通路☐PC、IMEM、RegFile、ALU、DMEM、Controller步骤2:设计单周期MIPS控制器⏹输入信号⏹指令字Opcode,Func字段(12位)⏹输出信号⏹多路选择器选择信号⏹内存访问控制信号⏹寄存器写使能信号⏹运算器控制信号、指令译码信号⏹纯组合逻辑电路、无时序逻辑控制信号功能说明(8条核心指令集)#控制信号信号说明产生条件1MemToReg写入寄存器的数据来自存储器lw指令2MemWrite写内存控制信号sw指令未单独设置MemRead信号3Beq Beq指令译码信号Beq指令4Bne Bne指令译码信号Bne指令5AluOP运算器操作控制符加法,比较两种运算6AluSrcB运算器第二输入选择Lw指令,sw指令,addi7RegWrite寄存器写使能控制信号寄存器写回信号8RegDst写入寄存器选择控制信号R型指令9Halt停机信号,取反后控制PC使能端syscall指令完善硬布线控制器内部逻辑⏹打开CPU.circ打开单周期硬布线控制器电路⏹实现指令译码、ALU控制逻辑完善控制信号逻辑⏹增加简单的组合逻辑⏹根据给出的指令译码信号,实现所有控制信号逻辑步骤3:CPU测试⏹在指令存储器中载入排序程序sort.hex⏹时钟自动仿真,Windows:Ctrl+k Mac: command+k运行程序⏹程序停机后,查看数据存储器中排序情况,有符号降序排列下节课再见…。

中山大学计算机组成原理实验单周期CPU设计

中⼭⼤学计算机组成原理实验单周期CPU设计《计算机组成原理实验》实验报告(实验三)学院名称:数据科学与计算机学院专业(班级):学⽣姓名:学号:时间:2019 年11 ⽉8 ⽇成绩:实验三:单周期CPU设计与实现⼀.实验⽬的(1) 掌握单周期CPU数据通路图的构成、原理及其设计⽅法;(2) 掌握单周期CPU的实现⽅法,代码实现⽅法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的⽅法。

⼆.实验内容设计⼀个单周期CPU,该CPU⾄少能实现以下指令功能操作。

指令与格式如下:==> 算术运算指令加“加”运算。

加“加”运算。

==> 逻辑运算指令加“与”运算。

功能:GPR[rt] ←GPR[rs] or zero_extend(immediate)。

==>移位指令==>⽐较指令==> 存储器读/写指令==> 分⽀指令else pc ←pc + 4特别说明:offset是从PC+4地址开始和转移到的指令之间指令条数。

offset符号扩展之后左移2位再相加。

为什么要左移2位?由于跳转到的指令地址肯定是4的倍数(每条指令占4个字节),最低两位是“00”,因此将offset放进指令码中的时候,是右移了2位的,也就是以上说的“指令之间指令条数”。

else pc ←pc + 4(16)bltz rs, offsetelse pc ←pc + 4。

==>跳转指令(17)j addr说明:由于MIPS32的指令代码长度占4个字节,所以指令地址⼆进制数最低2位均为0,将指令地址放进指令代码中时,可省掉!这样,除了最⾼6位操作码外,还有26位可⽤于存放地址,事实上,可存放28位地址,剩下最⾼4位由pc+4最⾼4位拼接上。

==> 停机指令功能:停机;不改变PC的值,PC保持不变。

三.实验原理单周期CPU指的是⼀条指令的执⾏在⼀个时钟周期内完成,然后开始下⼀条指令的执⾏,即⼀条指令⽤⼀个时钟周期完成。

MIPS指令单周期CPU设计

rd rs rt imm

sw rt rs imm Addr = R[rs] + SignExt(imm) MEM[Addr] = R[rt]

PC

Register File

ALU

+4

Data memory

4. MIPS指令——BEQ

比较指令BEQ

– beq rs rt imm

Phase 5: Register Write (WB for “write back”)

– Write the instruction result back into the Register File – Those that don’t (e.g. sw, j, beq) remain idle or skip this phase

– if R[rs] = R[rt] – then PC (PC +4)+ SignExt(imm) – Else PC PC+4

instruction memory rd rs rt imm MUX

PC

Register File

ALU

+4

Data memory

5. MIPS指令——Jump

Data memory

rd rs rt

Register File

PC

单周期CPU设计思路

指令的行

– 显然要设计一个时序逻辑电路 – 一条指令用一个CPU周期完成

执行步骤的实现

– 取指:从指令存储器中读指令(地址:PC)

– 读出一或两个源寄存器的值(寄存器组)

– 进行指令规定的运算(ALU) – 读/写数据存储器

– Zero extend imm16? – Pass imm16 to input of ALU? – Write result to rt?

MIPS单周期CPU实验报告

《计算机组成原理实验》实验报告(实验二)学院名称:专业(班级):学生姓名:学号:时间:2017 年11 月25 日成绩: 实验二:单周期CPU设计与实现一.实验目的(1) 掌握单周期CPU数据通路图的构成、原理及其设计方法;(2) 掌握单周期CPU的实现方法,代码实现方法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的方法;(5) 掌握单周期CPU的实现方法。

二.实验内容设计一个单周期的MIPSCPU,使其能实现下列指令:==> 算术运算指令==> 逻辑运算指令功能:rd←rs | rt;逻辑或运算。

==>移位指令==>比较指令==> 存储器读/写指令将rt寄存器的内容保存到rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中。

即读取rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中的数,然后保存到rt寄存器中。

==> 分支指令功能:if(rs=rt) pc←pc + 4 + (sign-extend)immediate <<2 else pc ←pc + 4特别说明:immediate是从PC+4地址开始和转移到的指令之间指令条数。

immediate 符号扩展之后左移2位再相加。

为什么要左移2位?由于跳转到的指令地址肯定是4的倍数(每条指令占4个字节),最低两位是“00”,因此将immediate放进指令码中的时候,是右移了2位的,也就是以上说的“指令之间指令条数”。

12特别说明:与beq不同点是,不等时转移,相等时顺序执行。

功能:if(rs>0) pc←pc + 4 + (sign-extend)immediate <<2 else pc ←pc + 4==>跳转指令==> 停机指令三.实验原理1.时间周期:单周期CPU指的是一条指令的执行在一个时钟周期内完成,然后开始下一条指令的执行,即一条指令用一个时钟周期完成。

单周期cpu设计代码解读

单周期cpu设计代码解读⽬录写在前⾯欢迎转载,转载请说明出处。

单周期cpu设计代码讲解概念回顾⼀、电⼦计算机的部件分为:中央处理器(cpu)、内部存储器(Memory)、输⼊/输出(I/O)设备,以及连接它们的总线(Bus)。

下图为图⽰,注意⾊块的区分。

⼆、cpu⼜包括控制器(Controller)和数据通路(Data Path)。

下图为图⽰,注意⾊块区分。

三、控制器分为主控(Main Control)和局控(Local Control或ALU Control)。

将⼆进制指令输⼊控制器,⽣成控制信号,该过程称为译码。

控制信号控制数据通路⼯作。

且不同的指定对应不同的控制信号。

下图为在控制器中译码的逻辑⽰意图:下图为在控制器中译码的物理⽰意图:讲解⼀下从逻辑图到物理图的转换:1. ⾸先由主控解析op指令,如果发现该指令为“000000”则表⽰该指令是R指令,输出中间信号R-Type为1,否则为0;如果发现该指令是其他值,则按照逻辑图,为RegDst等信号赋相应的值;2. 中间信号R-Type起到⼆路选择的作⽤,如图。

3. 中间信号ALUop,在R-Type为0(选择0路)时,直接通过局控,输出成为ALUctr信号,对应上⾯逻辑图的最后⼀⾏后5列;在R-Type为1时,局控起作⽤。

4. 局控解析R指令的func部分,输出对应指令的ALUctr信号。

四、数据通路:是包括运算器、寄存器组、存储器(⾼速缓存)、多路选择器等等在内的元件的有结构的组合。

如下图所⽰:【数据通路各部分的讲解将结合代码完成】Verilog代码讲解在代码讲解之前有必要放⼏张图:shift.v/*移位*//*输⼊⼀个数,返回移位之后的结果*//*输⼊d(待移的数)、sa(移动的位数)、right(移动⽅向)、arith(空位补全⽅式)*//*输出sh(移位后的结果)*/module shift (d,sa,right,arith,sh);input [31:0] d;input [4:0] sa;input right,arith;output [31:0] sh;reg [31:0] sh;// 组合逻辑always @* beginif (!right) begin // right为逻辑0时,左移sh = d << sa;end else if (!arith) begin // right为逻辑1,且arith为逻辑0时,右移、0补空sh = d >> sa;end else begin // 右移、1补空sh = $signed(d) >>> sa;endendendmodulescinstmem.v/*从ROM(只读存储器)读数据*//*输⼊⽬标数据在ROM中的地址a*//*输出地址对应的数据inst*/module scinstmem (a,inst);input [31:0] a;output [31:0] inst;wire [31:0] rom [0:31]; // 定义32个32位的存储器ROM// 想ROM中写⼊⼀组指令,指令对应的汇编含义见⾏注释assign rom[5'h00] = 32'h3c010000; // (00) main: lui r1,0assign rom[5'h01] = 32'h34240050; // (04) ori r4,r1,80assign rom[5'h02] = 32'h20050004; // (08) addi r5,r0, 4assign rom[5'h03] = 32'h0c000018; // (0c)call: jal sumassign rom[5'h04] = 32'hac820000; // (10) sw r2,0(r4)assign rom[5'h05] = 32'h8c890000; // (14) lw r9, 0(r4)assign rom[5'h06] = 32'h01244022; // (18) sub r8, r9. r4assign rom[5'h07] = 32'h20050003; // (lc) addi r5, r0. 3assign rom[5'h08] = 32'h20a5ffff; // (20) loop2: addi r5, r5, -1assign rom[5'h09] = 32'h34a8ffff; // (24) ori r8, r5, 0xffffassign rom[5'h0A] = 32'h39085555; // (28) xori r8. r8, 0x5555assign rom[5'h0B] = 32'h2009ffff; // (2c) addi r9, rO, -1assign rom[5'h0C] = 32'h312affff; // (30) andi rlO, r9, 0xffffassign rom[5'h0D] = 32'h01493025; // (34) or r6. rlO, r9assign rom[5'h0E] = 32'h01494026; // (38) xor r8, rlO, r9assign rom[5'h0F] = 32'h01463824; // (3c) and r7, rlO, r6assign rom[5'h10] = 32'h10a00001; // (40) beq r5, r0, shiftassign rom[5'h11] = 32'h08000008; // (44) j loop2assign rom[5'h12] = 32'h2005ffff; // (48) shift: addi r5. r0, -1assign rom[5'h13] = 32'h000543c0; // (4c) sll r8. r5. 15assign rom[5'h14] = 32'h00084400; // (50) sll r8, r8, 16assign rom[5'h15] = 32'h00084403; // (54) sra r8, r8, 16assign rom[5'h16] = 32'h000843c2; // (58) srl r8. r8. 15assign rom[5'h17] = 32'h08000017; // (5c) finish: j finishassign rom[5'h18] = 32'h00004020; // (60) sum: add r8, r0, r0assign rom[5'h19] = 32'h8c890000; // (64) loop: lw r9, (r4)assign rom[5'h1A] = 32'h20840004; // (68) addi r4, r4, 4assign rom[5'h1B] = 32'h01094020; // (6c) add r8, r8, r9assign rom[5'h1C] = 32'h20a5ffff; // (70) addi r5, r5, -1assign rom[5'h1D] = 32'h14a0fffb; // (74) bne rS, r0, loopassign rom[5'h1E] = 32'h00081000; // (78) sll r2f r8f 0assign rom[5'h1F] = 32'h03e00008; // (7c) jr r31// 将地址对应的数据放⼊instassign inst = rom[a[6:2]];endmodulescdatamem.v/*将数据写⼊RAM中(随机存取存储器)的指定位置*//*输⼊待写数据datain、⽬标地址addr;写使能信号we;时钟信号clk、inclk、outclk*//*输出将被覆盖的数据dataout*/module scdatamem (clk,dataout,datain,addr,we,inclk,outclk);input [31:0] datain;input [31:0] addr ;input clk, we, inclk, outclk;output [31:0] dataout;reg [31:0] ram [0:31]; // 定义32个32位RAM// 把将被覆盖的数据放⼊dataoutassign dataout =ram[addr[6:2]];// 时序逻辑,clk的上升沿触发always @ (posedge clk) beginif (we) ram[addr[6:2]] = datain; // 如果写使能信号we为1,将数据写⼊⽬标地址end// 为RAM赋值,这⼀步不是必要的,只是欲运⾏的⾃定义程序的需要。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1)设计一个单周期CPU,能实现基本的指令功能,如ADD,SUB指令实现对操作数加减功能,LW,SW指令实现从存储器取数和存数,J指令实现指令间的跳转。

2)采用模块化设计CPU,通过模拟仿真保证各模块的正确性,以保证最终CPU功能的正确性,能正确地在FPGA板上完成指令设计的效果。

3)通过设计合理的16位指令,实现从存储器取初始数和存数,对初始数进行加减操作,通过修改存储器初始数据,实现FPGA上LED显示无限加n减m的效果。

3.1.5数据选择器

数据选择器主要是解决数据来源问题,通过控制信号使数据选择器选择的数据端口不同,此数据选择器可选用软件封装的2选1选择器。

3.1.6ALU单元

ALU单元主要用于将输入端的两个数做加减操作,通过控制信号01的变化产生运算,该ALU可以使用软件封装的加减ALU(LPM-ADD-SUB),当控制信号为1时作加法,为0时作减法。

图3器件模块设计方案图

从上图我们可以看出各单元之间的联系:初始数据从数据存储器RAM中取出,通过两种数据传入方式:一种是不经过数据选择器,另一种是经过数据选择器,数据传入到寄存器组中作为寄存器数据。而后当传入的是地址数据时,就从寄存器取出,经过ALU运算单元,将数据传入寄存器组中保存或传入数据存储器中保存。在整个过程中,PC计数器自动加1作为地址去指令存储器ROM中取指令作为此轮执行的指令数据,而控制器在整个过程中依据指令数据的指令码产生相应的控制信号(操作码)控制器件的运作,从而完成整个CPU的执行功能。下面我们将对主要的单元进行简要概述。

(1)取指令(IF):根据程序计数器PC中的指令地址,从指令存储器中取出一条指令,同时PC根据指令字长度自动递增产生下一条指令所需要的指令地址,但遇到“地址转移”指令时,则控制器把“转移地址”送入PC,当然得到的“地址”需要做些变换才送入PC。

(2)指令译码(ID):对取指令操作中得到的指令进行分析并译码,确定这条指令需要完成的操作,由指令的[15-12]位产生相应的操作控制信号,用于驱动执行状态中的各种操作。

二、课程设计器C微型计算机和FPGA板--Cyclone III系列,型号EP3C16U484C6实验开发板以及USB连接线。

2.2 软件平台

1)操作系统:Win7;

2)开发平台:Quartus II 9.0集成开发软件;

3)编程语言:VerilogHDL硬件描述语言。

3.1.3存储器

存储器分为两种类型:一种是数据存储器RAM,另一种是地址存储器ROM。考虑到设计的方便,否则使用寄存器设计存储器也是可行的。

3.1.3.1数据储存器

数据存储器为RAM型,表示可读可写,所以数据储存器有4个端口,当写信号有效时,应给出写的地址及数据,再加上时钟信号,这里的数据存储器采用软件封装好的RAM-1-PORT存储器。

rd(3位)

reserved

此ADD加法指令完成的功能是:将rs3位对应的寄存器的数和rt3位对应的寄存器的数相加,结果数据存放至rd3位对应的寄存器的位置,reserved作为保留位。

(2)SUB指令

0110(4位)

rs(3位)

rt(3位)

rd(3位)

reserved

此SUB减法指令完成的功能是:将rs3位对应的寄存器的数和rt3位对应的寄存器的数相减,结果数据存放至rd3位对应的寄存器的位置,reserved作为保留位。

图1CPU宏观设计方案

3.1指令模块

3.1.1指令格式简要设计

本CPU实验是针对16位指令数据设计的,所以应当合理划分指令数据区间段的指令相应的功能。从下图2可以看出,16位指令数据划分为5个区间段,指令的[15-12]位作为控制位传入控制器产生控制信号,指令[11-9]位作为地址1从寄存器取数输出数据到寄存器1号输出口,指令[8-6]位作为地址2从寄存器取数输出数据到寄存器2号输出口,指令[5-3]位与指令[8-6]位作为数据选择器选择地址输入寄存器写地址口,指令[5-0]位作为扩展单元输入,扩展数据成16位。另外指令[11-0]位作为扩展输入,扩展成16位数据作为PC计数器的选择器一端。

4.2.1寄存器组

由上面总体设计方案中指出,每个寄存器应该由16个D触发器构成,为了避免设计复杂,我们采用迭代的设计方法,即先由单个D触发器设计成包含2个D触发器模块,图6示出了由单个D触发器构成2个D触发器模块。为了避免篇幅颇多,这仅展示由8个D触发器构成最终16个D触发器的示意图,如图7,以及最终16位D触发器综合模块效果,如图8。

(3)指令执行(EXE):根据指令译码得到的操作控制信号,具体地执行指令动作,然后转移到结果写回状态。

(4)存储器访问(MEM):所有需要访问存储器的操作都将在这个步骤中执行,该步骤给出存储器的数据地址,把数据写入到存储器中数据地址所指定的存储单元或者从存储器中得到数据地址单元中的数据。

(5)结果写回(WB):指令执行的结果或者访问存储器中得到的数据写回相应的目的寄存器中。

图2指令格式简要设计图

3.2器件单元模块

此模块的设计是CPU设计的核心部分,它主要涉及到CPU中多个器件的设计。我们依然采用模块设计方案,把总体设计拆分成多个相互独立的器件,再对每部分器件单独设计。在此模块中包括:寄存器组、控制器、存储器、PC计数器、数据选择器、ALU单元这六大主要单元。如下图2所示,展示出六大单元的设计方案以及六大单元之间的联系。

1.1设计目的

1.2设计目标

二、课程设计器材

2.1硬件平台

2.2 软件平台

三、CPU逻辑设计总体方案

3.1 指令模块

3.2 部件模块

四、模块详细设计

4.1 指令设计模块

4.2 部件设计模块

五、实验数据

5.1 初始数据

5.2 指令数据

六、结论和体会

七、参考文献

摘 要

本CPU设计实验以QuartusII 9.0为软件设计平台,以Cyclone采III型号EP3C16F484C6为FPGA实测板。此CPU设计采用模块化设计方案,首先设计指令格式模块,此模块决定CPU各个部件的接口数据容量及数量,再对CPU各个部件独立设计实现,主要涉及的部件有:寄存器组、控制器、存储器、PC计数器、数据选择器、ALU单元以及扩展单元。分部件的设计通过软件平台模拟仿真各部件的功能,在确保各部件功能正确的情况下,将所有部件模块整合在一起实现16位指令的CPU功能。再按照指令格式设计的要求,设计出一套能完整运行的指令,加载到指令存储器中,最终通过在FPGA实测板上实现了加2减1的循环运算效果,若要实现其他效果,也可更改指令存储器或数据存储器的数据而不需要对内部部件进行更改元件。

3.1.3.2指令存储器

指令存储器为ROM型,表示只读,所以地址存储器有2个端口,应给出读的地址信号以及时钟信号这里的数据存储器采用软件封装好的ROM-1-PORT存储器。

3.1.4PC计数器

PC计数器主要作为执行一条指令后,地址自动加1到指令存储器中取16位指令作为此轮操作。故PC计数器应能等待一个时钟后将加1后的数据送至指令存取器中,所以它应包括ALU累加器(一端为1)和寄存器(当一个时钟信号到来,将数据输出),书中还包括一个数据选择器,用于设置PC的值,以至于不会无限增长,实现J指令。

关键词:CPU设计、16位指令格式、模块化设计、Quartus软件、CPU各部件

一、设计目的与目标

1.1设计目的

1)了解Quartus II软件的使用,学习软件环境下设计CPU的基本过程;

2)在Quartus II平台上完成各个单元的设计,加深对每个单元(控制器、寄存器、存储器等)工作原理的理解;

3)对各个单元组合而成的CPU进行指令测试,配合使用模拟仿真,了解指令和数据在各个单元中的传输过程及方向。

3.1.1寄存器组

寄存器组是作为保存数据的器件,故应使用时钟触发的D触发器(DFFE),等待一个时钟到来将数据传出去。本实验设计为16位CPU,故每个寄存器应为16位,即每个寄存器是由16个D触发器扩展而成。考虑到指令从寄存器取数位数为3位,所以可以设置8个寄存器用于保存数据,如果是写地址的3位指令通过74138(3-8译码器)译码作为寄存器的有效EN使能端输出数据;如果是读地址的3位指令数据通过8位扩展数据选择器(LPM-MUX)选择数据输出。

3.1.2控制器

控制器是作为CPU控制信号产生的器件,通过产生控制信号,使其他器件有效或无效,因此控制器的设计显得尤为重要。控制器的设计主要如下:先必须自己设计好各功能指令的4位01码(指令的[15-12]),然后针对某个控制信号,找出使其为1的功能指令,对每个功能指令的0位上取非,然后4位相与,之后将所有为1的功能指令相或,结果作为此控制信号。对每个控制信号执行重复操作,控制器也就是这些信号的组合。

三、CPU逻辑设计总体方案

单周期CPU设计方案从宏观上把握主要分为器件模块和指令/数据模块这两大模块,器件模块是指令模块的载体,指令数据在器件上流动,指令数据的格式是器件模块的主宰。所以当设计CPU时,我们采用模块化设计,单独对着两模块进行设计,考虑到指令数据模块的格式决定指令器件模块接口的数据容量大小,所以应先完成指令数据模块的格式设计。

(3)LW指令

1001(4位)

base(3位)

rt(3位)

offset(6位)

此LW指令完成的功能是:将base3位对应的寄存器的数和offset6位扩展成16位数据相加,结果作为数据存储器地址,取出地址对应的数据存放到rt3位对应的寄存器中。

(4)SW指令

0001(4位)

base(3位)

rt(3位)

图9寄存器组综合模块

下面我们来看寄存器组综合模块的详细设计,如图10所示。主要有3处值得注意:

因为我们设计的从寄存器取数的指令位数为3位,所以最多可寻8个寄存器,所以可看到图中示出了8个16位D触发器的综合模块。

图4单周期CPU指令处理过程