实验3 基于硬件描述语言的电路设计

EDA技术及其应用(3)

1.4 EDA的优势

手工设计方法

●复杂电路的设计、调试十分困 难;

●无法进行硬件系统仿真,若某 一过程存在错误,查找和修改十 分不便;

●设计过程中产生大量文档,不 易管理;

●对于IC设计而言,设计实现过 程与具体生产工艺直接相关,因 此可移植性差;

●只有在设计出样机或生产出芯 片后才能进行实测;

EDA技术

在设计时加入用于测试的部分逻辑,即进行可测性设计(DFT ,Design For Test),在设计完成后用来测试关键逻辑。

在ASIC设计中的扫描寄存器,是可测性设计的一种,原理是 把ASIC中关键逻辑部分的普通寄存器用测试扫描寄存器来代替, 在测试中可以动态地测试、分析设计其中寄存器所处的状态,甚至 对某个寄存器加以激励信号,改变该寄存器的状态。

1.6.3 GAL

GAL的OLMC单元设有多种组态,可配置成专用组合输出、专 用输入、组合输出双向口、寄存器输出、寄存器输出双向口等, 为逻辑电路设计提供了极大的灵活性。由于具有结构重构和输出 端的任何功能均可移到另一输出引脚上的功能,在一定程度上, 简化了电路板的布局布线,使系统的可靠性进一步地提高。GAL 的出现是复杂PLD的里程碑。

1.11 编程与配置

目前常见的大规模可编程逻辑器件的编程工艺有三种: 1.基于电可擦除存储单元的EEPROM或Flash技术。 2.基于SRAM查找表的编程单元。 3.基于反熔丝编程单元。

1.12 FPGA配置器件

主动配置方式

由FPGA器件引导配置操作过程,它控 制着外部存储器和初始化过程

被动配置方式

1.2 EDA技术应用对象

全定制或半定制ASIC

实现目标 ASIC的设计和实现

FPGA/CPLD(或称可编程ASIC)开发应用

VHDL硬件描述语言在数字电路设计中的应用

VD H L对数字 电路 的硬件描述能力强 ,在设计 上非常 有效 ,是 数字 电路 教学 中全新 的理 论联 系实际 的方 法和

培养学生实 际动手能力 的有效 工具 。 关键词 :V D ;数字 电路 ;电子技术 H L 中图分类号 :P 9 T 31 文献标识码 : A di1 .9 9 ji n 17 — 35 2 1 .50 0 o:0 3 6/.s . 62 4 0 .0 10 .3 s

i lcr u tc n tme tt e n e so e d gt l n e r t d cr u t I h sb e e eo i g t n o a - t i i a a c e e d ft i i t g ae i i t a e n a d v l p n r d t c h h a i c . e c mp ih t e d s n o a d r i u tb o l h e i fh r wa e cr i y VHDL s g c .A r f n r d c in o e b s t c u e e t r s b i to u t ft a i sr t r ,f au e e i o h c u a d t e d sg r c s fVHDL i gv n n h e i n p o e so s i e .T ef l a d ri u e sa x mp e t l mi ae t ed sg h l d e s s d a n e a l o i u n t e i— u l h

随 着数 字 电子 技术 的发 展 , 字 电路 已 由早 期 数 的分 立元 件逐 渐 发 展成 集 成 电路 , 以及 具 有 特 定 功

vhdl设计实验报告

vhdl设计实验报告VHDL设计实验报告引言VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和验证。

本实验旨在通过设计一个简单的电路来熟悉VHDL语言的基本语法和设计流程。

一、实验背景数字电路是现代电子系统的基础,而VHDL则是描述和设计数字电路的重要工具。

VHDL可以帮助工程师们以一种形式化的语言来描述电路的功能和结构,从而实现电路的模拟和验证。

二、实验目的本实验的目的是通过使用VHDL语言设计一个简单的电路,加深对VHDL语言的理解,并掌握基本的电路设计流程。

三、实验步骤1. 确定电路功能在设计电路之前,首先需要明确电路的功能。

本实验中,我们选择设计一个4位加法器电路。

2. 设计电路结构根据电路功能的要求,设计电路的结构。

在本实验中,我们需要设计一个4位加法器,因此需要使用4个输入端口和一个输出端口。

3. 编写VHDL代码使用VHDL语言编写电路的描述代码。

在代码中,需要定义输入和输出端口的类型和位宽,并实现电路的功能。

4. 进行仿真使用仿真工具对设计的电路进行仿真,以验证电路的功能是否符合预期。

通过输入不同的测试数据,观察输出是否正确。

5. 下载到FPGA开发板将设计好的电路代码下载到FPGA开发板上进行验证。

通过连接输入信号和观察输出信号,验证电路在实际硬件上的运行情况。

四、实验结果与分析经过仿真和实际验证,我们设计的4位加法器电路在功能上符合预期。

输入不同的数据进行加法运算时,输出结果都正确。

五、实验总结通过本次实验,我们深入了解了VHDL语言的基本语法和设计流程。

通过设计一个简单的电路,我们掌握了VHDL的应用方法,并通过仿真和实际验证,加深了对电路设计的理解。

六、实验心得本实验让我对VHDL语言有了更深入的认识。

通过实际操作,我更加熟悉了VHDL的编写和仿真流程。

基于硬件描述语言VHDL的电路系统设计研究

4 传统设计和V D 的比较 H L 儿 乎在 集 成 电路 的每 个 没计 环节 和整 个 没 汁过程 都 普遍 使 用 E A( D 电子没计自动化 ) 技术 传统的 没汁方法是基于中小规 模集成

真 、 合的硬件描述 浯言 , 使用 中较 易发现错 洪,进 行修改 , 语 综 在 该 言提 供了很 强的类型 校验功能 ,它的 没计描述可 以被不 I的E A 司 D 工具 所 支持 ,即有很强的可移植性 V D E言描 述怏捷 ,节省人 力,易 、 H L.  ̄ 于 保密 ,是 目前国内外数字系统的主流没 汁语言 ,

5 VH 的新 发展 DL

任何复 杂的数字系统 都可以最终分解 成基本 ¨和存储器元件 ,这

种分解最 好由汁算机 自 动进行 传统的数字 系统 都是山一些固定功能 的器件 加上一定的外 电路构成模块 ,再 山这些模块进 一步组成各种 功能 的电路 . 在’ 汁时,儿乎没有灵活性可 言,且 没汁系统所需的芯 、 殳 片种类多、数 目 大 复杂数字 系统 的没汁 , 了’ 爿 除 殳汁J期长外 ,设汁 人 员的缺乏也是一个关键f 题 、 u J

的各项性能 ,还 直接 影响到 芯片 的集成度 以及生 产线上 的成本 . 能大

V D I 差 一些 ,而在 f级开 关电路描述方 面 ̄ V D 强一些 其 共 H Lr  ̄ j EH L 同的特 点在于 :能形式化地 抽象表示电路的行为和结构 高级语言的精巧结 构来简化电路 行为 {

( )汁算机辅助 的方 法 这是最早 的一种方法 , 目前已经发腱 1 得较为成熟 ,就是通常所 ’的C D 兑 A 技术 ( u编 程的方法 就 是利片 编 译的方法来进行数 字系统的 没 2) J ‘ j

汁.

对于数字系统的A I ,V D 作为一种硬件 电路描述 语言所 具备 SC H L 的行为级的描 述能 力为其仿真模型的建立提 供了一条途 径 但是 由于 缺 乏 高 效 可 靠 的 崩 V D 彳 述 的 A I 库 ,在 一 定 程 度 上 影 响 了 H L菡 SC V D 的应用 ,i HL 酊建立A I库的最 大困难在于V D 没有统一 、有效 SC HL

VHDL语言实现数字电路设计

VHDL语言实现数字电路设计数字电路是由逻辑门、寄存器以及其他数字组件组成的电子系统,用于处理和传输数字信号。

VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统。

通过使用VHDL语言,我们可以实现数字电路的设计,从而满足各种需求。

VHDL语言提供了一种结构化的设计方法,允许设计者描述硬件电路的结构、功能以及时序行为。

以下是一些常见的数字电路设计任务,以及如何使用VHDL语言来实现它们。

1. 门电路设计门电路是最简单的数字电路之一,由逻辑门组成。

使用VHDL语言,我们可以通过描述逻辑门的输入和输出来实现门电路的设计。

例如,我们可以使用VHDL语言描述一个与门:```vhdlentity AND_gate isport (A, B : in bit;Y : out bit);end entity AND_gate;architecture dataflow of AND_gate isbeginY <= A and B;end architecture dataflow;```在这个例子中,我们定义了一个输入端口A和B,以及一个输出端口Y。

在architecture部分,我们使用VHDL语言描述了Y的逻辑值为A和B的逻辑与。

2. 时序逻辑电路设计时序逻辑电路是根据时钟信号进行操作和状态转换的电路。

使用VHDL语言,我们可以描述时序逻辑电路的行为和状态变化。

例如,我们可以使用VHDL语言描述一个触发器:```vhdlentity D_flip_flop isport (D, CLK : in bit;Q : out bit);end entity D_flip_flop;architecture behavior of D_flip_flop issignal Q_temp : bit;beginprocess(CLK)beginif CLK'event and CLK = '1' thenQ_temp <= D;end if;end process;Q <= Q_temp;end architecture behavior;```在这个例子中,我们定义了一个输入端口D和CLK,以及一个输出端口Q。

现代电子电路与系统的分析设计与实现方法

现代电子电路与系统的分析设计与实现方法现代电子电路与系统的分析、设计与实现方法是指在设计电子电路和系统时,采用的一系列技术和工具,以确保电路和系统能够达到设计要求,并满足性能、可靠性和经济性等各方面的需求。

在现代电子技术的快速发展下,电子电路和系统设计面临着越来越多的挑战,因此分析、设计和实现方法变得越来越重要。

下面是一些常用的现代电子电路与系统的分析设计与实现方法:1. 基于硬件描述语言的设计:硬件描述语言(HDL)是一种用来描述电子系统硬件行为的语言。

通过使用HDL,设计人员可以对电路进行更高层次的抽象描述,从而更容易进行电路的分析和验证。

常用的HDL包括VHDL和Verilog。

2.元件级设计:元件级设计是指在电路设计中将电路拆分为可独立分析和设计的基本元件。

通过对各个元件的分析和设计,可以实现对整个电路的分析和设计。

3.数字信号处理(DSP)技术:数字信号处理技术在现代电子电路和系统中应用广泛。

通过使用DSP技术,可以对电路中的信号进行精确和高效的处理,以满足各种应用需求。

4.模拟电路分析与设计:模拟电路的分析与设计主要涉及电路的建模、分析和优化。

通过对电路元器件的特性进行数学建模,可以对电路的行为进行准确的分析,并通过各种优化方法来改进电路的性能。

5.电磁兼容性(EMC)设计:在现代电子电路和系统设计中,电磁兼容性是一个重要的考虑因素。

通过采用适当的布线和屏蔽技术,可以有效地减少电磁干扰和抗干扰能力,提高整个电路系统的EMC性能。

6.集成电路设计:集成电路设计是指将多个电路和系统集成到同一芯片上的设计方法。

通过采用现代的集成电路设计流程和工具,可以实现高度集成、低功耗和高性能的电子系统设计。

7.系统级设计和建模:系统级设计是指对整个电子系统进行高层次的建模和设计。

通过对系统功能、性能和约束进行详细分析和建模,可以优化整个电子系统的设计过程。

8.可靠性设计与分析:在现代电子电路和系统设计中,可靠性是一个重要的考虑因素。

mips控制器设计实验原理

mips控制器设计实验原理MIPS(Microprocessor without Interlocked Pipelined Stages)是一种32位的RISC (Reduced Instruction Set Computing)处理器架构,旨在提高处理器效率和性能。

MIPS 架构的处理器被广泛应用于各种领域,包括计算机、嵌入式系统、网络设备、数字信号处理等需要高性能的应用中。

在本实验中,我们将学习如何设计一个基于MIPS控制器的处理器。

控制器是一个能够控制处理器各个子系统如存储器、算术逻辑单元(ALU)、输入/输出设备等的模块。

MIPS控制器的设计是关键,因为它可以决定处理器的运行效率和性能。

MIPS控制器的设计需要考虑以下几个方面:1. 指令解码MIPS指令集包含了大量的指令,但是由于指令采用RISC架构,指令集中的每一个指令都很简单,只有少量的寄存器、立即数和内存操作。

控制器需要能够识别每一个指令,并正确地解码指令中的操作数。

为了实现这个目标,控制器需要包含适当的译码电路和其他必要的逻辑门电路。

2. 流水线控制流水线是一种增加处理器效率和性能的技术,通过将指令的执行拆分为多个阶段,多个指令可以在同一时刻被处理。

MIPS架构使用了5级流水线结构,即取指令、指令译码、执行、访问存储器和写回结果。

控制器需要能够控制流水线的各个阶段,确保它们按照正确的顺序执行。

3. 异常处理处理器在执行指令时可能会出现各种错误,如未定义的指令、内存访问冲突、算术溢出等。

这些错误称作异常。

处理器需要能够捕获异常并采取适当的措施,如停止当前指令的执行、中断指令流并处理异常。

控制器需要包含适当的硬件和逻辑电路来处理异常。

4. 输入/输出一个处理器需要有输入/输出接口来连接外部设备,如键盘、鼠标、显示器、网络等。

这些设备通过输入输出端口(I/O端口)与处理器相连。

控制器需要能够控制I/O端口的数据传输,并确保数据在正确的时刻被传输。

你的Basys 3第一个入门实验官方指导手册

位于母公司美国国家仪器NI中国总部大楼内电话:+86-21-58893151邮箱:china.sales@“你的Basys 3第一个入门实验”官方指导手册目录1.Basys3硬件电路………………………………………………………………………...P31.1 电源电路…………………………………………………………………..……......P51.2 LED灯电路…………………………………………………………………..……..P61.3 拨码开关电路………………………………………………………………..……...P71.4 按键电路…………………………………………………………………..……......P81.5 数码管电路…………………………………………………………………..……...P81.6 VGA电路…………………………………………………………………..…….....P91.7 I/O扩展电路…………………………………………………………………..….P101.8 FPGA调试及配置电路…………………………………………………………..P102.Basys3电路实验–七段数码管显示实验………………………………………..…P12第一章Basys3 硬件电路Basys3是围绕着一个Xilinx Artix®-7 FPGA芯片XC7A35T-1CPG236C搭建的,它提供了完整、随时可以使用的硬件平台,并且它适合于从基本逻辑器件到复杂控制器件的各种主机电路。

Basys3板上集成了大量的I/O设备和FPGA所需的支持电路,让您能够构建无数的设计而不需要其他器件。

主要规格/特殊功能产品规格:Basys3为想要学习FPGA和数字电路设计的用户提供一个理想的电路设计平台。

Basys3板提供完整的硬件存取电路,可以完成从基本逻辑到复杂控制器的设计。

四个标准扩展连接器配合用户设计的电路板,或Pmods(Digilent设计的A / D和D / A转换,电机驱动器,传感器输入等)其他功能。

基于Verilog的数字电路设计与模拟

基于Verilog的数字电路设计与模拟数字电路设计是现代电子领域中至关重要的一部分,它涉及到数字系统中各种逻辑门、寄存器、计数器等元件的设计和实现。

而Verilog作为一种硬件描述语言,被广泛应用于数字电路设计中,能够帮助工程师们更高效地进行数字电路的建模、仿真和验证。

本文将介绍基于Verilog的数字电路设计与模拟的相关内容,包括Verilog语言基础、数字电路设计流程、常用的数字电路元件设计以及Verilog仿真工具的使用等方面。

Verilog语言基础Verilog是一种硬件描述语言(HDL),它可以描述数字系统中的行为和结构,是数字电路设计中常用的编程语言之一。

Verilog包括结构化Verilog和行为Verilog两种描述方式,结构化Verilog主要用于描述数字系统的结构,而行为Verilog则用于描述数字系统的行为。

在Verilog中,最基本的单元是模块(module),一个模块可以包含输入端口、输出端口以及内部逻辑。

示例代码star:编程语言:verilogmodule and_gate(input a, input b, output y);assign y = a & b;endmodule示例代码end上面是一个简单的AND门模块的Verilog描述,其中input表示输入端口,output表示输出端口,assign用于赋值操作。

通过这样的描述,我们可以实现各种逻辑门、寄存器、计数器等数字电路元件。

数字电路设计流程在进行数字电路设计时,通常需要遵循一定的设计流程,以确保设计的正确性和可靠性。

典型的数字电路设计流程包括需求分析、概念设计、详细设计、验证和实现等阶段。

在Verilog中,我们可以通过编写相应的代码来完成这些阶段的工作。

需求分析:明确设计的功能需求和性能指标。

概念设计:根据需求设计数字系统的整体结构和功能模块。

详细设计:对各个功能模块进行详细设计,包括内部逻辑和接口定义。

实验三VHDL

4、模7计数器

硬件描述语言1

端口说明: PORT( clk : IN STD_LOGIC; q : OUT INTEGER RANGE 0 TO 6);

功能描述:

VARIABLE cnt : INTEGER RANGE 0 TO 6; BEGIN IF (clk'EVENT AND clk = '1') THEN IF cnt < 6 THEN cnt := cnt + 1; ELSE cnt :=0; END IF; END IF; q <= cnt;

ARCHITECTURE arc_shiftreg OF shiftreg IS SIGNAL q_temp : STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN PROCESS(cr,clk) BEGIN …… …… --见下页 END PROCESS; q<=q_temp; END arc_shiftreg;

假设数据已经被时钟的上升沿打入D触发器,那么数据 到达第一个触发器的Q端需要Tco,再经过组合逻辑的 延时Tdelay到达的第二个触发器的D端,要想时钟能在 第二个触发器再次被稳定的锁入触发器,则时钟的延 迟不能晚于Tco+Tdelay+Tsetup,(回顾建立和保持时 间的概念,就可以理解Tdelay) 由以上分析可知:最 小时钟周期:T=Tco+Tdelay+Tsetup 最快时钟频率 F= 1/T PLD开发软件也正是通过这个公式来计算系统运行 速度Fmax

硬件描述语言2: 功能描述:

IF (clk'EVENT AND clk='1') THEN CASE cnt IS WHEN "000"=>cnt<="001"; WHEN "001"=>cnt<="010"; WHEN "010"=>cnt<="011"; WHEN "011"=>cnt<="100"; WHEN "100"=>cnt<="101"; WHEN "101"=>cnt<="000"; WHEN others=>NULL; END CASE; END IF; q <= cnt;

基于VerilogHDL智能评测平台的“计算机组成原理”课程贯通式实验模式

I S S N1002-4956 C N11-2034/T实验技术与管理Experimental Technology and M a n a g e m e n t第38卷第3期202丨年3月Vol.38 No.3Mar. 2021D O I:10.16791/j.c n k i.s j g.2021.03.048基于V e rilo g H D L智能评测平台的“计算机组成原理”课程贯通式实验模式张磊,王建萍,郑榕,何杰,齐悦(北京科技大学计算机与通信工程学院,北京100083 )摘要:针对“计算机组成原理”课程,以计算机系统能力培养为中心目标,提出贯通式实验教学模式,设 计了基础实践、综合实践、创新实践三个层次的八项实验,构建了以M I P S单周期处理器设计为核心的实验内容,着眼于学生五方面能力的培养。

基于自研的V e r i l o g H D L智能评测平台,探索了提升学生实验效率和教师验收效率的方法,设计了更为科学合理的实验考核方式。

通过一系列改革与实践,学生在计算机系统能力上得到较好的训练,为后续专业课程的学习打下了良好基础,教师的实验教学水平也迈上一个新台阶。

关键词:M I P S单周期处理器;计算机组成原理实验;V e r i l o g H D L;智能评测平台中图分类号:T P301-4;G642文献标识码:A文章编号:1002-4956(2021)03-0236-06Through experiment model of “Computer organization’’ course based on VerilogHDL intelligent evaluation platformZHANG Lei,WANG Jianping,ZHENG Rong,HE Jie,QI Yue(School o f C o m p u t e r a n d C o m m u n i c a t i o n Engineering, University o f Science a n d T e c h n o l o g y Beijing, Beijing 100083, C h ina)A b s t r a c t:B a s e d o n the “C o m p u t e r o r g a n i z a t i o n”c o u r s e a n d b y t a k i n g the cultivation o f c o m p u t e r s y s t e m ability as the central goal, this p a p e r puts f o r w a r d a t h r o u g h e x p e r i m e n t a l t e a c h i n g m o d e l, a n d d e s i g n s eight e x p e r i m e n t s o n the basis o f basic practice, c o m p r e h e n s i v e practice a n d i n n o vative practice at the three levels a n d constructs thee x p e r i m e n t a l c o n t e n t w i t h M I P S single cy c l e p r o c e s s o r d e s i g n as the core,f o c u s i ng o n the cultivation o f students' ability in five aspects. B a s e d o n the s e l f-d e v e l o p e d V e r i l o g H D L intelligent e v a l u a t i o n platform, the m e th o d s toi m p r o v e s t u d e n t s’e x p e r i m e n t a l efficiency a n d t e a c h e r s’a c c e p t a n c e efficiency are expl o r e d, a n d a m o r e scientific a n dr e a s o n a b l e e x p e r i m e n t a l a s s e s s m e n t m e t h o d is desi g n e d. T h r o u g h a series o f r e f o r m a n d practice, students get better training for c o m p u t e r s y s t e m ability, w h i c h lays a g o o d f o u n d a t i o n for the f o l l o w-u p professional courses, a n dt e a c h e r s5 e x p e r i m e n t a l te a c h i n g level h a s also s t e p p e d to a n e w level.K e y w o r d s:M I P S single c y c l e processor; c o m p u t e r o r g a n i z a t i o n e x p e r i m e n t; V e r i l o g H D L; intelligent ev a l u a t i o np l a t f o r mi贯通式实验教学模式近年来,我校计算机专业的课程体系和实验教学 内容不断改革创新,正逐步推进贯通式教学+2]。

VHDL硬件描述语言与数字逻辑电路设计 第1章

图1-2 六进制约翰逊计数器原理图

12

与六进制计数器模块设计一样,系统的其它模块也按此 方法进行设计。在所有硬件模块设计完成以后,再将各模块 连接起来,进行调试。如有问题,则进行局部修改,直至整 个系统调试完毕为止。

由上述设计过程可以看到,系统硬件的设计是从选择具 体元器件开始的,并用这些元器件进行逻辑电路设计,完成 系统各独立功能模块的设计,然后将各功能模块连接起来, 完成整个系统的硬件设计。上述过程从最底层开始设计,直 至最高层设计完毕,故将这种设计方法称为自下至上的设计 方法。

26

第二层次是RTL方式描述。这一层次称为寄存器传输描 述(又称数据流描述)。如前所述,用行为方式描述的系统结 构的程序其抽象程度高,是很难直接映射到具体的逻辑元件 结构用硬件来实现的。要想得到硬件的具体实现,必须将行 为方式描述的VHDL语言程序改写为RTL方式描述的VHDL 语言程序。也就是说,系统采用RTL方式描述,才能导出系 统的逻辑表达式,才能进行逻辑综合。当然,这里所说的可 以进行逻辑综合是有条件的,它是针对某一特定的逻辑综合 工具而言的。

16

传统的硬件电路设计方法已经沿用了几十年,是目前广 大电子工程师所熟悉和掌握的一种方法。但是,随着计算机 技术、大规模集成电路技术的发展,这种传统的设计方法已 大大落后于当今技术的发展。一种崭新的、采用硬件描述语 言的硬件电路设计方法已经兴起,它的出现给硬件电路设计 带来了一次重大的变革。

17

1.2 利用硬件描述语言的硬件电路 设计方法

5

要设计一个六进制计数器,其方案是多种多样的,但是 摆在设计者面前的一个首要问题是如何选择现有的逻辑元器 件构成六进制计数器。设计六进制计数器首先从选择逻辑元 器件开始。

第一步,选择逻辑元器件。由数字电路的基本知识可知, 可以用与非门、或非门、D触发器、JK触发器等基本逻辑元 器件来构成一个计数器。设计者根据电路尽可能简单、价格 合理、购买和使用方便等原则及各自的习惯来选择构成六进 制计数器的元器件。本例中选择JK触发器和D触发器作为构 成六进制计数器的主要元器件。

VHDL硬件描述语言与数字逻辑电路设计第三版课程设计

VHDL硬件描述语言与数字逻辑电路设计第三版课程设计本次课程设计旨在帮助大家深入理解VHDL硬件描述语言和数字逻辑电路设计的相关知识,提高大家的实践能力和设计能力。

本文将对课程设计的要求和实现方法进行详细说明。

课程设计要求本次课程设计要求大家完成一个基于VHDL的数字逻辑电路设计,包括以下要求:1.手动编写VHDL程序,对指定的数字电路进行仿真分析,并输出相应的波形图。

2.设计一个数字电路,要求该电路可完成特定的逻辑功能,例如加法器、多路选择器等。

3.基于现实的场景需求,完成一个实际的数字电路设计。

例如,实现一个音乐播放器控制器、机器人控制器等。

设计步骤步骤一:了解VHDL语言和数字逻辑电路设计原理在进行数字电路设计之前,需要先理解VHDL语言和数字逻辑电路设计原理。

VHDL语言是一种硬件描述语言,主要用于描述数字逻辑电路。

数字逻辑电路由基本的逻辑单元组成,包括与门、或门、非门等,通过组合这些逻辑单元可以实现更复杂的逻辑电路设计。

步骤二:选择仿真工具选择一款仿真工具进行仿真分析。

常见的仿真工具有ModelSim、Xilinx ISE 等。

步骤三:编写VHDL程序编写VHDL程序,对指定的数字电路进行仿真分析。

根据实际需要,可以选择不同的VHDL语言结构进行编写。

步骤四:仿真分析在仿真工具中进行仿真分析,根据VHDL程序模拟出相应的波形图。

步骤五:设计数字电路基于数字逻辑电路设计原理,设计出特定的数字电路。

需要首先确定电路所需要的逻辑功能,然后根据这个功能设计出合适的电路。

步骤六:实现实际场景需求参考现实的场景需求,设计出一个实际的数字电路,并进行调试测试。

VHDL程序编写规范在编写VHDL程序时,需要遵循一定的编写规范,以保证程序的可读性和可维护性。

1.命名规范:变量和信号的命名应具有较好的描述性,易于理解和记忆。

2.缩进规范:代码缩进应该统一,便于代码的阅读和理解。

3.注释规范:代码中应加入必要的注释,解释各个模块的功能和作用。

《FPGA 应用开发》课程标准

《FPGA应用开发》课程标准课程名称:FPGA应用开发课时数:64 学分:4适用专业:智能产品开发与应用1.前言1.1课程的性质本课程是集成电路技术专业群共享课程,智能产品开发与应用专业根据培养目标,重在培养学生针对FPGA特定领域的应用设计、集成电路设计以及芯片验证能力。

掌握通用的FPGA 设计方法,能正确使用EDA工具,分析和论证确定基于FPGA的系统实现方案,编写基于FPGA的数字系统硬件描述语言Verilog程序,进一步熟悉EDA工具的编辑、编译、仿真及下载验证实现系统调试,使学生掌握FPGA系统初步设计的步骤和方法。

本课程学习以《数字电子技术》、《C语言程序设计》为基础和先导,也是进一步学习智能产品设计、集成电路设计等课程和开展毕业设计的基础。

1.2设计思路随着信息产业以及微电子技术的持续发展,FPGA的应用范围已经遍及航空航天、汽车、医疗、工业控制等领域。

当今集成电路芯片的种类繁多,而且每种芯片的功能、复杂程度都存在很大差异,技术的快速更新要求电子产品从业人员拥有更专业、更扎实的硬件语言编程知识和能力,才能够利用FPGA技术在纷繁复杂的应用场合。

Verilog语言作为一种应用广泛的硬件设计语言,掌握其编程能力是集成电路类与电子类专业学生毕业后的增值能力之一。

通过对该课程的学习,训练学生能够熟练地使用QuartusII等常用EDA软件对FPGA作一些基础电路系统的设计,同时能较好地使用Verilog语言设计简单的数字逻辑电路和逻辑系统,学会行为仿真与FPGA相关硬件测试技术。

这些都是智能产品开发、集成电路设计和测试岗位最为重要的能力,因此本课程在智能产品开发、微电子专业中处于非常重要的地位,应当作为专业核心课程和必修课程。

本课程立足于培养学生的实际能力,对课程内容的选择标准作了改革,打破以知识传授为主要特征的传统学科课程模式,转变为以工作任务为中心来组织课程内容和课程教学,让学生通过完成具体项目来构建相关理论知识,并发展职业能力。

《Verilog HDL硬件描述语言》实验教学大纲

《Verilog HDL硬件描述语言》实验教学大纲

课程代码:MICR3001

课程名称:Verilog HDL硬件描述语言

英文名称:Verilog HDL

实验室名称:微电子实验室

课程学时:72实验学时:18

一、本课程实验教学目的与要求

通过实验要求学生掌握用Verilog HDL硬件描述语言进行集成电路设计的流程和方法。

学会使用Max+plusⅡ,QuartusⅡ设计软件,掌握从HDL源代码的输入→编译→仿真→管脚锁定→下载全过程。

学会用ModelSim设计软件,用Verilog HDL编写测试码对设计模块进行仿真。

二、主要仪器设备及现有台套数

PC,现有35台; EDA实验箱,25套;

1、实验报告:有设计代码,仿真结果,管脚排列,验证结果。

2、考核方式:

(1)实验课的考核方式:教师验收评定成绩。

(2)实验课考核成绩:根据实验完成情况和实验报告是否完整确定,实验课成绩占课程总成绩的10%。

五、实验教材、参考书

1、教材:在编

2、参考书:J.Bhasker著,夏宇闻等译《Verilog HDL入门》.北京航空航天大学出版社.2008出版。

你的Basys 3第一个入门实验官方指导手册

位于母公司美国国家仪器NI中国总部大楼内电话:+86-21-58893151邮箱:china.sales@“你的Basys 3第一个入门实验”官方指导手册目录1.Basys3硬件电路………………………………………………………………………...P31.1 电源电路…………………………………………………………………..……......P51.2 LED灯电路…………………………………………………………………..……..P61.3 拨码开关电路………………………………………………………………..……...P71.4 按键电路…………………………………………………………………..……......P81.5 数码管电路…………………………………………………………………..……...P81.6 VGA电路…………………………………………………………………..…….....P91.7 I/O扩展电路…………………………………………………………………..….P101.8 FPGA调试及配置电路…………………………………………………………..P102.Basys3电路实验–七段数码管显示实验………………………………………..…P12第一章Basys3 硬件电路Basys3是围绕着一个Xilinx Artix®-7 FPGA芯片XC7A35T-1CPG236C搭建的,它提供了完整、随时可以使用的硬件平台,并且它适合于从基本逻辑器件到复杂控制器件的各种主机电路。

Basys3板上集成了大量的I/O设备和FPGA所需的支持电路,让您能够构建无数的设计而不需要其他器件。

主要规格/特殊功能产品规格:Basys3为想要学习FPGA和数字电路设计的用户提供一个理想的电路设计平台。

Basys3板提供完整的硬件存取电路,可以完成从基本逻辑到复杂控制器的设计。

四个标准扩展连接器配合用户设计的电路板,或Pmods(Digilent设计的A / D和D / A转换,电机驱动器,传感器输入等)其他功能。

vhdl硬件描述语言与数字逻辑电路设计

VHDL (VHSIC Hardware Description Language) is like the architect's blueprint for digital systems. It's a language that hardware engineers use to paint a vivid picture of how these systems are structured and how they behave. Think of it as a virtual playground where designers can play around with digital logic circuits before they bring them to life. With VHDL, they can test and verify their creations, ensuring that everything runs smoothly before it's time to hit the hardware. In other words, VHDL is the ultimate tool for digital wizards to work their magic and bring their ideas to life!VHDL(VHSIC硬件描述语言)就像建筑师的数字系统蓝图。

这种语言是硬件工程师用来描绘这些系统的结构及其表现的生动画面。

把它当作一个虚拟游乐场,设计者可以在带他们复活前用数字逻辑电路来游玩。

通过VHDL,他们可以测试和验证他们的创造,确保一切在击中硬件之前顺利运行。

VHDL是数位魔法师运用魔法,将想法带入生命的终极工具!One of the coolest things about VHDL is that it lets you test out your digital creations virtually before you actually build them. It's like a digital playground where you can play around with your ideas and see how they behave without spending a ton of money on physical prototypes. And the best part? You cancatch any design boo-boos early on and make sure everything is working smoothly. Not only that, VHDL also lets you create these little building blocks, kind of like digital Legos, that you can easily snap together to make bigger and better designs. It's like having a superpower for makingplex digital systems with lots of parts moving at the same time. So basically, VHDL is like the superhero of digital design – making things faster, cheaper, and a whole lot more fun!VHDL最酷的一件事就是它让你在实际建造之前测试你的数字创造。

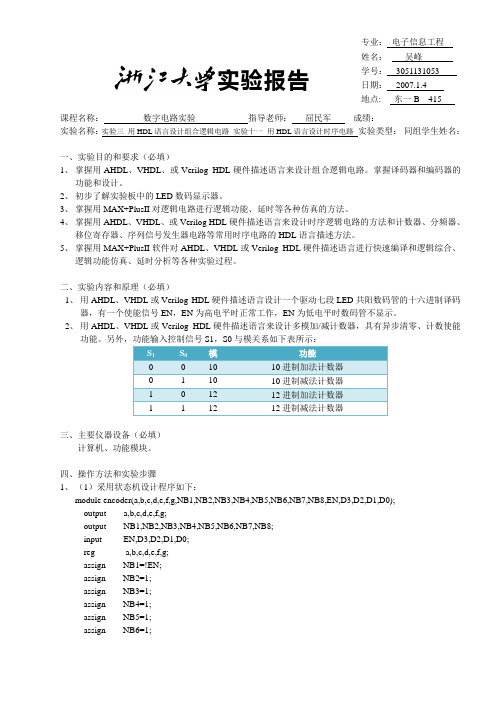

浙大数字电路实验报告

实验报告课程名称:_________数字电路实验____________指导老师:___屈民军___ 成绩:__________________ 实验名称:实验三 用HDL 语言设计组合逻辑电路 实验十一 用HDL 语言设计时序电路 实验类型:_同组学生姓名:_一、实验目的和要求(必填)1、 掌握用AHDL 、VHDL 、或Verilog HDL 硬件描述语言来设计组合逻辑电路。

掌握译码器和编码器的功能和设计。

2、 初步了解实验板中的LED 数码显示器。

3、 掌握用MAX+PlusII 对逻辑电路进行逻辑功能、延时等各种仿真的方法。

4、 掌握用AHDL 、VHDL 、或Verilog HDL 硬件描述语言来设计时序逻辑电路的方法和计数器、分频器、移位寄存器、序列信号发生器电路等常用时序电路的HDL 语言描述方法。

5、 掌握用MAX+PlusII 软件对AHDL 、VHDL 或Verilog HDL 硬件描述语言进行快速编译和逻辑综合、逻辑功能仿真、延时分析等各种实验过程。

二、实验内容和原理(必填)1、 用AHDL 、VHDL 或Verilog HDL 硬件描述语言设计一个驱动七段LED 共阳数码管的十六进制译码器,有一个使能信号EN ,EN 为高电平时正常工作,EN 为低电平时数码管不显示。

2、 用AHDL 、VHDL 或Verilog HDL 硬件描述语言来设计多模加/减计数器,具有异步清零、计数使能S 1 S 0 模 功能0 0 10 10进制加法计数器 0 1 10 10进制减法计数器 1 0 12 12进制加法计数器 111212进制减法计数器三、主要仪器设备(必填)计算机、功能模块。

四、操作方法和实验步骤1、 (1)采用状态机设计程序如下:module encoder(a,b,c,d,e,f,g,NB1,NB2,NB3,NB4,NB5,NB6,NB7,NB8,EN,D3,D2,D1,D0); output a,b,c,d,e,f,g;output NB1,NB2,NB3,NB4,NB5,NB6,NB7,NB8; input EN,D3,D2,D1,D0; reg a,b,c,d,e,f,g; assign NB1=!EN; assign NB2=1; assign NB3=1; assign NB4=1; assign NB5=1; assign NB6=1;专业: 电子信息工程 姓名: 吴峰学号: 3051131053 日期: 2007.1.4 地点: 东一B 415assign NB7=1;assign NB8=1;always @(D3 or D2 or D1 or D0)begincase({D3,D2,D1,D0})4'b0000: {a,b,c,d,e,f,g}=7'b0000001;4'b0001: {a,b,c,d,e,f,g}=7'b1001111;4'b0010: {a,b,c,d,e,f,g}=7'b0010010;4'b0011: {a,b,c,d,e,f,g}=7'b0000110;4'b0100: {a,b,c,d,e,f,g}=7'b1001100;4'b0101: {a,b,c,d,e,f,g}=7'b0100100;4'b0110: {a,b,c,d,e,f,g}=7'b0100000;4'b0111: {a,b,c,d,e,f,g}=7'b0001111;4'b1000: {a,b,c,d,e,f,g}=7'b0000000;4'b1001: {a,b,c,d,e,f,g}=7'b0001100;4'b1010: {a,b,c,d,e,f,g}=7'b0001000;4'b1011: {a,b,c,d,e,f,g}=7'b1100000;4'b1100: {a,b,c,d,e,f,g}=7'b0110001;4'b1101: {a,b,c,d,e,f,g}=7'b1000010;4'b1110: {a,b,c,d,e,f,g}=7'b0110000;4'b1111: {a,b,c,d,e,f,g}=7'b0111000;endcaseendendmodule(2)进行仿真,结果如下:(3)延时分析:(4)管脚分配a接73脚,b接76脚,c接4脚,d接10脚,e接8脚,f接74脚,g接81脚;NB1接79脚,NB2接75脚,NB3接77脚,NB4接80脚,NB5接9脚,NB6接11脚,NB7接15脚,NB8接12脚;D3接52脚,D2接51脚,D1接50脚,D0接49脚;EN接1脚;2、(1)用行为描述方法设计程序如下:module count(q,s1,s0,clear,clk,EN);output[3:0] q;input s1,s0;input clk,clear,EN;reg[3:0] q;always @(posedge clk or negedge clear)if(!clear) q=0;elsecase({s1,s0})2’b00: if(q==4’b1001) q=0; else q=q+EN;2’b01: if(q==4’b0000) q=4’b1001; else q=q-EN;2’b10: if(q==4’b1011) q=0; else q=q+EN;2’b11: if(q==4’b0000) q=4’b1011; else q=q-EN;endcaseendmodule(2)仿真结果如下:a、b、c、d、(3)延时分析:五、实验数据记录和处理按照上面的管脚分配将程序下载到实验模板进行实验。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验3 基于硬件描述语言的电路设计一、实验目的1 、了解可编程数字系统设计的流程;2 、掌握Quartus II 软件的使用方法;3 、掌握采用硬件描述语言设计数字系统的方法和流程。

二、实验设备1、计算机:Quartus II 软件2、Altera DE0三、实验内容要求1:学习并掌握硬件描述语言(VHDL或Verilog HDL);熟悉门电路的逻辑功能,并用硬件描述语言实现门电路的设计。

参考“参考内容1”中给出的与门源程序,编写一个异或门逻辑电路。

1)用QuartusII波形仿真验证;2)下载到DE0开发板验证。

要求2:熟悉中规模器件译码器的逻辑功能,用硬件描述语言实现其设计。

参考“参考内容2”中给出的将8421BCD码转换成0-9的七段码译码器源程序,编写一个将二进制码转换成0-F 的七段码译码器。

1)用QuartusII波形仿真验证;2)下载到DE0开发板,利用开发板上的数码管验证。

要求3:熟悉时序电路计数器的逻辑功能,用硬件描述语言实现其设计。

参考“参考内容3”中给出的四位二进制加减计数器的源程序,编写一个计数器。

1)用QuartusII波形仿真验证;2)下载到DE0开发板验证。

要求4:熟悉分频电路的逻辑功能,并用硬件描述语言实现其设计。

参考“参考内容4”中给出的50M分频器的源程序,编写一个能实现占空比50%的5M和50M分频器即两个输出,输出信号频率分别为10Hz和1Hz。

1)下载到DE0开发板验证。

(提示:利用DE0板上已有的50M晶振作为输入信号,通过开发板上两个的LED灯观察输出信号)。

电路框图如下:四、实验结果1、用硬件描述语言(VHDL 或Verilog HDL)实现一个异或门电路。

VHDL源程序:Library ieee;use ieee.std_logic_1164.all;entity vhdl isport(A,B:IN std_logic;C:OUTstd_logic);END vhdl;Architecture fwm of vhdl isbeginC<=A XOR B;END;波形图:引脚对应表2、用硬件描述语言实现将四位二进制码转换成0-F 的七段码译码器。

VHDL源文件:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY digital ISPORT (data_in:IN STD_LOGIC_VECTOR(3 DOWNTO 0);dis_out:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END digital;ARCHITECTURE fwm OF digital ISBEGINPROCESS(data_in)BEGINCASE data_in ISWHEN"0000"=>dis_out<="1000000";--显示0WHEN"0001"=>dis_out<="1111001";--显示1WHEN"0010"=>dis_out<="0010010";--显示2WHEN"0011"=>dis_out<="0000110";--显示3WHEN"0100"=>dis_out<="0001101";--显示4WHEN"0101"=>dis_out<="0100100";--显示5WHEN"0110"=>dis_out<="0100000";--显示6WHEN"0111"=>dis_out<="1001110";--显示7WHEN"1000"=>dis_out<="0000000";--显示8WHEN"1001"=>dis_out<="0000100";--显示9WHEN"1010"=>dis_out<="0001000";--显示AWHEN"1011"=>dis_out<="0100001";--显示bWHEN"1100"=>dis_out<="1110000";--显示CWHEN"1101"=>dis_out<="0000011";--显示dWHEN"1110"=>dis_out<="0110000";--显示EWHEN"1111"=>dis_out<="0111000";--显示FWHEN OTHERS=>dis_out<="1111111";--灭灯,不显示END CASE;END PROCESS;END fwm;波形图:引脚对应表:3、用硬件描述语言实现四位二进制加法或减法计数器,并用一位7段码显示减法计数器VHDL源文件LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY EX3 ISPORT ( clk,RST,MLZ : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0); COUT : OUT STD_LOGIC);END EX3;ARCHITECTURE fwm OF EX3 ISSIGNAL Q1 : STD_LOGIC_VECTOR (3 DOWNTO 0); BEGINPROCESS(clk,RST,Q1,MLZ)BEGINIF RST ='0' THEN Q1<=(OTHERS =>'0');COUT<='0'; ELSIF clk'EVENT AND clk='1' THENIF MLZ='0' THENQ1<=Q1+1;COUT<='0';IF Q1 >="1111"THEN Q1<=(OTHERS =>'0');COUT<='1'; END IF;ELSIF MLZ='1' THENQ1<=Q1-1;COUT<='0';IF Q1 <="0000"THEN Q1<=(OTHERS =>'1');COUT<='1'; END IF;END IF;END IF;END PROCESS;DOUT<=Q1 ;END fwm;减法计数器波形图:引脚对应表CLK对应开发板上的G21引脚4、用硬件描述语言实现5M 和50M 分频器(占空比为50% ),即两个输出信号频率分别为10Hz 和1Hz。

VHDL源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY EX4 ISPORT(clk,AS: IN STD_LOGIC;clk_out1: OUT STD_LOGIC);END EX4;ARCHITECTURE fwm OF EX4 ISSIGNAL A: STD_LOGIC;CONSTANT m: INTEGER:=25000000;SIGNAL tmp1: STD_LOGIC;SIGNAL tmp2: STD_LOGIC;BEGINPROCESS(clk,AS,A)VARIABLE cout1 : INTEGER range 0 to 50000000;VARIABLE cout2 : INTEGER range 0 to 5000000;BEGINIF clk'EVENT AND clk='1' THENcout1:=cout1+1;IF cout1<=m THEN tmp1<='0';ELSIF cout1<m*2 THEN tmp1<='1';ELSE cout1:=0;END IF;cout2:=cout2+1;IF cout2<=m/10 THEN tmp2<='0';ELSIF cout2<m/5 THEN tmp2<='1';ELSE cout2:=0;END IF;IF AS='1' THEN A<=tmp1;ELSE A<=tmp2;END IF;END IF;END PROCESS;clk_out1<=A;END fwm;五、心得体会实验结束后要进行验证,利用数码管在电路板上显示出的信息进行验证,确保实验结果的准确性,而且在编译程序时唇线的问题不少,总工会出现编译运行错误,但最终还是完成了。